**Doctoral Thesis**

# Strained Silicon Fin-Based High Electron Mobility Transistor for Optimal Device Design of Performance and Reliability

Sung-Ho Kim

Department of Electrical Engineering

Ulsan National Institute of Science and Technology

# Strained Silicon Fin-Based High Electron Mobility Transistor for Optimal Device Design of Performance and Reliability

Sung-Ho Kim

Department of Electrical Engineering

Ulsan National Institute of Science and Technology

# Strained Silicon Fin-Based High Electron Mobility Transistor for Optimal Device Design of Performance and Reliability

A thesis submitted to

Ulsan National Institute of Science and Technology

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

Sung-Ho Kim

12/15/2020 of submission

Approved by

Advisor

Kyung Rok Kim

# Strained Silicon Fin-Based High Electron Mobility Transistor for Optimal Device Design of Performance and Reliability

Sung-Ho Kim

This certifies that the thesis of Sung-Ho Kim is approved.

12/15/2020

Signature

Advisor: Prof. Kyung Rok Kim

Signature

Thesis Committee Member: Prof. Jiwon Chang

Signature

Thesis Committee Member: Prof. Kibog Park

Signature

Thesis Committee Member: Prof. Jongwon Lee

Signature

Thesis Committee Member: Prof. Rock-Hyun Baek

#### Abstract

I present the predictions of scaling and process variation for a strained-silicon (s-Si) fin-based high electron mobility transistor (FinHEMT) with well-tempered, short-channel characteristics. The operation principle of FinHEMT, which the SiGe behaves as an additional insulator forming quantum well (QW) channel in s-Si with the conduction band off-set improving the effective electron mobility, is clearly shown. By calibrating with experimental data, the high electron mobility ( $\sim$ 1100 cm<sup>2</sup>/Vs) and enhanced effective mobility (up to 2×) of the FinHEMT is predicted by suppressing the surface roughness scattering effect in the s-Si QW channel.

An extensive simulation is performed to find the optimized structure. The Si capping layer is replaced as high- $\kappa$  dielectric insulator to prevent the gate leakage current, and undoped SiGe layer is eliminated because the conduction band off-set ( $\Delta E_{\rm C}$ ) is enough to confine the electrons in s-Si QW channel. The parameter analysis is performed for both long and short channel regime of FinHEMT. Eventually, suppressed OFF-current ( $I_{\rm OFF}$ ) and improved ON-current ( $I_{\rm ON}$ ) with enhanced mobility can be achieved by fabrication process optimization and 10<sup>19</sup> cm<sup>-3</sup> of doping concentration and 2 nm thick of SiGe. Especially in short channel regime, maximized  $I_{\rm ON}$  and gate controllability clarify the FinHEMT optimization.

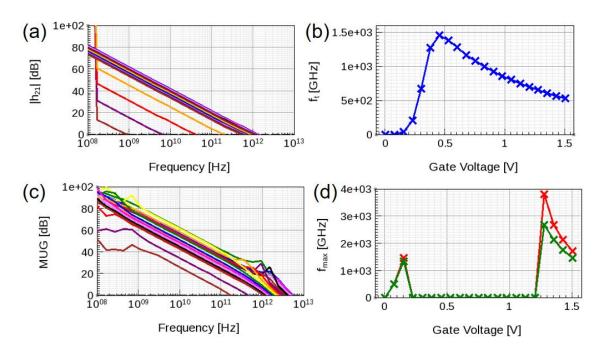

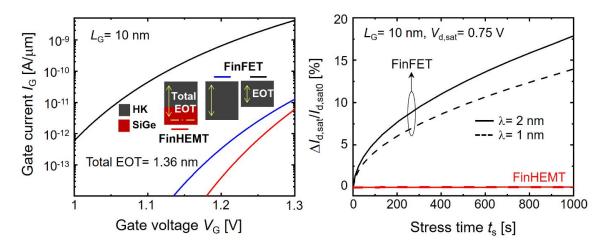

With enhanced effective mobility, excellent scalability of the FinHEMT  $I_{ON} > 1.1 \text{ mA}/\mu\text{m}$  at  $L_G = 10 \text{ nm}$  is predicted because the high channel mobility can reduce the series resistivity in the scaled device. Owing to this low series resistivity, The FinHEMT has little effect on the process variation. Moreover, the unique operation principle of FinHEMT, which the part of doped SiGe layer behaves as an additional high- $\kappa$  dielectric insulator, enhances the hot carrier reliability of FinHEMT by suppressing gate leakage current.

# Contents

Abstract

| Contents                                               |

|--------------------------------------------------------|

| List of Figures                                        |

| List of Tables                                         |

| Nomenclature                                           |

|                                                        |

| 1. Introduction                                        |

| 1.1 Transistor scaling technology                      |

| 1.1.1 Mobility degradation                             |

| 1.1.2 Reliability degradation by hot carrier injection |

| 1.2 Boost-up the channel mobility                      |

| 1.2.1 Compound/Ge MOSFET                               |

| 1.2.2 High electron mobility transistor (HEMT)         |

| 1.3 Motivation                                         |

|                                                        |

| 2. Fabrication process                                 |

| 2.1 Fabrication process and its optimization           |

| 2.2 Simulation models                                  |

|                                                        |

| 3. Operation principle of FinHEMT (Long channel)       |

| 3.1 Device parameter analysis                          |

| 3.2 Enhanced effective mobility                        |

#### ULSAN NATIONAL INSTITUTE OF SCIENCE AND TECHNOLOGY

| 4. | Short channel characteristics                    | 32 |

|----|--------------------------------------------------|----|

|    | 4.1 Performance optimization                     | 32 |

|    | 4.2 Variablility and scalability predictions     | 39 |

|    | 4.3 RF characteristics: cutoff/maximum frequency | 45 |

|    | 4.4 Improved reliability                         | 47 |

|    |                                                  |    |

| 5. | Conclusion                                       | 52 |

|    |                                                  |    |

| 6. Remaining work to be done |

|------------------------------|

|------------------------------|

# List of Figures

| Figure 1-1. Inter | rface trap f | formation and | gate leakage | e current mechanism | by hot carrier |

|-------------------|--------------|---------------|--------------|---------------------|----------------|

| injection         |              |               |              |                     |                |

**Figure 3-3.** Conduction band energy and electron density with  $\Delta E_{\rm C}$  variation at  $V_{\rm OV}$ = 0.8 V. As the  $\Delta E_{\rm C}$  increases, electron density in s-Si channel increases, while decreases in SiGe layer...23

**Figure 3-5.** (a) Transfer *I-V* curves of FinHEMT and FinFET for different  $t_{SiGe}$  with  $\Delta E_C = 0.2$  eV. Gate capacitance ( $C_G$ ) and calculated field effect mobility ( $\mu_{FE}$ ) at (b) low  $V_{OV} = 0.4$  V and (c) high  $V_{OV} = 0.8$  V for various  $t_{SiGe}$  and  $N_{SiGe}$  of FinHEMT benchmarking with FinFET. ... 26

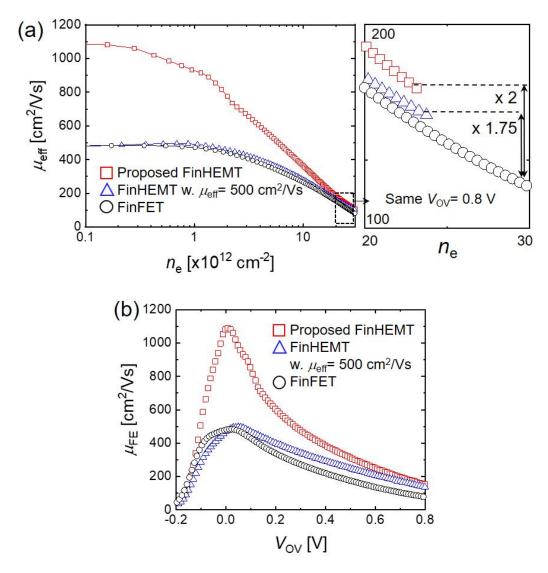

**Figure 3-7.** Universal  $\mu_{\text{eff}}$  vs. e-density ( $qn_e = C_G V_{OV}$ ) of FinFET and FinHEMT with experimental data [9], [28]. Inset: 2 times enhanced  $\mu_{\text{eff}}$  in s-Si channel in FinHEMT at same  $V_{OV} = 0.8 \text{ V}.$  28

Figure 3-8. (a) Effective mobility and (b) field-effect mobility with 500 cm²/Vs low-field mobility of FinHEMT.

29

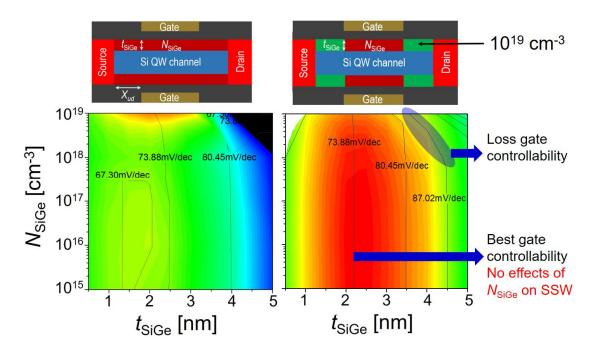

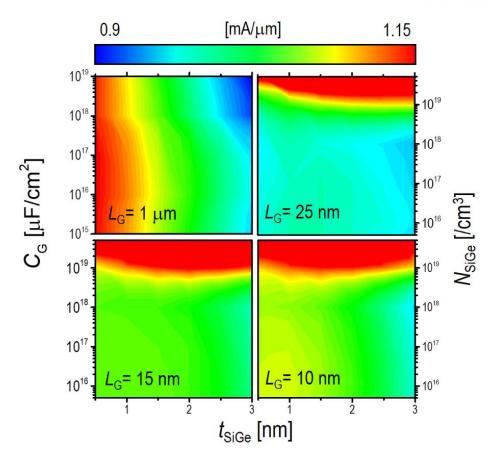

**Figure 4-1.**  $I_{ON}$  contour plots for (a) FinHEMT, and (b) considering diffusion process through the SiGe layer from source/drain to under the gate region. Optimized  $t_{SiGe}$  and  $N_{SiGe}$  following scaling rule. With  $t_{SiGe} = 2 \text{ nm}$  and  $N_{SiGe} = 10^{19} \text{ cm}^{-3}$ , the  $I_{ON}$  is maximized with 73.88 mV/dec of SS.

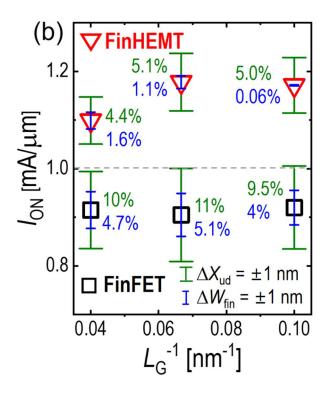

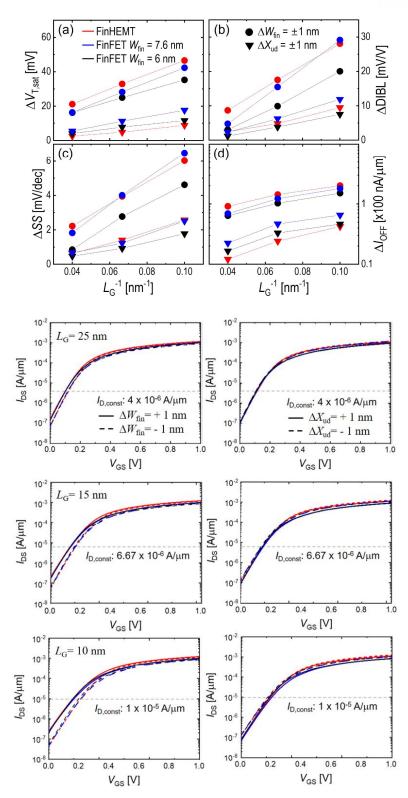

**Figure 4-6.**  $I_{\text{ON}}$  variability with process variation of  $X_{\text{ud}}$  and  $W_{\text{fin}}(\pm 1 \text{ nm})$  when scaling  $L_{\text{G}} = 25, 15, 10 \text{ nm}$  at  $V_{\text{DD}} = 1, 0.93, 0.9 \text{ V}$  with total EOT= 1.36 (1), 0.9 (0.9), 0.85 (0.85) nm of FinHEMT (FinFET).

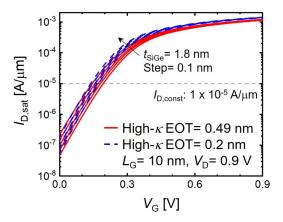

**Figure 4-9.** Contour plots of  $I_{ON}$  in FinHEMT to the gate dielectric EOT and  $V_{DD}$  scaling for  $L_G$ = 15 nm and 10 nm. 43

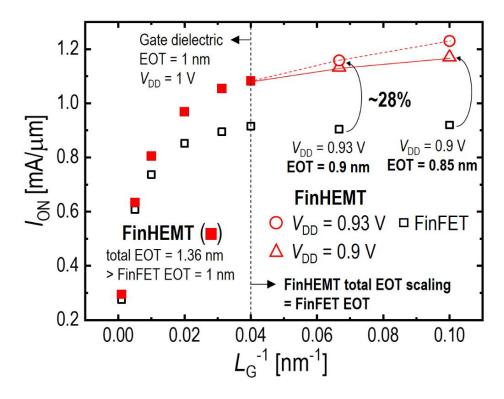

**Figure 4-11.** (a)  $|h_{21}|$  (b) cut-off frequency  $f_T$  using unit gain method (c) MUG, and (d) maximum frequency  $f_{max}$  using unit gain method and extrapolation method for FinHEMT. .. 45

| Figure 4-13. (a) Injection probability component effects for FinHEMT (b) Injection probability |

|------------------------------------------------------------------------------------------------|

| with $\lambda_{ins} = 1, 2$                                                                    |

| <b>Figure 4-14.</b> Interface trap density as a function of depassivation constant with initial $N_{it} = 10^6$ , |  |

|-------------------------------------------------------------------------------------------------------------------|--|

| $10^8$ , $10^{10}$ cm <sup>-2</sup> and $V_{DD}$ = 1.0, and 3.0 V                                                 |  |

| <b>Figure 4-15.</b> $\varepsilon_{\text{th}}$ , $\varepsilon_{\text{a}}$ sensitivity analysis on (a),(c) $N_{\text{it}}$ and (b),(d) $\tau_{\text{D}}$ | 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                                        |   |

| Figure 4-16. (a) Gate leakage current (b) drain current variation                                                                                      | 1 |

# List of Tables

| <b>Table I.</b> The extracted current density ( <i>J</i> ), mobility ( $\mu$ ), e-density ( <i>n</i> ), and calculated resistivity |  |

|------------------------------------------------------------------------------------------------------------------------------------|--|

| $ \rho_{Xud} $ for the gate underlap region                                                                                        |  |

# Nomenclature

| FET     | Field-effect transistor                     |

|---------|---------------------------------------------|

| Si      | Silicon                                     |

| HEMT    | High electron mobility transistor           |

| FinHEMT | Fin-based high electron mobility transistor |

| FinFET  | Fin-based field-effect transistor           |

| SRS     | Surface roughness scattering                |

| s-Si    | Strained-silicon                            |

| НК      | High- $\kappa$                              |

| QW      | Quantum well                                |

| sSOI    | strained silicon-on-insulator               |

| HCI     | Hot carrier injection                       |

| RD      | Reaction-diffusion                          |

### 1. Introduction

#### 1.1 Transistor scaling technology

#### 1.1.1 Mobility degradation

Multi-gate transistors such as Fin-based field effect transistor (FinFET) and tri-gate field effect transistor are adopted as a mainstream technology to sub-10 nm due to its good gate controllability [1]-[4]. FinFET has been successfully scaled down to the state-of-the-art 5 nm technology node [5] using metal gate and high- $\kappa$  dielectric material. It is possible to make thick gate oxide with scaled down gate capacitance ( $C_G$ ) preventing gate dielectric tunneling and more aggressive gate oxide thickness scaling satisfies the device's target performance such as ON-current ( $I_{ON}$ ), OFF-current ( $I_{OFF}$ ) and ON/OFF current ratio ( $I_{ON}/I_{OFF}$ ). While scaling in sub-5 nm node, however, the  $I_{ON}$  of FinFET is saturated around at or below 1 mA/µm [6]-[8] because of the universal effective mobility ( $\mu_{eff}$ ) degradation dominated by surface roughness scattering (SRS) [9][10] and the increased series resistance by the gate underlap structure [11]-[13] between the source and drain to suppress the short channel effects such as drain induced barrier lowering (DIBL), threshold voltage roll-off ( $V_{T,roll-off}$ ), and gate induced drain leakage (GIDL) (underlap length  $X_{ud}$  is where the physical gate length  $L_g$  is less than the effective gate length  $L_{eff}$ , i.e.  $X_{ud}$  is negative).

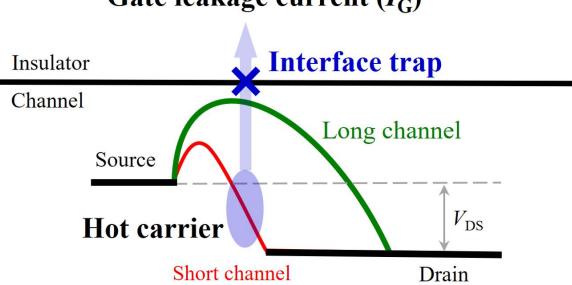

### 1.1.2 Reliability degradation by hot carrier injection

Although the aggressive scaling of gate oxide thickness achieves the target performance of devices, it causes the gate leakage current by hot carrier injection (HCI) from channel to insulator. HCI can be occurred by high electric field at drain side in short channel regime as shown in **Figure 1.2**. The injected hot carrier breaks off the hydrogen bond in the insulator and channel interface and the interface trap is formed by this hydrogen ion. Recently, interface trap formation is explained with reaction-diffusion (RD) theory [14] with fitting parameter of reaction constant (v) by electric field and HCI [15]. And the gate leakage current generation can be calculated by multiplication of hot carrier injection probability ( $P_{ins}$ ) as a function of the mean-free path in insulator ( $\lambda_{ins}$ ) to the drain current.

Gate leakage current (*I*<sub>G</sub>)

Figure 1-1. Interface trap formation and gate leakage current mechanism by hot carrier injection.

The mean-free path in insulator does not considered as a variable in Sentaurus TCAD, while it is reported as a function of inversion charge and lattice temperature [16]. In section 4.4, the effects of  $\lambda_{ins}$ on FinFET and FinHEMT is shown. Also, the device lifetime ( $\tau_D$ ), gate leakage current variation ( $\Delta I_G$ ), drain current variation ( $\Delta I_D$ ,) substrate current variation ( $\Delta I_{sub}$ ) and interface charge trap density ( $N_{it}$ ) are extensively verified with Sentaurus TCAD simulation comparing experimental data.

### 1.2 Boost-up the channel mobility

## 1.2.1 Compound/Ge MOSFET

Recently, new channel materials such as III-V compound semiconductor with high electron mobility for *n*-channel [17]-[19] and Ge with high hole mobility for *p*-channel [20]-[23] have been introduced on Si platform to boost-up channel mobility for high-performance CMOS but, the experimental values of  $\mu_{\text{eff}}$  on III-V/Ge inversion channel are significantly degraded from their intrinsically high bulk mobility values [24]-[26]. The expected manufacturing cost increase would be additional burden in economic aspects.

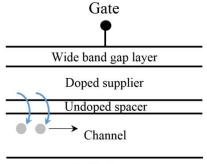

## 1.2.2 High electron mobility Transistor (HEMT)

To overcome the limitations in compound semiconductor MOSFETs, strained-silicon (s-Si)-based high electron mobility transistor (HEMT) minimized gate field effect by quantum-well (QW) channel is reported [27]-[29]. The electrons in channel can be accumulated by the lower conduction band energy of Si than that of SiGe. Eventually, the electrons in channel transferred from doped SiGe layer can flow from source to drain, thus, there is less gate electric field degrading the electron mobility. Even though the channel mobility is enhanced, however, the gate off-leakage current is significantly increased through a Si capping layer with a relatively low bandgap [30]. Figure 1.1 shows the schematic structure explaining the operation principle of s-Si HEMT.

Buffer layer

Figure 1-2. Operation principle of HEMT.

#### 1.2 Motivation

To adopt the advantages that excellent gate electrostatic of FinFET and high electron mobility of HEMT, a novel s-Si FinHEMT is proposed. FinHEMT is feasible by introducing a SiGe layer between the high- $\kappa$  (HK) gate dielectric insulator and s-Si channel of FinFET. The inserted SiGe layer forms the conduction band offset ( $\Delta E_C$ ) to separate the channel from the gate dielectric/channel interface by confining the electrons in the s-Si quantum well (QW) channel, resulting in effective suppression of the SRS effect. Enhanced effective mobility can break through the ON-current limitation of FinFET degrading the series resistance.

In this paper, we present a careful study on the device performance and hot carrier reliability of FinHEMT with optimized device structure. Our simulation reveals that the proposed FinHEMT can achieve enhanced mobility close to the Si bulk mobility. To analyze the variability and scalability of FinHEMT, the effects of various device parameters were extensively investigated. Moreover, the reliability of FinHEMT is improved compared with FinFET considering exact modeling of mean-free path and thickness of insulator.

## 2. Fabrication process

## Fabrication process and its optimization

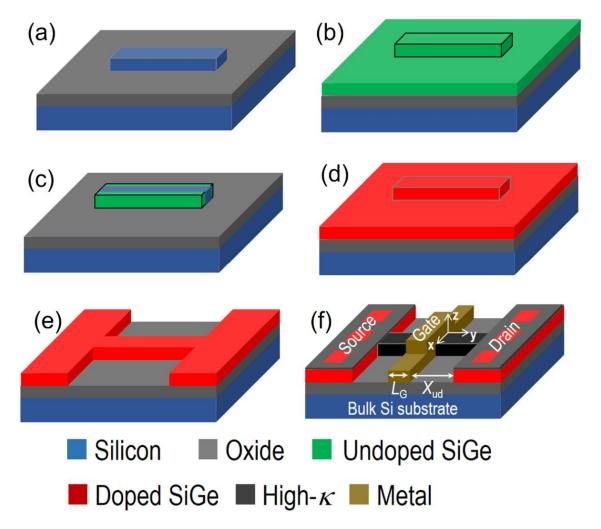

**Figure 2-1.** Fabrication process (a) Fin-first, (b) undoped SiGe deposition, (c) undoped SiGe etch, (c) doped SiGe deposition, (d) etching the doped SiGe layer as Source/Drain reservoir, and (f) final structure of proposed FinHEMT with device dimension parameters.

**Figure 2-1** shows the proposed novel FinHEMT fabrication process [31] for advantages combination of both FinFET and HEMT which are good gate controllability and high electron mobility respectively. Basic platform of FinHEMT is s-Si on insulator (sSOI) substrate. Firstly, the fin shape of top s-Si layer is etched for the channel and then, thin undoped SiGe layer, which is used as undoped spacer between channel and doped supply layer, is deposited on fin- sSOI layer. This undoped SiGe layer is etched to form the sidewalls of s-Si fin channel. Subsequently, deposited n-doped SiGe supply layer is etched

with a lithographical mask for the simultaneous formation of Source/Drain reservoirs and the sidewalls around s-Si fin channel. This point is distinguished from the conventional HEMT or FinFET process. It can be expected that doped SiGe layer for Source/Drain contacts can be placed close to the fin-channel and thus, reduce parasitic resistance which are usually exist in conventional HEMT structure for ohmic contact. Finally, nanoscale high- $\kappa$  dielectric such as hafnium oxide (HfO<sub>2</sub>) and metal-gate is formed to achieve high gate controllability and low gate-leakage mob. Based on this device structure, TCAD double gate HEMT device simulation is performed to analyze the electrical characteristics of the proposed FinHEMT.

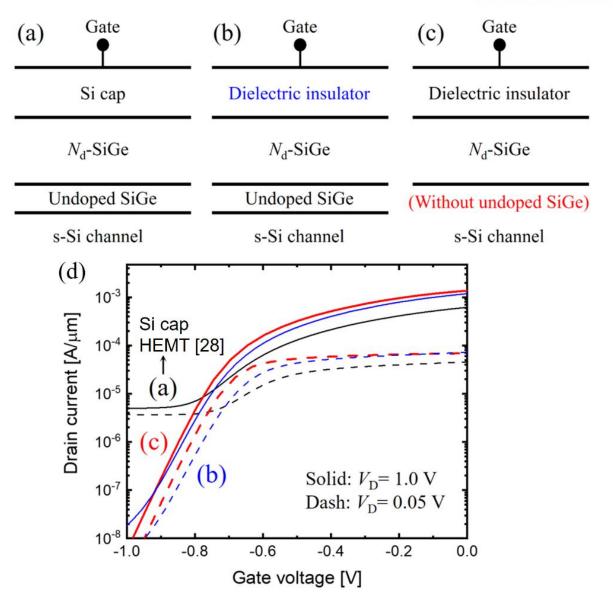

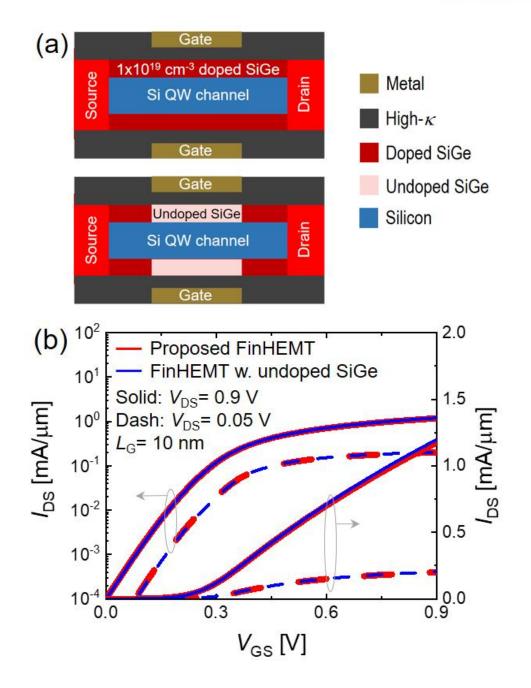

Figure 2-2 shows TCAD device simulation of double gate HEMT that is composed of 5-nm-thick  $1 \times 10^{19}$  cm<sup>-3</sup> doped SiGe, 3 nm undoped SiGe and 10 nm undoped s-Si channel. Gate length is 60 nm, HfO<sub>2</sub> thickness is 8 nm, and distance between gate and Source/Drain is 40 nm. Conduction band offset  $(\Delta E_C)$  between SiGe and s-Si is 0.2 eV which is enough to accumulate electrons transferred from doped SiGe layer to undoped s-Si channel with 1.02 eV band gap [32][33]. Drain currents as a function of gate voltage are shown in Figure 2-2 comparing (a) Si cap single-gate planar s-Si HEMT [28] with (b) HfO<sub>2</sub> cap double-gate FinHEMT. High OFF-current which is main weakness of conventional s-Si HEMT with Si cap is shown since relatively small Si bandgap results in high gate leakage current when it is at OFF-state. Also, Figure 2-2(c) shows the FinHEMT structure eliminated the undoped SiGe layer for improving the performance of the device. The subthreshold swing, ON-current, and OFF-current are improved because the  $\Delta E_C$  can prevent the electrons transferred to doped SiGe layer from QW channel.

Therefore, in case of FinHEMT with gate oxide (e.g.  $HfO_2$ ), on-current has been enhanced by the double-gate structural effect on fin channel and OFF-current has been reduced by the suppressed gate leakage and, simply doubled electron density and channel controllability. Through TCAD device simulation of FinHEMT as double-gate HEMT, on-current of 1.65 mA/µm and off-current of 11 pA/µm with the extremely high ON-OFF current ratio (=  $1.5 \times 10^8$ ) have been achieved on Si-compatible device platform. Moreover, good subthreshold swing (SSW) is observed as 63 mV/dec. Maximum depletion width of  $1 \times 10^{19}$  cm<sup>-3</sup> doped SiGe can be estimated 7.85 nm which is larger than the thickness (5 nm) of doped SiGe layer. Thus, FinHEMT gates can control whole of doped SiGe, undoped SiGe, and undoped s-Si channel which results in good SSW.

**Figure 2-2.** Structure optimization process from (a) Si cap HEMT [28], (b) replacing Si cap as dielectric insulator, and (c) without undoped SiGe layer.

#### 2.2 Simulation models

To form the  $\Delta E_{\rm C}$ , electron affinity (X) of s-Si is set as 4.295 eV rather than 4.05 eV for Si. And the bulk mobility value of 2600 cm<sup>2</sup>/Vs is used to match the experimental low-field mobility of s-Si FinFET [9]. Moreover, "eQuantumPotential" model is used to clarify s-Si QW channel. The general transport equation "Hydrodynamic(eTemperature)" is used to confirm the current density and electron velocity in short channel regime. To verify the mobility improvement in FinHEMT, "DopingDependence" "Enormal" and "HighFieldSaturation" are used with equivalent parameters set for both FinHEMT and FinFET. The mole fraction of Ge is 0.3 is used to realize biaxial tensile stress on Si and to form the  $\Delta E_{\rm C}$  [34]. The parameters set is calculated as linear interpolation of Si and Ge with the mole fraction.

# 3. Operation principle of FinHEMT (Long channel)

## 3.1 Device parameter analysis

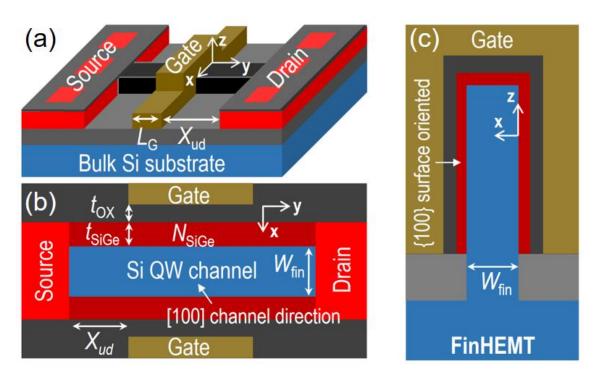

**Figure 3-1.** FinHEMT structure of (a) three dimensional schematic, (b) (x-y plane cut) cross-sectional schematic in channel and (c) (z–x plane cut) gate [100] direction with additional SiGe layer parameters ( $t_{SiGe}$ ,  $N_{SiGe}$ ) from FinFET.

The three dimensional and cross-sectional schematics of FinHEMT are presented in **Figure 3-1(a)** to (c), respectively. The relaxed Si<sub>0.7</sub>Ge<sub>0.3</sub> layer [32], [34] between the s-Si QW channel and HK gate dielectric, which the biaxial tensile stress is enable to applied on s-Si channel, distinguishes FinHEMT from FinFET. This unique Si<sub>0.7</sub>Ge<sub>0.3</sub> layer has two design parameters which are the thickness ( $t_{SiGe}$ = 2 nm) and doping concentration ( $N_{SiGe}$ = 1×10<sup>19</sup> cm<sup>-3</sup>) of the SiGe layer. And 6 nm-thick width of s-Si fin ( $W_{fin}$ ) and 6 nm-thick HK (= 23 $\varepsilon_0$ ) gate dielectric, which has effective oxide thickness EOT is 1 nm, are used as a reference from the 14 nm technology node [35] for both FinFET and FinHEMT. Moreover, the [100] channel direction and {100} surface orientation s-Si is adopted for bulk mobility of 2600 cm<sup>2</sup>/Vs [36] and minimized interface trap density [37].

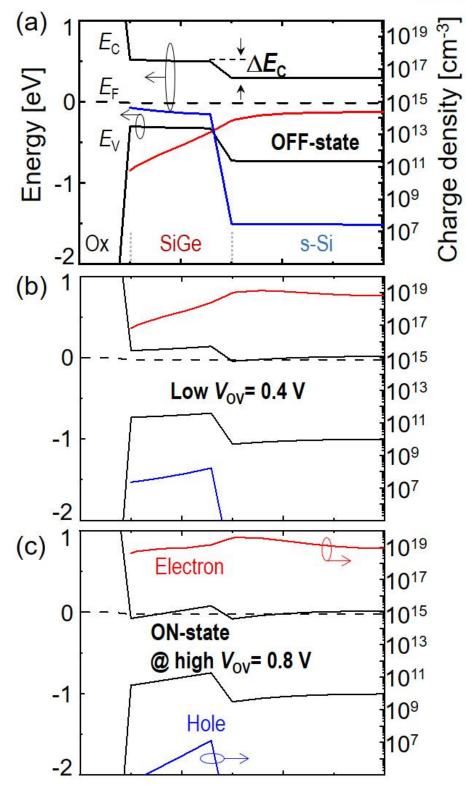

**Figure 3-2.** FinHEMT's electron/hole density profiles and corresponding conduction/valence band diagram (center of the gate) of (a) OFF-state at  $V_{\rm OV}$ = -0.2 V, (b) ON-state at relatively low  $V_{\rm OV}$ = 0.4 V and (c) high  $V_{\rm OV}$ = 0.8 V for  $L_{\rm G}$ = 1 µm, HK EOT = 1 nm,  $t_{\rm SiGe}$ = 2 nm,  $N_{\rm SiGe}$ = 1×10<sup>19</sup> cm<sup>-3</sup>,  $t_{s-\rm Si}$ = $W_{\rm fin}$  = 6 nm, and  $\Delta E_{\rm C}$ = 0.2 eV.

The ON/OFF-state conduction/valence band diagrams and corresponding charge density (red line for electron and blue line for hole) plots using the quantum-corrected potential model and Fermi–Dirac statistics [38] are presented in **Figure 3-2(a)** to (c). The conduction band offset  $\Delta E_{\rm C}$  of 0.2 eV formed at the Si<sub>0.7</sub>Ge<sub>0.3</sub> and s-Si interface is clearly shown [27], [39]. At the OFF-state with  $V_{\rm OV} = V_{\rm GS}-V_{\rm T} = -$  0.2 V (**Figure 3-2(a)**), where  $V_{\rm T} = 0.2$  V, both the SiGe and s-Si are fully depleted with the charge density below 10<sup>14</sup> cm<sup>-2</sup>, resulting in low OFF-current ( $I_{\rm OFF}$ ). At low gate overdrive voltage with  $V_{\rm OV} = 0.4$  V (**Figure 3-2(b**)), the s-Si QW channel confined the most electrons owing to the lower conduction band than that of SiGe [27], [39]. In the ON-state at high  $V_{\rm OV} = 0.8$  V, the e-density in the SiGe layer also increases by band bending of the SiGe forming surface channel, but only up to 10 % of that in the s-Si QW channel (**Figure 3-2(c**)). Therefore, the electrons in the s-Si QW channel separated from the gate dielectric interface are expected to dominate the ON-current ( $I_{\rm ON}$ ). For all  $V_{\rm OV}$ , as the hole density is significantly low and, due to the Source/Drain are n-type doped, there is no effects of holes in the FinHEMT operation.

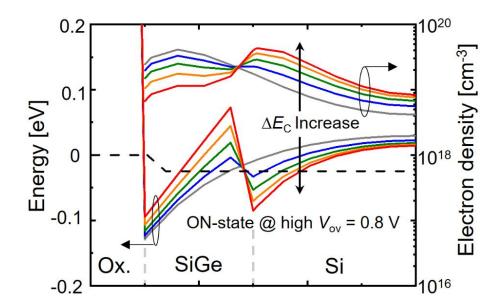

**Figure 3-3.** Conduction band energy and electron density with  $\Delta E_{\rm C}$  variation at  $V_{\rm OV}=0.8$  V. As the  $\Delta E_{\rm C}$  increases, electron density in s-Si channel increases, while decreases in SiGe layer.

The  $\Delta E_{\rm C}$  can be changed by the mole fraction of SiGe [32]. Figure 3-3 shows the conduction band energy and corresponding electron density with  $\Delta E_{\rm C}$  variation at  $V_{\rm OV}$ = 0.8 V.  $\Delta E_{\rm C}$  varies from wellknown value of 0.2 eV (red line) to 0 eV (gray line) with 0.05 eV step. If there is no  $\Delta E_{\rm C}$ , the operation principle of FinHEMT is equivalent with FinFET. Therefore, it should be noted that s-Si QW channel can be formed with the  $\Delta E_{\rm C}$ , which the lower gate capacitance ( $C_{\rm G}$ ) and surface roughness scattering than FinFET is expected.

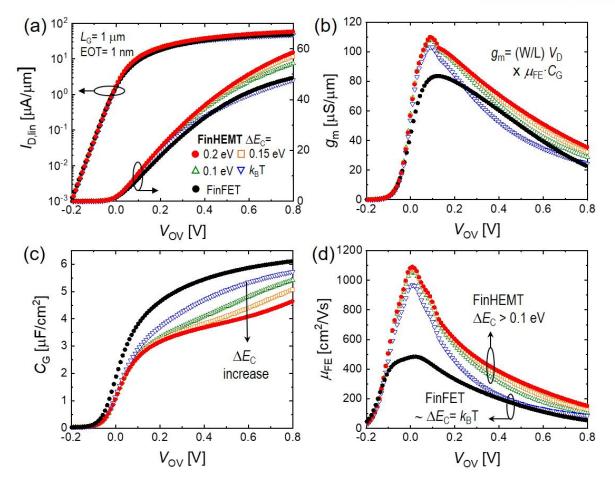

**Figure 3-4.** The calculated dataset of field-effect mobility ( $\mu_{FE}$ ) extraction: (a) transfer *I-V* curves (b) transconductance  $g_m$  (c) gate capacitance and (d) the extracted  $\mu_{FE}$  from  $g_m = (W/L) \mu_{FE}C_GV_D$  for the long-channel FinFET and FinHEMT with different  $\Delta E_C = 0.2$  [27][39], 0.15, 0.1 and 0.026 eV(=  $k_BT$ ),  $t_{SiGe} = 2$  nm, and  $N_{SiGe} = 1 \times 10^{19}$  cm<sup>-3</sup>.

Figure 3-4 shows the typical extraction dataset of field-effect mobility ( $\mu_{FE}$ ) based on the transconductance equation  $g_m = (W/L) \mu_{FE}C_GV_D$ , where  $W=L=1 \mu m$  and  $V_D=0.05 V$ . To investigate the effect of  $\Delta E_C$ , we consider various  $\Delta E_C$  in the simulation of FinHEMT with the 2-nm-thick SiGe layer. Clear current and  $g_m$  gain are obtained in FinHEMT, (Figure 3-4(a) and (b)) as long as  $\Delta E_C > 0.1$  eV. Even with the reduced gate capacitance ( $C_G$ ) by the additional gate dielectric coming from the depleted SiGe layer (Figure 3-4(c)), the dramatic mobility improvement in the well-confined QW channel formed by  $\Delta E_C$  enables the overall gain (Figure 3-4(d)). In Figure 3-4(c), the gate capacitance decreases as the  $\Delta E_C$  increases, because the s-Si channel can be confined away from the gate with  $\Delta E_C$ . And 25 % lower gate capacitance indicates that additional EOT of SiGe is 0.36 nm which is 1.2 nm

thick SiGe with relative permittivity  $\varepsilon_r = 13$ . If  $\Delta E_C$  is too small (e.g.  $\sim k_B T$ ), FinHEMT only suffers from the  $C_G$  reduction without any mobility improvement since QW is not well defined, thus resulting in the degraded current. The known value of  $\Delta E_C \sim 0.2 \text{ eV} [27][39]$  is more than enough to guarantee the overall current and  $g_m$  gain in our FinHEMT operation.

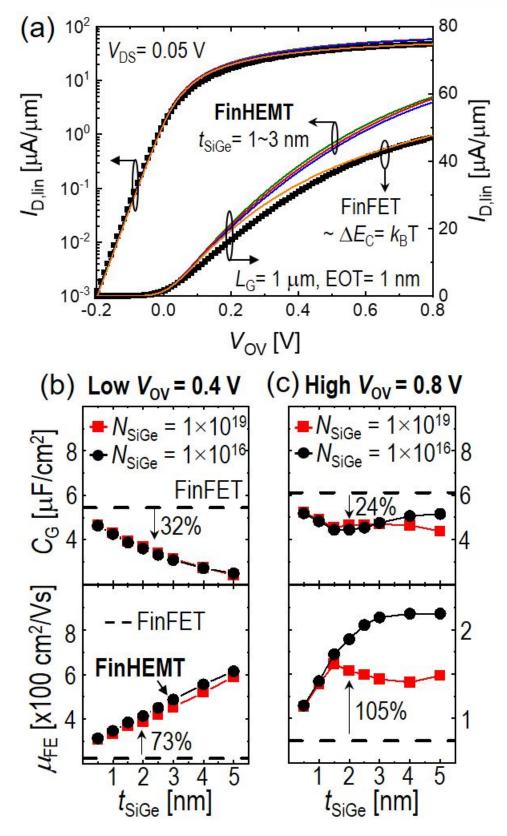

This doped and thin SiGe layer has two specific design parameters, which are thickness ( $t_{SiGe}$ ) and doping concentration ( $N_{SiGe}$ ) of the SiGe layer. As in **Figure 3-5(a)**, the enhanced current by SiGe layer remains same even with  $t_{SiGe}=1 \sim 3$  nm variation. From a simple guess, we may expect that the thicker SiGe layer results in the higher mobility and the lower  $C_G$ , which is valid at low  $V_{OV}$  (**Figure 3-5(b)**). In high  $V_{OV}$  regime, however, due to the electron density increase in SiGe (**Figure 3-2(c)**), the dependency of  $C_G$  and mobility on  $t_{SiGe}$  becomes weak for  $t_{SiGe}=1 \sim 3$  nm (**Figure 3-5(c)**). The effect of  $N_{SiGe}$  is not significant when  $t_{SiGe}$  is less than or equal to 2 nm since maximum depletion width  $W_{dm}=$  =~ 11 nm for high  $N_{SiGe} \sim 10^{19}$  cm<sup>-3</sup> is larger than  $t_{SiGe}$ , but it becomes effective in short-channel regime that will be discussed in the section 4.1.

SCIENCE AND TECHNOLOGY

**Figure 3-5.** (a) Transfer *I-V* curves of FinHEMT and FinFET for different  $t_{SiGe}$  with  $\Delta E_C = 0.2$  eV. Gate capacitance ( $C_G$ ) and calculated field effect mobility ( $\mu_{FE}$ ) at (b) low  $V_{OV} = 0.4$  V and (c) high  $V_{OV} = 0.8$  V for various  $t_{SiGe}$  and  $N_{SiGe}$  of FinHEMT benchmarking with FinFET.

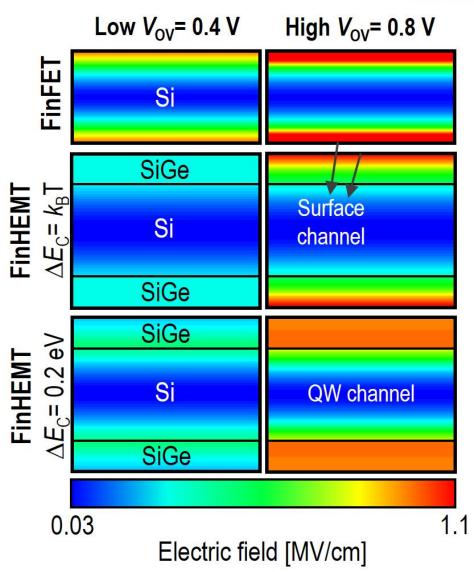

**Figure 3-6.**  $E_{\text{norm}}$  contour plot at low  $V_{\text{OV}}=0.4$  V and high  $V_{\text{OV}}=0.8$  V in FinHEMT with  $\Delta E_{\text{C}}=0.2$  eV and FinFET ( $\sim \Delta E_{\text{C}}=k_{\text{B}}$ T).

The increased electron density in SiGe layer at high  $V_{OV}$  blocks the normal electric field ( $E_{norm}$ ) and hence suppress the further  $E_{norm}$  increase in QW channel ( $\Delta E_{C} = 0.2 \text{ eV}$ ), thereby reducing SRS effect (**Figure 3-6**). However, the SiGe surface channel is activated when the  $\Delta E_{C} = \sim k_{b}T$  because there is no QW channel in FinHEMT. There is effective mobility degradation owing to high surface  $E_{norm}$  which is equivalent with FinFET operation.

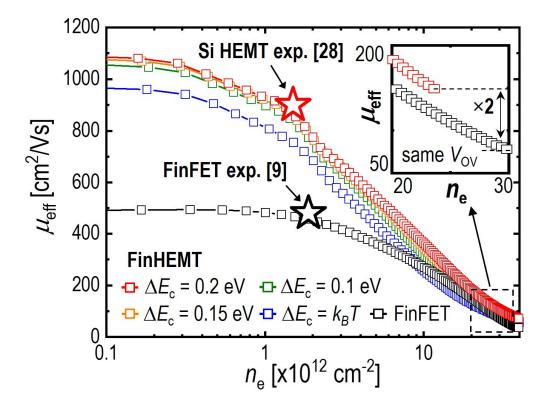

3.2 Enhanced effective mobility

**Figure 3-7.** Universal  $\mu_{\text{eff}}$  vs. e-density ( $qn_e = C_G V_{OV}$ ) of FinFET and FinHEMT with experimental data [9], [28]. Inset: 2 times enhanced  $\mu_{\text{eff}}$  in s-Si channel in FinHEMT at same  $V_{OV} = 0.8$  V.

Comparing with FinFET as a reference, the extracted  $\mu_{eff}$  of FinHEMT for different  $\Delta E_{\rm C}$  values is summarized in **Figure 3-7**. Based on our simulation platform, well-calibrated with the available experimental record mobility of s-Si on insulator (sSOI) FinFET ~500 cm<sup>2</sup>/Vs [9] and Si HEMT ~950 cm<sup>2</sup>/Vs [28], the proposed FinHEMT shows record-high low-field mobility ~1100 cm<sup>2</sup>/Vs and 2 times enhanced  $\mu_{eff}$  by SRS suppression in s-Si QW channel than in FinFET (inset), while keeping the same gate controllability with FinFET.

Figure 3-8. (a) Effective mobility and (b) field-effect mobility with 500 cm<sup>2</sup>/Vs low-field mobility of FinHEMT.

As shown in the left of **Figure 3-8(a)**, we intentionally lower the mobility of FinHEMT down to 500  $\text{cm}^2/\text{Vs}$  at low electron density by adjusting ionized impurity scattering parameters and run the FinHEMT simulation with the other scattering parameters remaining the same. Although the mobilities of FinHEMT and FinFET are matched at low electron density, FinHEMT could still have  $1.75 \times$  higher mobility than FinFET in the high electron density regime at the same gate overdrive voltage ( $V_{OV}$ = 0.8 V) because of the reduced SRS (**Figure 3-8(a)** right and (b)). However, as shown in **Figure 3-4(c)**, an additional EOT from the SiGe layer in FinHEMT leads to the lower capacitance, and hence we cannot achieve higher current in FinHEMT even with the improved mobility. If EOT of FinHEMT is scaled down further and matched to FinFET, we can expect higher current in FinHEMT.

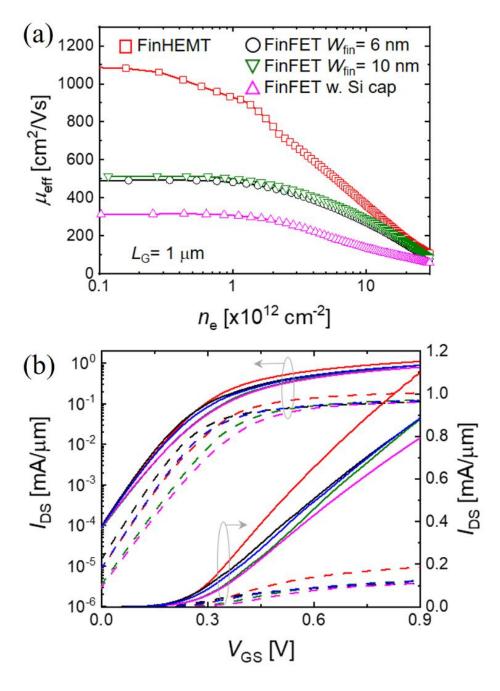

**Figure 3-9.** (a) Effective mobility versus electron density and (b) transfer  $I_{DS}$ - $V_{GS}$  curves compared with  $1 \times 10^{19}$  cm<sup>-3</sup> doped Si cap and  $W_{fin}$ = 6, 7.6, 10 nm of FinFET.

If we use  $1 \times 10^{19}$  cm<sup>-3</sup> doped Si cap instead of SiGe, the electron channel is formed at the interface between gate oxide and doped Si because there is no band offset to separate the electron from the interface. Therefore, as we expect, the effect of SRS and ionized impurity scattering severely degrade the mobility as shown in **Figure 3-9(a)**. If we just increase the Si channel thickness to 10 nm without doping, the mobility is recovered and becomes similar to the 6-nm-thick s-Si channel in **Figure 3-9(a)**. As a result, from the transfer characteristics in **Figure 3-9(b)**,  $1 \times 10^{19}$  cm<sup>-3</sup> doped Si cap exhibits lower current than FinFET and 10-nm-thick channel FinFET shows almost similar current with the original 6-nm-thick FinFET.

Additionally, we examine the validity of comparing FinHEMT and FinFET with the same 6-nm-thick Si Channel. In FinHEMT, if we consider the spreading of electron into the SiGe layer, the effective Si Fin width could be roughly estimated to 7.6 nm, suggesting that benchmarking our FinHEMT to 7.6-nm-thick channel FinFET is more reasonable. In **Figure 3-7(b)**, we show the transfer characteristics of 7.6-nm-thick channel FinFET and confirm that current is almost same with our original 6-nm-thick FinFET. Therefore, we believe that the comparison between FinHEMT and FinFET having the same 6 nm-thick s-Si channel could be valid in terms of the on-current and short channel effects (SCEs).

### 4.Short channel characteristics

# 4.1 Performance optimization

**Figure 4-1.**  $I_{ON}$  contour plots for (a) FinHEMT, and (b) considering diffusion process through the SiGe layer from source/drain to under the gate region. Optimized  $t_{SiGe}$  and  $N_{SiGe}$  following scaling rule. With  $t_{SiGe} = 2$  nm and  $N_{SiGe} = 10^{19}$  cm<sup>-3</sup>, the  $I_{ON}$  is maximized with 73.88 mV/dec of SS.

In short channel regime, ON-current is determined by the Source/Drain series resistance  $\rho_{s=} \rho_{source}$ +  $\rho_{channel}$  +  $\rho_{Drain}$ . Our proposed FinHEMT with gate undelap region ( $X_{ud}$ ) can achieve low Source/Drain resistance due to quantum well with high electron density transferred from high  $N_{SiGe}$ layer. **Figure 4-1** shows ON-current contour plot according to the  $N_{SiGe}$  and  $t_{SiGe}$  variation. Maximized ON-current can be achieved at  $t_{SiGe}=2$  nm and  $N_{SiGe}=1\times10^{19}$  cm<sup>-3</sup> and subthreshold swing is 73.88 mV/dec. If we consider the diffusion from Source/Drain to SiGe layer, the SiGe layer under the channel can be lower than the gate underlap region as shown in **Figure 4-1(b)**. The simulation result shows that there is subthreshold variation at higher  $t_{SiGe} > 3.5$  nm and  $N_{SiGe} > 10^{18}$  cm<sup>-3</sup>. However, at  $t_{SiGe}=2$  nm, there is no subthreshold swing variation which means that the best gate controllability regime. Therefore, optimized device parameters are  $t_{SiGe}=2$  nm, and  $N_{SiGe} < 5x10^{18}$  cm<sup>-3</sup>.

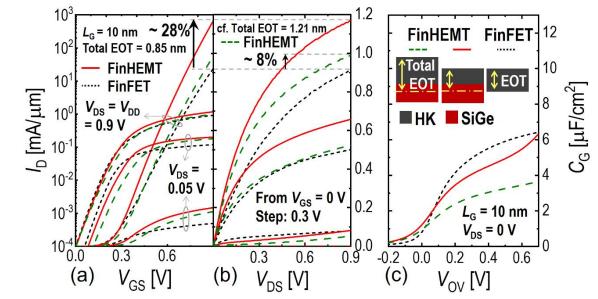

**Figure 4-2.** (a) Transfer  $I_D - V_{GS}$ , (b) output  $I_D - V_{DS}$ , and (c) C - V curves for FinHEMT with  $N_{SiGe} = 1 \times 10^{19}$  cm<sup>-3</sup> and  $t_{SiGe} = 2$  nm, gate HK dielectric EOT = 0.85 nm (green, total EOT= 1.21 nm), and 0.49 nm (red, total EOT= 0.85 nm) and FinFET (black) with total EOT = 0.85 nm, and gate workfunction WF= 4.95, 4.83, and 4.65 eV respectively. Inset in (c): schematic for total EOT of FinHEMT with SiGe layer compared to only HK EOT of FinFET.

Benchmarked with FinFET based on the technology node device parameters of the gate length  $L_{G}$ = 10 nm,  $W_{fin}$ = 6 nm, EOT= 0.85 nm, and the underlap length  $X_{ud}$ =  $(L_G-L_{eff})/2$ = -5 nm, **Figure 4-2** shows the dc characteristics of the short-channel FinHEMT. The  $I_{ON}$  is normalized with  $2H_{fin} + W_{eff}$ , where we use 50 nm for  $H_{fin}$ , and 6 and 7.6 nm for  $W_{eff}$  for FinFET and FinHEMT respectively. For FinHEMT, the additional SiGe thickness operating as the channel (**Figure 4-2(c)**, inset) is included in  $W_{eff}$ . FinHEMT shows 28% enhanced driving on-current  $I_{ON}$ = 1.176 mA/µm at  $V_{DD}=V_{GS}=V_{DS}$ = 0.9 V (**Figure 4-2 (a)(b)**) for the same total EOT= 0.85 nm of FinFET composed of gate HK dielectric EOT= 0.49 nm and SiGe EOT= 0.36 nm by the additional  $t_{SiGe}$ = 2 nm with  $N_{SiGe}$ = 1x10<sup>19</sup> cm<sup>-3</sup> (**Figure 4.2(c)**). Even in FinHEMT with thicker total EOT= 1.36 nm (HK EOT= 0.85 nm + SiGe EOT= 0.51 nm),  $I_{ON}$  is still enhanced by 8 %. This additional  $I_{ON}$  gain in the short-channel FinHEMT can be explained by the reduction of the series resistance composed of the channel and gate underlap region by the doped SiGe layer.

**Figure 4-3.** (a) Schematic structure of proposed FinHEMT and FinHEMT with undoped SiGe layer under the gate. (b) Those transfer  $I_{DS}$ - $V_{GS}$  curves at  $L_G$ = 10 nm.

If we consider 10 nm gate length, 50 nm fin height and 2-nm-thick SiGe layer, there are 10 impurities in 2-nm-thick SiGe layer. One may think that the impact of random discrete dopant (RDD) is significant, however, this SiGe layer behaves as additional high- $\kappa$  ( $\varepsilon_r$ = 13) dielectric insulator rather than channel. So, the effect of RDD should be limited. Moreover, we can also consider undoped SiGe layer to avoid

any concerns about RDD. As presented in **Figure 4-3(a)** bottom, we consider FinHEMT with the undoped SiGe layer and run the FinHEMT simulation again. From the transfer  $I_{DS}$ - $V_{GS}$  curves at the matched  $I_{OFF}$  in **Figure 4-3(b)**, FinHEMT with and without doping in the SiGe layer result in the almost identical transfer characteristics. Therefore, we can completely avoid RDD concern if the undoped SiGe layer is employed in FinHEMT.

Figure 4-4.  $I_{ON}$  contour plots as functions of  $t_{SiGe}$  and  $N_{SiGe}$  for various  $L_G=1 \mu m$ , 25 nm, 15 nm, and 10 nm.

As shown in the  $I_{ON}$  contour plots as functions of  $t_{SiGe}$  and  $N_{SiGe}$  (Figure 4-4),  $I_{ON}$  is improved as  $N_{SiGe}$  increases in short-channel regime upon scaling down to sub-30 nm where the underlap series resistance dominates while no  $I_{ON}$  dependence on  $N_{SiGe}$  (mainly on  $t_{SiGe}$ , i.e. EOT) in long-channel regime. In short channel regime, the length of channel is comparable with the gate underlap region  $X_{ud}$  and therefore, the resistivity of  $X_{ud}$  become significant to  $I_{ON}$ .

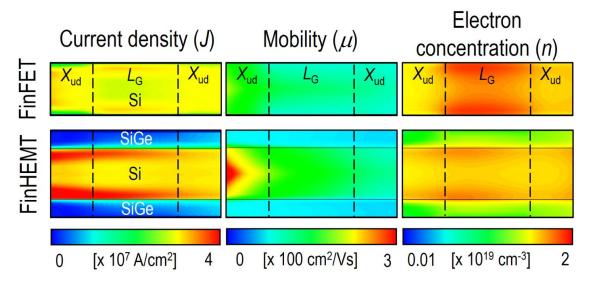

**Figure 4-5.** Contour plots of current density (*J*), mobility ( $\mu$ ) and electron concentration (*n*) in 2D crosssectional channel with underlap region ( $X_{ud}$ ) at  $V_{GS}=V_{DS}=0.9$  V for both FinHEMT and FinFET ( $L_G=10$  nm,  $L_{UN}=5$  nm, and same total EOT= 0.85 nm).

| <i>L</i> <sub>G</sub> = 10 nm                      |        | FinHEMT (N <sub>SiGe</sub> ) |                           |  |

|----------------------------------------------------|--------|------------------------------|---------------------------|--|

| Total EOT=                                         | FinFET | Undoped                      | Doped                     |  |

| 0.85 nm                                            |        | $10^{16} \text{ cm}^{-3}$    | $10^{19} \text{ cm}^{-3}$ |  |

| $\frac{J}{[10^7 \mathrm{A/cm^2}]}$                 | 3.3    | 3.7 (x 1.11)                 | 4.0 (x 1.21)              |  |

| $\mu$ [cm <sup>2</sup> /Vs]                        | 175    | 249 (x 1.42)                 | 259 (x 1.48)              |  |

| $n [10^{18} / \text{cm}^2]$                        | 6.7    | 6.2 (x 0.93)                 | 8.4 (x 1.27)              |  |

| <i>ρ</i> <sub>Xud</sub><br>[10 <sup>-3</sup> Ω·cm] | 5.4    | 4.1 (x 0.76)                 | 2.9 (x 0.53)              |  |

**Table I.** The extracted current density (*J*), mobility ( $\mu$ ), e-density (*n*), and calculated resistivity  $\rho_{Xud}$  for the gate underlap region.

Figure 4-5 provides the contour plots of the current density (*J*), electron concentration (*n*), and mobility ( $\mu$ ) in 2D cross-sectional channel with the gate underlap region at  $V_{\text{DD}}=V_{\text{GS}}=V_{\text{DS}}=0.9$  V for both FinHEMT and FinFET. As compared with FinFET, s-Si QW channel under the gate of FinHEMT has lower *n*, but improved  $\mu$  by SRS suppression as explained in the long-channel regime (Section 2). Especially in the gate underlap region, however, both higher  $\mu$  and *n* can be achieved by the doped SiGe layer ( $N_{\text{SiGe}}=1x10^{19}$  cm<sup>-3</sup>) with  $\Delta E_{\text{C}}=0.2$  eV as in HEMT [40], which results in the lower underlap resistivity ( $\rho_{\text{Xud}}$ ) than that of FinFET. The quantitative analysis is summarized in **Table I** resulting the 47% reduction of  $\rho_{\text{Xud}}=1/(q\mu n)$  in FinHEMT with  $N_{\text{SiGe}}=1x10^{19}$  cm<sup>-3</sup>. In the case of FinHEMT with the undoped SiGe layer ( $N_{\text{SiGe}}=1x10^{16}$  cm<sup>-3</sup>), it should be noted that there is still 24% reduction of  $\rho_{\text{Xud}}$ from FinFET by highly improved  $\mu$  (1.42 times higher than FinFET) even with lower *n* than those of FinFET.

#### 4.2 Variability and Scalability predictions

**Figure 4-6.**  $I_{\text{ON}}$  variability with process variation of  $X_{\text{ud}}$  and  $W_{\text{fin}}$  (±1 nm) when scaling  $L_{\text{G}}$  = 25, 15, 10 nm at  $V_{\text{DD}}$  = 1, 0.93, 0.9 V with total EOT= 1.36 (1), 0.9 (0.9), 0.85 (0.85) nm of FinHEMT (FinFET).

Ascribed to this low  $\rho_{Xud}$  in FinHEMT, a better immunity in  $I_{ON}$  to the process variation [41][42] of  $X_{ud}$  and  $W_{fin}$  is expected in FinHEMT than in FinFET. Figure 4-6 shows only 5% change in  $I_{ON}$  from the  $X_{ud}$  variation (±1 nm) in FinHEMT with  $L_G$ = 10 nm, while 9.5% in FinFET. The change of  $I_{ON}$  owing to the  $W_{fin}$  variation (±1 nm) is reduced to 0.06% in FinHEMT from 4% in FinFET. Observed excellent immunity to the process variation in FinHEMT is due to the both low underlap series resistance and low s-Si channel resistance since the main current path is the s-Si QW channel in FinHEMT (Figure 4-5). Furthermore, this uniformity to variability becomes more significant in the further scaling

Moreover, we analyze the variabilities of the DC characteristics such as  $V_{T,sat}$ , DIBL, SS, and  $I_{OFF}$  as summarized in **Figure 4-7**. Since FinHEMT has  $W_{eff}$ = 7.6 nm, the variability is the same as that of the 7.6 nm-thick FinFET for these parameters. Although comparing with  $W_{eff}$ = 6 nm of FinFET, there is little difference between FinHEMT and FinFET.

**Figure 4-7.** (a)  $V_{T,sat}$  considering the gate length scaling effects on  $V_T$ , (b) calculated DIBL, (c) extracted SS, and (d)  $I_{OFF}$  variabilities on  $X_{ud}$  and  $W_{fin}$  variations of FinHEMT and FinFET with  $W_{Fin} = 7.6$ , 6 nm.  $V_{T,sat}$  is extracted at  $I_D = 4$ , 6.67, 10  $\mu$ A/ $\mu$ m at  $L_G = 25$ , 15, 10 nm, respectively ( $V_{D,sat} = 1.0$ , 0.93, 0.9 V, and  $V_{D,lin} = 0.05$  V). Below figures are corresponding transfer  $I_{DS}-V_{GS}$  curves of each points.

We run the FinHEMT simulation with reducing the SiGe layer thickness from 2.2 to 1.8 nm as shown in **Figure 4-8** for the high- $\kappa$  EOT thicknesses of 0.49 and 0.2 nm, respectively. From the transfer  $I_{DS}$ - $V_{GS}$  curves in **Figure 4-8**,  $\Delta V_T$  and  $\sigma_{VT}$  are estimated to 49.0 and 28.2 mV, respectively, for the high- $\kappa$  EOT 0.49 nm. If the high- $\kappa$  EOT is reduced to 0.2 nm, we can obtain smaller values of  $\Delta V_T$  and  $\sigma_{VT}$ (35.7 and 25.6 mV, respectively). To check whether these amounts of variation are acceptable or not, we use  $A_{VT}$  defined as  $A_{VT} = \sigma \Delta V_T \sqrt{WL} = \sqrt{2}\sigma V_T \sqrt{WL}$  in Ref. [43]. For the stable operation of 6T-SRAM,  $A_{VT}$  less than 1.5 mVµm is required [43]. We roughly calculate  $A_{VT}$  values of FinHEMT considering  $\sigma_{VT}$  of FinHEMT originating the SiGe layer thickness variation and  $\sigma_{VT,FinFET}$  of 6-nmthick FinFET separately. As shown in Ref. [44],  $\sigma_{VT,FinFET}$  due to the metal gate granularity (MGG), fin width roughness (FWR) and fin height roughness (FHR) is estimated to ~22.3 mV for the fin height of 50 nm. Then, using the total  $\sigma_{VT}$  defined as total  $\sigma_{VT} = \sqrt{\sigma_{VT}^2 + \sigma_{VT,FinFET}^2}$  where  $\sigma_{VT}$  is from the SiGe layer thickness variation and  $\sigma_{VT,FinFET}$  is from FinFET, the total  $\sigma_{VT}$  values are estimated to 28.16 and 25.6 mV, resulting in the  $A_{VT}$  values of 1.31 and 1.19 mVµm for the high- $\kappa$  EOT thicknesses of 0.49 and 0.2 nm, respectively. Since those values are less than the require value of  $A_{VT}$  for the stable 6T-SRAM operation, we expect that the effect of the SiGe thickness variation is limited.

**Figure 4-8.** Transfer  $I_D$ - $V_G$  curves with the SiGe thickness variation for the high- $\kappa$  EOT= 0.49 (proposed FinHEMT) and 0.2 nm.  $\sigma_{VT}$  and  $A_{VT}$  values extracted from the transfer  $I_{DS}$ - $V_{GS}$  curves are summarized in Table II.

|                          | HK EOT= |       |  |

|--------------------------|---------|-------|--|

| FinHEMT                  | 0.49 nm | -     |  |

| $\sigma_{VT,FinFET}[mV]$ |         |       |  |

| (Ref. [43])              | 22      | 22.3  |  |

|                          |         |       |  |

| $\sigma_{VT} [mV]$       | 17.19   | 12.57 |  |

|                          |         |       |  |

| Total $\sigma_{VT}$      | 28.16   | 25.6  |  |

|                          |         |       |  |

| $A_{\rm VT}$ [mVµm]      | 1.31    | 1.19  |  |

**Table II.** Calculated  $\sigma_{VT}$  and  $A_{VT}$  of FinHEMT with conventional  $\sigma_{VT}$  of FinFET.

**Figure 4-9.** Contour plots of  $I_{ON}$  in FinHEMT to the gate dielectric EOT and  $V_{DD}$  scaling for  $L_G$ = 15 nm and 10 nm.

**Figure 4-9** shows the  $I_{ON}$  contours to the EOT and  $V_{DD}$  scaling for  $L_G$ = 15 nm and 10 nm. While scaling  $V_{DD}$  from 0.95 V to 0.75 V, FinHEMT shows  $I_{ON} > 1$  mA/µm by the gate dielectric EOT scaling from 0.7 to 0.2 nm.

**Figure 4-10.** FinHEMT scalability over FinFET by plot of  $I_{ON}$  as a function of  $1/L_G$ . For sub-10 nm scaling, FinHEMT  $I_{ON}$  keeps increasing by 28% from FinFET at the same total EOT and  $V_{DD}$  scaling.

**Figure 4-10** shows the overall scalability evaluation of the proposed FinHEMT. For sub-10 nm scaling with the equivalent total EOT with FinFET, 28% enhanced  $I_{ON}$  can be achieved for FinHEMT mainly due to higher electron mobility in QW channel while having lower capacitance. In technology aspects, more aggressive gate dielectric EOT scaling would be possible in FinHEMT since the additional SiGe layer can suppress the gate leakage current more effectively than in FinFET. If this ultimate gate dielectric EOT scaling is considered for FinHEMT,  $I_{ON}$  can be enhanced further.

### 4.3 RF characteristics: cutoff/maximum frequency

**Figure 4-11.** (a)  $|h_{21}|$  (b) cut-off frequency  $f_T$  using unit gain method (c) MUG, and (d) maximum frequency  $f_{max}$  using unit gain method and extrapolation method for FinHEMT.

Cut-off frequency is calculated with unit gain method searching for  $|\mathbf{h}_{21}|= 1$ . Here,  $|\mathbf{h}_{21}|$  is calculated as follow:

$$h_{21} = \frac{y_{21}}{y_{11}} \tag{3.1}$$

The subscript number 1 and 2 indicate the gate and drain node respectively. And Y-matrix can be converted from 2x2 conductance (*A*) and capacitance (*C*) matrix:

$$Y = A + j\omega C \tag{3.2}$$

Where *j* is the imaginary unit, and  $\omega = 2\pi f$ . Thus, the unit gain method is when  $y_{21} = y_{11}$ . Also, the maximum frequency  $f_{\text{max}}$  can be calculated when Mason's Unilateral Gain (MUG) is equal to 1 [45].

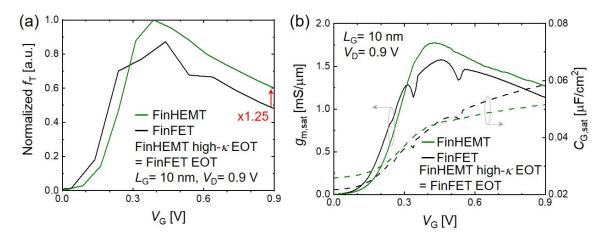

**Figure 4-12.** (a) Normalized cut-off frequency  $f_{\rm T}$  of FinFET and FinHEMT with equivalent high- $\kappa$  EOT. (b) Transconductance  $g_{\rm m,sat}$  and gate capacitance  $C_{\rm G,sat}$  at  $V_{\rm D}$ = 0.9 V.

As well as better DC performance, a higher cutoff/maximum frequency  $(f_T/f_{max})$  than conventional FET can be expected due to the lower capacitance in FinHEMT. In long channel regime, 2 times enhanced mobility (**Figure 3-7**) can be revealed as cutoff frequency enhancement from the following equation:  $f_T = \frac{g_m}{2\pi C_G} = \frac{1}{2\pi} \frac{WV_D}{L} \mu$ . Moreover, in short channel regime, we confirmed this expectation using TCAD  $f_T$  simulation with unity gain method for FinHEMT (8%  $I_{ON}$  increment) and FinFET as shown in **Figure 4-12**. The simulation results of  $g_{m,sat}$  and  $C_{G,sat}$  at  $V_D = 0.9$  V in **Figure 4-12(b)** and the extracted values at  $V_{DD}=V_G=V_D=0.9$  V are  $g_{m,sat}=1.25$  mS/µm,  $C_{G,sat}=5.15 \times 10^{-2}$  µF/cm<sup>2</sup> for FinHEMT and  $g_{m,sat}=1.14$  mS/µm,  $C_{G,sat}=5.85 \times 10^{-2}$  µF/cm<sup>2</sup> for FinFET respectively. Therefore, there is 1.25 times enhancement even with the lower capacitance (thicker EOT) in FinHEMT than in

FinFET as shown in **Figure 4-2(b)**

$$f_{T,FinHEMT} = \frac{1.10 \times g_{msat,FinFET}}{0.88 \times 2\pi C_{G,sat,FinFET}} = 1.25 f_{T,FinFET}$$

#### 4.4 Improved reliability

As the gate length get shorter, the electric field between source and drain become higher causing hot carrier injection (HCI) in insulator from channel. The Fiegna model explains this phenomenon simply by multiplying the gate leakage probability to drain current as shown below [46]:

$$I_{g} = q \int P_{ins} \left( \int_{E_{B0}}^{\infty} v_{\perp}(\varepsilon) f(\varepsilon) g(\varepsilon) d\varepsilon \right) d\varepsilon$$

(4.1)

Here,  $v(\varepsilon)$  is velocity,  $f(\varepsilon)$  is fermi-dirac distribution function, and  $g(\varepsilon)$  is density-of-state as a function of energy  $\varepsilon$ . And injection probability  $P_{ins}$  from the channel to insulator is:

$$P_{ins} = \begin{cases} \exp\left(-\frac{x_0}{\lambda_{ins}}\right) & E_{ins} < 0\\ \exp\left(-\frac{t_{ins} - x_0}{\lambda_{ins}}\right) & E_{ins} > 0 \end{cases}$$

(4.2)

where  $x_0$  is the distance from the interface to maximum position of barrier, and  $\lambda_{ins}$  is the mean-free path in insulator.  $\lambda_{ins}$  is highly affected by the temperature and inversion charge density [16]

$$x_0 = \min\left(\sqrt{\frac{q}{16\pi\widetilde{\varepsilon}_{ins}}|E_{ins}|}, \frac{t_{ins}}{2}\right)$$

(4.3)

where  $\widetilde{\varepsilon}_{ins}$  is average permittivity of insulator as follow:

$$\widetilde{\varepsilon}_{ins} = \varepsilon_{ins} \left( \varepsilon_{sem} + \varepsilon_{ins} \right) / \left( \varepsilon_{sem} - \varepsilon_{ins} \right)$$

(4.4)

Here,  $\varepsilon_{ins}$  and  $\varepsilon_{sem}$  is permittivity of insulator and semiconductor.

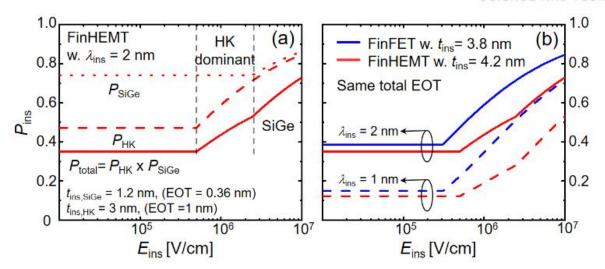

Figure 4-13. (a) Injection probability component effects for FinHEMT (b) Injection probability with  $\lambda_{ins}=1$ , 2.

**Figure 4-14(a)** presents the injection probability for FinHEMT considering HK dielectric and SiGe layer injection from the channel. For the calculation, we consider that the thickness of SiGe behaving as an additional EOT is 1.2 nm (detailed in Section 4.1.) and thickness of HK is 3 nm with  $\varepsilon_{r,HK}$ = 9.75 (EOT= 1 nm). Therefore, total injection probability is  $P_{total}$ =  $P_{HK} \times P_{SiGe}$ . Although the total EOT is equivalent for FinHEMT and FinFET, there is physical thickness difference 0.4 nm only owing to the permittivity of SiGe ( $\varepsilon_{r,SiGe}$ = 13) is greater than HK. Moreover, 10% of  $P_{ins}$  difference is shown in **Figure 4-14(b)** for  $\lambda_{ins}$ = 1 and 2 nm even 0.4 nm of physical thickness of insulator.

The kinetic equation of hydrogen bond at the interface is follow [47]:

$$\frac{dN_{hb}}{dt} = -vN_{hb} + \gamma (N - N_{hb})$$

$$\gamma = \gamma_0 \left[ N_H / N_H^0 + \Omega (N_{hb}^0 - N_{hb}) \right]$$

$$\gamma_0 = \frac{N_{hb}^0}{N - N_{hb}^0} v_0$$

(4.5)

$$v = v_{0} \exp\left(\frac{\varepsilon_{A}^{0}}{kT_{0}} - \frac{\varepsilon_{A}^{0} - \Delta\varepsilon_{A}}{\varepsilon_{T}}\right) k_{FN} k_{HC}$$

$$\varepsilon_{T} = k_{b}T + \delta_{\parallel} |E_{\parallel}|^{\rho_{\parallel}}$$

$$k_{FN} = 1 + \delta_{Tun} |I_{Tun}|^{\rho_{Tun}}$$

$$k_{HC} = 1 + \delta_{HC} |I_{HC}|^{\rho_{HC}}$$

$$\Delta\varepsilon_{A} = -\delta_{\perp} |E_{\perp}|^{\rho_{\perp}} + (1 + \beta)\varepsilon_{T} \ln\left(\frac{N - N_{hb}}{N - N_{hb}^{0}}\right)$$

(4.6)

Here, v is reaction constant,  $v_0$  is depassivation constant,  $\varepsilon_{\Gamma}$  is threshold energy,  $k_{FN}$  and  $k_{HC}$  is a constant suppling the effects of tunneling, and hot carrier injection respectively, and  $\Delta \varepsilon_A$  is the change of activation energy by vertical electric field.

Considering Spherical Harmonic Expansion (SHE) method [48], there is additional constant  $k_{\text{SHE}}$ :

$$k_{SHE} = 1 + \delta_{SHE} \frac{qg_{\nu}}{2} \int_{\varepsilon_{th}}^{\infty} \left( \min\left[ \exp\left(\frac{\varepsilon - \varepsilon_a}{kT}\right), 1\right] g(\varepsilon) f(\varepsilon) v(\varepsilon) \right) d\varepsilon$$

(4.7)

Where,  $\delta_{\text{SHE}}$  is a prefactor,  $\varepsilon_{\text{th}}$  is a threshold energy,  $\varepsilon_{a}$  is an activation energy to break the passivated hydrogen bond,  $g_{v}$  is the valley degeneracy, and  $g(\varepsilon)$ ,  $f(\varepsilon)$ , and  $v(\varepsilon)$  are the density of states, electron energy distribution and magnitude of the electron velocity respectively.

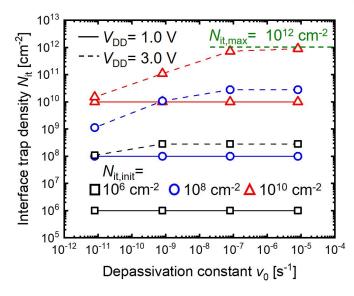

**Figure 4-14.** Interface trap density as a function of depassivation constant with initial  $N_{it}$ = 10<sup>6</sup>, 10<sup>8</sup>, 10<sup>10</sup> cm<sup>-2</sup> and  $V_{DD}$ = 1.0, and 3.0 V

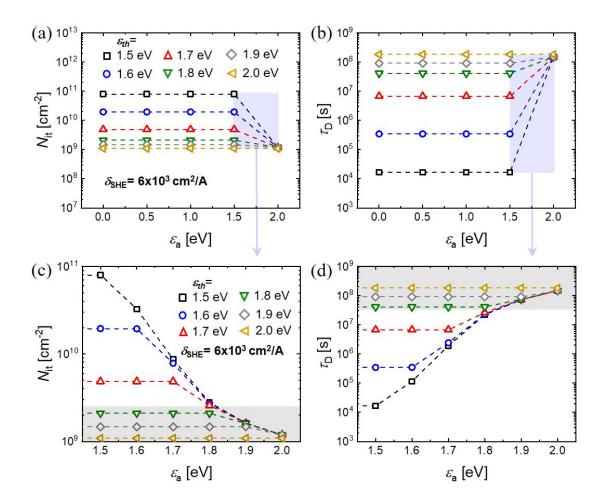

Figure 4-15.  $\varepsilon_{\text{th}}$ ,  $\varepsilon_{\text{a}}$  sensitivity analysis on (a),(c)  $N_{\text{it}}$  and (b),(d)  $\tau_{\text{D}}$

A rigorous simulation is performed to find the interface trap density  $N_{it}$  range for the device lifetime

(= degradation time  $\tau_D$ ,  $\tau_D = \left(\frac{v^{stress}}{v}\right) \times \tau_D^{stress}$ ) over 1 year. Figure 4-14 shows the results of changing

the depassivation constant, and the initial  $N_{it}$  are 10<sup>6</sup>, 10<sup>8</sup>, and 10<sup>10</sup> cm<sup>-2</sup> with maximum  $N_{it}$  is 10<sup>12</sup> cm<sup>-2</sup>,  $V_{DD}$ = 1.0 and 3.0 V. And we change the  $\varepsilon_a$  and  $\varepsilon_{th}$  considering standard deviation  $\sigma_{\varepsilon a}$ = 0.35 eV [49] as shown in **Figure 4-15**. Therefore,  $N_{it} < 2.5 \times 10^9$  cm<sup>-2</sup> is necessary for over 1 year of device lifetime (gray area in **Figure 4-15(c)(d)**).

The physical thickness of SiGe layer behaving as a HK dielectric insulator is 1.2 nm. Although the mean-free path increases to 2 nm, it is shorter than total insulator thickness resulting no change in drain current with stress time. Therefore, the proposed FinHEMT has improved reliability than FinFET.

Figure 4-16. (a) Gate leakage current (b) drain current variation.

### 5. Conclusion

Highly scalable and variability-immune Si FinHEMT has been demonstrated with "well-tempered" 10 nm gate length characteristics. Highly enhanced electron mobility ~ 1100 cm<sup>2</sup>/Vs close to bulk-Si value and doubly enhanced effective mobility are achieved in FinHEMT by degrading SRS in s-Si QW channel, which results in highly improved mA-level on-current than that of FinFET with the same gate controllability. FinHEMT also shows an excellent uniformity to the underlap length and fin width variations owing to the low resistivity in the gate underlap and channel region. The FinHEMT is predicted to exhibit excellent scalability and sturdiness to process variability, and may be a promising device platform in mainstream Si technology scaling. Moreover, the operation principle of SiGe layer which behaves as an additional HK insulator improve the reliability of FinHEMT suppressing the gate leakage current.

## 6. Remaining work to be done

- Theoretical modeling of FinHEMT operation

Atomistic modeling and experiments of channel mobility by SRS.

Analytical modeling of VT and ID based on the unique band structure.

- Reliability evaluation window development Analyze the effect of device parameters on reliability. Comparing with experimental data, enhance the effectiveness of the evaluation window.

Extend it to circuit level.

#### REFERENCES

- [1] C. C. Wu, D. W. Lin, A. Keshavarzi, C. H. Huang, C. T. Chan, C. H. Tseng, C. L. Chen, C. Y. Hsieh, K. Y. Wong, M. L. Cheng, T. H. Li, Y. C. Lin, L. Y. Yang, C. P. Lin, C. S. Hou, H. C. Lin, J. L. Yang, K. F. Yu, M. J. Chen, T. H. Hsieh, Y. C. Peng, C. H. Chou, C. J. Lee, C. W. Huang, C. Y. Lu, F. K. Yang, H. K. Chen, L. W. Weng, P. C. Yen, S. H. Wang, S. W. Chang, S. W. Chuang, T. C. Gan, T. L. Wu, T. Y. Lee, W. S. Huang, Y. J. Huang, Y. W. Tseng, C. M. Wu, Eric Ou-Yang, K. Y. Hsu, L. T. Lin, S. B. Wang, T. M. Kwok, C. C. Su, C. H. Tsai, M. J. Huang, H. M. Lin, A. S. Chang, S. H. Liao, "High performance 22/20nm FinFET CMOS devices with advanced high-K/metal gate scheme," *2010 International Electron Devices Meeting*, San Francisco, CA, 2010, pp. 27.1.1-27.1.4, doi: 10.1109/IEDM.2010.5703430.

- [2] J. Singh, A. Bousquet, J. Ciavatti, K. Sundaram, J. S. Wong, K. W. Chew, A. Bandyopadhyay, S. Li, A. Bellaouar, S. M. Pandey, B. Zhu, A. Martin, C. Kyono, J.-S. Goo, H. S. Yang, A. Mehta, X. Zhang, O. Hu, S. Mahajan, E. Geiss, S. Yamaguchi S. Mittal, R. Asra, P. Balasubramaniam, J. Watts, D. Harame, R. M. Todi, S. B. Samavedam and D. K. Sohningh, "14nm FinFET technology for analog and RF applications," *2017 Symposium on VLSI Technology*, Kyoto, 2017, pp. T140-T141, doi: 10.23919/VLSIT.2017.7998154.

- [3] R. Singh, K. Aditya, S. S. Parihar, Y. S. Chauhan, R. Vega, T. B. Hook, and A. Dixit, "Evaluation of 10-nm Bulk FinFET RF Performance—Conventional Versus NC-FinFET," in *IEEE Electron Device Letters*, vol. 39, no. 8, pp. 1246-1249, Aug. 2018, doi: 10.1109/LED.2018.2846026.

- [4] Q. Huo, Z. Wu, X. Wang, W. Huang, J. Yao, J. Bu, F. Zhang, L. Li, and M. Liu, "Physics-Based Device-Circuit Cooptimization Scheme for 7-nm Technology Node SRAM Design and Beyond," in *IEEE Transactions on Electron Devices*, vol. 67, no. 3, pp. 907-914, March 2020, doi: 10.1109/TED.2020.2964610.

- [5] G. Yeap, S.S. Lin, Y.M. Chen, H.L. Shang, P.W. Wang, H.C. Lin, Y.C. Peng, J.Y. Sheu, M. Wang, X. Chen, B.R. Yang, C.P. Lin, F.C. Yang, Y.K. Leung, D.W. Lin, C.P. Chen, K.F. Yu, D.H. Chen, C.Y. Chang, H.K. Chen, P. Hung, C.S. Hou, Y.K. Cheng, J. Chang, L. Yuan, C.K. Lin, C.C. Chen, Y.C. Yeo, M.H. Tsai, H.T. Lin, C.O. Chui, K.B. Huang, W. Chang, H.J. Lin, K.W. Chen, R. Chen, S.H. Sun, Q. Fu, H.T. Yang, H.T. Chiang, C.C. Yeh, T.L. Lee, C.H. Wang, S.L. Shue, C.W. Wu, R. Lu, W.R. Lin, J. Wu, F. Lai, Y.H. Wu, B.Z. Tien, Y.C. Huang, L.C. Lu, Jun He, Y. Ku, J. Lin, M. Cao, T.S. Chang, and S.M. Jang "5nm CMOS Production Technology Platform featuring full-fledged EUV, and High Mobility Channel FinFETs with densest 0.021µm2 SRAM cells for Mobile SoC and High Performance Computing Applications," 2019 IEEE International Electron Devices

*Meeting (IEDM)*, San Francisco, CA, USA, 2019, pp. 36.7.1-36.7.4, doi: 10.1109/IEDM19573.2019.8993577.

- [6] K. Liu and E. Chen, "Investigation of the Effects and the Random-Dopant-Induced Variations of Source/Drain Extension of 7-nm Strained SiGe n-Type FinFETs," in *IEEE Transactions on Electron Devices*, vol. 66, no. 2, pp. 847-854, Feb. 2019, doi: 10.1109/TED.2018.2884246.

- [7] S. Natarajan *et al.*, "A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 μm<sup>2</sup> SRAM cell size," 2014 IEEE International Electron Devices Meeting, San Francisco, CA, 2014, pp. 3.7.1-3.7.3, doi: 10.1109/IEDM.2014.7046976.

- [8] H. -. Cho *et al.*, "Si FinFET based 10nm technology with multi Vt gate stack for low power and high performance applications," *2016 IEEE Symposium on VLSI Technology*, Honolulu, HI, 2016, pp. 1-2, doi: 10.1109/VLSIT.2016.7573359.

- [9] W. Xiong, C. Rinn Cleavelin, P. Kohli, C. Huffman, T. Schulz, K. Schruefer, G. Gebara, K. Mathews, P. Patruno, Yves-Matthieu Le Vaillant, I. Cayrefourcq, M. Kennard, C. Mazure, K. Shin, and T.-J. King Liu, "Impact of strained-silicon-on-insulator (sSOI) substrate on FinFET mobility," in *IEEE Electron Device Letters*, vol. 27, no. 7, pp. 612-614, July 2006, doi: 10.1109/LED.2006.877714.

- [10] O. Badami, F. Driussi, P. Palestri, L. Selmi and D. Esseni, "Performance comparison for FinFETs, nanowire and stacked nanowires FETs: Focus on the influence of surface roughness and thermal effects," 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2017, pp. 13.2.1-13.2.4, doi: 10.1109/IEDM.2017.8268382.

- [11] J. Yang, P. M. Zeitzoff and H. Tseng, "Highly Manufacturable Double-Gate FinFET With Gate-Source/Drain Underlap," in *IEEE Transactions on Electron Devices*, vol. 54, no. 6, pp. 1464-1470, June 2007, doi: 10.1109/TED.2007.896387.

- [12] A. B. Sachid, C. R. Manoj, D. K. Sharma and V. R. Rao, "Gate Fringe-Induced Barrier Lowering in Underlap FinFET Structures and Its Optimization," in *IEEE Electron Device Letters*, vol. 29, no. 1, pp. 128-130, Jan. 2008, doi: 10.1109/LED.2007.911974.

- [13] A. B. Sachid, M. Chen and C. Hu, "FinFET With High-κ Spacers for Improved Drive Current," in *IEEE Electron Device Letters*, vol. 37, no. 7, pp. 835-838, July 2016, doi: 10.1109/LED.2016.2572664.

- [14] T. Grasser, W. Gos and B. Kaczer, "Dispersive Transport and Negative Bias Temperature Instability: Boundary Conditions, Initial Conditions, and Transport Models," in *IEEE Transactions* on Device and Materials Reliability, vol. 8, no. 1, pp. 79-97, March 2008, doi: 10.1109/TDMR.2007.912779.

- [15] O. Penzin, A. Haggag, W. McMahon, E. Lyumkis and K. Hess, "MOSFET degradation kinetics and its simulation," in *IEEE Transactions on Electron Devices*, vol. 50, no. 6, pp. 1445-1450, June 2003, doi: 10.1109/TED.2003.813333.

- [16] V. Barral *et al.*, "Evidences on the Physical Origin of the Unexpected Transport Degradation in Ultimate n-FDSOI Devices," in *IEEE Transactions on Nanotechnology*, vol. 8, no. 2, pp. 167-173, March 2009, doi: 10.1109/TNANO.2008.2010128.

- [17] A. W. Dey, C. Thelander, E. Lind, K. A. Dick, B. M. Borg, M. Borgström, P. Nilsson, and L.-E. Wernersson, "High-Performance InAs Nanowire MOSFETs," in *IEEE Electron Device Letters*, vol. 33, no. 6, pp. 791-793, June 2012, doi: 10.1109/LED.2012.2190132.

- [18] T. K. Agarwal, M. Rau, I. Radu, M. Luisier, W. Dehaene and M. Heyns, "Performance Comparison of s-Si, In0.53Ga0.47As, Monolayer BP, and WS2-Based n-MOSFETs for Future Technology Nodes—Part I: Device-Level Comparison," in *IEEE Transactions on Electron Devices*, vol. 66, no. 8, pp. 3608-3613, Aug. 2019, doi: 10.1109/TED.2019.2912005.

- [19] K.-S Im, C.-H. Won, Y.-W. Jo, J.-H. Lee, M. Bawedin, S. Cristoloveanu, and J.-H Lee, "High-Performance GaN-Based Nanochannel FinFETs With/Without AlGaN/GaN Heterostructure," in *IEEE Transactions on Electron Devices*, vol. 60, no. 10, pp. 3012-3018, Oct. 2013, doi: 10.1109/TED.2013.2274660.

- [20] R. Zhang, P. Huang, J. Lin, N. Taoka, M. Takenaka and S. Takagi, "High-Mobility Ge p- and n-MOSFETs With 0.7-nm EOT Using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge Gate Stacks Fabricated by Plasma Postoxidation," in *IEEE Transactions on Electron Devices*, vol. 60, no. 3, pp. 927-934, March 2013, doi: 10.1109/TED.2013.2238942.

- [21] H. Liu, G. Han, Y. Xu, Y. Liu, T. K. Liu and Y. Hao, "High-Mobility Ge pMOSFETs With Crystalline ZrO2 Dielectric," in *IEEE Electron Device Letters*, vol. 40, no. 3, pp. 371-374, March 2019, doi: 10.1109/LED.2019.2895856.

- [22] I. Ok, K. Akarvardar, S. Lin, M. Baykan, C. D. Young, P.Y. Hung, M. P. Rodgers, S. Bennett, H. O. Stamper, D. L. Franca, J. Yum, J. P. Nadeau, C. Hobbs, P. Kirsch, P. Majhi, and R. Jammy, "Strained SiGe and Si FinFETs for high performance logic with SiGe/Si stack on SOI," 2010 International Electron Devices Meeting, San Francisco, CA, 2010, pp. 34.2.1-34.2.4, doi: 10.1109/IEDM.2010.5703474.

- [23] M. Togo, J. W. Lee, L. Pantisano, T. Chiarella, R. Ritzenthaler, R. Krom, A. Hikavyy, R. Loo, E. Rosseel, S. Brus, J. W. Maes, V. Machkaoutsan, J. Tolle, G. Eneman, A. D. Keersgieter, G. Boccardi, G. Mannaert, S. E. Altamirano, S. Locorotondo, M. Demand, N. Horiguchi, and A. Thean, "Phosphorus doped SiC Source Drain and SiGe channel for scaled bulk FinFETs," *2012 International Electron Devices Meeting*, San Francisco, CA, 2012, pp. 18.2.1-18.2.4, doi: 10.1109/IEDM.2012.6479064.

- [24] S. Takagi and M. Takenaka, "III-V/Ge CMOS technologies on Si platform," 2010 Symposium on VLSI Technology, Honolulu, 2010, pp. 147-148, doi: 10.1109/VLSIT.2010.5556205.

- [25] C. H. Lee, T. Nishimura, N. Saido, K. Nagashio, K. Kita and A. Toriumi, "Record-high electron mobility in Ge n-MOSFETs exceeding Si universality," 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, 2009, pp. 1-4, doi: 10.1109/IEDM.2009.5424323.

- [26] Yosuke Nakakita, Ryosho Nakane, Takashi Sasada, H. Matsubara, Mitsuru Takenaka and S. Takagi, "Interface-controlled self-align source/drain Ge pMOSFETs using thermally-oxidized GeO2 interfacial layers," 2008 IEEE International Electron Devices Meeting, San Francisco, CA, 2008, pp. 1-4, doi: 10.1109/IEDM.2008.4796838.

- [27] F. Schäffler, "High-mobility Si and Ge structures," in Semicond. Sci. Technol. vol. 12, pp. 1515-1549, December 1997, doi: 10.1088/0268-1242/12/12/001.

- [28] A. Kasamatsu, K. Kasai, K. Hikosaka, T. Matsui, and T. Mimura, "60 nm gate-length Si/SiGe HEMT," in *Appl. Surf. Sci.* vol. 224, pp. 382-385, March 2004, doi: 10.1016/j.apsusc.2003.08.064.

- [29] J. Welser, J. L. Hoyt and J. F. Gibbons, "Electron mobility enhancement in strained-Si n-type metaloxide-semiconductor field-effect transistors," in *IEEE Electron Device Letters*, vol. 15, no. 3, pp. 100-102, March 1994, doi: 10.1109/55.285389.

- [30] D. Laroche, S.-H. Huang, E. Nielsen, Y. Chuang, J.-Y. Li, C. W. Liu, and T. M. Lu, "Scattering mechanisms in shallow undoped Si/SiGe quantum wells," *AIP Advances*. 5, 107106, 2015, doi: 10.1063/1.4933026.

- [31] S. Kim, J. Y. Park and K. R. Kim, "FinHEMT: FinFET-based high electron mobility transistor with strained silicon channel," 2015 IEEE 15th International Conference on Nanotechnology (IEEE-NANO), Rome, 2015, pp. 905-908, doi: 10.1109/NANO.2015.7388761.

- [32] M. L. Lee, E. A. Fitzgerald, M. T. Bulsara, M. T. Currie, and A. Lochtefeld, "Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors," J. Appl. Phy. 97, 011101, 2005, doi: 10.1063/1.1819976.

- [33] J. M. Hartmann, B. Gallas, R. Fergusion, J. Fernandez, J. Zhang, and J. J. Harris, "Gas-source molecular beam epitaxy of SiGe virtual substrates: I. Growth kinetics and doping," Semicond. Sci. Technol., vol. 15, no. 4, pp. 362-369, 2000.

- [34] H. Klauk, T. N. Jackson, S. F. Nelson, and J. O. Chu, "Thermal stability of undoped strained Si channel SiGe heterostructures," *Appl. Phy. Lett.* 68 (14), 1996, doi: 10.1063/1.115644.

- [35] International Technology Roadmap for Semiconductors. Accessed: Jul. 2017. [Online]. Available: https://www.dropbox.com/sh/qz9gg6uu4kl04vj/AADD7ykFdJ2ZpCR1LAB2XEjIa?dl=0&previe w=PIDS\_2013Tables.xlsx

- [36] M. V. Fischetti, and S. E. Laux, "Band structure, deformation potentials, and carrier mobility in strained Si, Ge, and SiGe alloys," Journal of Applied Physics 80, 2234 (1996).

- [37] G. Tsutsui *et al.*, "Leakage aware Si/SiGe CMOS FinFET for low power applications," 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, 2018, pp. 87-88, doi: 10.1109/VLSIT.2018.8510639.

- [38] Synopsys Sentaurus Device User Guide Version D-2010.03, Synopsys, Mountain View, CA, USA, 2010.

- [39] A. Paul, S. Mehrotra, M. Luisier and G. Klimeck, "Performance Prediction of Ultrascaled SiGe/Si Core/Shell Electron and Hole Nanowire MOSFETs," in *IEEE Electron Device Letters*, vol. 31, no. 4, pp. 278-280, April 2010, doi: 10.1109/LED.2010.2040577.

- [40] Y. -F. Wu, B. P. Keller, S. Keller, N. X. Nguyen, M. Le, C. Nguyen, T. J. Jenkins, L. T. Kehias, S. P. Denbaars, and U. K. Mishra, "Short channel AlGaN/GaN MODFET's with 50-GHz f<sub>T</sub> and 1.7-W/mm output-power at 10 GHz," in *IEEE Electron Device Letters*, vol. 18, no. 9, pp. 438-440, Sept. 1997, doi: 10.1109/55.622522.

- [41] S. Mittal, S. Gupta, A. Nainani, M. C. Abraham, K. Schuegraf, S. Lodha, and U. Ganguly, "Epitaxially Defined FinFET: Variability Resistant and High-Performance Technology," in *IEEE Transactions on Electron Devices*, vol. 61, no. 8, pp. 2711-2718, Aug. 2014, doi: 10.1109/TED.2014.2329993.

- [42] P. K. Pal, B. K. Kaushik and S. Dasgupta, "Asymmetric Dual-Spacer Trigate FinFET Device-Circuit Codesign and Its Variability Analysis," in *IEEE Transactions on Electron Devices*, vol. 62, no. 4, pp. 1105-1112, April 2015, doi: 10.1109/TED.2015.2400053.

- [43] T. Matsukawa *et al.*, "Suppressing Vt and Gm variability of FinFETs using amorphous metal gates for 14 nm and beyond," *2012 International Electron Devices Meeting*, San Francisco, CA, 2012, pp. 8.2.1-8.2.4, doi: 10.1109/IEDM.2012.6479002.

- [44] A. Sudarsanan, S. Venkateswarlu and K. Nayak, "Impact of Fin Line Edge Roughness and Metal Gate Granularity on Variability of 10-nm Node SOI n-FinFET," in *IEEE Transactions on Electron Devices*, vol. 66, no. 11, pp. 4646-4652, Nov. 2019, doi: 10.1109/TED.2019.2941896.

- [45] S. J. Mason, "Power gain in feedback amplifiers," IRE Trans. Circuit Theory, 1954.

- [46] C. Fiegna, F. Venturi, M. Melanotte, E. Sangiorgi and B. Ricco, "Simple and efficient modeling of EPROM writing," in *IEEE Transactions on Electron Devices*, vol. 38, no. 3, pp. 603-610, March 1991, doi: 10.1109/16.75172.

- [47] M. A. Alam and S. Mahapatra, "A comprehensive model of PMOS NBTI degradation," *Microelectronics Reliability*, vol. 45, no. 1, pp. 71-81, 2005.

- [48] A. Gnudi, D. Ventura, G. Baccarani and F. Odeh, "Two-dimensional MOSFET Simulation by means of Multidimensional Spherical Harmonics Expansion of the Boltzmann Transport Equation," *ESSDERC '92: 22nd European Solid State Device Research conference*, Leuven, Belgium, 1992, pp. 917-924.

[49] A. Makarov *et al.*, "Bi-Modal Variability of nFinFET Characteristics During Hot-Carrier Stress: A Modeling Approach," in *IEEE Electron Device Letters*, vol. 40, no. 10, pp. 1579-1582, Oct. 2019, doi: 10.1109/LED.2019.2933729.