| Title                       | A Study of the Functional Memory Type Parallel Processor(Dissertation_全文) |  |

|-----------------------------|---------------------------------------------------------------------------|--|

| Author(s)                   | Kobayashi, Kazutoshi                                                      |  |

| Citation                    | Kyoto University (京都大学)                                                   |  |

| Issue Date                  | 1999-01-25                                                                |  |

| URL                         | http://dx.doi.org/10.11501/3147511                                        |  |

| Right                       |                                                                           |  |

| Type Thesis or Dissertation |                                                                           |  |

| Textversion                 | sion author                                                               |  |

# A Study of the Functional Memory Type Parallel Processor

http://www.tamaru.kuee.kyoto-u.ac.jp/fmpp/

Kazutoshi Kobayashi

**Kyoto University**

September 1998

## **Abstract**

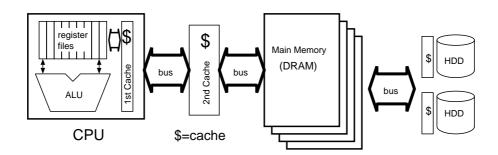

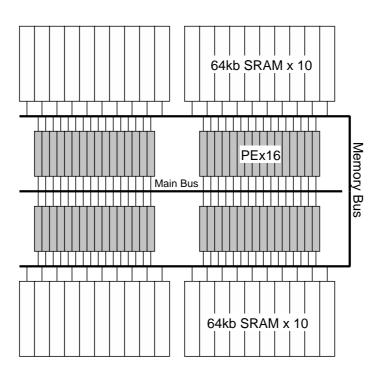

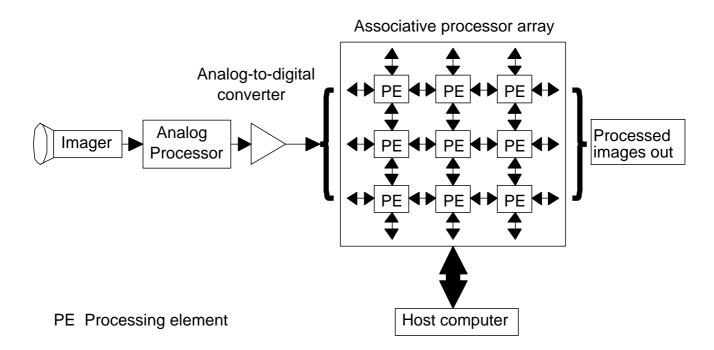

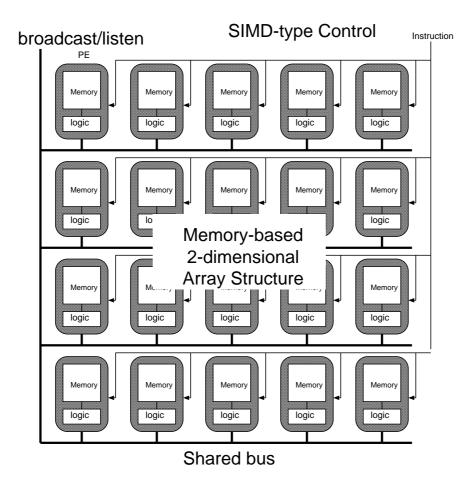

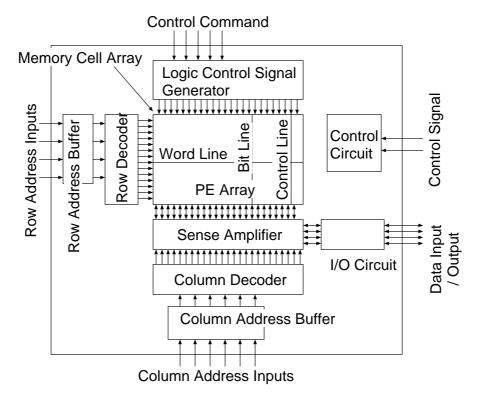

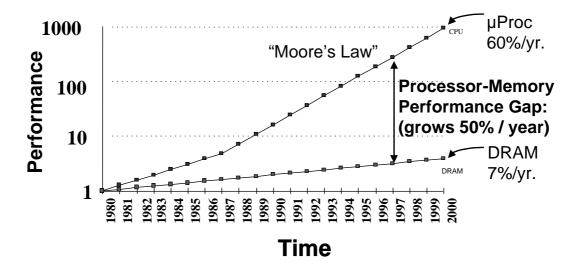

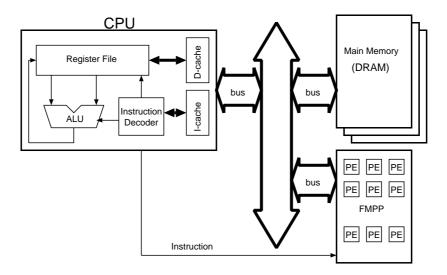

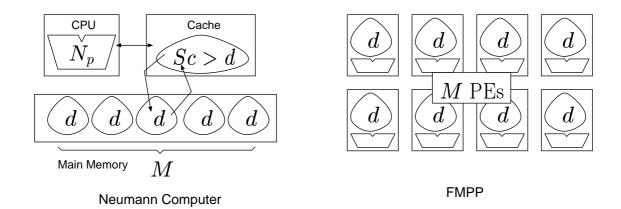

This paper describes a memory-based SIMD shared-bus parallel processor architecture, which is called "Functional Memory Type Parallel Processor" abbreviated as FMPP. The FMPP architecture integrates memory and an ALU closely on a single die. All the PEs are connected with a shared bus and laid out in a two-dimensional array like memory and perform the same instructions according to the SIMD manner. The FMPP architecture enables massively parallel computing inside a memory. It has a capability to break the Von Neumann bottleneck where the system performance is limited by the bus performance between memory and CPU.

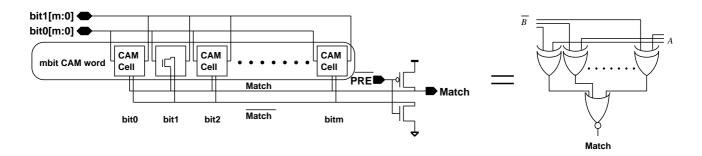

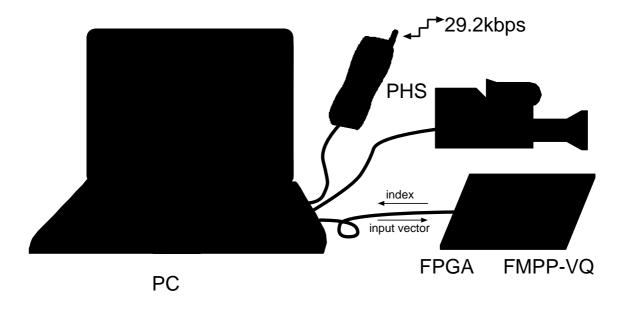

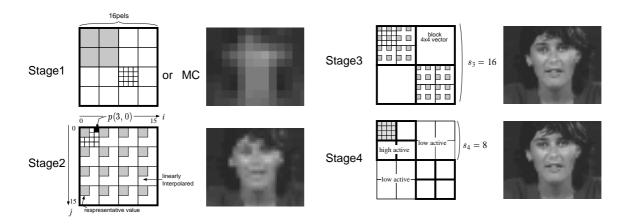

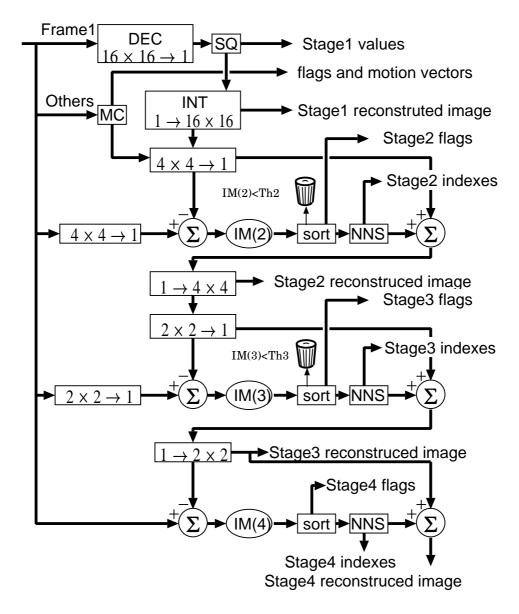

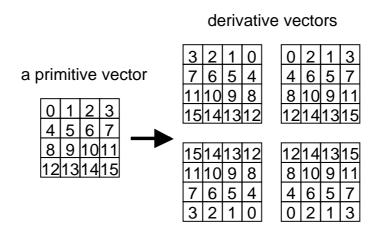

We have developed four LSIs based on the bit-parallel block-parallel architecture, where a PE consists of several words and a bit-parallel ALU. The first LSI called the BPBP-FMPP with 8 PEs is designed and fabricated for general purpose. A PE consists of 32bit CAM words and a 32bit ALU for numerical and logical operations. The following three LSIs called FMPP-VQ are for a special purpose: vector quantization (VQ). A PE consists of 16 words of 8bit SRAMs and a 12bit ALU. The FMPP-VQ accelerates the nearest neighbor search where the vector nearest to an input is extracted among large number of code vectors. The FMPP-VQ4 with 4 PEs is an evaluation LSI to confirm functionalities. The second FMPP-VQ64 integrates 64 PEs. It performs over 50,000 nearest neighbor searches per second, while its power consumption is 20mW. It can be used for real-time low-rate video compression. The third FMPP-VQ64M is designed for more powerful and low-power computation. Its performance becomes almost twice, while its power consumption is half compared with the FMPP-VQ64. We have also developed a low-rate video compression system using the FMPP-VQ. The proposed multi-stage hierarchical vector quantization algorithm can transmit 10 QCIF frames per second through a 29.2kbps mobile channel.

# **Contents**

| 1 | Intr | oductio       | n                                                              | 1  |

|---|------|---------------|----------------------------------------------------------------|----|

| 2 | Ove  | rview o       | f Parallel Processor and Functional Memory                     | 3  |

|   | 2.1  | Paralle       | el Processor Architectures to Break the Von Neumann Bottleneck | 3  |

|   |      | 2.1.1         | Von Neumann Computer Architecture                              | 3  |

|   |      | 2.1.2         | SIMD Parallel Processor to Solve the Von Neumann Bottleneck    | 5  |

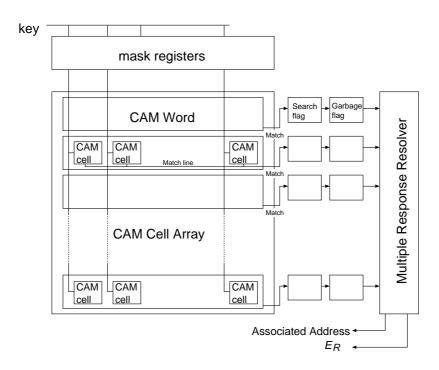

|   | 2.2  | Functi        | onal Memory and Associative Processor                          | 7  |

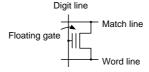

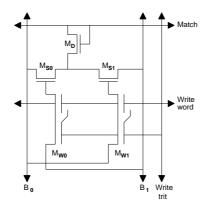

|   |      | 2.2.1         | Content Addressable Memory                                     | 7  |

|   |      | 2.2.2         | Associative Processors                                         | 9  |

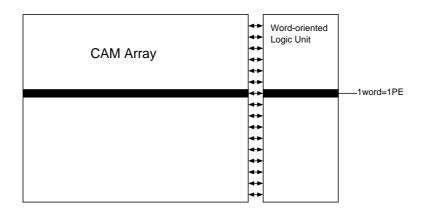

|   |      | 2.2.3         | Implementations of Associative Processors                      | 10 |

|   | 2.3  | Summ          | ary of the Chapter                                             | 13 |

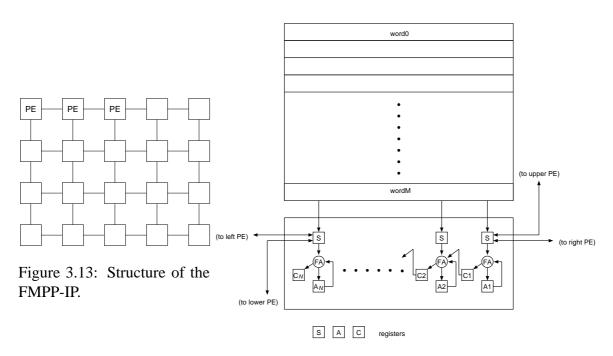

| 3 | Fun  | ctional       | Memory Type Parallel Processor: FMPP                           | 15 |

|   | 3.1  | Featur        | res of the FMPP                                                | 15 |

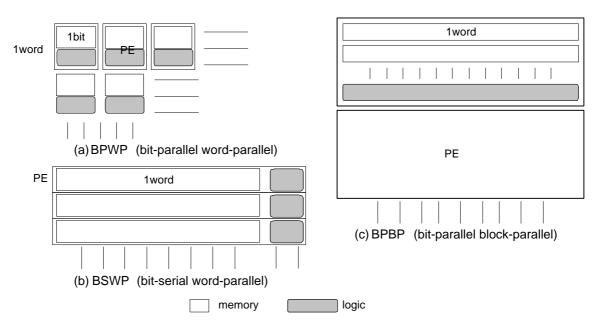

|   | 3.2  | FMPP          | Architectures According to the PE Granuality                   | 17 |

|   | 3.3  | Imple         | mentations of the FMPP Architecture                            | 18 |

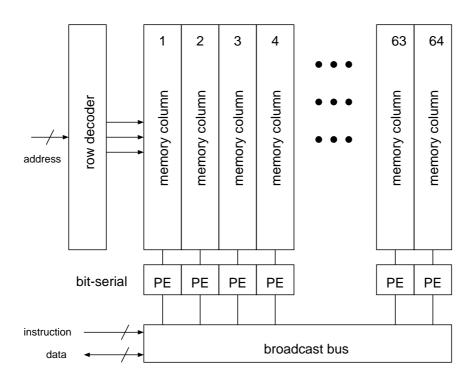

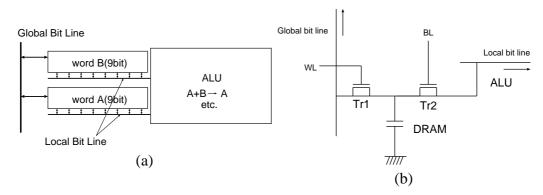

|   |      | 3.3.1         | Bit-serial Word-parallel Architecture                          | 19 |

|   |      | 3.3.2         | Bit-parallel Block-parallel Architecture                       | 21 |

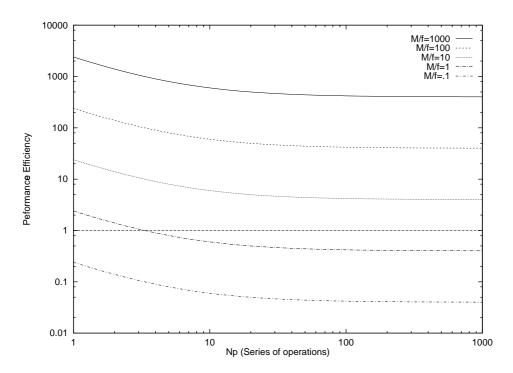

|   | 3.4  | Paralle       | el Computation Efficiency on the FMPP                          | 25 |

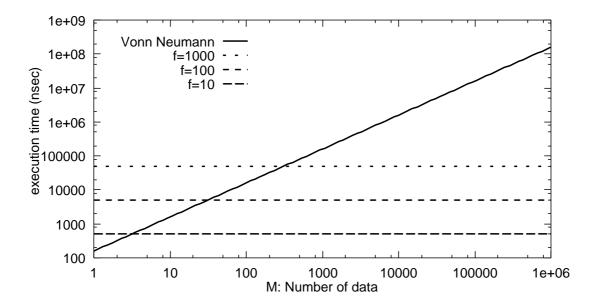

|   |      | 3.4.1         | Von Neumann Bottle Neck on the Conventional Computer           | 25 |

|   |      | 3.4.2         | Parallel Computation on the FMPP                               | 27 |

|   | 3.5  | Summ          | ary of the Chapter                                             | 31 |

| 4 | An l | <b>Implem</b> | entation of the Bit-Parallel Block-Parallel FMPP               | 33 |

|   | 4.1  | BPBP          | -FMPP                                                          | 33 |

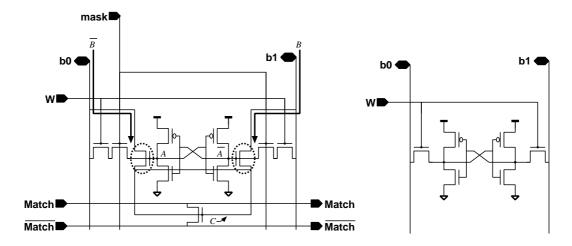

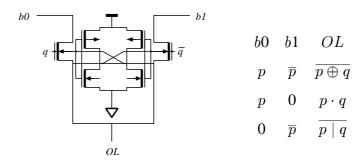

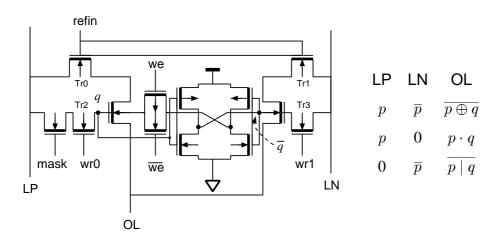

|   |      | 4.1.1         | Logical Operations on the CAM Cell                             | 34 |

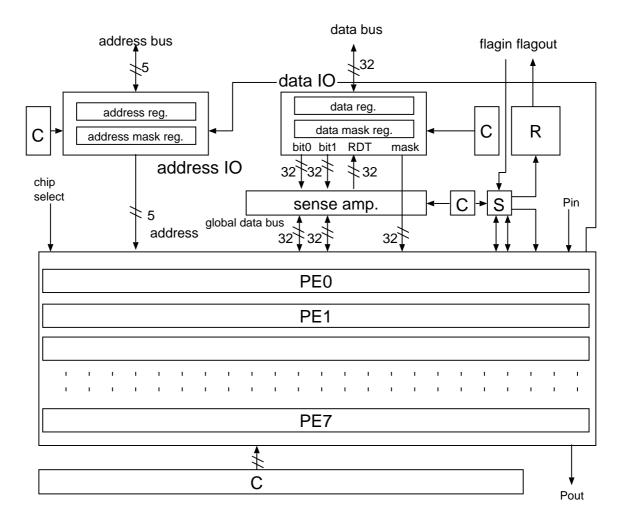

|   |      | 4.1.2         | Block Diagram                                                  | 34 |

|   |      | 4.1.3         | Primary Operations                                             | 35 |

|   |      | 4.1.4         | Data Mask and Address Mask Operations                          | 36 |

<u>iv</u> Contents

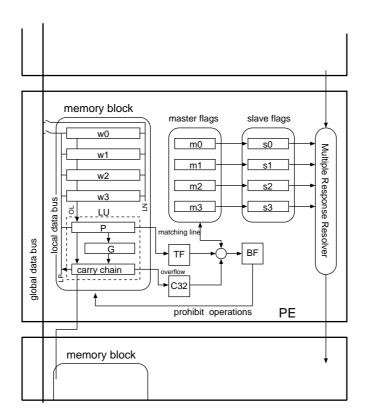

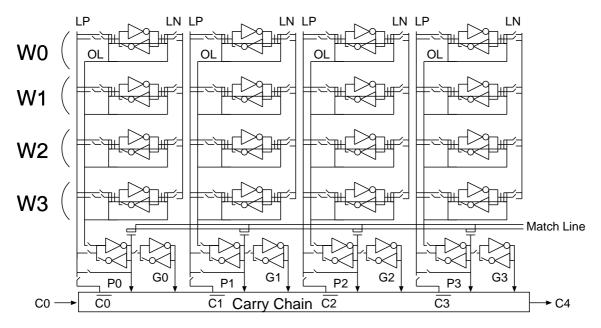

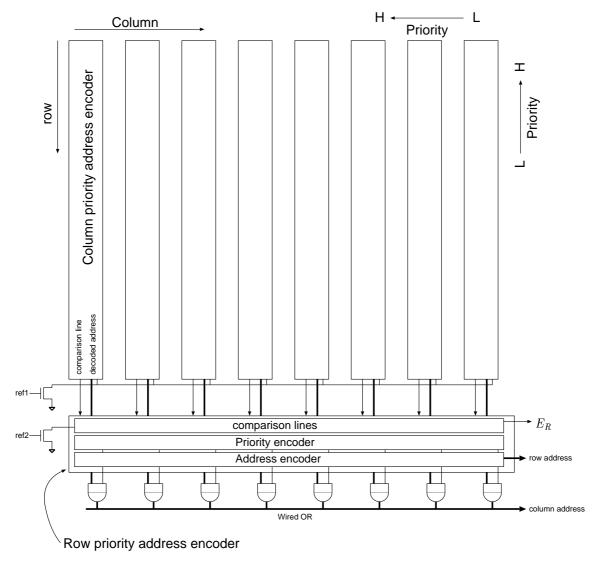

|   |     | 4.1.5     | Detailed Structure of the Memory Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

|---|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 4.2 | Detaile   | ed Operation Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 |

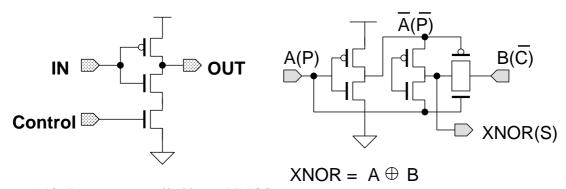

|   |     | 4.2.1     | Logical Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

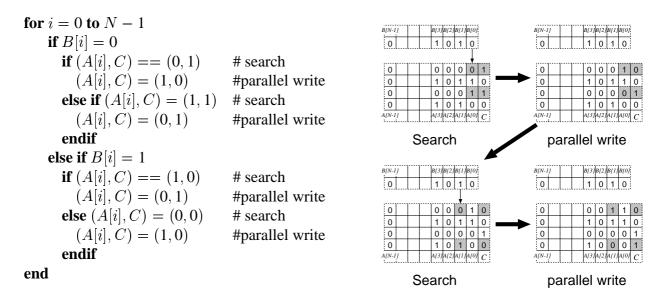

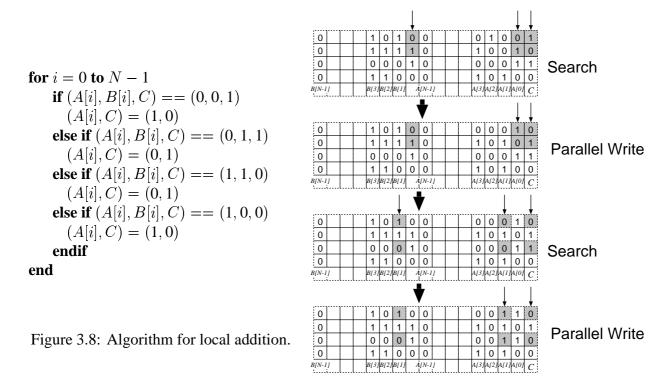

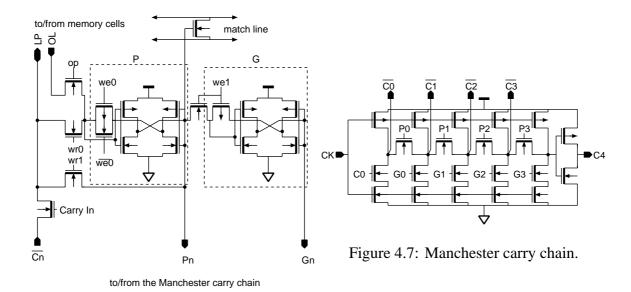

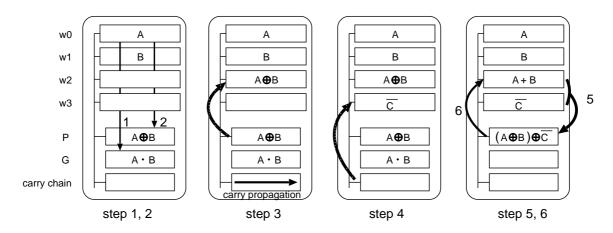

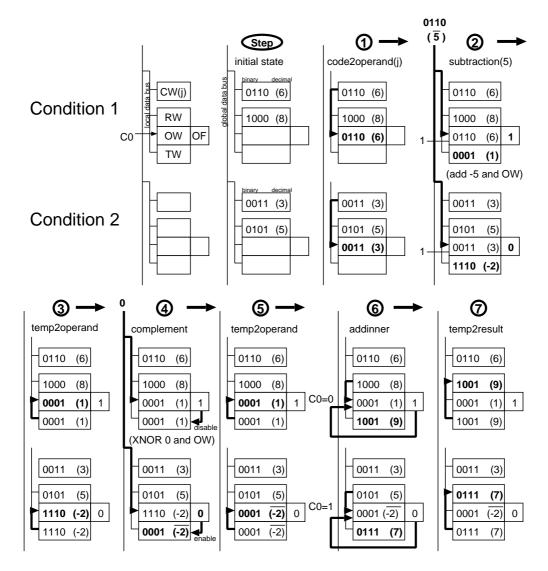

|   |     | 4.2.2     | Addition and Subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39 |

|   |     | 4.2.3     | Shift/rotate Left Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41 |

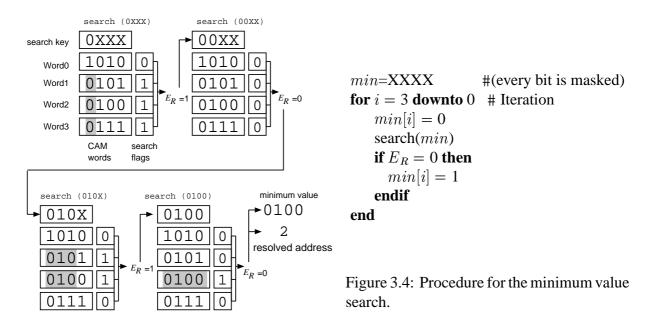

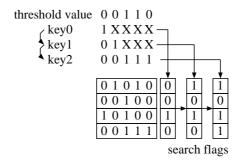

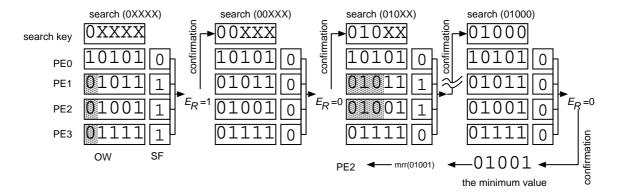

|   |     | 4.2.4     | Search Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41 |

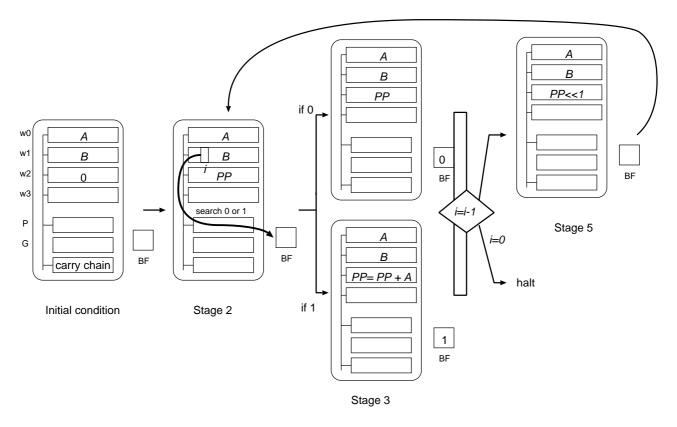

|   |     | 4.2.5     | Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41 |

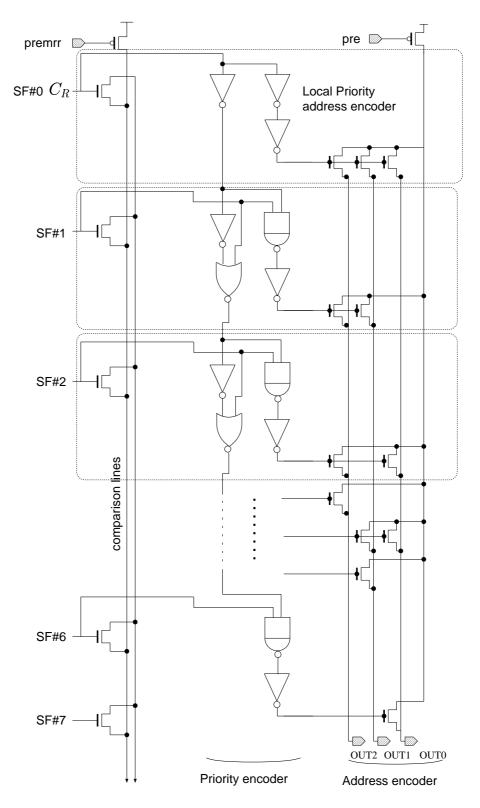

|   |     | 4.2.6     | Multiple Response Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 |

|   | 4.3 | 1kbit I   | BPBP-FMPP LSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43 |

|   |     | 4.3.1     | LSI Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 |

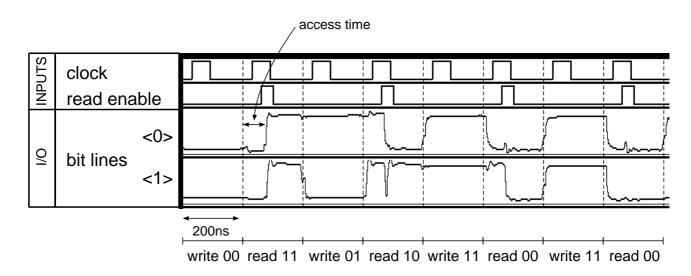

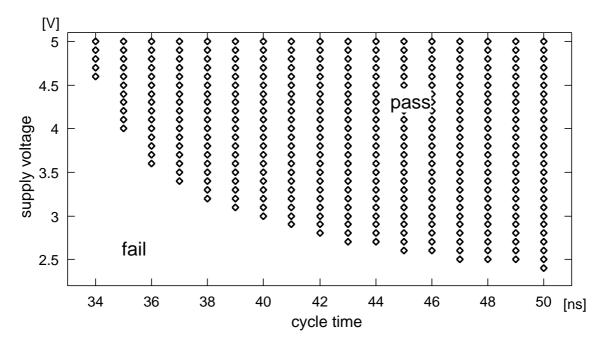

|   |     | 4.3.2     | Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44 |

|   |     | 4.3.3     | Comparison for the Circuit Areas between CMOS and CPL Logics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45 |

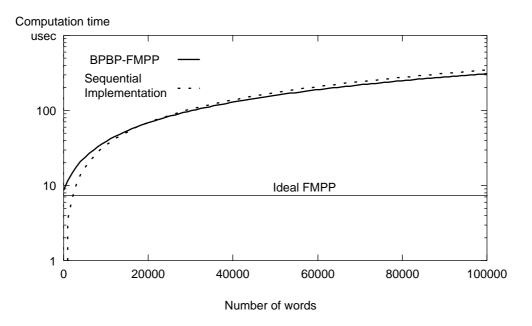

|   | 4.4 | Applic    | ations of the BPBP-FMPP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

|   |     | 4.4.1     | Threshold Search and Extremum Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47 |

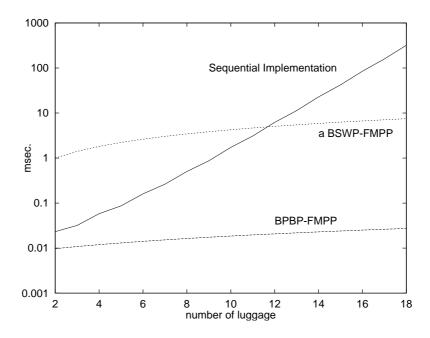

|   |     | 4.4.2     | Knapsack Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48 |

|   | 4.5 | Summ      | ary of the Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |

| 5 | Fun | ctional ' | Memory Type Parallel Processor for Vector Quantization: FMPP-VQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51 |

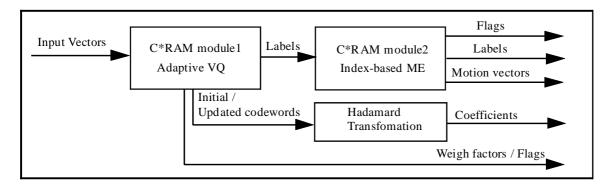

| • | 5.1 |           | action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51 |

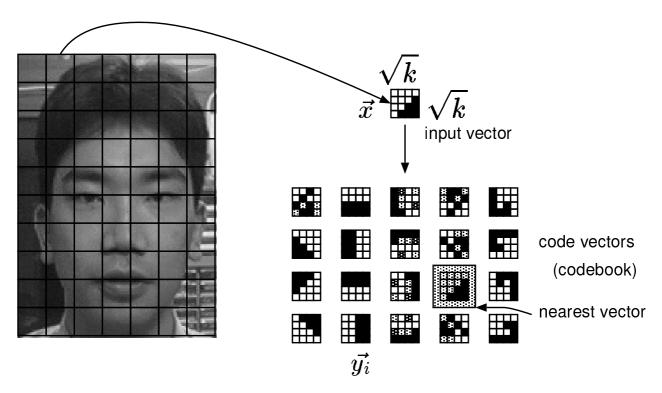

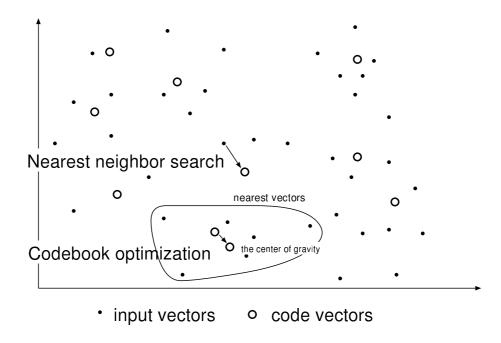

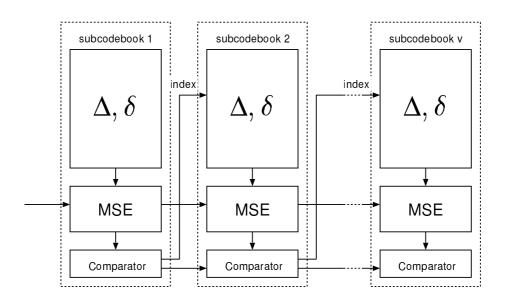

|   | 5.2 |           | Quantization of Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53 |

|   | 5.3 |           | Quantization on the FMPP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

|   | 5.4 |           | ecture and Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56 |

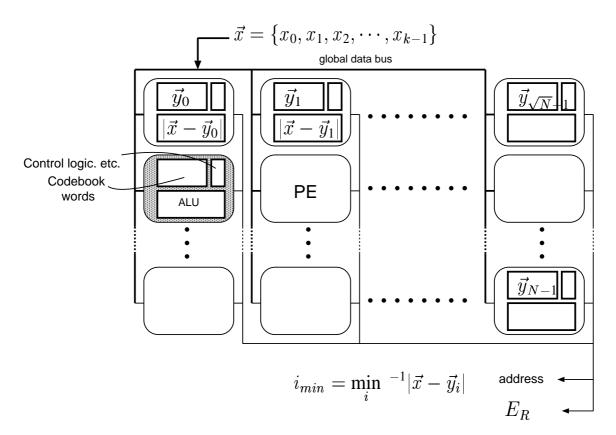

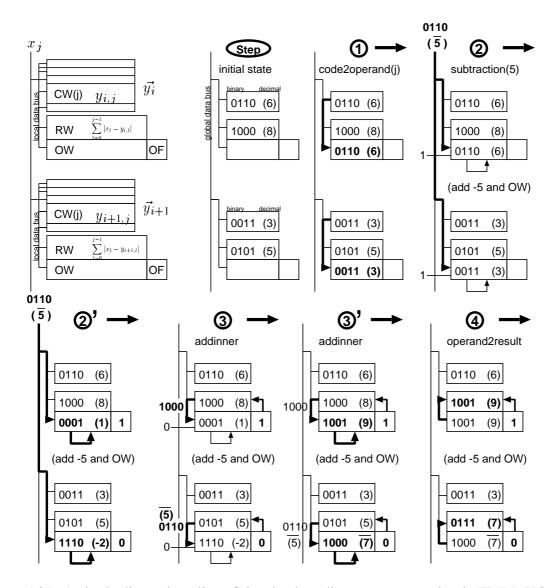

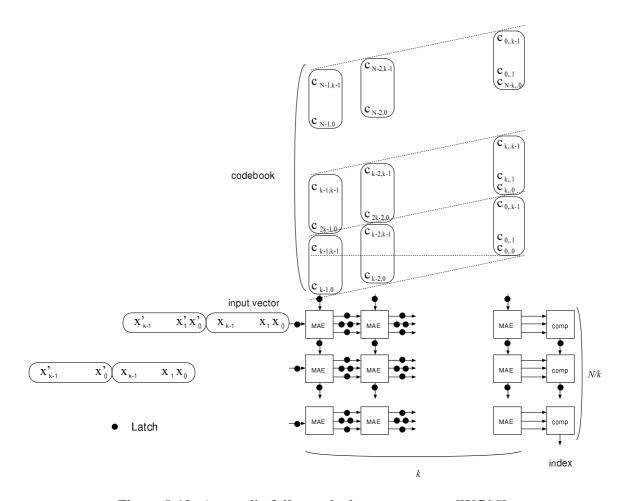

|   | J., | 5.4.1     | Nearest Neighbor Search on the FMPP-VQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57 |

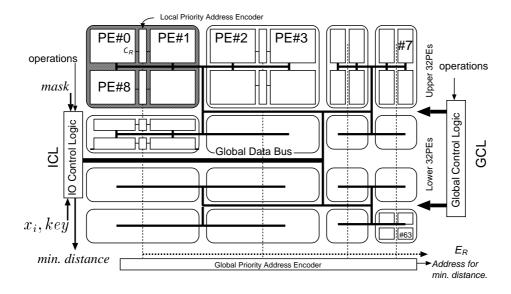

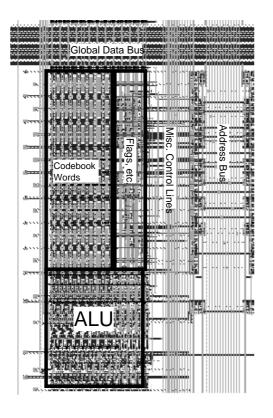

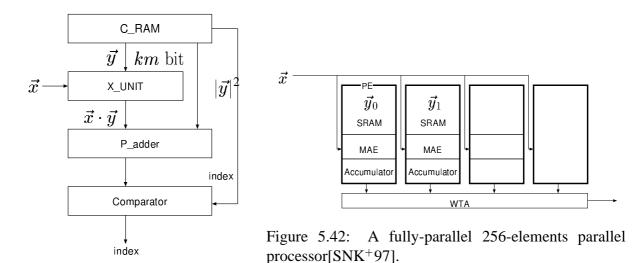

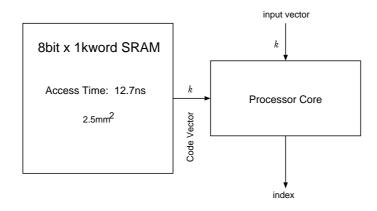

|   |     | 5.4.2     | Structure of the FMPP-VQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58 |

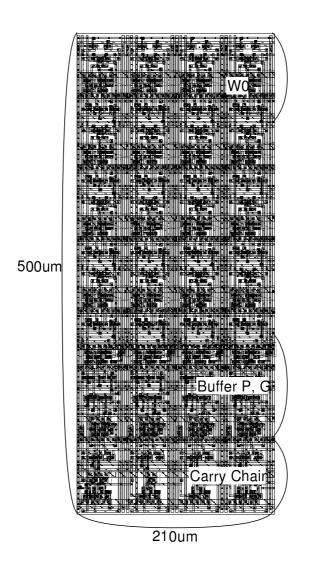

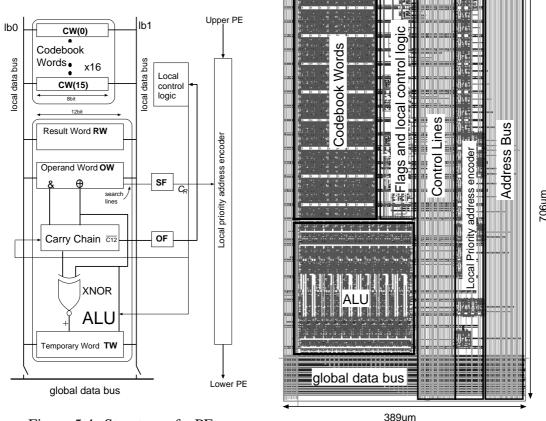

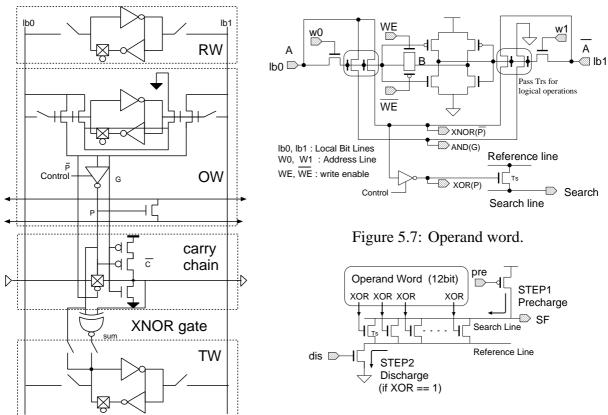

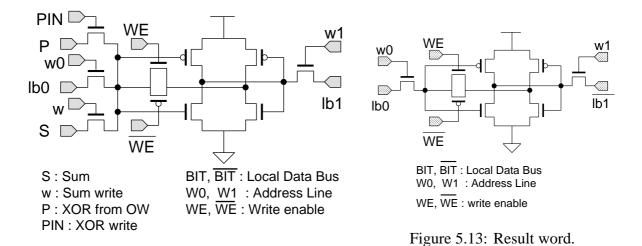

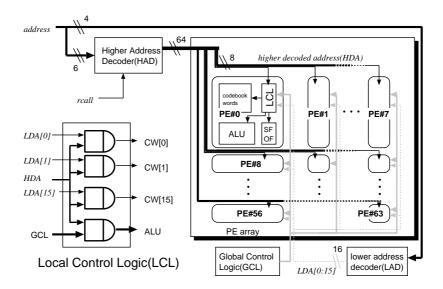

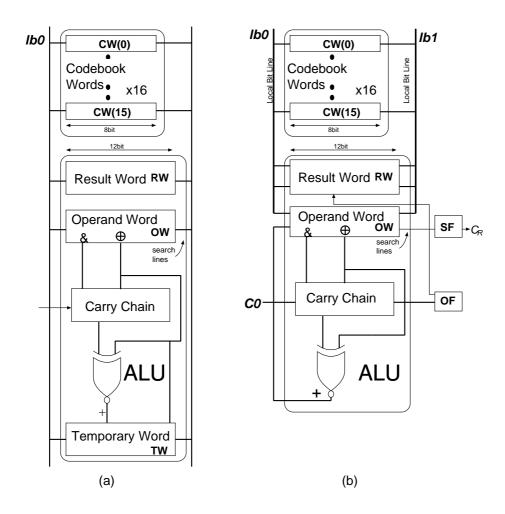

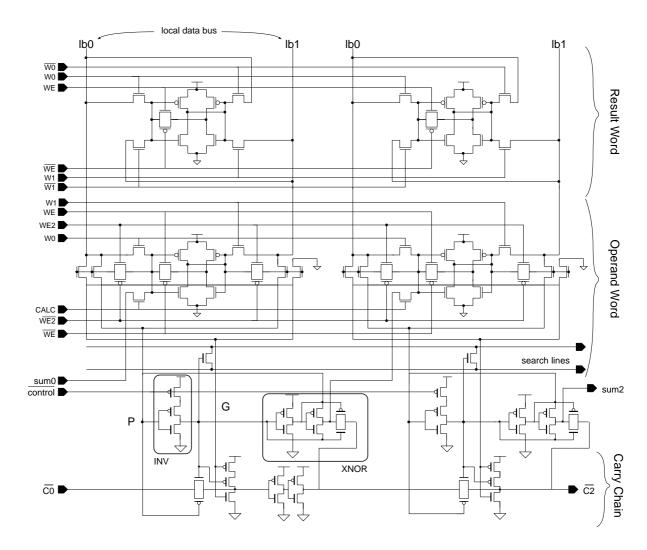

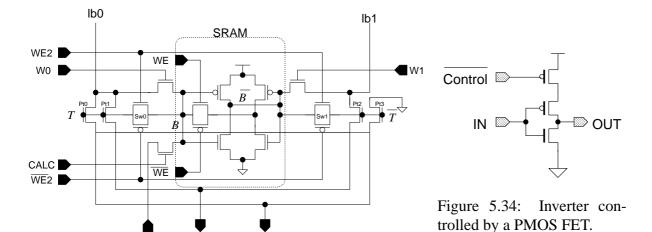

|   |     | 5.4.3     | Detailed Structure of the PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

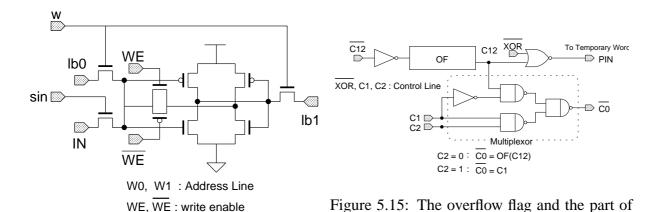

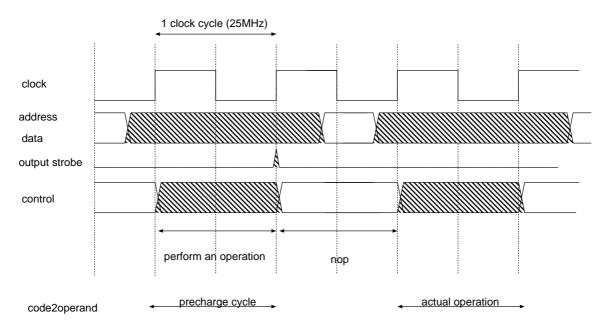

|   |     | 5.4.4     | Nearest Neighbor Search Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67 |

|   |     | 5.4.5     | List of Operations on the FMPP-VQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68 |

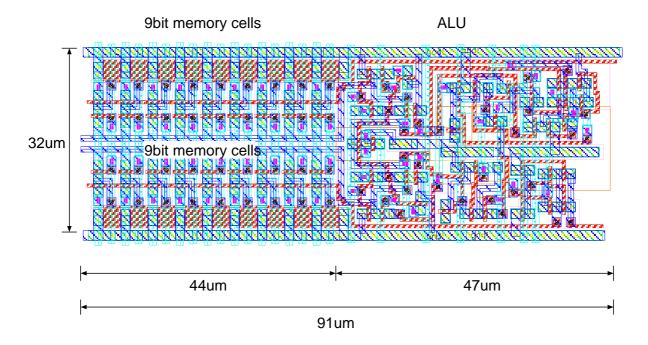

|   | 5.5 |           | mentations of FMPP-VQ LSIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72 |

|   | 0.0 | 5.5.1     | An LSI Including Four PEs and TEGs: FMPP-VQ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

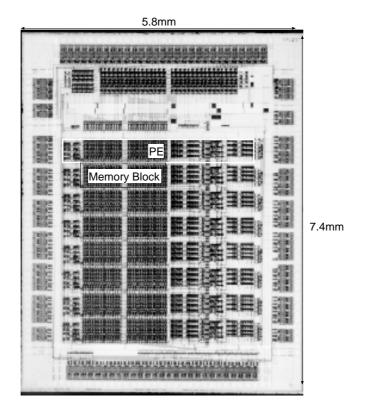

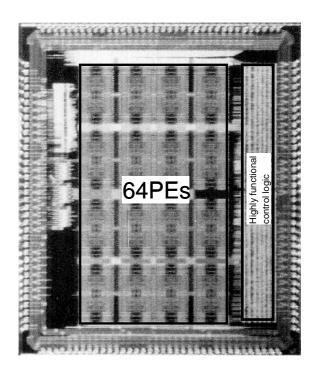

|   |     | 5.5.2     | An LSI Including 64 PEs and Control Logics: FMPP-VQ64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73 |

|   |     | 5.5.3     | Integration Density of the FMPP-VQ64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76 |

|   |     | 5.5.4     | Testability of the FMPP-VQ64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77 |

|   | 5.6 |           | ed Version of the FMPP-VQ: FMPP-VQ64M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78 |

|   | 5.0 | 5.6.1     | Structure of a PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79 |

|   |     | 5.0.1     | Substance of ulline in the control of the control of ulline in the cont | 1) |

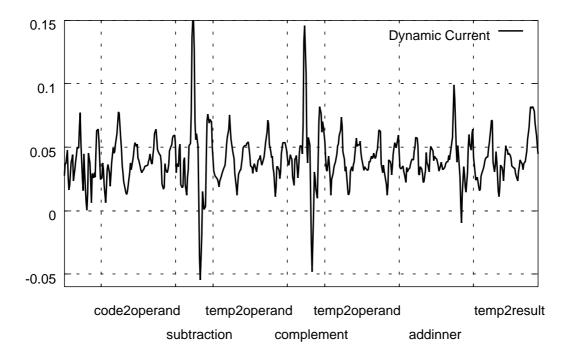

|   |     | 5.6.2     | Absolute Distance Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80 |

Contents v

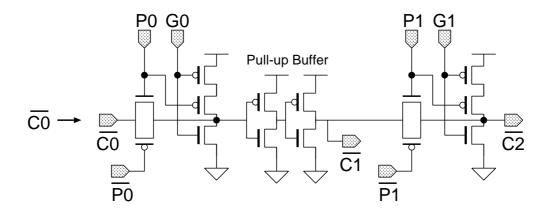

|    |                 | 5.6.3   | Detailed Structure of the ALU                                             | 81  |

|----|-----------------|---------|---------------------------------------------------------------------------|-----|

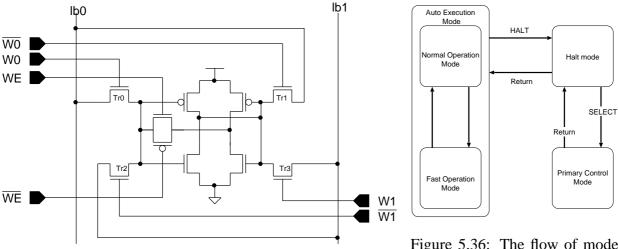

|    |                 | 5.6.4   | A Highly-Functional Control Logic                                         | 83  |

|    |                 | 5.6.5   | Specification and Implementation                                          | 84  |

|    | 5.7             | Compa   | arison with Other Implementations                                         | 88  |

|    |                 | 5.7.1   | Comparison with the Other Vector Quantizer                                | 88  |

|    |                 | 5.7.2   | Comparison with the Von Neumann Sequential Processors                     | 92  |