| Title       | Design and Fabrication of RESURF MOSFETs on 4H-SiC(0001), (1120), and 6H-SiC(0001)                                                                                                                                                                                                                                                                |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Author(s)   | Kimoto, T; Kosugi, H; Suda, J; Kanzaki, Y; Matsunami, H                                                                                                                                                                                                                                                                                           |  |  |  |

| Citation    | IEEE TRANSACTIONS ON ELECTRON DEVICES (2005), 52(1): 112-117                                                                                                                                                                                                                                                                                      |  |  |  |

| Issue Date  | 2005-01                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| URL         | http://hdl.handle.net/2433/39986                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Right       | (c)2005 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. |  |  |  |

| Туре        | Journal Article                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Textversion | publisher; none                                                                                                                                                                                                                                                                                                                                   |  |  |  |

# Design and Fabrication of RESURF MOSFETs on 4H-SiC(0001), $(11\bar{2}0)$ , and 6H-SiC(0001)

Tsunenobu Kimoto, *Member, IEEE*, Hajime Kosugi, Jun Suda, Yosuke Kanzaki, and Hiroyuki Matsunami, *Fellow, IEEE*

Abstract—Design and fabrication of lateral SiC reduced surface field (RESURF) MOSFETs have been investigated. The doping concentration (dose) of the RESURF and lightly doped drain regions has been optimized to reduce the electric field crowding at the drain edge or in the gate oxide by using device simulation. The optimum oxidation condition depends on the polytype: N2O oxidation at 1300 °C seems to be suitable for 4H-SiC, and dry O<sub>2</sub> oxidation at 1250 °C for 6H-SiC. The average inversion-channel mobility is 22, 78, and 68 cm<sup>2</sup>/Vs for 4H-SiC(0001),  $(11\bar{2}0)$ , and 6H-SiC(0001) MOSFETs, respectively. RESURF MOSFETs have been fabricated on  $10-\mu$ m-thick p-type 4H-SiC(0001), (11 $\bar{2}$ 0), and 6H-SiC(0001) epilayers with an acceptor concentration of  $1 \times 10^{16}$  cm<sup>-3</sup>. A 6H-SiC(0001) RESURF MOSFET with a 3- $\mu$ m channel length exhibits a high breakdown voltage of 1620 V and an on-resistance of 234 m $\Omega$  · cm<sup>2</sup>. A 4H–SiC(11 $\bar{2}$ 0) RESURF MOSFET shows the characteristics of 1230 V-138 m $\Omega \cdot \text{cm}^2$ .

*Index Terms*—Power device, power MOSFET, reduced surface field (RESURF), silicon carbide (SiC).

### I. INTRODUCTION

as a promising wide bandgap semiconductor projected for high-power devices [1], owing to its high electric breakdown field, high thermal conductivity, and reasonable maturity of crystals. Through recent progress in SiC device technology, high-voltage (300-1200 V) Schottky-barrier diodes have been commercially available [2]. In order to enjoy the full benefits of SiC-based power electronic systems such as high-voltage, low-loss, and high switching speed, SiC power switches are strongly required. In particular, SiC power metal-oxide-semiconductor field effect transistors (MOSFETs) have been recognized as an ideal power switch for a variety of voltage ranges, at least below 3 kV. Several groups have demonstrated vertical SiC power MOSFETs, which outperform the Si counterparts [3]–[7]. On the other hand, lateral SiC power MOSFETs are promising for high-voltage power integrated circuit (IC) applications in the future. Although several high-voltage lateral SiC MOSFETs have been reported [8]–[10], both the on-resistance and breakdown voltage have not reached the level achieved in vertical SiC MOSFETs.

In this paper, the design issues and fabrication of lateral SiC reduced surface field (RESURF) MOSFETs are inves-

Manuscript received June 16, 2004; revised November 11, 2004. This work was supported in part by Scientific Research Grant-in-Aid 16360153, in part by the 21st century COE program, Ministry of Education, Culture, Sports, Science and Technology, Japan under Grant 14213201, and in part by the TEPCO Research Foundation. The review of this paper was arranged by Editor M. A. Shibib.

The authors are with the Department of Electronic Science and Engineering, Kyoto University, Kyoto 615-8510, Japan (e-mail: kimoto@kuee.kyoto-u.ac.jp). Digital Object Identifier 10.1109/TED.2004.841358

TABLE I AVERAGE EFFECTIVE MOBILITY (cm²/Vs) for 4H-SiC(0001), (11 $\bar{2}0$ ), and 6H-SiC(0001) MOSFETs. The Acceptor Concentration of P-type Epilayers Is about 1  $\times 10^{16}$  cm $^{-3}$

| Substrate    | Oxidation condition         |                          |                          |                          |  |

|--------------|-----------------------------|--------------------------|--------------------------|--------------------------|--|

|              | wet O <sub>2</sub> , 1150°C | $dry \ O_2, \ 1250^{o}C$ | $dry \ O_2, \ 1300^{o}C$ | N <sub>2</sub> O, 1300°C |  |

| 4H-SiC(0001) | 8.2                         | 4.1                      | 3.9                      | 22                       |  |

| 4H-SiC(1120) | 22                          | 2.0                      | 0.11                     | 78                       |  |

| 6H-SiC(0001) | 36                          | 68                       | 37                       | 39                       |  |

|              |                             |                          |                          |                          |  |

tigated. MOSFETs have been processed on 4H-SiC(0001), 4H-SiC(11 $\overline{2}0$ ), and 6H-SiC(0001) substrates. An improvement of effective channel mobility has been also tried by high-temperature oxidation in  $O_2$  or  $N_2O$ . High breakdown voltages (1020–1620 V) are realized in fabricated devices.

## II. INCREASE OF EFFECTIVE CHANNEL MOBILITY BY HIGH-TEMPERATURE OXIDATION

The performance of SiC power MOSFETs is generally limited by a high channel resistance, or a low effective channel mobility. Okuno *et al.* reported that the interface state density for 4H-SiC(0001) MOS structures is reduced by increasing the oxidation temperature to 1250 °C [11]. On the other hand, post-oxidation annealing or direct oxidation in NO has been recognized as an effective process to improve the quality of 4H-SiC(0001) MOS interface [12]. More recently, the usage of N<sub>2</sub>O has been proposed for safety reason [13]. As another approach, the authors' group has found that 4H-SiC(11 $\bar{2}$ 0) exhibits superior MOS characteristics, especially processed by wet oxidation [14]. In this paper, planar n-channel MOSFETs were fabricated on 4H-SiC(0001), 4H-SiC(11 $\bar{2}$ 0), and 6H-SiC(0001) with gate oxides grown by either dry O<sub>2</sub> or N<sub>2</sub>O at high temperature in order to improve the channel mobility.

P-type epilayers with an acceptor concentration of  $1\text{--}2\times10^{16}~\text{cm}^{-3}$  were used [15], [16]. Source and drain regions were formed by P<sup>+</sup> ion implantation at 300 °C followed by annealing in pure Ar at 1600 °C for 30 min. The total implant dose was  $3\times10^{15}~\text{cm}^{-2}$ . Then, 50–70-nm-thick gate oxides were grown. Oxidation was performed in dry O<sub>2</sub> (10% diluted in N<sub>2</sub>) or N<sub>2</sub>O (also 10% diluted in N<sub>2</sub>) at 1250–1300 °C. Al was used as gate and ohmic contacts. The typical channel length and width were 30 and 200  $\mu$ m, respectively.

Table I summarizes the average effective channel mobility obtained for planar inversion-type MOSFETs fabricated on 4H-SiC(0001),  $(11\overline{2}0)$ , and 6H-SiC(0001) epilayers. Typ-

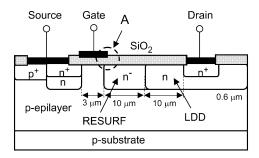

Fig. 1. Schematic structure of an SiC RESURF MOSFET simulated and fabricated in this paper. Both RESURF and LDD regions are  $10~\mu$  m long and  $0.6~\mu$ m deep. The p-type epilayer is  $10~\mu$ m thick, doped to  $1 \times 10^{16}~\rm cm^{-3}$ . The typical thickness of gate oxide and channel length are  $100~\rm nm$  and  $3~\mu$ m, respectively.

ical mobilities obtained by conventional wet  $O_2$  oxidation at 1150 °C are also shown for comparison. Dry  $O_2$  oxidation at 1250 °C resulted in a high channel mobility of 68 cm²/Vs for 6H-SiC(0001) MOSFET, but further increase in oxidation temperature caused a decrease in mobility. In the case of 4H-SiC, dry  $O_2$  oxidation at high temperature did not bring the improvement of channel mobility for both (0001) and (11 $\overline{2}$ 0). Instead, direct oxidation by  $N_2O$  at 1300 °C is very effective to enhance the mobility of 4H-SiC MOSFETs. A very high mobility close to 80 cm²/Vs was attained for 4H-SiC(11 $\overline{2}$ 0) MOSFETs by  $N_2O$  oxidation. This mobility improvement can be correlated to the reduction of interface state density near the conduction band edge. The detailed investigation on the MOS interface properties and analysis on the interface structure will be described in a subsequent publication.

#### III. STRUCTURE OPTIMIZATION OF SIC RESURF MOSFETS

Fig. 1 illustrates a schematic structure of SiC RESURF MOSFET simulated and fabricated in this paper. Since it is not easy to satisfy both high avalanching voltage in SiC and low electric field strength in the gate oxide with a simple RESURF structure [17], the lightly doped drain (LDD) region is introduced near the n<sup>+</sup> drain. This is basically the same structure as "two-zone" RESURF reported by Banerjee *et al.* [18].

In this paper, both RESURF and LDD regions are  $10~\mu m$  long and  $0.6~\mu m$  deep. The p-type epilayers are  $10~\mu m$  thick, doped to  $1\times10^{16}~cm^{-3}$ . The thickness of the gate oxide was 100~nm. The channel length was fixed at  $3~\mu m$ . The doping concentration (dose) of the RESURF and LDD regions were optimized by using device simulation (ISE-TCAD) to reduce the electric field crowding at the drain edge and in the gate oxide. In the simulation, material properties such as mobility and breakdown field were assumed as those of 4H-SiC(0001), and anisotropy was neglected. Since the properties of SiC depend on polytype as well as crystal orientation, the optimum dose for 4H-SiC(11 $\overline{2}0$ ) and 6H-SiC(0001) may be different.

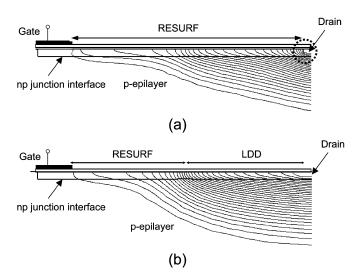

Fig. 2 shows the equipotential lines for RESURF MOSFETs (a) without LDD (single RESURF zone) and (b) with properly designed LDD (two RESURF zones) at a high drain voltage of 600 V. The RESURF dose is  $3.6 \times 10^{12}$  cm<sup>-2</sup> in this particular case. For the MOSFET without LDD, severe electric field crowding takes place at the drain edge as indicated by a dotted circle in Fig. 2(a). By introducing LDD with a  $7.8 \times 10^{12}$  cm<sup>-2</sup> dose, the equipotential lines are more uniformly distributed in

Fig. 2. Equipotential lines for RESURF MOSFETs (a) without LDD (single RESURF zone) and (b) with properly designed LDD (two RESURF zones) at a high drain voltage of 600 V. The RESURF dose is  $3.6 \times 10^{12}$  cm $^{-2}$  in this particular case. The LDD dose shown in (b) is  $7.8 \times 10^{12}$  cm $^{-2}$ . The step for equipotential lines is 20 V.

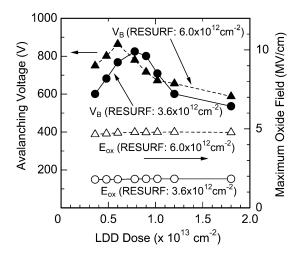

Fig. 3. LDD dose dependencies of avalanching voltage and maximum oxide field at the gate edge (point A in Fig. 1).

both RESURF and LDD regions as shown in Fig. 2(b). The breakdown voltage simulated for MOSFETs with LDD was typically 50–80% higher than that for MOSFETs without LDD.

Fig. 3 depicts the LDD dose dependencies of the avalanching voltage (inside SiC) and the maximum oxide field at the gate edge (point A in Fig. 1) for MOSFETs with a fixed RESURF dose of  $3.6 \times 10^{12}~\rm cm^{-2}$  or  $6.0 \times 10^{12}~\rm cm^{-2}$ . The avalanching voltage was defined when the impact ionization integral along an electric-force line reaches unity [19]. When the LDD dose is varied, the avalanching voltage exhibits a peak while the oxide field is almost constant. The maximum oxide field only depends on the RESURF dose (a higher RESURF dose leads to an increased oxide field). Thus, the optimum LDD dose can be easily determined for a given RESURF dose, typically in the range from  $5 \times 10^{12}~\rm cm^{-2}$  to  $9 \times 10^{12}~\rm cm^{-2}$ . Electric field crowding occurs at the drain edge when the LDD dose is too low, and does at the RESURF/LDD interface when the LDD dose is too high.

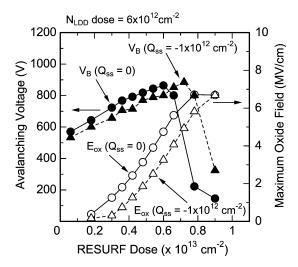

The RESURF dose dependencies of the avalanching voltage and the oxide field are plotted in Fig. 4, where the influences of

Fig. 4. RESURF dose dependencies of avalanching voltage and maximum oxide field. The influences of MOS-interface charge  $(Q_{\rm ss})$  is also presented.

MOS-interface charge  $(Q_{ss})$  is also presented. Negative charge was assumed because of electron trapping at the interface. In this simulation, the LDD dose was fixed at  $6 \times 10^{12}$  cm<sup>-2</sup>. To keep the oxide field below 3 MV/cm for long-term reliability, the RESURF dose should not exceed  $5 \times 10^{12}$  cm<sup>-2</sup> in the case of an ideal MOS interface  $(Q_{ss} = 0)$ . The optimum RESURF dose shifts toward a higher value with increasing the interface charge, because the negative interface charge enhances the depletion of the RESURF region. In fact, a negative interface charge of  $1 \times 10^{12}$  cm<sup>-2</sup> actually causes the shift of both plots toward the high RESURF dose side by  $1 \times 10^{12}$  cm<sup>-2</sup>. When the RESURF dose is low, the electric field strength shows a sharp peak at the RESURF/LDD interface in an electric field analysis. On the other hand, if the RESURF dose is increased too much, the RESURF region fails to be depleted, leading to an abrupt drop of avalanching voltage. The oxide field increases with the RESURF dose, because the voltage drop inside the RESURF region is reduced and the potential at the gate edge of RESURF region is increased for a high RESURF dose.

### IV. FABRICATION OF RESURF MOSFETS

RESURF MOSFETs were fabricated on 10  $\mu$ m-thick p-type 4H-SiC(0001),  $(11\overline{2}0)$ , and 6H-SiC(0001) epilayers doped to  $1.2 \times 10^{16} \text{ cm}^{-3}$  [15], [16]. The RESURF and LDD regions were formed by N<sup>+</sup> implantation with a dose of  $4.0 \times 10^{12}$  and  $8.7 \times 10^{12}$  cm<sup>-2</sup>, respectively. High-dose P<sup>+</sup> implantation at 300 °C was employed to form the source/drain regions. Post-implantation annealing was performed at 1600 °C in Ar for 20 min. About 2-μm-thick SiO<sub>2</sub> films deposited by plasma chemical vapor deposition (CVD) were used as an implantation mask. In order to reduce the channel resistance, the gate oxides for 6H-SiC(0001) MOSFETs were formed by dry O<sub>2</sub> oxidation at 1250 °C, and the oxides for 4H-SiC(0001) and (11 $\overline{2}$ 0) MOS-FETs by N<sub>2</sub>O oxidation at 1300 °C, as described in Section III. The typical channel length and width were 3  $\mu$ m and 200  $\mu$ m, respectively. Al was used as gate and ohmic contacts. Ohmic characteristics can be obtained with Al metal when it is deposited on highly-doped n<sup>+</sup>-SiC.

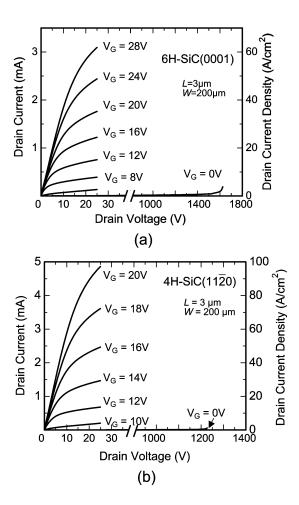

Fig. 5. Output characteristics of (a) 6H-SiC (0001) and (b) 4H-SiC(11 $\bar{2}0)$  RESURF MOSFETs fabricated in this paper.

Fig. 5 represents the output characteristics of (a) 6H-SiC(0001) and (b)  $4H-SiC(11\overline{2}0)$  RESURF MOSFETs fabricated in this paper, where normal on-state operation and high-voltage blocking performance are observed. The threshold voltage was 1.0 V for 6H-SiC(0001) and 6.1 V for 4H-SiC( $11\overline{2}0$ ) RESURF MOSFET, respectively. The 6H-SiC MOSFET exhibited a high breakdown voltage of 1620 V, while the breakdown voltage for 4H-SiC(0001) and  $(11\bar{2}0)$ MOSFETs were 1020 (not shown) and 1230 V, respectively. The higher breakdown voltage for the 6H-SiC device may be partly attributed to the higher breakdown field along the  $\langle 0001 \rangle$ direction of 6H polytype [20]. However, it is also known that the negative charge at the MOS interface of 6H-SiC is lower than that of 4H-SiC. As indicated in Figs. 3 and 4, the interface charge significantly influences the optimum RESURF/LDD doses and thereby the breakdown voltage of MOSFET. To clarify this effect, both 4H- and 6H-SiC RESURF MOS-FETs fabricated with various RESURF/LDD doses should be compared. The absolute values of breakdown voltage experimentally obtained were higher than simulated values by 20% in the case of 4H-SiC devices. The reason for this difference might be ascribed to the reduced electric field crowding due to differences in experimental and simulated doping profiles caused by channeling effects in ion implantation and/or lateral diffusion of impurities during annealing. Since the breakdown

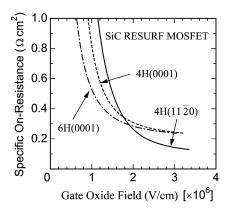

Fig. 6. Specific on-resistances for various SiC RESURF MOSFETs as a function of electric field in gate oxide.

was reversible for all the devices fabricated, the breakdown seems to be limited not by oxide failure but by avalanche inside SiC, probably near the drain edge.

Fig. 6 shows the specific on-resistances for various SiC RESURF MOSFETs as a function of electric field in the gate oxide. Here, the electric field in the oxide was defined simply as the gate voltage divided by the oxide thickness  $(V_q/d_{\rm ox})$ , because this field is reached in the oxide above the gate-source overlapping region. The on-resistance at an oxide field of 3.0 MV/cm was 234 m $\Omega \cdot \text{cm}^2$  for 6H-SiC(0001), 241 m $\Omega \cdot \text{cm}^2$  for 4H-SiC(0001), and 138 m $\Omega \cdot \text{cm}^2$  for 4H-SiC(1120) RESURF MOSFETs. These characteristics are one of the best performances reported for lateral SiC MOSFETs [21]–[23]. Furthermore, the on-resistances for 6H-SiC(0001) and 4H-SiC( $11\bar{2}0$ ) MOSFETs are lower than the classical "Si limit." However, the on-resistances are far from the level expected from the material potential. A rough estimation of the resistance components by using test elements indicates that the channel resistance governs about 40%, 65%, and 45% of total resistances for 6H-SiC(0001), 4H-SiC(0001), and 4H-SiC( $11\bar{2}0$ ) MOSFETs, respectively. It also turns out that the contact resistance cannot be neglected in these devices: Contribution to the total on-resistance is about 10%-20%. Further improvements of the MOS interface and/or shortening the channel length will lead to a decreased on-resistance.

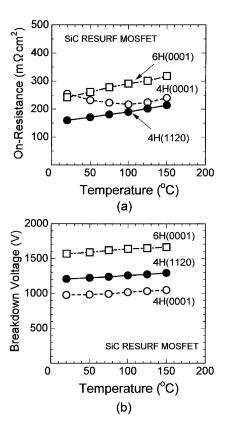

Fig. 7 shows the temperature dependence of the specific on-resistance for 4H-SiC(0001), 4H-SiC( $11\overline{2}0$ ), and 6H-SiC(0001) RESURF MOSFETs fabricated in this paper. The on-resistance is taken at an oxide field of 3.0 MV/cm. The on-resistances for 4H-SiC( $11\overline{2}0$ ) and 6H-SiC(0001) RESURF MOSFETs increase at elevated temperature, because both channel and bulk resistances increase due to enhanced phonon scattering. However, the on-resistance for the 4H-SiC(0001) MOSFET decreases from room temperature to 100 °C, because the channel resistance, the dominant component, is decreased owing to reduced electron trapping. Above 100 °C, phonon scattering becomes more dominant, and the on-resistance turned to increase with increasing temperature. The breakdown voltage exhibited a positive temperature coefficient for all of the measured MOSFETs. For example, the breakdown voltage increased from 1620 V at 20 °C to 1740 V at 150 °C, indicating that the breakdown is governed by an avalanche phenomenon

Fig. 7. Temperature dependence of (a) specific on-resistance and (b) breakdown voltage for 4H-SiC(0001), 4H-SiC( $11\bar{2}0$ ), and 6H-SiC(0001) RESURF MOSFETs fabricated in this paper. The on-resistance is taken at an oxide field of 3.0 MV/cm.

in SiC, and not by oxide breakdown. The breakdown voltages of 4H-SiC MOSFETs at 150 °C were also about 6–9% higher than those at room temperature. Although this phenomenon can be interpreted by avalanche breakdown, the reduced negative charge at the MOS interface at elevated temperature might cause the change of electric field distribution, and may also contribute to the increased breakdown voltage.

#### V. CONCLUSION

Structure optimization and fabrication of RESURF MOS-FETs on 4H-SiC(0001), 4H-SiC( $11\bar{2}0$ ), and 6H-SiC(0001) have been investigated. By utilizing N<sub>2</sub>O oxidation at 1300 °C, the effective channel mobility was improved to 22 and 78 cm<sup>2</sup>/Vs for 4H-SiC(0001) and (11 $\overline{2}$ 0), respectively. Dry O<sub>2</sub> oxidation at 1250 °C resulted in an effective channel mobility of 68 cm<sup>2</sup>/Vs for 6H-SiC. The optimum doping concentrations (doses) of the RESURF and LDD regions to reduce the electric field crowding at the drain edge or in the gate oxide were estimated by using device simulation. RESURF MOS-FETs were fabricated on 10  $\mu$ m-thick p-type 4H-SiC(0001),  $(11\overline{2}0)$ , and 6H-SiC(0001) epilayers doped to  $1 \times 10^{16}$  cm<sup>-3</sup>. A 6H-SiC(0001) RESURF MOSFET with a 3- $\mu$ m channel length exhibited a high breakdown voltage of 1620 V and an on-resistance of 234 m $\Omega \cdot \text{cm}^2$ . A 4H-SiC(11 $\bar{2}0$ ) RESURF MOSFET showed the characteristics of 1230 V-138 m $\Omega \cdot \text{cm}^2$ , which is better than that of 4H-SiC(0001) MOSFET, owing to the higher channel mobility in the 4H-SiC( $11\bar{2}0$ ) device.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. T. Fuyuki and Dr. T. Hatayama at NAIST for the use of the plasma CVD equipment.

#### REFERENCES

- [1] M. Bhatnager and B. J. Baliga, "Comparison of 6H-SiC, 3C-SiC, and Si for power devices," *IEEE Trans. Electron Devices*, vol. 40, no. 4, pp. 645–655, Apr. 1993.

- [2] R. Rupp and I. Zverev, "System design considerations for optimizing the benefit by unipolar SiC power devices," in *Proc. Mater. Res. Soc. Symp.*, vol. 742, 2003, pp. 329–340.

- [3] S. Onda, R. Kumar, and K. Hara, "SiC integrated MOSFETs," *Phys. Stat. Sol.* (a), vol. 162, pp. 369–388, 1997.

- [4] J. Tan, J. A. Cooper Jr., and M. R. Melloch, "High-voltage accumulationlayer UMOSFETs in 4H-SiC," *IEEE Electron Device Lett.*, vol. 19, no. 6, pp. 487–489, Jun. 1998.

- [5] D. Peters, R. Schörner, P. Friedrichs, J. Volkel, H. Mitlehner, and D. Stephani, "An 1800 V triple implanted vertical 6H-SiC MOSFET," *IEEE Trans. Electron Devices*, vol. 46, no. 5, pp. 542–545, May 1999.

- [6] Y. Sugawara, K. Asano, D. Takayama, S. Ryu, R. Singh, J. W. Palmour, and T. Hayashi, "5.0 kV 4H-SiC SEMOSFET with low  $R_{\rm on}S$  of 88 m $\Omega \cdot {\rm cm^2}$ ," *Mater. Sci. Forum*, vol. 389–393, pp. 1199–1202, 2002.

- [7] S. Harada, M. Okamoto, T. Yatsuo, K. Adachi, K. Fukuda, and K. Arai, "An ultra-low Ron in 4H-SiC vertical MOSFET: Buried channel doubleepitaxial MOSFET," in *Proc. Int. Symp. Power Semiconductor Devices* ICs, Kitakyusyu, Japan, 2004, pp. 313–316.

- [8] J. Spitz, M. R. Melloch, J. A. Cooper Jr., and M. A. Capano, "2.6 kV 4H-SiC lateral DMOSFETs," *IEEE Electron Device Lett.*, vol. 19, no. 2, pp. 100–102, Feb. 1998.

- [9] N. S. Saks, S. S. Mani, A. K. Agarwal, and M. G. Ancona, "A 475-V high-voltage 6H-SiC lateral MOSFET," *IEEE Electron Device Lett.*, vol. 20, no. 5, pp. 431–433, May 1999.

- [10] S. Banerjee, K. Chatty, T. P. Chow, and R. J. Gutmann, "Improved high-voltage lateral RESURF MOSFETs in 4H-SiC," *IEEE Electron Device Lett.*, vol. 22, no. 4, pp. 209–211, Apr. 2001.

- [11] E. Okuno and S. Amano, "Reduction of interface trap density in 4H-SiC MOS by high-temperature oxidation," *Mater. Sci. Forum*, vol. 389–393, pp. 989–992, 2002.

- [12] S. Dimitrijev, H. B. Harrison, P. Tanner, K. Y. Cheong, and J. Han, "Properties of nitrided oxides on SiC," in *Silicon Carbide: Recent Major Advances*, W. J. Choyke, H. Matsunami, and G. Pensl, Eds. Berlin, Germany: Springer–Verlag, 2003, pp. 373–386.

- [13] L. A. Lipkin, M. K. Das, and J. W. Palmour, "N<sub>2</sub>O processing improves the 4H-SiC:SiO<sub>2</sub> interface," *Mater. Sci. Forum*, vol. 389–393, pp. 985–988, 2002.

- [14] H. Yano, T. Hirao, T. Kimoto, H. Matsunami, K. Asano, and Y. Sug-awara, "High channel mobility in inversion layers of 4H-SiC MOSFETs by utilizing (1120) face," *IEEE Electron Device Lett.*, vol. 20, no. 10, pp. 611–613, Oct. 1999.

- [15] H. Matsunami and T. Kimoto, "Step-controlled epitaxial growth of SiC: high quality homoepitaxy," *Mater. Sci. Eng.*, vol. R20, pp. 125–166, 1997.

- [16] T. Kimoto, T. Yamamoto, Z. Y. Chen, H. Yano, and H. Matsunami, "4H-SiC(1120) epitaxial growth," *Mater. Sci. Forum*, vol. 338–342, pp. 189–192, 2000.

- [17] H. Kosugi, T. Hirao, H. Yano, J. Suda, T. Kimoto, and H. Matsunami, "Design and fabrication of SiC RESURF MOSFETs," in *Proc. Asia-Pacific Workshop Fundamental Applications Advanced Semiconductor Devices*, Sapporo, Japan, 2001, pp. 61–66.

- [18] S. Banerjee, T. P. Chow, and R. J. Gutmann, "Robust, 1000 V, 130  $\,\mathrm{m}\Omega\cdot\mathrm{cm}^2$ , lateral two-zone RESURF MOSFETs in 6H-SiC," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, Santa Fe, NM, 2002, pp. 69–72.

- [19] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York: Wiley, 1985, ch. 2.

- [20] J. W. Palmour, C. H. Carter Jr, C. E. Weitzel, and K. J. Nordquist, "High power and high frequency silicon carbide devices," in *Proc. Mater. Res. Soc. Symp.*, vol. 339, 1994, pp. 133–144.

- [21] S. Banerjee, T. P. Chow, and R. J. Gutmann, "Comparison of 1 kV lateral RESURF MOSFETs in 4H-SiC and 6H-SiC," *Mater. Sci. Forum*, vol. 433–436, pp. 757–760, 2003.

- [22] S. Suzuki, S. Harada, T. Yatsuo, R. Kosugi, J. Senzaki, and K. Fukuda, "4H-SiC lateral RESURF MOSFET with a buried channel structure," *Mater. Sci. Forum*, vol. 433–436, pp. 753–756, 2003.

- [23] W. Wang, S. Banerjee, T. P. Chow, and R. J. Gutmann, "930-V 170-mΩ·cm² lateral two-zone RESURF MOSFETs in 4H-SiC with NO annealing," *IEEE Electron Device Lett.*, vol. 25, no. 2, pp. 185–187, Feb. 2004.

**Tsunenobu Kimoto** (M'02) received the B.E, M.E., and Ph.D. degrees from Kyoto University, Kyoto, Japan, in 1986, 1988, and 1996, respectively. His Ph.D. work involved SiC epitaxial growth, material characterization, and device fabrication such as high-voltage diodes.

In April 1988, he joined Sumitomo Electric Industries, Ltd., Hyogo, Japan, where he conducted research on amorphous Si solar cells and semiconducting diamond materials for high-temperature devices. In 1990, he started SiC research work as a

Research Associate with Kyoto University. From September 1996 to August 1997, he was a Visiting Scientist at Linköping University, Sweden, where he was involved in fast epitaxy of SiC and high-voltage Schottky diodes. He is currently an Associate Professor in the Department of Electronic Science and Engineering, Kyoto University. His main research activity includes SiC epitaxial growth, optical and electrical characterization, ion implantation, MOS physics, and high-voltage devices. He has published over 180 papers in scientific journals and international conference proceedings.

**Hajime Kosugi** received the B.E. and M.E. degrees in electrical and electronic engineering, from Kyoto University, Kyoto, Japan, in 2001 and 2003, respectively. His research focused on SiC oxidation process as well as fabrication of SiC RESURF MOSFETs.

**Jun Suda** was born in 1969 in Ashikaga, Japan. He received the B.E., M.E. and Ph. D. degrees from Kyoto University, Kyoto, Japan.

From 1992 to 1997, he worked on the growth of ZnSe-based semiconductors by molecular-beam epitaxy and the characterization of ZnMgSSe strained quantum well structures for optoelectronic applications. In 1997, he began research on group-III nitride semiconductors (III-N) and SiC as a Research Associate at Kyoto University. He is currently a Lecturer in the Department of Electronics Science and Engi-

neering. His research interests include heteroepitaxial growth of III-N, functional integration of III-N and SiC materials by precise control of the heterointerface, design of wide bandgap semiconductor devices, and characterization of device structures by scanning-probe microscopy. He has authored or coauthored over 35 publications in peer-reviewed journals and international conferences and is the inventor of six pending patents.

Dr. Suda is a member of The Materials Research Society, the Japan Society of Applied Physics and the Japanese Association for Crystal Growth.

**Yosuke Kanzaki** was born in Osaka, Japan, on April 4, 1979. He received the B.E. and M.E. degrees in electrical and electronic engineering from Kyoto University, Kyoto, Japan, in 2002 and 2004, respectively. He was involved in the fabrication of SiC MOSFETs during his graduate studies.

**Hiroyuki Matsunami** (M'84–SM'00–F'03) received the B.E., M.E., and Ph.D. degrees, all from Kyoto University, Kyoto, Japan, in 1962, 1964, and 1970.

He was a Research Associate, Associate Professor, and Professor at Kyoto University. Since April 2003, he has been a Professor Emeritus, and is currently Director of Innovation Plaza Kyoto, Japan Science and Technology Agency. He was a Visiting Associate Professor at North Carolina State University, Raleigh, from 1976 to 1977. His professional work

is on semiconductor science and engineering. He has also been working on semiconductor material synthesis, characterization, and device demonstration. He began his work on semiconductor SiC in 1968. He has worked in SiC blue light—emitting diodes, heteroepitaxial growth of SiC on Si, and step-controlled epitaxial growth of SiC on SiC substrates. He has contributed greatly to the progress in SiC devices by bringing high-quality epitaxial layers grown by the concept of step-controlled epitaxy, such as high-performance Schottky diodes and high-channel electron mobility in SiC MOSFETs. He has published more than 200 papers in scientific journals and more than 200 papers in international conference proceedings. He is one of the three editors of Silicon Carbide I, II (Akademie Verlag: Berlin, Germany, 1997), and Silicon Carbide—Recent Major Advances (Springer Verlag: Berlin, Germany, 2003). He is on the Editorial Board of Solar Energy Materials and Solar Cells.

Dr. Matsunami is a Fellow of The Institute of Electronics, Information, and Communication Engineers, and a member of The Institute of Electrical Engineers of Japan, The Japan Society of Applied Physics, and the Japanese Association of Crystal Growth. He was awarded the "Outstanding Research Award" from the Ministry of Education, Japan Society of Applied Physics, and The Institute of Electronics, Information, and Communication.