FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Active Inductor Techniques for BW Extension

João Pedro Bastos Santos

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor: Dr. Vítor Tavares External Supervisor: Eng. Bruno Silva

July 30, 2020

© João Pedro Bastos Santos, 2020

# Abstract

Advances in integrated circuit technology have been reducing costs and increasing the functionality of consumer electronics. Today's nano-meter technologies benefit from higher integration allowing for increased complexity but also higher speeds. The demand for higher speeds at lower area and cost pushes the design of integrated systems toward more self-contained circuits without the use of integrated passive components mainly due to the large area required.

There are many circuits that may require the implementation of inductors to improve their performance and thus meet the needs of today's communication systems. These inductors are increasingly being implemented active, due to the effectiveness of the integration of active inductors compared to a passive implementation.

This dissertation aims to take advantage of CMOS technology and its reduced cost to research and design active inductors and its integration in circuits. The final designed active inductor is intended to be integrated into an output driver with the ultimate goal of extending the bandwidth and consequently improve the driver's speed.

A study of different topologies is performed with the respective evaluation of their pros and cons and those configurations that demonstrate a greater potential are implemented. Taking into account the analyses carried out and the respective performance parameters, a circuit architecture is developed resulting in a novel active inductor topology. The proposed solution is evaluated and compared with other approaches, proving to be the most effective solution to fulfill the ultimate goal of extending bandwidth, thus increasing the speed of the driver.

This work is carried out in an enterprise team environment, more specifically at Synopsys - Portugal.

ii

## Resumo

O avanço tecnológico na área dos circuitos integrados tem vindo a reduzir custos e a aumentar funcionalidades da eletrónica de consumo. As tecnologias atuais, na ordem dos nanómetros, beneficiam da alta integração, na medida em que, não só suportam maior complexidade, como tambem permitem circuitos mais rápidos. A procura por maior velocidade em sistemas de baixo custo e área reduzida motiva o interesse da adoção de circuitos mais independentes, sem o uso de componentes passivos, principalmente devido à elevada área que é exigida.

Existem diversos circuitos que poderão exigir a implementação de indutores de forma a melhorarem o seu desempenho e, assim, atenderem às necessidades dos sistemas de comunicação atuais. Esses indutores estão a ser, cada vez mais, implementados de forma ativa, uma vez que, revelam ser mais eficientes principalmente em área relativamente às implementações passivas.

A presente dissertação visa ter em consideração a tecnologia CMOS e o seu custo reduzido, de forma a pesquisar e projetar indutores ativos e as respetivas implementações em circuitos integrados. O indutor ativo final tem como finalidade ser integrado num driver de saída, com o objetivo final de extensão de largura de banda e, consequentemente, melhorar a respetiva velocidade do driver.

Um estudo das diferentes topologias é efetuado, juntamente com a respetiva avaliação dos prós e contras, sendo que, as configurações que demonstram maior potencial, são posteriormente implementadas. Tendo em conta as análises realizadas assim como os respetivos parâmetros de desempenho, é desenvolvida uma configuração que resulta numa nova topologia de indutor ativo. A solução proposta é avaliada e comparada com outras abordagens, revelando ser a mais eficaz em cumprir o principal objetivo de aumentar a largura de banda, e consequentemente, melhorar a velocidade do driver.

Este trabalho é realizado em ambiente empresarial, na Synopsys - Portugal.

iv

# Acknowledgments

I would like to take this opportunity to express my sincere gratitude to my parents and my brother for all the support during this long journey. My parents always made a great effort to afford my education and from an early age, they taught me the concept of working hard to achieve my goals. For all that, I am very grateful.

I would like to thank Bruno Silva for teaching me things that you don't learn in college and for always finding time to help me, even in chaotic times. His ideas and suggestions were crucial to the success of this work.

I would also like to thank Professor Dr. Vítor Grade Tavares for the support provided during the development of this thesis and for all the essential advice to solve countless problems encountered along the way.

In addition, I would like to express my gratitude to all the members of the Analog Team at Synopsys, which have received me and shared valuable knowledge during this my last academic year.

Finally, I especially thank Sofia for the emotional support and for being always on my side.

João Pedro Santos

vi

"O que dá o verdadeiro sentido ao encontro é a busca, e é preciso andar muito para se alcançar o que está perto"

José Saramago

viii

# Contents

| 1 | Intro | oduction      |                                          |   | 1 |

|---|-------|---------------|------------------------------------------|---|---|

|   | 1.1   | Context       |                                          |   | 1 |

|   | 1.2   | Problem and   | Motivation                               |   | 2 |

|   | 1.3   | Objectives .  |                                          |   | 2 |

|   | 1.4   | Document Str  | ructure                                  |   | 3 |

| 2 | Back  | kground       |                                          |   | 5 |

|   | 2.1   | Introduction  |                                          |   | 5 |

|   | 2.2   | Methods for b | bandwidth enhancement                    |   | 5 |

|   |       | 2.2.1 Capac   | citive compensation technique            |   | 5 |

|   |       | 2.2.2 Distri  | ibuted amplification                     |   | 6 |

|   |       | 2.2.3 Shunt   | t peaking                                |   | 7 |

|   | 2.3   |               | on of on-chip inductors                  |   | 9 |

|   |       | 2.3.1 Passiv  | ve inductor                              | 1 | 0 |

|   |       |               | e inductor                               |   | 0 |

|   | 2.4   |               | analysis of active and passive inductors |   | 1 |

|   |       |               | ity Factor                               |   | 2 |

|   |       | -             | on Area Consumption                      |   | 4 |

|   |       |               | Resonant Frequency                       |   | 4 |

|   |       |               | r Consumption                            |   | 5 |

|   |       |               | arity                                    |   | 6 |

|   |       |               | 2                                        |   | 6 |

|   |       |               | tance Tunability                         |   | 7 |

|   | 2.5   |               | g active inductor implementations        |   | 8 |

|   |       |               | le Active inductor                       |   | 8 |

|   |       | -             | ed Active Inductor                       |   | 9 |

|   |       |               | Active Inductor                          |   | 0 |

|   | 2.6   |               |                                          |   |   |

| 3 | Shu   | nt peaking im | plementation                             | 2 | 3 |

|   | 3.1   |               | e Inductor                               |   |   |

|   |       |               | l signal analysis                        |   |   |

|   |       |               | t vs Series peaking                      |   |   |

|   | 3.2   |               |                                          |   |   |

|   | 2.2   |               | l signal analysis                        |   |   |

|   |       |               |                                          |   |   |

|   |       | 322 Activ     | e inductor integration                   | 2 | 9 |

|   |       |               | re inductor integration                  |   |   |

## CONTENTS

|    |                               | 3.2.5 Biasing adjustments                                                                                       | <u> 39</u> |  |  |  |

|----|-------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|--|--|--|

|    |                               | 3.2.6 Bandwidth enhancement                                                                                     | 13         |  |  |  |

|    | 3.3                           | Summary                                                                                                         | 17         |  |  |  |

| 4  | Sim                           | le AI 5                                                                                                         | 51         |  |  |  |

|    | 4.1                           | Topology Conception                                                                                             | 51         |  |  |  |

|    | 4.2                           | Biasing Adjustments                                                                                             | 52         |  |  |  |

|    | 4.3                           | AC analysis                                                                                                     | 53         |  |  |  |

|    | 4.4                           | Small Signal Analysis                                                                                           | 57         |  |  |  |

|    |                               | 4.4.1 Transfer function & Resonant frequency                                                                    | 57         |  |  |  |

|    |                               | 4.4.2 Equivalent <i>RLC</i> model                                                                               | 58         |  |  |  |

|    |                               |                                                                                                                 | 59         |  |  |  |

|    | 4.5                           |                                                                                                                 | 52         |  |  |  |

|    |                               | 4.5.1 First transient simulation                                                                                | 52         |  |  |  |

|    |                               | 4.5.2 Improvement approaches                                                                                    | 53         |  |  |  |

|    |                               | 4.5.3 Output voltage range analysis                                                                             | 54         |  |  |  |

|    |                               |                                                                                                                 | 54         |  |  |  |

|    | 4.6                           |                                                                                                                 | 58         |  |  |  |

| 5  | Conclusions and Future Work 6 |                                                                                                                 |            |  |  |  |

|    | 5.1                           | Summary of the work developed                                                                                   | 59         |  |  |  |

|    | 5.2                           | Concluded Objectives                                                                                            | 71         |  |  |  |

|    | 5.3                           | Future work                                                                                                     | 71         |  |  |  |

| A  | Exp                           | essions Deduction 7                                                                                             | 73         |  |  |  |

|    | A.1                           | Equivalent impedances of the AI solution designed in chapter 3 and of the novel simple AI designed in chapter 4 | 73         |  |  |  |

|    | Δ 2                           |                                                                                                                 | 74         |  |  |  |

|    | A.2<br>A.3                    |                                                                                                                 | 77         |  |  |  |

|    | 11.5                          |                                                                                                                 | '          |  |  |  |

| Re | feren                         | es 7                                                                                                            | 79         |  |  |  |

# **List of Figures**

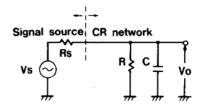

| 2.1  | Simple CR network, reprinted from [1]                                                  | 6  |

|------|----------------------------------------------------------------------------------------|----|

| 2.2  | CR network with capacitance compensation circuit, reprinted from [1]                   | 6  |

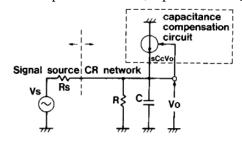

| 2.3  | The distributed amplifier based on lumped-element artificial transmission lines,       |    |

|      | reprinted from [2]                                                                     | 7  |

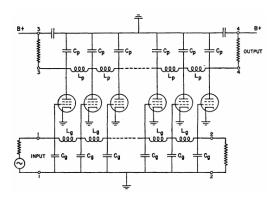

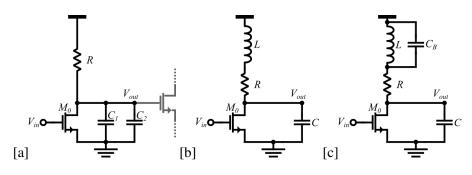

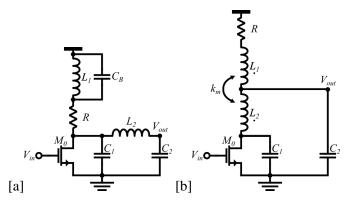

| 2.4  | (a) Simple common source amplifier (b) Common source amplifier with shunt              |    |

|      | peaking (c) Common source amplifier with bridged-shunt peaking                         | 8  |

| 2.5  | (a) Common source amplifier with bridged-shunt-series peaking and drain para-          |    |

|      | sitic capacitance (b) Common source amplifier with asymmetric T-coil peaking           |    |

|      | and drain capacitance                                                                  | 9  |

| 2.6  | Amplifier with T-Coil bandwidth enhancement                                            | 10 |

| 2.7  | Spiral inductor, reprinted from [3]                                                    | 11 |

| 2.8  | (a) Single-ended gyrator-C active inductor (b) Lossy single-ended gyrator-C active     |    |

|      | inductors (reprinted from [4])                                                         | 12 |

| 2.9  | Formation of conductor eddy currents, reprinted from [5]                               | 13 |

| 2.10 | Bode plots of the impedance of lossy single-ended gyrator-C active inductor, reprinted | 1  |

|      | from [4]                                                                               | 15 |

| 2.11 | Transconductance of MOSFETs in the saturation and triode regions, reprinted            |    |

|      | from [4]                                                                               | 17 |

| 2.12 | Inductance as a function of the number of turns for a given line length, reprinted     |    |

|      | from [3]                                                                               | 18 |

| 2.13 | Inductance as a function of the number of metal spiral layers                          | 18 |

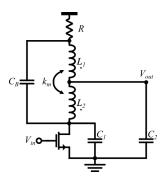

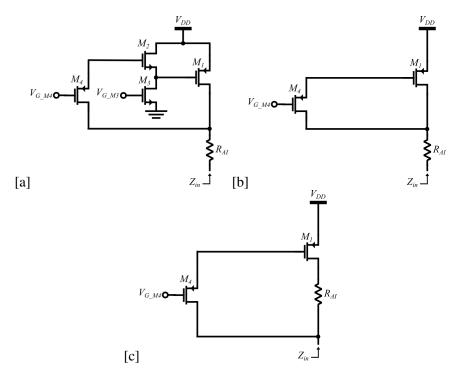

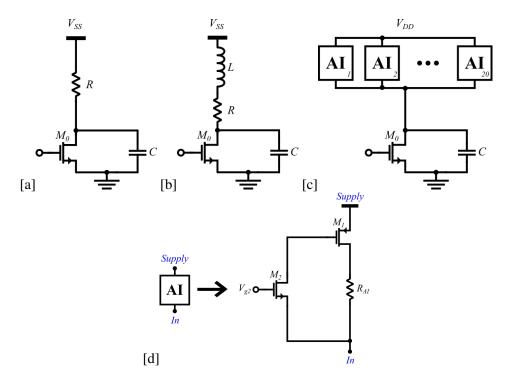

| 2.14 | Common source amplifier with shunt peaking - (a) Using a spiral inductor (b)           |    |

|      | Using a simple active inductor (c) Using an active inductor with voltage boosting      | 19 |

| 2.15 | (a) Folded active inductor NMOS (b) PMOS version: Simple active inductor and           |    |

|      | Folded active inductor (c) Lee's active inductor                                       | 19 |

| 2.16 | Doubly terminated I/O blocks with inductive peaking terminations, reprinted from       |    |

|      | [6]                                                                                    | 20 |

|      |                                                                                        |    |

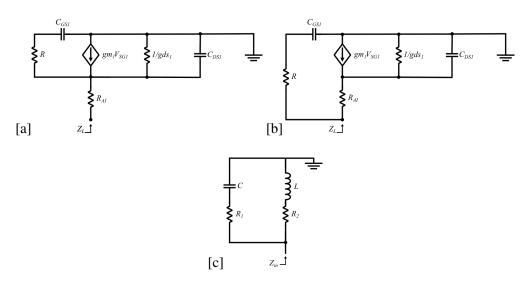

| 3.1  | Folded active inductor - (a) Schematic (b) Small signal model (c) Small signal         |    |

|      | equivalent                                                                             | 24 |

| 3.2  | Application of the folded active inductor                                              | 25 |

| 3.3  | Testing scenarios: (a) Resistance in series with the inductor ( $(R+sL)//(1/sC)$       |    |

|      | ) (b) Resistance in parallel with the inductor $(R / sL / (1/sC))$                     | 25 |

| 3.4  | Simulation results: (a) Resistance in series with the inductor ( $(R+sL)//(1/sC)$      |    |

|      | ) (b) Resistance in parallel with the inductor $(R / sL / (1/sC))$                     | 26 |

| 3.5  | Lee's active inductor                                                                  | 27 |

| 3.6  | Schematic of Lee's active inductor                                                     | 27 |

| 3.7  | Lee's active inductor RLC (a) initial (b) simplified                                   | 29 |

| 3.8  | Application of Lee's active inductor                                                               | 30 |

|------|----------------------------------------------------------------------------------------------------|----|

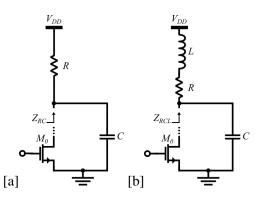

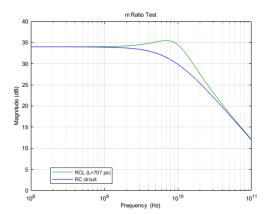

| 3.9  | Small test to prove the ratio value (a) RC circuit (b) RCL ciruit                                  | 30 |

| 3.10 | Result of the small test to prove the ratio value                                                  | 31 |

|      | Adopted procedure to measure the impedance                                                         | 32 |

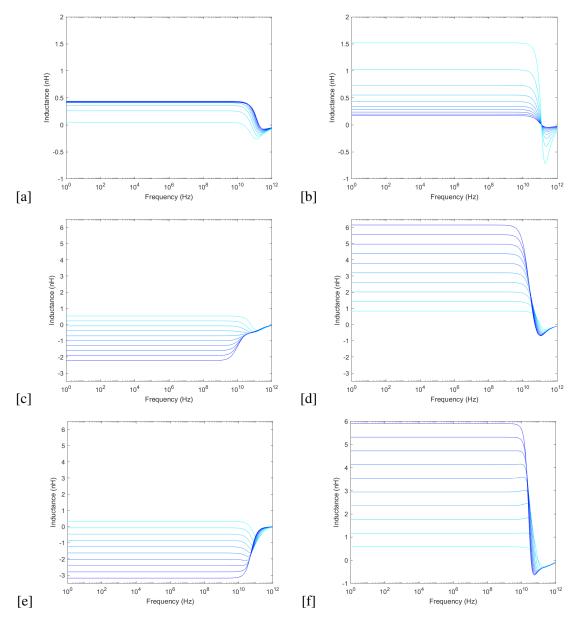

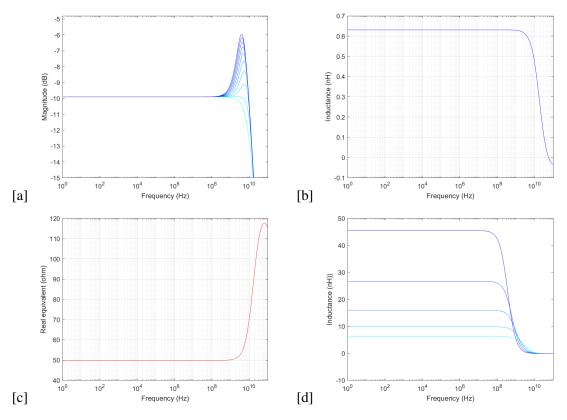

| 3.12 | Parametric analysis - sweep of each parameter at a time, between a minimum value                   |    |

|      | (lighter line) and a maximum value (darker line): (a) $gm$ (b) $gds$ (c) $C_{gd}$ (d) $C_{gs}$ (e) |    |

|      | $C_{ds}$ (f) $R$                                                                                   | 33 |

| 3.13 | Application of Lee's active inductor                                                               | 34 |

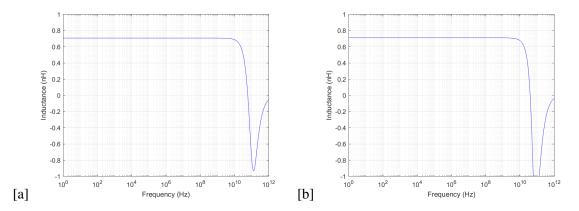

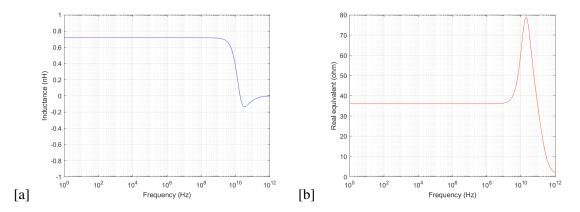

|      | Equivalent inductance: (a) After real model adjustments (b) After replacing $R$ by $M_4$           | 35 |

|      | Parametric analysis of $V_{G_{M4}}$                                                                | 35 |

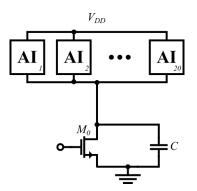

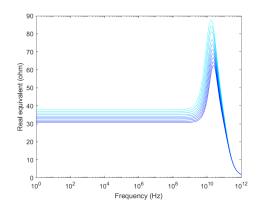

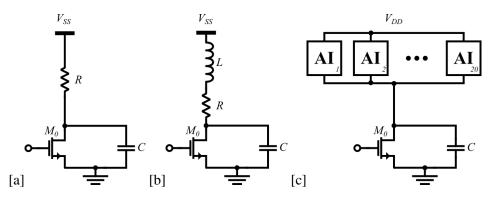

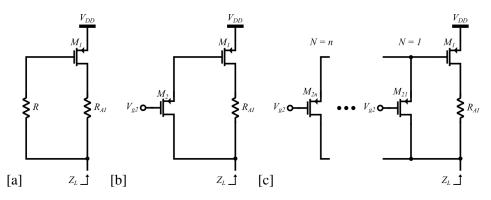

|      | Scenario with N branches, each with an active inductor                                             | 36 |

|      | After branches approach application: (a) Equivalent inductance (b) Real part equiv-                |    |

|      |                                                                                                    | 37 |

| 3.18 | Scenario with N branches, each with a Lee's active inductor in series with a resistor              | 38 |

|      | After resistor application: (a) Equivalent inductance (b) Real part equivalent                     | 39 |

|      | $M_1$ size sweep                                                                                   | 40 |

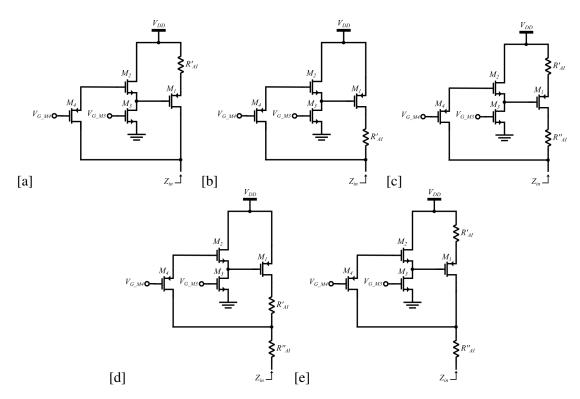

|      | Application of the resistor inside the active lee inductor: (a) Between supply and                 |    |

| 0.21 | source of $M_1$ (b) Between drain of $M_1$ and output node (c) Split the resistor and              |    |

|      | insert it in both places (d) Split the resistor and insert part of it between drain of             |    |

|      | $M_1$ and output node, and other part outside (e) Split the resistor and insert part of            |    |

|      | it between supply and source of $M_1$ , and other part outside $\ldots$ $\ldots$ $\ldots$          | 41 |

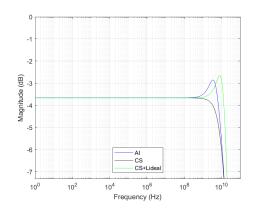

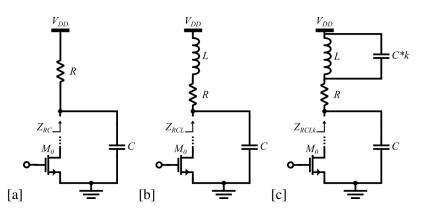

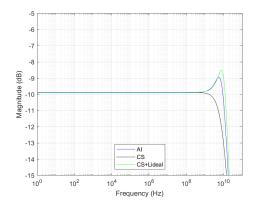

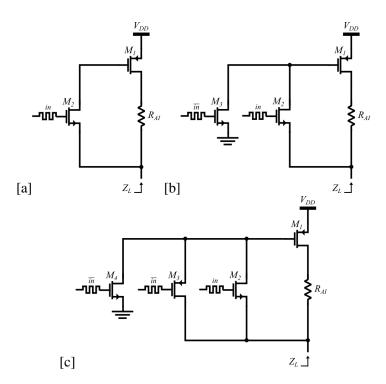

| 3 22 | Common source test scenarios: (a) Simple (b) With ideal inductor (c) With de-                      |    |

| 5.22 | signed active inductor                                                                             | 43 |

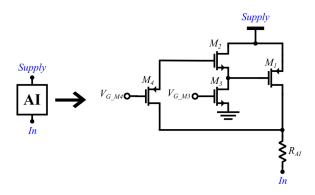

| 3 23 | Proposed AI topology: Lee's active inductor in series with a resistor                              | 43 |

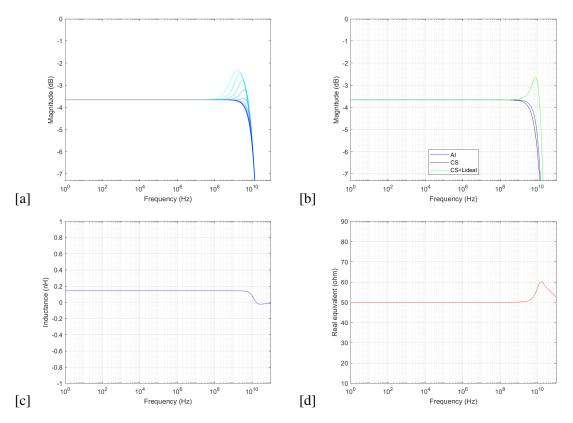

|      | AC analysis of the three cases                                                                     | 44 |

|      | (a) Sweep of the voltage at the gate of $M_4$ , lighter and darker lines correspond to             |    |

| 5.25 | the lower and higher applied voltage value, respectively (b) AC analysis of the tree               |    |

|      | cases after the inductance adjustment of the AI (c) Final equivalent inductance of                 |    |

|      | the AI (d) Final real equivalent of the AI                                                         | 45 |

| 3 26 | Small test to prove the ratio value (a) RC circuit (b) RCL circuit (c) RCL circuit                 | ч3 |

| 5.20 | with inserted parallel capacitor                                                                   | 46 |

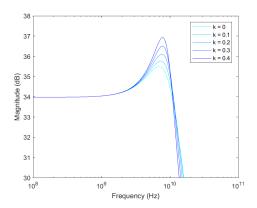

| 2 77 | $Z_{RCLK}$ behavior with k value sweep between 0 and 0.4 with step of 0.1                          | 47 |

| 2.20 | <i>Z<sub>RCLK</sub></i> behavior with <i>k</i> value sweep between 0 and 0.4 with step of 0.1      | 47 |

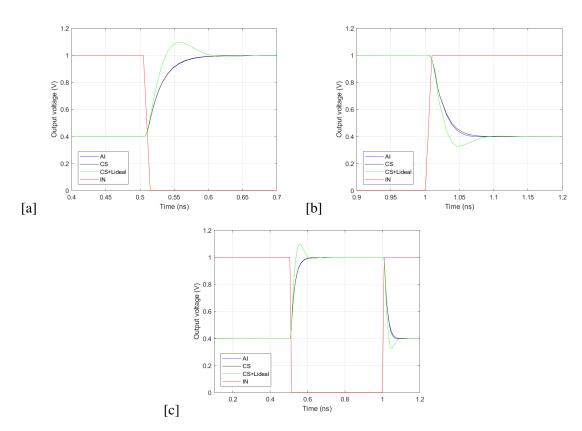

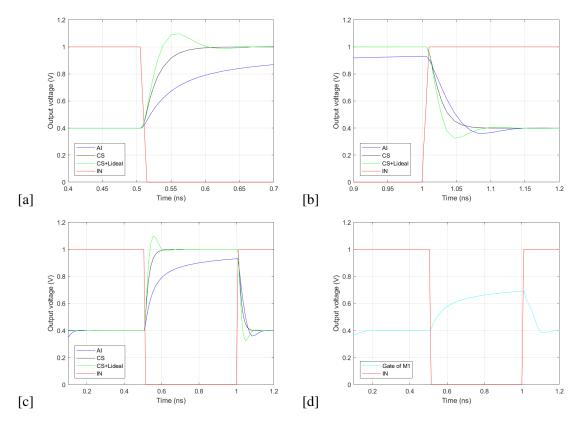

| 5.20 | Transient analysis: (a) Rise (b) Fall (c) Geral                                                    | 40 |

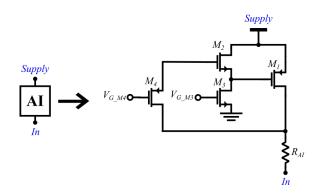

| 4.1  | (a) AI solution designed in the chapter 3 (b) Level shifter removal that results in                |    |

|      | the PMOS version of the simple AI in series with a resistor (c) Novel simple active                |    |

|      | inductor approach                                                                                  | 52 |

| 4.2  | Novel approach of the simple AI concept considering: (a) A resistor $R$ (b) PMOS                   | -  |

|      | $M_2$ (c) <i>n</i> transistors PMOS in parallel                                                    | 53 |

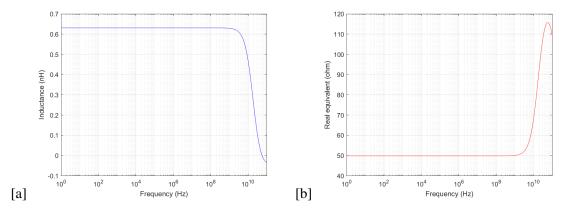

| 4.3  | (a) <i>R</i> sweep between a minimum and a maximum value, lighter and darker lines,                |    |

|      | respectively (b) Equivalent inductance of the simple AI with optimal $R$ value (c)                 |    |

|      | Equivalent real part of the simple AI with optimal <i>R</i> value (d) Sweep of the voltage         |    |

|      | at the gate of PMOS $M_4$ between a minimum (0V) and a maximum value, lighter                      |    |

|      | and darker lines, respectively                                                                     | 54 |

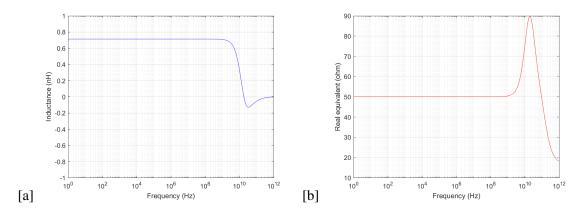

| 4.4  | (a) Final equivalent inductance of the simple AI (b) Final equivalent real part of                 | -  |

|      | the simple AI                                                                                      | 55 |

| 4.5  | Common source test scenarios: (a) Simple (b) With ideal inductor (c) With simple                   | 55 |

|      | AI (d) Each branch of the simple AI                                                                | 56 |

| 4.6  | AC analysis result - Simple AI                                                                     | 56 |

|      |                                                                                                    | 50 |

| 4.7  | Small signal model: (a) AI solution designed in the chapter 3 (b) Simple active                  |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | inductor approach (c) <i>RLC</i> simplified model                                                | 57 |

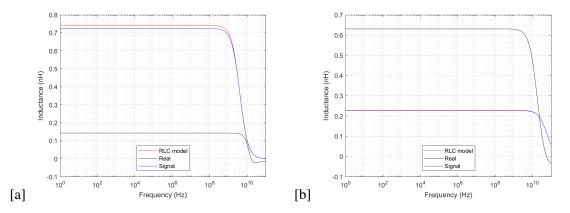

| 4.8  | Simulation to compare: <i>RLC</i> model vs Signal model vs Real model (a) Solution               |    |

|      | proposed in chapter 3 (b) Simple AI                                                              | 59 |

| 4.9  | Small-signal model for simple AI: (a) Considering $C_{gs}$ , $C_{gd}$ and $C_{ds}$ (b) Consider- |    |

|      | ing the total capacitance associated with each node                                              | 60 |

| 4.10 | (a) Simulation of the small-signal models represented in Fig.4.9 (b) Simulation                  |    |

|      | of the second small-signal model, excluding each node total capacitance, at a time               | 60 |

| 4.11 | (a) Chapter 3 solution (b) Simple AI solution                                                    | 61 |

| 4.12 | (a) Small-signal model to chapter 3 AI solution (b) Small-signal model assuming                  |    |

|      | unitary level shifter AC gain (c) Simulations of the mentioned small-signal models               | 62 |

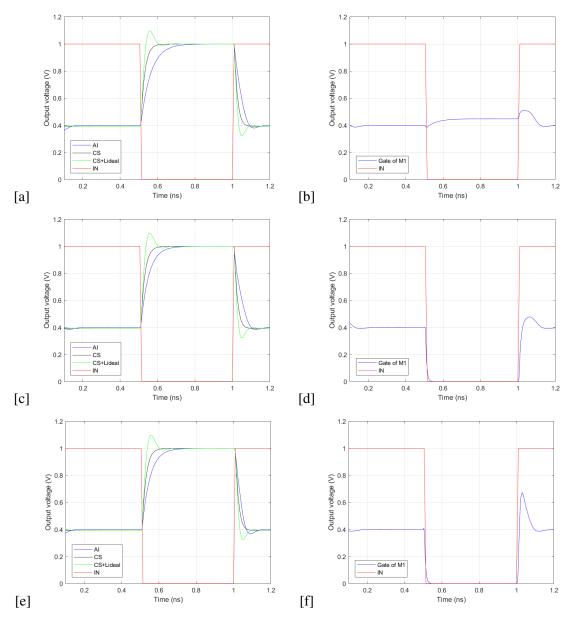

| 4.13 | Simple AI transient analysis: (a) Rise (b) Fall (c) Geral (d) Gate of $M_1$                      | 63 |

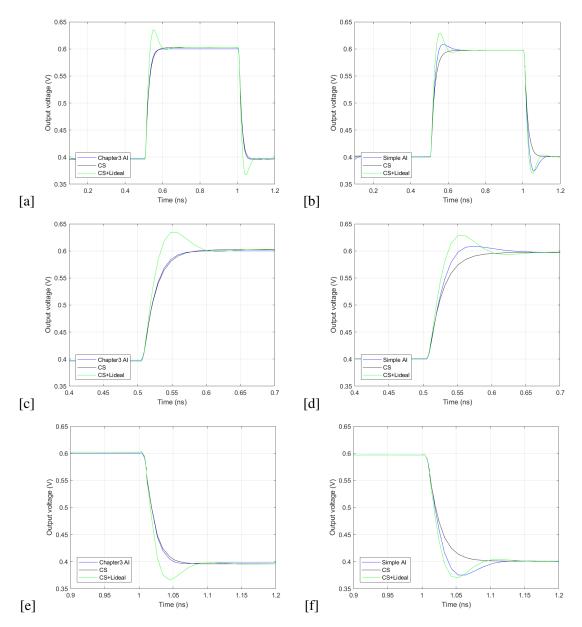

| 4.14 | Simple AI improvement approaches: (a) First (b) Second (c) Third                                 | 64 |

| 4.15 | Simple AI transient analysis geral and gate of $M_1$ , respectively: (a,b) First ap-             |    |

|      | proach (c,d) Second approach (e,f) Third approach                                                | 65 |

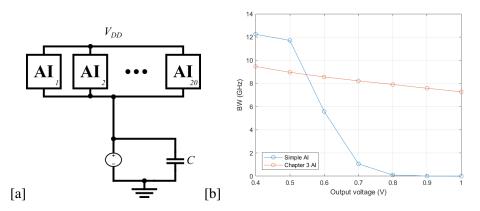

| 4.16 | (a) AC analysis to measure the bandwidth of the equivalent AI impedance consid-                  |    |

|      | ering different output voltages (b) Result of the simulations carried out                        | 66 |

| 4.17 | Simple AI final topology                                                                         | 66 |

| 4.18 | Transient analysis with 0.2V output voltage range: (a) Chapter 3 AI (b) Simple AI                |    |

|      | (c) Chapter 3 AI Rise (d) Simple AI Rise (e) Chapter 3 AI Fall (f) Simple AI Fall                | 67 |

| A.1  | Small signal model: (a) AI solution designed in the chapter 3 (b) Novel simple                   |    |

|      | active inductor approach                                                                         | 74 |

| A.2  | <i>RLC</i> simplified model                                                                      | 75 |

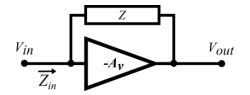

| A.3  | An ideal voltage inverting amplifier with an impedance connecting output to input                | 77 |

|      |                                                                                                  |    |

# **List of Tables**

| 3.1 | AC analysis summary (after inductance adjustment)                              | 47 |

|-----|--------------------------------------------------------------------------------|----|

| 3.2 | Transient analysis summary                                                     | 48 |

| 4.1 | AC analysis summary - Simple AI                                                | 55 |

| 4.2 | Components of <i>RLC</i> model                                                 | 58 |

| 4.3 | Transient analysis summary - Output voltage range 200mV - Proposed AI solution |    |

|     | in chapter 3: Lee's active inductor in series with a resistor                  | 67 |

| 4.4 | Transient analysis summary - Output voltage range 200mV - Proposed simple AI   |    |

|     | solution                                                                       | 68 |

# **Abbreviations, Acronyms and Symbols**

| AI     | Active Inductor                                   |

|--------|---------------------------------------------------|

| BW     | Bandwidth                                         |

| CMOS   | Complementary metal-oxide-semiconductor           |

| CML    | Current Mode Logic                                |

| CTLE   | Continuous-Time Linear Equalizer                  |

| I/O    | Input/Output                                      |

| IC     | Integrated Circuit                                |

| LNA    | Low-Noise Amplifier                               |

| MOSFET | Metal-oxide-semiconductor field-effect transistor |

| NMOS   | N-type metal-oxide-semiconductor                  |

| PMOS   | P-type metal-oxide-semiconductor                  |

| PVT    | Process Voltage Temperature                       |

| VLSI   | Very-Large-Scale Integration                      |

| RF     | Radio Frequency                                   |

|        |                                                   |

| dB       | decibel                          |

|----------|----------------------------------|

| Hz       | Hertz                            |

| gds      | Drain to source transconductance |

| gm       | Transconductance                 |

| $V_{th}$ | Threshold voltage                |

## Chapter 1

# Introduction

## 1.1 Context

The fact that silicon integrated circuit technology is scalable was observed and described in 1965 by Intel founder Gordon Moore [7]. This observation, known as Moore's Law, predicted that the number of devices would double every 18 to 24 months. Through a period of 50 years, the exponential growth of Moore's Law has continued, though with several bumps and turns along the way [8]. The technological evolution that occurred during this time resulted in the integration of large numbers of tiny MOS transistors into a small chip.

Advances in integrated circuit technology (IC) have been reducing costs and increasing functionality. In other words, the cost per transistor and the switching power per transistor has been reduced, while the memory capacity and speed have been improved, following the Dennard's Scaling Law [9], which is a corollary of Moore's law. It states, roughly, that as transistors shrink, they become faster, consume less power, and are cheaper to manufacture.

Nowadays, an increasing number of people are questioning whether the pace of the semiconductor industry is slowing down or not and if it is still in line with what Moore predicted [10, 11]. The truth is that, although the transistors have become smaller, the passive devices used for analog circuits have not scaled at the same pace.

In modern-day communications systems consisting of multiple integrated circuits, high-bandwidth communications between these ICs is one of the most critical concerns regarding the overall system performance. There are many circuits such as low-noise amplifiers (LNA), continuous-time linear equalizers (CTLE), current mode logic (CML) buffers, voltage mode drivers that may require the implementation of inductors to enhance its performance in today's era demand for speed.

While it is possible to shrink the digital circuitry, the same is not true for analog circuits when they require the use of passive devices such as inductors. Since it is economically viable to manufacture an inductor on the chip, the decision to choose the type of inductor to be applied has a significant impact when it comes to the time to integrate it.

### **1.2** Problem and Motivation

Demand for higher speeds at lower area and cost system pushes toward more self-contained circuits without the use of integrated passive components due to intrinsic constraints. These limitations include a low-quality factor, a low self-resonant frequency, a small and non-tunable inductance, and the need for a large silicon area.

In contrast, inductors synthesized using active devices, known as active inductors, guarantee large and tunable inductances and quality-factors, high self-resonant frequencies, and negligible silicon area consumption compared with that of their spiral counterparts [4].

Therefore, an active inductor solution ensures higher effectiveness compared to a passive implementation, meeting today's needs, pointing to the potential of this dissertation.

## 1.3 Objectives

This thesis aims to take advantage of CMOS technology and its reduced cost to research and design several active inductor solutions and its integration in circuits. A study of the different topologies/techniques will be performed with the respective evaluation of their pros and cons. Based on these, a circuit architecture will be proposed, developed and integrated within a block circuit with proper validation of the circuit performance parameters.

The designed active inductor topology will be integrated into an output driver with the ultimate goal of extending the bandwidth and consequently improve the driver's speed.

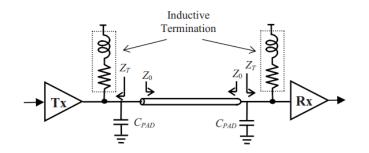

Additionally, the active inductor must guarantee impedance matching, which is required between channels and high-speed circuits to minimize signal reflection at their interfaces. Considering the general form of the voltage reflection coefficient,  $\Gamma$ , which is given by Eq.1.1, for a wave moving from medium 1 to medium 2, in a typical system, the magnitude of the reflection coefficient is a number between zero and one. When the impedance of medium 1,  $Z_1$ , is equal to the impedance of medium 2,  $Z_2$ , the numerator is zero. Thus, the match is perfect, and there is no reflection. In the case of the reflection coefficient being different from zero, there is a mismatch that results in return loss. To avoid this undesirable situation, the active inductor must have an equivalent impedance accordingly to the impedance of the cable, that in most wired serial protocols is 50  $\Omega$ .

$$\Gamma = \frac{Z_2 - Z_1}{Z_1 + Z_2} \tag{1.1}$$

This thesis is based on 28nm technology. Due to confidentiality agreements in place, details on the technology used including device characteristics and biasing voltages are not provided.

### **1.4 Document Structure**

This document presents the following structure:

- Chapter 2 [Background] Provides a theoretical background regarding several methods for bandwidth extension, implementation of on-chip inductors, a performance analysis of active and passive inductors as well as an introduction to shunt peaking implementations using active inductors. All of these topics are covered in this chapter, in order to familiarize the reader with some of the concepts that are involved in the work carried out.

- Chapter 3 [Shunt peaking implementation] Presents a detailed analysis to the shunt peaking implementations using active inductors mentioned in the previous chapter. For the topologies which show a greater potential as a possible solutions, this chapter also covers their pratical implementation as well as the comparation between the theoretical analyses and the simulations results.

- Chapter 4 [Simple AI] Explores the results obtained in chapter 3 to reach a final active inductor design. A novel approach for the simple active inductor topology is presented and it is integrated and simulated. The final of the chapter demonstrates the results of the proposed solution, evaluating and comparing them with other approaches.

- Chapter 5 [Conclusions and Future Work] Presents the conclusion of this dissertation, discussing the main out-comes obtained, regarding the work developed along with proposals for future improvement of the proposed active inductor topology.

Introduction

## Chapter 2

# Background

## 2.1 Introduction

This chapter covers topics considered relevant to understanding the problems presented in Chapter 1. It is divided into the following sections:

- Methods for bandwidth enhancement A few methods for bandwidth enhancement are presented with emphasis on the shunt peaking method

- Implementation of on-chip inductors A brief summary of the implementation of passive and active on-chip inductors is presented

- Performance analysis of active and passive inductors A detailed comparison between the active and passive inductors is performed based on several performance criteria

- Shunt peaking active inductor implementations A brief summary of the main active inductor approaches implementing the shunt peaking technique

## 2.2 Methods for bandwidth enhancement

Nowadays, bandwidth is of critical concern in wired serial communications with protocols reaching the tens of gigabit per second (Gbps), for example USB4 operates at 20Gbps and PCiE5.0 at 32Gbps.

Many methods have been proposed in the past for bandwidth enhancement. This section covers some of the most relevant: capacitive compensation technique, distributed amplification technique, and inductor shunt peaking technique.

#### 2.2.1 Capacitive compensation technique

This bandwidth-enhancing technique is presented in [1] using a simple CR network driven by a source signal source  $V_s$  with an internal resistance  $R_s$  (Fig. 2.1). The capacitance C and resistance

Figure 2.1: Simple CR network, reprinted from [1]

Figure 2.2: CR network with capacitance compensation circuit, reprinted from [1]

*R*, corresponds to the capacitance and to the input or output impedance, at a certain node in a circuit, respectively. In this case the 3-dB bandwidth  $f_{3dBo}$  is expressed by Eq. 2.1.

$$f_{3dBo} = \frac{1}{2\pi C(R//R_s)}$$

(2.1)

Eq. 2.1 suggests that the pole resulting from *C*, *R*, and *R*<sub>s</sub> limits the bandwidth. It is possible to achieve bandwidth improvement by reducing *R* or *C*. A small R, however, could result in gain degradation at lower frequencies. In contrast, a smaller C increases the bandwidth without degrading the low-frequency voltage gain. A new circuit technique to reduce the parasitic junction capacitance is represented in Fig. 2.2 where the part enclosed by the dashed line is a capacitance compensation circuit. It detects the voltage  $V_0$  across the capacitance C and generates a compensation current that charges or discharges the capacitance. This way, both the bandwidth and the gain-bandwidth product are enhanced.

This technique can also compensate for both poles at the input and output nodes. Although [1] suggests a technique for canceling undesired capacitors, frequency limitation of the active compensating network does not allow exact cancellation so the maximum bandwidth obtained is less than 1GHz.

#### 2.2.2 Distributed amplification

This is another approach to improve the bandwidth and focus on minimizing the effect of the large shunt capacitance at critical nodes. The key idea behind this method is to break the large shunt capacitor into several smaller shunt capacitors and separate them with inductors. As a result, the large shunt capacitor is replaced with a distributed LC network or a transmission line.

Fig. 2.3 shows an example of a distributed amplifier architecture based on lumped-element artificial transmission lines, where  $C_g$  and  $C_p$  are capacitances at the input and output of each active

Figure 2.3: The distributed amplifier based on lumped-element artificial transmission lines, reprinted from [2]

device, while  $L_g$  and  $L_p$  denote the inductance of the input and output line sections, respectively. The bandwidth of the distributed amplifier is limited by the cut-off frequency of the transmission lines. The wave propagating through the lumped-element line experiences significant attenuation beyond the cut-off frequency. In order to achieve high bandwidth, small active devices should be used, but, this lowers the gain of the distributed amplifier. As the ratio L/C determines the characteristic impedance of the lines, inductance L cannot be made arbitrarily small to achieve higher bandwidth. Thus, there is a trade-off between gain and bandwidth of the distributed amplifier [12].

Despite the bandwidth extension, the integration of distributed amplifiers consume large area and high power and are difficult to design owing to delay line losses that necessitate extensive modeling and electromagnetic simulation [13].

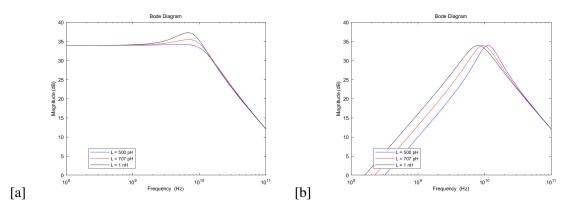

#### 2.2.3 Shunt peaking

Considering the simple common source amplifier illustrated in Fig. 2.4 (a), by neglecting the intrinsic parasitics of the transistor, the bandwidth is determined by a single dominant pole, which is determined by the output load resistance R and the load capacitance C. The capacitance  $C = C_1 + C_2$ , represents all the loading on the output node, including that of a subsequent stage while the effective load resistance at that node is represented by resistance R.

The introduction of an inductance L in series with the load resistance, represented in Fig. 2.4 (b), provides an impedance component that increases with frequency, which compensates the decreasing impedance of the capacitance, leaving a net impedance that remains roughly constant over a wider frequency range than that of an *RC* network. This technique, called shunt peaking, improves the bandwidth of the amplifier by transforming the frequency response from that of a single pole to one with two poles and a zero (Eq. 2.2).

$$Z(s) = (\frac{1}{sC}) / (R+sL) = \frac{R+sL}{1+sRC+s^2LC}$$

(2.2)

The frequency response of this shunt peaked amplifier is characterized by the ratio of the L/Rand RC time constants. This ratio can be denoted by m so that  $L = mR^2C$ . The problem, then, is to

Background

Figure 2.4: (a) Simple common source amplifier (b) Common source amplifier with shunt peaking (c) Common source amplifier with bridged-shunt peaking

choose a value of *m* that leads to some desired behavior, in this case, maximizing the bandwidth. This maximum occurs at a value of  $m = \sqrt{2}$ , which extends the bandwidth to a value of about 1.85 times as large as the uncompensated bandwidth [14, 15, 16]. This extension comes with a 1.5dB of peaking. A maximally flat gain is achieved for  $m = 1 + \sqrt{2}$  but bandwidth is reduced to 1.72.

#### 2.2.3.1 Bridged-shunt-peaking

Despite the increased impedance of the inductor contribute to the bandwidth improvement, it also leads to peaking in the response. Since there are applications where the presence of peaking is a concern, techniques to eliminate peaking with maximum bandwidth are desired. This can be achieved by adding in shunt with the inductor a capacitor, shown in Fig. 2.4 (c), that should be large enough to negate peaking but small enough to not significantly alter the gain response. Compared to the common source amplifier with shunt peaking (Fig. 2.4 (b)), this new approach achieves approximately the same maximum bandwidth (1.85 times as large as the uncompensated bandwidth), but this time, with a flat gain response.

#### 2.2.3.2 Bridged-shunt-series-peaking

So far, bandwidth has almost doubled while a flat response has been guaranteed, however, it is possible to do better still by employing a two-port network between amplifier and load. An inductor is inserted to separate the total load capacitance into two constituent components. The overall result is a bridged-shunt-series peaking, Fig. 2.5 (a). Without  $L_2$ , the transistor charges C (where  $C = C_1 + C_2$ ), but with  $L_2$  only  $C_1$  is charged initially because  $L_2$  delays current flow to the rest of the network. Taking into account some specific values combinations for the components, this approach can potentially achieve bandwidth improvements situated in the range of [3.5 to 4] times larger with no gain-peaking. However, such precise component values are difficult to realize due to distributed parasitic effects and process, voltage, and temperature (PVT) variations making difficult to obtain values near to 4 times more bandwidth [13].

Figure 2.5: (a) Common source amplifier with bridged-shunt-series peaking and drain parasitic capacitance (b) Common source amplifier with asymmetric T-coil peaking and drain capacitance

#### 2.2.3.3 Asymmetric T-Coil peaking

As the load capacitance increases, the capacitive-splitting action of  $L_2$  and the bridging action of  $C_B$  become ineffective in achieving a large bandwidth. The magnetic coupling action of a transformer is used as a solution to the mentioned problem. In an asymmetric T-coil-peaked amplifier, Fig. 2.5 (b), the coils are wound to achieve a negative mutual inductance. Similarly to bridged-shunt-series peaking, the secondary inductor  $L_2$  facilitates capacitive splitting so that the initial charging flows only to  $C_1$ . Next, the current begins to flow in  $L_2$ , which results in a proportional amount of current to flow to  $C_2$ . The negative magnetic coupling allows for an initial boost in the current flow to the load capacitance  $C_2$  because the capacitor is effectively connected in series with the negative mutual inductance (-*M*) element of the T-coil. Improvements in the range of [4 to 5.5] are obtained in [13] using T-Coil peaking although non-peaking is again difficult to implement for the reasons mentioned in 2.2.3.2.

This method is implemented in [16] as well, achieving a bandwidth improvement of 3.23 times, which is considered sub-optimal since finding the layout geometry that yields the best performance is challenging, as the choice of  $L_1$ ,  $L_2$  and  $k_m$  is constrained by layout feasibility and the resulting parasitics. The coupling constant  $k_m$  (represented in Fig. 2.5 (b)) is related to the mutual inductance M as  $k_m = M/\sqrt{L_1L_2}$ .

A further improvement is possible and it is suggested in [14]. This adjustment consists in adding a small bridging capacitance across the inductors to create a parallel resonance (Fig. 2.6). The increased circulating currents associated with the resonance help to push the bandwidth out even further. Applying these conditions, [14] indicates a theoretical maximum of 2.83 times more bandwidth.

### **2.3 Implementation of on-chip inductors**

What nearly all the approaches to bandwidth improvement have in common is the use of an inductor, which has a significant impact when it comes to the time to integrate it on the chip. The cost increases proportionately with the area so it is desired that the inductor occupies the less area

#### Background

Figure 2.6: Amplifier with T-Coil bandwidth enhancement

possible. But, the integration of the inductor has to take into account more performance factors that are crucial for the proper functioning of the entire system.

Thus, the need arises to study what type of inductors should be implemented in an approach to increase bandwidth, taking into account their characteristics. Traditionally, passive inductors are implemented as off-chip discrete components. The need for off-chip communications using passive components drastically limits the bandwidth, reduces the reliability, and increases the overall system's cost. Since the early 1990s, a significant effort has been made to fabricate inductors on a silicon substrate such that an entire wireless transceiver could be integrated on a single substrate monolithically. In the meantime, the need for a large silicon area to fabricate spiral inductors has also contributed to intensive research on the design of inductors using active devices, aiming to improve the overall performance while minimizing the silicon consumption and subsequently the fabrication cost [4]. In this section, a brief summary of the implementation of passive and active on-chip inductors will be presented.

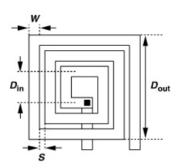

#### 2.3.1 Passive inductor

Passive inductors are realized on-chip by laying out the metal trace on silicon using one or more interconnects in different ways. The most popular planar inductor topology is the square spiral [17]. Owing to the mutual coupling between every two turns, spirals exhibit a higher inductance than a straight line having the same length [3]. A simple two-dimensional square spiral is fully specified by five quantities (Fig. 2.7): the outer diameter,  $D_{out}$ , the inner diameter,  $D_{in}$ , the line width, W, the line spacing, S, and the number of turns, N.

#### 2.3.2 Active inductor

A much more compact alternative to running inductors on the chip to improve bandwidth is to use active inductors as they are possible to implement in standard digital CMOS processes, which consist of active networks composed mainly of MOS. transistors.

Figure 2.7: Spiral inductor, reprinted from [3]

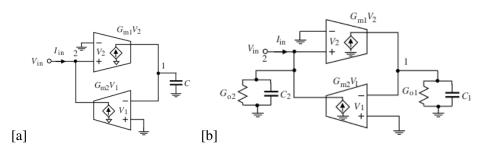

#### 2.3.2.1 Gyrator-C

The Gyrator-C is an example of an implementation of CMOS active inductors. A gyrator consists of two back-to-back connected transconductors. When one port of the gyrator is connected to a capacitor, as illustrated in Fig.2.8 (a), the configuration is called the gyrator-C network. A gyrator-C network is considered as lossless when both the input and output impedances of the transconductors of the network are infinite and the transconductances of the transconductors are constant [4]. The inductance looking into port 2 is given by Eq.A.27.

$$L = \frac{C}{G_{m1}G_{m2}} \tag{2.3}$$

Therefore, Gyrator-C networks can be used to synthesize inductors. These synthesized inductors are called gyrator-C active inductors.

When either the input or the output impedances of the transconductors of gyrator-C networks are finite, the synthesized inductors are no longer lossless, as represented in Fig.2.8 (b) where  $G_{o1}$  and  $G_{o2}$  denote the total conductances at nodes 1 and 2, respectively.

### 2.4 Performance analysis of active and passive inductors

Now that there is an idea of how to increase the bandwidth and how to implement the inductors, the focus now is to know what type of inductors to implement taking into account their characteristics. In this section a detailed comparison between the active and passive inductors has been performed regarding several performance criteria such as:

- Quality Factor

- Silicon Area Consumption

- Self-Resonant Frequency

- Power Consumption

- Linearity

Figure 2.8: (a) Single-ended gyrator-C active inductor (b) Lossy single-ended gyrator-C active inductors (reprinted from [4])

- Noise

- Frequency Range

- Inductance Tunability

The performed comparison establishes important guidelines for choosing which type of inductor to integrate, according to specific applications.

#### 2.4.1 Quality Factor

In RF circuit design, consideration of the total energy stored in the component as well as of the total loss is relevant [18]. As a result, the conventional definition of Q, is the ratio of the stored to the dissipated total energy in the component, so the related quality factor can simply be calculated as Eq.2.4, with z being the impedance of the inductor.

$$Q = \frac{im(z)}{Re(z)} \tag{2.4}$$

Taking into account this ratio, the quality factor of spiral inductor, can be represented by Eq. 2.5 [19], which is the ratio of the energy stored in the inductor to its energy dissipated in one oscillation cycle.

$$Q = 2\pi \frac{\text{energy stored}}{\text{energy dissipated in one oscillation cycle}}$$

(2.5)

The energy dissipated is directly related to the loss mechanisms of inductors, which basically, consists of various resistances within or around the structure that carries current when the inductor does. These loss mechanisms could result from several events [3] such as metal resistance, skin effect and capacitive coupling to substrate:

- Metal Resistance The metal forming an inductor exhibits an intrinsic resistance.

- Skin Effect and Eddy currents At high frequencies, the current through a conductor prefers to flow at the surface skin effect causing a nonuniformity in the current. At the same time, the magnetically induced eddy currents will also contribute to non-uniform

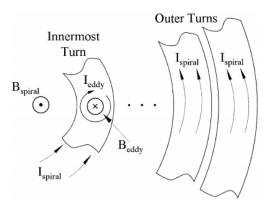

Figure 2.9: Formation of conductor eddy currents, reprinted from [5]

behavior. This way, in passive inductors, the proximity of adjacent turns results in a complex current distribution.

As an example, a circular inductor is shown in Fig.2.9. This inductor carries a current  $I_{spiral}$  which flows in the direction as indicated, generating an associated magnetic field  $B_{spiral}$ , which has a maximum intensity at the center of the spiral. In the case of a large inductor with a very small core diameter, a significant part of this magnetic field does not pass through the center of the spiral but rather through its inner turns. Following the Faraday and Lenz's laws, an electric field is magnetically induced in these inner turns, that will generate circular eddy currents,  $I_{eddy}$ , which flow in the direction opposing the original change in the magnetic field. From the Fig.2.9, it is possible to observe that the eddy current,  $I_{eddy}$ , will add to the  $I_{spiral}$  on the inner side and subtract from  $I_{spiral}$  on the outer side of the conductor. As a result, the current density will be higher on the inner side than on the outer side causing a nonuniform current in the metal turns of the spiral inductor.

The magnitude of these eddy currents is comparable to the spiral current at high frequencies, hence increasing the series resistance of the inductor, reducing this way its quality factor [20].

• Capacitive Coupling to Substrate - Once that the substrate resistivity is neither zero nor infinity, there is a flow of current which results in a loss in each cycle of operation, hence, lowering the *Q*.

Despite some approaches that can potentially raise the Q, that include: thicker metallization [21], stacking of metal layers in a multilevel metal process [22], fabrication using high-resistivity silicon substrates [21] and the selective removal of silicon from beneath the inductor structure by chemical etching [23], the Q enhancement is not very effective considering the increased processing cost and required area.

In contrast, the quality factor of CMOS active inductors is set by the ohmic loss of the inductors, arising mainly from the finite output resistance of the transconductors of the inductors. Threefore, the quality factor of CMOS active inductors can be improved by increasing this output resistance. Several techniques are adopted to boost the output resistance, such as cascodes, regulated cascodes, and negative resistor compensation [4].

#### 2.4.2 Silicon Area Consumption

Typically, the implementation of a spiral inductor requires a huge area on the die. Since the cost increases proportionately with the area, the designer always aims to minimize the occupied area. The inductor chip area can be reduced by choosing the optimum physical layout, that is, the strip width, the spacing between adjacent lines, the gap between opposing sets of coupled strips, the outer dimension of the spiral, and the number of turns. Therefore, these chip area reduction techniques are useful for obtaining higher inductances, at the expense of higher parasitic which degrades the overall performance of the inductor [24].

On the other hand, since that only MOS transistors are generally needed in the realization of CMOS active inductors and the inductance of these active inductors is inversely proportional to the transconductances of the transistors, the silicon consumption of CMOS active inductors is considered negligible as compared to that of their spiral counterparts [4, 25].

With the reduction of technological nodes, in CMOS, the scalability factor is related to digital parts while analog components with passive inductors have reduced scalability since they depend on the metal and dielectric characteristics. Despite all the methods to reduce the area occupied by passive elements, they will always fill a significant area.

#### 2.4.3 Self-Resonant Frequency

The self-resonant frequency of an inductor is the frequency at which the parasitic capacitance of the inductor resonates with the ideal inductance of the inductor resulting in an extremely high impedance, so it is highly desirable to have an inductor with a large self-resonant frequency, ensuring that the active inductor has an inductive characteristic over a large frequency range.

The self-resonance of a spiral inductor is the resonance of the *LC* tank formed by the series inductance of the spiral inductor and the shunt capacitance between the spiral of the inductor and the substrate, as well as its underpass capacitance. The low self-resonant frequency of spiral inductors is mainly due to the large spiral-substrate capacitance, arising from the large metal area occupied by the spiral [4]. A thicker oxide layer reduces the parasitic capacitance of the structure, which improves the inductor self-resonant frequency [26]. However, despite some efforts to increase the self-resonant frequency, this remains a major drawback of passive components.

Taking the example in [4] to the active inductors, where a lossy single-ended gyrator-c is represented (Fig. 2.8 (b)), being  $G_{o1}$  and  $G_{o2}$  the total conductances at nodes 1 and 2, respectively. Assuming that the transconductances of the transcoductors are constant the resonant frequency of the RLC networks of the active inductor is given by Eq. 2.6.

$$\omega_0 = \frac{1}{LC_P} = \sqrt{\frac{G_{m1}G_{m2}}{C_1C_2}} = \sqrt{\omega_{t1}\omega_{t2}}$$

(2.6)

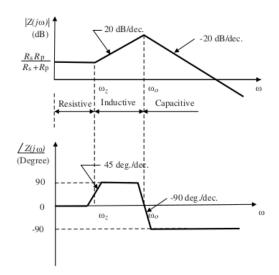

Figure 2.10: Bode plots of the impedance of lossy single-ended gyrator-C active inductor, reprinted from [4]

Where  $\omega_{t1,2}$  is the cut-off frequency of the transcoductors (Eq. 2.7).

$$\omega_{t1,2} = \frac{G_{m1,2}}{C_{1,2}} \tag{2.7}$$

$\omega_0$  is the self-resonant frequency of the gyrator-C active inductor. After a careful analysis, it is possible to observe that the pole resonant frequency of the impedance of the RLC equivalent circuit of the lossy inductor is given by Eq. 2.8

$$\omega_p \approx \sqrt{\frac{1}{LC_P}} = \omega_0 \tag{2.8}$$

Also, the impedance of the equivalent RLC circuit has a zero at frequency:

$$\omega_z = \frac{G_{o1}}{C_1} \tag{2.9}$$

The Bode plots of the impedance of the equivalent RLC circuit of the lossy inductor is sketched in Fig. 2.10 and it shows that the frequency range in which the gyrator-C network is inductive is lower-bounded by  $\omega_z$  and upper-bounded by  $\omega_0$ . It is possible to conclude, from this example, that the upper bound of the frequency range is set by the self-resonant frequency of the active inductor, which is set by the cut-off frequency of the transconductors constituting the active inductor.

#### 2.4.4 Power Consumption

Unlike passive inductors, active inductors consume power to generate inductive impedance. In active inductor configurations, for instance, Gyrator-C active inductors, the dc power is used mainly for biasing the transconductors. However, power consumption is not a huge concern because the inductance of the inductors is inversely proportional to the transconductances. This way,  $gm_1$  and  $gm_2$  are designed to be small in order to produce a large inductance. By lowering the dc biasing currents of the transconductors, this goal is achieved. The power consumption of active inductor is often set by replica-biasing and negative resistor networks [4].

#### 2.4.5 Linearity

The linearity of a circuit signifies how well its output power can be represented as a linear function of the input power. Passive components have a wider linear operating range than their electronic equivalents [26]. Linearity is a relevant issue regarding the use of active inductors. When an active circuit is driven with a large signal, the operating points of the devices vary with the signal amplitude. This non-linear large-signal behavior of the devices results in impedance fluctuations and produces higher distortion that leads to the generation of harmonic frequencies [27]. Hence, active inductors do not apply to circuits involving large signal performance, such as power amplifiers.

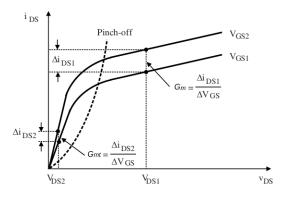

Following the example in [4], which uses a gyrator-C network that consists of one port of a gyrator connected to a capacitor, as shown in Fig. 2.8 (a), it is possible to conclude that the inductance of the gyrator-C active inductor is represented by the Eq. 2.10, where  $G_{m1,m2}$  are the transconductances of transconductors 1 and 2 respectively when in saturation. The inductance of the gyrator-C when in triode is given by Eq. 2.11, where  $G_{mt1,mt2}$  are the transconductances of transconductances of transconductances of the gyrator-C when in triode is given by Eq. 2.11, where  $G_{mt1,mt2}$  are the transconductances of transcondu

$$L = \frac{C}{G_{m1}G_{m2}} \tag{2.10}$$

$$L = \frac{C}{G_{mt1}G_{mt2}} \tag{2.11}$$

Fig. 2.11 shows that when the transistors of active inductors enter the triode region, the transconductances of the transistors decrease from  $G_m$  (saturation) to  $G_{mt}$  (triode) in a nonlinear way. Therefore, when the voltage swing is large enough to change the operating point of the transistors of the transconductors, regarding the Eq. 2.10 and 2.11, the inductance of the gyrator-C active inductors will exhibit a nonlinear characteristic.

#### 2.4.6 Noise

Unlike the passive inductor where the damping resistor is the main noise producer, noise is a major drawback of an active inductor and it is originated from the thermal and flicker noise of MOS transistor channel, while the damping resistor is a fictitious one without any noise contribution [28].

Thermal noise is due to the thermal excitation of charge carriers in a conductor. This noise has a white spectral density, it is proportional to absolute temperature and not dependent on bias conditions (dc bias current) [29].

Figure 2.11: Transconductance of MOSFETs in the saturation and triode regions, reprinted from [4]

Although flicker noise is found on all active devices, it occurs only when a dc current is flowing. Typically, flicker noise arises due to traps in the semiconductor, where carriers that would normally constitute dc current flow are held for some time period and then released. Flicker noise is also commonly referred to as 1/f noise since it is well modeled as having a  $1/f^{\alpha}$  spectral density, where  $\alpha$  is between 0.8 and 1.3 [29]. It is apparent that flicker noise is most significant at low frequencies, although, in devices exhibiting high flicker noise levels, this noise source may dominate the device noise at frequencies well into the megahertz range [30].

#### 2.4.7 Inductance Tunability

The inductance of a spiral inductor remains reasonably fixed up to a certain frequency, called self-resonance frequency (low-pass behavior). Beyond this frequency, the inductor has a capacitive behavior. In contrast, the inductance of the active inductor is determined by a specific frequency range (band-pass behavior - represented previously in Fig. 2.10).

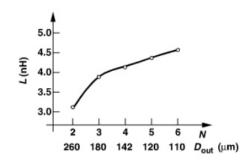

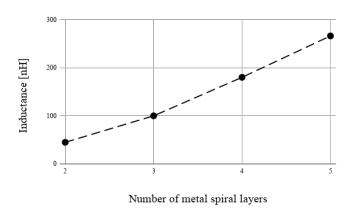

There are some techniques to increase the inductance of the spiral inductor such as increasing the number of the turns of the spiral or use a stacked configuration where spirals on multiple metal layers are connected using vias. However, for a given length, width, and spacing, the passive inductor's inductance is a weak function of the number of turns (Fig. 2.12) [3] and at the expense of a large silicon area. In [31], it is demonstrated that the inductance of stacked spiral inductors increases approximately linearly with the increase in the number of the spiral layers of the inductors (Fig. 2.13) but it increases the spiral-substrate capacitance as well.

In section 2.3.2.1, it was shown that in a gyrator-C network, inductance is proportional to the capacitance and inversely proportional to the transconductances. In this case, transconductance is dependent on current flowing through that transconductor so gate voltage can be manipulated to control the current of that particular branch that will ultimately vary the inductance of the active inductor. Thus, the inductance can be tuned conveniently by varying the dc biasing condition of the transistors. The fine tuning of the inductance of active inductors can also be achieved by

Figure 2.12: Inductance as a function of the number of turns for a given line length, reprinted from [3]

varying the load capacitance of the transconductors of the active inductors using MOS varactors [4].

### 2.5 Shunt peaking active inductor implementations

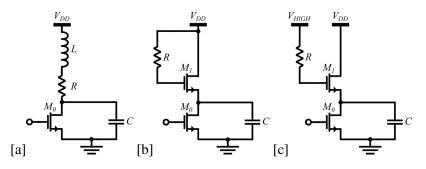

The previous Shunt peaking section, 2.2.3, presented several shunt peaking approaches, assuming only the implementation of on-chip inductors, being the simplest one showed in Fig.2.14 (a). As discussed previously, it is desired to adopt an active inductor solution, since it is the most viable option to guarantee a resonant frequency that is aligned with the bandwidth required in today's wired serial communications with protocols reaching the tens of Gbps while using a reduced silicon area.

#### 2.5.1 Simple Active inductor

This way, the replacement of the passive on-chip inductor by an active inductor, results in a simple active inductor, represented in Fig.2.14 (b). However, the main drawback of this basic topology

Figure 2.13: Inductance as a function of the number of metal spiral layers

Figure 2.14: Common source amplifier with shunt peaking - (a) Using a spiral inductor (b) Using a simple active inductor (c) Using an active inductor with voltage boosting

is its significant dc voltage drop caused by the NMOS threshold voltage, which is enlarged by the body effect. In [32], it is proposed a solution to this problem, which is biasing the gate of the active inductor one NMOS threshold voltage above  $V_{DD}$  reducing the voltage drop across the active inductor to about half its value (Fig. 2.14 (c) ). The cost of this method is increased design complexity and area associated with the addition of voltage-boosting circuitry.

#### 2.5.2 Folded Active Inductor

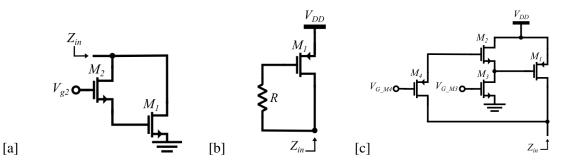

Another solution is presented in [33], initially proposed by [34], and is represented in Fig. 2.15 (a). It adopts a folded topology that allows the gate-source voltage of the NMOS transistor to be biased at much higher than its  $V_{th}$  level without additional circuitry, and where  $M_2$  transistor is biased in linear region, operating as a resistor.

This topology is widely used in many high frequency applications, such as limiting amplifiers for optical receivers [33, 34], RF transmitters [35] or even to equalization purposes [36].

Although the folded topology is mostly associated with the use of NMOS, some consider that the PMOS version of folded is the one represented in figure 2.15 (b), for example in [37, 38, 39]. However, this PMOS version is nothing less than the PMOS version of the simple active inductor.

Figure 2.15: (a) Folded active inductor NMOS (b) PMOS version: Simple active inductor and Folded active inductor (c) Lee's active inductor

Figure 2.16: Doubly terminated I/O blocks with inductive peaking terminations, reprinted from [6]

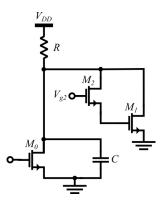

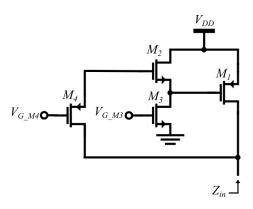

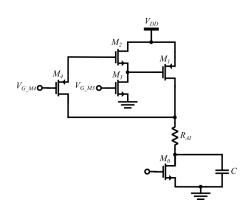

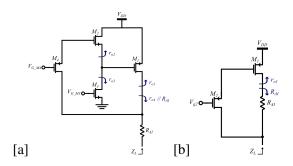

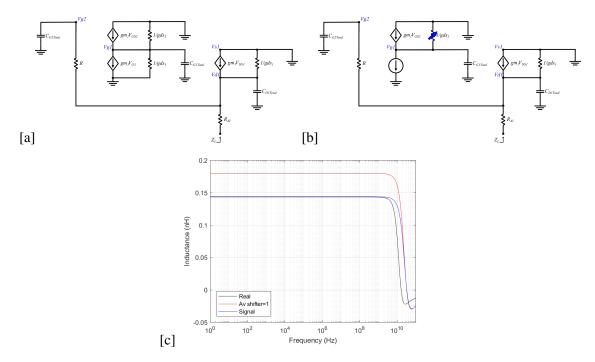

#### 2.5.3 Lee's Active Inductor

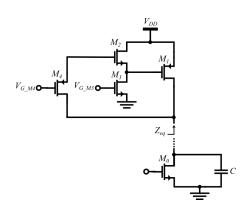

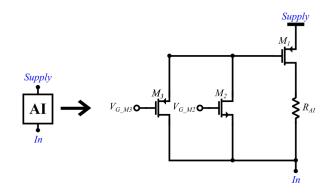

In [40], an active inductor termination for high speed I/O circuits is presented. This approach, represented in Fig.2.15 (c), has a transistor  $M_4$ , operating in linear region to act as a resistor, coupling, this way, the gate of the PMOS  $M_1$  to the output node. To guarantee a lower gate bias voltage for  $M_1$ , a level shifter is introduced, which is constituted by a source follower  $M_2$  and a current source  $M_3$ . Similarly to the Folded active inductor, this topology does not need the addition of a voltage-boosting circuitry. However, it could have an additional overhead power consumed by the level shifter, which also contributes to increase the overall parasitics in the configuration.

This configuration is also used in [6], as an inductive termination in an output driver in the serial link transmitter shown in Fig.2.16. The active inductor aims to compensate the high frequency loss of the channel.

#### 2.6 Summary

In this chapter, three of the most relevant methods in bandwidth enhancement were covered, namely, capacitive compensation technique, distributed amplification, and shunt peaking. While capacitive compensation suffers from critical frequency limitations, distributed amplification consumes large area and high power. Shunt peaking, in contrast, allows an increase in bandwidth by simply adding a reduced number of inductors.

A detailed comparison between the active and passive inductors was performed based on several performance criteria. Passive inductors suffer from a low quality factor, a low self-resonant frequency, a low and fixed inductance and occupy a large silicon area. On the other hand, active inductors offer a number of attractive characteristics as compared with their passive counterparts. These characteristics include a low silicon consumption, a large and tunable inductance, a large and tunable quality factor. The applications of active inductors, however, are affected by some stiff difficulties arising from the intrinsic characteristics of MOS devices including a limited dynamic range and a high level of noise.

#### 2.6 Summary

Finally, the concept of shunt peaking was presented considering only active inductors. The basic active inductor has a significant voltage drop, which can be compensated with a voltage-boosting circuitry with the cost of introducing extra design complexity. The folded active inductor avoids both these problems by using just an NMOS transistor with a resistor connected to the gate being widely used in different high speed applications. Lastly, the Lee active inductor is a viable shunt peaking technique that uses a level shifter to increase the ability to regulate the voltage depending on the scenario where it is applied.

Background

## **Chapter 3**

## Shunt peaking implementation

As shown in the previous chapter, inductive shunt peaking is a technique that allows the improvement of bandwidth using a reduced number of inductors, which can be implemented passively or actively. Nowadays, since it is economically viable to manufacture an inductor on the chip, the decision to choose the type of inductor to be applied has a significant impact when it comes to the time of integration. The need for a large silicon area to fabricate passive inductors and features such as low-quality factor, low and fixed inductance, and low self-resonant frequency, dramatically increase the interest in using an active inductor solution, aiming to minimize silicon area consumption and, subsequently, the manufacturing cost while improving the overall performance.

During this chapter, the AI (active inductor) configurations presented in the previous chapter will be analyzed. For the topologies which show a greater potential as a possible starting point for the solution of the problem at hand, a practical design will be carried out so that a more complete analysis can be performed with simulation results. Along with the simulation results, a theoretical analysis will be also made. Both of these analyses will serve as a basis for all of the work that will be later done in the thesis.

Taking into account the scenario and the requirements described in chapter 1, a journey begins in search of the most suitable active inductor configuration with the ultimate goal of extending the bandwidth.

## 3.1 Folded Active Inductor

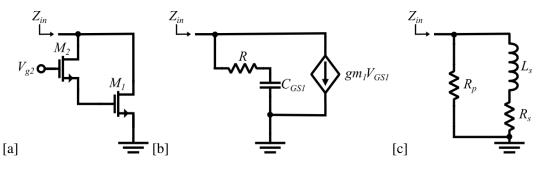

#### 3.1.1 Small signal analysis

To better understand how the folded configuration works (Fig.3.1 (a)), first, it is considered the small-signal model, which is represented in Fig.3.1 (b), as well as the respective input impedance. In order to simplify the analysis,  $M_1$  is modeled just with  $C_{gs}$  and gm, while the  $M_2$  transistor, which is biased in linear region to perform as a resistor, is represented by a R. By the application of a test voltage  $V_{in}$  with the current out of the positive terminal being  $I_{in}$  it is possible to obtain the Thévenin equivalent impedance  $Z_{in}$ , that is given by the ratio of the test voltage to the test current

Shunt peaking implementation

Figure 3.1: Folded active inductor - (a) Schematic (b) Small signal model (c) Small signal equivalent

(Eq. 3.1).

$$Z_{in} = \frac{V_{in}}{I_{in}} \tag{3.1}$$

Considering now the Ohm's and short Kirchhoff's Current Laws, the Eq.3.2 represents the algebric sum of all the currents at the gate of  $M_1$  while  $I_{in}$  is given by Eq.3.3.

$$\frac{V_{in} - V_g}{R} - \frac{V_g}{1/(s\,C)} = 0 \tag{3.2}$$

$$I_{in} = gm V_g + \frac{V_{in} - V_g}{R} \tag{3.3}$$

Solving these three equations, it is obtained the input impedance, given in Eq.3.4.

$$Z_{in} = \frac{s R C_{gs} + 1}{s C_{gs} + gm}$$

(3.4)

From  $Z_{in}$ , it can be quickly inferred that it has a zero ( $w_z = 1/(R C_{gs})$ ) and a pole ( $w_p = gm/C_{gs}$ ). And similarly the input admittance,  $Y_{in}$ , is given by Eq. 3.5.

$$Y_{in} = \frac{1}{R} + \frac{1}{s\frac{RC_{gs}}{gm - 1/R} + \frac{1}{gm - 1/R}}$$

(3.5)

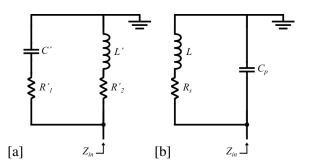

The parameters of the *RLC* equivalent circuit are now more easy to reach, once that, the equation of  $Y_{in}$  can be represented by an *RL* network in parallel with a resistor  $R_p$  (Eq.3.6), that is shown in Fig.3.1 (c).

$$Y_{in} = \frac{1}{R_p} + \frac{1}{s\,L + R_s} \tag{3.6}$$

where

$$R_p = R$$

$L = \frac{R C_{gs}}{gm - 1/R}$   $R_s = \frac{1}{gm - 1/R}$  (3.7)

From these expressions, it is possible to conclude that the value of the inductance can be tuned by the  $M_2$  transistor as the inductance range is strongly dependent on the R value. It is also important to highlight the impact that the gm has on the performance of this topology. If

Figure 3.2: Application of the folded active inductor

increasing gm corresponds to increasing the pole frequency value, it also decreases the inductance value. Additionally, the value of gm is also required to be higher than 1/R in order to have L > 0.

#### 3.1.2 Shunt vs Series peaking

Simulations carried out, proved what the previous Small signal analysis section demonstrated (3.1.1). A high inductance is achieved during a wide range of frequency, just taking into account the values of specific parameters, especially *gm*, which makes the folded configuration a candidate to be a solution to the exposed problem.

Now, it is necessary to decide where the folded inductor will be inserted. Remembering the conditions mentioned in the chapter 1, the inductor must have a real linear part equivalent of 50  $\Omega$ , so the only way will be to apply the inductor in parallel with the resistance, as represented in the Fig. 3.2. This scenario was simulated, and the results were not very encouraging. It seems that the fact of having an inductor in parallel compromises the generated inductance.

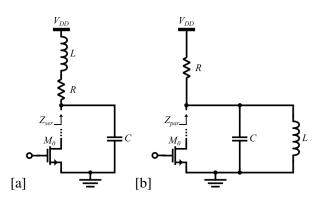

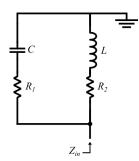

In order to evaluate the impact in the equivalent impedance of having a resistor in parallel with an inductor instead of having it in series, a test was performed, considering a resistor and an ideal inductor, as it is suggested in Fig. 3.3.

Figure 3.3: Testing scenarios: (a) Resistance in series with the inductor ((R+sL)//(1/sC)) (b) Resistance in parallel with the inductor (R//sL//(1/sC))

Figure 3.4: Simulation results: (a) Resistance in series with the inductor ((R+sL) // (1/sC)) (b) Resistance in parallel with the inductor (R // sL // (1/sC))

Fig.3.3 (a) represents the case where the configuration has three branches, each one having just one component, hence constituting, a parallel between a resistor, R, a capacitor, C, and an inductor, L. Elaborating Eq.3.8, the equivalent impedance,  $Z_{par}$ , is given by Eq.3.9.

$$Z_{par} = R // sL // \frac{1}{sC}$$

$$(3.8)$$

$$Z_{par} = \frac{sL}{s^2 L C + (sL/R) + 1}$$

(3.9)

On the other hand, Fig.3.3 (b) shows the case where the equivalent impedance,  $Z_{ser}$ , corresponds to a parallel of two branches, one with a resistor, R, in series with an inductor, L, and another with just a capacitor, C. This way,  $Z_{ser}$  can be obtained through the Eq. 3.10 that results in the final expression of the equivalent impedance in this case is given by Eq. 3.11.

$$Z_{ser} = (R + sL) / / \frac{1}{sC}$$

(3.10)

$$Z_{ser} = \frac{R + s L}{s^2 L C + s R C + 1}$$

(3.11)

The main difference between these two approaches is implicit, both in the performed simulation (Fig.3.4) and in the analytical analysis. The approach (b), which has all the components in parallel, has an undesired bandpass behavior due to the presence of a zero at zero frequency. For this reason, it could never be considered a good approach to extend the bandwidth. Despite achieving a high inductance during a wide range of frequency, this folded active inductor configuration does not suit so well when integrated into the described shunt peaking scenario.

Figure 3.5: Lee's active inductor

## 3.2 Lee's Active Inductor

#### 3.2.1 Small signal analysis

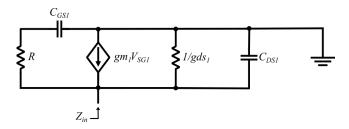

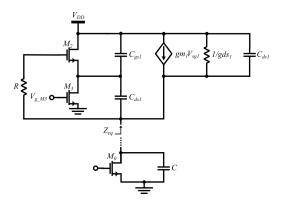

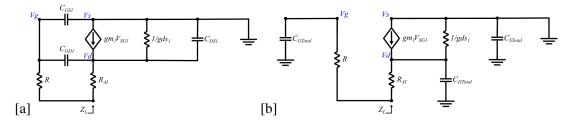

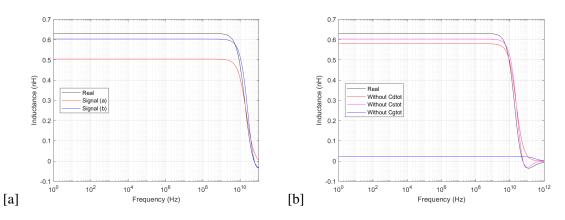

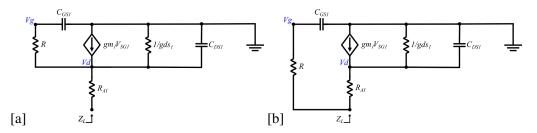

The small signal analysis of this subsection follows the analysis carried out in [40] (topology represented in Fig.3.5), which assumes that the level shifter has unitary AC gain. As will be shown later, this assumption is a rough approximation of the actual gain of the level shifter. Transistor  $M_1$  is modelled neglecting  $C_{gd}$  (which will be considered later in a more detailed analysis) and considering gm, gds,  $C_{gs}$  and  $C_{ds}$  inherent parameters of transistor  $M_1$ . Resistor R, represents transistor  $M_4$ , which is operating in linear region. The small signal of this active inductor is shown in Fig. 3.6.

By deactivating all the independent sources and using a test voltage  $V_{in}$  with the current out of the positive terminal being  $I_{in}$ , it is possible to obtain the Thévenin equivalent impedance,  $Z_{in}$ , that is given by the ratio of the test voltage to the test current (3.12).

$$Z_{in} = \frac{V_{in}}{I_{in}} \tag{3.12}$$

Figure 3.6: Schematic of Lee's active inductor

Considering the Ohm's and short Kirchhoff's Current Laws, Eq.3.13 and Eq.3.14 represents the algebraic sum of all the currents at the gate of  $M_1$  and the expression of  $I_{in}$ , respectively.

$$\frac{V_{in} - V_g}{R} + \frac{V_g}{1/(s C_{gs})} = 0$$

(3.13)

$$I_{in} = \frac{V_{in} - V_g}{R} + gm \, V_g + V_{in} \, gds + \frac{V_{in}}{1/(s \, C_{ds})}$$

(3.14)

Deriving these three equations, it is obtained the input impedance, given in Eq.3.15.

$$Z_{in} = \frac{1 + s R C_{gs}}{s^2 C_{ds} C_{gs} R + s (C_{gs} + gds C_{gs} R + C_{ds}) + gm + gds}$$

(3.15)

Knowing that the admittance,  $Y_{in}$ , is defined as the reciprocal of impedance and neglecting the  $C_{ds}$ , to simplify, the expression of  $Y_{in}$  can be derived from Eq.3.16.