## David Barros Leonardo

Licenciatura em Ciências da Engenharia Electrotécnica e de Computadores

## Design of High-Bandwidth and High-Linearity Input Buffers for ADCs

Dissertation submitted in partial fulfillment of the requirements for the degree of

Master of Science in Engenharia Electrotécnica e de Computadores

Adviser: João Carlos da Palma Goes, Prof. Doutor, NOVA University of Lisbon

Examination Committee

Chairperson: André Mora Raporteur: Luís Bica Oliveira

November, 2020

### Design of High-Bandwidth and High-Linearity Input Buffers for ADCs

Copyright © David Barros Leonardo, Faculty of Sciences and Technology, NOVA University Lisbon.

The Faculty of Sciences and Technology and the NOVA University Lisbon have the right, perpetual and without geographical boundaries, to file and publish this dissertation through printed copies reproduced on paper or on digital form, or by any other means known or that may be invented, and to disseminate through scientific repositories and admit its copying and distribution for non-commercial, educational or research purposes, as long as credit is given to the author and editor.

This document was created using the (pdf)  $\[MT_EX\]$  processor, based in the "novathesis" template[1], developed at the Dep. Informática of FCT-NOVA [2]. [1] https://github.com/joaomlourenco/novathesis [2] http://www.di.fct.unl.pt

### ACKNOWLEDGEMENTS

I would like to thank all the professors who were part of my academic path and who were kind enough to share some of their knowledge with me. I would like to give a special thanks to Professor Luís Oliveira for all the help given at the beginning of my master's degree and a huge thanks to Professor João Goes for having accepted to advise and to have advised me in this work.

I am thanking the people at Xilinx Ireland for the opportunity of an internship while working at my thesis. Special thanks to Vincent Callaghan, Bruno Vaz, Roswald Francis and Sohaib Afridi for their patience and will to teach me all of the important things for for my work there.

I will not forget my peers, friends and colleagues and their dedication, I would like to thank everyone who made me the person I am today. I would like to give special thanks to Francisco Matos, Diogo Pereira, Lucas Fioravanço and Clarisse Feio for all the support they gave me during my years in college and a special word for Miguel Calado for keeping my spirits high in the last stage of the thesis.

Finally, I would like to thank my parents, for all the work, effort and dedication that they have shown in all these years, and my little sister, for always being concerned with things that would never bother me.

## ABSTRACT

Nowadays on-chip Input Buffers (IBs) for direct conversion front-ends are realized with a higher voltage supply than that of the core voltage of the technology, mainly for linearity purposes. This, in turn, makes it mandatory to have more than one voltage source to supply a single chip in addition to having devices capable of handling higher voltages.

This work explores the possibility of having IBs supplied with the technology's core voltage to standardize all of the devices and reducing the different voltage supply sources and/or voltage regulators needed for operating the front-end drivers of the Analog to Digital Converters (ADCs).

A new input buffer architecture will be presented and compared to some prior input buffer implementations in the same conditions. This new architecture presents good linearity and bandwidth results and can be used for input buffers with the added benefit of not needing higher voltages nor special devices.

This new architecture is based off an existing one with another feedback loop to improved high-frequency peaking and linearity issues. This architecture achieves better results in bandwidth, a SNDR of 58 dB with and output voltage of 600 mV peak-to-peak differential. Furthermore, this buffer achieves a better efficiency linearity-wise when comparing to other buffers in the same conditions.

**Keywords:** ADC, Input Buffer, CMOS, High Linearity, High Bandwidth, Direct Conversion, Harmonic Distortion, Intermodulation Distortion.

## Resumo

Nos dias que correm, Input Buffers (IBs) para interfaces de alta frequência dos circuitos de conversão directa em receptores de áudio são alimentados com tensões superiores à tensão de alimentação nominal da tecnologia, principalmente por questões de linearidade. Isto obriga ao uso de várias fontes de tensão para alimentar um único *chip* bem como a utilização de transístores capazes de suportar maiores níveis de tensão.

Neste trabalho é explorada a possibilidade de usar IBs com tensão de alimentação nominal para uniformizar todos os transístores utilizados dentro de um projecto e diminuir a necessidade de mais do que um nível de tensão para a operação dos *drivers* dos Analog to Digital Converters (ADCs).

Será apresentada uma nova arquitectura e esta será comparada, nas mesmas condições, com várias implementações de *input buffer* existentes na literatura. Esta nova arquitectura apresenta bons resultados em termos de linearidade e largura de banda, podendo ser utilizada para projectos de alta frequência sem a necessidade de diferentes tipos de dispositivos ou diferentes níveis de tensão.

Esta nova arquitectura é baseada noutra acrescentando uma malha de realimentação para melhorar a linearidade e peakings na largura de banda a altas frequências. Esta arquitectura tem melhores resultados em termos de largura de banda, um SNDR de 58 dB com um sinal de saída com 600 mV pico-a-pico diferencial. Para além disto, este buffer é mais eficiente em termos de linearidade quando comparado com outros buffers nas mesmas condições.

**Palavras-chave:** ADC, *Input Buffer*, CMOS, Linearidade, Largura de Banda, Converão Directa, Distorção Harmónica, Distorção de Intemodulação.

## Contents

| Li                           | List of Figures xv  |                 |                                                      |     |  |

|------------------------------|---------------------|-----------------|------------------------------------------------------|-----|--|

| Li                           | List of Tables xvii |                 |                                                      |     |  |

| A                            | crony               | ms              |                                                      | xix |  |

| 1                            | Intr                | oductio         | on                                                   | 1   |  |

|                              | 1.1                 | Motiv           | ation and Background                                 | 1   |  |

|                              | 1.2                 | Object          | tives and Original Contribution                      | 4   |  |

|                              | 1.3                 | Thesis          | Organization                                         | 5   |  |

| 2 review of state-of-the-art |                     | tate-of-the-art | 7                                                    |     |  |

|                              | 2.1                 | Gener           | al Purpose Buffers                                   | 8   |  |

|                              |                     | 2.1.1           | Common Drain Input Buffer                            | 8   |  |

|                              |                     | 2.1.2           | Cascaded Source Follower Input Buffer                | 11  |  |

|                              |                     | 2.1.3           | Super Source Follower Input Buffer                   | 12  |  |

|                              |                     | 2.1.4           | Flipped Voltage Follower Input Buffer                | 13  |  |

|                              | 2.2                 | Input           | Buffers Design                                       | 13  |  |

|                              |                     | 2.2.1           | Differential Source Follower Input Buffer            | 13  |  |

|                              |                     | 2.2.2           | Differential Super Source Follower Input Buffer      | 14  |  |

|                              |                     | 2.2.3           | Input Buffer with Current Feedback                   | 15  |  |

|                              |                     | 2.2.4           | Push-Pull Input Buffer                               | 16  |  |

|                              |                     | 2.2.5           | Vgs-controlled Cascaded Source Follower Input Buffer | 17  |  |

|                              | 2.3                 | Other           | implementations                                      | 18  |  |

|                              |                     | 2.3.1           | BiCMOS solution                                      | 18  |  |

|                              | 2.4                 | Final t         | thoughts                                             | 19  |  |

| 3                            | Stuc                | dy and          | simulation of the voltage buffers                    | 21  |  |

|                              | 3.1                 | The P           | rocess Guidelines and Simulating Conditions          | 21  |  |

|                              | 3.2                 | Sizing          | -<br>;                                               | 22  |  |

|                              |                     | 3.2.1           | Sizing Main Buffer Transistors                       | 22  |  |

|                              |                     | 3.2.2           | Sizing Current Biasing Circuitry                     | 23  |  |

|                              |                     | 3.2.3           | Sizing Feedback                                      | 24  |  |

|   | 3.3  | Simulation testbench                                                      | 5 |

|---|------|---------------------------------------------------------------------------|---|

|   | 3.4  | Simulations setup and objectives 2                                        | 6 |

|   |      | 3.4.1 DC Simulation                                                       | 7 |

|   |      | 3.4.2 AC Simulation                                                       | 7 |

|   |      | 3.4.3 Transient-noise Simulation                                          | 7 |

| 4 | Ana  | ysis and Results of the state-of-the-art 2                                | 9 |

|   | 4.1  | Source Follower Input Buffer Analysis                                     | 9 |

|   |      | 4.1.1 DC Analysis (SF) 2                                                  | 9 |

|   |      | 4.1.2 AC Analysis (SF)                                                    | 0 |

|   |      | 4.1.3 Transient-noise Analysis (SF) 3                                     | 1 |

|   | 4.2  | Super Source Follower Input Buffer Analysis                               | 3 |

|   |      | 4.2.1 DC Analysis (SSF)                                                   | 3 |

|   |      | 4.2.2 AC Analysis (SSF)                                                   | 3 |

|   |      | 4.2.3 Transient-noise Analysis (SSF)                                      | 4 |

|   | 4.3  | Cascaded Source Follower Input Buffer Analysis 3                          | 6 |

|   |      | 4.3.1 DC Analysis (CSF)                                                   | 6 |

|   |      | 4.3.2 AC Analysis (CSF)                                                   | 7 |

|   |      | 4.3.3 Transient-noise Analysis (CSF) 3                                    | 7 |

|   | 4.4  | Current Feedback Input Buffer Analysis 3                                  | 9 |

|   |      | 4.4.1 DC Analysis (Current Feedback Input Buffer (Current Feedback IB)) 3 | 9 |

|   |      | 4.4.2 AC Analysis (Current Feedback IB)                                   | 0 |

|   |      | 4.4.3 Transient-noise Analysis (Current Feedback IB)                      | 1 |

|   | 4.5  | Vgs-controlled Cascaded Source Follower Input Buffer                      | 3 |

|   |      | 4.5.1 DC Analysis (Vgs-controlled Cascaded Source Follower (CSF) Input    |   |

|   |      | Buffer (IB))                                                              | 3 |

|   |      | 4.5.2 AC Analysis (Vgs-controlled CSF IB) 4                               | 3 |

|   |      | 4.5.3 Transient-noise Analysis (Vgs-controlled CSF IB)                    | 4 |

|   | 4.6  | Summary of all the analyses                                               | 6 |

| 5 | Prop | osed Architecture 4                                                       | 9 |

|   | 5.1  | Circuit Schematic and Proposed Idea                                       | 9 |

|   | 5.2  | DC Analysis                                                               | 0 |

|   | 5.3  | AC Analysis                                                               | 1 |

|   | 5.4  | Transient-noise Analysis 5                                                | 3 |

|   | 5.5  | Proposed Buffer with Improvements 5                                       | 6 |

|   |      | 5.5.1 DC Analysis                                                         | 7 |

|   |      | 5.5.2 AC Analysis                                                         | 8 |

|   |      | 5.5.3 Transient-noise Analysis                                            | 9 |

| 6 | Con  | clusion 6                                                                 | 5 |

|   | 6.1  | Final Comparisons                                                         | 5 |

| 6.2     | Final conclusion of the work | 68 |

|---------|------------------------------|----|

| Bibliog | raphy                        | 69 |

# List of Figures

| 1.1  | High level design of a direct-conversion Receiver System (Rx) comprising an | _  |

|------|-----------------------------------------------------------------------------|----|

|      | IB and an ADC.                                                              | 2  |

| 1.2  | High level representation (a) and implementation (b) of a buffer            | 3  |

| 1.3  | Basic common-drain topology [12].                                           | 3  |

| 2.1  | Source Follower Design.                                                     | 9  |

| 2.2  | Small-Signal equivalent with Ideal Current Source (no parasitic effects, no |    |

|      | body effect.)                                                               | 9  |

| 2.3  | Cascaded Source Follower Design.                                            | 11 |

| 2.4  | Super Source Follower.                                                      | 12 |

| 2.5  | Flipped Voltage Follower [20]                                               | 13 |

| 2.6  | Differential Source Follower IB [16].                                       | 14 |

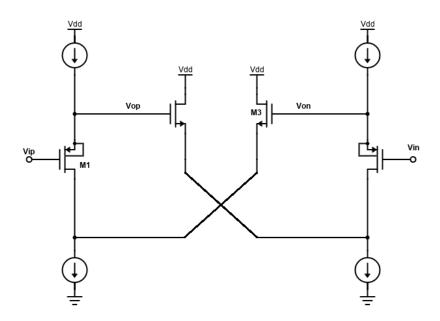

| 2.7  | Differential Super Source Follower IB [16]                                  | 15 |

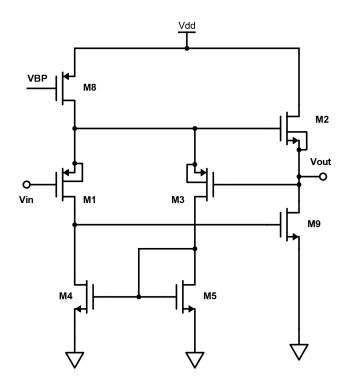

| 2.8  | Current Feedback Input Buffer.                                              | 16 |

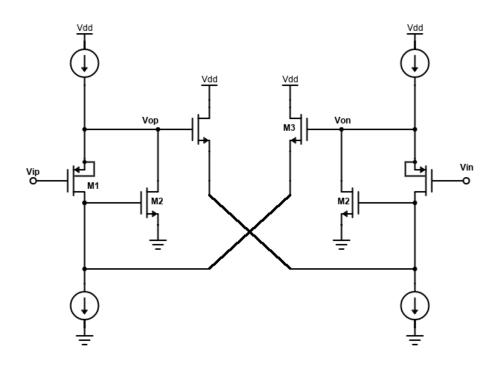

| 2.9  | Push-Pull Input Buffer [14].                                                | 17 |

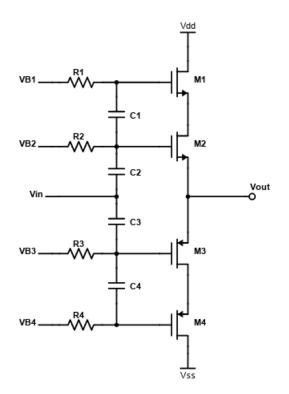

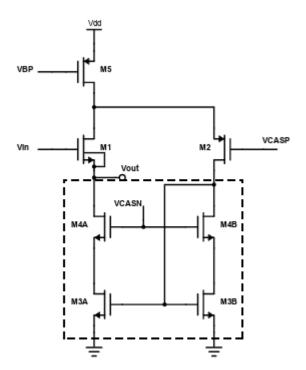

| 2.10 | Cascaded Source Follower with Vgs control [26].                             | 18 |

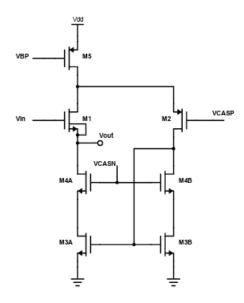

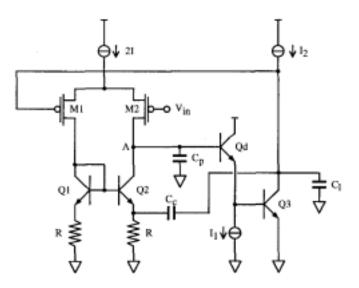

| 2.11 | BiCMOS PMOS input buffer [6]                                                | 19 |

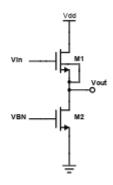

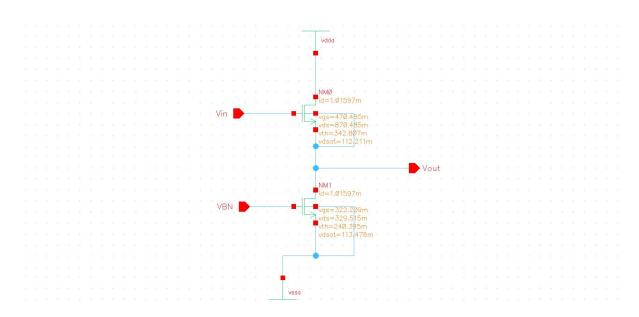

| 3.1  | Source Follower.                                                            | 22 |

| 3.2  | Current Feedback buffer (Current Mirror Feedback Highlighted)               | 24 |

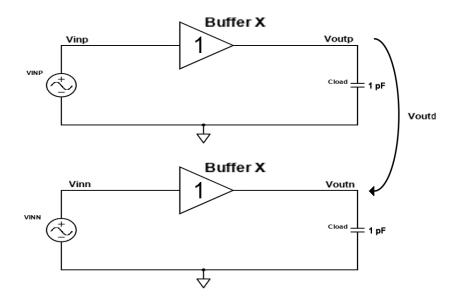

| 3.3  | Simulation testbench for all the simulated buffers.                         | 25 |

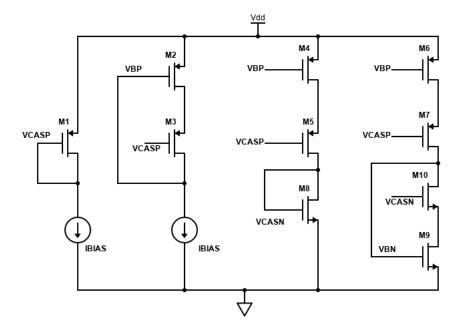

| 3.4  | Current Mirror used to BIAS all the simulated circuits                      | 26 |

| 4.1  | Source Follower DC Operating point.                                         | 30 |

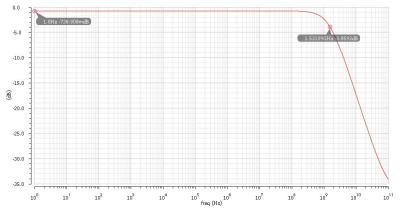

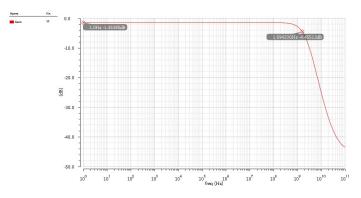

| 4.2  | Source Follower Frequency Response                                          | 30 |

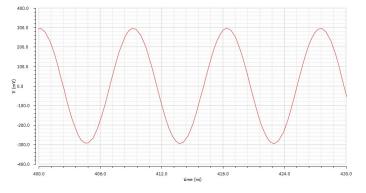

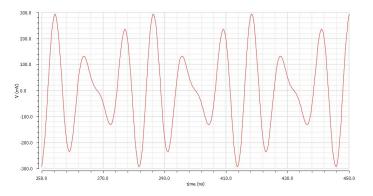

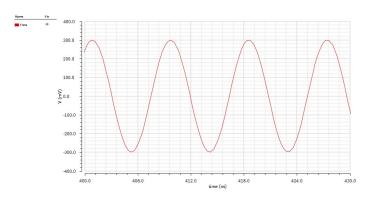

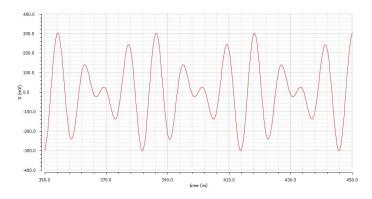

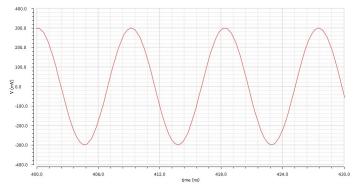

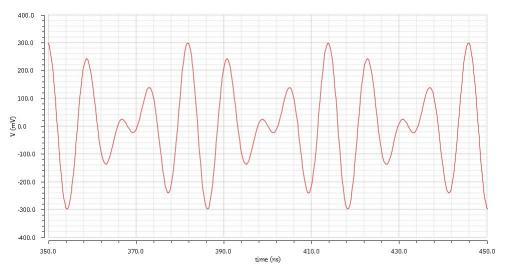

| 4.3  | Source Follower Output (time).                                              | 31 |

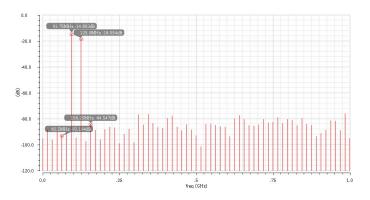

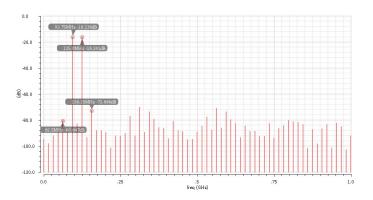

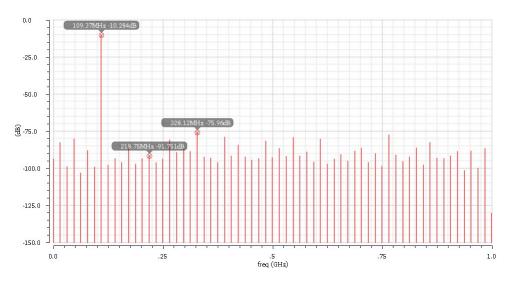

| 4.4  | Source Follower Output (frequency).                                         | 31 |

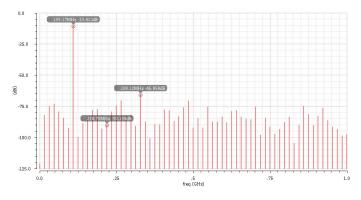

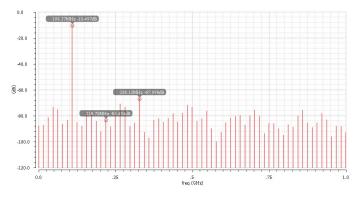

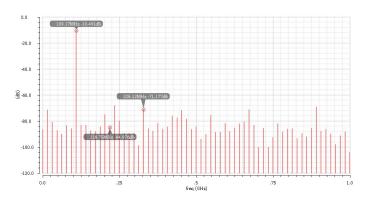

| 4.5  | Source Follower 2 Tone Analysis Output (time)                               | 32 |

| 4.6  | Source Follower 2 Tone Analysis Output (frequency)                          | 32 |

| 4.7  | Super Source Follower DC Operating point.                                   | 33 |

| 4.8  | Super Source Follower Frequency Response.                                   | 34 |

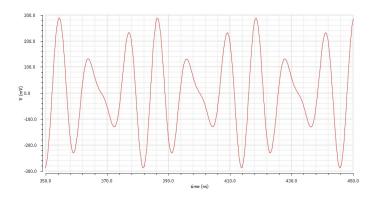

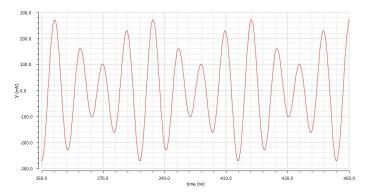

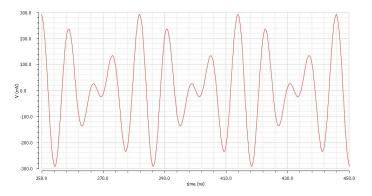

| 4.9  | Super Source Follower Output (time)                                         | 34 |

| 4.10 | Super Source Follower Output (frequency).                                   | 35 |

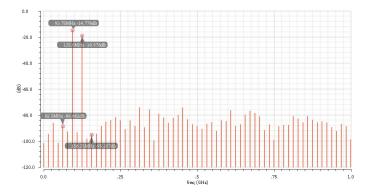

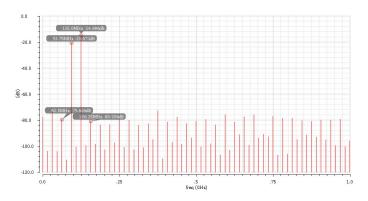

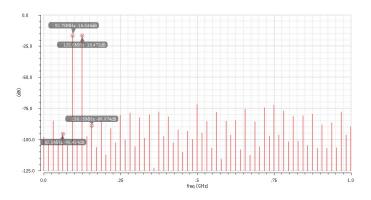

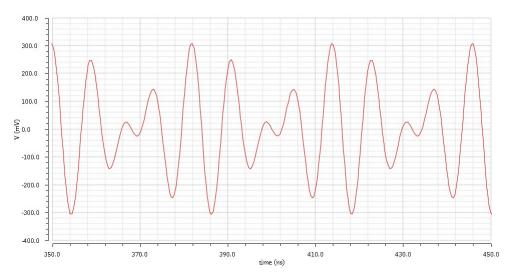

| 4.11                                                                                                                         | Super Source 2 Tone Analysis Follower Output (time).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

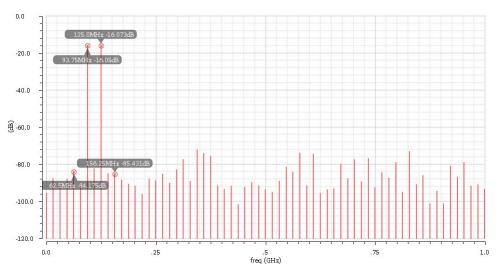

|                                                                                                                              | Super Source Follower 2 Tone Analysis Output (frequency).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35                                                                                                                                                                     |

|                                                                                                                              | Cascaded Source Follower DC Operating point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36                                                                                                                                                                     |

|                                                                                                                              | Cascaded Source Follower Frequency Response.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                                                                                                                     |

|                                                                                                                              | Cascaded Source Follower Output (time).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38                                                                                                                                                                     |

|                                                                                                                              | Cascaded Source Follower Output (frequency).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                                                                                                                     |

|                                                                                                                              | Cascaded Source Follower 2 Tone Analyse Output (time).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38                                                                                                                                                                     |

|                                                                                                                              | Cascaded Source Follower 2 Tone Analyse Output (frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                                                                                     |

|                                                                                                                              | Current Feedback IB DC Operating point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                     |

| 4.20                                                                                                                         | Current Feedback IB Frequency Response.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                     |

|                                                                                                                              | Current Feedback IB Output (time).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41                                                                                                                                                                     |

|                                                                                                                              | Current Feedback IB Output (frequency).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41                                                                                                                                                                     |

| 4.23                                                                                                                         | Current Feedback IB 2 Tone Analysis Output (time).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42                                                                                                                                                                     |

| 4.24                                                                                                                         | Current Feedback IB 2 Tone Analysis Output (frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                                                                                                                     |

| 4.25                                                                                                                         | Vgs-controlled CSF IB DC Operating point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43                                                                                                                                                                     |

| 4.26                                                                                                                         | Vgs-controlled CSF IB Frequency Response.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                                                                                                                                     |

| 4.27                                                                                                                         | Vgs-controlled CSF IB Output (time)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                                                                                                                     |

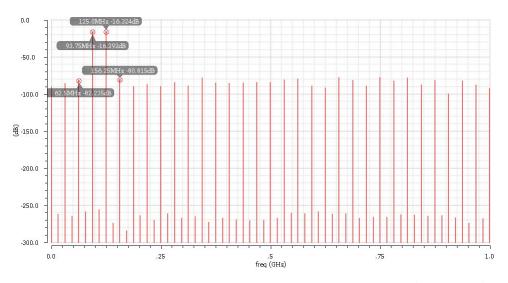

| 4.28                                                                                                                         | Vgs-controlled CSF IB Output (frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                                                                                     |

| 4.29                                                                                                                         | Vgs-controlled CSF IB 2 Tone Analysis Output (time).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                                                                                                                                                     |

| 4.30                                                                                                                         | Vgs-controlled CSF IB 2 Tone Analysis Output (frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                                                                                     |

|                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                        |

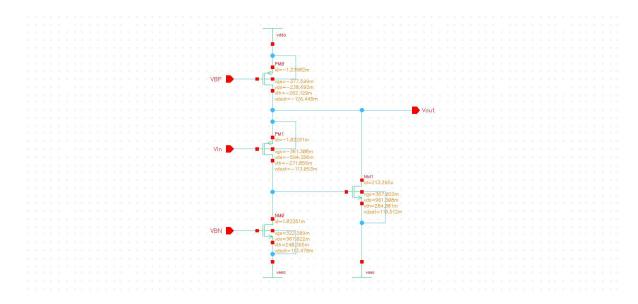

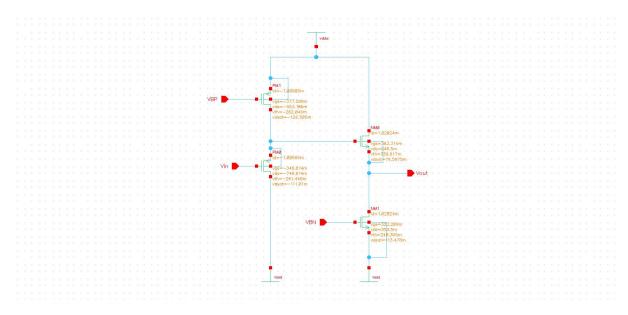

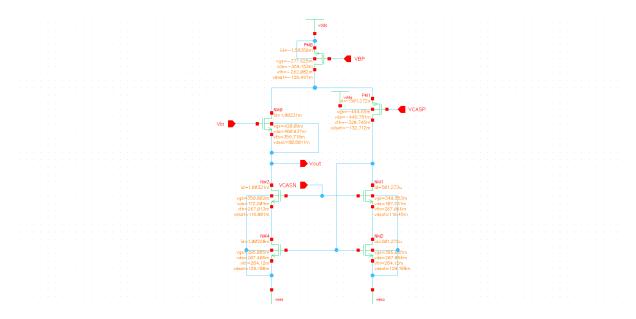

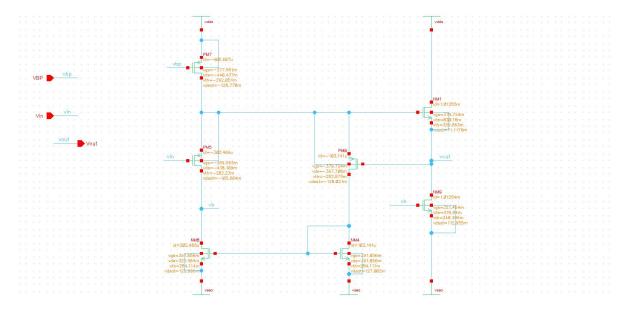

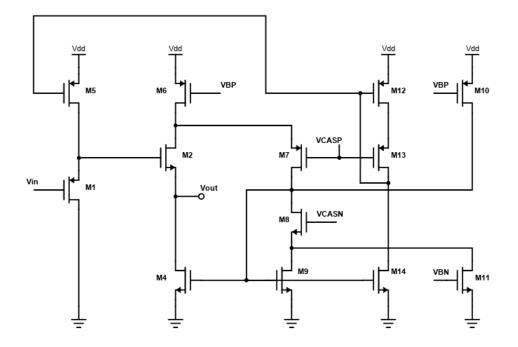

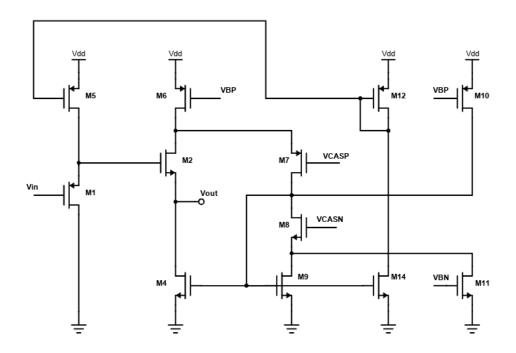

| 5.1                                                                                                                          | Proposed Input Buffer Architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50                                                                                                                                                                     |

| 5.1<br>5.2                                                                                                                   | Proposed Input Buffer Architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50<br>51                                                                                                                                                               |

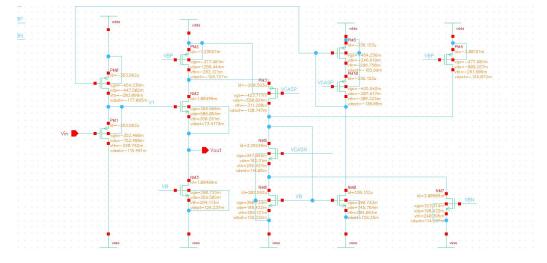

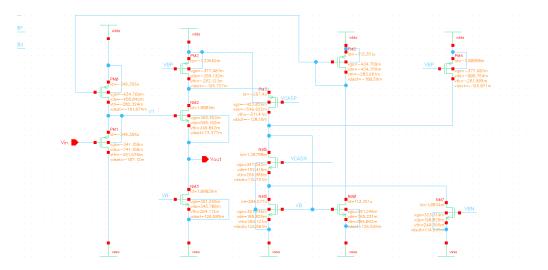

|                                                                                                                              | Operating point of proposed architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 5.2                                                                                                                          | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                                                                                                                     |

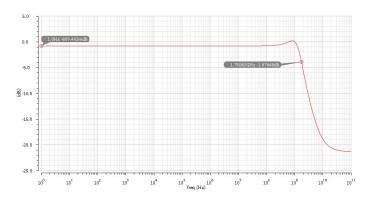

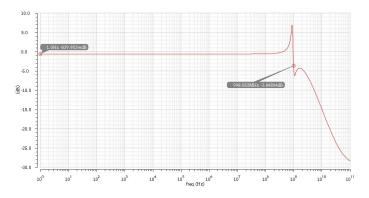

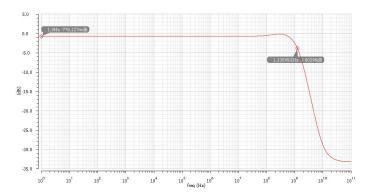

| 5.2<br>5.3                                                                                                                   | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>52                                                                                                                                                               |

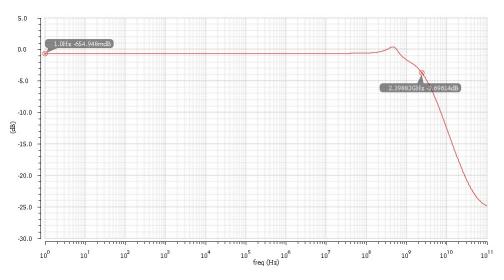

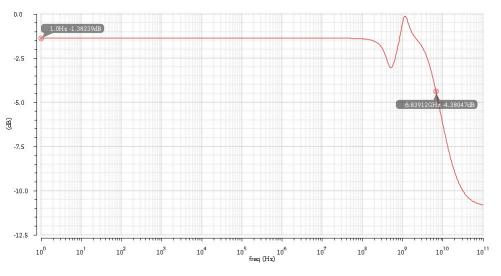

| 5.2<br>5.3<br>5.4                                                                                                            | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>52<br>52                                                                                                                                                         |

| 5.2<br>5.3<br>5.4<br>5.5                                                                                                     | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>52<br>52<br>53                                                                                                                                                   |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                              | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>52<br>52<br>53<br>53                                                                                                                                             |

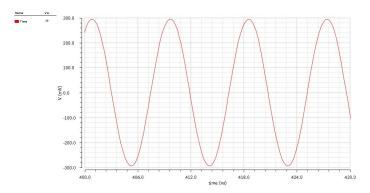

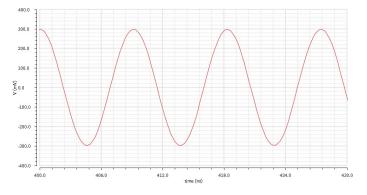

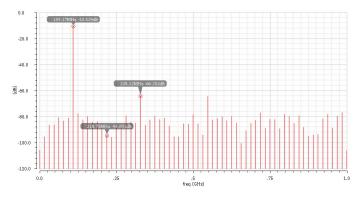

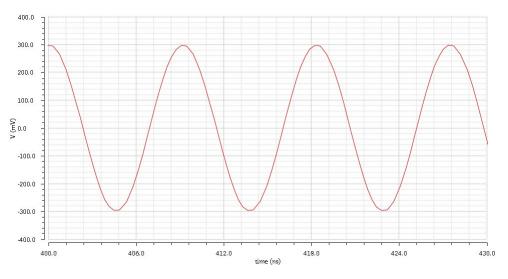

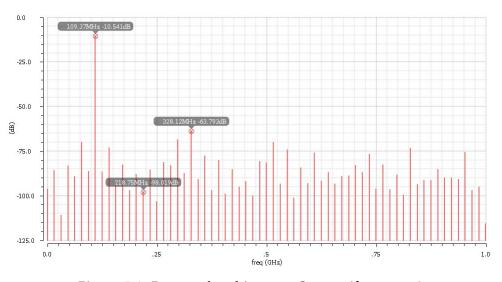

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                                       | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>52<br>53<br>53<br>54                                                                                                                                             |

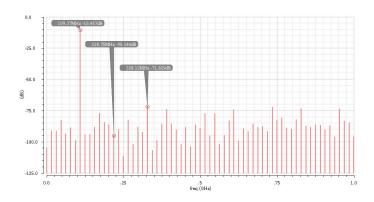

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> </ol>           | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).                                                                                                                                                                                                                                                                                                                                                                                                              | 51<br>52<br>53<br>53<br>54<br>54                                                                                                                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                                 | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).Proposed architecture 2 Tone Analysis Output (time).                                                                                                                                                                                                                                                                                                                                                          | 51<br>52<br>53<br>53<br>54<br>54<br>55                                                                                                                                 |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                         | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).Proposed architecture 2 Tone Analysis Output (frequency).Proposed architecture 2 Tone Analysis Output (frequency).                                                                                                                                                                                                                                                                                            | 51<br>52<br>53<br>53<br>54<br>54<br>55<br>55                                                                                                                           |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                                                 | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).Proposed architecture 2 Tone Analysis Output (time).Proposed Improved Input Buffer Architecture.                                                                                                                                                                                                                                                                                                              | 51<br>52<br>53<br>53<br>54<br>54<br>55<br>55<br>55                                                                                                                     |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                                         | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>52<br>53<br>53<br>54<br>54<br>55<br>55<br>55<br>55<br>56<br>57                                                                                                   |

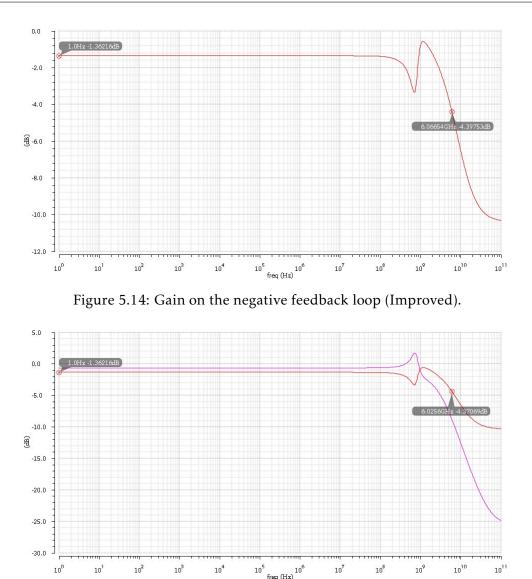

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14                                 | Operating point of proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>52<br>53<br>53<br>54<br>54<br>55<br>55<br>56<br>57<br>58                                                                                                         |

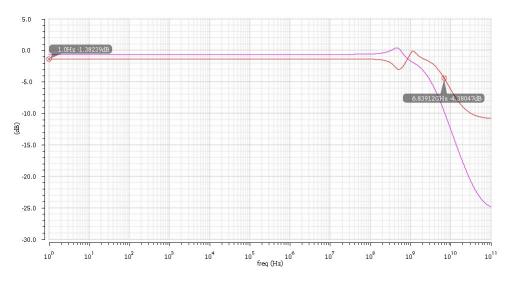

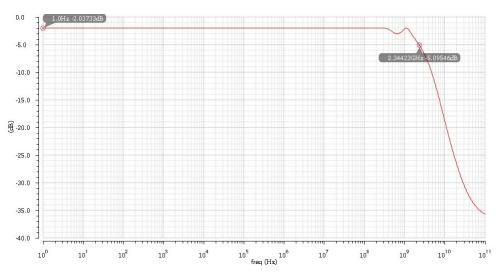

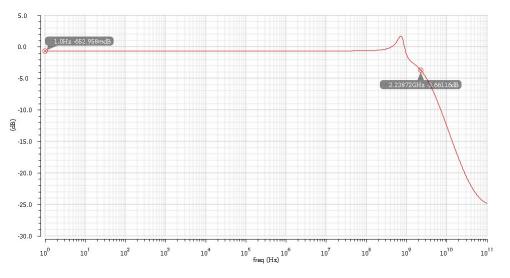

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15                         | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).Proposed architecture 2 Tone Analysis Output (time).Proposed architecture 2 Tone Analysis Output (frequency).Proposed Improved Input Buffer Architecture.Operating point of proposed improved input buffer architecture.Gain on the positive feedback loop (Improved).Gain on the negative feedback loop (Improved).                                                       | <ul> <li>51</li> <li>52</li> <li>53</li> <li>53</li> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> </ul>                                     |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16                 | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).Proposed architecture 2 Tone Analysis Output (time).Proposed architecture 2 Tone Analysis Output (frequency).Operating point of proposed improved input buffer architecture.Gain on the positive feedback loop (Improved).Gain on the negative feedback loop (Improved).Comparison between positive and negative feedback loop gains.                                                                         | <ul> <li>51</li> <li>52</li> <li>53</li> <li>53</li> <li>54</li> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> <li>59</li> </ul>             |

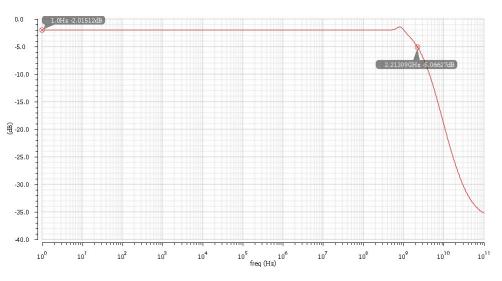

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17         | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).Proposed architecture 2 Tone Analysis Output (time).Proposed architecture 2 Tone Analysis Output (frequency).Proposed Improved Input Buffer Architecture.Operating point of proposed improved input buffer architecture.Gain on the positive feedback loop (Improved).Comparison between positive and negative feedback loop gains.Improved Architecture frequency gain. | <ul> <li>51</li> <li>52</li> <li>53</li> <li>53</li> <li>54</li> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> <li>50</li> <li>60</li> </ul> |

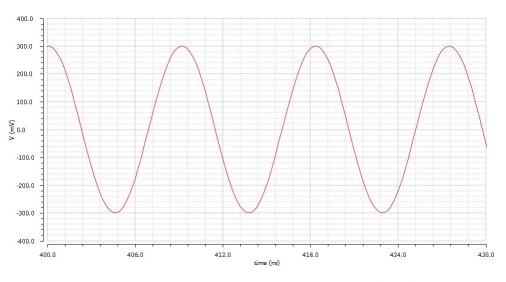

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18 | Operating point of proposed architecture.Gain on the positive feedback loop.Gain on the negative feedback loop.Comparison between positive and negative feedback loop gains.Proposed architecture frequency gain.Proposed architecture Output (time).Proposed architecture Output (frequency).Proposed architecture 2 Tone Analysis Output (time).Proposed Improved Input Buffer Architecture.Operating point of proposed improved input buffer architecture.Gain on the negative feedback loop (Improved).Comparison between positive and negative feedback loop gains.Improved Architecture frequency gain.Improved Architecture feedback loop (time).Improved Architecture feedback loop (time).         | <ul> <li>51</li> <li>52</li> <li>53</li> <li>53</li> <li>54</li> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> <li>60</li> <li>60</li> </ul> |

# LIST OF TABLES

| 3.1 | Specifications of the simulation.                                    | 21 |

|-----|----------------------------------------------------------------------|----|

| 3.2 | Buffer Transistors Sizing.                                           | 23 |

| 3.3 | Current Sources Sizing.                                              | 24 |

| 4.1 | Summary from the Source Follower Simulation Analysis.                | 32 |

| 4.2 | Summary from the Super Source Follower Simulation Analysis           | 35 |

| 4.3 | Summary from the Cascaded Source Follower Simulation Analysis        | 39 |

| 4.4 | Summary from the Current Feedback IB Simulation Analysis             | 42 |

| 4.5 | Summary from the Vgs-controlled CSF IB Simulation Analysis           | 45 |

| 4.6 | Comparison between tested designs analysis.                          | 46 |

| 5.1 | Summary from the Proposed Buffer Simulation Analysis.                | 55 |

| 5.2 | Summary from the Improved Buffer Simulation Analysis.                | 61 |

| 5.3 | Comparison between simulated designs analysis                        | 62 |

| 6.1 | Comparison between tested designs analysis.                          | 66 |

| 6.2 | Comparison between tested designs analysis (@ 1.08 V supply voltage) | 67 |

| 6.3 | Comparison between tested designs analysis (@ 1.32 V supply voltage) | 68 |

## ACRONYMS

| ADC                 | Analog to Digital Converter.                     |

|---------------------|--------------------------------------------------|

| BB                  | Baseband.                                        |

| BiCMOS              | Bipolar Complementary Metal Oxide Semiconductor. |

| BJT                 | Bipolar Junction Transistor.                     |

| BW                  | Bandwidth.                                       |

| CMOS                | Complementary Metal Oxide Semiconductor.         |

| CSF                 | Cascaded Source Follower.                        |

| Current Feedback IB | Current Feedback Input Buffer.                   |

| ENOB                | Effective Number of Bits.                        |

| FFT                 | Fast Fourier Transform.                          |

| FOM                 | Figure of Merit.                                 |

| FVF                 | Flipped Voltage Follower.                        |

| GBW                 | Product Gain Bandwidth.                          |

| HD2                 | 2 <sup>nd</sup> Harmonic Distortion.             |

| HD3                 | 3 <sup>rd</sup> Harmonic Distortion.             |

| HD5                 | 5 <sup>th</sup> Harmonic Distortion.             |

| I/Q                 | Inphase/Quadrature.                              |

| IB                  | Input Buffer.                                    |

| IF                  | Intermediate Frequency.                          |

| IM3                 | 3 <sup>rd</sup> order Inter-Modulation.          |

| KCL                 | Kirchhoff's Current Law.                         |

| LNA                 | Low Noise Amplifier.                             |

#### ACRONYMS

| MOS<br>MSAAC | Metal Oxide Semiconductor.<br>Matlab tool for Symbolic Analysis of Analog Circuits. |

|--------------|-------------------------------------------------------------------------------------|

| NMOS         | N-channel Metal Oxide Semiconductor.                                                |

| OpAmp<br>OTA | Operational Amplifier.<br>Operational Transconductance Amplifier.                   |

| PMOS         | P-channel Metal Oxide Semiconductor.                                                |

| RF           | Radio Frequency.                                                                    |

| SC           | Sampling-Capacitor.                                                                 |

| SF           | Source Follower.                                                                    |

| SFDR         | Spurious-Free Dynamic Range.                                                        |

| SNDR         | Signal to Noise and Distortion Ratio.                                               |

| SNR          | Signal to Noise Ratio.                                                              |

| SSF          | Super Source Follower.                                                              |

| TF           | Transfer Function.                                                                  |

| TH           | Track-and-Hold.                                                                     |

| THD          | Total Harmonic Distortion.                                                          |

|              |                                                                                     |

| VCMI         | Input Common-Mode Voltage.                                                          |

## INTRODUCTION

This Chapter provides the motivation and purpose for this project. It points out the main features of Input Buffers (IBs) and the challenges of its design. Finally, it presents the organization of this thesis and its main contributions.

### 1.1 Motivation and Background

Nowadays, most signal processing operations are done in the digital domain, implying the necessity of having Analog to Digital Converters (ADCs) serving as an A/D interface between the physical world and the digital world.

For this reason, ADCs have increased the sampling rate, improving the maximum allowed Bandwidth (BW) of the input signal, converting signals directly from Radio Frequency (RF). This is a practice to either reduce or eliminate the need for analog mixers and complex filters. We make these operations in the digital domain with the help of software.

Presently, the ADC is closer to the antenna on receiver systems. As a result, this kind of RF ADCs must be able to convert signals with frequencies in the GHz range. Besides the intrinsic speed necessary of the ADC, these conversions come with another level of complexity since the Low Noise Amplifier (LNA) might not be able to drive the ADC without rising significantly the power dissipation of the receiving system.

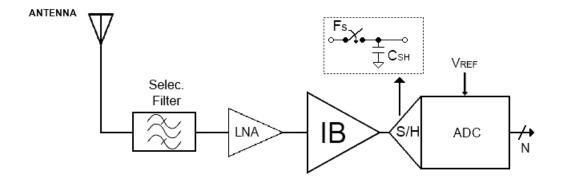

The driving of the RF ADCs is done by analog buffers, as shown in figure 1.1. This block drives the ADC without changing the input signal, serving as an interface between the LNA and the ADC, making those blocks independent of each other. A good buffer should have the following specifications:

- high linearity, so that it does not alter input signal properties;

- high bandwidth, because the input signal should be at RF range;

- low output resistance, so that it can drive the ADC;

- high input impedance, to limit the influence in the input signal;

- low power dissipation targeting handset applications;

- low footprint (area) for reducing cost.

Figure 1.1: High level design of a direct-conversion Receiver System (Rx) comprising an IB and an ADC.

Figure 1.1 represents the direct-conversion front-end architecture. The direct-conversion is becoming more relevant for its advantages [11]. These advantages include flexibility, power dissipation, reduced system complexity and reduced weight [7, 10, 11]. The down-conversion process is done in the digital domain [10] and the Inphase/Quadrature (I/Q) demodulator can be replace by just one ADC while the demodulation is done in the digital domain [11].

The LNA on the figure is mandatory for impedance matching of the antenna. As stated earlier, the input buffer input impedance is desired to be with an high value. This block connects to the antenna (or the selection filter in the figure) and determines the performance of the receiver [2]. The LNA is supposed to amplify the input signal with the minimum noise figure possible [1] while achieving an input impedance matching in all of the signal bandwidth of 50  $\Omega$  [1, 2] to minimize any influence on the receiving signal [3]. Usually this amplifier is done with a common gate or common source configuration [23].

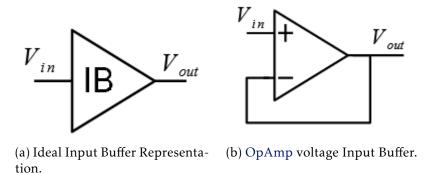

An ideal voltage buffer (figure 1.2 a) serves as an interface between two distinct circuits to eliminate any influence that they can have on one another. Meaning that the input impedance should be high, and the output impedance should be zero so that the buffer would be capable of driving whichever load [19], while achieving good linearity [13]. An Operational Amplifier (OpAmp) in unity gain configuration (figure 1.2 b) can implement an ideal voltage buffer.

Figure 1.2: High level representation (a) and implementation (b) of a buffer.

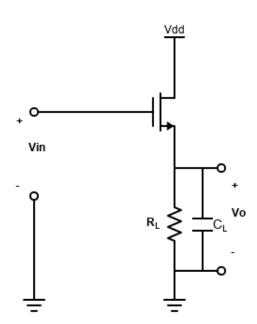

Traditionally the most common voltage buffer is the well-known source-follower (Complementary Metal Oxide Semiconductor (CMOS) transistor in common-drain configuration) shown in figure 1.3, but with some studies, there have been new designs that implement different buffers with different strengths, that are efficient for some applications.

Figure 1.3: Basic common-drain topology [12].

Perfect analog unity buffers can be described as circuits characterized by a Transfer Function (TF) = 1, meaning that the output is a replica of the input. Typically the gain, defined by the ratio between the output signal and the input signal, is a ratio between 2 expressions. In voltage buffers, usually, there are some similarities between the numerator and the denominator. If both terms are equal then we have a perfect unity voltage buffer.

Let's imagine that a buffer's TF is determined by

$$\frac{g_m + s \cdot C_{gs}}{g_m + s \cdot \left(C_{gs} + C_{gd}\right)} \tag{1.1}$$

where we see similarities between the numerator and denominator. If the equation (1.1) is rearranged to

$$\frac{g_m + s \cdot C_{gs}}{\left[g_m + s \cdot C_{gs}\right] + s \cdot C_{gd}} \tag{1.2}$$

then the similarities are much easier to perceive. If in equation (1.2) we substitute the numerator by *B* and the remaining of the denominator by *C* we can simplify the expression as

$$\frac{B}{B+C}.$$

(1.3)

emphasizing the problem of analog buffers. Term *C* is the difference between a real buffer and an ideal perfect buffer. In a perfect buffer C = 0, which makes equation (1.3) = 1, for this reason  $\frac{C}{B}$  is sometimes called follow-up error (*FE*) meaning the error that takes the buffer away from the ideal unitary buffer. However, the description of *C* is valuable in a real voltage buffer to check how it behaves and how it differs from a perfect buffer with different frequency ranges.

Since the perfect unity voltage buffer is not achievable, the perfect topology for this building-block does not exist. Usually, each case uses one architecture that satisfies the need for each implementation. The main differences rely on optimizing the buffer in some specifications and compare this new design with others in terms of simplicity, linearity, and power consumption. There are, however, some topologies that, instead of trying to achieve a unity gain, ultimately try to achieve higher gains to limit the need for extra gain blocks in the signal path.

## 1.2 Objectives and Original Contribution

The first objective of this thesis is to study, simulate, and compare different input voltage buffer designs already described in the literature. It will examine the ability of these buffers to work at high speed with a load of 1 pF with a voltage supply of 1.2 V, for 130 nm technology.

The second objective is to propose a new buffer design and do the same tests and simulations to compare its performance with the state-of-the-art input buffers.

This thesis presents a new functional buffer design described in chapter 5. This architecture will be explained, with all the considerations taken into account. The proposed new buffer achieves superior performance when compared with the state-of-the-art. Regarding this new architecture, a paper was submitted to ISCAS 2021 with the authorship of David Leonardo, João Goes and João Melo.

## **1.3 Thesis Organization**

This work is organized as follows.

In chapter 2 is described as a general idea about voltage buffer designs. It will show some architectures already published in the literature, deriving their transfer function and some thoughts about each buffer.

In chapter 3 there will be presented the systematic buffer simulation analysis. It will show the simulation guidelines that every simulation followed, both in technology, capacitive load, and sizing of the devices. Furthermore, it explains all the simulations done and what can be expected to extract from them.

In chapter 4 the simulation results of some of the voltage input buffers, presented in chapter 2, will be shown. Here, it will be possible to see how each design in previous works compares to each other when carried out the same analysis.

In chapter 5 a new IB architecture will be presented and studied with the same type of simulations that every other buffer. The same chapter provides an in-depth analysis of the new architecture and an improvement to the design.

In chapter 6 will be drawn some conclusions about the work. This final chapter will reinforce the comparisons between all the buffers, concluding the best performances between all the designs.

Снартек

### **REVIEW OF STATE-OF-THE-ART**

Analog voltage buffers were used for quite some time as output stages of gain blocks, like Operational Amplifiers (OpAmps) [8, 17, 27], since the gain block first stages' output impedance was high and was hard to drive whatever circuitry implemented after the block. High output impedance would degrade the performance of the circuit comprised of this block. By implementing a last-stage common-drain class A, B, or AB output buffer, the output impedance lowers and the block can drive circuits with more ease. Also, this output stage isolates the gain stages from the load effects.

Nowadays, analog buffers are used for different applications. With the need to downconvert signals from RF into Baseband (BB) the buffers are used as an isolator from the effects that come from analog designs like mixers (that could kickback large signals that could influence the LNA). Eventually, the analog mixer can be removed from the receiving chain and the ADC can move closer to the antenna. Now, the problem is that the frontend Track-and-Hold (TH) circuit that samples the input signal to be quantized by the ADC can be a source of interference and have quite low switched impedance. Therefore, an input buffer is used as an interface between the input signal and the ADC.

The input buffer needs to isolate the input from the Sampling-Capacitor (SC) sampling stage of the ADC while maintaining to feed the input signal to the ADC with low distortion. However, this can be difficult to implement as most of the buffers comprise non-linear devices. The non-linearities of the input buffer severely impact the performance of the ADC.

Bearing this in mind, the design of Input Buffer (IB) must follow the specification of the ADC to minimize the effect of the buffer on the overall ADC dynamic performance. An input buffer must not just have a high input bandwidth with unity-gain, but also have high enough Signal to Noise Ratio (SNR), Signal to Noise and Distortion Ratio (SNDR), Spurious-Free Dynamic Range (SFDR), as well as enough Effective Number of Bits (ENOB)

to allow driving a moderate to high effective resolution ADC.

This chapter describes several buffer projects in the literature as well as an analysis of the transfer function of most of these projects. Since some designs are difficult to analyze by hand, it was used the Matlab tool for Symbolic Analysis of Analog Circuits (MSAAC) toolbox. MSAAC mainly uses a netlist to derive the transfer function of the circuit - within a given error.

It is taken into consideration that some of the designs can be used for a multitude of tasks. As such, they will be shown in the first section as general-purpose designs. Then it is shown some of the buffers already designed to implement IB for properly driving ADC.

## 2.1 General Purpose Buffers

Generally, buffers can be used either to interface between circuits or to limit the influence of a part of the circuit in whatever comes next. For this reason, traditionally, voltage buffers have been used as the last stage of amplifiers, so that the output resistance of the amplifier circuit is low and to achieve higher speed. This section shows some possibility of voltage buffers that can be readily used as input buffers for driving ADCs but due to their simplicity, they are versatile for other applications.

#### 2.1.1 Common Drain Input Buffer

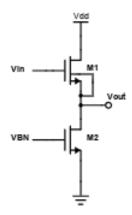

The classic Source Follower (SF) topology, figure 2.1, can be used as one of the main building-blocks of current mirrors, differential Operational Transconductance Amplifiers (OTAs), and class AB output-stage [8], as well as, interfacing with a front-end for ADC.

Due to its simplicity, the common-drain configuration is the first design option for voltage buffers. The output voltage extracted on the source of a CMOS transistor is almost a perfect copy of its gate voltage, aside for the  $V_{gs}$  [12]. This fact makes this circuit a simple yet effective voltage buffer when nominal power-supply is not a big concern (e.g.  $V_{DD} \ge 1.8 \text{ V}$ ).

A CMOS implementation ensures a minimum input current [6] since the input resistance is defined by the input impedance of the gate of a transistor.

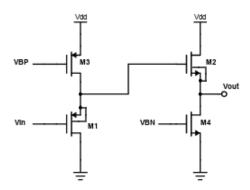

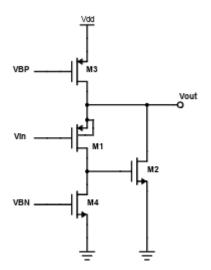

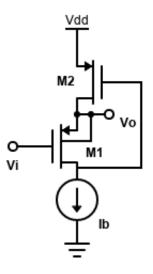

Figure 2.1: Source Follower Design.

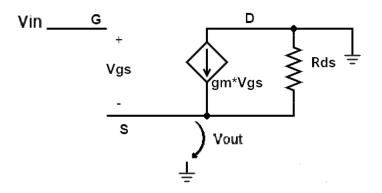

Ignoring the body effect and the parasitic capacitances (low-frequency model) and assuming M2 as an ideal current source, figure 2.2 represents the small-signal equivalent of figure 2.1. With this, it is possible to extract an approximated TF of the SF.

Figure 2.2: Small-Signal equivalent with Ideal Current Source (no parasitic effects, no body effect.)

By inspection on figure 2.2, it is possible to obtain an equation that relates  $v_{in}$  and  $v_{gs}$ ,

$$v_{gs1} = v_{in} - v_{out},$$

(2.1)

as well as apply the Kirchhoff's Current Law (KCL) to the drain node to obtain another equation that relates  $v_{gs}$  and  $v_{out}$

$$v_{out} \cdot R_{ds1} = g_{m1} * v_{gs1}. \tag{2.2}$$

By rearranging equation (2.2) and replacing  $R_{ds1}$  for  $\frac{1}{g_{ds1}}$  it can be written

$$v_{out} = \frac{g_{m1}}{g_{ds1}} \cdot v_{gs1},\tag{2.3}$$

#### if (2.1) is substituted in (2.3) then

$$v_{out} = \frac{g_{m1}}{g_{ds1}} \cdot (v_{in} - v_{out}), \qquad (2.4)$$

where by extracting  $\frac{v_{out}}{v_{in}}$  from (2.4) we get the familiar gain expression,

$$\frac{v_{out}}{v_{in}} = \frac{\frac{g_{m1}}{g_{ds1}}}{\frac{g_{m1}}{g_{ds1}} + 1}.$$

(2.5)

If the intrinsic gain  $\frac{g_{m1}}{g_{ds1}}$  is far larger than 1, then (2.5) could be written as  $\frac{v_{out}}{v_{in}} \approx 1$ , which is the ideal buffer. Note, however, that even the SF doesn't have gain of 0 dB, but it can be approximately that.

The previous study was done without considering any parasitic effects to simplify the calculations. However, these should be taken into account since the purpose of this work is to design high bandwidth buffers. Therefore, it is important to assume the parasitic effects and find out their impact on the bandwidth. Taking into consideration some of these effects, the transfer function of the SF can be described as

$$TF = \frac{g_{m1} + s \cdot C_{gs1}}{g_{m1} + g_{ds1} + g_{ds2} + s \cdot (C_{gd2} + C_{gs1})}$$

(2.6)

that even without much error (2.6) can still be approximated to a unity gain TF if  $g_m >> g_{ds}$ and  $C_{gs} >> C_{gd}$ . However, as frequency increases, the effect of  $C_{gd2}$  becomes stronger and it limits the useful bandwidth of the buffer.

This design (Figure 2.1), however, has some limitations that were analyzed and optimized in different studies. Limitations in the output resistance have been studied in [9, 12, 18]. Linearity issues with this design were studied in [21, 25], as well as studies to try and overcome the offset at the output [9].

One of the major problems with this topology is the non-linearity that comes with a lack of isolation of just a single transistor [21] and the strong dependence of  $v_{gs}$  regarding signal variations.

On another note, even though this configuration theoretically has the lowest output resistance of all the three single transistor configurations, the output resistance ( $R_o$ ) is roughly around 1/gm, in [12, 22] the output resistance is calculated to be

$$R_{out} = \frac{1}{g_m + g_{mb}} || R_L, \tag{2.7}$$

where  $R_{out}$  is the output resistance, gm is the intrinsic gain of the device,  $R_L$  is the load of the buffer and  $g_{mb}$  represents the body-effect transconductance. This value can be around some k $\Omega$  and thus may be higher than expected. This makes it necessary to increase the bias current and increase the aspect ratio  $\frac{W}{L}$ , increasing the power dissipation and the area of the buffer [16].

#### 2.1.2 Cascaded Source Follower Input Buffer

One of the issues associated with the simple source follower is the DC level shifting. This can be more or less problematic depending on each specific problem and application.