Aalborg Universitet

#### Adaptive Lightweight Compression Acceleration on Hybrid CPU-FPGA System

Jahan Lisa, Nusrat

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Jahan Lisa, N. (2020). Adaptive Lightweight Compression Acceleration on Hybrid CPU-FPGA System. Aalborg Universitetsforlag. Ph.d.-serien for Det Ingeniør- og Naturvidenskabelige Fakultet, Aalborg Universitet

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# ADAPTIVE LIGHTWEIGHT COMPRESSION ACCELERATION ON HYBRID CPU-FPGA SYSTEM

BY NUSRAT JAHAN LISA

**DISSERTATION SUBMITTED 2020**

# Adaptive Lightweight Compression Acceleration on Hybrid CPU-FPGA System

Dissertation

submitted October 26, 2020

by **M.Sc. Nusrat Jahan Lisa** born June 7, 1985 in Dhaka, Bangladesh

at Technische Universität Dresden and Aalborg University

Supervisors: Prof. Dr.-Ing. Wolfgang Lehner Prof. Torben Bach Pedersen

| Dissertation submitted:                                 | October 2020                                                          |

|---------------------------------------------------------|-----------------------------------------------------------------------|

| PhD supervisor:                                         | Professor Torben Bach Pedersen<br>Aalborg University                  |

| PhD committee:                                          | Associate Professor Gabriela Montoya (chairman)<br>Aalborg University |

|                                                         | Professor Gunter Saake<br>University of Magdeburg                     |

|                                                         | Professor Kai-Uwe Sattler<br>Technical University of Ilmenau          |

| PhD Series:                                             | Technical Faculty of IT and Design, Aalborg University                |

| Institut:                                               | Department of Computer Science                                        |

| ISSN (online): 2446-1628<br>ISBN (online): 978-87-7210- | -833-9                                                                |

Published by: Aalborg University Press Kroghstræde 3 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Nusrat Jahan Lisa

Printed in Denmark by Rosendahls, 2020

## **THESIS DETAILS**

| Thesis Title:  | Adaptive Lightweight Compression Acceleration on Hybrid      |  |

|----------------|--------------------------------------------------------------|--|

|                | CPU-FPGA System                                              |  |

| Ph.D. Student: | Nusrat Jahan Lisa                                            |  |

| Supervisors:   | Prof. DrIng. Wolfgang Lehner, Technische Universität Dresder |  |

| _              | Prof. Torben Bach Pedersen, Aalborg University               |  |

This thesis consists of the following peer-reviewed and published papers.

- 1. Nusrat Jahan Lisa, Annett Ungethüm, Dirk Habich, Wolfgang Lehner, Tuan D. A. Nguyen, and Akash Kumar. Column scan acceleration in hybrid CPU-FPGA systems. In Rajesh Bordawekar and Tirthankar Lahiri, editors, *International Workshop on Accelerating Analytics and Data Management Systems Using Modern Processor and Storage Architectures, ADMS@VLDB 2018, Rio de Janeiro, Brazil, August 27, 2018*, pages 22–33, 2018. [*Relates to Chapter 3*]

- 2. Nusrat Jahan Lisa, Annett Ungethüm, Dirk Habich, Tuan D. A. Nguyen, Akash Kumar, and Wolfgang Lehner. Column scan optimization by increasing intra-instruction parallelism. In *DATA*, pages 344–353. SciTePress, 2018. [*Relates to Chapter 3*]

- 3. Nusrat Jahan Lisa, Annett Ungethüm, Dirk Habich, Wolfgang Lehner, Tuan Duy Anh Nguyen, and Akash Kumar. FPGA vs. SIMD: comparison for main memory-based fast column scan. In Christoph Quix and Jorge Bernardino, editors, *Data Management Technologies and Applications 7th International Conference, DATA 2018, Porto, Portugal, July 26-28, 2018, Revised Selected Papers,* volume 862 of *Communications in Computer and Information Science,* pages 116–140. Springer, 2018. [Relates to Chapter 3]

- 4. Nusrat Jahan Lisa, Tuan Duy Anh Nguyen, Dirk Habich, Akash Kumar, and Wolfgang Lehner. High-throughput bitpacking compression. In 22nd Euromicro Conference on Digital System Design, DSD 2019, Kallithea, Greece, August 28-30, 2019, pages 643–646. IEEE, 2019. [Relates to Chapter 4]

- 5. Nusrat Jahan Lisa, Dirk Habich, Wolfgang Lehner, Akash Kumar, and Torben Bach Pedersen. Adaptive Lightweight Integer Compression on FPGA. In preparation for submission to the journal *IEEE Embedded Systems Letters*. *[Relates to Chapter 4]*

This thesis has been submitted for assessment in partial fulfillment of the joint Ph.D. degree. The thesis is based on the published scientific papers which are listed above. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Technical Doctoral School of IT and Design at Aalborg University and the Faculty of Computer Science at Technische Universität Dresden.

# ABSTRACT

With an increasingly large amount of data being collected in numerous application areas, the importance of online analytical processing (OLAP) workloads increases constantly. OLAP queries typically access only a small number of columns but a high number of rows and are, thus, most efficiently executed by column-stores. With the significant developments in the main memory domain even large datasets can be entirely held in the main memory. Thus, main memory column-stores have been established as state-of-the-art for OLAP scenarios. In these systems, all values of every column are encoded as a sequence of integer values and, thus, query processing is completely done on these integer sequences. To improve query processing, vectorization based the Single Instruction Multiple Data (SIMD) parallel paradigm is a state-of-the-art technique. Aside from vectorization, lightweight integer compression algorithms also play an important role to reduce the necessary memory space. Unfortunately, there is no single-best lightweight integer compression algorithm, and the algorithm selection decision depends most importantly on the data characteristics. Nevertheless, vectorization and integer compression complement each other, and the combined usage improves the query Unfortunately, the benefits of vectorization are limited on modern performance. x86-processors due to predefined and fixed SIMD instruction set extensions. Nowadays, the Field Programmable Gate Array (FPGA) offers a novel opportunity with regard to hardware reconfigurable capability. For example, we can use an arbitrary length of processor word in FPGA leading to a higher performance, we can prepare proper pipeline-based custom-made database accelerators, and we can develop embedded systems through utilizing such accelerators. Moreover, modern hybrid CPU-FPGA systems have a direct data communication channel between the main memory and FPGA which is useful for throughput acceleration. Based on these advantages, this thesis examines the utilization of FPGA for main memory column-stores. This examination is two-fold. First, we investigate the column *scan* on compressed data as important operation and second, we systematically look at lightweight integer *compression*. These two aspects are considered from the hardware perspective to guarantee a certain level of query performance acceleration. In particular, this thesis explores different embedded design options and proposes an adaptive lightweight integer compression system. Based on a comprehensive evaluation, we find out the optimal design constraint as per implementation mechanism for column scan and lightweight integer compression. Finally, we conclude this thesis by mentioning our upcoming research activities.

### **KURZZUSAMMENFASSUNG (ABSTRACT IN GERMAN)**

Die Bedeutung von analytischen Anfragen im Sinne des Online Analytical Processing (OLAP) im Datenbankumfeld nimmt stetig zu, da in zahlreichen Anwendungsbereichen von der Wissenschaft bis zur Industrie immer größere Datenmengen gesammelt werden. Um aus diesen immensen Datenmengen die notwendigen Informationen zu extrahieren, ist es notwendig, eine Vielzahl komplexer analytischer Aufgaben Derartige komplexe Analysen speisen sich normalerweise aus auszuführen. einer zwar kleinen Anzahl von Attributen (Spalten) aber einer hohen Anzahl von Zeilen und werden daher am effizientesten mit Hilfe von spaltenorientierten Datenbanksystemen verwaltet und verarbeitet. Durch die signifikante Vergrößerung der Hauptspeicherkapazitäten im Laufe des letzten Jahrzehnts können mittlerweile große Datensätze vollständig im Hauptspeicher gespeichert werden. Daher sind hauptspeicherzentrische spaltenorientierte Datenbanksysteme Stand der Technik für OLAP-Anwendungen. In diesen Systemen werden alle Werte jeder Spalte als eine Folge von ganzzahligen Werten im Hauptspeicher codiert und die Abfrageverarbeitung erfolgt vollständig auf diesen ganzzahligen Folgen. Um die Effizienz der Abfrageverarbeitung zu verbessern, ist Vektorisierung auf der Basis des parallelen Paradigmas SIMD (Single Instruction Multiple Data) in diesen Systemen von entscheidender Bedeutung. Neben der Vektorisierung spielen auch einfache Ganzzahlkomprimierungsalgorithmen zur Reduzierung des erforderlichen Speicherplatzes eine wichtige Rolle. Leider gibt es keinen optimalen Komprimierungsalgorithmus für Ganzzahlen und die Entscheidung für einen Algorithmus hängt primär von den Dateneigenschaften ab. Trotzdem ergänzen sich Vektorisierung und Ganzzahlkomprimierung, so dass die gezielte Verwendung die Effizienz der Anfrageverarbeitung verbessert. Leider sind die Vorteile der Vektorisierung bei modernen x86-Prozessoren aufgrund vordefinierter und fester Befehlssatzerweiterungen von SIMD begrenzt. Heutzutage bietet aber das Field Programmable Gate Array (FPGA) eine neuartige Möglichkeit hinsichtlich der Hardware-Rekonfigurierbarkeit an. Zum Beispiel können beliebige Längen von Prozessorwörtern in FPGA realisiert werden, was zu einer höheren Leistung führt. Darauf aufbauend können spezifische Pipeline-basierte Datenbankbeschleuniger eingebettet werden. Darüber hinaus verfügen moderne hybride CPU-FPGA-Systeme über einen direkten Datenkommunikationskanal zwischen dem Hauptspeicher der CPU und dem FPGA, was für die Durchsatzbeschleunigung wichtig ist. Hierauf aufbauend untersucht diese Arbeit die Verwendung von FPGA für hauptspeicherzentrische spaltenorientierte Datenbanksysteme und konzentriert sich dabei auf zwei Schwerpunkte. Erstens untersucht die Arbeit die Verarbeitungsoperation Spaltenscan (Column-Scan) komprimierte und zweitens wird die Ganzzahlkomprimierung systematisch betrachtet. Diese beiden Aspekte werden aus Hardware-Sicht erörtert, um ein gewisses Maß an Beschleunigung der Anfrageverarbeitung zu gewährleisten. Dazu werden in dieser Arbeit verschiedene eingebettete Entwurfsoptionen untersucht und ein adaptives Ganzzahlkomprimierungssystem vorgestellt. Basierend auf einer umfassenden Evaluierung werden optimale Entwurfsbeschränkungen ermittelt. Die Arbeit schließt mit einer Diskussion weiterführender Forschungsaktivitäten in diesem Umfeld.

### DANSK ABSTRAKT (ABSTRACT IN DANISH)

I takt med at der i mange sektorer indsamles stadigt større mængder data, stiger behovet for effektivt af kunne udføre On-Line Analytical Processing (OLAP) forespørgsler. OLAP-forespørgsler tilgår typisk kun et lille antal søjler, men et stort antal rækker, og kan derfor udføres mest effektivt på data arrangeret i søjler. Samtidig gør betydelige fremskidt inden for systemhukommelse at selv store datasæt kan lagres helt i hukommelsen. Systemer der arrangerer data i søjler og lagrer komplette datasæt i hukommelsen er derfor de førende til udførsel af OLAP-forespørgsler. Disse systemer omskriver alle værdierne i hver søjle til sekvenser af heltal, og alle forespørgsler bliver udført på disse heltalssekvenser. For at udføre forespørgsler mere effektivt kan de paralleliseres ved brug af vektorisering baseret på Single Instruction Multiple Data (SIMD). Udover vektorisering spiller effektive letvægtsheltalskomprimeringsalgoritmer også en vigtig rolle da de reducerer hukommelsesforbruget. Desværre afhænger det af et datasæts karakteristika hvilken letvægtsheltalskomprimeringsalgoritme der giver det bedste resultat. Ikke desto mindre komplementerer vektorisering og heltalskomprimering hinanden, og når de kombineres, kan forespørgsler udføres Desværre er effekten af vektorisering begrænset for moderne mere effektivt. x86-processorer da deres SIMD-instruktioner er foruddefinerede og uforanderlige. Field Programmable Gate Arrays (FPGA)s åbner nye mulighed eftersom deres hardware kan ændres løbende efter behov. For eksempel kan en FPGA konfigureres som en processor med en arbitrær ordlængde hvilket fører til en højere vdeevne. Derudover kan specialiserede pipeline-baserede database acceleratorer udvikles, og indlejrede systemer kan blive udviklet som gør brug af sådanne acceleratorer. Desuden har moderne hybrid CPU-FPGA-systemer en direkte datakommunikationskanal imellem hukommelsen og FPGA'en som er nyttig til at accelerere udførslen af forespørgsler. På bagrund af disse fordele ved FPGAer, analyserer denne afhandling brugen af FPGAer i systemer der arrangerer data i søjler og lagrer komplette datasæt i hukommelsen. Analysen består af to dele. Først undersøges skanning af søjler der lagrer komprimeret data, og herefter analyseres letvægtsheltalskomprimeringsalgoritmer Disse to aspekter bliver betragtet ud fra et hardwareperspektiv for systematisk. at garantere et bestemt niveau af acceleration for forespørgsler. Specifikt udforsker denne afhandling forskellige designmuligheder for indlejrede systemer og foreslår et adaptivt letvægtskomprimeringssystem. Baseret på en omfattende evaluering, finder vi de optimale designbegrænsninger for en implementering af skanning af søjler og letvægtsheltalskomprimering. Endelig afslutter vi denne afhandling med at nævne vores fremtidige forskningsaktiviteter.

# CONTENTS

| 1 | INTRODUCTION |                                                                                                                                                |                                                     |

|---|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|   | 1.1          | Analytical Data Systems                                                                                                                        | 2                                                   |

|   | 1.2          | Query Acceleration                                                                                                                             | 3                                                   |

|   | 1.3          | Thesis Contributions                                                                                                                           | 5                                                   |

| 2 | BAC          | CKGROUND AND PROBLEM DEFINITION                                                                                                                | 7                                                   |

|   | 2.1          | Main Memory Column-Store Database Systems                                                                                                      | 8                                                   |

|   | 2.2          | State-of-the-art Optimization of Query Processing2.2.1Optimization using SIMD-Vectorization2.2.2Optimization using GPU-Accelerator2.2.3Summary | 11<br>11<br>13<br>14                                |

|   | 2.3          | Opportunities and Challenges of FPGA-based Acceleration2.3.1Hybrid CPU-FPGA Architecture2.3.2Related Works on FPGA-based Acceleration          | 15<br>15<br>17                                      |

|   |              | 2.3.3 Research Challenges                                                                                                                      | 19                                                  |

| 3 | Co           |                                                                                                                                                |                                                     |

| 3 |              | 2.3.3 Research Challenges                                                                                                                      | 19                                                  |

| 3 | 3.1          | 2.3.3 Research Challenges                                                                                                                      | 19<br><b>21</b><br>22<br>22<br>24                   |

| 3 | 3.1<br>3.2   | 2.3.3 Research Challenges                                                                                                                      | 19<br><b>21</b><br>22<br>24<br>26<br>29<br>30<br>31 |

| 4            | AD              | APTIVE LIGHTWEIGHT COMPRESSION SYSTEM                                                                                                                                                                                                   | 40                               |

|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|              | 4.1             | Lightweight Integer Compression4.1.1Overview and Classification4.1.2State-of-the-art Implementation Concepts4.1.3Discussion                                                                                                             | 41<br>41<br>43<br>46             |

|              | 4.2             | FPGA-based Implementation of Lightweight Integer Compression<br>Algorithms4.2.1 Recap FPGA-based Architecture4.2.2 Custom-made Compression HW Implementation4.2.3 Lightweight Integer Compression System Implementation4.2.4 Discussion | 46<br>47<br>47<br>56<br>57       |

|              | 4.3             | Adaptive Compression Systems4.3.1User-Specified Adaptive System4.3.2HW-Specified Adaptive Systems                                                                                                                                       | 57<br>58<br>59                   |

|              | 4.4             | Experimental Evaluation4.4.1Data Properties Definition4.4.2Physical-Level Compression4.4.3Logical-Level Compression4.4.4Cascaded Compression4.4.5Adaptive Compression                                                                   | 63<br>64<br>65<br>67<br>69<br>74 |

|              | 4.5             | Lessons Learned and Summary                                                                                                                                                                                                             | 78                               |

| 5            | Co              | NCLUSION AND FUTURE WORK                                                                                                                                                                                                                | 81                               |

|              | 5.1             | Conclusion                                                                                                                                                                                                                              | 82                               |

|              | 5.2             | Future Work                                                                                                                                                                                                                             | 84                               |

| BIBLIOGRAPHY |                 |                                                                                                                                                                                                                                         |                                  |

| Lis          | List of Figures |                                                                                                                                                                                                                                         |                                  |

| Lis          | List of Tables  |                                                                                                                                                                                                                                         |                                  |

# INTRODUCTION

- 1.1 Analytical Data Systems

- 1.2 Query Acceleration

- 1.3 Thesis Contributions

In the data-driven world, modern business technology is constantly taking care of a vast variety of customer demands. To satisfy customer requirements business technology requires to analyze and process information, whereby information is nothing but a collection of data. This leads the business organizations to deal with data from a variety of sources, including any kind of business transaction, industrial equipment, videos, sensors, social media, smart Internet of Things devices, and more. That means the amount of data is growing drastically. This gigantic amount of data arise the term "Big Data" [ES16]. Big data refers to the amount of data which is huge in volume, complex for analytics, and needs to be processed very fast [JWCW15, FLZ15]. This defines insights analytics is very crucial for big data. Moreover, big data even outnumbers Moore's law of digital circuit complexity [Sch97]. As a consequence, database researchers are continuously facing challenges to tackle big data. Big data require fast analysis in the huge amount of complex analytical queries. Fast analysis demands high-performance with high-throughput and low-latency. Unfortunately, traditional database methods are not good enough to manage analytical complex database queries more efficiently along with high throughput and low latency. This situation leads to create fast database architecture. As a result, database systems are constantly adapting novel features to satisfy high performance with low latency demands.

# 1.1 ANALYTICAL DATA SYSTEMS

Analytical queries are required to quickly analyze massive amounts of data. That means analytical queries are reading lots of rows but only a few columns of the database tables, as all columns are not required for processing. Thus, the organizational pattern of relational tables in the main memory influences the analytical query performance [SAB+05]. We can store a relational table either row-wise or column-wise. However, data can be more precisely accessed by storing in columns rather than by rows. In other words, column-wise storage allows us to ignore all the data that does not apply for a particular query because we can retrieve the required information from the particular columns. In contrast, the query of a row-oriented database system accesses each record along with all of its fields in the database to get the information, which involves a lot of unnecessary reads. As a result, query performance deteriorates drastically. In the case of analytical queries, row-oriented query processing is not effective as it is dealing with a large amount of data. Processing unnecessary information among the massive amounts of data is not performance-efficient. Therefore, column-wise data stores are beneficial for efficient and scalable processing of analytical queries.

Recently, the database community has been focusing on the main memory based system to efficiently exploit the ever-increasing capacities of main memory [BKM08, OBL<sup>+</sup>17, BATO13]. The main reason is, the price of semiconductor devices, e.g., transistors, becomes cheaper and the memory chip densities increase with more capacity. This enables the main memory to store larger datasets. To efficiently use this feature, database systems are shifting from disk to main memory [BKM08, OBL<sup>+</sup>17]. The two most important correlated reasons for this shifting are, i) main memory based sequential or random read and write are significantly faster over a disk, ii) fast data communication between main memory and processor words speed up the query processing speed tremendously compared to disk or flash drive based systems [MS14]. Therefore, to speed up the performance of database systems shifting from disk to main memory is fruitful. As a consequence, main memory database systems became the state-of-the-art for analytical workloads [SAB<sup>+</sup>05, BATO13]. It is important for a specific system that the main memory has a sufficient amount of space for the database. However, the space of main memory is still multi-gigabyte, while disk can be multi-terabyte.

One of the key primitives of a column-store main memory database system is scan, as analytical queries compute aggregations over full or large parts of single columns [LP13, LUH<sup>+</sup>18c]. The column-store main memory system increases the opportunity for compactness and the ability to process multiple columnar values at once. Thus, the optimization of the scan primitive is very crucial, in particular, for integer type data [LP13, LUH<sup>+</sup>18c]. Analytical queries usually involve CPU intensive operations, such as aggregation evaluation, column projection, sorting, searching, joins, and more [BATO13]. Using an efficient optimization scheme in modern hardware to process such query operations not only improves the query response time, but also minimizes the impact on query analysis by offloading the expensive queries out of massive data. However, it is highly questionable whether it is possible to hold and to process large operational data sets in main memory, as the space of main memories is still a bottleneck for large databases. Moreover, working with a giant dataset in the main memory increases the hardware maintenance cost and failure rates. To deal with such problems, data compression plays an important role in the main memory for analytical guery processing. Thus, another key primitive for the main memory based database system is data compression. Data compression is a well-known optimization technique for database systems [ZHNB06, AMF06]. Generally, analytical data systems have a common approach to encode each data element as an integer value. Therefore, each column is represented as a sequence of integer values. Dictionary encoding is used for non-integer data like strings. Afterward, each sequence of integer data is compressed using a lightweight integer compression algorithm. Based on this, each column is represented as a sequence of compressed column codes. Thus, for the main memory based database system, lightweight compression algorithms are used to optimize main memory processing in terms of evaluating a query directly in the compressed form of integer data [HHDL16, AMF06]. Processing analytical queries on column-store main memory based systems accelerates performance while data are compressed through lightweight compression algorithms. In this case, the processing is completely done on the integer type of data. Any type of operator consumes integer columns for processing and provides outputs of integer columns. During processing analytical queries on compressed datasets in main memory, late materialization occurred to decrease latency, whereby tuples are reconstructed on demand for each operator in the query plan. Lightweight compression algorithms are handy as operators are working directly on compressed data which accelerates the performance drastically. However, in the large corpus of lightweight integer compression algorithms, there is no single best compression algorithm and the choice depends on data characteristics [DUH<sup>+</sup>19].

# 1.2 QUERY ACCELERATION

Modern database systems are constantly exposed to a broad variety of novel requirements to improve query performance, ranging from analytical, transactional, or hybrid workload based applications to operators (relational model, graph processing, etc.) and various data characteristics. To satisfy these diverse requirements, there are several modern hardware opportunities available, that use the properties and possibilities of modern hardware appropriately.

There are several hardware possibilities, the common one is a general purpose modern CPU. To speed up CPU performance, CPU manufacturers usually increase the clock speed of single-core processors. After increasing the clock speed of single-core processors to a certain level it became increasingly difficult to increase further due to technological limitations. Hence, CPU manufacturers move towards two directions to speed up CPU performance, i) developing a system with either 2 to 8 processors oriented multicore or hundred to thousand processors oriented manycore architectures, ii) developing

the idea of instruction-level parallelism, which is known as *vectorization*. The length of general processor words in modern CPUs is usually fixed to 64-bit, which limits the performance of query operation in particular for column scan. However, modern column scan methods exploit the intra-instruction parallelism to increase performance [WPB<sup>+</sup>09, LUH<sup>+</sup>18b]. To explore such a modern scan method, the *vectorization* concept is used. The Single Instruction Multiple Data (SIMD) instruction set extensions such as Intel's SSE (Streaming SIMD Extensions) and AVX (Advanced Vector Extensions) have been available in modern Intel processors for *vectorization* [WWT<sup>+</sup>14]. SIMD instructions apply one operation to multiple data elements of so-called vector registers at once, which reduces the instruction calls. The size of the vector registers ranges from 128-bit (Intel SSE 4.2) to 512-bit (Intel AVX-512). These registers are used instead of regular processor words to improve performance [LUH<sup>+</sup>18b]. Therefore, SIMD vectorized implementations are beneficial for analytical queries execution [PRR15, ZR02]. By utilizing SIMD fundamental vector operations and good vectorization principles, several database primitives such as selection scans, hash tables, sorting, join, compression, have been implemented [PRR15]. SIMD based database system is moderate in manufacturing cost as well as performance.

Another modern hardware opportunity to accelerate query performance is GPU, whereby GPU acts as a co-processor to accelerate CPU based query processing. Typically, there is a large number of simple cores residing in a GPU for massive parallelism through thousands of threads of computation at a time. GPU cores are usually organized in blocks of 32 cores that execute the exact instruction at a given time parallelly, similar to the SIMD architecture of CPU. However, the main advantage of using GPU over CPU for query acceleration is bandwidth, e.g., a modern GPU NVIDIA TITAN Xp has 547.7GB/s memory bandwidth. In contrast, a modern CPU Intel Core i7-7700K has about 50GB/s. GPU-accelerated database system is perfect for the column-store due to its connected memory access pattern on the GPU. GPUs are not only suitable for column-store but also other database operations such as relational operations, compression, XML filtering, scan, etc. Although in the modern system, the CPU is transferring data to the GPU through a powerful PCI express bus. Transferring large chunks of memory from CPU to GPU is still a bigger challenge. However, query acceleration either through GPU or by using vectorization of CPU is always implemented on the software-level. To guarantee a certain expected level of performance on query processing also requires real-time hardware configuration. Therefore, modern database systems consider efficient ways for query processing not only through software-level implementation but also by hardware-based configuration. This leads database researchers towards the other modern hardware possibilities.

Nowadays, database researchers move towards the development of application-specific integrated circuit (ASIC) based column-store database systems [BKG<sup>+</sup>18]. The ever increasing demand for more and more performance-based database systems, also becoming power-hungry. Hence, to balance performance and power efficiency, the query processing engine can be implemented by developing the software design together with the hardware architecture. However, it takes a year or more to design ASIC based database systems, as such implementation requires several steps like fabrication, testing, verifications [AIR<sup>+</sup>17, AHF<sup>+</sup>14]. Moreover, ASIC based implementation is post-order configuration bound. This defines, after the fabrication process system acts as a permanent circuitry, which can not go through reconfiguration phases to satisfy additional requirements or modifications. As a consequence, such system development is time consuming as well as not cost-effective. All these constraints of ASIC based systems show the database researcher the way to the Field Programmable Gate Array (FPGA) based system.

FPGAs are accumulated with reprogrammable integrated circuits, whereby integrated circuits contain an array of programmable logic blocks. The high parallelism characteristic ensures hardware together with software system development on FPGA. In

other words, an FPGA is an innovative platform, whereby application-specific hardware can be implemented on the fly. Thus, FPGAs not only reduce the energy footprint but also provide software specific hardware-level implementation flexibility. All these features indicate that FPGA is fruitful for the query performance acceleration. However, working with FPGA requires comprehensive skills from high-level programming language skills to low-level circuit implementation knowledge. Previously, the business world has lost interest in FPGA based database acceleration, especially for main memory based database systems as FPGAs have integrated with insufficient bandwidth based memory interfaces which are limiting their performance [FMH<sup>+</sup>19]. Recently, the new generation FPGAs, e.g. Xilinx® UltraScale+<sup>TM</sup>, have overcome such limitations. Nevertheless, the key feature of FPGA hardware is reconfiguration [Teu17]. Platform with reconfigurable feature is always available to satisfy system-level requirements. Therefore, FPGA is perfect for main memory based database systems regarding many aspects: performance, manufacturing time as well as cost in terms of resource consumption.

### **1.3 THESIS CONTRIBUTIONS**

A Column-store data organizational pattern in main memory based database systems is necessary to accelerate the analytical query processing performance. Among others, the column scan is one of the very crucial operators in the main memory based database system. It has become obvious that the amount of data is ever-increasing in the modern world. As a consequence, main memory based database systems are required to deal with two major obstacles on top of the growing amount of datasets: i) to fit large datasets within few gigabytes of main memory, ii) to speed up the important database operations, e.g., the column scan operator. To deal with such obstacles, on the one side data needs to be compressed, and on the other side, optimization is necessary for the operators to work directly on the compressed form of data. Modern performance-efficient column scan mechanisms make it possible to perform queries directly on compressed data [LP13]. Additionally, lightweight compression algorithms are ideal for reducing the data footprint by reducing the gap between processor speed and main memory bandwidth [LB15]. Thus, constructing a system that producing compressed data through lightweight compressions for direct query evaluation require software-level specifications together with hardware-level attention. Recently, FPGA has become one of the most promising approaches for query acceleration. The flexibility of reconfiguration as per individual database operation implementation requirement makes FPGA an interesting platform. In this situation, considering FPGA for database operators implementation, such as scan or compression, for main memory based database system implies an optimistic choice. Hence, we investigate FPGA regarding two aspects:

• Column scan operation on compressed data.

• Adaptive lightweight integer compression.

Therefore, this thesis investigates the main memory based hardware-level FPGA-oriented implementations, specifically for column scan mechanisms and lightweight data compression algorithms.

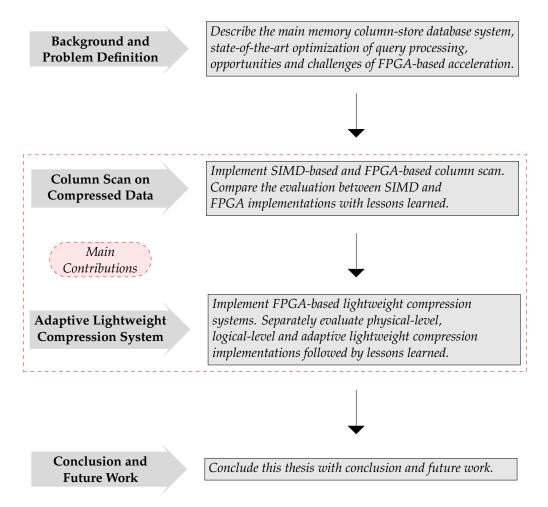

Figure 1.1: The Top-Down Structure of This Thesis.

Based on that, the top-down structure of this thesis is shown in Figure 1.1. Each highlighted arrow represents a chapter of this thesis. In Chapter 2, titled Background and Problem Definition, this thesis starts with a background study of the main memory column-store database systems as it is the software-side foundation of this thesis, and the hybrid CPU-FPGA architecture as it is the hardware-side foundation of this thesis. Then, we discuss recent research on FPGA-based acceleration to show that this novel class of accelerator is beneficial for query performance, and end with defining the research challenges that this thesis strives to resolve. Next, in Chapter 3, titled Column Scan on *Compressed Data*, this thesis gives an elaborate overview regarding state-of-the-art column scan techniques. Here, this thesis focuses on a naive scan technique [Lam75] as well as on a modern intra-instruction parallelism based technique called *Bitweaving* [LP13]. Then, we show the efficient ways of state-of-the-art column scan techniques implementation details using SIMD extensions and FPGA, comparison evaluations between SIMD and FPGA based implementation, and end this chapter with lessons learned. Afterward, in *Chapter 4*, titled *Adaptive LightWeight Compression System*, this thesis describes the possible implementation opportunities on FPGA for lightweight integer compression algorithms. Thus, this thesis implements the hardware-based physical-level, logical-level, and cascaded lightweight integer compression algorithm based systems on FPGA. Moreover, an efficient implementation detail for adaptive lightweight integer compression systems on FPGA is proposed. Then, an exhaustive experimental comparative evaluation of all the implemented compression systems is performed. This chapter ends with the lessons learned from the evaluation. We conclude this thesis with a summary and list of potential future work in *Chapter 5*.

# BACKGROUND AND PROBLEM DEFINITION

- 2.1 Main Memory Column-Store Database Systems

- 2.2 State-of-the-art Optimization of Query Processing

- 2.3 Opportunities and Challenges of FPGA-based Acceleration

This chapter presents an elaborative description of main memory column-store database systems along with selected related work. Thereafter, the state-of-the-art optimization opportunities for query processing acceleration are illustrated. Then, the modern hybrid CPU-FPGA architecture is discussed as the novel class of accelerator hardware including recent database domain-related works on FPGAs. Finally, the research challenges and proposed solutions of this thesis are defined.

# 2.1 MAIN MEMORY COLUMN-STORE DATABASE SYSTEMS

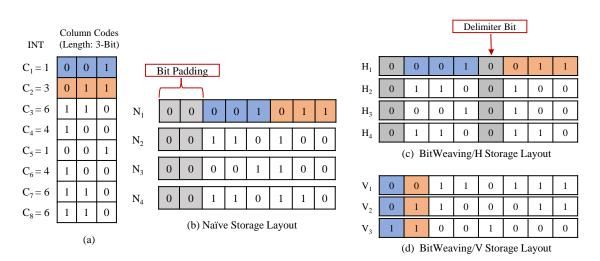

Figure 2.1: Illustration of Main Memory Column-Store Database System.

For decades, the main research goal of the database community has been performance. To meet this goal, the database community has explored possible alternatives including indexing, materialized views, vertical/horizontal partitioning, etc. Recently, the so-called column-store database systems have become state-of-the-art regarding query performance for certain workloads. Column-store database systems organize records or tuples or data tables in a columnar fashion. Unlike traditional systems, column-store databases are responsible to store and perform different types of queries. In various tools or software, column-store databases act as the backbone of the system to extract, transform, load, or for the visualization of data. However, storing data in columns benefits the database systems, because they are accessing the particular data they need to perform a query, but do not require scanning and discarding of unwanted data. The query performance of the database system is explicitly correlated with the efficiency of data movement between storage and CPU registers for processing. Usually, the storage database systems are disk-oriented. A typical disk has an average read/write latency of 5 milliseconds while the main memory has 50 nanoseconds, which is nearly 100,000 times as fast [OBL<sup>+</sup>17]. Undoubtedly, the disk-oriented data access is the major bottleneck of the database systems. However, the characteristic of column-store databases increases performance as less amount of read operation is required on disk. Additionally, shifting column-store database systems from disk to main memory benefit even more regarding performance. Figure 2.1 illustrates the main memory column-store database system in an exemplary way. In this figure, the table called Order\_Table, which has four

columns, namely ID, #Items, Order\_Price and Shipping\_Mode. The ID and #Items columns consist of integer values, the Order\_Price and Shipping\_Mode columns consist of float and string values, respectively. In column-store organization, all data traversal happens column-wise one after another (see Figure 2.1). All logical data represented in Order\_Table are mapped to integer data on the physical level in terms of main memory. Thus, the string values of the Shipping\_Mode column are encoded to integer values using the dictionary encoding technique. Similarly, the float values of the Order\_Price column are stored as integer and keep the precisions as metadata. As data are stored column-wise at the physical level, it is easy to access a particular column at once for query processing which accelerates the performance. Subsequently, the era of main memory column-store database systems arises which creates several research dimensions for optimization.

For instance, Stonebraker et al. [SAB<sup>+</sup>05] invented the extended version of column-store database system as C-Store. Usually, an entry sequence order is maintained to insert data in columns. This is efficient for new data insertion, either batch-wise or transactionally, at the end of the column. However, this situation becomes very difficult and expensive for column update operations without an entry sequence of orders, which is a common problem. C-Store overcomes such issues through a read-optimized column-store and an update/insert-oriented writeable store, connected by a tuple mover. C-Store is implemented on top of several components. It has, i) a small Writeable Store (WS) component to support high-performance inserts and updates, ii) the Read-optimized Store (RS) is capable of supporting very large amounts of information, iii) additionally, RS is optimized for reading and supports a restricted form of insert, for instance, the batch movement of records from WS to RS is performed by the tuple mover [SAB+05]. Stonebraker et al. evaluated C-Store on the TPC-H benchmark and the result showed that C-Store is on average 21 times faster than the native column-store system [SAB+05]. The design of C-Store emphasized radical departure from the traditional database systems. C-Store targeted for the read-intensive database market. C-Store is a column-store representation connected to a query execution engine [SAB+05]. C-Store focused on economizing the storage representation on disk by coding data values and dense-packing the data [SAB+05]. C-Store supports distributed transactions without a redo log or two-phase commit and efficient snapshot isolation  $[SAB^+05]$ .

In contrast, MonetDB is the first database system that accumulates the main memories for column-store database systems effectively and efficiently for query processing [BZN05, IGN<sup>+</sup>12]. To increase performance, MonetDB mainly focuses on analytical workloads that are read-intensive, whereby updates are appending new data in terms of large chunks to the database. MonetDB reconsiders all aspects of the traditional database systems in terms of design, architecture, and implementation. However, technology-wise MonetDB effectively exploits the potentials of modern hardware. For example, Boncz et al. [BZN05] investigated the inefficiencies of modern CPUs. On one side, they triggered out huge amount of query execution introduces interpretation overhead which prevents the compiler from using the most performance-critical optimization techniques, such as loop pipelining. On the other side, they analyzed that the main memory database system MonetDB applies a column-at-a-time materialization policy, which makes it memory bandwidth bound. Therefore, Boncz et al. [BZN05] proposed pipelined operators that pass to each other small, cache-resident, vertical data fragments called vectors and they called this new query engine MonetDB/X100. This work [BZN05] evaluated their system on the TPC-H benchmark for 100 GB data, showing that MonetDB/X100 can be up to two orders of magnitude faster than the existing system. Internally, MonetDB does not follow the exact column-oriented data storage logic. MonetDB came up with a whole new design tailored for columnar execution along with cache-conscious data structures and algorithms to provide optimal use of hierarchical memory systems  $[BZN05, IGN^+12]$ .

Thus, we can state that the main memory column-store database systems rely on two key factors,

(*a*) Columnar Storage Organization.

(b) Columnar Processing.

(a) Columnar Storage Organization: In columnar storage organization, each column is encoded as a sequence of integer values. Hence, it is very important to reduce the column size to fit in the main memory. To obtain this, the columns are usually compressed with a common approach: (i) Encode the values of each column as a sequence of integers using some kind of dictionary encoding and (ii) Apply lightweight lossless integer compression to each sequence of integers resulting in a sequence of compressed column codes. Generally, there are two main types of compression: (i) Heavyweight compression, (ii) Lightweight compression. Usually, lightweight compression algorithms work for main memory oriented datasets and heavyweight compression algorithms are for disk-based datasets. However, lightweight compression has two major benefits compared to heavyweight compression. Firstly, the data transmission rate of lightweight compression is higher than the heavyweight compression, as the main memory stays closer to the CPU than the disk. Secondly, the computational effort of the lightweight compression algorithm, especially for the (de)compression, is much lower than for heavyweight compression algorithms. To achieve these benefits, there is a large corpus of compression schemes that have been developed in the domain of lightweight lossless integer compression. Every individual lightweight compression scheme depends on a unique data property, such as value distributions, run lengths, sorting, or the number of distinct data elements. Hence, in this large corpus of lightweight compression schemes, there is no single-best scheme suitable for all datasets [DUH<sup>+</sup>19].

(b) Columnar Processing: It is very crucial to determine when the projection of columns should occur to accelerate the performance during processing columnar queries. In column-store, attributes are usually stored in a distributed manner on the storage medium. Information of a single entity could be distributed over several columns. As a consequence, query processing over several attributes is required to access a single entity. Hence, during query processing, multiple columns have to be reassembled at some point to create tuples. This tuple reconstruction process is called *Materialization*. In the query plan design context, there are two types of *Materialization*, (i) *Early Materialization*, (ii) Late Materialization. In Early Materialization, tuple reconstruction happens early in the query plan. This means, during query processing, it selects all relevance columns and reconstructs tuples from their component attributes first. Afterward, it executes standard row-store operations on the resulting tuples. Thus, implementation-wise *Early Materialization* is easy but generally performance-wise is poor. In contrast, *Late* Materialization fetches columns on demand for each operator in the query plan. In Late Materialization, tuple reconstruction happens at the end of the query plan. This makes it necessary to keep efficiently the intermediate join operations results that have been conducted on individual columns. These intermediate results are represented as a set of ranges of positions. These positions can be intersected to extract the values of interest which finally join into the final projection. Thus, implementation-wise *Late* Materialization is complex but generally performance-wise is better. Additionally, in the context of analytical columnar query processing, all query operators are working on integer data and usually, the tuples are only reconstructed at the end for the query result. Thus, the analytical columnar query processing applies the Late Materialization concept to achieve good performance. For instance, MonetDB defined all operators using the Monet Interpreter Language (MIL) which is an algebraic query language including a good join order through emphasizing the Late Materialization concept [BK99]. Column-store is suitable for the compression scheme. However, this advantage is not available in

row-store since a tuple contains data from multiple different attributes. Column-store does not guarantee to give better compression ratios but the column-store has the potential to be highly compressible. Different factors are taken into account, such as column cardinality, data types, and sorting, which help to decide about the compression scheme. In this context, *Late Materialization* becomes more effective since it processes the column values before forming tuples that helps to work directly on the compressed columnar data. Therefore, the major advantage of lightweight integer compression in the main memory based column-store databases is that some query operators can process the compressed data directly, without decompression.

The goal of the above discussion was to show the importance of the main memory column-store database systems. Main memory column-store database systems keep and process data column-wise, which is perfect for analytical queries, because each query is read-intensive on a limited set of columns. Another key aspect of the main memory column-store database system is data compression. Nevertheless, data compression is a well-known optimization technique for database systems. In particular, for the main memory column-store database systems, lightweight compression algorithms are used to optimize query processing by evaluating the query directly in the compressed form of integer data. However, the most important aspect of the main memory column-store database system is query performance. Hence, the software-side foundation of this thesis is based on the main memory column-store database systems.

## 2.2 STATE-OF-THE-ART OPTIMIZATION OF QUERY PROCESSING

Main memory based analytical databases are continuously exploring a variety of optimization opportunities with respect to the underlying hardware. Among several modern hardware systems, SIMD-vectorization and GPU-based accelerator became the state-of-the-art optimization opportunities for query processing. Therefore, this section concentrates on some recent related works regarding SIMD-vectorization and GPU-based database systems including the limitations of such optimization opportunities.

### 2.2.1 Optimization using SIMD-Vectorization

To accelerate performance, three different sources of parallelism are possible on the hardware side: i) Thread parallelism, ii) Instruction level parallelism, iii) Data parallelism. Among these parallelisms, data parallelism can be achieved through SIMD instructions. Single instruction multiple data (SIMD) performs the same operation on multiple data simultaneously. SIMD operations utilize a set of vector registers, whereby one operation is applied to all elements of the vector at the same time. In other words, a single instruction can be applied to multiple data elements in parallel. Several processors such as Intel's Xeon Phi, Intel Sandy Bridge, Haswell/Broadwell, AMD Bulldozer, ARM, and PowerPC implement SIMD instructions, although the instruction details may vary. Since hardware-specific SIMD instructions involved operations depend on vector operands. SIMD operations are also referred to as vectorizations. Therefore, many database systems continuously utilize SIMD-vectorization as an optimization opportunity to accelerate performance. For instance, recent related works [PRR15], [PR19], and [BRT<sup>+</sup>18] utilized SIMD-vectorization to implement the fundamental database operators. In the following, we will detail on related works [PRR15], [PR19], and [BRT<sup>+</sup>18].

Polychroniou et al. [PRR15] presented main memory based analytical database execution using generic SIMD vectorized implementations. Selection scans, hash tables, sorting, and join operators were implemented through the fundamental SIMD-vector operations. For instance, SIMD-based fundamental vector operations were implemented that are required to implement vectorized database operators. Among several, two operations are termed as selective loads and selective stores. Selective stores write a specific subset of the extension/vector lanes to a memory location contiguously based on a mask. Selective loads are the symmetric operation that involves loading from a memory location contiguously to a subset of extension/vector lanes based on a mask. Afterward, selective store operation is utilized in the implementation of a selection scan database operator, whereas the selection scan is a very useful operator for main memory query execution. A selection scan is a conditional scan operation that uses selective store operation (which Polychroniou et al. [PRR15] implemented through SIMD provided instructions) to store the extensions or vector lanes that satisfy selection predicates. Polychroniou et al. [PRR15] evaluated the performance of selection scans on Xeon Phi and Haswell systems for the selection condition  $k_{min} \leq k \leq k_{max}$ , where  $k_{min}$  and  $k_{max}$  are query constants. Polychroniou et al. [PRR15] varied the selectivity and measured the throughput for six different implementation versions of the selection scan to show the efficiency of vectorized implementation over non-vectorized implementation. Polychroniou et al. [PRR15] implemented two scalar variants with and without branching of selection scan. The rest variants implemented using SIMD vectorization. On both systems: Xeon Phi and Haswell, all vector codes outperform scalar codes. Besides selection scan, other vectorized implementations, e.g., hashing, partitioning, sorting, and join, were evaluated against scalar and vector code on Haswell and Xeon Phi systems. This work [PRR15] utilized SIMD-vectorization in the context of main memory database operators, and focused on the impact of vectorization on algorithmic designs, as well as the architectural designs.

Some years later, the same database research group introduced an analytical query engine implemented entirely by using SIMD instructions namely VIP [PR19]. The VIP engine supports all fundamental database operators, such as selections, hash joins, group-by aggregations, multiple data types, compression, and complex predicates or expressions. The latest AVX-512 SIMD instructions are utilized on VIP, which supports 512-bit width based vector registers and additional functionality, e.g. conflict detection or prefetching. Polychroniou et al. [PR19] implemented one of the key lightweight physical-level compression called *Bitpacking* using only 5 AVX-512 SIMD instructions. During the evaluation of the TPC-H workload, VIP outperforms query-specific hand-optimized scalar code.

Hashing is one of the important database operator that is very useful for hash-based joins and aggregations. Hence, Behrens et al. [BRT<sup>+</sup>18] focused on the efficient ways of hashing implementation. However, Behrens et al. [BRT<sup>+</sup>18] noticed that vectorized database operators improve performance but require processor-specific APIs. Therefore, Behrens et al. [BRT<sup>+</sup>18] vectorized the essential primitives, such as gather, scatter, selective load, and selective store in OpenCL to reduce code complexity and to ensure portability. This work [BRT<sup>+</sup>18] used Intel Core i7-6700K CPU and Xeon Phi processors for evaluations. During evaluation, SIMD intrinsics based vectorized hashing outperforms OpenCL-based hashing. However, on Intel Core i7-6700K CPU, OpenCL-based vectorized hashing outperforms scalar hashing for moderately sized hash tables that fit into the L2 cache. In this case, Behrens et al. [BRT<sup>+</sup>18] OpenCL-based hashing.

Although the above-mentioned works explain that the SIMD-optimization became one of the popular opportunities for database researchers, it is still not used in all cases. For instance, a heavy flow control-oriented operator like parsing is not doable from SIMD. However, SIMD-vectorize comparisons based parsing is possible using a large cache that can store more intermediate states. But it requires exclusive SIMD intrinsics based cache control features which are not available in SIMD. Additionally, the extended vector register increases power consumption and chip area of the system which increases the system cost. Moreover, gathering data into SIMD vector registers and storing it to the correct destination locations requires extra efforts and sometimes it is inefficient, which implies data alignment is a big obstacle in SIMD. Finally, SIMD instructions are hardware architecture-specific. Different processors have different sets of SIMD instructions which implies that database researchers must provide multiple vectorized database operator implementations to operate optimally on any given processor. Hence, SIMD is a hardware-tight opportunity and it is not suitable for all types of operator implementation. As a consequence, it provides limited system performance. All these shortcomings show that SIMD-vectorization is not a flexible optimization opportunity in the database domain.

### 2.2.2 Optimization using GPU-Accelerator

The massive parallel capabilities with thousands of cores for analyzing volumes of data to solve difficult computational problems with great speed makes the GPU-accelerator an interesting platform for data-intensive applications. As a consequence, database researchers adopted the key feature *perform parallel operations on multiple sets of data* of GPU (Graphics Processing Units) to accelerate performance. Initially, GPU was used in databases to enhance operations by adding compute workloads to the graphics shields. When the NVIDIA introduced GPU along with CUDA [BS10], the application-specific general-purpose logic implementation became more convenient on GPU. Architecture and processing paradigm wise GPU is completely different from CPU. GPU is advantageous as it is keeping up with today's big data demands. Hence, GPU based databases can provide speedups over the CPU-based system. Some related works are discussed below.

The recent trend of database systems are changing hardware platform from homogeneous CPU systems towards heterogeneous CPU-GPU based systems including different computing units (CUs). The computing architecture in a heterogeneous system is different from a homogeneous system. Therefore, database management systems (DBMS) are continuously adapting to this hardware trend to efficiently utilize the given opportunities. Traditional database systems require query execution plans (QEP) to compute query results. To determine the most efficient QEP, the query optimizer is used for logical and physical optimizations. In a heterogeneous CPU-GPU based database system, before query execution, performing a placement optimization is essential, because it assigns physical operators of the most efficient QEP to the ideal computing units. Hence, Karnagel et al. [KHL17] proposed a novel adaptive placement approach for query processing on a heterogeneous CPU-GPU system. This work [KHL17] approaches a physical query execution plan as input and divides the plan into disjoint execution islands at compile-time. The execution islands are determined in a way that the cardinalities of intermediate results within each island are known or can be precisely calculated. The placement optimization and execution are performed separately per island at query runtime. The processing of the execution islands takes place successively following data dependencies. Karnagel et al. [KHL17] also proposed two additional improvements: (i) a fine-grained runtime estimation technique, (ii) a placement-friendly data transfer technique. This work [KHL17] implemented the techniques as a virtualization layer called HERO (HEterogeneous Resource Optimizer), which can be used by any OpenCL-based database system. This work's [KHL17] evaluation is based on OpenCL driver implementation with the OpenCL database systems gpuDB2 and Ocelot3. Karnagel et al. [KHL17] used a highly heterogeneous hardware setup consisting of a CPU and three different GPUs (AMD Radeon R7, Nvidia Tesla K20, Nvidia GT 640), because of their general availability and their support for OpenCL. In the evaluation, this work [KHL17] showed that their approach improves the performance up to 50x over gpuDB and Ocelot system by choosing good heterogeneous placements.

In the last few years, many approaches utilized GPUs for the database system acceleration. Breß et al. [BHS<sup>+</sup>14] theoretically explored the design space of GPU-aware database systems. Breß et al. [BHS<sup>+</sup>14] argued that a GPU-aware DBMS should be a main memory, column-oriented DBMS using the block-at-a-time processing model, possibly extended by a just-in-time-compilation component. The system should have a query optimizer that is aware of co-processors and data-locality, and can distribute a workload across all available (co-)processors. Breß et al. [BHS<sup>+</sup>14] validated these findings by surveying the implementation details of eight existing GPU-aware DBMSs and classifying them according to the mentioned dimensions. Additionally, this work [BHS<sup>+</sup>14] summarized common optimizations implemented in GPU-based DBMSs and inferred a reference architecture for GPU-aware DBMSs, which acts as a starting point in integrating GPU-acceleration in popular main memory DBMSs.

Despite having massive parallel capabilities, the GPU can only be programmed using its available static vectored instruction set. Typically, a GPU is connected as a co-processor of CPU, so the GPU-based programming model is quite restricted under CPU. However, modern NVIDIA GPU overcomes a certain level of restrictions. However, the transfer of data to the GPU increases the latency as it needs to go through the PCIe channel. Therefore, the PCIe bus is still a bottleneck of GPU-based query processing. Moreover, on GPU the low-level instructions are not implementable, which makes GPU a hardware-tight platform. Additionally, GPU is not suited for all database algorithms. Mostly, the database operations are reformulated to take advantage of the parallelism of GPU, which increases the operation overheads. Finally, GPU is an instructional computation device that needs to run various computing units to perform a particular operation, which makes GPU a power-hungry device. All these limitations corroborate that GPU is not perfectly suited for all types of database operators.

### 2.2.3 Summary

Recent related works show that SIMD optimization is heavily applied for different query operators as well as lightweight integer compression [PRR15, PR19, BRT<sup>+</sup>18]. Additionally, recent works also show that columnar processing is suited for GPU co-processing [KHL17, BHS<sup>+</sup>14]. In the database research domain, SIMD optimization and GPU optimization are heavily used, but their benefits are limited to fixed hardware. Fixed hardware defines that SIMD and GPU based on some fixed set of instructions. Database researchers are bound to work within this fixed set of instructions. That means researchers are neither able to modify any instruction nor implement any new instruction to accelerate performance. This limits the implementation-level flexibility to accelerate query performance. To overcome such limitations, a new class of accelerator hardware arises the so-called FPGA. FPGA is not bound to fixed hardware. It is a flexible platform where different types of operators can be implemented on-the-fly as per system requirements. Hence, this thesis targets this new class of hardware to accelerate query performance.

# 2.3 OPPORTUNITIES AND CHALLENGES OF FPGA-BASED ACCELERATION

In this section, the benefits and opportunities of the new class of accelerator hardware, namely the hybrid CPU-FPGA architecture is defined. The hybrid CPU-FPGA architecture is the hardware-end backbone of this thesis. Afterward, some exclusive database related works with regards to FPGAs are discussed as an application of a new class of accelerator hardware. In the end, we conclude this section by defining the research challenges of this thesis.

#### 2.3.1 Hybrid CPU-FPGA Architecture

In the early 1980s, the digital circuit community envision "reconfigurable after being manufactured" type technology to gear up the scalability and flexibility regarding the development process of integrated devices. As a continuation, the programmable logic array (PLA) device was introduced for fixed architecture logic devices with programmable AND gates followed by programmable OR gates. Manufacturing-wise PLA was efficient while it collapsed during scaling as the programmable instances in the array grew with the square of the number of inputs. Therefore, PLA became impractical for integrated circuitry regarding power efficiency and performance. Later, other devices like CPLD, EEPROM came onto the digital market, but none of them was able to completely satisfy the "reconfigurable after being manufactured" vision. Later as a successor of PLA in 1984, Xilinx® first introduced the concept of Field Programmable Gate Array (FPGA), which fulfills the vision of reconfiguration [FMH<sup>+</sup>19]. In Field Programmable Gate Array (FPGA), a group of reconfigurable logic array memory cells is distributed along with interconnecting switching nodes and wiring. The reconfigurable logic array memory cells of FPGA increase the scalability in terms of power efficiency and performance compared to programmable AND-OR-based PLA structure.

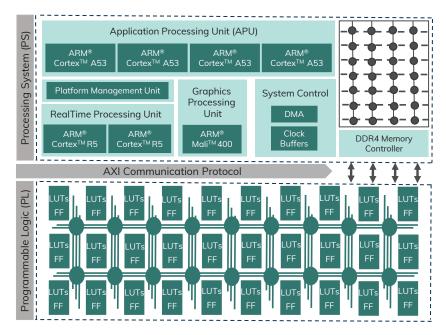

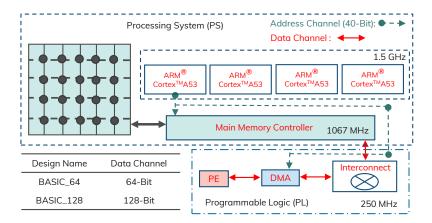

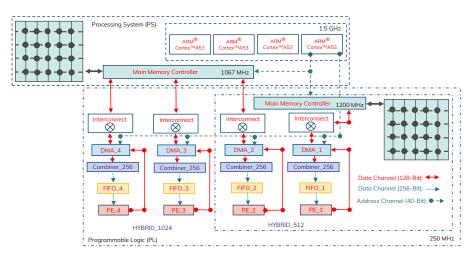

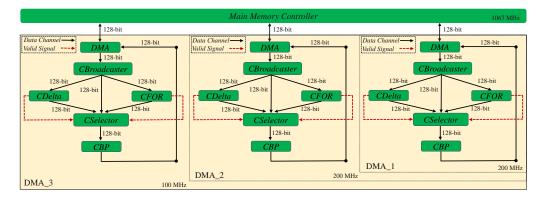

Recently, FPGA vendors like Intel® or Xilinx® incorporate an FPGA and a CPU into a common system leading to System-on-Chip (SoC) architecture. Thus, the modern generation hardware era of hybrid CPU-FPGA hardware systems arises. This thesis is evaluated on a hybrid CPU-FPGA hardware system from Xilinx® called Zynq UltraScale+<sup>TM</sup> [Xil19b] as hardware foundation. The architecture of this hybrid system is depicted in Figure 2.2. As shown in this figure, the target system is divided into two major top-level blocks, *i*) *Processing System* (*PS*), *ii*) *Programmable Logic* (*PL*), while *the AXI Communication Protocol* is used as a bridge to connect these two blocks.

*Processing System (PS)* is based on so-called multiple processor system-on-chip (MPSoC) architecture. Therefore, PS integrates 64-bit quad ARM® Cortex-A53 based Application Processing Unit (APU), dual-core ARM® Cortex-R5 based Real-Time Processing Unit (RPU), ARM® Mali-400 based Graphics Processing Unit (GPU) in a single chip. The maximum frequency of APU is 1.5 GHz. Although the PS part features RPU and GPU cores, both are not considered further in this thesis. The PS part also includes on-chip memory and a rich set of peripheral connectivity interfaces. Moreover, the Zynq UltraScale+<sup>TM</sup> has two DDR4 main memories. While the size of one DDR4 is 4 GB, the size of other one is 512 MB. Additionally, the platform management unit controls the power of the overall system and the system control unit is occupied by various categories of clock buffers and some pre-fixed controllers, such as direct memory access (DMA).

*Programmable Logic (PL)* part is responsible for designing all programmable custom-made hardware. Internally, *PL* is composed of configurable logic blocks (CLBs), a

Figure 2.2: Hybrid CPU-FPGA Architecture of Zynq UltraScale+™[Xil19b].

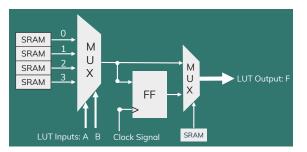

collection of block and distributed memories (BRAM, LUTRAM), and arithmetic units (DSPs) [MTA09, TW13]. CLBs plays a significant role in the reconfiguration context, whereby it occupied with look-up tables (LUTs). LUT is reflected as static RAM (SRAM), which holds a custom-made truth table while the power is turned on. Basically, a LUT circuit is occupied with SRAM, multiplexer (MUX), and flip-flops. The SRAM cells hold the outputs of a custom-made truth table which is connected with a MUX and the inputs of MUX act as the address lines for a corresponding one-bit-wide SRAM cell. When a specific boolean function is configured, the SRAM cells are loaded with their corresponding truth table. Therefore, instead of wiring lots of AND-OR-XOR-based logic gates, LUTs just simulates this with SRAMs. A 2-input LUT circuit requires (4X1)-bit SRAM as shown in Figure 2.3, whereby it can configure any 2-input boolean expression F(A, B). Likewise 2-input LUT, 3-, 4-, 5-, as well as up to 6-input LUTs are available in modern generation FPGAs. In CLBs, LUTs are cascaded to implement *n*-ary boolean functions. Therefore, any type of application-specific custom-made hardware is realized by cascading a bunch of CLBs in terms of various sizes of LUTs.

Figure 2.3: Internal Circuit of 2-Input LUT.

In contrast to previous FPGAs offered by Xilinx®, the *AXI Communication Protocol* between the *PS* and the *PL* on the Zynq UltraScale+<sup>TM</sup> is more powerful. Concretely, it has several high performance AXI interfaces between *PL* and *PS* providing a data bus width of 32-bit/64-bit/128-bit. More precisely, the configurable hardware on the *PL* part has direct access to the main memory on the *PS* part, so that *PS* and *PL* can work on the same data elements as shown in Figure 2.2.

To describe the operation mode of a specific application logic on FPGAs, a hardware description language, such as Verilog or VHDL is used. This description is then synthesized to RTL (register transfer logic) through several steps towards implementation along with bitstream for the FPGAs. Typically, FPGAs offer a higher performance while maintaining a lower power dissipation than the CPUs. To be competitive with common CPUs, the configurable hardware for a specific application logic has to be well-designed, since current FPGAs usually run at very low clock-rates around (200 - 400) MHz. To enable that, the most challenging issue is to create efficient processing pipelines due to the proximity of logic and memories [MTA09, TW13].

The above-mentioned architecture defines that the hybrid CPU-FPGA system is extremely beneficial for the main memory column-store database systems, in particular for two reasons, i) the direct access to the main memory, ii) a large variety of custom-made design implementation possibilities. To utilize such advantages for query performance, the hardware-side foundation of this thesis is based on hybrid CPU-FPGA architecture.

Moreover, Xilinx® have very recently offered Alveo<sup>TM</sup> U50 data center accelerator cards to optimize acceleration. The key features of such a card are 8 GB HBM memory with data transfer rates up to 2 GT/s and 32 *AXI* channel access [Xil19a]. It clarifies that the modern trends of FPGA is significantly useful for the main memory column-store database systems regarding query performance.

#### 2.3.2 Related Works on FPGA-based Acceleration

The application of FPGA in the database domain regarding acceleration is very common nowadays. The database community continuously utilizes the high parallelism feature of FPGA for the acceleration of distinct database operation. This thesis analyzes some related works to show that FPGA is used to implement database operators, in particular, XML parsing [TWN13], regular expression [SIOA17], near-data processing [ISA17], and binary packing compression [MMFB20]. In the following, we detail on related works.

In the database system, a parser is responsible to break down the data information into its corresponding specified grammar components leading to high parallel activities. Thus, Teubner et al. [TWN13] utilized the high parallelism feature of FPGAs for XML parsing processing through reducing the computation and main memory overhead. They implemented an FPGA-based XML processor as so-called XLynx, whereby design perspective-wise a skeleton automata is used for data-intensive hardware circuits that offer high expressiveness and quick reconfiguration at the same time. However, skeleton automata is a subset of finite state automata that provides the generic implementation. XLynx is a microbenchmark-based engine for projection. The throughput of XLynx in-network filtering is 180 MB/s, whereby in-network filtering with XLynx significantly eases the XML parsing burden on the backend XML processor. XLynx operates on streaming mode and processes one input character per clock cycle. Thus, the filtering throughput of this system is independent of the query workload. XLynx addressed the key limitation in modern system designs through savings up to 94% of electrical power consumption. Finally, in many real-world database systems the main bottleneck is parsing and XLynx is improving the overall query execution time in terms of performance by reducing the parsing cost.

In the database domain, a regular expression operator provides a powerful and flexible pattern match that helps to implement efficient search utilities for the systems. In other words, regular expressions enable the search patterns in string type data by utilizing standardized syntax. However, real-world data is occupied with complex information, and a regular expression operator is able to extract information within a limited number of known formats which makes it compute-bound. Sidler et al. [SIOA17] looked into this compute-bound regular expression matching operator. They exploited the modern generation hybrid CPU-FPGA system for regular expression operator to overcome the compute-bound bottleneck. In particular, they used Intel® provided by a hybrid Xeon-FPGA system, whereby FPGA has coherent access to the main memory through the QPI bus. Operator-wise they focused on two commonly used SQL operators for strings, *LIKE* and *REGEXP\_LIKE*. They implemented these regular expression operators on the hybrid Xeon-FPGA system. The overall system can be categorized into three parts, i) a CPU-based regular expression Hardware User Defined Function (HUDF) which is integrated with the popular column-store system MonetDB, ii) a Hardware Operator Abstraction Layer (HAL) for the interaction between Xeon and FPGA, iii) the FPGA-based hardware part of the HAL and four regular expression Regex engines. All Regex engines can operate independently for different queries and are parameterizable at runtime. The max data processing throughput per Regex engine is 6.4 GB/s, while the combined four *Regex* engines throughput is 25.6 GB/s. This meant a significant improvement regarding response time and throughput. Precisely, Sidler et al. [SIOA17] evaluated the following types of complex regular expression queries:

SELECT count (\*) FROM address\_table WHERE REGEXP\_LIKE (address\_string, '[0-9]+(USD | EUR | GBP)')

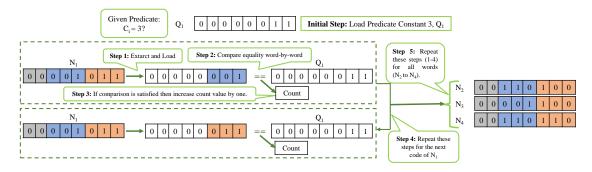

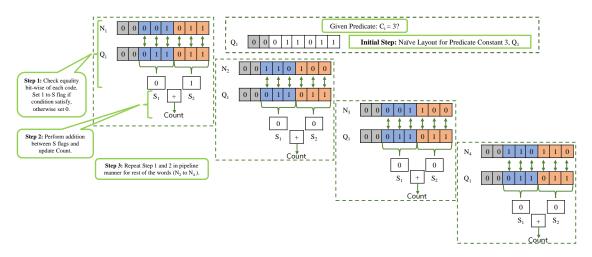

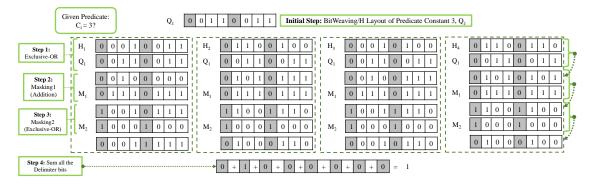

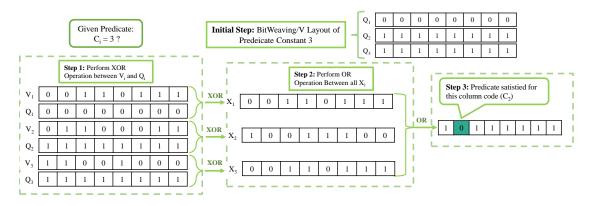

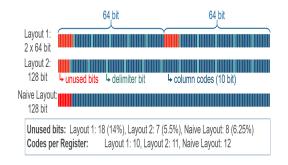

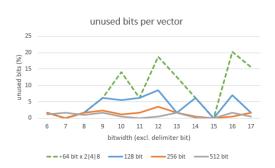

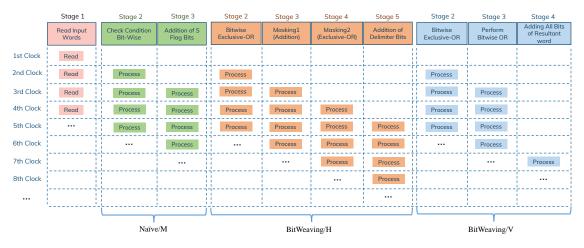

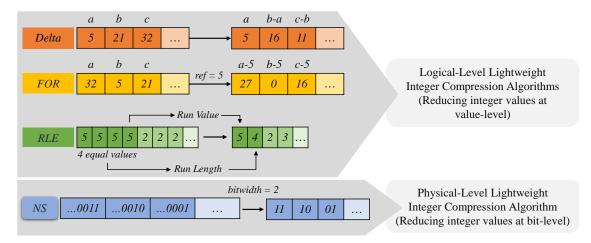

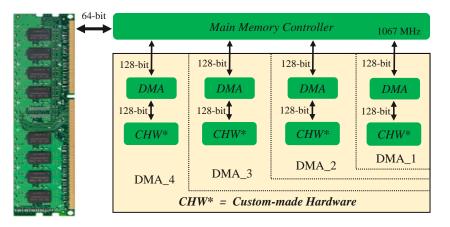

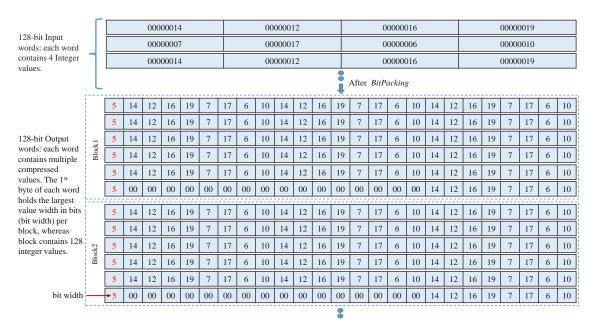

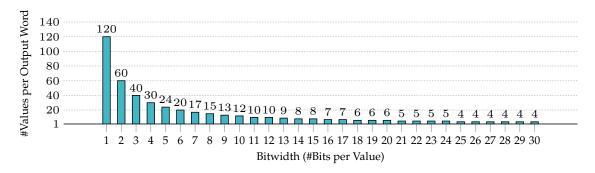

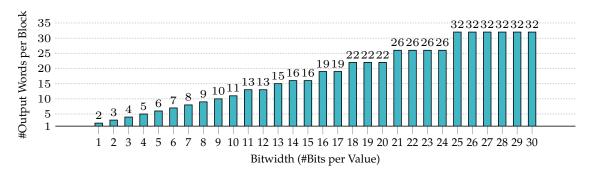

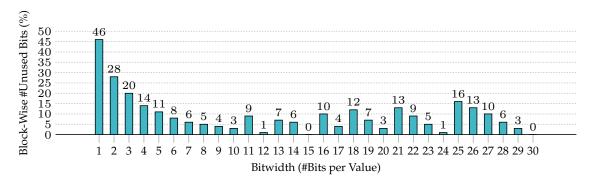

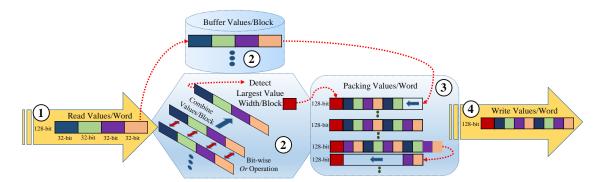

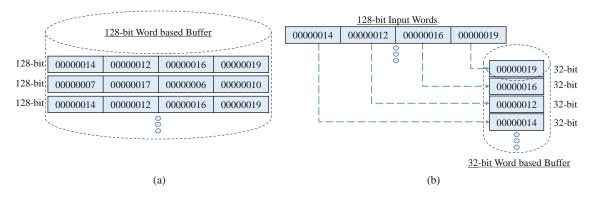

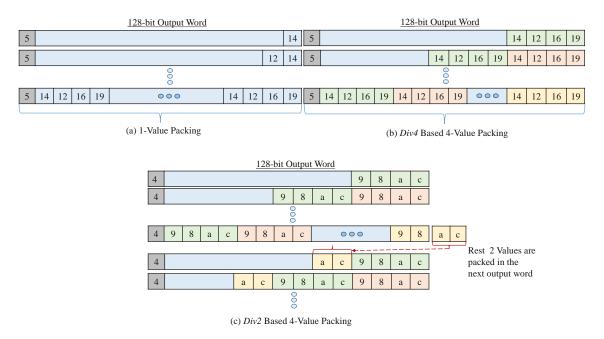

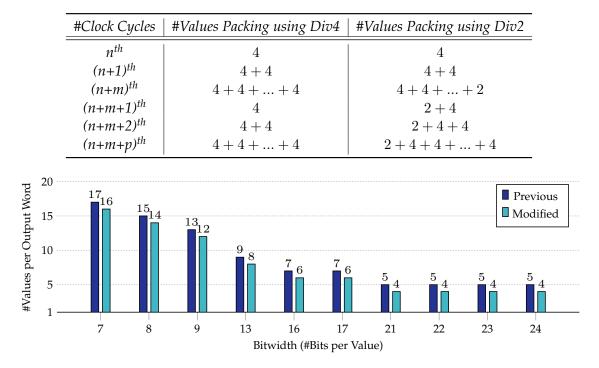

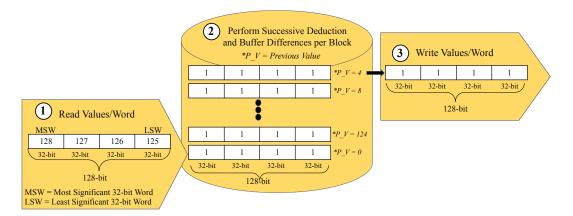

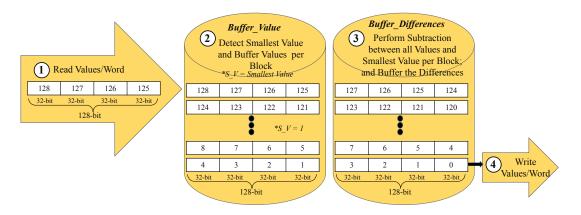

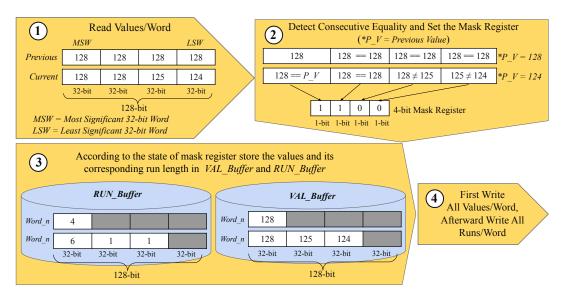

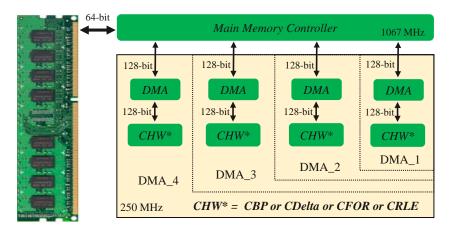

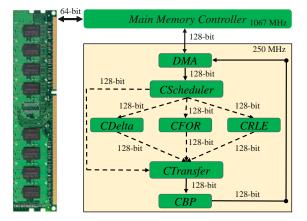

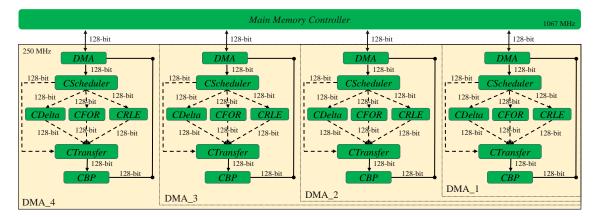

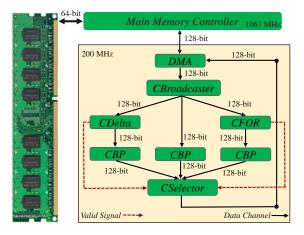

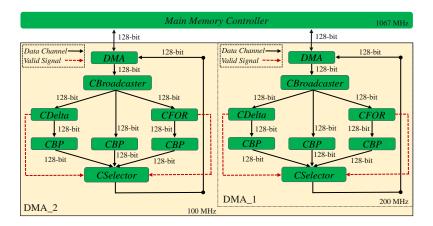

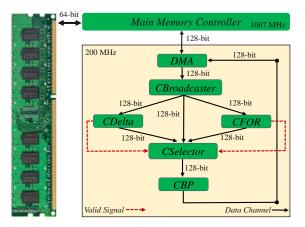

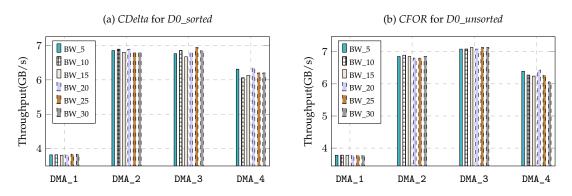

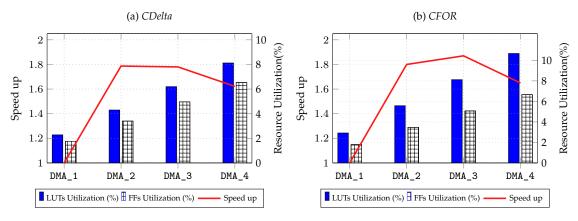

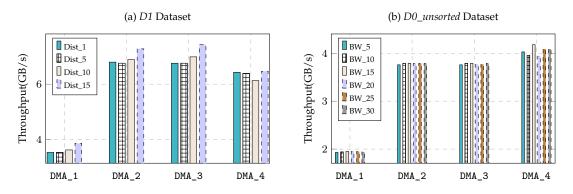

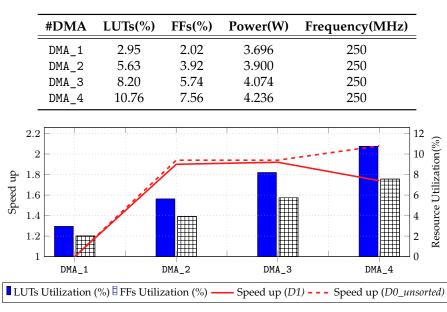

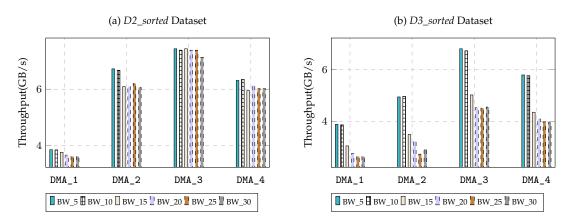

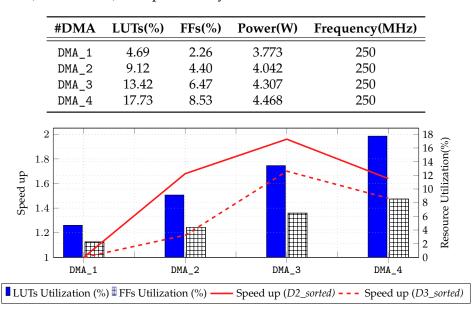

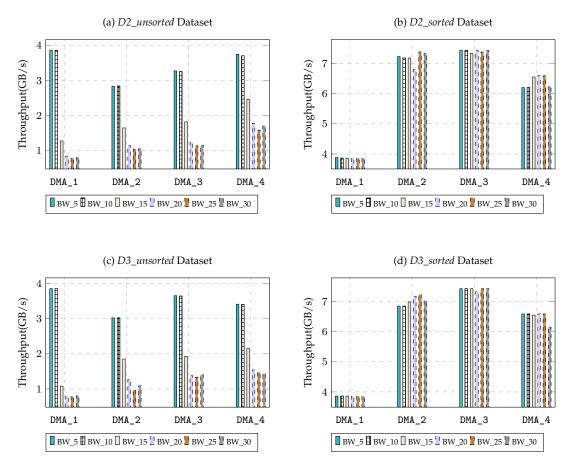

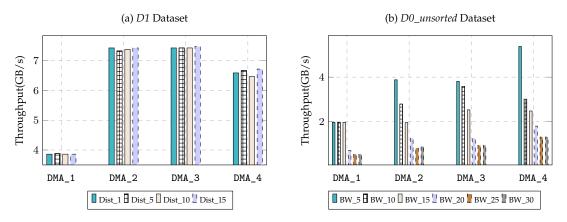

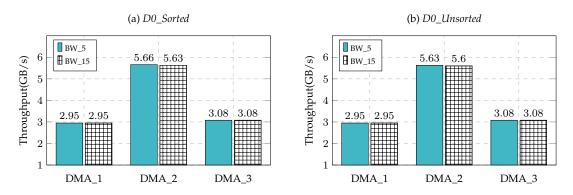

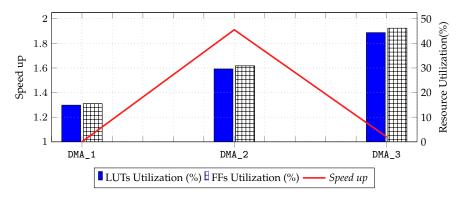

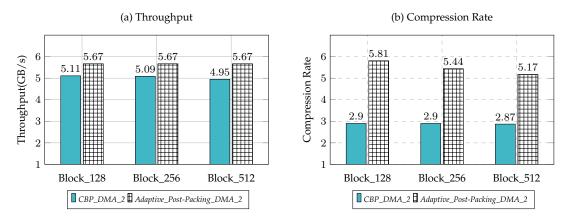

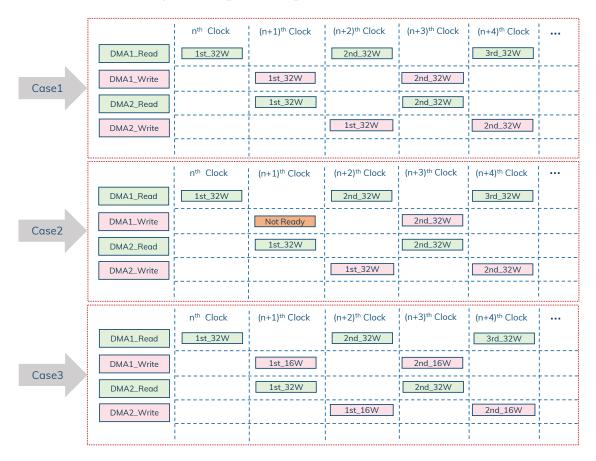

The traditional CPU-based MonetDB performs about 5x to 15x times slower than the FPGA-based regular expression system [SIOA17]. In other words, the FPGA-based regular expression system is capable of speeding up complex pattern matching by an order of magnitude in comparison to the database running on a 10-core CPU. In conclusion, Sidler et al. [SIOA17] proposed regular expression *HUDF* not only shows a significant acceleration of query execution in comparison to traditional MonetDB, but also provides predictable performance independent of regular expression complexity.