## **Aalborg Universitet**

## An Original Hybrid Multilevel DC-AC Converter Using Single-Double Source Unit for **Medium Voltage Applications**

Hardware Implementation and Investigation

Almakhles, Dhafer J.; Ali, Jagabar Sathik Mohamed; Padmanaban, Sanjeevikumar; Bhaskar, Mahajan Sagar; Subramaniam, Umashankar; Sakthivel, Rathinasamy

Published in: **IEEE Access**

DOI (link to publication from Publisher): 10.1109/ACCESS.2020.2986932

Creative Commons License CC BY 4.0

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Almakhles, D. J., Ali, J. S. M., Padmanaban, S., Bhaskar, M. S., Subramaniam, U., & Sakthivel, R. (2020). An Original Hybrid Multilevel DC-AC Converter Using Single-Double Source Unit for Medium Voltage Applications: Hardware Implementation and Investigation. *IEEE Access*, *8*, 71291-71301. https://doi.org/10.1109/ACCESS.2020.2986932

**General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Received March 22, 2020, accepted April 1, 2020, date of publication April 9, 2020, date of current version April 29, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.2986932

# An Original Hybrid Multilevel DC-AC Converter Using Single-Double Source Unit for Medium Voltage Applications: Hardware Implementation and Investigation

DHAFER J. ALMAKHLES<sup>10</sup>, (Member, IEEE),

JAGABAR SATHIK MOHAMED ALI<sup>10</sup>, (Senior Member, IEEE),

SANJEEVIKUMAR PADMANABAN<sup>10</sup>, (Senior Member, IEEE),

MAHAJAN SAGAR BHASKAR<sup>10</sup>, (Member, IEEE),

UMASHANKAR SUBRAMANIAM<sup>1</sup>, (Senior Member, IEEE),

AND RATHINASAMY SAKTHIVEL<sup>10</sup>

<sup>1</sup>Renewable Energy Lab (REL), Department of Communication and Networks, College of Engineering, Prince Sultan University (PSU), Riyadh 11586, Saudi Arabia

Corresponding author: Mahajan Sagar Bhaskar (agar25.mahajan@gmail.com)

This work was supported by the Renewable Energy Lab (REL), College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia, through the Scheme of Postdoctoral Fellowship under Grant PSU/12REL2019/PDF001.

**ABSTRACT** In this article, an original hybrid multilevel DC-AC converter configurations are proposed by using single-double source unit for medium voltage applications. The proposed topologies are derived by hybridization of single and double source units with polarity changer and cascaded with full-bridge converter for medium and high voltage applications. Two different hybrid topologies presented and each topology configured for both symmetric and asymmetric method. The proposed hybrid topologies compared with the conventional cascaded H-bridge converter (CHB), and the best topologies recommended for medium voltage applications. The comparison in terms of the number of switches, gate driver circuits, maximum blocking voltage by switches and total peak inverse voltages of switches presented. The proposed topologies require a small installation area and low cost. The validity of the proposed hybrid converter structures is verified by simulation using MATLAB/Simulink and hardware results. The simulation and hardware results show a good agreement with the theoretical approach.

**INDEX TERMS** Harmonics distortion, multilevel converters, hybrid converter topology, power switches, symmetric and asymmetric inverter.

#### I. INTRODUCTION

Multilevel DC-AC converters are the preferred choice of a power converter in medium voltage and high power applications. Generally, the multilevel converters generated staircase output voltage with several D.C. source as input [1]–[3]. The multilevel converter has numerous advantages over two-level inverter like low output voltage total harmonic distortion (THD), low Electromagnetic Interference (EMI), reduced the size of L.C. filter, low dv/dt stress and overall higher

The associate editor coordinating the review of this manuscript and approving it for publication was Ramazan Bayindir.

efficiency [4]–[8]. The three primary conventional multilevel converters are Neutral Point Clamped (NPC), Flying Capacitor (F.C.) and Cascaded H-bridge (CHB) multilevel inverter. The main advantage of Neutral Point Clamped (NPC) topology is that it is more suitable for back to back operation in HVDC applications. However, NPC has some drawbacks including the following: 1) it generates output voltage equals half of the input voltage; it requires additional circuits for voltage balancing of DC-link capacitor, and 3) it uses high number of power diode [9]. Flying capacitor (F.C.) [10] converter topology produces full input voltage at the output, but this topology uses a large number of DC-link capacitor to

<sup>&</sup>lt;sup>2</sup>Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark

<sup>&</sup>lt;sup>3</sup>Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Chennai 603203, India

<sup>&</sup>lt;sup>4</sup>Department of Applied Mathematics, Bharathiar University, Coimbatore 641046, India

achieve a high number of output voltage levels. Furthermore, the reliability of the converter is reduced due to the large number of capacitors used in this design. Cascaded H-bridge converter (CHB) [11]-[13] topology is attractive due to their modular structure and more redundant state. This topology consists of a series connection full-bridge two-level inverter with isolated D.C. source, and it does not require any additional power electronic components. This topology configured as symmetric and asymmetric methods. In the symmetric configuration, the magnitude of all the dc sources are equal and results in a large number of power electronic switches to obtain the high number of output voltage which is not the case in an asymmetric configuration where the magnitude of D.C. source can determine in geometric progression (binary and trinary method). Therefore, it requires fewer switches to generate a high number of voltage levels. Generally, the conventional multilevel inverter topology always requires the high number of switches to generate a higher number of output voltage levels. As a result, the switching pulse generation is sophisticated, the installation area is large, and the total cost of the converter is high.

New symmetric multilevel converter, non-isolated dc sources with bidirectional switches presented [14]. This converter topology uses various voltage ratings of power switches. It can be extended to n number of sources and required *n* number of the various voltage rating of switches. A new semi-cascaded inverter is proposed in [15], which configured in both symmetric and asymmetric configuration. However, this topology requires a large number of power switches and its maximum blocking voltage is relatively high. Another non-isolated dc source with bidirectional switches presented in [16]. A large number of switches reduced in this topology, but it requires various voltage rating of power switches which increase the cost of the converter. Besides, it is not a viable solution for high voltage applications due to more voltage stress across the full-bridge switches. For utilize this topology in high voltage applications, the full-bridge converter cascaded with symmetric topology. However, these topologies are not suitable for high voltage applications due to high voltage stress of switches. Motivated by the above discussion, and to increase efficiency and reduce the number of switches and a variety of dc sources for high voltage application, two-hybrid converter topologies presented in this article.

The proposed topology has the following advantages:

- The proposed topology generates a higher number of voltage level with fewer power switches count, which further reduces the number of gate driver circuits, heat sink, size and layout of the circuit.

- The voltage stress on full-bridge switches reduced.

- The proposed hybrid topology I have high modularity.

- In the asymmetric configuration, the number of isolated dc sources reduced.

- The number of ON state switches are less, which leads to a more reduction in power loss.

#### **II. PROPOSED MULTILEVEL INVERTER TOPOLOGY**

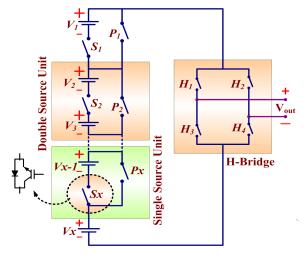

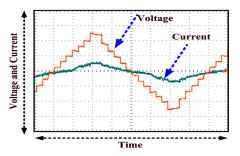

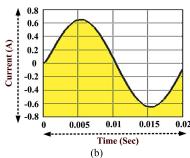

A new multilevel converter with a smaller number of power switches proposed by using single and double source unit. The series/parallel combination of switches connected with single and double source unit. The single source unit consists of one dc source connected with series/parallel combination of power switches, and standing voltage of the switch is  $V_{dc}$ . In double source unit, two dc sources connected along with series/parallel switches, but the standing voltage of switches is  $2V_{dc}$ . The multilevel structure constructed with a combination of both single-double source units (SDS Unit) as shown in Fig. 1, and the 13-level output voltage and current waveforms shown in Fig. 2. The basic unit consists of n number of dc sources, and all these source magnitudes are equal to generate 2n + 1 level. The full-bridge converter used to produce both positive and negative output voltage, and it withstood for the sum of all the dc source magnitude values. In Table 1, the proposed converter topology is compared with Cascaded H-Bridge (CHB) multilevel inverter. The maximum output voltage  $V_{o,max}$  of the proposed topology expressed as,

$$V_{o,max} = \sum_{i=1}^{n} V_i \tag{1}$$

where *n* denotes the number of isolated dc source presented in the input side. The power loss on a switch is the sum of both

FIGURE 1. Generalized structure of proposed multilevel inverter topology.

FIGURE 2. 13 level output voltage and current waveform.

switching and conduction losses. The voltage drop across each switch is undesirable. The losses considered while the switch is changed from ON state to OFF state and vice versa. The voltage drops of each switch are assumed to be  $V_{T.}$ , the maximum output voltage with power losses calculated as follows,

$$V_{o,max} = \sum_{i=1}^{n} V_i - nV_T \tag{2}$$

# III. HYBRID STRUCTURE OF PROPOSED MULTILEVEL CONVERTER

The proposed topology uses a lower number of switches; however, restricted for high voltage applications due to its high voltage stress across the full-bridge converter. For utilizing the proposed topology in high voltage applications, two new hybrid multilevel topologies presented in this section.

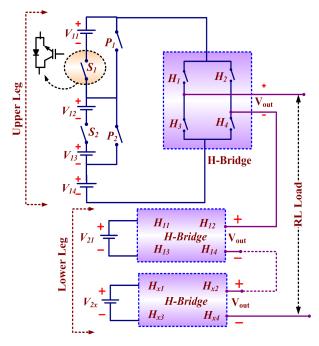

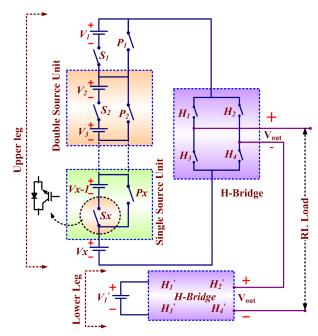

#### A. HYBRID TOPOLOGY I

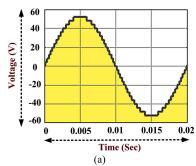

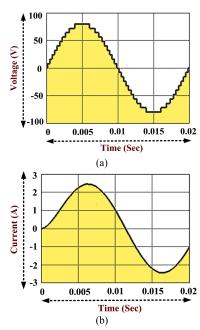

In hybrid topology, I, the maximum output voltage level is generated with a minimum number of switches. For example, if n=4 considered as the basic unit, then it consists of four dc sources and eight switches with maximum possible of the 9-level output voltage. In this topology, the magnitude of each dc source is equal. This proposed multilevel topology (discussed in section-2) is hybrid with conventional cascaded H-bridge inverter as shown in Fig. 3, in which nU and nL represent the number of dc source presented in the upper leg and lower leg, respectively. The corresponding 27 level output voltage and current waveforms are shown in Fig. 4(a) and Fig. 4(b).

FIGURE 3. Generalized structure of proposed hybrid basic unit with Cascaded H-Bridge (Hybrid Topology I).

FIGURE 4. Simulation output results of hybrid proposed topology I for 27 Level (a) Voltage waveform (b) Current waveform.

For symmetrical configurations, the magnitude of n number of dc source for both basic unit and CHB is equal, and equations expressed as follows,

$$\begin{pmatrix} V_{11} = V_{12} \\ = V_{13} = V_{14} \end{pmatrix} = V_{dc}; \quad \begin{pmatrix} V_{21} = V_{22} \\ = \dots = V_{2n} \end{pmatrix} = V_{dc} \quad (3)$$

For asymmetric configurations, the magnitude of basic unit dc sources is,

$$V_{11} = V_{12} = V_{13} = V_{14} = V_{dc} (4)$$

The magnitude of dc sources for cascaded H-Bridge unit are expressed as follow,

$$\begin{cases}

1^{st} \ Unit \ V_{21} = (2nU+1) * V_{dc} \\

2^{nd} \ Unit \ V_{22} = V_{21} * 3 * V_{dc} \\

3^{rd} \ Unit \ V_{23} = V_{22} * 3 * V_{dc} \\

k^{th} \ Unit \ V_{2n} = V_{2n-1} * 3 * V_{dc}

\end{cases} (5)$$

#### B. HYBRID TOPOLOGY II

The basic unit of the proposed topology is hybrid with the full-bridge converter (Hybrid Topology II) as shown in Fig. 5 and its corresponding simulated 21 level output voltage and current waveforms shown in Fig. 6(a) and Fig. 6(b). For symmetrical configurations, the magnitude of *n* number of dc source for symmetric topology and the full-bridge unit is equal, and equations expressed as follows,

$$V_1 = V_2 = V_3 = \dots V_n = V_{dc}; \quad V'_1 = V_{dc}$$

(6)

For asymmetric configurations, the magnitude of extended unit dc sources is as,

$$V_1 = V_2 = V_3 = \dots V_n = V_{dc}$$

(7)

| Description                | Proposed Topology (Fig. 1)                                             | Conventional Cascaded H-Bridge (CHB) |  |

|----------------------------|------------------------------------------------------------------------|--------------------------------------|--|

| No. of dc source           | n                                                                      | n                                    |  |

| No. of switches            | $N_{Switch} = \begin{cases} n+5, n = odd \\ n+4, n = even \end{cases}$ | 4n                                   |  |

| No. of output levels       | 2n+1                                                                   | 2n+1                                 |  |

| Maximum output voltage     | $n^*V_{dc}$                                                            | $n*V_{dc}$                           |  |

| Maximum blocking Voltage   | $n^*V_{dc}$                                                            | $V_{dc}$                             |  |

| Total Peak Inverse Voltage | $V_{max} = (6n - 2)V_{s}$                                              | $A *_{n} *_{V}$                      |  |

TABLE 1. Comparison of proposed topology with cascaded multilevel inverter.

FIGURE 5. Generalized structure of proposed hybrid extended symmetrical topology full bridge (Hybrid Topology II).

The magnitude of dc sources for full-bridge unit follows,

$$V_1' = 2nU + 1 \tag{8}$$

where nU is the number of dc source in an extended unit of the proposed multilevel inverter. The required number of switches, number of levels, maximum blocking voltage and total standing voltage of switches presented for both symmetric and asymmetric configurations of Hybrid Topology I and II in Table 2 and Table 3, respectively.

#### IV. COMPARISON OF MULTILEVEL CONVERTERS

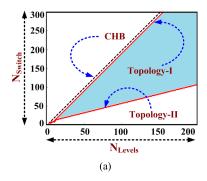

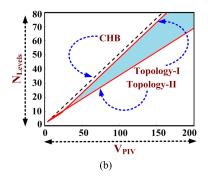

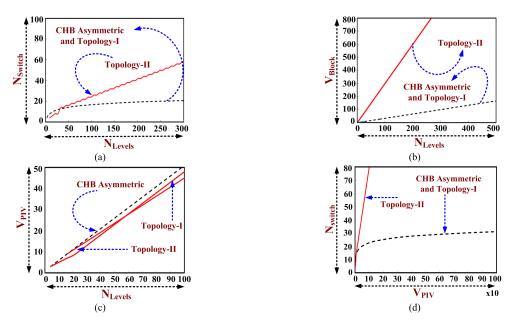

The hybrid topology I and conventional CHB multilevel inverter produce very close results in terms of the number of switches and total peak inverse voltage. The number of switches in topology II is lower than the other two topologies, but the total peak inverse voltage is higher in topology II as presented in Fig. 7(a) and Fig. 7(b), respectively. For generate maximum output voltage level with reduced dc source and switches, the asymmetric configurations are preferable, but they require a variety of dc source voltage value and different voltage ratings of switches. Two different methods used to determine the magnitude of dc sources in CHB asymmetric

FIGURE 6. Simulation output results of hybrid proposed topology II for 21 level (a) voltage waveform (b) current waveform.

configuration; those are binary (power of 2) and trinary (power of 3) configuration. In this paper, the trinary configuration is considered because it is capable of producing a maximum output voltage level with minimum switches.

For comparisons, the graph of the number of switches  $(N_{switch})$  versus the number of levels  $(N_{Level})$ , number of blocks ( $N_{Blocks}$ ) versus the number of levels ( $N_{Level}$ ), switch Peak Inverse Voltage  $(V_{PIV})$  versus the number of levels  $(N_{Level})$  and number of switches  $(N_{switch})$  versus switch Peak Inverse Voltage  $(V_{PIV})$  depicted in Fig. 8(a)-8(d), respectively. In Table 4, the symmetric configuration of multilevel inverter compared for maximum output voltage level against equals the power component. In hybrid topology I, maximum blocking voltage of switches is  $k^{th}$  cascaded h-bridge unit switches  $(2nUL + 1)x(3k-1)V_{dc}$  and basic unit full-bridge converter blocking voltage is  $4V_{dc}$ . In [17], the auxiliary circuit is hybrid with the full-bridge converter. In this topology, the maximum blocking voltage of switches is higher than the hybrid topology I. The proposed hybrid topology I and CHB Trinary configuration uses the lower number of switches for any given number of voltage levels in comparison with proposed hybrid topology II. The basic unit full-bridge converter has to withstand for a maximum of  $4V_{dc}$  whereas in hybrid

TABLE 2. Power component requirements for proposed hybrid topology I.

| Description                | Topology I (nU=4)                                    |                                                                                    |  |  |

|----------------------------|------------------------------------------------------|------------------------------------------------------------------------------------|--|--|

| Description                | Symmetric Configuration                              | Asymmetric Configuration                                                           |  |  |

| Number of Level            | $N_{\text{Step}} = 2nL + 9$                          | $N_{\text{Step}} = (3^{nL+2})$                                                     |  |  |

| Number of Switches         | $N_{Switches} = 8 + nL * 4$                          | $N_{\text{Switches}} = 8 + nL * 4$                                                 |  |  |

| Number of Gate Driver      | $N_{Driver} = 8 + nL * 4$                            | $N_{Driver} = 8 + nL * 4$                                                          |  |  |

| Maximum Blocking Voltage   | $V_{Block}$ = 4 * $V_{dc}$                           | $V_{\text{Block}} = \left(\frac{1 - 3^{\text{nL} + 2}}{-2}\right) * V_{\text{dc}}$ |  |  |

| Total Peak Inverse Voltage | $V_{\text{PIV}} = (22 + 4\text{nL}) * V_{\text{dc}}$ | $V_{PIV} = \left[4*\left(\frac{1-3^{nL+2}}{-2}\right) + 6\right]*V_{dc}$           |  |  |

TABLE 3. Power component requirements for proposed hybrid topology II.

| Description                | Topology II (nL=1)                                                                                                                                                   |                                                                                      |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Description                | Symmetric Configuration                                                                                                                                              | Asymmetric Configuration                                                             |  |  |

| Number of Level            | $N_{Step} = 2nU + 3$                                                                                                                                                 | $N_{\text{Step}} = 3*(2nU+1)$                                                        |  |  |

| Number of Switches         | $N_{\text{Swicth}} = \begin{cases} 8 & \text{nU} = 1\\ \text{nU} + 9, \text{ nU} = \text{Odd}, \text{ nU} > 1\\ \text{nU} + 8, \text{ nU} = \text{Even} \end{cases}$ | $N_{Switch} = \begin{cases} nU + 9 \ , nU = Odd \\ nU + 8 \ , nU = Even \end{cases}$ |  |  |

| Number of Gate Driver      | $N_{Driver} = \begin{cases} 8 & , & nU = 1\\ nU + 9, & nU = Odd & nU > 1\\ nU + 8, & nU = Even \end{cases}$                                                          | $N_{Driver} = \begin{cases} nU + 9, nU = Odd \\ nU + 8, nU = Even \end{cases}$       |  |  |

| Maximum Blocking Voltage   | $V_{\text{Block}} = (N_{\text{Level}} - 3) * V_{\text{dc}}$                                                                                                          | $V_{\text{Block}} = (2nU + 1) * V_{\text{dc}}$                                       |  |  |

| Total Peak Inverse Voltage | $V_{PIV} = ((6nU + 2) * V_{dc}$                                                                                                                                      | $V_{PIV} = ((14nU + 2) * V_{dc}$                                                     |  |  |

FIGURE 7. Comparison of symmetric configuration of Hybrid Topology I and II with Cascaded H-Bridge multilevel inverter (a) Graph of number of switches versus number of levels (b) Graph of number of levels versus Peak Inverse Voltage (PIV or V<sub>PIV</sub>) of switch.

topology II is  $n * V_{dc}$ , and thus it is restricted to high power applications.

#### **V. NEAREST LEVEL MODULATION SCHEME**

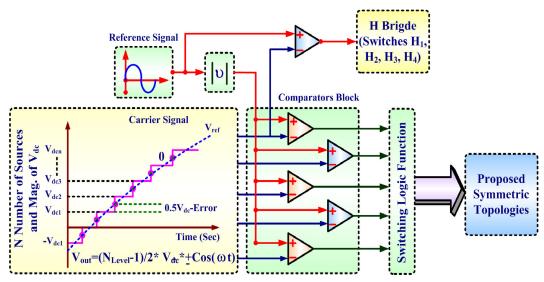

Several high and low switching frequency modulation techniques proposed for multilevel converters such as multi-carrier PWM, Space Vector PWM, Selective Harmonic Elimination Method, hybrid modulation and fundamental switching. The nearest level control modulation technique used to control proposed inverter topologies is shown in Fig. 9. The switching sequence for topologies I and II are given in Table 5 and VI, respectively.  $L_1$  to  $L_{12}$  are the comparator output, as shown in Fig. 9, and  $\bar{L}_1$  to  $\bar{L}_{12}$  is the NOT of the comparator output.

The switching logic equations for 27 level hybrid topology I are as follows,

y I are as follows,

$$P_1 = (L_1 \&\& \overline{L_2}) + (L_3 \&\& \overline{L_4}) + (L_6 \&\& \overline{L_7})$$

$$+ (L_8 \& \overline{L_9}) + (L_{10} \& \overline{L_{11}}) + L_{12}$$

(9)

$$P_2 = (L_1 \& \overline{L_3}) + (L_7 \& \overline{L_9}) + (L_{10} \& \overline{L_{12}})$$

(10)

$$H_1 = L_1 \&\& \overline{L_{11}} \tag{11}$$

$$H_1' = (L_1 \&\& \overline{L_5}) + L_9 \tag{12}$$

$$H_2' = \left(L_8 \& \& \overline{L_9}\right) \tag{13}$$

$$H'_2 = (L_8 \& \& L_9)$$

(13)

$H'_3 = (L_4 \& \& L_9)$  (14)

$$H_4' = L_9 \tag{15}$$

$$H_4 = (L_1 \&\& \overline{L_9}) + L_{10} \tag{16}$$

FIGURE 8. Comparison of asymmetric configuration of Hybrid Topology I and II with Cascaded H-Bridge multilevel inverter (a) Graph of number of switches versus number levels (b) graph of number of blocks versus number levels (c) graph of PIV or V<sub>PIV</sub> of switch versus number levels (d) graph of number of switch versus PIV or V<sub>PIV</sub> of switch.

TABLE 4. Comparison of symmetric configuration of multilevel inverter for maximum output voltage level against equal power component.

| Description                               | СНВ   | [19]  | [17]  | Hybrid<br>Topology I | Hybrid<br>Topology II |

|-------------------------------------------|-------|-------|-------|----------------------|-----------------------|

| Number of Level                           | 13    | 17    | 23    | 17                   | 35                    |

| Number of Switches (BUP400D)              | 24    | 24    | 24    | 24                   | 24                    |

| Number of gate driver circuits (HCPL316j) | 24    | 24    | 14    | 24                   | 24                    |

| Number of ON state switches               | 12    | 12    | 4     | 12                   | 11                    |

| THD %                                     | 6.39% | 4.84% | 3.56% | 4.84%                | 2.33%                 |

FIGURE 9. Schematic of nearest level control modulation technique to control proposed inverter.

The switching logic equations for 21 level hybrid topology II are as follows,

$$P_2 = (L_1 \&\& \overline{L_3}) + (L_6 \&\& \overline{L_7}) + (L_8 \&\& \overline{L_9}) + (L_{10})$$

(18)

$$H_1 = L_1 \tag{19}$$

$$P_{1} = (L_{1} \& \& \overline{L_{2}}) + (L_{3} \& \& \overline{L_{4}})$$

$$+ (L_{6} \& \& \overline{L_{7}}) + (L_{8} \& \& \overline{L_{9}}) + (L_{10})$$

$$(17) \qquad H'_{1} = (L_{1} \& \& \overline{L_{3}}) + L_{7}$$

$$(20)$$

$$H'_{1} = (L_{1} \& \& \overline{L_{3}}) + L_{7}$$

$$(21)$$

TABLE 5. Switching sequence for proposed 27 level hybrid topology I.

| T1    |                                 | ON State Switches                                                 | Outmut Waltage                                                           |                                          |

|-------|---------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------|

| Level | Upper Leg                       | Upper Leg H Bridge                                                | Lower Leg H Bridge                                                       | Output Voltage                           |

| 0     | -                               | H <sub>1</sub> ,H <sub>2</sub> or H <sub>3</sub> , H <sub>4</sub> | H <sub>1</sub> ', H <sub>2</sub> ' or H <sub>3</sub> ', H <sub>4</sub> ' | 0 V                                      |

| +1    | $P_1, P_2$                      | $H_{1}, H_{4}$                                                    | H <sub>1</sub> ', H <sub>2</sub> '                                       | $+V_{14}$                                |

| +2    | S <sub>1</sub> , P <sub>2</sub> | $H_{1}, H_{4}$                                                    | H <sub>1</sub> ', H <sub>2</sub> '                                       | $+V_{11}+V_{14}$                         |

| +3    | $S_2, P_1$                      | $H_1, H_4$                                                        | H <sub>1</sub> ', H <sub>2</sub> '                                       | $+V_{12}+V_{13}+V_{14}$                  |

| +4    | $S_1, S_2$                      | $H_1, H_4$                                                        | H <sub>1</sub> ', H <sub>2</sub> '                                       | $+V_{11}+V_{12}+V_{13}+V_{14}$           |

| +5    | $S_1, S_2$                      | $H_1, H_4$                                                        | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{11}+V_{12}+V_{13}+V_{14})+V_{21}$ |

| +6    | $S_2, P_1$                      | $H_1, H_4$                                                        | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{12}+V_{13}+V_{14})+V_{21}$        |

| +7    | $S_1, P_2$                      | $H_1, H_4$                                                        | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{11}+V_{14})+V_{21}$               |

| +8    | $P_2, P_1$                      | $H_1, H_4$                                                        | H <sub>2</sub> ', H <sub>3</sub> '                                       | -(+V <sub>14</sub> )+V <sub>21</sub>     |

| +9    | -                               | $H_1, H_2$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $+V_{21}$                                |

| +10   | $P_2, P_1$                      | $H_1, H_4$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $+V_{14}+V_{21}$                         |

| +11   | S <sub>1</sub> , P <sub>2</sub> | $H_1, H_4$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $+V_{11}+V_{14}+V_{21}$                  |

| +12   | $S_2, P_1$                      | $H_1, H_4$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $+V_{12}+V_{13}+V_{14}+V_{21}$           |

| +13   | $S_1, S_2$                      | $H_1, H_4$                                                        | $H_{1}', H_{4}'$                                                         | $+V_{11}+V_{12}+V_{13}+V_{14}+V_{21}$    |

| -13   | $S_1, S_2$                      | $H_2, H_3$                                                        | $H_2', H_3'$                                                             | $-(+V_{11}+V_{12}+V_{13}+V_{14})-V_{21}$ |

| -12   | $S_2, P_1$                      | $H_2, H_3$                                                        | $H_2', H_3'$                                                             | $-(+V_{12}+V_{13}+V_{14})-V_{21}$        |

| -11   | $S_1, P_2$                      | $H_2, H_3$                                                        | $H_2', H_3'$                                                             | $-(+V_{11}+V_{14})-V_{21}$               |

| -10   | $P_2, P_1$                      | $H_2, H_3$                                                        | H <sub>2</sub> ', H <sub>3</sub> '                                       | -V <sub>14</sub> -V <sub>21</sub>        |

| -9    | -                               | $H_2, H_3$                                                        | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-V_{21}$                                |

| -8    | $P_2,P_1$                       | $H_2, H_3$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $(+V_{14})-V_{21}$                       |

| -7    | $S_1,P_2$                       | $H_2, H_3$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $(+V_{11}+V_{14})-V_{21}$                |

| -6    | $S_2,P_1$                       | $H_2, H_3$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $(+V_{12}+V_{13}+V_{14})-V_{21}$         |

| -5    | $S_1,S_2$                       | $H_2, H_3$                                                        | H <sub>1</sub> ', H <sub>4</sub> '                                       | $(+V_{11}+V_{12}+V_{13}+V_{14})-V_{21}$  |

| -4    | $S_1,S_2$                       | $H_2,H_3$                                                         | H <sub>3</sub> ', H <sub>4</sub> '                                       | $-(+V_{11}+V_{12}+V_{13}+V_{14})$        |

| -3    | $S_2,P_1$                       | $H_2, H_3$                                                        | H <sub>3</sub> ', H <sub>4</sub> '                                       | $-(+V_{12}+V_{13}+V_{14})$               |

| -2    | $P_{2}, S_{1}$                  | $H_2, H_3$                                                        | H <sub>3</sub> ', H <sub>4</sub> '                                       | -(+V <sub>11</sub> +V <sub>14</sub> )    |

| -1    | $P_2,P_1$                       | $H_2, H_3$                                                        | H <sub>3</sub> ', H <sub>4</sub> '                                       | -(V <sub>14</sub> )                      |

TABLE 6. Switching sequence for proposed 21 level hybrid topology II.

| Level |                                 | ON State Switches               | Output Voltage                                                           |                                       |  |

|-------|---------------------------------|---------------------------------|--------------------------------------------------------------------------|---------------------------------------|--|

| Level | Upper Leg                       | Upper Leg H Bridge              | Lower Leg H Bridge                                                       | Output Voltage                        |  |

| 0     | -                               | $H_1, H_2 \text{ or } H_3, H_4$ | H <sub>1</sub> ', H <sub>2</sub> ' or H <sub>3</sub> ', H <sub>4</sub> ' | 0 V                                   |  |

| +1    | $P_2,P_1$                       | $H_1,H_4$                       | H <sub>1</sub> ', H <sub>2</sub> '                                       | $+V_{13}$                             |  |

| +2    | $P_2, S_1$                      | $H_1,H_4$                       | H <sub>1</sub> ', H <sub>2</sub> '                                       | $+V_{11}+V_{13}$                      |  |

| +3    | S <sub>2</sub> ,P <sub>1</sub>  | $H_1,H_4$                       | $H_1$ ', $H_2$ '                                                         | $+V_{12}+V_{13}+V_{11}$               |  |

| +4    | $S_2,P_1$                       | $H_1,H_4$                       | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{12}+V_{13}+V_{11})+V_{21}$     |  |

| +5    | $S_1,P_2$                       | $H_1,H_4$                       | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{11}+V_{12})+V_{21}$            |  |

| +6    | $P_2,P_1$                       | $H_1,H_4$                       | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{11})+V_{21}$                   |  |

| +7    | -                               | $H_1,H_2$                       | H <sub>1</sub> ', H <sub>4</sub> '                                       | $+V_{21}$                             |  |

| +8    | $P_2,P_1$                       | $H_1,H_4$                       | $H_{1}', H_{4}'$                                                         | $+V_{13}+V_{21}$                      |  |

| +9    | $S_1,P_2$                       | $H_1,H_4$                       | $H_1$ ', $H_4$ '                                                         | $+V_{11}+V_{12}+V_{21}$               |  |

| +10   | $S_2,P_1$                       | $H_1,H_4$                       | $H_{1}', H_{4}'$                                                         | $+V_{12}+V_{13}+V_{11}+V_{21}$        |  |

| -10   | $S_2,P_1$                       | $H_2,H_3$                       | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{12}+V_{13}+V_{11})-V_{21}$     |  |

| -9    | $S_1,P_2$                       | $H_2,H_3$                       | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-(+V_{11}+V_{12})-V_{21}$            |  |

| -8    | $P_2,P_1$                       | $H_2,H_3$                       | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-V_{13}-V_{21}$                      |  |

| -7    | -                               | $H_2,H_3$                       | H <sub>2</sub> ', H <sub>3</sub> '                                       | $-V_{21}$                             |  |

| -6    | $P_2,P_1$                       | $H_2,H_3$                       | $H_1$ ', $H_4$ '                                                         | $(+V_{13})-V_{21}$                    |  |

| -5    | $S_1,P_2$                       | $H_2,H_3$                       | H <sub>1</sub> ', H <sub>4</sub> '                                       | $(+V_{11}+V_{13})-V_{21}$             |  |

| -4    | $S_2,P_1$                       | $H_2,H_3$                       | H <sub>1</sub> ', H <sub>4</sub> '                                       | $(+V_{12}+V_{13}+V_{11})-V_{21}$      |  |

| -3    | $S_2,P_1$                       | $H_{2},H_{3}$                   | H <sub>3</sub> ', H <sub>4</sub> '                                       | $-(+V_{12}+V_{13}+V_{11})$            |  |

| -2    | P <sub>2</sub> , S <sub>1</sub> | $H_{2},H_{3}$                   | H <sub>3</sub> ', H <sub>4</sub> '                                       | -(+V <sub>13</sub> +V <sub>12</sub> ) |  |

| -1    | $P_2,P_1$                       | $H_2,H_3$                       | H <sub>3</sub> ', H <sub>4</sub> '                                       | -(V <sub>13</sub> )                   |  |

$$H_2' = L_6 \tag{22}$$

$$H_3' = \left(L_4 \& \& \overline{L_7}\right) \tag{23}$$

$$H_4' = L_7 \tag{24}$$

For the negative half cycle, the same logic function with the corresponding comparator signal given. This modulation technique operates under the fundamental switching frequency method. The fundamental switching method has low switching losses compared to other modulation strategies. The THD is another important measuring factor in the multilevel converter, which calculates the percentage of harmonic content present in the output waveform.

In general, the THD for the sinusoidal waveform calculated as follows:

$$THD = \frac{\sqrt{\left(\sum_{h=3,5,7....}^{\infty} V_{oh}\right)}}{V_{of}} = \sqrt{\left(\frac{V_{orms}}{V_{of}}\right)^2 - 1} \quad (25)$$

| TABLE 7.   | Comparison of the asymmetric configuration for equal number |

|------------|-------------------------------------------------------------|

| of level a | gainst number of power switches.                            |

| Description                                        | CHB<br>Asymmetric   | Hybrid<br>Topology I<br>Asymmetric | Hybrid<br>Topology II<br>Asymmetric | [16]         |

|----------------------------------------------------|---------------------|------------------------------------|-------------------------------------|--------------|

| Number of<br>Level                                 | 81                  | 81                                 | 81                                  | 81           |

| Number of<br>Switches<br>(BUP400D)                 | 16                  | 16                                 | 22                                  | 32           |

| Number of<br>gate driver<br>Circuits<br>(HCPL316j) | 16                  | 16                                 | 22                                  | 20           |

| Maximum<br>Blocking<br>Voltage                     | $27V_{dc}$          | $27V_{\rm dc}$                     | $27V_{dc}$                          | $27\;V_{dc}$ |

| Total Peak<br>Inverse<br>Voltage                   | $160 V_{\text{dc}}$ | $166 V_{\rm dc}$                   | $184 \rm{V}_{\rm{dc}}$              | $274V_{dc}$  |

| Variety of DC Source                               | 4                   | 3                                  | 2                                   | 2            |

where  $V_{orms}$  and  $V_{of}$  denote the magnitude of rms value and fundamental output voltage waveform, respectively. The  $V_{rms}$  and  $V_{of}$  calculated with the help of switching angles. The formula for finding switching angle represented as follows,

$$\theta_i = \sin^{-1}\left(\frac{i - 0.5}{N_{Level}}\right) \quad i = 1, 2, 3 \dots N_{Level}$$

(26)

The THD of the output voltage waveform depends on the number of levels and switching angles, which is not the case of current waveform because the inductive load acts as a low pass filter and brings to sinusoidal shape. The  $V_{out}$  of the proposed topology represented as,

$$V_{out} = (N_{Level} - 1) / 2^* V_{dc}^* \pm (\cos \omega t)$$

(27)

#### VI. EXPERIMENTAL RESULTS

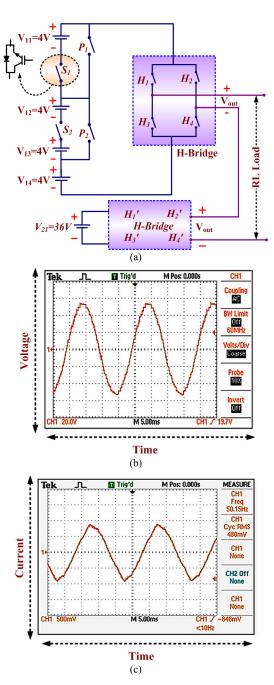

For analyze the operation of proposed topologies, the experimental test has conducted and results discussed. The nearest level control technique used to generate the appropriate gate pulses for the switches. For verify the performance of the proposed multilevel converter, an experimental prototype based on the primary unit configuration is developed for a resistive-inductive load of  $R=65~\Omega$  and  $L=40~\rm mH$ . Moreover, the conventional nearest-voltage level modulation technique, presented in [17], is embedded in the FPGA Spartan XE3S250E controller (that generates the trigger pulses to the appropriate switches) with a fundamental frequency of 50 Hz.

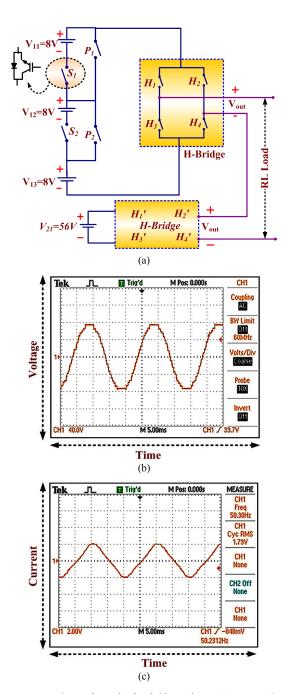

#### A. HYBRID TOPOLOGY I (ASYMMETRIC CONFIGURATION)

The 27-level hybrid topology I multilevel converter is simulated using MATLAB/Simulink and SimPower Systems toolbox for the proposed topologies. Topology I, asymmetric

FIGURE 10. Experimental circuit and result of Hybrid Topology I (a) Power circuit of 27 level Hybrid Topology I (b) Output voltage waveform (c) Output current waveform.

configuration showed in Fig. 10(a), the magnitude of dc sources of basic unit is  $V_{11} = V_{12} = V_{13} = V_{14} = 4$  V and the full-bridge converter voltage  $V_{21} = 36$  V for the resistive-inductive load value of 50  $\Omega$  and 60 mH. The hardware experimental output voltage and current waveform showed in Fig. 10(b) and Fig. 10(c), respectively. In hybrid topology, I, the maximum blocking voltage of the lower is 36 V, and upper leg is 16 V, the total peak inverse voltage is 232 V whereas in CHB trinary configuration uses 208 V,

FIGURE 11. Experimental Result of Hybrid Topology II (a) Power Circuit of 21 level Hybrid Topology II (b) Output voltage waveform (c) Output current waveform.

in case of topology [16]–[19] uses a higher number of blocking voltages.

# B. HYBRID TOPOLOGY II (ASYMMETRIC CONFIGURATION)

The hybrid topology II asymmetric configuration is shown in Fig. 11(a). The magnitude of dc sources of basic unit is  $V_{11} = V_{12} = V_{13} = 8 \text{ V}$  and the full-bridge converter voltage  $V_{21} = 56 \text{ V}$  for the resistive-inductive load value of 30  $\Omega$  and 45 mH. This topology is more suitable for the reduction

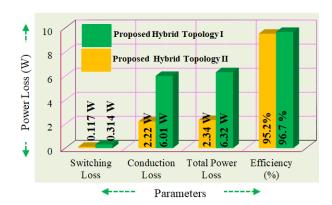

FIGURE 12. Plot of power Loss and efficiency.

of a variety of dc source because it uses two varieties of dc source for m-levels and the total peak inverse voltage is close to topology I and CHB. The hardware experimental output voltage and current waveforms are shown in Fig. 11(b) and Fig. 11(c). The maximum blocking voltage of upper leg full bridge converter is 24 V and lower leg is 56 V and total peak inverse voltage is 352 V.

Table 5 describes the equal number of levels produces by the various topologies with the different switch count. It is once again proved that the proposed topology I and CHB produces the same number of voltage level, whereas topology II and [16]–[19] uses a large number of switches. The maximum blocking voltage of all the topologies is the same; but, the total peak inverse voltage is higher in [16]–[19] due to various rating of bidirectional switches used. The plots of power loss and efficiency of the proposed topology given in Fig. 12, which shows that the proposed hybrid topology I have higher efficiency compared with topology II.

#### VII. CONCLUSION

In this article, a new single/double source unit-based hybrid multilevel converter topologies proposed for medium applications. The proposed multilevel converter uses a minimum number of power switches. The comparison of hybrids proposed symmetric and asymmetric topologies presented in terms of the number of switches, the number of gate driver circuits and total peak inverse voltage. These factors reduce the size of the circuit, installation area and total cost of the converter. In the symmetric configuration, the proposed hybrid topologies are superior to the conventional topology, but in case of asymmetric configuration, the proposed hybrid topology I and CHB use an equal number of switches for same output voltage level.

The proposed basic multilevel inverter and hybrid topology II are not suitable for high voltage applications due to restriction of maximum voltage stress on the full-bridge converter, and these topologies are suitable for medium voltage application like 2.0 kV -to- 6.0 kV grid-connected photovoltaic system. The proposed hybrid Topology I is suggested for high voltage applications because it is closer

to conventional CHB with increased stepped output voltage level as compared to conventional CHB topology.

#### **ACKNOWLEDGMENT**

The authors would like to thank Renewable Energy Lab, College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia for the financial support.

#### **REFERENCES**

- [1] L. Franquelo, J. Rodriguez, J. Leon, S. Kouro, R. Portillo, and M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol. 2, no. 2, pp. 28–39, Jun. 2008.

- [2] A. R. Kumar, M. S. Bhaskar, U. Subramaniam, D. Almakhles, S. Padmanaban, and J. B.-H. Nielsen, "An improved harmonics mitigation scheme for a modular multilevel converter," *IEEE Access*, vol. 7, pp. 147244–147255, 2019.

- [3] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Pérez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [4] B. Chokkalingam, M. S. Bhaskar, S. Padmanaban, V. K. Ramachandaramurthy, and A. Iqbal, "Investigations of multi-carrier pulse width modulation schemes for diode free neutral point clamped multilevel inverters," *J. Power Electron.*, vol. 19, no. 3, pp. 702–713, May 2019.

- [5] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," *IEEE Trans. Ind. Appl.*, vol. 35, no. 1, pp. 36–44, Jan./Feb. 1999.

- [6] P. Sanjeevikumar, M. S. Bhaskar, F. Blaabjerg, M. Pecht, L. Martirano, and M. Manganelli, "Dual six-phase multilevel AC drive with single carrier optimized five-level PWM for star-winding configuration," in *Advances* in Systems, Control and Automation (Lecture Notes in Electrical Engineering), vol. 442. Singapore: Springer, 2017, pp. 733–740.

- [7] M. S. Bhaskar, M. Meraj, A. Iqbal, L. Ben-Brahim, S. Padmanaban, and H. Abu-Rub, "Ε<sup>K</sup>θ multilevel inverter—A minimal switch novel configuration for higher number of output voltage levels," *IET Power Electron.*, early access, Jan. 2020. [Online]. Available: https://digitallibrary.theiet.org/content/journals/10.1049/iet-pel.2019.0945

- [8] S. Padmanaban, M. S. Bhaskar, F. Blaabjerg, L. E. Norum, S. Seshagiri, and A. Hajizadeh, "Nine-phase hex-tuple inverter for five-level output based on double carrier PWM technique," in *Proc. 4th IET Clean Energy Technol. Conf. (CEAT)*, Kuala Lumpur, Malaysia, Nov. 2016, pp. 91–97.

- [9] N. S. Choi, J. G. Cho, and G. H. Cho, "A general circuit topology of multilevel inverter," in *Proc. 22nd Annu. IEEE Power Electron. Spec. Conf.*, Cambridge, MA, USA, Jun. 1991, pp. 96–103.

- [10] J.-S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 509–517, May/Jun. 1996.

- [11] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

- [12] L. Jingsheng, W. Kai, and M. Ferdowsi, "Cascaded H-bridge multilevel inverters—A reexamination," in *Proc. IEEE Vehicle Power Propuls. Conf.* (*IEEE-VPPC*), Arlington, TX, USA, Sep. 2007, pp. 203–207.

- [13] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-voltage multilevel converters—State of the art, challenges, and requirements in industrial applications," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2581–2596, Aug. 2010.

- [14] M. F. Kangarlu, E. Babaei, and S. Laali, "Symmetric multilevel inverter with reduced components based on non-insulated DC voltage sources," *IET Power Electron.*, vol. 5, no. 5, pp. 571–581, 2012.

- [15] M. R. Banaei, M. R. J. Oskuee, and H. Khounjahan, "Reconfiguration of semi-cascaded multilevel inverter to improve systems performance parameters," *IET Power Electron.*, vol. 7, no. 5, pp. 1106–1112, May 2014.

- [16] R. S. Alishah, M. Sabahi, D. Nazarpour, and S. H. Hosseini, "Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches," *IET Power Electron.*, vol. 7, no. 12, pp. 3062–3071, Dec. 2014.

- [17] S. Thamizharasan, S. Jeevananthan, J. Baskaran, and S. Ramkumar, "Cross-switched multilevel inverter using auxiliary reverse-connected voltage sources," *IET Power Electron.*, vol. 7, no. 6, pp. 1519–1526, Jun. 2014.

- [18] S. Kouro, R. Bernal, H. Miranda, C. A. Silva, and J. Rodriguez, "High-performance torque and flux control for multilevel inverter fed induction motors," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2116–2123, Nov. 2007.

- [19] A. Ajami, A. Mokhberdoran, M. R. J. Oskuee, and M. T. Khosroshahi, "Cascade-multi-cell multilevel converter with reduced number of switches," *IET Power Electron.*, vol. 7, no. 3, pp. 552–558, Mar. 2014.

**DHAFER J. ALMAKHLES** (Member, IEEE) received the B.E. degree in electrical engineering from the King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia, in 2006, and the master's degree (Hons.) and Ph.D. degree from The University of Auckland, New Zealand, in 2011 and 2016, respectively.

Since 2016, he has been with Prince Sultan University, Saudi Arabia, where he is currently the Chairman of the Communications and Networks

Engineering Department, and the Director of the Science and Technology Unit and Intellectual Property Office, Prince Sultan University. He is the Leader of the Renewable Energy Research Team and Laboratory. His research interests include power electronics, control theory, crewless aerial vehicles, renewable energy systems, and FPGA applications. He is a member of the IEEE Power Electronics and the IEEE Control Society. He is a Reviewer Member of various international journals and conferences, including the IEEE and IET.

JAGABAR SATHIK MOHAMED ALI (Senior Member, IEEE) was born in Thanjavur, India, in 1979. He received the B.E. degree in electronics and communication engineering from Madurai Kamarajar University, Madurai, India, in 2002, and the M.E. and Ph.D. degrees from the Faculty of Electrical Engineering, Anna University, Chennai, India, in 2004 and 2016, respectively.

He is currently a Postdoctoral Fellow with the Renewable Energy Lab, College of Engineering

Department, Prince Sultan University, Riyadh, Saudi Arabia. He is a Consultant of various power electronics companies for the design of power electronics converters in India. He has authored more than 30 articles publications in international peer-reviewed journals and conference proceedings. His research interests include multilevel inverters, grid-connected inverters, and power electronics converters and its applications to renewable energy systems. He is serving as a Regular Reviewer for several journals, including the IEEE Transactions on Industrial Electronics, *Transactions on Power Electronics*, and IEEE Access.

SANJEEVIKUMAR PADMANABAN (Senior Member, IEEE) received the bachelor's degree in electrical engineering from the University of Madras, Chennai, India, in 2002, the master's degree (Hons.) in electrical engineering from Pondicherry University, Puducherry, India, in 2006, and the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012.

He was an Associate Professor with VIT University, from 2012 to 2013. In 2013, he joined the National Institute of Technology, India, as a Faculty Member. In 2014, he was invited as a Visiting Researcher with the Department of Electrical Engineering, Qatar University, Doha, Qatar, funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Dublin, Ireland, in 2014. He was an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, Johannesburg, South Africa, from 2016 to 2018. Since 2018, he has been a Faculty Member with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. He has authored more than 300 scientific articles. He is a Fellow of the Institution of Engineers, India, the Institution of Electronics and Telecommunication Engineers, India, and the Institution of Engineering and Technology, U.K. He was a recipient of the Best Paper cum Most Excellence Research Paper Award from IET-SEISCON'13, IET-CEAT'16, the IEEE-EECSI'19, the IEEE-CENCON'19, and five best paper awards from ETAEERE'16 sponsored Lecture Notes in electrical engineering (Springer). He is the Editor/Associate Editor/Editorial Board for refereed journals, in particular the IEEE Systems Journal, IEEE Access, IET Power Electronics, and Journal of Power Electronics (South Korea), and the Subject Editor for the IET Renewable Power Generation, IET Generation, Transmission and Distribution, and FACTS journal (Canada).

UMASHANKAR SUBRAMANIAM (Senior Member, IEEE) is with the Renewable Energy Lab, College of Engineering, Prince Sultan University, Saudi Arabia. He worked as a Associate Professor and the Head of VIT, Vellore, and a Senior Research and Development and Senior Application Engineer in the field of power electronics, renewable energy and electrical drives. He is a member of IACSIT, IDES, and ISTE. He has more than 15 years of teaching, research,

and industrial Research and Development experience. He has published more than 250 research articles in national and international journals and conferences. He has also authored/coauthored/contributed 12 books/chapters and 12 technical articles on power electronics applications in renewable energy and allied areas. Under his guidance, 24 PG students and more than 25 UG Students completed the senior design project work. Also, six Ph.D. scholars completed Ph.D. thesis as Research Associate. He is also involved in collaborative research projects with various international and national level organizations and research institutions. He was an Executive Member, from 2014 to 2016. He received the Danfoss Innovator Award-Mentor from 2014 to 2015 and 2017 to 2018, the Research Award in VIT University, from 2013 to 2018, the INAE Summer Research Fellowship for the year 2014. He is the Vice-Chair of the IEEE MAS Young Professional, from 2017 to 2019 by the IEEE Madras Section. He has taken charge as the Vice-Chair of the IEEE Madras Section, the Chair of the IEEE Student Activities, from 2018 to 2019. He is the Editor of Heliyon (Elsevier).

MAHAJAN SAGAR BHASKAR (Member, IEEE) received the bachelor's degree in electronics and telecommunication engineering from the University of Mumbai, Mumbai, India, in 2011 and the master's degree in power electronics and drives from VIT University, India, in 2014, and the Ph.D. degree in electrical and electronic engineering, University of Johannesburg, South Africa, in 2019. He worked as a Researcher Assistant with the Department of Electrical Engineering, Qatar Uni-

versity, Doha, Qatar, from 2018 to 2019. He worked as a Research Student with the Power Quality Research Group, Department of Electrical Power Engineering, Universiti Tenaga Nasional (UNITEN), Private University, Kajang, Kuala Lumpur, Malaysia, from August 2017 to September 2017. He is currently with the Renewable Energy Lab, Department of Communications and Networks Engineering, College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia. He has authored 100 plus scientific articles particular reference to X.Y. converter family, multilevel DC/DC and DC/AC converter, and high-gain converter. He received the Best Paper Research Paper Awards from the IEEE-CENCON'19, IEEE-ICCPCT'14, IET-CEAT'16, and ETAEERE'16 sponsored Lecture note in electrical engineering, (Springer). He is a member of the IEEE Industrial Electronics, Power Electronics, Industrial Application, and Power and Energy, Robotics and Automation, Vehicular Technology Societies, Young Professionals, various IEEE Councils and Technical Communities. He is a Reviewer Member of various international journals and conferences including IEEE and IET. He received the IEEE Access Award Reviewer of Month, in January 2019, for his valuable and thorough feedback on manuscripts, and for his quick turnaround on reviews.

RATHINASAMY SAKTHIVEL received the B.Sc., M.Sc., M.Phil., and Ph.D. degrees in Mathematics from Bharathiar University, Coimbatore, India, in 1992, 1994, 1996, and 1999, respectively. He served as a Lecturer with the Department of Mathematics, Sri Krishna College of Engineering and Technology, Coimbatore, from 2000 to 2001. From 2001 to 2003, he was a Postdoctoral Fellow with the Department of Mathematics, Inha University, Incheon, South Korea. He visited the

Max Planck Institute, Magdeburg, Germany, in September 2002. From 2003 to 2005, he was a Japan Society for the Promotion of Science Fellow with the Department of Systems Innovation and Informatics, Kyushu Institute of Technology, Kitakyushu, Japan. He was a Research Professor with the Department of Mathematics, Yonsei University, Seoul, South Korea, till 2006. He was a Postdoctoral Fellow (Brain Pool Program) with the Department of Mechanical Engineering, Pohang University of Science and Technology, Pohang, South Korea, from 2006 to 2008. He served as an Assistant and Associate Professor with the Department of Mathematics, Sungkyunkwan University, Suwon, South Korea, from 2008 to 2013. From 2013 to 2016, he was a Professor with the Department of Mathematics, Sri Ramakrishna Institute of Technology, India. He is currently a Professor with the Department of Applied Mathematics, Bharathiar University, Coimbatore, India. He has published over 300 research articles in reputed Science Citation Index journals. His current research interests include systems and control theory, optimization techniques, and nonlinear dynamics. He has been on the Editorial Board of international journals, including IEEE Access, Journal of the Franklin Institute, Neurocomputing, Advances in Difference Equations and Journal of Electrical Engineering and Technology.

• • •