#### Cover Page

## Universiteit Leiden

The handle <a href="http://hdl.handle.net/1887/24481">http://hdl.handle.net/1887/24481</a> holds various files of this Leiden University dissertation

Author: Bamakhrama, Mohamed A.

Title: On hard real-time scheduling of cyclo-static dataflow and its application in system-

level design

**Issue Date:** 2014-03-12

# On Hard Real-Time Scheduling of Cyclo-Static Dataflow and its Application in System-Level Design

Mohamed A. Bamakhrama

## On Hard Real-Time Scheduling of Cyclo-Static Dataflow and its Application in System-Level Design

#### **PROEFSCHRIFT**

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus prof.mr. C.J.J.M. Stolker, volgens besluit van het College voor Promoties te verdedigen op woensdag 12 maart 2014 klokke 15:00 uur

door

Mohamed Ahmed Mohamed Bamakhrama geboren te Dubai in 1983

#### **Promotion Committee**

Promotor: Prof. dr. Ed F. Deprettere Universiteit Leiden Co-Promotor: Dr. Todor P. Stefanov Universiteit Leiden Other Members: Prof. dr. Petru Eles Linköpings Universitet

Prof. dr. Rolf Ernst Technische Universität Braunschweig

Prof. dr. Marco Bekooij Universiteit Twente

Prof. dr. Joost Kok Universiteit Leiden

Prof. dr. Farhad Arbab Universiteit Leiden

Prof. dr. Harry Wijshoff Universiteit Leiden

On Hard Real-Time Scheduling of Cyclo-Static Dataflow and its Application in System-Level Design Mohamed A. Bamakhrama. -Dissertation Universiteit Leiden. - With ref. - With summary in Dutch.

Copyright © 2014 by Mohamed A. Bamakhrama. All rights reserved. This dissertation is licensed under the Creative Common Attribution-Share Alike 3.0 license. You can obtain a copy of this license from the following URL: http://creativecommons.org/licenses/by-sa/3.0/

This dissertation was typeset using LATEX and version controlled using Git.

ISBN 978-90-9028032-5 Printed in the Netherlands. My prayer and my sacrifice and my life and my death are all for God, the Lord of the worlds.

Holy Quran 6:162

### **Contents**

| Ta | ble of  | f Conte | nts                                               | vii  |

|----|---------|---------|---------------------------------------------------|------|

| Li | st of I | Figures |                                                   | xi   |

| Li | st of T | Tables  |                                                   | xiii |

| 1  | Intr    | oductio | on                                                | 1    |

|    | 1.1     | Curre   | nt Design Challenges and Trends                   | 3    |

|    |         | 1.1.1   | Design of Concurrent Software                     | 4    |

|    |         | 1.1.2   | Designer Productivity                             | 6    |

|    |         | 1.1.3   | Real-Time Guarantees                              | 8    |

|    | 1.2     | Proble  | em Statement                                      | 10   |

|    | 1.3     | Resear  | rch Contributions                                 | 11   |

|    | 1.4     | Relate  | d Work                                            | 13   |

|    |         | 1.4.1   | Hard Real-Time Scheduling of Streaming Programs   | 14   |

|    |         | 1.4.2   | Design Flows for Hard Real-Time Streaming Systems | 19   |

|    | 1.5     | Organ   | nization of this Dissertation                     | 20   |

| 2  | Bacl    | kgroun  | d                                                 | 23   |

|    | 2.1     | Notati  | ions                                              | 23   |

|    | 2.2     | Paralle | el Execution of Programs                          | 23   |

|    | 2.3     | Cyclo-  | -Static Dataflow (CSDF)                           | 26   |

|    | 2.4     | Real-T  | Time Scheduling                                   | 29   |

|    |         | 2.4.1   | Task Model                                        | 29   |

|    |         | 2.4.2   | Scheduling Concepts                               | 30   |

|    |         | 2.4.3   | Uniprocessor Schedulability Analysis              | 32   |

|    |         | 2.4.4   | Multiprocessor Schedulability Analysis            |      |

viii Contents

| 3  | Auto                 | omated Parallelization and Model Construction                     | 39  |  |  |  |  |  |  |

|----|----------------------|-------------------------------------------------------------------|-----|--|--|--|--|--|--|

|    | 3.1                  | Input Programs                                                    | 39  |  |  |  |  |  |  |

|    |                      | 3.1.1 Top-Level Part                                              | 39  |  |  |  |  |  |  |

|    |                      | 3.1.2 Implementation Part                                         | 40  |  |  |  |  |  |  |

|    | 3.2                  | Automated Parallelization                                         | 41  |  |  |  |  |  |  |

|    | 3.3                  | Model Construction                                                | 42  |  |  |  |  |  |  |

| 4  | Scheduling Framework |                                                                   |     |  |  |  |  |  |  |

|    | 4.1                  | Input Streams                                                     | 48  |  |  |  |  |  |  |

|    | 4.2                  | Basic Definitions                                                 | 50  |  |  |  |  |  |  |

|    | 4.3                  | Deriving Periods                                                  | 52  |  |  |  |  |  |  |

|    | 4.4                  | Deriving Deadlines and Start Times                                | 57  |  |  |  |  |  |  |

|    | 4.5                  | Deriving Buffer Sizes                                             | 61  |  |  |  |  |  |  |

|    | 4.6                  | Throughput Analysis                                               | 65  |  |  |  |  |  |  |

|    | 4.7                  | Latency Analysis                                                  | 67  |  |  |  |  |  |  |

|    | 4.8                  | Deriving Architecture and Mapping Specifications                  | 70  |  |  |  |  |  |  |

| 5  | Syst                 | System-Level Synthesis                                            |     |  |  |  |  |  |  |

|    | 5.1                  | Hardware                                                          | 75  |  |  |  |  |  |  |

|    | 5.2                  | Software                                                          | 77  |  |  |  |  |  |  |

|    |                      | 5.2.1 Scheduling Infrastructure                                   | 78  |  |  |  |  |  |  |

|    |                      | 5.2.2 Communication Infrastructure                                | 83  |  |  |  |  |  |  |

| 6  | Eval                 | uation and Results                                                | 87  |  |  |  |  |  |  |

|    | 6.1                  | Experiment I: Evaluating Automated Parallelization and Model Con- |     |  |  |  |  |  |  |

|    |                      | struction                                                         | 88  |  |  |  |  |  |  |

|    | 6.2                  | Experiment II: Evaluating Performance and Resource Usage Metrics  |     |  |  |  |  |  |  |

|    |                      | under Periodic Scheduling                                         | 88  |  |  |  |  |  |  |

|    |                      | 6.2.1 Benchmarks                                                  | 89  |  |  |  |  |  |  |

|    |                      | 6.2.2 Throughput Evaluation                                       | 89  |  |  |  |  |  |  |

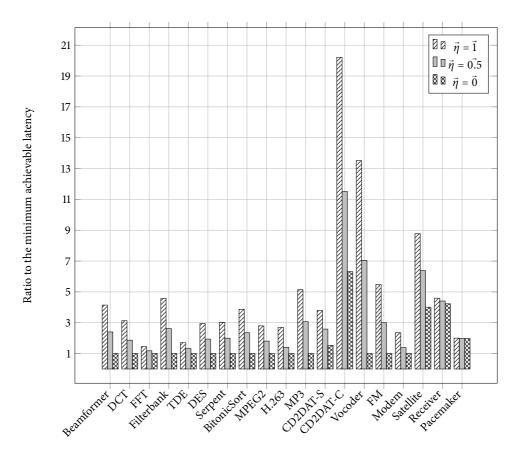

|    |                      | 6.2.3 Latency Evaluation                                          | 90  |  |  |  |  |  |  |

|    |                      | 6.2.4 Processor Requirements Evaluation                           | 91  |  |  |  |  |  |  |

|    |                      | 6.2.5 Memory Requirements Evaluation                              | 93  |  |  |  |  |  |  |

|    |                      | 6.2.6 Summary of Experiment II                                    | 93  |  |  |  |  |  |  |

|    | 6.3                  | Experiment III: Validating Synthesized Systems                    | 95  |  |  |  |  |  |  |

| 7  | Sum                  | nmary and Future Work                                             | 99  |  |  |  |  |  |  |

|    | 7.1                  | Suggestions for Future Work                                       | 101 |  |  |  |  |  |  |

| Bi | bliog                | raphy                                                             | 103 |  |  |  |  |  |  |

| Contents             | ix  |

|----------------------|-----|

| Curriculum Vitae     | 119 |

| List of Publications | 120 |

121

123

Samenvatting

Acknowledgments

## **List of Figures**

| 1.1  | The challenges involved in designing modern hard real-time multipro-              |    |

|------|-----------------------------------------------------------------------------------|----|

|      | cessor streaming systems                                                          | 4  |

| 1.2  | Decidability and expressiveness for popular dataflow MoCs                         | 6  |

| 1.3  | System-level design of modern embedded systems                                    | 7  |

| 1.4  | Popular real-time task models and the complexity of their feasibility tests       | 9  |

| 1.5  | Bridging dataflow MoCs and real-time task models through the pro-                 |    |

|      | posed scheduling framework                                                        | 11 |

| 1.6  | Input and outputs of the proposed scheduling framework                            | 12 |

| 1.7  | Overview of the proposed design flow                                              | 14 |

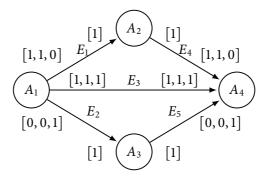

| 2.1  | Example of a CSDF graph that corresponds to the SANLP program in                  |    |

|      | Listing 1                                                                         | 29 |

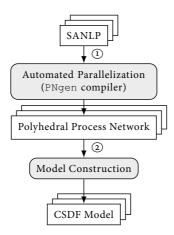

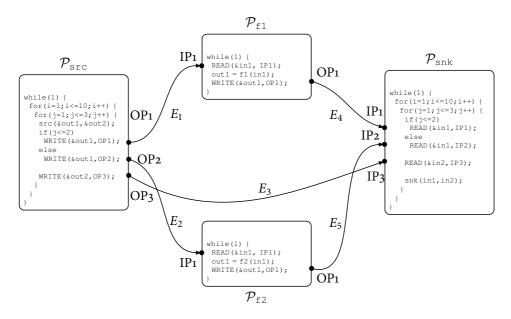

| 3.1  | Automated parallelization and model construction                                  | 40 |

| 3.2  | The parallel program corresponding to the SANLP shown in Listing 1                | 42 |

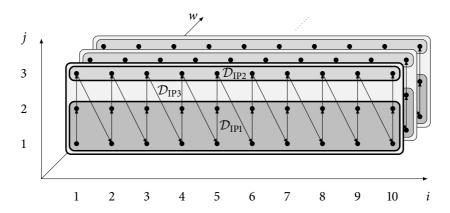

| 3.3  | The port domains of $\mathcal{P}_{\mathtt{snk}}$ shown in Figure 3.2              | 43 |

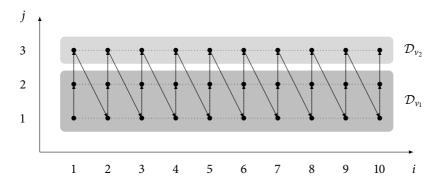

| 3.4  | The domains of $v_1$ and $v_2$                                                    | 44 |

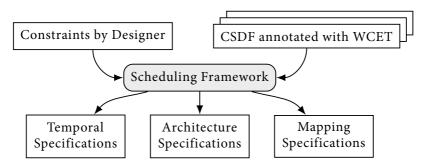

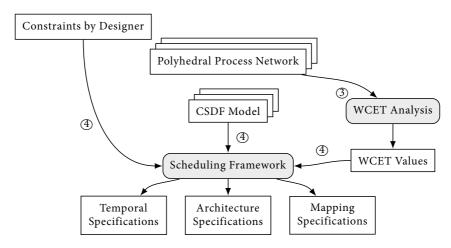

| 4.1  | Scheduling framework                                                              | 48 |

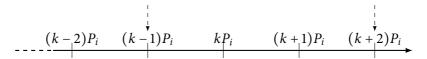

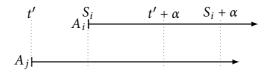

| 4.2  | Occurrence of $t_{MIT}(I_{i,j})$                                                  | 49 |

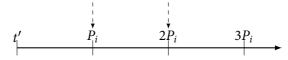

| 4.3  | Computing $t_{\text{buffer}}(I_{i,j})$                                            | 49 |

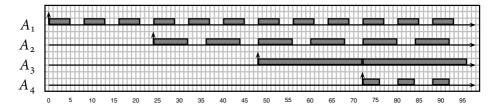

| 4.4  | Schedule $\mathbb{S}_1$                                                           | 55 |

| 4.5  | Schedule $\mathbb{S}_2$                                                           | 55 |

| 4.6  | Schedule $\mathbb{S}_{\mathbb{L}}$                                                | 55 |

| 4.7  | Schedule $\mathbb{S}_{\infty}$                                                    | 56 |

| 4.8  | The periodic schedule for the CSDF graph shown in Figure 2.1 con-                 |    |

|      | structed using Theorem 4.3.1                                                      | 57 |

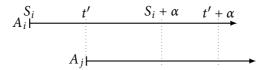

| 4.9  | Timeline of $A_i$ and $A_j$ when $t' \geq S_i \ldots \ldots \ldots \ldots \ldots$ | 60 |

| 4.10 | Timeline of $A_i$ and $A_j$ when $t' < S_i \ldots \ldots \ldots \ldots$           | 60 |

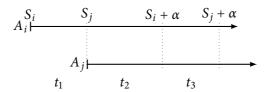

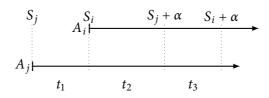

| 4.11 | Execution time-lines of $A_i$ and $A_j$ when $S_i \leq S_i \dots \dots \dots$     | 63 |

xii List of Figures

| 4.12 | Execution time-lines of $A_i$ and $A_j$ when $S_i > S_j$             | 63 |

|------|----------------------------------------------------------------------|----|

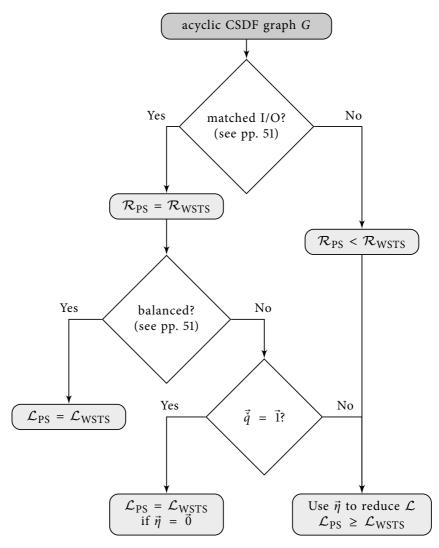

| 4.13 | Decision tree for scheduling CSDF actors as real-time periodic tasks | 71 |

| 4.14 | The CSDF graph corresponding to the SANLP program shown in           |    |

|      | Listing 2                                                            | 72 |

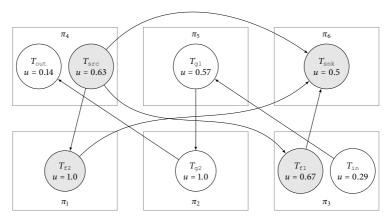

| 4.15 | Mapping of $G_1$ and $G_2$ onto 6 processors assuming EDF and FFD    | 73 |

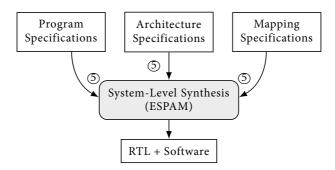

| 5.1  | Electronic System-Level Synthesis                                    | 76 |

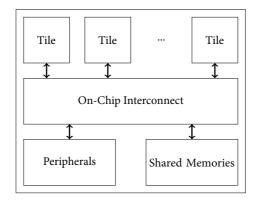

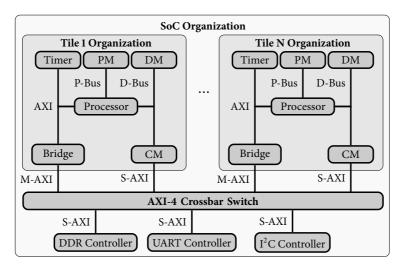

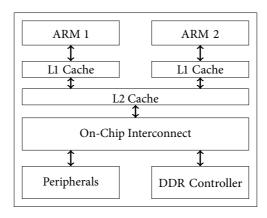

| 5.2  | Top-level block diagram of the hardware platform considered in this  |    |

|      | dissertation                                                         | 76 |

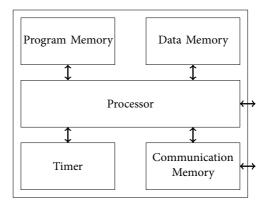

| 5.3  | Tile organization                                                    | 77 |

| 5.4  | Complete MPSoC architecture                                          | 78 |

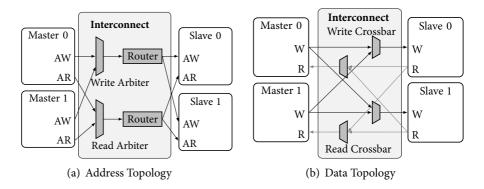

| 5.5  | Crossbar Topology                                                    | 79 |

| 5.6  | Detailed description of function vTaskDelayUntil                     | 81 |

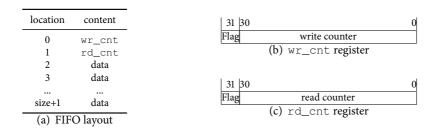

| 5.7  | FIFO layout in memory and the read/write registers                   | 83 |

| 6.1  | Results of the latency evaluation                                    | 92 |

| 6.2  | Minimum number of processors required by optimal and partitioned     |    |

|      | schedulers                                                           | 94 |

| 6.3  | Zynq-7000 SoC architecture                                           | 97 |

## **List of Tables**

| 2.1 | Summary of mathematical notations                                                                                                            | 24 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Approximation rations for known bin packing heuristics                                                                                       | 37 |

| 3.1 | Deriving production/consumption rates sequences from the shortest repetitive pattern                                                         | 45 |

| 4.1 | Computing $\vec{D}$ and $\vec{S}$ for the CSDF graph shown in Figure 2.1 on page 29 under different values of $\vec{\eta}$                   | 61 |

| 4.2 | Computing the buffer sizes for the CSDF graph shown in Figure 2.1 on page 29 under different values of $\vec{\eta}$                          | 64 |

| 4.3 | Values of $K_i^u$ and $K_j^u$ defined in (4.49) and (4.50) for the CSDF graph shown in Figure 2.1                                            | 68 |

| 4.4 | The output paths latencies and graph maximum latency of the CSDF graph shown in Figure 2.1 on page 29 under different values of $\vec{\eta}$ | 68 |

| 4.5 | The taskset parameters for $G_1$ and $G_2$ assuming $\mu_G = 1$ and $\vec{\eta} = \vec{1}$ for both graphs                                   | 72 |

| 6.1 | Specifications of the machine on which the experiments were performed                                                                        | 87 |

| 6.2 | Time needed to parallelize and derive the CSDF model for the benchmark programs                                                              | 88 |

| 6.3 | Benchmarks used for evaluating the periodic scheduling framework                                                                             | 00 |

|     | proposed in Chapter 4                                                                                                                        | 90 |

| 6.4 | Results of Throughput Comparison                                                                                                             | 91 |

| 6.5 | The total amount of memory needed to realize the buffers in the com-                                                                         |    |

|     | munication channels under periodic and self-timed schedules                                                                                  | 95 |

| 6.6 | Programs used in Experiment III                                                                                                              | 96 |

| 6.7 | Hardware platforms used in Experiment III                                                                                                    | 97 |

| 6.8 | The set of synthesized systems                                                                                                               | 98 |

### **Chapter 1**

### Introduction

The computer was born to solve problems that did not exist before.

Bill Gates

THE current period of human history is known as the **information** age. This name stems from the fact that humanity is shifting from the traditional industry-based society that characterized the industrial revolution period between 1700-1900 CE, into a *knowledge-based* society. The knowledge which used to be concentrated only in libraries and accessible only to a small fraction of the society has now become available (mostly for free) to anyone with a computer and Internet access. This dissemination of knowledge has been mainly enabled by the advent of **electronic computers** and all the advances that they enabled and brought such as the Internet. Electronics in general, and computers in particular, have changed many aspects in our behavior and way of thinking. Today, computers resemble the "backbone" of a modern society. They are everywhere starting from mobile phones and MP3 players and all the way to satellites, airplanes, and nuclear reactors. They process daily vast amounts of data to ensure that our societies continue to function properly. Computer systems can be classified based on *their functionality* into two categories:

- 1. **General-purpose** systems such as Personal Computers (PC). Such systems are flexible and can be controlled directly by the user to perform a variety of tasks such as web browsing, word processing, gaming, etc.

- 2. **Embedded** systems such as the ones that you can find inside digital TVs, cars, trains, etc. Such systems have specific functionality and they are mostly invisible to the user. Such computer systems are said to be *embedded* within larger systems.

Most of people are familiar with the first category since they use them in their daily

life. However, almost 90% of all computer systems shipped worldwide in 2010 were actually embedded systems [MRP+11]. Embedded systems have become pervasive in our life. They are everywhere, and even though that we mostly do not see them, we still feel their presence through their actions. A very important property of embedded systems is that their correct functionality does not depend only on producing the correct result but also on producing the correct result at the right time. Such systems, where time is critical to the correct functionality, are called **real-time systems**. Real-time systems can be either **hard** or **soft**. A hard real-time system is one where the failure to meet the timing requirements leads to a system *failure*. In contrast, a soft real-time system is one where the failure to meet the timing requirements does not lead to a failure but to *degraded* system performance that can be tolerated. Deciding whether a system is hard or soft depends usually on the overall system requirements and the environment where the system is deployed.

Real-time systems can be further classified, based on the *type of programs* they run, into:

- Control programs that wait for external events from the physical world, and then react to these events. Examples include factory automation programs running on Programmable Logic Controllers (PLC) and railway switching systems.

- 2. Streaming programs that are characterized by processing continuous *streams* of data which arrive to the system. Usually, such programs process large amounts of data within short periods of time. Examples of such programs include those used in video and audio processing, digital signal processing, and network protocol processing.

In many cases, a single embedded system can contain both control and streaming programs.

A hard real-time streaming system is a hard real-time system that runs a set of streaming programs. This implies that all the streaming programs running on the system have hard timing requirements (i.e., timing requirements that must be always met). Examples of such systems include: (1) collision avoidance and path planning sub-systems in Unmanned Aerial Vehicles (UAV) and self-driving cars, and (2) Software-Defined Radio (SDR) used in wireless communication. For instance, a typical value of required reaction time to new sensor data in self-driving cars is around 300 ms [Thr10]. At the same time, some self-driving cars, such as Google's self-driving car, have been reported to gather around 750 MB of data per second [Woo]. Such tremendous amount of gathered data implies the need for parallel processing in order to meet the required reaction times. In this dissertation, we tackle the problem of designing such streaming systems in an automated and systematic way such that all the programs "provably" meet their timing requirements. In the next section, we explain the current challenges in

designing such systems and their implications.

#### 1.1 Current Design Challenges and Trends

As general-purpose computers have moved from single core processors to multicore processors [HNO97], the same has happened in the embedded systems domain. Today, embedded systems designers integrate multiple processors, hardware peripherals and memories into a single chip. Such chips are referred to as Multiprocessor Systemon-Chip (MPSoC) [JTW05]. MPSoCs represent a good candidate for running many computationally-intensive streaming programs in hard real-time systems. For example, Thrun reported in [Thr10] that Stanford's Stanley self-driving car, which was used in DARPA 2005 challenge, employed two Intel quad-core processors in order to run the autonomous driving software, including path planning and collision avoidance algorithms. Such algorithms are also highly parallelizable [KKLR13], which means that they benefit from execution on multiprocessor systems. However, such algorithms are specified, most of the time, as sequential programs. This means that such programs must be parallelized in order to meet their timing constraints and utilize the underlying processors. Another challenge is that designing MPSoCs is becoming increasingly complex as the number of processors integrated onto a single chip keeps increasing. According to the International Technology Roadmap for Semiconductors (ITRS) report for 2011 [Int11]:

"In the near term, the grand challenges for design technology remain (1) power management, and (2) design productivity and design for manufacturability. In the long term, the grand challenges for design technology have been updated as (1) design of concurrent software, and (2) design for reliability and resilience."

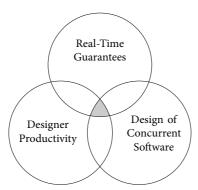

Therefore, we can represent the problem of designing hard real-time multiprocessor systems that run multiple streaming programs as an intersection of three different problems as shown in Figure 1.1. The gray area represents the area to which the aforementioned design problem belongs. In this gray area, the designer must produce a hard real-time multiprocessor system that runs several streaming programs in parallel with the ability to provide **temporal isolation** between the programs. Temporal isolation is the ability to start/stop programs, at run-time, without violating the timing requirements of other already running programs. In the following three sections, we describe each of the three challenges shown in Figure 1.1 in detail and the current approaches in addressing these challenges.

**Figure 1.1:** The challenges involved in designing modern hard real-time multiprocessor streaming systems.

#### 1.1.1 Design of Concurrent Software

Software became a very important component in modern embedded systems. The amount and complexity of software that is running on such systems has increased dramatically over the last decades. For example, the size of embedded software in automotive systems has increased by two orders of magnitude between 1990 and 2010 [EJ09]. According to [EJ09], software is becoming a key differentiator in many domains such as automotive. A complicating factor in designing modern embedded systems is that embedded software must be written as *parallel* software in order to utilize the underlying processors in an MPSoC. Given a sequential program, researchers have identified three possible types of parallelism:

- 1. **Instruction-Level** Parallelism (ILP): this represents the lowest level of parallelism that is visible to the programmer. Under ILP, multiple instructions within the program may be executed in parallel.

- 2. **Data-Level** Parallelism (DLP): under DLP, a function (or block) within the program is executed simultaneously on several processors and each copy of the function processes its own stream of data.

- 3. **Task-Level** Parallelism (TLP): under TLP, the program is split into a set of functions (or *tasks*) and these functions execute in parallel.

It is important to note that a program might contain more than one type of parallelism. For example, a program might exhibit task-level parallelism and data-level parallelism. In this case, the program is split into multiple tasks that execute in parallel and a certain task has several concurrently executing replicas with each replica processing a separate stream of data. In general, identifying parallelism in a sequential program is a tedious task. This tedious task is exacerbated further by the fact that designers need to provide timing guarantees for programs running on hard real-time

multiprocessor systems. Traditionally, embedded software has been designed at the level of Board Support Package (BSP) and high-level Application Programming Interface (API) [HHBT09]. An example of a popular API for designing concurrent software is the POSIX threads (Pthreads) standard [SG13]. However, designing concurrent software at this level is known to be a cumbersome and error-prone task and it is not easy to provide timing guarantees [Lee06]. Therefore, it has been recognized that the designers need to abstract from the actual programs by building *high-level models* of them [EJ09, Tei12]. Then, these models are used to analyze the program performance under different scheduling and mapping decisions. Such design approach is often called **Model-Based Design (MBD)** or **Model-Driven Design (MDD)** and the models used in such approaches are called **Models of Computation (MoC)** [HHBT09].

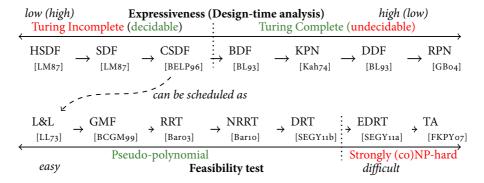

In the broadest sense, a MoC defines the set of permitted operations used in computation. MoCs can be classified as either sequential or parallel. In this dissertation, we are interested in parallel MoCs as they are suitable for expressing programs that are mapped onto MPSoCs. In particular, dataflow MoCs have been identified as suitable parallel MoCs for expressing streaming programs [TA10]. In general, dataflow MoCs abstract the program in the form of a directed graph, where graph nodes represent the tasks of the program and graph edges represent the data dependencies among the tasks. Thus, parallelism is explicitly specified in the model. According to [TA10], almost all streaming programs can be modeled as Synchronous Dataflow (SDF, [LM87]) graphs. Several parallel dataflow MoCs have been proposed in the literature that vary in their expressiveness and decidability [LN05, JS05]. The expressiveness of a MoC is usually measured by its Turing completeness. On the other hand, decidability refers to the ability to perform scheduling decisions at compile-time [HO10]. If the execution order of tasks can be determined at compile-time, then the designer can decide before running the program if the program has the possibility of buffer overflow or deadlock. Decidable dataflow MoCs achieve their decidability by placing restrictions on the semantics of the MoC [HO10]. Generally speaking, expressiveness and decidability are inversely related as shown in Figure 1.2, which shows the expressiveness and decidability for popular dataflow MoCs.

Another development in designing parallel software is the advent of **automated parallelization** tools. Streaming programs, in general, are designed at an algorithmic level using a high-level sequential language such as C or MATLAB. Once the correctness of these sequential specifications is verified, they are passed to subsequent design stages. It has been noted that most of the execution of these sequential specifications is spent in nested loops [Fra10]. Thus, researchers have investigated several techniques for parallelizing such programs. One particular class of nested loop programs that received a lot of attention is *static control and affine indices* programs—also called *Static Affine Nested Loop Programs* (SANLP) [Fea91]. This class has been shown to embody a large

**Figure 1.2:** Decidability and expressiveness for popular dataflow MoCs. The arrows between the MoCs indicate that the MoC on the left-side is a subset of the one on the right-side. For example, SDF is a subset of CSDF. The dotted vertical line represents the borderline between decidable and undecidable models.

#### **Listing 1** Example of a SANLP in C

portion of streaming programs [Bas04]. An example of a valid SANLP is shown in Listing 1. It has been shown in [Fea91] that a SANLP can be automatically analyzed to construct a parallel version of it. Hence, it is important to utilize this property to relieve the designer from the burden of parallelizing such programs manually. Given a sequential program, automated parallelization tools analyze the program and construct a parallel version of it. This parallel version of the program exposes the parallelism present in the original sequential program. Several parallelizing compilers have been proposed for SANLPs, such as the PNgen compiler [VNS07].

#### 1.1.2 Designer Productivity

Improving designer productivity has been an active area of research since the advent of electronic systems. This area of research is called **Electronic Design Automation**

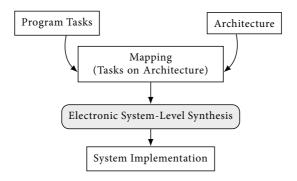

**Figure 1.3:** *System-level design of modern embedded systems*

(EDA). A common thing among all electronic systems is that they are made of transistors. Modern electronics are developed by putting an enormous number of transistors into an Integrated Circuit (IC) (commonly known as chip) that is manufactured on a single plane of silicon. Gordon Moore has predicted in 1965 [Moo65] that the number of transistors that can be put into an IC doubles approximately every 18 months. The 18 months period has been revised later to 24 months. The rationale behind this prediction is that the physical processes used to manufacture ICs keep improving. This in turn will lead to the ability to shrink the transistors, and hence, put more transistors into the same area. Moore's prediction has survived, till now, the test of time and turned into one of the most important rules of semiconductor industry, known as Moore's law. Therefore, as the number of transistors in a chip keeps increasing, it is necessary to design the chip at the right level of abstraction. In the 1960s and 1970s, electronic systems were designed at the gate level; designers represented their system as a set of Boolean equations and then they translated these equations into circuits composed of gates. With the number of transistors doubling every 24 months, the designers eventually had to deal with a very large number of gates. This forced the shift from gate-level design to Register-Transfer Level (RTL) in 1980s. At RTL, the designer deals no more with gates, but rather with components such as registers, adders, multipliers, etc. Again, as the number of transistors kept increasing, the designers eventually had to deal with a very large number of such components. Therefore, it became necessary to raise the level of abstraction again from RTL to system-level [KM+00]. At system-level, the designer deals with processors, memories, interconnects, and peripherals as the primitive blocks that form the system. System-level design has been identified as a promising design approach for MPSoCs [Hen03]. System-level design abstracts the SoC design by considering it as a process of mapping a set of tasks onto a set of processing elements as shown in Figure 1.3. Once such a mapping is determined, for example using design space exploration, **Electronic System-Level (ESL) synthesis** [GHP<sup>+</sup>09]

tools provide (mostly) automated procedures to generate the hardware descriptions (i.e., RTL) and the parallel software running on the processors. In addition, **Platform-Based Design (PBD)** has emerged as a de facto solution to address the design re-use problem [KM<sup>+</sup>00]. System-level design and platform-based design are closely related. Under PBD, a system is divided into *three* layers:

- 1. *Hardware platform*: consists of a set of processors, Input/Output (I/O) peripherals, and accelerators. The hardware components have a largely *fixed* functionality, with some degree of parameterization.

- 2. *Software platform*: consists of the RTOS, device drivers, and Basic I/O System (BIOS) routines. The software platform offers a set of APIs to the user programs running on the system. The software platform is sometimes called *Hardware-dependent Software (HdS)*.

- 3. *Programs software*: consists of the users' programs running on the system. These programs communicate with the underlying software platform through the API, which abstracts the underlying hardware platform.

#### 1.1.3 Real-Time Guarantees

As mentioned earlier, several modern streaming programs have very high computational demands together with hard timing requirements. Such programs have two primary performance metrics which are throughput and latency. Throughput measures how many samples (or data-units) a program can produce during a given time interval. Latency measures the time elapsed between receiving a certain input sample and producing the processed sample by the program. Therefore, it is important to provide guaranteed throughput and latency for each program running on the designed system. Providing such guarantees depends on the system hardware and software. The hardware must be **predictable** which means that any hardware operation must have a bounded worst-case duration. The same applies to system software such as operating system and device drivers. In addition, the operating system scheduler must be capable of enforcing temporal isolation among the running programs on the system. Temporal isolation, as mentioned earlier, is the ability to start/stop programs, at run-time, without violating the timing requirements of other already running programs. Commercial Off-The-Shelf (COTS) multicore hardware systems have been identified as inadequate for hard real-time embedded systems [WGR<sup>+</sup>09]. Recently, several attempts have been made to propose predictable multicore hardware architectures that can be used in hard real-time embedded systems (e.g., [HGBH09, Sch09, UCS+10, Liu12]).

On the software side, several scheduling policies have been proposed for scheduling streaming programs on MPSoCs [NVC10]. For a long time, self-timed scheduling was considered the most appropriate policy for streaming programs modeled as dataflow graphs [LH89,SB09]. Under self-timed scheduling, a task is executed *as soon as possible*

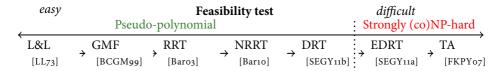

**Figure 1.4:** Popular real-time task models and the complexity of their feasibility tests. The arrows between the models indicate that the model on the left-side is a subset of the one on the right-side. For example, L&L is a subset of GMF.

(i.e., when its input data is available). However, the need to support multiple programs running on a single system without prior knowledge of the properties of the programs (e.g., required throughput, number of tasks, etc.) at system design-time is forcing a shift towards run-time scheduling approaches. Most of the existing run-time scheduling solutions assume programs modeled as task graphs and provide best-effort or soft real-time guarantees [NVC10]. Few run-time scheduling solutions exist which support programs modeled using a MoC and provide hard real-time guarantees [God98,BHM+05,Mor12]. However, these solutions use either simple MoCs such as SDF graphs or Time Division Multiplexing (TDM) scheduling.

Several algorithms from the classical hard real-time multiprocessor scheduling theory [DB11] can perform *fast* admission and scheduling decisions for incoming programs while providing hard real-time guarantees. Moreover, these algorithms enforce temporal isolation between running programs. Another key advantage of using classical hard real-time scheduling algorithms is the ability to derive in an analytical and fast way the minimum number of processors needed to schedule a set of tasks and the mapping of tasks to processors. Hard real-time scheduling theory and algorithms work in a similar way to model-based design; they abstract the programs in the form of a *real-time task model*. Such task models impose restrictions on the timing of the program tasks. As a result, it becomes easier to perform timing analysis of the program and reason about its behavior during the design phase. Several real-time task models have been proposed in the literature which differ in the complexity of their *feasibility tests* as shown in Figure 1.4. A feasibility test deals with the problem of deciding whether a given set of tasks can be scheduled to meet all their deadlines.

The most famous model is the *real-time periodic* task model proposed by Liu and Layland in 1973 [LL73]—often called Liu and Layland (L&L) model. This model has simple feasibility analysis which led to its wide adoption. However, this model places several restrictions on the tasks such as:

- The releases (i.e., invocations) of all tasks are periodic, with constant interval between releases.

- All tasks are independent in that releases of a certain task do not depend on the

initiation or completion of releases of other tasks.

• Execution time of each task is constant.

Several models were proposed to extend Liu and Layland model as shown in Figure 1.4. However, these extended models have more sophisticated feasibility analysis.

#### 1.2 Problem Statement

We can summarize the discussion in Section 1.1 as follows. Model-based design and electronic system-level synthesis have emerged as de facto solutions to the problems of designing parallel software for MPSoCs and generating the complete MPSoC, respectively. However, no such de facto solution exists yet for the problem of scheduling parallel streaming programs on MPSoCs used in hard real-time systems. Scheduling has a direct influence on the architecture and mapping specifications needed to perform electronic system-level synthesis as shown in Figure 1.3. One possible and attractive solution is to use classical hard real-time scheduling algorithms due to their benefits mentioned in Section 1.1.3. However, most hard real-time scheduling algorithms assume independent periodic or sporadic tasks [DB11]. Such a simple task model is not directly applicable to modern streaming programs which, as mentioned in Section 1.1.1, are typically modeled as directed graphs, where graph nodes represent actors (i.e., tasks) and graph edges represent data-dependencies. The actors in such graphs have data-dependency constraints and do not necessarily conform to the periodic or sporadic task models. Therefore, the core problem addressed by this dissertation is to investigate the applicability of hard real-time scheduling theory for real-time periodic tasks to streaming programs modeled as acyclic Cyclo-Static Dataflow (CSDF, [BELP96]) graphs.

We argue that in a hard real-time system, one would like to choose, as much as possible, a decidable MoC in order to verify the timing behavior at system design time. At the same time, one would like to use the least complex (in terms of feasibility) real-time task model that is permissive enough in its semantics to model the underlying program. Therefore, in this dissertation, we consider Cyclo-Static Dataflow (CSDF) as the model of computation and the real-time periodic (i.e., L&L [LL73]) model as the real-time task model. The choice of CSDF is motivated by the fact that it is expressive enough to model most streaming programs as demonstrated in [TA10], while the choice of the real-time periodic model is motivated by the fact that it has a simple feasibility test and is widely adopted by existing real-time operating systems. By considering acyclic CSDF graphs, our findings and results are applicable to most streaming programs since it has been shown recently that around 90% of streaming programs can be modeled as acyclic SDF graphs [TA10]. Note that SDF graphs are a subset of the CSDF graphs considered in this dissertation.

**Figure 1.5:** Bridging dataflow MoCs and real-time task models through the proposed scheduling framework. The link indicates that any acyclic CSDF can be scheduled as a set of L&L tasks.

#### 1.3 Research Contributions

The research contributions of this dissertation can be summarized as follows.

#### Contribution 1: Proposing a Scheduling Framework that Bridges Dataflow MoCs and Real-Time Task Models

We propose an analytical scheduling framework (see [BS11, BS12]) that bridges classical dataflow models and classical real-time task models as shown in Figure 1.5. We prove analytically using this framework that any streaming program, modeled as an acyclic CSDF graph, can be executed as a set of real-time periodic tasks. The proposed framework computes the parameters (i.e., periods, start times, and deadlines) of the periodic tasks corresponding to the graph actors and the minimum buffer sizes of the communication channels such that a valid periodic schedule is guaranteed to exist. This framework shows that the use of both models is possible and that they complement each other; CSDF captures the functional aspects of the program, while the real-time periodic task model captures the timing aspects. Using both models, as demonstrated by our proposed framework, enables the designer to: (1) schedule the tasks to meet certain performance metrics (i.e., throughput and latency), (2) derive analytically the scheduling parameters that guarantee the required performance, and (3) compute analytically the minimum number of processors that guarantee the required performance together with the mapping of tasks to processors. An overview of the inputs and outputs of the proposed scheduling framework is shown in Figure 1.6. Each CSDF is annotated with the Worst-Case Execution Time (WCET) of its actors. The WCET values are obtained from the program through either static analysis tools or profiling the program on the target MPSoC platform [WEE+08]. The user input constraints include:

Figure 1.6: Input and outputs of the proposed scheduling framework

(i) type of scheduling algorithm, (ii) type of allocation algorithm, and (iii) values of parameters used to control the derivation of periods and deadlines as explained later in Chapter 4. The outputs of the framework are: (i) architecture specifications which describe how many processors are needed to schedule the programs, (ii) mapping specifications which associate each task with the processor on which it runs, and (iii) temporal specifications which consist of the parameters (i.e., periods, start times, and deadlines) of the periodic tasks corresponding to the CSDF actors together with the buffer sizes of the CSDF communication channels.

Additionally, the proposed scheduling framework establishes the following results:

- Matched I/O rates graphs (which correspond to roughly 90% of streaming programs) have a throughput under periodic schedules that is equal to their throughput under worst-case self-timed schedules. Periodic schedules here refers to scheduling the graph actors as real-time periodic tasks. This result opens the door for applying periodic scheduling to streaming programs.

- For certain classes of CSDF graphs, it is possible to achieve throughput and latency, under periodic schedules, that are equal to the throughput and latency under worst-case self-timed schedules. It is also shown that, for CSDF graphs in general, the latency can be reduced via reducing the deadlines of the actors along the critical paths.

## Contribution 2: Proposing and Realizing a System-Level Design Flow that Incorporates the Proposed Scheduling Framework

In order to demonstrate the applicability of the proposed scheduling framework, we propose a system-level design flow that incorporates the proposed scheduling framework (see [BZNS12]). This design flow represents a contribution because most of the existing scheduling frameworks for streaming programs represent theoretical frameworks that have limited or no applicability in real design flows. The proposed design flow is

1.4. Related Work

based on an existing state-of-the-art system-level design flow for streaming programs called Daedalus [TNS+07, NTS+08]. Similar to Daedalus, the proposed design flow starts from the sequential specifications of the programs, and then, generates in a fully automated manner the final system implementation, which provably meets the timing requirements of the programs. A complete implementation of the proposed design flow is available for download as an open source framework from http://daedalus.liacs.nl/. This implementation of the proposed design flow is called the Daedalus<sup>RT</sup> design flow.

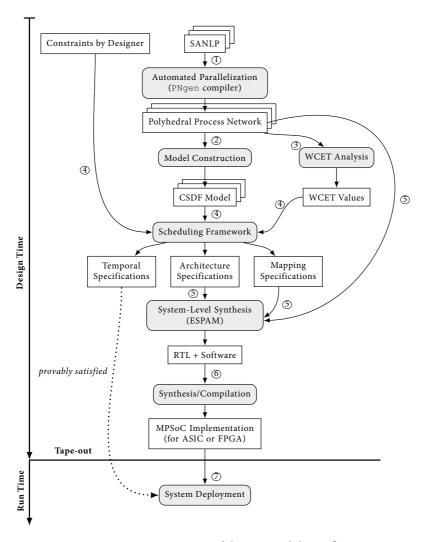

The proposed design flow is illustrated in Figure 1.7. It consists, in total, of six steps that are marked inside circles in Figure 1.7. Step 1 accepts, as input, a set of SANLPs and then uses the PNgen compiler to parallelize them and generate the parallel specification of these input programs. The parallel specification consists of the Polyhedral Process Network (PPN, [VNS07]) representation of the program. PPN is a parallel MoC that is useful for code generation and optimizations. However, it is not suitable for analytical performance analysis. This leads us to the next step.

In *Step 2*, the generated PPNs in step 1 are used to construct the performance analysis model, i.e., CSDF model. Given a PPN, we use the algorithm proposed in [BZNS12] to derive a CSDF graph that is equivalent to the given PPN.

In *Step 3*, we perform WCET analysis on the parallel specification of the program. WCET analysis, as mentioned earlier, can be performed through either static analysis tools or profiling the code on the target MPSoC platform.

In *Step 4*, the CSDF models generated in step 2, the WCET values generated in step 3, and the user constraints, which include for example the type of scheduler and other parameters as explained earlier, are fed to the proposed scheduling framework explained in Contribution 1. This results in: (i) the architecture specification, which describes how many processors are needed to schedule the programs, and (ii) the mapping specification, which describes the allocation of tasks to processors.

In *Step 5*, the PPNs together with architecture and mapping specifications are processed by ESPAM [NSD08]. ESPAM is an ESL synthesis tool that supports MPSoC synthesis from PPNs. We have extended ESPAM to support synthesizing the target MPSoC hardware and software. The output from this step is a full MPSoC implementation consisting of the RTL needed to perform low-level synthesis for FPGA or ASIC together with the software running on each processor in the MPSoC.

Step 6 is the last step in the design flow and consists of performing low-level synthesis for FPGA or ASIC together with compiling the code for each processor.

#### 1.4 Related Work

Design of hard real-time streaming systems has been an active research area for a long time. We give in this section a survey of the existing work and how it relates to

**Figure 1.7:** Overview of the proposed design flow

this dissertation. The related work is organized into two categories: hard real-time scheduling of streaming programs, and design flows for hard real-time streaming systems.

#### 1.4.1 Hard Real-Time Scheduling of Streaming Programs

It is shown in [LM87, BELP96] that any SDF/CSDF graph can be converted into a functionally equivalent Homogenous SDF (HSDF, [LM87]) graph, where HSDF is equivalent to Computation Graphs introduced by Karp and Miller in 1966 [KM66].

1.4. Related Work

Several scheduling techniques (e.g., [Mor12]) utilize this property by converting a given SDF/CSDF into an HSDF graph and then performing the scheduling analysis on the HSDF. However, the resulting HSDF graph has a size that grows exponentially with the size of the input SDF/CSDF. Therefore, such scheduling techniques have two disadvantages. First, the resulting HSDF might be huge which introduces large overhead when the actual HSDF is scheduled on the system. Second, in a periodic schedule of CSDF, each actor must have a start time and a period and each channel must have a buffer size. By deriving the schedule for the HSDF graph, it is possible to derive a start time and a period for each CSDF actor. However, it is not clear how to derive a buffer size for each CSDF channel from the buffer sizes of the HSDF.

Parks and Lee [PL95] studied the applicability of non-preemptive fixed task priority scheduling with rate monotonic priority assignment to streaming programs modeled as SDF graphs. Our work differs in the following aspects. First, they considered non-preemptive scheduling, while we consider only preemptive scheduling. Non-preemptive scheduling is known to be NP-hard in the strong sense even for the uniprocessor case [JSM91]. Second, they considered SDF graphs which are a subset of the more general CSDF graphs.

Verhaegh et al. [VLA+96] proposed Multidimensional Periodic Scheduling (MPS) to schedule digital signal processing programs written as a set of nested loops and modeled using Signal Flow Graphs (SFG). The inputs to MPS are the SFG and a set of explicit timing constraints. Given an SFG, MPS derives a schedule for each operation, where this schedule is described by multiple periods and offsets, and a buffer size for each channel such that the precedence and timing constraints are met. The scheduled operations execute in a strictly periodic manner (similar to the real-time periodic model). Verhaegh et al. showed that MPS is NP-hard and they proposed a two-stage solution approach in [VAvGL01]. The MPS framework is very similar to the framework proposed in Chapter 4 in that both frameworks derive the periods and start times of the tasks and the buffer sizes of the channels. However, the frameworks differ in the considered MoC. MPS considers SFG, while the framework in Chapter 4 considers CSDF which is more general than SFG [PC13]. Another difference is that the framework in Chapter 4 can derive a deadline for each task to reduce the graph latency.

Goddard [God98] studied applying real-time scheduling to streaming programs modeled using the Processing Graphs Method (PGM). He used a task model called *Rate-Based Execution (RBE)* which is a generalization of the real-time periodic task model. For a given PGM, he developed an analysis technique to find the RBE task parameters of each actor and buffer size of each channel. Each channel in PGM is associated with a production/consumption rate (as in SDF) and a consumption threshold. The interpretation is that the consumer consumes a number of tokens equal to the consumption rate only if the channel contains a number of tokens that is greater than

or equal to the consumption threshold. In contrast, CSDF supports a sequence of predefined production/consumption rates. As a result, the analysis technique in [God98] is not applicable to CSDF graphs.

Ziegenbein et al. [ZUE00] proposed a technique to optimize the response time of SDF graphs under Earliest Deadline First (EDF) scheduling assuming jittery input streams. Their technique accepts, as input, the SDF graphs, the average period of each actor, and the jitter bounds of the input streams. Then, they revise the deadline of each actor in such a way that the data dependencies are respected and the total response time is minimized. Our approach differs from [ZUE00] in the following aspects. First, we compute all the scheduling parameters of the tasks including the deadline, while in [ZUE00] the authors assume that the periods are given. Thus, our approach gives the designer greater flexibility in controlling the timing behavior of the tasks. Second, we consider CSDF graphs which extend the SDF model considered in [ZUE00].

Bekooij et al. [BHM<sup>+</sup>05] analyzed the impact of TDM scheduling on programs modeled as SDF graphs running on embedded real-time multiprocessor systems. Wiggers et al. [WBS09] proposed a classification scheme for run-time scheduling algorithms based on the causes of interference among programs. They identified two causes of interference which are (i) how often other tasks are executed and (ii) what execution time is associated with these executions. According to Wiggers taxonomy [WBS09], run-time scheduling algorithms are classified into:

- 1. *Non-starvation-free* algorithms: under such algorithms, interference depends on (i) and (ii). Examples include fixed-task priority scheduling.

- 2. *Starvation-free* algorithms: interference is independent of (i) but depends on (ii). Examples include round-robin scheduling.

- 3. *Budget-schedulers*: interference is independent of (i) and (ii). Thus, a budget scheduler guarantees every task a minimum amount of time *x* in every time interval of length *y*. Examples of budget schedulers include TDM and Constant Bandwidth Server (CBS, [AB98]).

Wiggers et al. defined a subset of dataflow graphs called *functionally deterministic dataflow graphs* and showed that such graphs have time deterministic behavior under budget schedulers. CSDF is an example of a functionally deterministic dataflow graph. In [SBW09], Steine et al. proposed a priority-based budget scheduling algorithm that overcomes some of the limitations of TDM. Recently, Hausmans et al. [HWGB13] extended the analysis in [BHM $^+$ 05, WBS09] to programs modeled as arbitrary HSDF graphs when they are scheduled using algorithms of the first class according to Wiggers taxonomy. In another work, Hausmans et al. [HGWB13] proposed a two parameter  $(\sigma, \rho)$  workload characterization to reduce the gap between the worst-case throughput determined by the analysis and the actual throughput of the program. The  $(\sigma, \rho)$  workload characterization uses the average execution time of consecutive executions of a

1.4. Related Work

task to provide throughput and latency guarantees. Compared to [BHM $^+$ 05, HWGB13], the framework in Chapter 4 applies the analysis directly to a more expressive MoC (namely CSDF) and avoids the conversion to a larger HSDF. Compared to [WBS09, SBW09], we use the real-time periodic model which does not restrict the designer to a certain class of algorithms as defined by Wiggers taxonomy. The designer can use any algorithm that supports the underlying task model. Compared to [HGWB13], we consider "classical" hard real-time tasks, where each execution of a task must meet its deadline. In contrast, under the  $(\sigma, \rho)$  workload characterization, the average WCET is used to improve the minimum guaranteed throughput/latency. Thus, an internal task in the dataflow graph may miss its deadline without causing the program to violate its guaranteed throughput/latency.

Thiele and Stoimenov [TS09] proposed an analysis framework for HSDF graphs based on Real-Time Calculus (RTC, [CKT03]). Their analysis framework provides upper and lower bounds on the performance metrics under different scheduling policies (e.g., TDM and fixed task priority scheduling). An advantage of their framework is its ability to handle cyclic graphs. However, their framework acts as a general performance analysis technique that provides only upper and lower bounds on the performance. In contrast, our scheduling framework computes the tasks' parameters that guarantee a certain performance under certain scheduling policies. Moreover, we apply the analysis directly on the more general CSDF model (although acyclic graphs only), while the framework in [TS09] applies the analysis to HSDF graphs. This means that a program modeled as an SDF/CSDF graph must be converted into HSDF in order to apply the analysis in [TS09]. Such conversion has disadvantages as mentioned earlier.

Moreira [Mor12] has investigated temporal analysis of hard real-time radio programs modeled as SDF graphs. He proposed a scheduling framework based on TDM combined with static allocation. He also proved that it is possible to derive a periodic schedule for the actors of a cyclic SDF graph if and only if the periods are greater than or equal to the maximum cycle mean of the graph. He formulated the conditions on the start times of the actors in the equivalent HSDF graph in order to enforce a periodic execution of every actor as a Linear Programming (LP) problem. Our approach differs from [Mor12] in the following aspects. First, we use the periodic task model which allows applying a variety of hard real-time scheduling algorithms for multiprocessors. Second, we use the CSDF model which is more expressive than the SDF model and perform the analysis directly on CSDF instead of converting it into HSDF as done in [Mor12].

Bodin et al. [BMKdD12] studied the throughput of programs modeled as SDF graphs under K-periodic schedules. In a K-periodic schedule, a schedule of  $K_i$  occurrences of task i is repeated every  $O_i$  time units. It has been shown that self-timed schedules are K-periodic schedules [CMQV89]. Thus, K-periodic schedules achieve

the maximum throughput for a given SDF program. When  $K_i = 1$  for all tasks, we obtain 1-periodic schedules which are equivalent to the schedules generated using the real-time periodic task model. Thus, K-periodic schedules serve as a powerful tool to analyze different scheduling policies. However, the realization of such schedules is more complex than the 1-periodic ones. In this dissertation, we prove the existence of 1-periodic schedules for acyclic CSDF graphs. 1-periodic schedules are easier to realize, however, this simplicity comes at the price of extra buffer requirements as shown later in Chapter 6.

Bouakaz et al. [BTV12, BT13] proposed recently a new dataflow model called *Affine Dataflow (ADF)* which extends the CSDF model. They proposed as well an analysis framework similar to ours to schedule the actors in an ADF graph as periodic tasks. They claim also that their analysis framework is capable of handling cyclic ADF graphs. An advantage of their approach is the enhanced expressiveness of the ADF model. The framework proposed in [BTV12, BT13] has been proposed after our framework and the authors in [BTV12, BT13] refer to our framework and compare empirically their framework with ours using the benchmarks explained later in Chapter 6. For most benchmarks, both CSDF and ADF achieve the same throughput and latency while requiring the same buffer sizes. However, in few cases, ADF results in reduced buffer sizes compared to CSDF [BT13].

Benabid-Najjar et al. [BNHMMK12] studied periodic scheduling of SDF graphs. For acyclic graphs, they proved that any acyclic SDF graph can be scheduled as a set of periodic tasks. For cyclic SDF graphs, they showed that the existence of a periodic schedule depends on the number of initial tokens in the graph cycles and provided a framework to derive the graph throughput under a periodic schedule. Compared to [BNHMMK12], our framework proves the existence of periodic schedules for acyclic CSDF graphs, which are more expressive than SDF graphs. Recently, Bodin et al. [BMKdD13] extended the work in [BNHMMK12] to cyclic CSDF graphs by providing a framework to derive the maximum throughput of a CSDF graph under a periodic schedule. Similar to [BT13], the work in [BMKdD13] is very recent and was proposed after our framework.

Geuns et al. [GHB13] proposed a technique to parallelize automatically sequential streaming programs containing while loops and if statements. Their technique derives a Structured Variable-rate Phased Dataflow (SVPDF) model of the parallelized program. After that, they perform scheduling analysis on the model to derive a schedule which ensures that the source and sink tasks can be scheduled in a strictly periodic fashion. A key difference between the analysis framework in [GHB13] and the framework in Chapter 4 is that the analysis in [GHB13] does not impose strict periodicity on all tasks. It is imposed only on the source and sink tasks. In contrast, the framework in Chapter 4 imposes strict periodicity on all the tasks to ensure that they conform

1.4. Related Work

with the real-time periodic task model. Using the real-time periodic task model has the following advantages. First, any scheduling algorithm that supports the real-time periodic task model can be used to schedule the programs. Second, multiple programs can be scheduled, while preserving temporal isolation, as long as the programs' tasks conform to the task model and satisfy the schedulability test of the used scheduling algorithm. Third, the minimum number of processors needed to schedule the programs can be determined in a fast and analytical way.

#### 1.4.2 Design Flows for Hard Real-Time Streaming Systems

Several design flows for automated mapping of streaming programs onto MPSoC platforms are surveyed in [GHP+09]. Most of these flows deal with soft real-time streaming systems. Additionally, these flows assume that the program model is derived manually by the designer/programmer. In contrast, our proposed design flow deals with hard real-time systems and derives the program model in a completely automated manner.

Distributed Operation Layer (DOL, [TBHH07]) is a framework for mapping parallel applications onto tiled MPSoCs. It accepts, as input, an application, which is specified as a process network, and an architecture specification. After that, it uses multi-objective optimization algorithms to perform the mapping of application to architecture. Then, it applies analytical performance analysis based on Real-Time Calculus (RTC, [CKT03]) to estimate the performance of the application after mapping. Our proposed design flow differs from DOL in the following aspects. First, we perform automated parallelization and model construction of the input applications, while DOL assumes that the input is a parallel application. Second, Real-Time Calculus gives worst-case upper and lower bounds on the performance, however, in reality these bounds may be rarely reached. In contrast, our proposed design flow guarantees a certain performance of the programs under certain scheduling policies.

PeaCE [HKL<sup>+</sup>08] is an integrated hardware/software co-design framework for embedded multimedia systems. It employs Synchronous Piggybacked Dataflow (SPDF) for computation tasks and Flexible Finite State Machines (fFSM) for control tasks. PeaCE uses hardware/software co-simulations during the design phase in order to meet certain timing constraints. In contrast, our proposed flow avoids these iterative steps by applying hard real-time multiprocessor scheduling theory to guarantee temporal isolation and a given throughput of each application running on the target MPSoC.

CA-MPSoC [SKS<sup>+</sup>10] is an automated design flow for mapping multiple applications modeled as SDF graphs onto Communication Assist (CA) based MPSoC platform. The flow uses non-preemptive scheduling to schedule the applications. In contrast, we consider only preemptive scheduling, because non-preemptive scheduling to meet all the deadlines is known to be NP-hard in the strong sense even for the uniprocessor

case [JSM91]. Moreover, we consider a more expressive MoC, namely the CSDF model.

CompSOC [GAC+13] is a platform and an associated design flow for running applications modeled as CSDF graphs. The platform part (called CoMPSoC [HGBH09]) provides predictability and *composability*, which means that the applications running on the system are completely isolated in terms of execution time, power, and access to shared resources. Similar to CoMPSoC, the hardware architecture proposed in Chapter 5 is designed to provide predictability. For the software side, CompSOC uses a custom OS called Compose that implements two-level hierarchical scheduling. In the first (or base) level, it divides the processor time into fixed intervals and uses TDM scheduling to provide complete isolation between the applications running on different intervals. In the second level, each interval may use a different scheduling policy (e.g., EDF or round-robin) to schedule the tasks executed within the interval. The associated design flow with CompSOC accepts, as input, the CSDF models of the application. Then, it uses SDF<sup>3</sup> [SGB06] to derive the buffer sizes and TDM interval sizes needed to guarantee a certain performance. Therefore, CompSOC provides a platform for executing given parallel applications, while our proposed design flow is concerned with providing a complete integrated design flow that parallelizes the applications and then derives the scheduling and platform parameters that guarantee a certain performance.

MAPS [Cas13] is a design flow for mapping dataflow applications onto MPSoCs. The design flow accepts, as input, a set of sequential programs written in a variant of C called *C for Process Networks (CPN)*. After that, it parallelizes these programs and generates a performance analysis model based on Kahn Process Networks (KPN, [Kah74]). Then, it uses a simulation-based composability analysis to provide certain performance guarantees on the target platform. Our proposed design flow differs from MAPS in that our flow provides hard real-time guarantees to the programs, while MAPS provides soft real-time guarantees.

MAMPSx [FSH<sup>+</sup>13] is an automated design flow for mapping applications modeled as SDF graphs onto heterogeneous MPSoCs while providing performance guarantees. The flow requires the designer to specify a sequential implementation (in C) of each actor in an SDF graph. The generated implementation uses either self-timed scheduling or TDM scheduling to ensure meeting the throughput constraints. In contrast, our proposed design flow starts from sequential applications written in C, and consequently, the parallelized programs are automatically extracted from the initial C programs. Moreover, we schedule the actors as real-time periodic tasks, which enables applying very fast schedulability analysis to determine the minimum number of required processors. Instead, [FSH<sup>+</sup>13] applies design space exploration techniques to determine the minimum number of processors and the mapping. Finally, our methodology supports multiple applications to run simultaneously on an MPSoC, while the work in [FSH<sup>+</sup>13] does not support multiple applications.

#### 1.5 Organization of this Dissertation

The rest of this dissertation is organized as follows:

- 1. Chapter 2 presents an overview of dataflow models and hard real-time scheduling theory. This overview is necessary to understand the subsequent chapters.

- 2. Chapter 3 presents the first two stages in the proposed design flow: automated parallelization and model construction.

- 3. Chapter 4 presents the key contribution of this dissertation: scheduling framework for streaming programs. This framework constitutes the third stage in the proposed design flow.

- 4. Chapter 5 presents the fourth stage of the proposed design flow (i.e., ESL synthesis) and explains the hardware and software parts of the synthesized systems.

- 5. Chapter 6 presents the results of empirical evaluation of the proposed scheduling framework and design flow. This empirical evaluation is performed through a set of experiments.

- 6. Chapter 7 ends this dissertation with conclusions and suggestions for future work.

# Chapter 2

# **Background**

Essentially, all models are wrong, but some are useful.

George E. P. Box

HIS chapter introduces the notations, definitions, and existing results that are used in the subsequent chapters. It also contains material from the theory of dataflow models and hard real-time scheduling that is needed to understand the subsequent chapters.

### 2.1 Notations

We present in Table 2.1 a summary of the mathematical notations used throughout this dissertation.

**Definition 2.1.1** (Partition of a Set). Let V be a set. An x-partition of V is a set, denoted by  ${}^xV$ , where

$$^{x}V = \{^{x}V_{1}, ^{x}V_{2}, \cdots, ^{x}V_{x}\},\$$

such that each subset  $^{x}V_{i}\subseteq V$ , and

$$\bigcap_{i=1}^{x} V_i = \emptyset \text{ and } \bigcup_{i=1}^{x} V_i = V$$

## 2.2 Parallel Execution of Programs

We start by defining what we mean by a *program*.

| Symbol         | Meaning                                               |

|----------------|-------------------------------------------------------|

| $\mathbb{N}$   | The set of natural numbers excluding zero             |

| $\mathbb{N}_0$ | $\mathbb{N} \cup \{0\}$                               |

| $\mathbb Z$    | The set of integers                                   |

| $\mathbb{Q}$   | The set of rational numbers                           |

| x              | The cardinality (i.e., size) of a set <i>x</i>        |

| $\hat{x}$      | The maximum value of <i>x</i>                         |

| ž              | The minimum value of $x$                              |

| lcm            | The least common multiple operator                    |

| gcd            | The greatest common divisor operator                  |

| ÷              | The integer division operator                         |

| mod            | The integer modulo operator                           |

| $^{x}V$        | An $x$ -partition of a set $V$ (see Definition 2.1.1) |

**Table 2.1:** *Summary of mathematical notations*

**Definition 2.2.1** (Program). A **program** (also called **application**) is a sequence of operations (also called statements) that transform a given input to an output.

A statement can be a simple expression (e.g., z = x + y), an invocation of a function (e.g., z = f(x,y)), or a control statement (e.g., if(x>1)). For some programs, the statements need to be executed in a strictly sequential way in order to maintain the correct functionality of the program. For some other programs, the statements can be executed in a parallel fashion while maintaining the correct functionality. In general, the main objective of executing the statements of a given program in parallel is to achieve a **speedup**. Let  $\Delta_1$  be the time needed to run the program on one processor, and  $\Delta_m$  be the time needed to run the program on m processors. We define the speedup as:

speedup =

$$\frac{\Delta_1}{\Delta_m}$$

(2.1)

An ideal parallel implementation of a program running on m processors achieves a speedup equal to m. However, Amdahl in 1967 [Amd67] observed that, in reality, any program consists of two portions: a *parallelizable* portion, and a *sequential* portion. The statements in the sequential portion *can not* be executed in parallel, and hence, do not benefit from execution on multiprocessor systems. Let  $f \in [0,1]$  be a fraction that denotes the relative size of the parallelizable portion of a program. Amdahl showed that the actual speedup is given by:

$$speedup = \frac{1}{(1-f) + \frac{f}{m}}$$

(2.2)

For example, for a program where f = 0.9 (i.e., 90% of the program is parallelizable), the maximum speedup is:

maximum speedup =

$$\lim_{m \to \infty} \frac{1}{(1 - 0.9) + \frac{0.9}{m}} = \frac{1}{0.1} = 10$$

(2.3)

This means that the maximum speedup that can be obtained by executing the program on a multiprocessor system is 10. Therefore, executing this program on more than 10 processors does not result in an extra speedup.

The ability to execute two program statements in parallel is constrained by the *data dependencies* between them. For example, if a statement  $S_j$  requires the data produced by statement  $S_i$ , then  $S_j$  must be executed after  $S_i$  has completed its execution. To find all data dependencies in a given program, one needs to perform **dependency analysis**. Dependency analysis reveals, for a given program, all data dependencies among the statements of the program. Let S be a program where  $S_i$  and  $S_j$  represent two statements of the program. Additionally, let INPUT( $S_i$ ) be the set of resources read by  $S_i$ , and OUTPUT( $S_i$ ) be the set of resources written to by  $S_i$ . We denote the sequential execution of  $S_j$  after  $S_i$  by  $S_i \rightarrow S_j$ , while we denote the parallel execution of  $S_i$  and  $S_j$  by  $S_i \parallel S_j$ . Bernstein [Ber66] showed that  $S_i \rightarrow S_j$  and  $S_i \parallel S_j$  are equivalent provided that:

- 1.  $OUTPUT(S_i) \cap OUTPUT(S_j) = \emptyset$

- 2.  $OUTPUT(S_i) \cap INPUT(S_j) = \emptyset$

- 3. OUTPUT(S<sub>i</sub>)  $\cap$  INPUT(S<sub>i</sub>) =  $\emptyset$

The three conditions above are known in the literature as **Bernstein's conditions**. They form the basis of how we can analyze a given program to determine the statements that can be executed in parallel. During the execution of a program S, we say that a statement  $S_i$  precedes a statement  $S_j$ , denoted by  $S_i < S_j$ , if  $S_i$  is executed before  $S_j$ . Given a program S where  $S_i$  and  $S_j$  are two statements and  $S_i < S_j$ , one can identify the following types of data dependencies:

- Flow (True) Dependence: If  $OUTPUT(S_i) \cap INPUT(S_j) \neq \emptyset$

- Anti-Dependence: If INPUT( $S_i$ )  $\cap$  OUTPUT( $S_j$ )  $\neq \emptyset$

- Output Dependence: If  $OUTPUT(S_i) \cap OUTPUT(S_j) \neq \emptyset$

- Input Dependence: If INPUT( $S_i$ )  $\cap$  INPUT( $S_j$ )  $\neq \emptyset$

Standard dataflow analysis [ALSU86] is a body of techniques that derive the data dependencies among the statements of a given program. Array dataflow analysis [Fea91] is a technique which performs dataflow analysis for SANLP programs. Feautrier [Fea91] showed that array dataflow analysis can be used to construct a *parallel* version of a given SANLP program. This means that programs written in SANLP form can be

<sup>&</sup>lt;sup>1</sup>resource here means hardware resources used to store data such as memory locations and registers.

automatically analyzed and parallelized. An example of a tool which implements such automated analysis and parallelization is the PNgen compiler [VNS07]. The details of how a parallel program is derived using automated parallelization are explained in Chapter 3.

## 2.3 Cyclo-Static Dataflow (CSDF)

As mentioned earlier in Chapter 1, we use in this dissertation the Cyclo-Static Dataflow (CSDF) model for modeling streaming programs. In this section, we introduce this model and its properties.

CSDF is a dataflow model that extends the well-known Synchronous Dataflow (SDF, [LM87]) model. It is defined in [BELP96] as a directed graph G = (A, E), where A is a set of **actors** that correspond to the graph nodes and  $E \subseteq A \times A$  is a set of **communication channels** that correspond to the graph edges. Actors represent statements in the program that transform incoming data streams into outgoing data streams, while communication channels represent data dependencies among the actors. The communication channels carry streams of data, and an atomic data object is called a **token**. A channel  $E_u \in E$  is a first-in, first-out (FIFO) queue with unbounded capacity defined by a tuple  $E_u = (A_i, A_j)$ . The tuple means that  $E_u$  is directed from  $A_i$  (called source) to  $A_i$  (called destination). An actor receiving an input stream of the program is called input actor, and an actor producing an output stream of the program is called output actor. A path  $W_k$  between actors  $A_a$  and  $A_z$  is an ordered sequence of channels defined as  $W_k = \{(A_a, A_b), (A_b, A_c), \dots, (A_y, A_z)\}$ . A path  $W_k$  is called *output path* if the starting actor  $A_a$  is an input actor and the ending actor  $A_z$  is an output actor. For a graph G, we use W to denote the set of all output paths in G. Each actor  $A_i \in A$  is associated with two sets of channels and two sets of actors. The sets of channels are the *input channels set*, denoted by  $inp(A_i)$ , which consists of all the input channels to  $A_i$ , and the *output channels set*, denoted by out( $A_i$ ), which consists of all the output channels from  $A_i$ . The sets of actors are the *successors set*, denoted by  $succ(A_i)$ , and the *predecessors set*, denoted by  $prec(A_i)$ . They are given by:

$$\operatorname{succ}(A_i) = \{ A_i \in A : \exists E_u = (A_i, A_i) \in E \}$$

(2.4)

$$\operatorname{prec}(A_i) = \{ A_i \in A : \exists E_u = (A_i, A_i) \in E \}$$

(2.5)

We assume that: (1) for any input actor  $A_i$ ,  $\operatorname{prec}(A_i) = \emptyset$ , and (2) for any output actor  $A_j$ ,  $\operatorname{succ}(A_j) = \emptyset$ .

Every actor  $A_j \in A$  has an **execution sequence**  $[f_j(1), f_j(2), \dots, f_j(\mathcal{N}_j)]$  of length  $\mathcal{N}_j$ . The interpretation of this sequence is: the nth time that actor  $A_j$  is fired, it executes the code of function  $f_j(((n-1) \mod \mathcal{N}_j) + 1)$ . Similarly, production and consumption rates of tokens are also *sequences* of length  $\mathcal{N}_j$  in CSDF. The token

#### **Algorithm 1** Levels(G)

```

Require: Acyclic CSDF graph G = (A, E)

1: i \leftarrow 1

2: while A \neq \emptyset do

3: {}^{\mathbb{L}}A_i \leftarrow \{A_j \in A : \operatorname{prec}(A_j) = \emptyset\}

4: E'_i \leftarrow \{E_u \in E : \exists A_k \in {}^{\mathbb{L}}A_i \text{ such that } E_u = (A_k, A_l)\}

5: A \leftarrow A \setminus {}^{\mathbb{L}}A_i

6: E \leftarrow E \setminus E'_i

7: i \leftarrow i + 1

8: end while

9: \mathbb{L} \leftarrow i - 1

10: return \mathbb{L}-partition of A given by \mathbb{L}A = \{{}^{\mathbb{L}}A_1, {}^{\mathbb{L}}A_2, \dots, {}^{\mathbb{L}}A_{\mathbb{L}}\}.