## Cover Page

# Universiteit Leiden

The handle <a href="http://hdl.handle.net/1887/119358">http://hdl.handle.net/1887/119358</a> holds various files of this Leiden University dissertation.

Author: Mirsoleimani, S.A.

Title: Structured parallel programming for Monte Carlo tree search

**Issue Date:** 2020-06-17

# Structured Parallel Programming FOR Monte Carlo Tree Search

S. Ali Mirsoleimani

# **Structured Parallel Programming**

Monte Carlo Tree Search

## **Proefschrift**

ter verkrijging van de graad van Doctor aan de Universiteit Leiden, op gezag van Rector Magnificus prof. mr. C.J.J.M. Stolker, volgens besluit van het College voor Promoties te verdedigen op woensdag 17 juni 2020 klokke 11.15 uur

door

**Sayyed Ali Mirsoleimani** geboren te Abadeh, Iran in 1986

Promotoren:

Prof. dr. H. J. van den Herik

Prof. dr. A. Plaat

Copromotor:

Dr. J. A. M. Vermaseren Nikhef

Promotiecommissie:

Prof. dr. P. J. G. Mulders Vrije Universiteit Amsterdam

Prof. dr. F. J. Verbeek Prof. dr. H. A. G. Wiishoff

Dr. F. Khunjush Shiraz University, Shiraz, Iran

Dr. W. A. Kosters

Dr. ir. A. L. Varbanescu Universiteit van Amsterdam

HEPGAME, ERC Advanced Grant No. 320651

The research reported in this thesis has been additionally funded by Nikhef, the Nationaal instituut voor subatomaire fysica.

In the first year, the research reported in this thesis has been performed at Tilburg center for Cognition and Communication (TiCC) at Tilburg University, the Netherlands.

The research reported in this thesis has been completed at Leiden Centre of Data Science (LCDS) hosted by Leiden Institute of Advanced Computer Science (LIACS) at the Faculty of Science, Universiteit Leiden, the Netherlands.

SIKS Dissertation Series No. 2020-08

The research reported in this thesis has been carried out under the auspices of SIKS, the Dutch Research School for Information and Knowledge Systems.

Copyright © 2020 by S.A. Mirsoleimani

An electronic version of this dissertation is available at http://openaccess.leidenuniv.nl/.

I would like to dedicate this thesis to my wife Elahe and to my parents, for all of their love and support.

In loving memory of my grandfathers, Bahram and Abolghasem

## Preface

The thesis is part of a bigger project, the HEPGAME (High Energy Physics Game). The project started in 2011 when Jos Vermaseren developed the first ideas on improving FORM at Nikhef, Amsterdam. In 2012 he submitted an ERC advanced research grant together with Tilburg University. It was accepted on 12/12/2012. Half a year later in July 2013, the program started. The main objective for HEPGAME was the utilization of AI solutions, particularly by using MCTS for simplification of HEP calculations. One of the issues is solving mathematical expressions of interest with millions of terms. Up to 2011, these calculations were executed with the FORM program, which is software for symbolic manipulation. These calculations are computationally intensive and take a large amount of time. Hence, the FORM program was parallelized to solve large equations in a reasonable amount of time. Therefore, any new algorithm, for instance, the ones based on MCTS, should also be parallelized. Here our research comes in. It is dedicated to parallelization of MCTS on multi-core and manycore processors. The research was ambitious and challenging. Therefore, we divided the research area into three main parts: (1) the evaluation of current methods for parallelization of MCTS, (2) addressing the shortcomings in these methods, and (3) providing new ways of parallelization for MCTS. In the first part, we investigated the current methods and evaluated them in terms of performance and scalability on both multi-core and manycore processors. In the second part, we examined how we can solve the actual shortcomings in the existing parallelization methods for MCTS. The third part was dedicated to finding new ideas, methods, and ways beyond the existing ones to parallelize MCTS.

# Contents

| Pr | eface   |          |                                                       | vii   |

|----|---------|----------|-------------------------------------------------------|-------|

| Co | onten   | ts       |                                                       | ix    |

| Li | st of l | Definiti | ions                                                  | xv    |

| Li | st of l | Figures  |                                                       | xvii  |

| Li | st of ' | Гables   |                                                       | xxi   |

| Li | st of l | Listings | S                                                     | xxiii |

| Li | st of   | Abbrev   | iations                                               | xxv   |

| 1  | Intr    | oductio  | on                                                    | 1     |

|    | 1.1     | HEPG.    | AME                                                   | . 2   |

|    | 1.2     | Monte    | e Carlo Tree Search                                   | . 2   |

|    | 1.3     | Paralle  | elism and Parallelization                             | . 3   |

|    |         | 1.3.1    | Thread-level Parallelization                          | . 4   |

|    |         | 1.3.2    | Task-level Parallelization                            | . 4   |

|    | 1.4     | Gener    | al Obstacles for Parallelization of MCTS              | . 5   |

|    |         | 1.4.1    | Irregular Parallelism Causes Load Balancing Overhead  | . 6   |

|    |         | 1.4.2    | Shared Data Structure Causes Synchronization Overhead | . 6   |

|    |         | 1.4.3    | Ignoring Data Dependencies Causes Search Overhead     | . 7   |

|    |         | 1.4.4    | Complex Interactions Leading to Deployment Overhead   | . 8   |

|   | 1.5  | Perfor  | mance and Scalability Studies                         |

|---|------|---------|-------------------------------------------------------|

|   | 1.6  | Scope   | and Research Goals                                    |

|   | 1.7  | Proble  | em Statement and Research Questions                   |

|   | 1.8  | Resear  | rch Methodology                                       |

|   | 1.9  | Struct  | ure of the thesis                                     |

|   | 1.10 | Contri  | butions                                               |

| 2 | Bac  | kgroun  | d 15                                                  |

|   | 2.1  | Upper   | Confidence Bound (UCB)                                |

|   | 2.2  | Upper   | Confidence Bounds for Trees (UCT)                     |

|   |      | 2.2.1   | UCT Formula                                           |

|   |      | 2.2.2   | UCT Algorithm                                         |

|   | 2.3  | Paralle | elization Methods for MCTS                            |

|   |      | 2.3.1   | Parallel Methods with a Shared Data Structure 17      |

|   |      | 2.3.2   | Parallel Methods with More than one Data Structure 18 |

|   | 2.4  | Case S  | Studies                                               |

|   |      | 2.4.1   | Case 1: The Game of Hex                               |

|   |      | 2.4.2   | Case 2: Horner Schemes                                |

|   | 2.5  | Perfor  | mance Metrics                                         |

|   |      | 2.5.1   | Playout Speedup                                       |

|   |      | 2.5.2   | Playing Strength                                      |

|   | 2.6  | Our Pa  | arallelUCT Package                                    |

|   |      | 2.6.1   | Framework of multiple benchmark problems              |

|   |      | 2.6.2   | Framework of multiple parallelization methods 23      |

|   |      | 2.6.3   | Framework of multiple programming models 23           |

| 3 | Thre | ead-lev | el Parallelization for MCTS 25                        |

|   | 3.1  | Micro-  | benchmark Code Performance                            |

|   |      | 3.1.1   | Xeon Phi Micro-architecture                           |

|   |      | 3.1.2   | Experimental Setup                                    |

|   |      | 3.1.3   | Experimental Design                                   |

|   |      | 3.1.4   | Experimental Results                                  |

|   |      | 3.1.5   | Section Conclusion                                    |

|   | 3.2  | FUEG    | O Performance and Scalability                         |

|   |      | 3.2.1   | Experimental Setup                                    |

|   |      | 3.2.2   | Experimental Design                                   |

|   |      | 3.2.3   | Experimental Results                                  |

|   |      | 3.2.4   | Section Conclusion                                    |

|   |      | 3.2.5   | Answer to RQ1a for FUEGO                              |

|   | 3.3  | Paralle | elUCT Performance and Scalability                     |

|   |      | 3.3.1 Experimental Setup                     | 40        |

|---|------|----------------------------------------------|-----------|

|   |      |                                              | 41        |

|   |      |                                              | ·-<br>41  |

|   |      |                                              | 46        |

|   |      |                                              | . o<br>47 |

|   | 3.4  |                                              | 17<br>48  |

|   | 3.5  |                                              | 48        |

| 4 | Task | -level Parallelization for MCTS              | 51        |

|   | 4.1  | Irregular Parallelism Challenge              | 52        |

|   | 4.2  | Achieving Task-level Parallelization         | 52        |

|   |      | 4.2.1 Decomposition of Iterations into Tasks | 53        |

|   |      |                                              | 53        |

|   | 4.3  |                                              | 53        |

|   |      | 4.3.1 Cilk Plus                              | 54        |

|   |      |                                              | 54        |

|   | 4.4  |                                              | 54        |

|   | 4.5  |                                              | 56        |

|   |      |                                              | 56        |

|   |      |                                              | 57        |

|   | 4.6  |                                              | 57        |

|   | 4.7  | , ,                                          | 58        |

|   | 4.8  |                                              | 58        |

|   | 4.9  | 1 6                                          | 59        |

|   |      | 1                                            | 60        |

|   |      |                                              | 64        |

|   |      |                                              | 64        |

| 5 | A Lo | ock-free Algorithm for Parallel MCTS         | 67        |

|   | 5.1  | Shared Data Structure Challenge              | 68        |

|   |      |                                              | 69        |

|   |      |                                              | 69        |

|   |      | 5.1.3 Protecting Shared Data Structure       | 70        |

|   | 5.2  |                                              | 71        |

|   |      |                                              | 71        |

|   |      |                                              | 72        |

|   | 5.3  |                                              | 73        |

|   | 5.4  | č                                            | 77        |

|   | 5.5  | •                                            | 77        |

|   |      |                                              | 78        |

|   |      | 5.5.2   | Performance Metrics                            |

|---|------|---------|------------------------------------------------|

|   |      | 5.5.3   | Hardware                                       |

|   | 5.6  | Experi  | mental Design                                  |

|   | 5.7  | Experi  | mental Results                                 |

|   |      | 5.7.1   | Scalability and $C_p$ parameters               |

|   |      | 5.7.2   | GSCPM vs. Root Parallelization 82              |

|   | 5.8  | Answe   | er to RQ3                                      |

| 6 | Pipe | line Pa | ttern for Parallel MCTS 85                     |

|   | 6.1  | Data D  | Dependencies Challenges                        |

|   |      | 6.1.1   | Loop Independent Data Dependency               |

|   |      | 6.1.2   | Loop Carried Data Dependency                   |

|   |      | 6.1.3   | Why a Pipeline Pattern?                        |

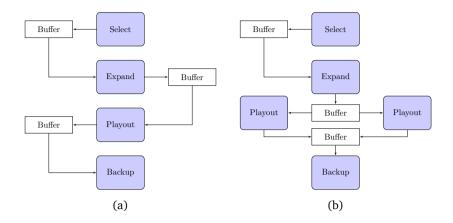

|   | 6.2  | Design  | of 3PMCTS                                      |

|   |      | 6.2.1   | A Pipeline Pattern for MCTS                    |

|   |      | 6.2.2   | Pipeline Construction                          |

|   | 6.3  | Impler  | nentation Considerations                       |

|   | 6.4  | Experi  | mental Setup                                   |

|   |      | 6.4.1   |                                                |

|   |      | 6.4.2   | Performance Metrics                            |

|   |      | 6.4.3   | Hardware                                       |

|   | 6.5  | Experi  | mental Design                                  |

|   | 6.6  | Experi  | mental Results                                 |

|   |      | 6.6.1   | Performance and Scalability of 3PMCTS 94       |

|   |      | 6.6.2   | Flexibility of Task Decomposition in 3PMCTS 96 |

|   | 6.7  | Answe   | er to RQ4                                      |

| 7 | Ense | emble U | JCT Needs High Exploitation 99                 |

|   | 7.1  |         | ible UCT                                       |

|   | 7.2  |         | d Work                                         |

|   | 7.3  |         | mental Setup                                   |

|   |      | 7.3.1   | The Game of Hex                                |

|   |      | 7.3.2   | Hardware                                       |

|   | 7.4  |         | mental Design                                  |

|   | 7.5  | -       | mental Results                                 |

|   | 7.6  |         | er to the First Part of RO5                    |

| 8   | An A   | analysis of Virtual Loss in Parallel MCTS | 109 |

|-----|--------|-------------------------------------------|-----|

|     | 8.1    | Virtual Loss                              | 110 |

|     | 8.2    | Related Work                              | 112 |

|     | 8.3    | Experimental Setup                        | 112 |

|     | 8.4    | Experimental Design                       | 112 |

|     | 8.5    | Experimental Results                      | 113 |

|     | 8.6    | Answer to the Second Part of RQ5          | 115 |

|     | 8.7    | A Complete answer to RQ5                  | 115 |

| 9   | Con    | clusions and Future Research              | 117 |

|     | 9.1    | Answers to the RQs                        | 117 |

|     |        | 9.1.1 Answer to RQ1                       | 117 |

|     |        | 9.1.2 Answer to RQ2                       |     |

|     |        | 9.1.3 Answer to RQ3                       |     |

|     |        | 9.1.4 Answer to RQ4                       |     |

|     |        | 9.1.5 Answer to RQ5                       |     |

|     | 9.2    | Answer to the PS                          |     |

|     | 9.3    | Limitations                               |     |

|     |        | 9.3.1 Maximizing Hardware Usage           | 120 |

|     |        | 9.3.2 Using More Case Studies             |     |

|     | 9.4    | Future Research                           |     |

| Bil | oliogi | raphy                                     | 123 |

| ۸   |        |                                           | 101 |

| Ар  | pend   | ices                                      | 131 |

| Α   | Micı   | o-benchmark Programs                      | 133 |

| В   | Stati  | istical Analysis of Self-play Experiments | 135 |

| С   | Imp    | lementation of GSCPM                      | 137 |

|     | C.1    | TBB                                       | 137 |

|     | C.2    | Cilk Plus                                 | 137 |

|     | C.3    | TPFIFO                                    |     |

| D   | Imp    | lementation of 3PMCTS                     | 139 |

|     | D.1    | Definition of Token Data Type (TDT)       | 139 |

|     | D.2    | TBB Implementation Using TDD              | 141 |

| Su  | mma    | rv                                        | 143 |

| X | 1 | 7 | 1 |

|---|---|---|---|

|   |   |   |   |

| Samenvatting             | 145 |

|--------------------------|-----|

| Acknowledgment           | 147 |

| Curriculum Vitae         | 149 |

| Publications             | 151 |

| SIKS Dissertation Series | 153 |

# List of Definitions

| 1.1  | Parallelization              | 5 |

|------|------------------------------|---|

| 1.2  | Thread                       | 4 |

| 1.3  | Multi-core Processor         | 1 |

| 1.4  | Task                         | 4 |

| 1.5  | Many-core Processor          | 5 |

| 1.6  | Parallel Pattern             | 5 |

| 1.7  | Irregular Parallelism        | 5 |

| 1.8  | Load Balancing               | 5 |

| 1.9  | Shared Data Structure        | 7 |

| 1.10 | Synchronization              | 7 |

| 1.11 | Loop Carried Data Dependency | 7 |

|      |                              | 7 |

| 1.13 | Search Overhead              | 7 |

| 1.14 | Complex Interactions         | 3 |

| 1.15 | Deployment Overhead          | 3 |

| 1.16 | Performance Study            | 3 |

| 1.17 | Playout Speedup              | 3 |

| 1.18 | Playing Strength             | 3 |

| 1.19 | Scalability Study            | 9 |

| 1.20 | Memory Bandwidth             | ) |

| 1.21 | Uniform Memory Access        | ) |

| 1.22 | Many Integrated Core         | ) |

| 1.23 | Non Uniform Memory Access    | ) |

| 2.1 | Exploitation                           | 16  |

|-----|----------------------------------------|-----|

| 2.2 | Exploration                            | 16  |

| 2.3 | Tree Parallelization                   | 18  |

| 2.4 | Root Parallelization                   | 19  |

| 2.5 | Strong Scalability                     | 21  |

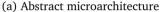

| 3.1 | Thread Affinity Policy                 | 28  |

| 3.2 | Double-Precision Floating-Point Format | 29  |

| 3.3 | Integer Format                         | 30  |

| 4.1 | Iteration Pattern                      | 53  |

| 4.2 | Fork-join Pattern                      | 53  |

| 4.3 | Iteration-level Task                   | 55  |

| 4.4 | Iteration-level Parallelism            | 55  |

| 4.5 | Fork-join Parallelism                  | 55  |

| 5.1 | Race Condition                         | 69  |

| 5.2 | Lock-based                             | 70  |

| 5.3 | Lock-free                              | 71  |

| 6.1 | Operation-Level Task                   | 86  |

| 6.2 | Operation-Level Parallelism            | 86  |

| 6.3 | Sequence Pattern                       | 87  |

| 6.4 | Iteration Pattern                      | 87  |

| 6.5 | Pipeline Pattern                       | 88  |

| 8.1 | Virtual Loss                           | 110 |

# List of Figures

| 1.1 | An example of the search tree                                                                                                              | 3  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | The main loop of MCTS                                                                                                                      | 3  |

| 1.3 | One iteration of MCTS                                                                                                                      | 4  |

| 2.1 | A sample board for the game of Hex                                                                                                         | 19 |

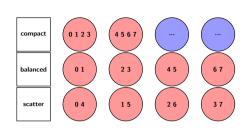

| 3.1 | Intel Xeon Phi Architecture.                                                                                                               | 29 |

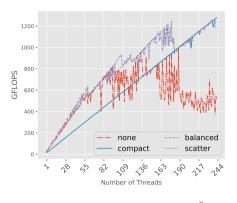

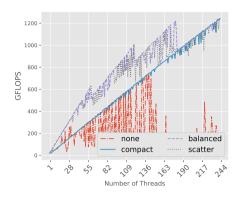

| 3.2 | Performance and scalability of double-precision operations for different                                                                   |    |

|     | numbers of iterations                                                                                                                      | 31 |

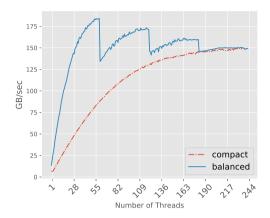

| 3.3 | Memory bandwidth of double-precision operations on the Xeon Phi for                                                                        |    |

|     | increasing numbers of threads. Each interval contains 27 points                                                                            | 32 |

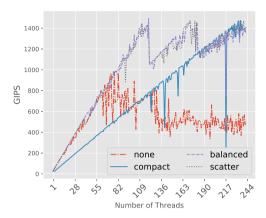

| 3.4 | Performance and scalability of integer operations of the Xeon Phi for                                                                      |    |

|     | different numbers of threads                                                                                                               | 33 |

| 3.5 | Performance and scalability of Fuego in terms of PPS when it makes<br>the second move. Average of 100 games for each data point. The board |    |

|     | size is $9 \times 9$                                                                                                                       | 35 |

| 3.6 |                                                                                                                                            |    |

|     | with $N/2$ threads. The board size is $9 \times 9$                                                                                         | 38 |

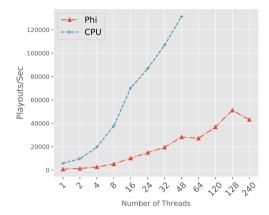

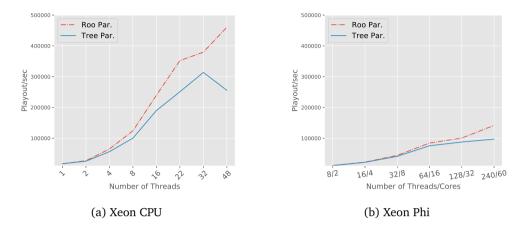

| 3.7 | Performance and scalability of ParallelUCT in terms of PPS for both                                                                        |    |

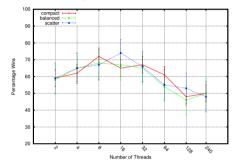

|     | Tree and Root Parallelization.                                                                                                             | 43 |

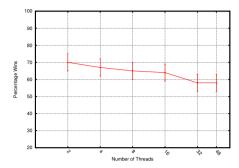

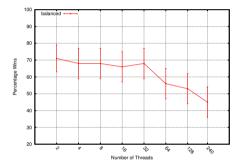

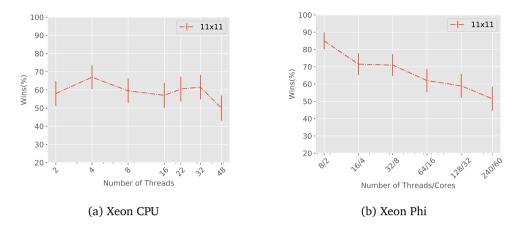

| 3.8 | Scalability of ParallelUCT in terms of PW for Tree Parallelization                                                                         | 44 |

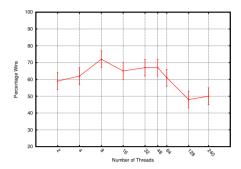

| 3.9 | Scalability of ParallelUCT in terms of PW for Root Parallelization                                                                         | 46 |

xviii List of Figures

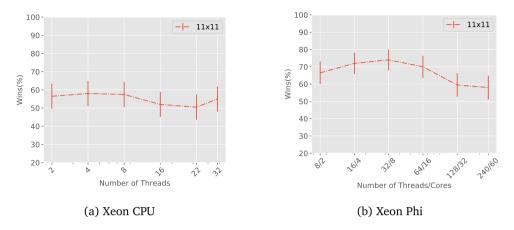

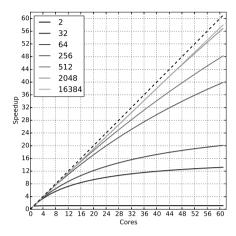

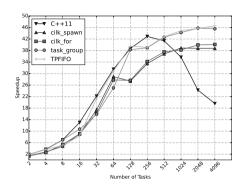

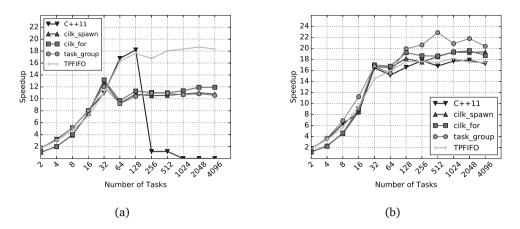

| 4.1 | The scalability profile produced by Cilkview for the GSCPM algorithm.  The number of tasks is shown. Higher is more fine-grained                                                                                                                                                                                                             | 57 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

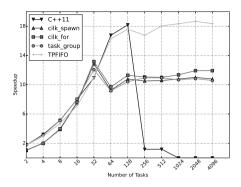

| 4.2 | Speedup for task-level parallelization utilizing five methods for parallel implementation from four threading libraries. Higher is better. Left: coarse-grained parallelism. Right: fine-grained parallelism                                                                                                                                 | 61 |

| 4.3 | Comparing Cilkview analysis with TPFIFO speedup on the Xeon Phi. The dots show the number of tasks used for TPFIFO. The lines show the number of tasks used for Cilkview.                                                                                                                                                                    | 63 |

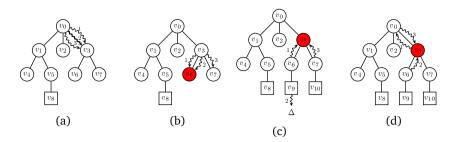

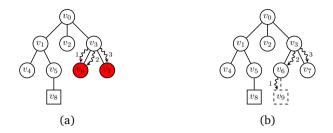

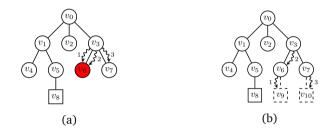

| 5.1 | (5.1a) The initial search tree. The internal and non-terminal leaf nodes are circles. The terminal leaf nodes are squares. The curly arrows represent threads. (5.1b) Thread 1 and 2 are expanding node $v_6$ . (5.1c) Thread 1 and 2 are updating node $v_3$ . (5.1d) Thread 1 is selecting node $v_3$ while thread 2 is updating this node | 69 |

| 5.2 | Tree parallelization with coarse-grained lock.                                                                                                                                                                                                                                                                                               | 72 |

| 5.3 | Tree parallelization with fine-grained lock                                                                                                                                                                                                                                                                                                  | 72 |

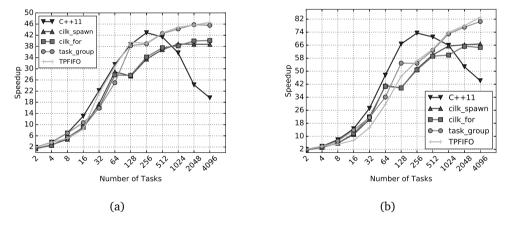

| 5.4 | The scalability of Tree Parallelization for different parallel programming libraries when $C_p=1$ . (5.4a) Coarse-grained lock. (5.4b) Lock-                                                                                                                                                                                                 |    |

| 5.5 | free                                                                                                                                                                                                                                                                                                                                         | 80 |

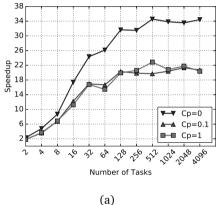

| 5.6 | (5.6a) The scalability of the algorithm for different $C_p$ values. (5.6b) Changes in the depth of tree when the number of tasks are increasing.                                                                                                                                                                                             | 81 |

| 5.7 | The playing results for lock-free Tree Parallelization versus Root Parallelization. The first value for $C_p$ is used for Tree Parallelization and the second value is used for Root Parallelization                                                                                                                                         | 82 |

| 6.1 | (6.1a) Flowchart of a pipeline with sequential stages for MCTS. (6.1b) Flowchart of a pipeline with parallel stages for MCTS                                                                                                                                                                                                                 | 88 |

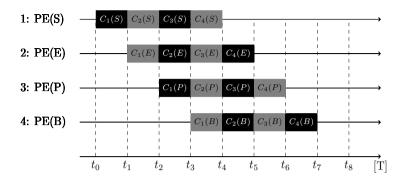

| 6.2 | Scheduling diagram of a pipeline with sequential stages for MCTS. The computations for stages are equal.                                                                                                                                                                                                                                     | 89 |

| 6.3 | Scheduling diagram of a pipeline with sequential stages for MCTS. The computations for stages are not equal                                                                                                                                                                                                                                  | 89 |

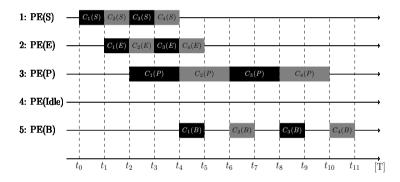

| 6.4 | Scheduling diagram of a pipeline with parallel stages for MCTS. Using parallel stages create load balancing                                                                                                                                                                                                                                  | 90 |

| 6.5 | The 3PMCTS algorithm with a pipeline that has three parallel stages (i.e., EXPAND, RANDOMSIMULATION, and EVALUATION)                                                                                                                                                                                                                         | 91 |

List of Figures xix

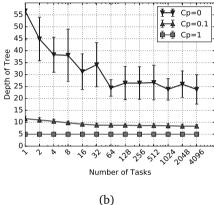

| 6.6 | Playout-speedup as function of the number of tasks (tokens). Each data point is an average of 21 runs for a search budget of 8192 playouts. The constant $C_p$ is 0.5. Here a higher value is better                                                                                                   | 94  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7 | Number of operations as function of the number of tasks (tokens). Each data point is an average of 21 runs for a search budget of 8192 playouts. Here a lower value is better.                                                                                                                         | 95  |

| 6.8 | Percentage of win as function of the number of tasks (tokens). Each data point is the outcome of 100 rounds of playing between the two opponent players. Each player has a search budget of $2^{20}=1,048,576$                                                                                         |     |

|     | playouts in each round. Here a higher value is better                                                                                                                                                                                                                                                  | 97  |

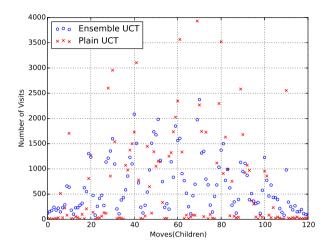

| 7.1 | The number of visits for root's children in Ensemble UCT and plain UCT. Each child represents an available move on the empty Hex board with size $11 \times 11$ . Both Ensemble UCT and plain UCT have 80,000                                                                                          |     |

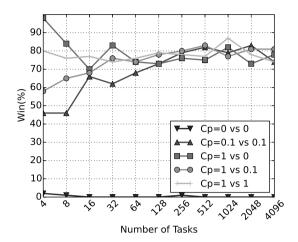

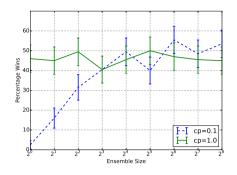

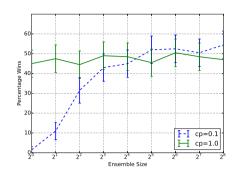

| 7.2 | playouts and $C_p=0$ . In Ensemble UCT, the size of the ensemble is 8 The percentage of wins for ensemble UCT is reported. The value of $C_p$ for plain UCT is always 1.0 when playing against Ensemble UCT. To                                                                                        | 104 |

|     | the left few large UCT trees, to the right many small UCT trees                                                                                                                                                                                                                                        | 105 |

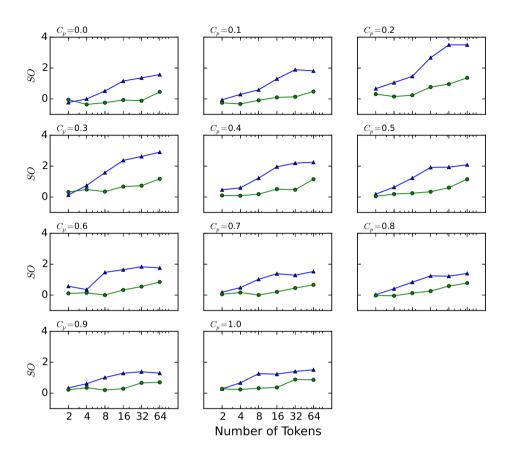

| 8.1 | Search overhead $(SO)$ for Horner (average of 20 instances for each data point). Tree parallelization is the green line which is indicated by circles, and Tree Parallelization with virtual loss is the blue line which is indicated by triangles. Note that the higher $SO$ of Tree Parallelization  |     |

|     | with virtual loss means lower performance                                                                                                                                                                                                                                                              | 113 |

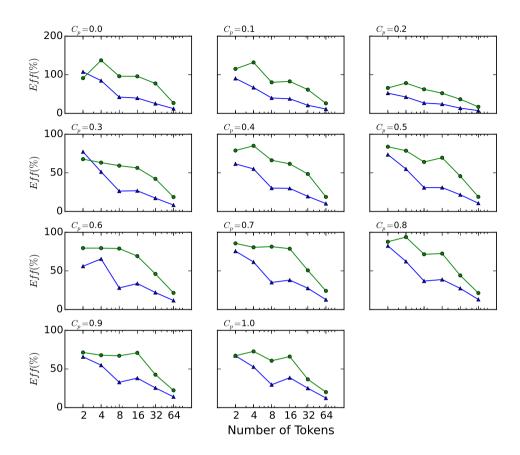

| 8.2 | Efficiency ( <i>Eff</i> ) for Horner (average of 20 instances for each data point). Tree parallelization is the green line which is indicated by circles and Tree Parallelization with virtual loss is the blue line which is indicated by triangles. Note that Tree Parallelization with virtual loss |     |

|     | has a lower efficiency meaning lower performance                                                                                                                                                                                                                                                       | 114 |

|     | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                |     |

# List of Tables

| 3.1        | Thread affinity policies                                                   | 29  |

|------------|----------------------------------------------------------------------------|-----|

| 3.2        | Performance of FUEGO on the Xeon CPU. Each column shows data for           |     |

|            | $N$ threads. The board size is $9 \times 9$                                | 36  |

| 3.3        | Performance of FUEGO on the Xeon Phi. Each column shows data for           |     |

|            | $N$ threads. The board size is $9 \times 9$                                | 37  |

| 4.1        | The conceptual effect of grain size                                        | 56  |

|            | Sequential baseline for GSCPM algorithm. Time in seconds                   |     |

|            | bequestian basesine for GBGI in angorithmic in seconds.                    | 0,  |

| 5.1        | Sequential execution time in seconds                                       | 81  |

| <i>6</i> 1 | Cognential time in second when C 0.5                                       | 0.4 |

|            | Sequential time in seconds when $C_p = 0.5$                                |     |

|            | Definition of layouts for 3PMCTS                                           |     |

| 6.3        | Details of experiment to show the flexibility of 3PMCTS                    | 96  |

| 71         | Different massible configurations for Encemble LICE Encemble size is       | 101 |

| 7.1        | Different possible configurations for Ensemble UCT. Ensemble size is $n$ . |     |

| 7.2        | The performance of Ensemble UCT vs. plain UCT based on win rate            | 103 |

# List of Listings

| A.1 | Micro-benchmark code for measuring performance of Xeon Phi       | 133 |

|-----|------------------------------------------------------------------|-----|

| A.2 | Micro-benchmark code for measuring memory bandwidth of Xeon Phi. | 134 |

| C.1 | Task parallelism for GSCPM using TBB (task_group)                | 137 |

| C.2 | Task parallelism for GSCPM using Cilk Plus (cilk_spawn)          | 138 |

| C.3 | Task parallelism for GSCPM using Cilk Plus (cilk_for)            | 138 |

| C.4 | Task parallelism for GSCPM, based on TPFIFO                      | 138 |

| D.1 | An implementation of the 3PMCTS algorithm in TBB                 | 141 |

## List of Abbreviations

**3PMCTS** Pipeline Pattern for Parallel MCTS.

FIFO First In, First Out.FMA Fused Multiply Add.

**GFLOPS** Giga Floating Point Operations per Second.

**GIPS** Giga Integers per Second.

**GSCPM** Grain Size Controlled Parallel MCTS.

**HEP** High Energy Physics.

**HEPGAME** High Energy Physics Game.

ILD Iteration-Level Dependency.

ILP Iteration-Level Parallelism.

**ILT** Iteration-Level Task.

**ISA** Instruction Set Architecture.

MC Memory Controller.MCTS Monte Carlo Tree Search.MIC Many Integrated Core.

**NUMA** Non Uniform Memory Access.

OLD Operation-Level Dependency.

OLP Operation-Level Parallelism.

**OLT** Operation-Level Task.

PPS Playouts per Second.

PS Problem Statement.

PW Percentage of Wins.

**RNG** Random Number Generation.

**RQ** Research Question.

**SMT** Simultaneous Multithreading.

**TBB** Threading Building Blocks.

**TD** Tag Directories.

**TPFIFO** Thread Pool with FIFO scheduling.

**UCB** Upper Confidence Bound.

**UCT** Upper Confidence Bounds for Trees.

**UMA** Uniform Memory Access.

**VPUs** Vector Processing Units.

## Introduction

In the last decade, there has been much interest in the Monte Carlo Tree Search (MCTS) algorithm. It started by the publication "Bandit Based Monte-Carlo Planning", when Kocsis and Szepesvári proposed a new, adaptive, randomized optimization algorithm [KS06]. In the same year, it was followed by Rémi Coulom in presenting "Efficient selectivity and backup operators in Monte-Carlo tree search" in Turin [Cou06]. After that, the time has arrived to collect the ideas in a framework for MCTS by Chaslot et al. [CWvdH+08b]. In fields as diverse as Artificial Intelligence, Combinatorial Optimization, and High Energy Physics (HEP), research has established that MCTS can find approximate answers without domain-dependent heuristics [KS06, KPVvdH13, Ver13]. The strength of the MCTS algorithm is that it provides answers for any given computational budget [GBC16]. The amount of error can typically be reduced by expanding the computational budget for more running time. Much effort has been put into the development of parallel algorithms for MCTS to reduce the running time. The efforts have as their target a broad spectrum of parallel systems, ranging from small shared-memory multi-core machines to large distributed-memory clusters. The emergence of the Xeon Phi co-processor with over 61 simple cores has extended this spectrum with shared-memory many-core processors. In this thesis, we will study the parallel MCTS algorithms for multi-core and many-core processors.

This chapter is structured as follows. Section 1.1 introduces the HEPGAME project. Section 1.2 explains briefly the MCTS algorithm. Section 1.3 discusses parallelism and parallelization. Section 1.4 explains the general obstacles to the parallelization of MCTS. Section 1.5 discusses performance and scalability. The scope and research goals are mentioned in Section 1.6. The problem statement and five research questions are given in Section 1.7. Section 1.8 discusses the research methodology. Section 1.9 gives the structure of the thesis. Section 1.10 provides a list of contributions.

2 1.1. HEPGAME

#### 1.1 HEPGAME

The work in the thesis is part of High Energy Physics Game (HEPGAME) project [Ver13]. The HEPGAME project intends to use techniques from game playing for solving large equations in particle physics (High Energy Physics (HEP)) calculations. One of these techniques is MCTS. Before the beginning of the project, it was clear that without parallelization any algorithm based on MCTS cannot be useful. The main prerequisite for the parallelization was that the algorithm should be executed in a reasonable time when trying to simplify large equations. Therefore, our focus in this research was on finding new methods to parallelize the MCTS algorithm. The multithreaded version of the FORM program (i.e., TFORM) [TV10] can use our findings. FORM is open source software used for solving large High Energy Physics (HEP) equations. FORM has an optimization module which receives the main conclusions of our research.

#### 1.2 Monte Carlo Tree Search

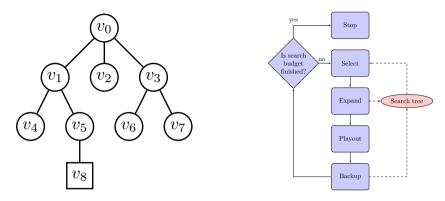

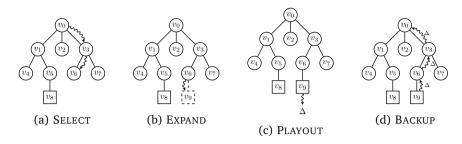

The MCTS algorithm iteratively repeats four steps to construct a search tree until a predefined computational budget (i.e., time or iteration constraint) is reached [Cou06, CWvdH+08b]. Figure 1.2 shows the main loop of the MCTS algorithm and Figure 1.1 shows an example of the search tree. At the beginning the search tree has only a root node. Each node in the search tree is a state of the domain, and directed edges to child nodes represent actions leading to the following states. Figure 1.3 illustrates one iteration of the MCTS algorithm on a search tree that already has nine nodes. Circles represent the non-terminal and internal nodes. Squares show the terminal nodes. The four steps are:

- 1. Select: A path of nodes inside the search tree is selected from the root node until a non-terminal leaf with unvisited children is reached ( $v_6$ ). Each of the nodes inside the path is selected based on a predefined *selection policy*. This policy controls the balance between exploitation and exploration of searching inside the domain [KS06] (see Figure 1.3a).

- 2. EXPAND: One of the children  $(v_9)$  of the selected non-terminal leaf  $(v_6)$  is generated randomly and added to the tree and also the selected path (see Figure 1.3b).

- 3. PLAYOUT: From the given state of the newly added node, a sequence of randomly simulated actions is performed until a terminal state in the domain is

Figure 1.1: An example of the search tree. Figure 1.2: The main loop of MCTS.

reached, i.e., RANDOMSIMULATION. The terminal state is evaluated using a utility function to produce a reward value  $\Delta$ , i.e., EVALUATION (see Figure 1.3c).

4. Backup: In the selected path, each node's visit count n is incremented by 1 and its reward value w updated according to  $\Delta$  [BPW+12]. These values are required by the selection policy (see Figure 1.3d).

As soon as the computational budget is exhausted, the best child of the root node is returned (e.g., the one with the highest number of visits).

### 1.3 Parallelism and Parallelization

In this thesis, we aim at parallelism, and we use parallelization as the act towards parallelism. Doing more than one thing at the same time introduces *parallelism*. A programmer has to find opportunities for *parallelization* in an algorithm and use parallel programming methods to write a parallel program. A parallel program uses the parallel processing power of processors for faster execution.

**Definition 1.1 (Parallelization)** Parallelization is the act of transforming code to enable simultaneous activities. The parallelization of a program allows execution of (at least parts of) the program in parallel.

Below we describe two types of parallelism: thread-level parallelization in Subsection 1.3.1 and task-level parallelization in Subsection 1.3.2.

Figure 1.3: One iteration of MCTS.

#### 1.3.1 Thread-level Parallelization

The first choice for doing parallel programming is to use software threads, such as POSIX threads, usually referred to as *pthreads*. It enables a program to control multiple different flows of work that overlap in time. Each flow of work is seen as a thread; creation and control over threads are achieved by making calls to the API (e.g., pThreads). Here we remark that the use of software threads in parallel programming is considered as equivalent to writing in assembly language [JR13]. A multi-core processor consists of multiple cores that execute at least one independent software thread per core through duplication of hardware. A multithreaded or hyperthreaded processor core will multiplex a single core to execute multiple software threads through interleaving of software threads via hardware mechanisms. A computation that employs multiple software threads in parallel is called *thread parallel* [MRR12]. This type of parallelization is what we call *thread-level parallelization*.

**Definition 1.2 (Thread)** A thread is any software unit of parallel work with an independent flow of control.

**Definition 1.3 (Multi-core Processor)** A multi-core processor is a single chip that contains multiple core processing units, more commonly known as cores.

#### 1.3.2 Task-level Parallelization

To use task-level parallelization, a programmer should program in tasks, not threads [Lee06]. Threads are a mechanism for executing tasks in parallel, and tasks are units of work that merely provide the opportunity for parallel execution; tasks are not themselves a mechanism of parallel execution [MRR12]. For a proper definition, see below.

**Definition 1.4 (Task)** A task is a logical unit of potential parallelism with a separate flow of control.

Tasks are executed by scheduling them onto software threads, which in turn the operating system schedules onto hardware threads. Scheduling of software threads onto hardware threads is usually preemptive (i.e., it can happen at any time). In contrast, scheduling of tasks onto software threads is typically non-preemptive (i.e., a thread switches tasks only at predictable switch points). Non-preemptive scheduling enables significantly lower overhead and stronger reasoning about space and time requirements than preemptive scheduling [JR13]. A computation that employs tasks over threads is called *task parallel*. This type of parallelization is what we call *task-level parallelization*. It is the preferred method of parallelism, especially for many-core processors.

**Definition 1.5 (Many-core Processor)** A many-core processor is a specialized multi-core processor designed for a high degree of parallel processing, containing a large number of simpler, independent processor cores.

In the task-level parallelization, the programmer should expose parallelism and share the opportunities for parallelization as *tasks*, but the work to map tasks to threads should not be encoded into an application. Hence, do not mix the concept of exposing tasks with the effort to allocate tasks to threads. The later causes inflexibility in scaling on different and future hardware. Hence, we are creating tasks and give the job of mapping tasks onto hardware to a parallel programming library, such as Threading Building Blocks (TBB) [Rei07] and Cilk Plus [Suk15].

The task-level parallelization is also tightly coupled with *parallel patterns*. A pattern is a recurring combination of data and task management, separate from any particular algorithm [MRR12]. The parallel patterns are not necessarily tied to any particular hardware architecture or programming language or system. Parallel patterns are essential for efficient computations of tasks.

**Definition 1.6 (Parallel Pattern)** A parallel pattern is a recurring combination of task distribution and data access that solves a specific problem in parallel algorithm design [MRR12].

Parallel patterns are often composed with, or generalized from, a set of serial patterns. The serial patterns are the foundation of *structured programming*. The pattern-based approach to parallel programming can be considered an extension of the idea of structured programming [MRR12].

#### 1.4 General Obstacles for Parallelization of MCTS

Since its inception, MCTS was the subject of parallelization, and several parallelization methods have been developed for it [CWvdH08a, CJ08, EM10, SKW10, SHM+16].

This trend comes from the fact that MCTS usually needs a large number of iterations to converge, and every iteration can be executed in parallel. Therefore, MCTS has sufficient potential for parallelization in theory, and it even seems to be straightforward. However, a closer look reveals that there are four obstacles to achieve parallelism: (1) irregular parallelism, (2) shared data structure, (3) data dependencies, and (4) complex interactions among obstacles. If we are not able to overcome these obstacles, the consequence will be four types of overhead, respectively: (1) load balancing overhead, (2) synchronization overhead, (3) search overhead, and (4) deployment overhead. In the following, we will explain these obstacles and what type of overhead they cause. Each of the subsections below introduces the necessary techniques for dealing with these obstacles.

#### 1.4.1 Irregular Parallelism Causes Load Balancing Overhead

The first obstacle is irregular parallelism. Parallel algorithms with irregular parallelism suffer from a lack of load balancing over processing cores. MCTS constructs asymmetric search trees because the selection policy in MCTS allows the algorithm to favor more promising nodes (exploitation), leading to a tree with unbalanced branches over time [BPW+12]. Parallel execution of the algorithm with such a search tree results in *irregular parallelism* because one thread traverses a shorter branch while the other one works on a longer one. Chapter 4 provides more details and tries to handle this obstacle.

**Definition 1.7 (Irregular Parallelism)** In irregular parallelism, the units of possible parallel work in this type of parallelism are dissimilar in a way that creates unpredictable dependencies.

**Definition 1.8 (Load Balancing)** Load balancing is a method used to allocate workloads uniformly across multiple computing resources, such as computing cores, to improve the distribution of workloads.

#### 1.4.2 Shared Data Structure Causes Synchronization Overhead

The second obstacle for parallelizing MCTS is a shared search tree. A parallel algorithm with a shared data structure suffers from *synchronization overhead* when it utilizes locks for data protection. Locks are notoriously bad for parallel performance because other threads have to wait until the lock is released. Moreover, locks are often a bottleneck when many threads try to acquire the same lock. The MCTS algorithm uses a tree data structure for storing the states of the domain and guiding the search process. The basic premise of a search tree in MCTS is relatively simple: (A) nodes are

added to the tree in the order in which they were expanded. (B) nodes are updated in the tree along with the order in which they were selected. In parallel MCTS, parallel threads are manipulating a shared search tree concurrently, and locks are required for data protection. It seems that we should have synchronization without using locks to avoid synchronization overhead. In Chapter 5, we show how we deal with this obstacle.

**Definition 1.9 (Shared Data Structure)** A shared data structure, also known as a concurrent data structure, is a particular way of storing and organizing data that can be accessed by multiple threads simultaneously on a shared-memory machine.

**Definition 1.10 (Synchronization)** *Synchronization is the coordination of tasks or threads to obtain the desired runtime order [Wil12].*

#### 1.4.3 Ignoring Data Dependencies Causes Search Overhead

The third obstacle that should be addressed is the data dependencies. We find two types of data dependencies in MCTS: (1) the data dependency that exists among iterations and (2) the data dependency that exists among operations. The first type of data dependency exists because each of the iterations in the main loop of the algorithm requires the updated data which should be provided by its previous iterations. This type of data dependency is also known as *loop carried data dependencies*. Ignoring this type of data dependency causes *search overhead*. The second type of data dependency exists because each of the four operations inside each iteration of the algorithm depends on the data that is provided by the previous operation. Ignoring this type of data dependency is not possible for obvious reasons. Chapter 6 provides more details and our solution for overcoming this obstacle.

**Definition 1.11 (Loop Carried Data Dependency)** A loop carried data dependency exists when a statement in one iteration of a loop depends in some way on a statement in a different iteration of the same loop.

**Definition 1.12 (Loop Independent Data Dependency)** A loop independent data dependency exists when a statement in one iteration of a loop depends only on a statement in the same iteration of the loop.

**Definition 1.13 (Search Overhead)** Search overhead exists in the MCTS algorithm when the number of nodes searched by a parallel algorithm is more than that of the serial algorithm.

#### 1.4.4 Complex Interactions Leading to Deployment Overhead

The fourth obstacle is the complexity of addressing the three above mentioned obstacles together. Trying to address all of them at once is difficult, due to the interactions among them. The overhead caused by complex interactions is called *deployment overhead*. The level of complexity forced the researchers to make compromises when solving some of these obstacles to have a parallel implementation of MCTS. In this research, we aim to mitigate the deployment overhead through structured parallel programming.

**Definition 1.14 (Complex Interactions)** *Complex interactions refer to the relationships among the general obstacles for parallelization of MCTS.*

**Definition 1.15 (Deployment Overhead)** Deployment overhead is the amount of time spent to deploy an algorithm in a hardware environment.

## 1.5 Performance and Scalability Studies

MCTS works by selectively building a tree, expanding only branches it deems worth-while to explore [Cou06, AHH10, vdHPKV13]. The algorithm can converge to an optimal solution using a large number of playouts. It means that the algorithm requires more computation and memory to converge as the number of playouts increases. It leads to two distinct goals. The first and ultimate goal of parallelization is improving the *performance* of the parallelized application. The performance could be measured differently depending on the context in which it is used. In the context of MCTS, we measure performance by two different terms: (A) in terms of runtime (i.e., playout speedup), and (B) in terms of search quality (i.e., playing strength).

**Definition 1.16 (Performance Study)** A performance study for the parallel MCTS algorithm on shared-memory systems examines where the performance of the parallelization of MCTS is guided by a certain number of cores and a certain amount of memory for one specific performance metric such as the number of Playouts per Second (PPS) or the Percentage of Wins (PW).

**Definition 1.17 (Playout Speedup)** Playout speedup is the improvement in the speed of execution.

**Definition 1.18 (Playing Strength)** Playing strength is the achieved performance compared to a standard rating.

Adding more computing power and memory makes the process faster only if a scalable parallelization of the algorithm exists to harness the additional resources. Therefore, the second goal of parallelization is *scalability*. It will let the MCTS algorithm converge faster to a solution. By scalability, we mean that when we increase the number of cores and memory bandwidth, it results in improved performance in a manner proportional to the resources added. Being scalable is the main idea behind many parallelization methods for the MCTS algorithm on shared-memory machines [CWvdH08a, EM10, SKW10, SHM+16].

**Definition 1.19 (Scalability Study)** A scalability study for parallel MCTS on shared-memory systems refers to how the performance of parallelization of MCTS changes given the increase of the number of cores and the amount of memory.

**Definition 1.20 (Memory Bandwidth)** Memory bandwidth is the rate at which data can be read from or stored into memory by a processor. Memory bandwidth is usually expressed in units of bytes per second.

## 1.6 Scope and Research Goals

Our research handles and investigates parallel systems. To understand later design and implementation decisions as well as evaluation results, it is necessary to explain the scope in which the research is conducted.

Concerning the scope, we see that two major types of parallel architectures are prevailing in the industry: (A) shared-memory architecture and (B) distributed-memory architecture. Among these two principal types, the shared-memory architecture is of our main concern. Therefore, we concentrate on developing algorithms and finding solutions for shared-memory machines only. In passing, we remark that studies with a focus on distributed-memory systems [SP14, YKK+11] may benefit from our examinations, since our findings might be indirectly useful for the distributed-memory community of research. The explanation is that shared-memory machines are building blocks for distributed-memory systems.

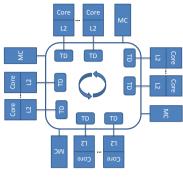

The shared-memory architecture also has two types: (A1) Uniform Memory Access (UMA) and (A2) Non Uniform Memory Access (NUMA). We are interested in both of these architectures. In the UMA shared-memory architecture, each processor must use the same shared bus to access memory. Here we note that the access time remains the same despite which shared-memory module contains the data to be retrieved. The Phi co-processor has an UMA-based many-core architecture called Many Integrated Core (MIC). In the NUMA architecture, each processor has direct access to its local memory module. At the same time, it can also access any remote memory module

belonging to another processor using a shared interconnect network. The outcome of having many memory modules is that memory access time varies with the location of the data to be accessed. Each processor in a NUMA machine is multi-core. In the thesis, our goal is to work with both NUMA-based multi-core systems and UMA-based many-core systems for both the design and the implementation of the algorithms.

**Definition 1.21 (Uniform Memory Access)** A Uniform Memory Access refers to a memory system in which the memory access time is uniform across all processors.

**Definition 1.22 (Many Integrated Core)** A Many Integrated Core is an UMA-based many-core architecture designed for highly parallel workloads. The architecture emphasizes higher core counts on a single die, and simpler cores, than on a traditional CPU.

**Definition 1.23 (Non Uniform Memory Access)** A Non Uniform Memory Access is a system in which certain banks of memory take longer to access than others, even though all the memory uses a single address space.

# 1.7 Problem Statement and Research Questions

The MCTS algorithm is a good candidate for parallelization. This has been known since the introduction of the algorithm in 2006 [Cou06, KS06, EM10]. However, until now, the research community has only used thread-level parallelization when parallelizing the algorithm. The current parallel programming approaches are unstructured and do not use modern parallel programming patterns, languages, and libraries. We aim to address the complications of designing parallel algorithms for MCTS using the modern techniques, tools, and machines which are discussed above. We focus on both NUMA and MIC architectures to evaluate our implementations. Therefore, the Problem Statement (PS) of the thesis is as follows.

PS: How do we design a structured pattern-based parallel programming approach for efficient parallelism of MCTS for both multi-core and many-core shared-memory machines?

We define five specific research questions (RQs) derived from the *PS* that we try to answer in the following chapters. We will describe the five research questions below.

**Thread-level parallelization:** Until now, the research community has only used thread-level parallelization when parallelizing MCTS. However, today, the NUMA-based multi-core and UMA-based many-core architectures are very important. These are the architectures that we will use in our experiments. We believe that thread-level parallelization is not anymore a suitable method for the many-core processors.

Therefore, it is important to know the performance of the thread-level parallelization on the new architectures. It leads us to the first research question.

• RQ1: What is the performance and scalability of thread-level parallelization for MCTS on both multi-core and many-core shared-memory machines?

**Task-level parallelization:** One of the essential developments in parallel programming methods is the use of task-level parallelization. In task-level parallelization, calculations are partitioned into tasks, rather than spread over software threads. The use of task-level parallelization has three benefits: (1) it is conceptually simpler, (2) it may make the development of parallel MCTS programs easier, and (3) it leads to more efficient scheduling of CPU time. These benefits lead us to the second research question.

• **RQ2**: What is the performance and scalability of task-level parallelization for MCTS on both multi-core and many-core shared-memory machines?

A lock-free data structure: MCTS requires a tree data structure. For efficient parallelism, this tree data structure must be lock-free. The existing lock-free tree data structure is inconsistent; i.e., it suffers from loss of information during the search phase. We are interested in developing a lock-free tree data structure for use in parallelized MCTS, in such a way that it avoids loss of information and simultaneously improves the speed of MCTS execution. This leads us to the third research question.

RQ3: How can we design a correct lock-free tree data structure for parallelizing MCTS?

Patterns for task-level parallelization: Task-level parallelization requires specific patterns by which the tasks are processed. Modern parallel libraries and languages support these patterns, thereby allowing quick construction of parallel programs that have these patterns. It may be possible to apply one or more patterns in the parallelization of MCTS. We are interested in (1) finding these patterns, and (2) using them in the parallelization of MCTS. This leads us to the fourth research question.

• **RQ4**: What are the possible patterns for task-level parallelization in MCTS, and how do we use them?

**Improving search quality of MCTS:** It has been shown that the parallelization of MCTS leads to a decrease in the quality of search results. Various solutions have been developed that attempt to mitigate this decrease in quality. We are interested in

finding out to what extent the existing solutions apply to the parallelized MCTS that we will develop in this thesis. This leads us to the fifth research question.

• **RQ5**: To what extent do the existing solutions which improve search quality, apply to our version of parallelized MCTS?

By the existing solutions, we mean two methods: (1) ensemble methods, and (2) virtual loss

# 1.8 Research Methodology

For answering a research question, our research methodology consists of four phases:

- The first phase is characterized by collecting knowledge on existing methods and algorithms. It is performed by reading to some extent, the existing literature and becoming familiar with the existing tools.

- The second phase is investigating the performance of the existing methods, tools, and techniques for parallelizing MCTS.

- The third phase is designing new ideas and algorithms. Then, the implementation of these designs takes place in a new software framework.

- In the fourth phase, an experiment is executed, and the results are collected, interpreted, analyzed, and reported.

# 1.9 Structure of the thesis

The problem statement and the five research questions introduced in Section 1.7 are addressed in eight chapters. Below we provide a brief description of the contents of each chapter.

**Chapter 1** introduces the Monte Carlo Tree Search algorithm and defines the concepts of parallelism and parallelization. Then, it gives four general obstacles for parallelization of MCTS: load balancing, synchronization overhead, search overhead, and deployment overhead. After that, the chapter gives the definitions for performance and scalability and provides the scope of research. Then, it formulates the problem statement, five research questions, and the research methodology. Finally, it lists our contributions.

**Chapter 2** provides the necessary background for the rest of the thesis. It discusses the benchmark problems, the parallelization methods for MCTS, the performance metrics, and our Upper Confidence Bounds for Trees (UCT) parallelization software package.

**Chapter 3** answers *RQ1*. The chapter provides, to the best of our knowledge, the first performance and scalability study of non-trivial MCTS programs on the Intel Xeon Phi.

**Chapter 4** answers *RQ2*. The chapter investigates how to parallelize irregular and unbalanced tasks in MCTS efficiently on the Xeon Phi.

**Chapter 5** answers *RQ3*. The chapter proposes a new lock-free tree data structure for parallel MCTS.

**Chapter 6** answers *RQ4*. The chapter proposes a new algorithm based on a *Pipeline Pattern* for Parallel MCTS.

**Chapter 7** answers the first part of *RQ5*. The chapter shows that balancing between the exploitation-exploration parameter and the tree size can be useful in Ensemble UCT to improve its performance.

**Chapter 8** answers the second part of *RQ5*. The chapter evaluates the benefit of using the virtual loss in lock-free (instead of locked-based) Tree Parallelization. Hence, it addresses the trade-off between search overhead and efficiency.

**Chapter 9** concludes the thesis with a summary of the answers to what has been achieved with regards to the research questions and the problem statement, formulates conclusions, describes limitations and shows possible directions for future work.

# 1.10 Contributions

Below we list six contributions of our research. There are three main contributions (1 to 3) and three technical contributions (4 to 6).

- 1. The use of many-core machines for studying the performance and scalability of MCTS (see Chapter 2 and 3).

- 2. The use of task-level parallelization for MCTS (see Chapter 4).

14 1.10. Contributions

- 3. The design of a lock-free data structure for parallel MCTS (see Chapter 5)

- 4. The introduction of a pipeline pattern for parallel MCTS (see Chapter 6).

- 5. We established a balance for the trade-off between exploitation-exploration for Root Parallelization (see Chapter 7).

- 6. By using lock-free parallelization, a virtual loss does not bring any improvement in search quality for a Horner Scheme (see Chapter 8).

# Background

The MCTS algorithm iteratively repeats four steps or operations to construct a search tree until a predefined computational budget (i.e., time or iteration constraint) is reached [CWvdH+08b]. Algorithm 2.1 shows the general MCTS algorithm (see Section 1.2 and Algorithm 2.2).

### **Algorithm 2.1:** The general MCTS algorithm.

```

1 Function MCTS(s_0)

2 v_0 := create root node with state s_0;

3 while within search budget do

4 \langle v_l, s_l \rangle := SELECT(v_0, s_0);

5 \langle v_l, s_l \rangle := EXPAND(v_l, s_l);

6 \Delta := PLAYOUT(v_l, s_l);

7 BACKUP(v_l, \Delta);

```

The purpose of MCTS is to approximate the domain-dependent theoretic value of the actions that may be selected from the current state by iteratively creating a partial search tree [BPW+12]. How the search tree is built depends on how nodes in the tree are selected (i.e., tree selection policy). For instance, nodes in the tree are selected according to the estimated probability that they are better than the current best action. It is essential to reduce the estimation error of the nodes' values as quickly as possible. The current chapter provides a more detailed overview of MCTS. Section 2.1 describes the UCB selection policy. In Section 2.2, we provide the UCT formula and the UCT algorithm. Section 2.3 discusses the parallelization methods for MCTS. Section 2.4 presents the benchmarks for experimental studies. Section 2.5 explains the performance metrics. Finally, Section 2.6 briefly describes our software tool.

# 2.1 Upper Confidence Bound (UCB)

The tree selection policy in the MCTS algorithm is based on two fundamentally different concepts, viz. exploitation and exploration. Hence, the selection is a search process and the aim of the search is to reduce the error as soon as possible [KS06].

**Definition 2.1 (Exploitation)** Exploitation looks in areas which appear to be promising  $[BPW^+12]$ .

**Definition 2.2 (Exploration)** Exploration looks in areas that so far have not been sampled well [BPW<sup>+</sup>12].

Kocsis and Szepesvári [KS06] aimed to design a Monte Carlo search algorithm that had a small error probability if stopped prematurely and that converged to the domain-dependent theoretic optimum given sufficient time [KS06]. They proposed the use of the simplest Upper Confidence Bound (UCB) policy (i.e., UCB1) as a tree selection policy for MCTS. UCB1 is an obvious choice for node selection given its application in multi-armed bandit problems for balancing between exploitation and exploration of actions. Bandit problems are a well-known class of sequential decision problems, in which one needs to choose among K actions (e.g., the K arms of a multi-armed bandit slot machine) to maximize the cumulative reward by consistently taking the optimal action [BPW $^+$ 12, ACBF02].

Auer et al. [ACBF02] proposed UCB1 for *bandit problems*. The UCB1 policy selects the arm *j* that maximizes:

$$UCB1(j) = \overline{X}_j + \sqrt{\frac{2\ln(n)}{n_j}}$$

(2.1)

where  $\overline{X}_j$  is the average reward from arm j;  $n_j$  is the number of times arm j was played, and n is the overall number of plays so far. The first term at the right-hand side  $\overline{X}_j$  encourages the exploitation of higher-reward arms, while the second term at the right-hand side  $\sqrt{\frac{2\ln(n)}{n_j}}$  promotes the exploration of less played arms.

# 2.2 Upper Confidence Bounds for Trees (UCT)

This section explains the most common algorithm in the MCTS family, the Upper Confidence Bounds for Trees (UCT) algorithm. The formulas are given in Subsection 2.2.1 and the algorithm in Subsection 2.2.2

### 2.2.1 UCT Formula

The UCT algorithm addresses the exploitation-exploration dilemma in the selection step of the MCTS algorithm using the UCB1 policy [KS06]. A child node j is selected to maximize:

$$UCT(j) = \overline{X}_j + 2C_p \sqrt{\frac{2\ln(N(v))}{N(v_j)}}$$

(2.2)

where  $\overline{X}_j = \frac{Q(v_j)}{N(v_j)}$  is an approximation of the node j domain-dependent theoretic value.  $Q(v_j)$  is the total reward of all playouts that passed through node j,  $N(v_j)$  is the number of times node j has been visited, N(v) is the number of times the parent of node j has been visited, and  $C_p \geq 0$  is a constant. The first term at the right-hand side is for exploitation and the second term is for exploration [KS06]. The decrease or increase in the amount of exploration can be adjusted by  $C_p$  in the exploration term.

# 2.2.2 UCT Algorithm

The UCT algorithm is given in Algorithm 2.2. Each node v stores four pieces of data: the action to be taken a(v), p(v) the current player at node v, the total simulation reward Q(v) (a real number), and the visit count N(v) (a non-negative integer). Each node v is also associated with a state s. The state s is recalculated as the Select and Expand steps descends the tree. The term  $\Delta \langle p(v) \rangle$  denotes the reward after simulation for each player.

# 2.3 Parallelization Methods for MCTS

In this section, two categories for parallelization of MCTS are presented. Traditionally, parallelization methods for MCTS are classified based on the parallelism technique. Currently, we believe that we should classify them into two categories solely based on the way that the search tree is used. We introduce parallel methods with a shared tree in Subsection 2.3.1 and with an ensemble of search trees in Subsection 2.3.2.

### 2.3.1 Parallel Methods with a Shared Data Structure

The first category is for the parallel methods with a shared search tree. The tree is shared among parallel threads or processes which means data is accessible globally. The methods that belong to this category can be implemented on both shared-memory and distributed-memory systems. In both environments, a synchronization method should create constraints threads from accessing the tree simultaneously. The most well-known method in this category is Tree Parallelization.

### Algorithm 2.2: The UCT algorithm.

```

1 Function UCTSEARCH(s<sub>0</sub>)

v_0 := create root node with state s_0;

2

while within search budget do

3

\langle v_l, s_l \rangle := SELECT(v_0, s_0);

4

\langle v_l, s_l \rangle := \text{EXPAND}(v_l, s_l);

5

\Delta := PLAYOUT(v_l, s_l);

6

BACKUP(v_l, \Delta);

return a(best \ child \ of \ v_0)

R

Function Select(Node v,State s): <Node,State>

10

while v is fully expanded do

\underset{v_j \in \textit{children of } v}{\arg\max} \ \frac{\frac{Q(v_j)}{N(v_j)} + 2C_p \sqrt{\frac{2 \ln(N(v))}{N(v_j)}};

11

s_l := p(v) takes action a(v_l) from state s;

12

v := v_l;

13

s := s_l;

14

return \langle v, s \rangle;

15

Function Expand(Node v.State s): <Node.State>

16

if s is non-terminal then

17

choose a \in \text{set of untried actions from state } s:

18

add a new child v' with a as its action to v;

19

s' := p(v) takes action a from state s;

20

return \langle v', s' \rangle;

21

Function PLAYOUT(Node v,State s)

while s is non-terminal do

23

choose a \in \text{set of untried actions from state } s uniformly at random;

24

s := p(v) takes action a from state s;

25

26

\Delta \langle p(v) \rangle := reward for state s for each player p;

27

Function BACKUP(Node v, \Delta): void

28

while v is not null do

29

N(v) := N(v) + 1;

30

31

Q(v) := Q(v) + \Delta \langle p(v) \rangle;

v := parent of v;

32

```

**Definition 2.3 (Tree Parallelization)** In Tree Parallelization, the tree is shared among parallel threads, tasks, or processes which means data is accessible globally.

### 2.3.2 Parallel Methods with More than one Data Structure

The second category is for the parallel methods where several search trees or an ensemble of search trees are used. Each parallel thread has its own search tree which means the information is local to that thread. The methods that belong to this category can also be implemented on both shared-memory and distributed-memory environments. The most well-known method in this category is Root Parallelization.

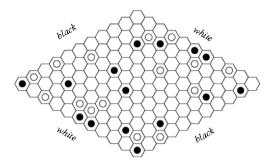

Figure 2.1: A sample board for the game of Hex

**Definition 2.4 (Root Parallelization)** *In Root Parallelization, each parallel thread, task, or process has its own search tree which means the information is local to that thread.*

### 2.4 Case Studies

In this section, we present two case studies for MCTS. In Subsection 2.4.1 we present the game of Hex, a strategy board game for two players. In Subsection 2.4.2 we describe the method for approximating the roots of a polynomial called Horner scheme.

### 2.4.1 Case 1: The Game of Hex

Hex is a board game with a diamond-shaped board of hexagonal cells [AHH10, HT19]. The game is usually played on a board of size 11 on a side, for a total of 121 hexagons, as illustrated in Figure 2.1 [Wei17]. Each player is represented by a color (Black or White). Players take turns placing a stone of their color on a cell on the board. The goal for each player is to create a connected chain of stones between the opposing sides of the board marked by their colors. The first player to complete this path wins the game. The game cannot end in a draw since no path can be completely blocked except by a complete path of the opposite color. Since the first player to move in Hex has a distinct advantage, the swap rule is generally implemented for fairness. This rule allows the second player to choose whether to switch positions with the first player after the first player has made a move.

#### **Evaluation Function**

In our implementation of Hex, a disjoint-set data structure is used to determine the connected stones. A disjoint-set data structure maintains a collection of disjoint (non-overlapping) subsets of a set of elements  $S = \{S_1, S_2, \dots, S_k\}$ . A union-find algorithm

performs two operations on such a data structure: First, the *Find* operation determines in which subset a particular element is located. This can be used for determining whether two elements are in the same subset. Second, the *Union* operation joins two subsets into a single subset. Each set is identified by a representative, which usually is a member in the set. Using this data structure and algorithm, the evaluation of the board position to find the player who won the game becomes very efficient [GI91].

### 2.4.2 Case 2: Horner Schemes

Horner's rule is an algorithm for polynomial computation that reduces the number of multiplications and results in a computationally efficient form [OS12]. For a polynomial in one variable

$$p(x) = a_n x^n + a_{n-1} x^{n-1} + \dots + a_0,$$

(2.3)

the rule simply factors out powers of x. Thus, the polynomial can be written in the form

$$p(x) = ((a_n x + a_{n-1})x + \dots)x + a_0.$$

(2.4)

This representation reduces the number of multiplications to n and has n additions. Therefore, the total evaluation cost of the polynomial is 2n. Here it is assumed that the cost of addition and multiplication are equal.

Horner's rule can be generalized for multivariate polynomials. Here, Eq. 2.4 applies to a polynomial for each variable, treating the other variables as constants. The order of choosing variables may be different, each order of the variables is called a *Horner scheme*.

The number of operations can be reduced even more by performing common subexpression elimination (CSE) after transforming a polynomial with Horner's rule [ALSU07]. CSE creates new symbols for each subexpression that appears twice or more and replaces them inside the polynomial. Then, the subexpression has to be computed only once.

# 2.5 Performance Metrics

In our experiments, the performance is reported by two metrics: (A) playout speedup (Subsection 2.5.1) and (B) playing strength (Subsection 2.5.2). Below, we define both metrics.

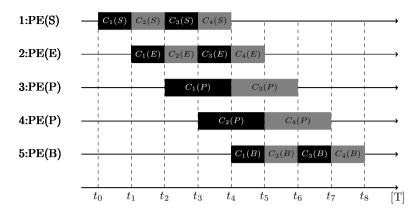

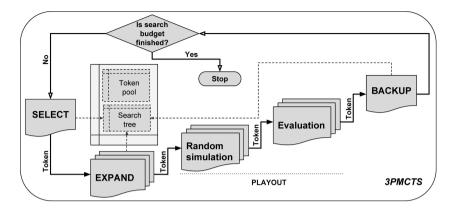

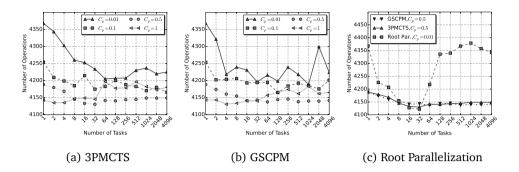

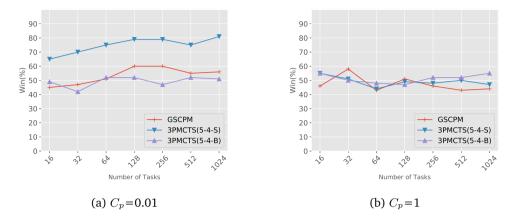

### 2.5.1 Playout Speedup