# TOWARDS AUTOMATED SECURITY VALIDATION FOR HARDWARE DESIGNS

# Rui Zhang

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2020

Approved by:

Cynthia Sturton

Leonard McMillan

Fabian Monrose

Michael Reiter

**Daniel Sorin**

©2020 Rui Zhang ALL RIGHTS RESERVED

#### **ABSTRACT**

Rui Zhang: Towards Automated Security Validation for Hardware Designs (Under the direction of Cynthia Sturton)

Hardware provides the foundation of trust for computer systems. Defects in hardware designs routinely cause vulnerabilities that are exploitable by malicious software and compromise the security of the entire system. While mature hardware validation tools exist, they were primarily designed for checking functional correctness. How to systematically detect security-critical defects remains an open and challenging question.

In this dissertation, I develop formal methods and practical tools for automated hardware security validation. To identify and develop security-critical properties for hardware design, I developed SCIFinder, a methodology that leverages known vulnerabilities to mine and learn security invariants. I show that security vulnerabilities together with machine learning techniques can give us a set of security properties to detect both known and unknown security bugs in the OR1200 processor. I also proposed another method to develop security-critical properties by leveraging existing ones, and I built a tool, Transys, to translate security properties across similar or different versions of hardware designs. I demonstrate that translating security properties across AES hardware, RSA hardware and RISC processors is feasible and light-weight. Given the security properties, I developed Coppelia to validate the security of hardware designs. I proposed a hardware-oriented backward symbolic execution strategy to find violations and generate exploit programs. I successfully generate exploits for known security bugs on the OR1200 processor, and discovered and generated exploit programs for 4 unknown bugs across two different processors and architectures.

To my parents, and my husband.

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor Professor Cynthia Sturton. Professor Sturton kindly accepted me as her student, guided and supported me throughout my PhD study. I really appreciate her extreme patience with me during my PhD. She always patiently listens to my dumb and premature ideas, and often gives constructive and insightful feedback to me. She patiently helps me practicing my presentations numerous times, and encourages me before each of my presentation.

I would like to express my gratitude to all my committee members: Professor Leonard McMillan, Professor Fabian Monrose, Professor Michael Reiter, and Professor Daniel Sorin. I am grateful for the time and wisdom they devoted, and the helpful discussions and feedbacks they provided. I am super lucky to have all of them to be my committee members. I would like to thank Professor Sorin for his supports and help, especially during my hard time.

I am thankful to my research collaborators and co-authors: Natalie Stanly, Andrew Chi, Chris Griggs, and Calvin Deutschbein, for their contributions, tremendous help and insightful comments. I would also like to thank to my colleagues and friends in all UNC security groups: Michael Brown, Alyssa Byrnes, Abhishek Singh, Qiuyu Xiao, Ziqiao Zhou, Sheng Liu, Marie Nesfield, for their friendship, inspiration and all the generous help. I am also grateful to all the people I met during these years at UNC, other institutions, and the conferences, as well as the anonymous reviewers, all of whom made my PhD life colorful.

Lastly, I would like to thank my family. I appreciate all the love, supports and encouragements from my husband, Peng. He encourages me to think bigger, and motivates me to fight harder during the dark times. Although we had a long-distance relationship, he made me feel that he was always around me. I also would like to thank my parents for their unconditional love, understanding, and supports. They are always proud of me no matter what I achieve. I cannot express how grateful I am to them.

# TABLE OF CONTENTS

| LI | ST OI | TABL    | ES                                              | X   |

|----|-------|---------|-------------------------------------------------|-----|

| LI | ST OI | F FIGUI | RES                                             | xii |

| LI | ST OI | F ABBR  | EVIATIONS                                       | xiv |

| 1  | INT   | RODUC   | TION                                            | 1   |

|    | 1.1   | Thesis  | Statement                                       | 2   |

|    | 1.2   | Develo  | oping Hardware Security Properties              | 2   |

|    | 1.3   | Transla | ating Hardware Security Properties              | 4   |

|    | 1.4   | Genera  | ating Hardware Exploit Programs                 | 5   |

|    | 1.5   | Organi  | zation                                          | 6   |

| 2  | BAC   | KGRO    | UND AND RELATED WORK                            | 7   |

|    | 2.1   | Appro   | aches for Protecting Vulnerable Hardware        | 7   |

|    |       | 2.1.1   | Secure Processors                               | 7   |

|    |       | 2.1.2   | Information Flow Security                       | 9   |

|    |       | 2.1.3   | Property Driven Hardware Security Validation    | 9   |

|    |       | 2.1.4   | Language Based Approaches                       | 10  |

|    | 2.2   | Develo  | pping Security Specifications                   | 11  |

|    |       | 2.2.1   | Extracting assertions from hardware designs     | 11  |

|    |       | 2.2.2   | Data Mining for Security Properties of Software | 11  |

|    | 2.3   | Symbo   | olic Execution                                  | 12  |

|    |       | 2.3.1   | Symbolic Execution Technique                    | 12  |

|    |       | 2.3.2   | Automatic Exploit Generation                    | 13  |

|   |     | 2.3.3   | Hardware Symbolic Simulation                      | 13 |

|---|-----|---------|---------------------------------------------------|----|

| 3 | DEV | ELOPI   | NG HARDWARE SECURITY PROPERTIES                   | 14 |

|   | 3.1 | Overvi  | ew                                                | 14 |

|   | 3.2 | Design  | L                                                 | 15 |

|   |     | 3.2.1   | Invariant Generation                              | 16 |

|   |     | 3.2.2   | Optimization                                      | 20 |

|   |     | 3.2.3   | Security-Critical Invariant Identification        | 21 |

|   |     | 3.2.4   | Security-Critical Invariant Inference             | 22 |

|   |     | 3.2.5   | False Positives                                   | 24 |

|   | 3.3 | Implen  | nentation                                         | 24 |

|   |     | 3.3.1   | Security-Critical Errata                          | 24 |

|   |     | 3.3.2   | Assertions                                        | 26 |

|   | 3.4 | Evalua  | tion                                              | 27 |

|   |     | 3.4.1   | Invariant Generation                              | 27 |

|   |     | 3.4.2   | SCI Identification                                | 28 |

|   |     | 3.4.3   | SCI Inference                                     | 30 |

|   |     | 3.4.4   | Representing Manually Written Security Properties | 33 |

|   |     | 3.4.5   | Classification of Security Properties             | 34 |

|   |     | 3.4.6   | Detecting Unknown Bugs                            | 35 |

|   |     | 3.4.7   | Performance                                       | 35 |

|   | 3.5 | Summa   | ary                                               | 36 |

| 4 | TRA | NSLAT   | TING HARDWARE SECURITY PROPERTIES                 | 37 |

|   | 4.1 | Motiva  | ation and Threat Model                            | 37 |

|   |     | 4.1.1   | Threat Model                                      | 39 |

|   | 4.2 | Securit | ty Properties                                     | 40 |

|   |     | 4.2.1   | Restricted Temporal Logic                         | 40 |

|   |     | 4.2.2   | Information Flows                                 | 41 |

|     | 4.2.3  | Hardware Security Properties             | 41 |

|-----|--------|------------------------------------------|----|

| 4.3 | Proble | m Statement                              | 43 |

| 4.4 | Design | 1                                        | 43 |

|     | 4.4.1  | Overview                                 | 44 |

|     | 4.4.2  | Variable Mapping Pass                    | 46 |

|     | 4.4.3  | Structural Transformation Pass           | 48 |

|     | 4.4.4  | Constraint Refinement Pass               | 51 |

|     | 4.4.5  | Property Does not Exist                  | 54 |

|     | 4.4.6  | Bugs in the Code                         | 54 |

| 4.5 | Impler | nentation                                | 55 |

| 4.6 | Evalua | tion                                     | 55 |

|     | 4.6.1  | Experiment Setup and Dataset             | 56 |

|     | 4.6.2  | Translation Results                      | 56 |

|     | 4.6.3  | Quality                                  | 59 |

|     | 4.6.4  | Case Studies                             | 61 |

|     | 4.6.5  | Performance                              | 65 |

|     | 4.6.6  | Effectiveness of Each Pass               | 66 |

|     | 4.6.7  | Security Impact                          | 66 |

|     | 4.6.8  | Bugs in the Code                         | 67 |

| 4.7 | Summ   | ary                                      | 69 |

| GEN | NERATI | NG HARDWARE EXPLOIT PROGRAMS             | 70 |

| 5.1 | Overvi | ew and Challenges                        | 70 |

|     | 5.1.1  | Challenges                               | 70 |

| 5.2 | Design | 1                                        | 71 |

|     | 5.2.1  | Overview of Coppelia                     | 71 |

|     | 5.2.2  | Preprocessing: Transcompiling RTL to C++ | 72 |

|     | 523    | Rackground Notation and Definitions      | 74 |

5

|    |     | 5.2.4  | Building the trigger: Backward Symbolic Execution | 75 |

|----|-----|--------|---------------------------------------------------|----|

|    |     | 5.2.5  | Building the Trigger: Optimizations               | 81 |

|    |     | 5.2.6  | Adding the Payload: Program Stubs                 | 83 |

|    | 5.3 | Impler | mentation                                         | 83 |

|    |     | 5.3.1  | Testbench Generation                              | 83 |

|    |     | 5.3.2  | Translating Security Assertions.                  | 84 |

|    |     | 5.3.3  | Program Stubs                                     | 84 |

|    | 5.4 | Evalua | ition                                             | 84 |

|    |     | 5.4.1  | Dataset and Experiment Setup.                     | 86 |

|    |     | 5.4.2  | Generating Exploits for Known Bugs                | 86 |

|    |     | 5.4.3  | Comparison with Model Checking                    | 87 |

|    |     | 5.4.4  | Effects of Optimizations                          | 89 |

|    |     | 5.4.5  | Performance                                       | 90 |

|    |     | 5.4.6  | Finding New Bugs                                  | 91 |

|    |     | 5.4.7  | Verify Patches and Refine Assertions              | 92 |

|    | 5.5 | Summ   | ary                                               | 93 |

| 6  | CON | ICLUSI | ON                                                | 94 |

|    | 6.1 | Summ   | ary                                               | 94 |

|    | 6.2 | Future | Directions                                        | 95 |

| DТ |     |        |                                                   |    |

# LIST OF TABLES

| 3.1 | Security-critical bugs implemented and used for evaluation.                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Effect of invariant optimizations (Section 3.2.2) in reducing the total number of invariants and variables in all invariants. CP is constant propagation; DR is deducible removal; ER is equivalence removal.                                                                                                                                                                                                                                                                                   | 28 |

| 3.3 | SCI identified from the 17 security-critical bugs we reproduced (see Table 3.1).  Detected means enforcing the SCI as assertions on the processor can detect the buggy behavior dynamically.                                                                                                                                                                                                                                                                                                    | 29 |

| 3.4 | 24 identified features with non-zero coefficients. Features with negative weights are associated with SCI. Features with positive weights are associated with non-SCI                                                                                                                                                                                                                                                                                                                           | 31 |

| 3.5 | SCI inference results                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

| 3.6 | Evaluation against security properties from prior work. For each property we indicate whether it was found in the identification (From Ident) or the inference (From Infer) step. The bug numbers correspond to Table 3.1. $\checkmark$ means the property is found. If the property is not found it may be because it is not generated from Daikon ( $\blacktriangle$ ), it needs micro-architectural state ( $\bigstar$ ), or it relates to HW outside the processor core ( $\blacksquare$ ). | 32 |

| 3.7 | New security properties generated by our tool that are not covered in prior work                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

| 3.8 | Execution time. Except for traces, sizes are given as number of items, <i>e.g.</i> , the inference phase reads in 88,301 invariants                                                                                                                                                                                                                                                                                                                                                             | 36 |

| 3.9 | Hardware overhead. The baseline is the OR1200, Xilinx xupv5-lx110t-based System-on-Chip. Initial SCI are the 14 assertions from Identification step. Final SCI are the 33 assertions from both Identification and Inference steps                                                                                                                                                                                                                                                               | 36 |

| 4.1 | Security properties of OR1200 processor mined from the specification                                                                                                                                                                                                                                                                                                                                                                                                                            | 42 |

| 4.2 | Security critical properties of AES cryptographic hardware mined from the specification                                                                                                                                                                                                                                                                                                                                                                                                         | 42 |

| 4.3 | Security critical properties of RSA cryptographic hardware mined from the specification                                                                                                                                                                                                                                                                                                                                                                                                         | 43 |

| 4.4 | Information flow security properties of cryptographic hardware                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43 |

| 4.5 | Possible formats of translated assertions in the new design. The simplifications are standard propositional rewrite rules.                                                                                                                                                                                                                                                                                                                                                                      | 44 |

| 4.6 | Features from AST and PDG for variable mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45 |

| 4.7 | Security critical assertions of cryptographic hardware. Assertion A27-01—10 and A28-01—04 are drafted for the AES09 design; Assertion A29-01—02 are for AES11; Assertion A32-01 is for RSA03. The first number in A No. refers to the                                                                                                                                                                                                                                                           |    |

|     | property number in Table 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57 |

| 4.8  | to the property number in Table 4.1                                                                                                                                                                                                                                                                                                                                                                          | 57 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Information flow assertions of cryptographic hardware. The first num in A No. refers to the property num in Table 4.4, 4.3                                                                                                                                                                                                                                                                                   | 58 |

| 4.10 | Main results of assertion translation for 18 AES designs, 20 AES designs with trojans, 5 processor designs, and 3 RSA designs                                                                                                                                                                                                                                                                                | 59 |

| 4.11 | The results of translating A28-01 to 18 AES designs                                                                                                                                                                                                                                                                                                                                                          | 63 |

| 4.12 | Detailed results of translating A28-01 to the AES03 design. VM: Variable Mapping, ST: Structural Transformation, CR: Constraint Refinement                                                                                                                                                                                                                                                                   | 64 |

| 4.13 | The results of translating A04 to 5 CPU designs.                                                                                                                                                                                                                                                                                                                                                             | 64 |

| 4.14 | Lines of code of the RISC processor designs.                                                                                                                                                                                                                                                                                                                                                                 | 66 |

| 4.15 | Accumulative valid ratio of each pass for AES designs.                                                                                                                                                                                                                                                                                                                                                       | 67 |

| 4.16 | Accumulative valid ratio of each pass for CPU designs.                                                                                                                                                                                                                                                                                                                                                       | 67 |

| 4.17 | Results of security impact of translated assertions to detect trojans in AES cores                                                                                                                                                                                                                                                                                                                           | 67 |

| 5.1  | Program stub categories for each bug and implementation details.                                                                                                                                                                                                                                                                                                                                             | 83 |

| 5.2  | Generating exploits of collected bugs. The first 14 bugs are from SPECS [59] and the last 17 bugs are from SCIFinder. The Instructions Generated column shows the number of instructions generated; the Replayable column shows whether the generated exploits can be replayable on an FPGA board. X means either the triggering information cannot be generated or the generated exploit is not replayable. | 85 |

| 5.3  | Effects of optimizations. This table is aggregative, e.g. Compiler Optimizations means that Coppelia is running with both Hybrid Search and Compiler Optimizations on. Time columns show the CPU time. Speedup columns show the relative                                                                                                                                                                     | 03 |

|      | improvements in CPU time compared to previous columns                                                                                                                                                                                                                                                                                                                                                        | 89 |

| 5.4  | Details of the Cone of Influence Pruning.                                                                                                                                                                                                                                                                                                                                                                    | 90 |

| 5.5  | Details of the Compiler Optimizations.                                                                                                                                                                                                                                                                                                                                                                       | 90 |

| 5.6  | New security-critical bugs and exploits found in Mor1kx-Espresso and PULPino-RI5CY Processor.                                                                                                                                                                                                                                                                                                                | 91 |

| 5.7  | Security Patch Verification.                                                                                                                                                                                                                                                                                                                                                                                 | 92 |

# LIST OF FIGURES

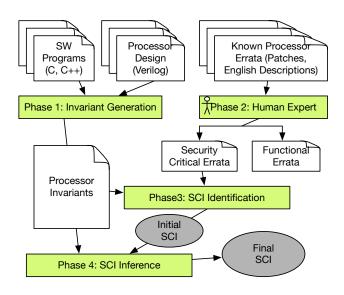

| 3.1  | Workflow of SCIFinder.                                                                                                                                                                                                                                                                                                                     | 16 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

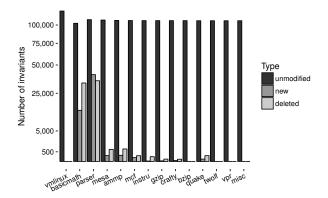

| 3.2  | The grammar of invariant expressions. orig() indicates the value of a variable before the instruction executes; the default is the variable value after the instruction executes. imm refers to an immediate value. in indicates set inclusion. Boolean operators are all bitwise operators.                                               | 19 |

| 3.3  | Unique invariants generated from executing programs. The X-axis is aggregative, e.g., basicmath means invariants generated from running both vmlinux and basicmath                                                                                                                                                                         | 28 |

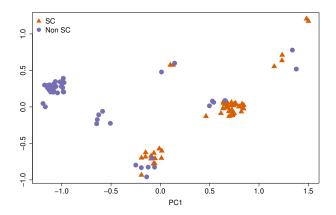

| 3.4  | PCA using selected features. From the learned elastic net logistic regression model, 24 of the original set of 158 features had non-zero coefficients. PCA was performed using the 24 selected features on 102 SCI/non SCI. The plot shows the projection of these invariants in 2 dimensions.                                             | 31 |

| 4.1  | The restricted temporal logic used by security properties expressed as assertions, where $\mathtt{reg}$ is a signal, register, or port in the design, and $N$ is the set of natural numbers.                                                                                                                                               | 40 |

| 4.2  | The syntax used to track how information flows through a hardware design at the gate level. A property is a series of <i>set</i> statements over source variables and <i>assert</i> statements over sink variables. The <i>assert</i> statements may be made conditional using <i>when</i> . Declassification is done using <i>allow</i> . | 41 |

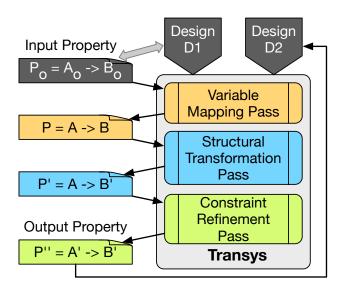

| 4.3  | The workflow of Transys.                                                                                                                                                                                                                                                                                                                   | 44 |

| 4.4  | Code snippets from AES designs.                                                                                                                                                                                                                                                                                                            | 48 |

| 4.5  | Code snippets from AES designs.                                                                                                                                                                                                                                                                                                            | 48 |

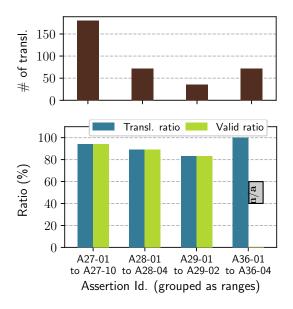

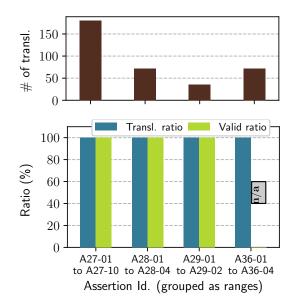

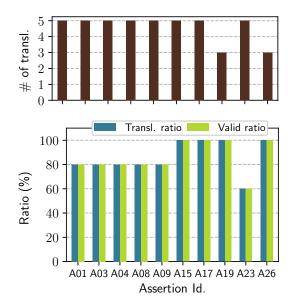

| 4.6  | AES01—AES18 translation results: total translation number and success translation rate.                                                                                                                                                                                                                                                    | 60 |

| 4.7  | AES-T100—AES-T2100 translation results: total translation number and success translation rate.                                                                                                                                                                                                                                             | 60 |

| 4.8  | RSA01—RSA03 translation results: total translation number and success translation rate.                                                                                                                                                                                                                                                    | 61 |

| 4.9  | CPU translation results: total transl. number and success transl. rate                                                                                                                                                                                                                                                                     | 61 |

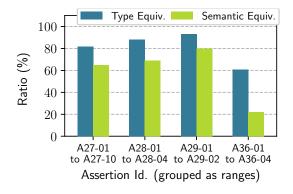

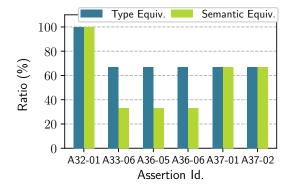

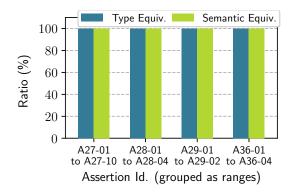

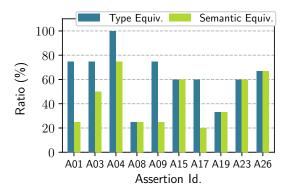

| 4.10 | Type and semantic equivalent for AES01—AES18 designs                                                                                                                                                                                                                                                                                       | 62 |

| 4.11 | Type and semantic equivalent for AES-T100—AES-T2100 designs                                                                                                                                                                                                                                                                                | 62 |

| 4.12 | Type and semantic equivalent for RSA01—RSA03 designs.                                                                                                                                                                                                                                                                                      | 62 |

| 4.13 | Type and semantic equivalent for CPU designs.                                                                                                                                                              | 62 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

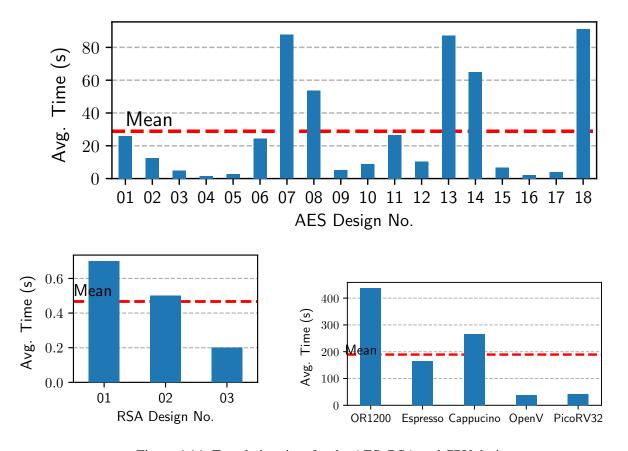

| 4.14 | Translation time for the AES, RSA and CPU designs                                                                                                                                                          | 65 |

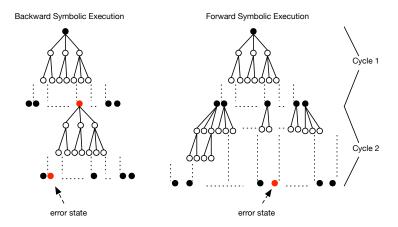

| 5.1  | Backward symbolic execution strategy: We search for a path from the last cycle to the first cycle (black arrows). Within each cycle, we symbolically execute the hardware design forwardly (green arrows). | 72 |

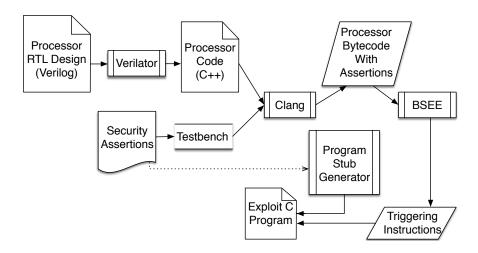

| 5.2  | Workflow of Coppelia. The process labeled BSEE is the backward symbolic execution engine.                                                                                                                  | 73 |

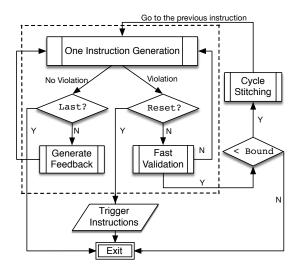

| 5.3  | Workflow of Backward Symbolic Execution                                                                                                                                                                    | 76 |

| 5.4  | Comparison of backward and forward symbolic execution for 2 clock cycles                                                                                                                                   | 80 |

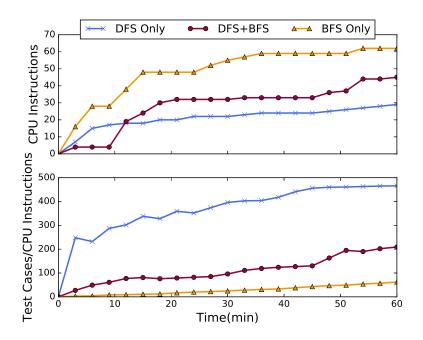

| 5.5  | Comparison of different search heuristics.                                                                                                                                                                 | 91 |

## LIST OF ABBREVIATIONS

ABV Assertion Based Verification

AES Advanced Encryption Standard

AST Abstract Syntax Tree

BFS Breadth First Search

CNF Conjunctive Normal Form

DAG Directed Acyclic Graph

DFS Depth First Search

DoS Denial of Service

GPR General Purpose Register

HDL Hardware Description Language

ISA Instruction Set Architecture

ORAM Oblivious RAM

OVL Open Verification Library

PC Program Counter

PCA Principal Component Analysis

PDG Program Dependence Graph

RISC Reduced Instruction Set Computer

RTL Register Transfer Level

SCI Security-Critical Invariants

SEV Secure Encrypted Virtualization

SGX Software Guard Extension

SPR Special Purpose Register

SR Status Register

TCB Trusted Computing Base

VM Virtual Machine

XOM Execute-Only Memory

#### **CHAPTER 1**

## INTRODUCTION

Hardware provides the foundation of computing and represents the minimal Trusted Computing Base (TCB) for the upper-level software systems. The implication is that an attacker who controls the hardware of a machine can often gain unrestricted access to the entire machine. A well-resourced attacker with access to the hardware supply chain may incorporate a backdoor into the design. Yet an easier way exists: by leveraging existing vulnerabilities within hardware designs, the attacker can gain control of hardware using software-only exploits launched remotely from the hardware. For example, a defect in recent x86 CPUs' exception delivery logic could be exploited by a guest VM to launch a denial of service attack against its host [9]. The infamous Spectre and Meltdown attacks [67, 74] exploited the vulnerability in speculative execution to leak kernel memory. This problem is exacerbated by the growing complexities of hardware and varieties of domain-specific architectures. Indeed, security experts have warned recently that hardware is in "the crosshairs of cyberhackers" [88].

The current state of the art to find vulnerabilities in hardware designs uses hardware design verification, which combines simulation based testing and formal static analysis. The efficacy of simulation-based testing depends on the coverage of the testbenches used, and is unlikely to uncover a vulnerability that is exploitable by only a handful of possible input sequences. Formal static analysis, on the other hand, is a systematic approach to potentially combat hardware security vulnerabilities. One promising direction of formal static analysis for security validation is assertion-based verification. Each assertion is a proposition encoding a property that should always hold, and monitors the hardware signals and states named in the property. Because the expected behavior is described via a property, the assertion can potentially expose a class of seemingly different defects in the processors. The questions of what are the security-critical properties we should protect for hardware and how to efficiently develop them, however, are not clear.

Another big challenge often faced by hardware designers and security experts is: when a vulnerability is fixed or mitigated, is the problem fully solved? There are three aspects of this question: First, is the vulnerability fully or only partially fixed – can the attacker modify the original attack program or use a new

attack program to trigger the same vulnerability? Second, are similar vulnerabilities also fixed – are simple variants of the original vulnerabilities (low-hanging fruits to attackers) also fixed? Third, when we move to the next generation of the product, will the design be vulnerable to the same attacks again?

This dissertation aims to answer the above questions. I develop systematic methods and practical tools that help hardware designers efficiently detect a class of security vulnerabilities (software exploitable bugs) at design time and build more secure hardware designs. Our research efforts have explored achieving this objective from two broad lines.

The first line is identifying and automatically generating security properties for hardware designs. I developed a semi-automatic approach, SCIFinder [112], that uses known processor errata and machine learning techniques to identify security properties. The security properties are useful to protect the hardware design they are derived from, but repeating the whole process for each new design can be tedious. Thus, I built a tool, Transys [113], that automatically translates security properties from one design to similar designs to reduce the effort in developing security properties. The second line is automatically generating exploit programs. I developed an end-to-end tool, Coppelia [111], that automatically generates exploit programs. The core of Coppelia is a hardware-oriented backward symbolic execution engine. It helps designers better analyze, understand, and assess the security threat for vulnerabilities in processor designs.

#### 1.1 Thesis Statement

In the hardware design process, security validation of open-source RISC processors designs can be automated through mining security assertions with machine learning and known security errata, translating security assertions using static analysis techniques, and generating exploit programs using backward symbolic execution.

## 1.2 Developing Hardware Security Properties

The current practice for hardware designers and security experts to write security-critical properties is through manually studying the processor's Instruction Set Architecture (ISA) and its documentation, such as hardware specification sheets and user manuals. This process is time consuming, error-prone, and easy to miss important security properties. To address this challenge, we introduce SCIFinder in Chapter 3.

SCIFinder semi-automatically generates Security-Critical Invariants (SCI) for processor designs. Our first insight is that hardware security essentially concerns a core set of processor functionality (e.g., exception delivery, protection rings) that the upper-level software must depend on; any bugs in this subset could result in security compromises. Thus, we can first automatically generate a large set of processor invariants that describe all aspects of software-visible processor behavior by exercising the processor with a variety of programs. Then security-critical invariants can be algorithmically identified by checking the generated invariants against known software exploitable vulnerabilities. Our second insight is that SCIs tend to have common features such as the registers and flags used in them, and machine learning techniques can be used to infer additional security SCIs based on the existing ones.

Specifically, SCIFinder starts with obtaining processor execution traces by simulating the processor's register-transfer-level (RTL) design. To ensure wide coverage of the processor states, it runs a variety of software programs. SCIFinder then derives invariants within and across these traces by using a modified version of Daikon (as the original Daikon is not specifically designed for hardware). Among the derived invariants, SCIFinder uses known processor errata to differentiate the security-critical invariants from the purely functional ones. SCIFinder relies on a human to identify which errata are security-critical. For each security-critical erratum, we craft an exploit program that triggers the vulnerability. Then SCIFinder generates execution traces from executing the exploit program on both the buggy processor and the patched processor. SCIFinder further identifies those invariants that get violated in the execution trace of buggy processor but not the patched processor's as security-critical. In the last step, SCIFinder uses machine learning techniques to infer additional security-critical invariants. SCIFinder models the probability that an invariant is non-security-critical as a function of its measured features.

SCIFinder is evaluated on the OR1200 RISC processor. It identified 19 (86.4%) of the 22 manually crafted security-critical properties from prior work and generated 3 new security properties not covered in prior work. The generated assertions were tested against 14 new vulnerabilities adapted from real-world AMD processor errata, and find the assertions stop 12 (86%) of these bug-based exploits. The following invariant shows an example of security property that SCIFinder identifies (related to privilege-escalation):

$$I \doteq risingEdge(\texttt{l.rfe}) \rightarrow \texttt{SR} = orig(\texttt{ESRO})$$

This invariant states that when returning from an exception (indicated by the 1.rfe instruction), the status register (SR) should be correctly updated with the value it had before the processor entered the exception handler. ESR0 stores that value. The orig(ESR0) denotes the value of ESR0 before 1.rfe is executed, while SR denotes the value of SR after the 1.rfe instruction is executed.

The unique contribution of SCIFinder is that it demonstrates the feasibility and benefits to derive hardware security invariants from software-exploitable bugs and in turn use the derived invariants to protect the hardware against a class of vulnerabilities and zero-day attacks.

## 1.3 Translating Hardware Security Properties

A comprehensive set of properties describing the security requirements is useful for validating the security of hardware designs. However, developing security properties for hardware designs is challenging, and this effort needs to be repeated for each version of the design and each new design. The insight is that if we can leverage existing security properties and translate them from one design to another, we can reduce the effort in developing security properties.

To this end, I introduce Transys in Chapter 4, a tool for translating security critical properties written for one hardware design to analogous properties suitable for a second design. Transys takes a set of security properties that already developed for one hardware design, and two implementations of hardware designs as inputs. It works in three steps: first, it maps variable names by using a statistical matching method to semantically correlate variables between the two designs; second, it adjusts arithmetic expressions by using a program analysis-based re-structuring phase to make assertions functional in the new design; finally, it refines the constraints to iron out remaining issues with the constraints of the result properties. Transys is evaluated for translating 27 assertions written in a temporal logic and 9 properties written for use with gate-level information flow tracking, across 38 AES designs, 3 RSA designs, and 5 RISC processor designs. It successfully translates 96% of the properties (the output properties are validated by model checking). Among these, the translation of 23 (64%) of the properties achieved a semantic equivalence rate of above 60%. The average translation time per property is about 70 seconds.

Transys is the first tool to translate security properties across hardware designs. Applying Transys to hardware designs also suggests that hardware designers can keep the assertions of a single project in sync

with the design. Over the life cycle of the hardware code base, designers could use Transys to suggest updates to properties they had affected by changing the target design.

# 1.4 Generating Hardware Exploit Programs

Formal static analysis and simulation-based testing are powerful to help find many potential bugs in hardware designs. However, reporting a potential bug is only the first step. A reported bug, in the form of some violated assertion, could turn out to be a false alarm due to errors in the assertion itself, the formal method tools, or the simulation environment. Even if a reported violation is a true bug, it is unclear whether this bug poses security risk or not, and if so, how it may be exploited. Determining true bugs and their security implications for found violations is time-consuming, a process that involves hardware designers, security experts and formal method experts. To address the gap in the current practice, we developed Coppelia that provides an end-to-end solution that helps hardware designers systematically find potential bugs and assess the security implication of the vulnerabilities.

Our key strategy is to automatically generate exploit programs for hardware designs. In this way, hardware designers can narrow down and contextualize the true vulnerabilities in the set of reported violations. Moreover, when hardware designers fix some vulnerabilities, they can check whether exploit programs can still be generated for the updated hardware design and use this fact to validate the correctness and security implication of the vulnerability fix. Symbolic execution is a promising technique for our scenario because symbolic execution can generate a concrete input that leads to the assertion-violation path. The bug-triggering input will be essential for generating exploit programs. While symbolic execution has been extensively explored in the software world and successfully applied to relatively large software, how to perform symbolic execution on hardware designs is under-explored. Two characteristics of hardware designs require rethinking the standard symbolic execution. First, the symbolic execution of a hardware design represents an exploration of the design for a single clock cycle, but hardware executes continuously, and security vulnerabilities may only become apparent many clock cycles after the initial state. Second, security properties developed for hardware designs capture the semantics of particular signals and their connecting logic. Finding such violations is akin to finding a needle in a haystack.

Coppelia designs a novel hardware-oriented backward symbolic execution strategy to enable a targeted search through the hardware design space for rare assertion violations. To begin, Coppelia translates the

hardware design from an hardware description language implementation to C++. After translation, Coppelia generates testbenches with security-critical assertions. To build a trigger to the exploits, Coppelia leverages KLEE and implements backward symbolic execution. Starting at the point of an assert statement, Coppelia symbolically executes the design backwardly, searching for a path from an assertion-violating state back to the reset state. To handle symbolic execution across multiple clock cycles, Coppelia adopts a cycle stitching method that can generate a complete sequence of instructions that triggers a bug starting from the reset state. Coppelia also uses several optimizations to tackle the challenge of state exploration in hardware. To better contextualize and analyze the security threat, Coppelia goes beyond triggering the vulnerability. It adds a program stub to complete the exploit. These program stubs are generated according to the category of the security-critical assertion violated. Coppelia is evaluated on three CPUs of different architectures: it generates exploits for 26 out of 29 known vulnerabilities in these CPUs, all of which are successfully replayable on an FPGA board; it also finds 4 new vulnerabilities along with exploits in these CPUs.

# 1.5 Organization

The remaining of this thesis is organized as follows: Chapter 2 discusses the background and prior work that is related to this thesis. Chapter 3 and 4 presents our work in developing security properties for hardware designs. Chapter 3 describes the design and implementation of SCIFinder, together with an evaluation of its effectiveness in generating security properties for detecting both known and unknown security bugs on the OR1200 processor. Chapter 4 introduces Transys, presents the three phases for translating the security properties across hardware designs, and reports its uses in translating both temporal and informatino flow tracking assertions in AES, RSA, and RISC designs. Chapter 5 presents our work in using the security properties for security validation for hardware designs. Chapter 5 describes Coppelia and the details of our backward symbolic execution strategy, and shows an evaluation of using it for two different processor and architectures. Chapter 6 summarizes the contributions and concludes this dissertation.

#### **CHAPTER 2**

#### BACKGROUND AND RELATED WORK

In this chapter I place my proposed methods and tools in the wider context of hardware security defense and validation methods by describing related work and background information. I first describe several research directions in defending against different hardware vulnerabilities, including novel hardware features and mechanisms, information flow security, hardware security validation, and novel hardware description languages. Then I discuss research in extracting and mining assertions for hardware designs, as well as software designs. These research are related to our work in developing hardware security assertions. Finally, I present the background of symbolic execution, and its application in software security research and hardware validation, which are related to our work in generating exploit programs for hardware.

## 2.1 Approaches for Protecting Vulnerable Hardware

Major types of attacks to hardware include physical attacks, privileged software attacks, software attacks on peripherals, hardware trojans, and cache timing attacks. I describe detection methods and countermeasures to these attacks in this section.

## 2.1.1 Secure Processors

To defend against physical and software attacks to hardware, as well as to protect the integrity of sensitive data, different mechanisms and features have been proposed. I categorize them into academic solutions and industry solutions.

## **Academic Solutions**

The execute-only memory (XOM) architecture [73] proposes the approach of executing sensitive code and data in isolated compartments. XOM tags each cache line with a XOM identifier, and disallows memory accesses to cache lines by compartments whose identifier mismatches the current one. AEGIS secure

processor architecture [95] protects the integrity and privacy of applications from physical attacks and software attacks. AEGIS uses physical random functions and off-chip memory protection to defend against physical attacks. It uses a security kernel to isolate compartments. Bastion [30] relies on a trusted hypervisor to provide secure compartments for running applications. The Ascend secure processor [89] leverages the Oblivious RAM (ORAM) technique which obfuscates address buses by reshuffling memory as it is accessed to defend against attacks that learns private information from DRAM memory access patterns. The Capability Hardware Enhanced RISC Instructions (CHERI) [104], based on RISC ISA, introduces a hybrid capability model to mitigate memory related vulnerabilities. CHERI includes a capability coprocessor and tagged memory to support a self-contained virtual capability system.

## **Industry Solutions**

ORWL [5] is an open-source processor aiming to defend against physical attacks. ORWL uses the outer shell and the sensors to detect physical attempts to tamper encrypted data, and once detected, ORWL destroys all hardware encrypted data instantly. IBM SecureBlue++ [6] is an architecture that protects confidentiality and integrity of information in an application against other applications, as well as against attempts to introduce malware inside the application. An application's information is encrypted whenever it is outside the processor and other software cannot access the application's cleartext information inside the processor. ARM TrustZone [1] is a hardware architecture that creates an isolated environment to allow confidentiality and integrity of code and data. TrustZone conceptually partitions a system's resources between a secure world for the security subsystem and a normal world. The secure world resources cannot be accessed by the normal world components. TrustZone also provides hardware extensions that enables code execution from both the secure world and the normal world in a time-sliced fashion, allowing high performance security software to run alongside the normal world operating environment [1]. Intel Software Guard Extensions (SGX) [79] enables processors to execute code in an enclave that is isolated from the untrusted software, and also provides a software attestation scheme that allows a remote party to authenticate the software running inside the enclave. AMD Secure Encrypted Virtualization (SEV) [63] aims for protecting data in DRAM against physical threats as well as threats from virtual machines or hypervisors. SEV isolates a full virtual machine (VM) by tagging and encrypting all code and data to prevent data from being used by anyone other than the owner.

# 2.1.2 Information Flow Security

Hardware is capable of leaking information through timing, power, thermal and other covert channels. Information flow security in hardware uses dataflow tracking to track the flow of untrusted network, file and user inputs through memory. Information Flow Tracking logic can be added at the gate level [99] or register transfer level [14] of a hardware design, and can capture timing flows [13, 78] or data flows [85]. While there is a trade-off to be made between precision and performance [19, 105], these techniques can demonstrate whether sensitive inputs to a design, e.g., the key material input to a cryptographic core, is directly or indirectly visible in the output signals. As with language based verification, this approach can provide strong guarantees, but also requires modifying the original design, either by adding tracking logic or, as in the case of CPUs, redesigning from the ground up to provide provable isolation between software contexts [97, 98]. Efficiently tracking information flow in hardware has been studied [41, 101, 33, 99, 14], but this approach often requires modifying or extending the hardware architecture. Cherupalli et al. proposed a gate-level symbolic simulation tool for information flow for particular IoT applications [35].

## 2.1.3 Property Driven Hardware Security Validation

## **Assertion Based Verification for Security**

Assertion based verification (ABV) is the form of testing in which assertions added to the design encode functional correctness properties, such as a request–acknowledge pattern [50]. Once assertions are added, simulation-based testing or formal static analysis may then be used to search for violations of the assertions. Both approaches have gained wide acceptance and commercial tools are available, including Cadence [2]. In simulation-based testing the aim is to achieve high code coverage using many test cases [103]; assertion violations that exist along untested paths will not be discovered. In formal static analysis the design is unrolled some number of cycles and the state space is methodically explored [25, 24, 46]. Test cases are no longer the limitation, but rather the size of the state space limits how far the design can be unrolled. Both simulation-based testing and formal static analysis are performed at design time.

Properties can be encoded as assertions and added to the design under review, at which point standard ABV techniques can be used to find property violations. Historically, functional properties were used, but recently security properties have been considered. These security properties are manually developed [21, 22, 59]. SecurityCheckers [21, 22] and SPECS [59] developed temporal logic security assertions from the

manual or specification of the RISC processors, e.g. the return from exception instruction causes the program counter (PC) to be loaded from EPCR and the status register (SR) to be loaded from ESR; unspecified custom instructions are not allowed. Information flow properties have also been manually developed [60, 62]. An example information flow property in an AES core is that the secret key should not flow to the ciphertext ready signal otherwise there would be a timing side channel. There has lately been a call for "property driven hardware security" [60, 61, 64] that advocates building security specifications into the hardware design workflow, automating the process of doing so, and developing quantifiable measures of security.

## **Protecting Buggy Hardware Post Deployment**

Some bugs may persist to the final product and work must be done to mitigate the resulting harm. Solutions include adding redundancy to the hardware design to protect against random errors [16] and checking processor state transitions against a known set of errata signatures [83, 91, 92]. Once discovered (post-deployment), some bugs are amenable to being patched by software. These methods include microcode patching and binary translation [57, 100, 80]. A hybrid software–hardware approach adds additional hardware to the design in the form of assertions and uses software to handle any assertion failures that occur at run-time [40, 39, 59].

## 2.1.4 Language Based Approaches

There is a body of work on developing new or extending current hardware description languages for secure hardware development. One language based approach uses typed hardware description languages, which can enforce security policies by construction [72, 71, 109, 110, 48]. Caisson [72] is a hardware description language (HDL) targeting statically-verifiable information-flow secure hardware designs. Caisson enforces security policies by using a lease mechanism between trusted and untrusted states during execution. Sapper [71] compiles code to synthesizable Verilog that enforces security policies by automatically deriving and inserting dynamic security checks. SecVerilog [109, 110] extends Verilog with security labels to mitigate external timing channels. SecVerilog relies on hardware designers to annotate the security lables and to distinguish between benign timing variations and and those carrying confidential information. ChiselFlow [48] is a security-typed HDL embedded in Scala. ChiselFlow reduces its trusted component by compiling to a small intermediate language that is responsible for the enforcement of security policies, and reduces programmer efforts by providing label inference for internal signals inside hardware modules. Although these

approaches can prove that a hardware design meets the security policies, they cannot verify those designs not already implemented in these languages. A second language based approach uses a formally defined language to first specify a policy and then refine the specification to a provably correct design [102, 23, 37]. Fe-Si [23] is a functional language that is a deterministic subset of Bluespec. Fe-Si embeds Coq as a meta programming tool that allows it to prove the correctness of the circuits. Kami [37], also based on Coq, verifies circuits by proving that each hardware module refines its specification modules.

# 2.2 Developing Security Specifications

## 2.2.1 Extracting assertions from hardware designs

In ABV, assertions are added to the hardware design, typically written in a hardware description language (HDL) such as Verilog or VHDL, and the design, with assertions added, is simulated with random or selected inputs. Any assertions that fire during simulation point to a bug in the design. Considering properties beyond those critical to security, there is a body of work on specification mining from hardware designs.

The IODINE [54] tool automatically extracts ABV assertions from designs. The IODINE tool looks for possible instances of known design patterns, such as one-hot encoding or mutual exclusion between signals, and creates assertions that encode the found patterns [54]. Change et al. examines frequently occurring patterns in a number signals that the user deems important based on knowledge of the domain, and then generates assertions based on the most frequent patterns [32]. Avoiding the dependence on human choice, the GoldMine system used a combination of static analysis of the hardware design to guide the data mining on the simulation data providing a more robust set of assertions [58]. While these techniques are not concerned with finding security properties, they provide lessons on how to scale assertion extraction effectively. Our work goes beyond just extraction and focuses on *finding* security critical assertions.

## 2.2.2 Data Mining for Security Properties of Software

Security properties in software have been found using human specified rules [96], by observing instances of deviant behavior [86, 81, 47], or by identifying instances of known bugs [107].

Tan et al. looks for patterns of security checks and the sensitive operations protected by those functions, and subsequently searches the rest of the code base for unprotected sensitive operations [96]. Moving away from human specified rules, more recent work explored extracting the latent security rules inherent in the

code by modeling the normal behavior in a more descriptive manner [86, 81]. Perkins et al. models software behavior [47] by monitoring registers and memory locations in order to create invariants that defined normal program behavior. By examining which invariants are violated during erroneous execution, they were able to define and identify deviant behavior [86]. Another technique that comes from the concept of normal and deviant behavior is modeling abnormal behavior from a previously known vulnerability or bug. Yamaguchi et al. established a pattern based vulnerability extrapolation where they define deviant behavior and examine the rest of the code base to identify similar abnormal behavior [107].

## 2.3 Symbolic Execution

## 2.3.1 Symbolic Execution Technique

Symbolic execution is a technique of analyzing a program to determine what inputs cause each part of a program to execute [65]; it is often used to check which inputs cause assertion failures. At the beginning, the inputs to a program are marked as symbolic. Then the program executes step by step, building constraints on the symbolic variables based on the program operations. When reaching the branch statements, symbolic execution forks into two paths. Each path gets assigned a copy of the program state and the path constraint at the branch statement. When paths terminate, symbolic execution uses the accumulated path constraints to determine whether assertions fires by solving the path constraints together with the assertions with a solver (e.g. stp [52], z3 [43]). Meanwhile, symbolic execution can generate concrete values of the inputs that cause errors to occur.

Directed symbolic execution [76] and execution synthesis [108] use guided symbolic execution to increase the probability of executing paths of interest. In software, backward symbolic execution has been studied to solve the goal-reachability problem [31, 76]. Otter [76] developed the call-chain-backward symbolic execution which begins at a target line and proceeds backward to the start state. Application to real-world software raises many challenges such as complicated arithmetic (such as floating point), external method calls, and data-dependent loops [45, 31].

Researchers also explored different ways to mix concrete and symbolic runs [28, 27, 29]. The symbolic engine always executes concretely on operations with concrete values only, which makes symbolic execution possible to reason over complex operations. S2E [36] presents a systematic approach to consistently cross the

symbolic and concrete boundaries. It interleaves portions of code that are concretely run with fully symbolic phases, which is done carefully to preserve the meaningfulness of the whole execution.

# 2.3.2 Automatic Exploit Generation

Software symbolic execution has been widely explored [28, 53, 29, 27, 42, 65]. Symbolic execution is also often used in automatic exploit generation for software [26, 56, 17, 18, 29]. Typically, vulnerabilities (e.g., buffer overflows) are first found through static or dynamic analysis, and then program input satisfying identified constraints are found. We tackle similar problems but differ in that we target the hardware domain, which requires a stateful analysis across multiple clock cycles to generate a series of input for hardware, instead of a single input as in software.

The problem I tackle in this thesis is similar in nature to the problems in the software domain of automatic exploit-based generation [17] and patch-based exploit generation [26]. In those cases, as in ours, strategies are needed to focus the search toward an exploitable bug. Brumley et al. [26] focus their search by calculating the weakest precondition of a vulnerable state, and my use of backward symbolic execution is, in effect, a method for calculating a precondition, although not the weakest. However, the approach we take is geared toward handling a stateful hardware design, which may require a sequence of inputs to find a bug, rather than a single input.

# 2.3.3 Hardware Symbolic Simulation

Applying symbolic execution to hardware designs for verification and testing has also been studied [75, 82]. STAR [75] is a functional input vector generation tool combining symbolic and concrete simulation for RTL designs over multiple time frames. It provides high range statements and branch coverage, but is limited by the sequential depth (around 6 cycles) [75]. PATH-SYMEX is a forward symbolic execution engine that takes in ANSI-C interpretation of the RTL code [82]. Its application is limited to small RTL designs. With the purpose of reproducing bug exploits, my work focuses more on the sequential depth of the exploration with Backward Symbolic Execution Scheme and can be easily integrated to the current industrial verification flow by leveraging software verification methods.

#### **CHAPTER 3**

#### DEVELOPING HARDWARE SECURITY PROPERTIES

In this chapter, I present the details our semi-automatic approach, SCIFinder, for developing hardware security properties outlined in Section 1.2. I first give an overview of the proposed approach in Section 3.1. I then describe the design and implementation details in Section 3.2 and 3.3. Finally, I show our evaluation of SCIFinder on the OR1200 processor in Section 3.4.

#### 3.1 Overview

Previously, researchers develop security assertions manually by studying the processor's instruction set architecture (ISA), identifying properties of the ISA that are critical to the security of software running on the processor, and encoding those properties as assertions [59, 21, 22]. The process requires human expertise and judgment. The process can be tedious and time consuming. Moreover, some properties that are important for security are obscure and unlikely to be identified. Furthermore, because the instruction manuals describing an ISA may be incomplete and ambiguous there are important properties which even the most thorough perusal of the ISA will be unable to uncover.

However, there is a benefit to having a human in the loop. The line between a security property and a purely functional property is blurry. Some properties seem obviously critical to security. As an example, each of the above cited works ([21, 59, 22]) includes an assertion that the supervisor signal is set only in response to a small number of well defined events. Other properties, such as the one(s) violated by Intel's infamous FDIV bug [8, 15], feel safely characterized as purely functional.

SCIFinder is a methodology and tool chain for semi-automatically generating a set of security-critical processor invariants that can be encoded as synthesizable assertions. Our approach is informed by three observations. First, detailed information about processor invariants may not exist in any specification documents; this information can only be learned by studying a running processor. Second, human expertise is still needed for, and well suited to, distinguishing security concerns from purely functional ones. And, third,

properties that are critical to security tend to have commonalities between them, for example, they concern state that is critical to security, such as the supervisor signal.

Rather than try to cull security-critical properties from the ISA, we instead generate, automatically, a large set of processor invariants that describe all aspects of processor behavior and then categorize each invariant as critical to security or not. While we wish to use human judgment to guide this process, we do not want to burden the designers with the task of combing through hundreds of thousands of invariants to perform the categorization. Therefore, we have developed two ways to algorithmically differentiate security-critical invariants from functional invariants: 1) Use published processor errata that can be shown to pose a threat to security to drive the categorization, and 2) Use statistical analysis techniques to classify the invariants. The benefit of using published errata as a starting point is the potential to create assertions with high value. These assertions will at a minimum catch actual bugs that have historically had a deleterious effect on security. The approach has the potential to be stronger than that, however. If the assertions are well crafted, they capture not just the absence of a particular bug, but the presence of a desired security property. These assertions will detect any bug that violates the protected property, even if the bug itself is entirely different from the one that first inspired the assertion. Still, the errata-based approach is limited to finding properties that have at one point been violated by a known security bug. In our second approach, we explore to conjecture that once a human has identified points along the security-functionality boundary, machine learning techniques can be used to automate the classification of additional invariants. In this way new security-critical invariants can be identified.

# 3.2 Design

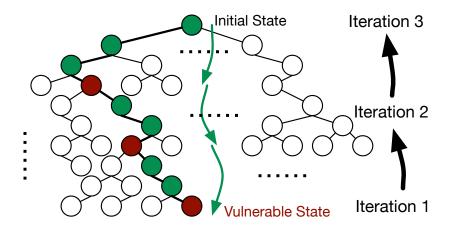

As shown in Figure 3.1, SCIFinder has four phases. The first phase is invariant generation. We observe a processor executing a variety of programs to collect a set of likely processor invariants defined over software-visible processor states. The second phase is to classify each collected known design errata, using human expertise and judgment, as either a functional bug or a potential security vulnerability. The third phase is security-critical invariant (SCI) identification. We identify SCI as those invariants violated by the security vulnerabilities from the second phase. The fourth phase is SCI inference. We apply machine learning techniques to find additional SCI in the set of processor invariants. We next discuss phase one, three and four in detail. Details of our implementation of phase two are in Section 3.3.1.

Figure 3.1: Workflow of SCIFinder.

## 3.2.1 Invariant Generation

In the first phase, we collect a set of likely processor invariants. We use a modified version of Daikon, a dynamic invariant generation tool, and execute the processor design in simulation with a variety of software running on it. We operate at the ISA level: we track software-visible states and consider execution of an instruction to be a single step of execution. We wish to collect meaningful processor invariants. We do this by generating a large number of processor execution traces covering as many processor states as possible, and then observing invariants within and across these traces. Some of the generated invariants are potentially security critical and will be identified as such in the following phases (see Section 3.2.3 and Section 3.2.4).

## **Execution Traces**

We obtain the processor execution traces by simulating the processor's register-transfer-level (RTL) design. During simulation we track architectural signals and selected register values of the RTL design at each instruction boundary. To provide as much breadth as possible, we run a variety of programs including SPEC benchmarks, a Linux boot, and scientific computations (see Section 3.4.1). Our execution traces must, at a minimum, cover all the instructions in the ISA, including system calls, bit-rotation operations, word-extension operations, and interrupts and exceptions.

#### **Daikon**

From the execution traces, we use Daikon, a dynamic invariant detection tool, to gather meaningful invariants [47]. Daikon has an instrumenter and an inference engine. The instrumenter records information about variable values as a program executes, and the inference engine reads the traces produced by the instrumenter to generate invariants.

Daikon is not specifically designed for hardware, and we adapted it to suit our needs. Daikon is intended to learn software-level invariants: procedure pre- and post-conditions, class invariants, and data structure invariants. These are not directly applicable to processor execution traces; we extend Daikon to suit our hardware use case (see Section 3.2.1). Patterns often seen in hardware design, such as bit-packing several flags into a single register, are unknown to Daikon. We develop new invariant patterns that capture such non-linear relationships between variables (see Section 3.2.1). Certain processor design optimizations, such as delay slots, need to be carefully handled (see Section 3.2.1). The invariants generated by Daikon contain redundancies. Our SCI will be enforced on processors dynamically and should be concise to avoid overhead. We introduce optimizations to remove redundancy (see Section 3.2.2).

#### **Invariant Variables**