# Clock Synchronisation Assisted Clock and Data Recovery for Sub-Nanosecond Data Centre Optical Switching

A thesis submitted to UCL (University College London) for the partial fulfilment of the requirements for the degree of Doctor of Philosophy (PhD)

by

## **Kari Aaron Clark**

Optical Networks Group

Department of Electronic and Electrical Engineering

UCL (University College London)

## **Declaration**

I, Kari Aaron Clark, confirm that the work presented in this thesis is my own. Where information has been derived from other sources, I confirm that this has been indicated in the thesis.

### **Copyright Notice**

The copyright of this thesis belongs to the author, Kari Aaron Clark.

The exclusive right to publish the analysis of the impact of clock and data recovery locking time on optical switch performance in Chapter 1 Section 1.1.2, the description of clock synchronisation assisted clock and data recovery (CSA-CDR) in Chapter 3 Section 3.4 (originally published as clock phase caching) and the experimental work in Chapter 6 within this thesis was granted to Springer Nature for publication in Nature Electronics [1]. The exclusive right to publish the experimental work in Chapter 7 was granted to the Institute of Electrical and Electronics Engineers for publication in the Journal of Lightwave Technology [2]. The primary author of these works, Kari Aaron Clark, has retained the non-exclusive right to reproduce these works (including graphic elements) in whole or in part in this thesis.

The remaining material within this thesis is licensed under a Creative Commons Attribution 4.0 International Public Licence (CC BY 4.0).

Under the Creative Commons Attribution 4.0 International Public Licence (CC BY 4.0), you may copy and redistribute the remaining material within this thesis in any medium or format. You may create and distribute modified versions of the work, on the condition that: 1) you credit the author, Kari Aaron Clark, and 2) if the work has been modified, you indicate that the work has been changed and describe those changes. When reusing or sharing this work, ensure that you make the licence terms clear to others by naming the licence and linking to the licence text.

Please seek permission from the copyright holder, Kari Aaron Clark, for uses of this work that are not included in this licence or permitted under UK Copyright Law.

The way to deal with an impossible task was to chop it down into a number of merely very difficult tasks, and break each one of them into a group of horribly hard tasks, and each of them into tricky jobs, and each of them...

TERRY PRATCHETT, TRUCKERS

For Grandma Cats and Grandma Dogs.

#### **Abstract**

In current 'Cloud' data centres, switching of data between servers is performed using deep hierarchies of interconnected electronic packet switches. Demand for network bandwidth from emerging data centre workloads, combined with the slowing of silicon transistor scaling, is leading to a widening gap between data centre traffic demand and electronically-switched data centre network capacity. All-optical switches could offer a future-proof alternative, with potentially under a third of the power consumption and cost of electronically-switched networks. However, the effective bandwidth of optical switches depends on their overall switching time. This is dominated by the clock and data recovery (CDR) locking time, which takes hundreds of nanoseconds in commercial receivers. Current data centre traffic is dominated by small packets that transmit in tens of nanoseconds, leading to low effective bandwidth, as a high proportion of receiver time is spent performing CDR locking instead of receiving data, removing the benefits of optical switching. High-performance optical switching requires sub-nanosecond CDR locking time to overcome this limitation.

This thesis proposes, models, and demonstrates clock synchronisation assisted CDR, which can achieve this. This approach uses clock synchronisation to simplify the complexity of CDR versus previous asynchronous approaches. An analytical model of the technique is first derived that establishes its potential viability. Following this, two approaches to clock synchronisation assisted CDR are investigated: *1) Clock phase caching*, which uses clock phase storage and regular updates in a 2 km intra-building scale data centre network interconnected by single-mode optical fibre. *2) Single calibration clock synchronisation assisted CDR*, which leverages the 20× lower thermal sensitivity of hollow core optical fibre versus single-mode fibre to synchronise a 100 m cluster scale data centre network, with a single initial phase calibration step. Using a real-time FPGA-based optical switch testbed, sub-nanosecond CDR locking time was demonstrated for both approaches.

**Keywords:** Clock Synchronisation Assisted Clock and Data Recovery, Clock Phase Caching, Sub-Nanosecond Optical Switching, Hollow Core Fibre, Clock Synchronisation, Data Centre Networks, All-Optical Data Centre Switching.

### **Impact Statement**

The lack of sub-nanosecond clock and data recovery in data centre optical switches was a key impediment to practical optical switching in the data centre, by limiting the achievable overall switching times, and therefore the achievable performance, of data centre optical switches. This thesis establishes clock synchronisation assisted clock and data recovery, an approach that leverages clock frequency and phase synchronisation to minimise clock and data recovery time to sub-nanosecond. This improvement in clock and data recovery time versus the previous state-of-the-art, by more than an order of magnitude, enables practical data centre all-optical switching.

In turn, all-optical switches could enable high-performance data centre networks that support emerging high-bandwidth hardware-based workloads such as deep neural network training, while simultaneously reducing data centre network power consumption by two thirds versus electronically-switched networks. Both outcomes are of extensive benefit to worldwide society: deep neural networks have many applications across fields including medicine, autonomous driving and machine translation; and minimising the power consumption of data centres, which could by 2030 consume 3 to 15% of global power, contributes towards limiting global warming.

The clock phase caching approach to clock synchronisation assisted clock and data recovery, which was investigated in collaboration with and patented by Microsoft Research, was published as a post-deadline conference paper at ECOC 2018, followed by a high-impact journal paper in Nature Electronics in 2020. Clock phase caching was used in Microsoft's prototype data centre all-optical switch, Sirius, presented at SIGCOMM 2020, in which the sub-nanosecond clock and data recovery locking time of clock phase caching was a key enabler of its high performance.

The single calibration approach to clock synchronisation assisted clock and data recovery using the low thermal sensitivity of hollow core fibre, investigated in collaboration with the Optoelectronics Research Centre, was published as a top-scored conference paper at ECOC 2019, followed by an invited, highly-scored journal paper in JLT in 2020. This work was also, to my and my coauthor's knowledge, the first demonstration of optical switching using hollow core fibre.

The analytical modelling of clock synchronisation assisted clock and data recovery established in this thesis, which explains why the approach works, is not yet published, and is intended to lead to a further one to two journal papers.

The work also led to two UK national competitions wins: 1) The Connected Nation Pioneers 2018 Competition, in which I was Overall Winner and Winner of the Intelligent Informatics category, against over 100 other PhD student competitors. 2) STEM for BRITAIN 2019, held at UK Parliament, in which I won Bronze in Engineering, against over 30 other junior researcher competitors in my category.

Clock synchronisation assisted clock and data recovery is also likely to have further applications beyond data centre optical switching, for instance in optical access networks. The distributed phase synchronisation enabled by the approach could also be of value in many applications that require synchronisation, such as quantum key distribution clock networks, and in the optical backbone supporting fifth-generation (5G) wireless networks.

### Acknowledgements

For many reasons, the last six years of my life have been exceedingly difficult. While that is true, the last six years of my life have also been highly rewarding, and highly fulfilling. Many difficult challenges were overcome in the process of studying for my PhD, both academic and personal, and there are many to whom I owe thanks.

For the last three years of my PhD, I have been supervised by Dr. Zhixin Liu. His extensive knowledge of optics and analog electronics, wealth of excellent general advice, and infectious enthusiasm for research, has been invaluable. I am delighted that many of the ideas and goals that we discussed together – some of them rather ambitious – did with time and a lot of effort come to fruition. I also thank Dr. Philip Watts, who supervised me for the first two years of my PhD. His expertise on optical switching got my project started, and I owe my FPGA programming expertise to him. Prof. Polina Bayvel, Prof. Izzat Darwazeh and Dr. Georgios Zervas also provided invaluable academic support and advice at many points throughout my project.

Microsoft Research Cambridge have given much to the project. In addition to supporting my PhD financially through the Microsoft Optics for the Cloud programme, their industrial perspective on data centre networks acted to strengthen the depth and impact of my project. Dr. Benn Thomsen, Dr. István Haller, Dr. Krzysztof Jozwik and Mr Hugh Williams all stand out, but I am particularly thankful for the academic advice, supervision and enthusiasm of Dr. Paolo Costa, closely followed by Dr. Hitesh Ballani, who have both particularly closely supported my PhD throughout. I am also grateful for the opportunity I was given to complete a 9-month internship at Microsoft Research Cambridge in 2016, which I thoroughly enjoyed.

The Optoelectronics Research Centre (ORC) at the University of Southampton allowed me to add a new dimension to my PhD by granting me the opportunity to investigate the impact of using their low thermal sensitivity hollow core fibre on clock synchronisation assisted clock and data recovery. The ORC also supported my PhD financially through the EPSRC Lightpipe Project. Dr. Yong Chen, Dr. Eric R. Numkam Fokua, Dr. Tom Bradley, Prof. Francesco Poletti and Prof. David J. Richardson all contributed, but I extend particular thanks to Prof. Radan Slavík for his academic advice, support and fantastic humour.

I also extend my appreciation to Inphi Corporation, who funded the first three years of my PhD through the UCL Impact Award. Mr Mike Harwood and Mr Andre Szczepanek provided excellent industrial advice and support throughout these first three years, and their extensive experience with designing electronic high-speed serial transceivers, along with their industrial view on data centre interconnects, was particularly valuable – and I also rather enjoyed the academic discussions assisted by the pints of cider they bought me at their excellent local pub in Northampton.

I have greatly enjoyed studying alongside my fellow PhD students and friends in the Optical Networks Group. In particular, (now) Dr. Paris Andreades, (now) Dr. Joshua Benjamin, (now) Dr. Thomas Gerard and Mr Ronit Sohanpal stand out. Our many discussions about optical interconnects have been highly stimulating, and it has been a pleasure to work together with them towards enabling optically-switched data centres.

Outside of work, the many board games evenings and other events that I attended (and helped organise, first as Society Treasurer for a year, and later as Webmaster for two years) at the UCL Science-Fiction and Fantasy Society have contributed much to keeping me sane during stressful times. There are many names – too many to include here – but I am particularly thankful for the support of Miss Andrea Petrou, who was instrumental in helping me get through one of the most difficult periods of my PhD.

I am, as always, grateful for the love and support of my family: Mum, Dad, Laif, Vena, Grandma Cats and Grandma Dogs. They, as they always have done, helped me to succeed in my pursuits, both academic and personal, during my PhD. There have been many very difficult points during the last six years, and without their support, it is likely that I would not have completed my PhD. I do wish that my maternal grandmother, nicknamed Grandma Cats within my family, who died during the second year of my PhD, had lived to see me fulfil my dream of contributing something new for science and engineering – to place my brick in the wall – but nonetheless, I am sure that she, like the rest of my family, would have been proud of me.

Finally, I would like to thank my partner, Elisabeth (E.V.V.), who has been consistently by my side, and supported me, during the latter part of my PhD. From exploring London, to doing photography in the Scottish Highlands, to writing our PhD theses together under the COVID-19 lockdown, she has made my life, and by extension also my work, brighter, and better.

## **Table of Contents**

| Abst | ract                                                           | 5  |

|------|----------------------------------------------------------------|----|

| Impa | act Statement                                                  | Ć  |

| Ackı | nowledgements                                                  | 8  |

| List | of Figures                                                     | 16 |

| List | of Tables                                                      | 22 |

| List | of Terms and Abbreviations                                     | 23 |

| List | of Symbols                                                     | 28 |

| 1    | Introduction                                                   | 35 |

| 1.1  | Scope of the Thesis                                            | 35 |

|      | 1.1.1 Clock and Data Recovery (CDR) Locking Time               | 38 |

|      | 1.1.2 Impact of CDR Locking Time on Optical Switch Performance | 39 |

| 1.2  | Tools used in the Thesis                                       | 41 |

| 1.3  | Chapter Overview                                               | 42 |

| 1.4  | Key Contributions                                              | 44 |

| 1.5  | List of Publications                                           | 46 |

| 2    | The Data Centre Networking Environment                         | 49 |

| 2.1  | Introduction                                                   | 49 |

| 2.2  | Electronically-Switched Data Centre Networks                   | 49 |

| 2.3  | Priorities and Properties of Data Centre Networks              | 53 |

| 2.4  | Data Centre Optical Transmission                               | 54 |

| 2.5  | Optically-Switched Data Centre Networks                        | 57 |

| 2.6  | Comparison of Data Centre Network Approaches                   | 60 |

| 2.7  | Data Centre Temperature Variation                              | 62 |

| 3   | Burst  | -Mode Clock and Data Recovery (CDR),                              |     |

|-----|--------|-------------------------------------------------------------------|-----|

|     | Clock  | Synchronisation Approaches and Proposed Approach                  | 65  |

| 3.1 | Requi  | rements for Burst-Mode CDR Circuits                               | 65  |

| 3.2 | Burst- | Mode CDR Approaches                                               | 66  |

|     | 3.2.1  | Gated-Voltage Controlled Oscillator                               | 66  |

|     | 3.2.2  | Oversampling                                                      | 68  |

|     | 3.2.3  | Digital Phase Interpolator                                        | 69  |

|     | 3.2.4  | Summary and Limitations of Existing Approaches                    | 71  |

| 3.3 | Clock  | Synchronisation Approaches in Optical Networks                    | 73  |

|     | 3.3.1  | Optical Time Division Multiplexing                                | 74  |

|     | 3.3.2  | Synchronous Telecommunication Standards                           | 75  |

|     | 3.3.3  | Precision Time Protocol (PDP) and Datacentre Time Protocol (DTP)  | 77  |

|     | 3.3.4  | White Rabbit                                                      | 78  |

| 3.4 | Propo  | sed Approach: Clock Synchronisation Assisted                      |     |

|     | Clock  | and Data Recovery (CSA-CDR)                                       | 79  |

| 4   | Single | e Calibration CSA-CDR                                             |     |

|     | Part 1 | : Without Packet Clock Phase Tracking                             | 81  |

| 4.1 | Introd | uction                                                            | 81  |

| 4.2 | Impac  | et of Data Centre Environmental Conditions                        | 82  |

| 4.3 | Analy  | tical Modelling of Bit Error Probability                          |     |

|     | Degra  | dation from Clock Phase Shift                                     | 82  |

|     | 4.3.1  | Sources of Signal Impairment in Intra-Data Centre NRZ-OOK         |     |

|     |        | Transmission                                                      | 83  |

|     | 4.3.2  | Effect of Temperature on Fibre Time-of-Flight and Clock Phase .   | 85  |

|     | 4.3.3  | Effect of Fibre Topology on Clock Phase Offset                    | 88  |

|     | 4.3.4  | Gaussian NRZ Pulse Shape                                          | 90  |

|     | 4.3.5  | NRZ-OOK Photocurrent Pulse Shape Bit Error Probability            | 97  |

|     | 4.3.6  | PIN Photoreceiver NRZ-OOK Photocurrent Pulse Shape                | 99  |

|     | 4.3.7  | PIN Photoreceiver NRZ-OOK Photocurrent Noise                      | 101 |

|     | 4.3.8  | NRZ-OOK Photocurrent Pulse Shape Bit Error Probability            | 107 |

|     | 4.3.9  | Effect of Jitter on Clock Phase Shifted NRZ-OOK Error Probability | 111 |

| 4 4 | Analy  | tical Modelling of Power Penalty                                  | 116 |

Table of Contents

|     | 4.4.1  | Effect of Clock Phase Offset (With and Without Clock Jitter)       | 116 |

|-----|--------|--------------------------------------------------------------------|-----|

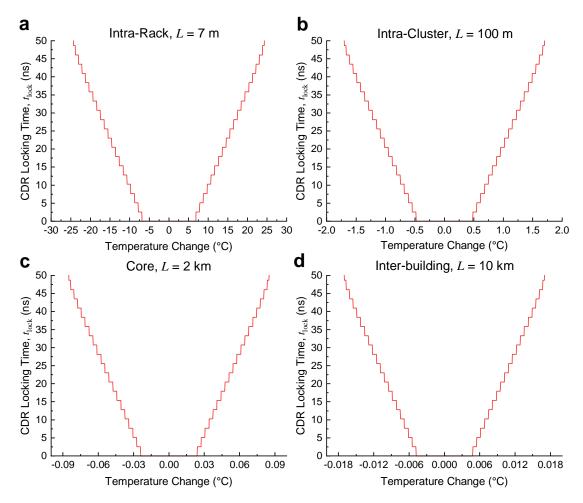

|     | 4.4.2  | Effect of Temperature Variation at Different Data Centre Distances | 120 |

|     | 4.4.3  | Summary of Analytical Modelling Assumptions                        | 123 |

| 4.5 | Discu  | ssion                                                              | 124 |

| 4.6 | Contri | ibution Statement                                                  | 124 |

| 5   | Single | e Calibration CSA-CDR                                              |     |

|     | Part 2 | 2: With Packet Clock Phase Tracking                                | 125 |

| 5.1 | Introd | uction                                                             | 125 |

| 5.2 | CDR    | Locking Process in a Burst-Mode Receiver                           | 126 |

| 5.3 | Link I | Performance Metrics                                                | 127 |

| 5.4 | Analy  | tical Modelling of the Evolution of                                |     |

|     | Bit Er | ror Probability during CDR Locking                                 | 128 |

|     | 5.4.1  | Clock Phase Error of a Phase Interpolator CDR Circuit              | 128 |

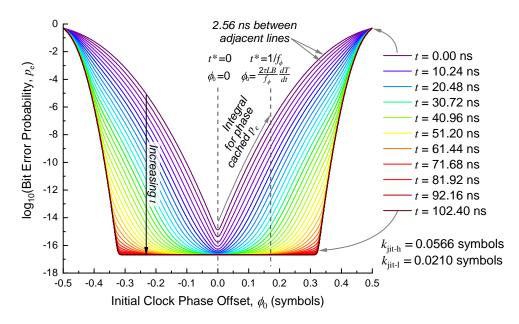

|     | 5.4.2  | Evolution of Clock Phase Offset within Received Data Packets       | 130 |

|     | 5.4.3  | Evolution of Bit Error Probability within Received Data Packets    |     |

|     |        | (Not Including the Impact of Jitter on Clock Phase)                | 134 |

|     | 5.4.4  | Evolution of Bit Error Probability within Received Data Packets    |     |

|     |        | (Including the Impact of Jitter on Clock Phase)                    | 138 |

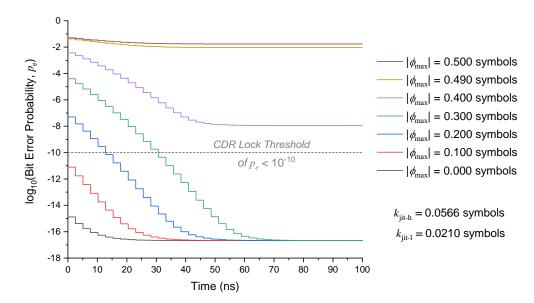

| 5.5 | Analy  | tical Modelling of CDR Locking Time                                | 146 |

|     | 5.5.1  | Impact of Initial Clock Phase Offset                               | 146 |

|     | 5.5.2  | Impact of Data Centre Temperature Change                           | 147 |

|     | 5.5.3  | Summary of Analytical Modelling Assumptions                        | 149 |

| 5.6 | Discu  | ssion                                                              | 150 |

| 5.7 | Contri | ibution Statement                                                  | 150 |

| 6   | Clock  | Phase Caching for                                                  |     |

|     | Sub-N  | Nanosecond CDR Locking Time                                        | 151 |

| 6.1 | Introd | uction                                                             | 151 |

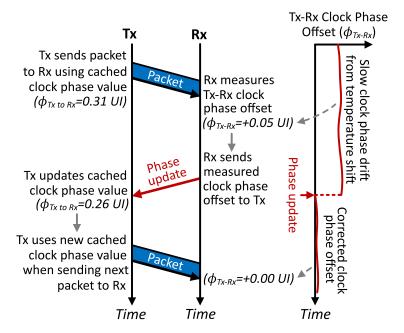

| 6.2 | Clock  | Phase Caching Concept                                              | 152 |

|     | 6.2.1  | Important Considerations for Implementing Clock Phase Caching      | 153 |

| 6.3 | Analy  | tical Modelling of Clock Phase Caching                             | 153 |

|     | 631    | Clock Phase Cached Rit Error Probability                           | 153 |

|     | 6.3.2  | CDR Locking Time in a Clock Phase Cached Receiver              | 158 |

|-----|--------|----------------------------------------------------------------|-----|

|     | 6.3.3  | Effect of Rate-of-Change of Temperature on CDR Locking Time .  | 159 |

|     | 6.3.4  | Effect of Sampling Clock Gaussian Jitter on CDR Locking Time . | 160 |

|     | 6.3.5  | Minimum Required Rate of Clock Phase Updates                   | 161 |

|     | 6.3.6  | Throughput Overhead                                            | 162 |

|     | 6.3.7  | Theoretical Viability                                          | 163 |

|     | 6.3.8  | Summary of Analytical Modelling Assumptions                    | 163 |

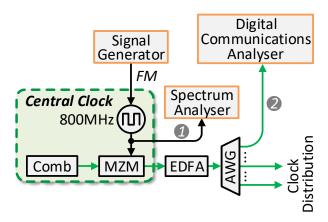

| 6.4 | Proof- | of-Concept Experimental Setup                                  | 164 |

|     | 6.4.1  | Data Packet Transmission and Optical Switch Implementation     | 164 |

|     | 6.4.2  | Establishment of Optical Clock Frequency Synchronisation       | 165 |

| 6.5 | Clock  | Phase Caching Experimental Implementation                      | 166 |

|     | 6.5.1  | Measurement of Transmitter to Receiver Clock Phase Offset      | 166 |

|     | 6.5.2  | Implementation of Transmitter Clock Phase Shift                | 167 |

|     | 6.5.3  | Data Packet Structure and Measurement of CDR Locking Time      | 169 |

| 6.6 | Emula  | ation of Data Centre Environmental Conditions                  | 171 |

|     | 6.6.1  | Optical Fibre Length                                           | 171 |

|     | 6.6.2  | Rate-of-Change of Temperature                                  | 171 |

|     | 6.6.3  | Clock Jitter Generation and Measurement                        | 172 |

| 6.7 | Exper  | imental Results                                                | 173 |

|     | 6.7.1  | Tolerance to Clock Phase Offset                                | 173 |

|     | 6.7.2  | Long-Term Stability                                            | 174 |

|     | 6.7.3  | Resilience to Rapid Temperature Change                         | 175 |

|     | 6.7.4  | Tolerance to Rate-of-Change of Temperature                     | 177 |

|     | 6.7.5  | Tolerance to Source Clock Jitter                               | 179 |

|     | 6.7.6  | Measurement of Clock Phased Cached Receiver Jitter             | 181 |

| 6.8 | Estima | ated Scalability of Clock Phase Caching                        | 182 |

| 6.9 | Contri | bution Statement                                               | 184 |

| 7   | Hollo  | w Core Fibre Synchronisation                                   |     |

|     | for Su | ab-Nanosecond CDR Locking Time                                 | 185 |

| 7.1 | Introd | uction                                                         | 185 |

| 7.2 | Using  | Low-TDC Fibre with Single Calibration CSA-CDR                  | 186 |

| 73  | Therm  | nal Properties of Hollow Core Fibre                            | 187 |

Table of Contents

| 7.4   | Analy   | tical Modelling of Single Calibration                          |       |

|-------|---------|----------------------------------------------------------------|-------|

|       | CSA-    | CDR with Hollow Core Fibre Transmission                        | . 189 |

|       | 7.4.1   | Optical Power Penalty from Single Calibration CSA-CDR          |       |

|       |         | Without Packet Clock Phase Tracking                            | . 189 |

|       | 7.4.2   | CDR Locking Time using Single Calibration CSA-CDR With         |       |

|       |         | Packet Clock Phase Tracking                                    | . 191 |

|       | 7.4.3   | Theoretical Viability of Single Calibration CSA-CDR Approaches |       |

|       |         | using Hollow Core Fibre Transmission                           | . 191 |

| 7.5   | Exper   | imental Investigation of Single Calibration                    |       |

|       | CSA-    | CDR Techniques with Hollow Core Fibre                          | . 193 |

|       | 7.5.1   | Experimental Setup                                             | . 193 |

|       | 7.5.2   | Experimental Results                                           | . 196 |

| 7.6   | Discus  | ssion                                                          | . 199 |

| 7.7   | Contri  | ibution Statement                                              | . 202 |

| 8     | Concl   | lusions and Future Work                                        | 203   |

| 8.1   | Concl   | usions                                                         | . 203 |

| 8.2   | Future  | e Work                                                         | . 205 |

|       | 8.2.1   | Supporting Longer Distance Scale Applications                  | . 205 |

|       | 8.2.2   | Supporting Higher Symbol Rates and Higher Order Modulation     |       |

|       |         | Formats                                                        | . 207 |

|       | 8.2.3   | Time Synchronisation                                           | . 208 |

| Bibli | ography | y                                                              | 209   |

| Appe  | endix A | Mathematical Derivations                                       | 225   |

| A.1   | Gauss   | ian Filter Impulse Response                                    | . 226 |

| A.2   | Confi   | rming Normalisation of the Gaussian Impulse Filter             | . 227 |

| A.3   | Gauss   | ian NRZ Pulse Shape                                            | . 228 |

| A.4   | Clock   | Jittered Alexander Phase Detector                              |       |

|       | Phase   | Error Expectation                                              | . 230 |

| A.5   | Contri  | ibution Statement                                              | . 233 |

| Appen | ndix B Clock Synchronisation Assisted          |    |

|-------|------------------------------------------------|----|

|       | Clock and Data Recovery FPGA Hardware Design 2 | 35 |

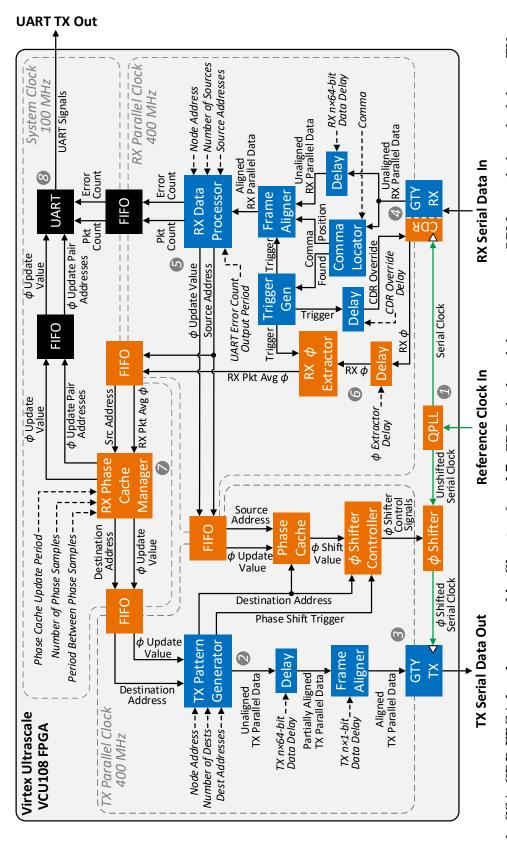

| B.1   | Overview of FPGA Hardware Design               | 35 |

| B.2   | Contribution Statement                         | 40 |

| Appen | ndix C Photographs 2                           | 41 |

# **List of Figures**

| 1.1 | Data centre electronically-switched and all-optically-switched network  |    |

|-----|-------------------------------------------------------------------------|----|

|     | architectures                                                           | 36 |

| 1.2 | The four components of overall switching time for packets arriving at a |    |

|     | receiver connected to an optical switch.                                | 37 |

| 1.3 | Clock recovery in a generalised serial transmission link                | 38 |

| 1.4 | Recovery of the embedded transmitter clock from received data           | 38 |

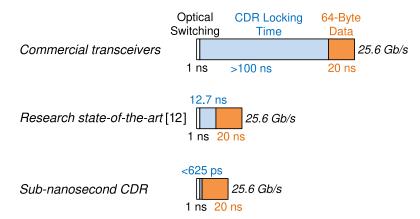

| 1.5 | The proportion of receiver time used by different clock and data        |    |

|     | recovery (CDR) techniques when receiving minimum size (64-Byte)         |    |

|     | data packets                                                            | 40 |

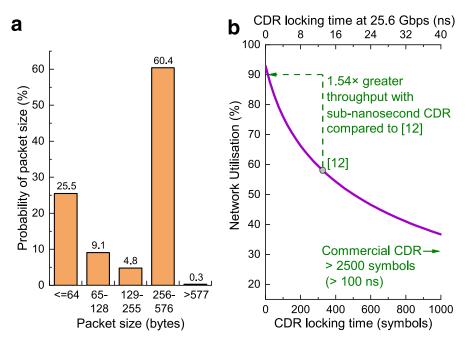

| 1.6 | Impact of CDR locking time on optical switch performance when           |    |

|     | handling real data centre traffic                                       | 41 |

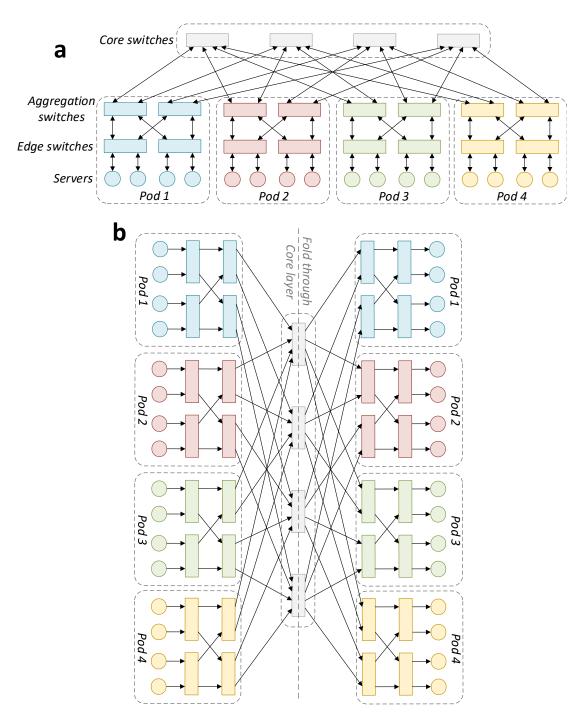

| 2.1 | Example folded-Clos data centre network topology used for               |    |

|     | electronically-switched data centre networking                          | 51 |

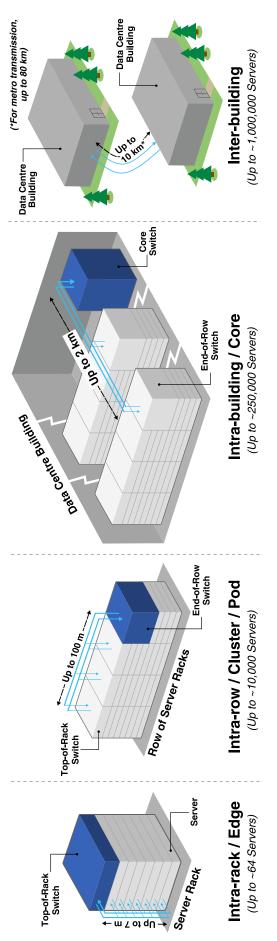

| 2.2 | Standardised data transmission scales in the data centre environment    | 55 |

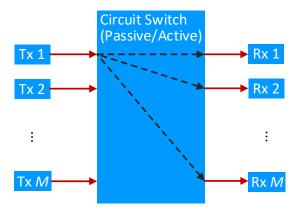

| 2.3 | Principle of optical circuit switching                                  | 58 |

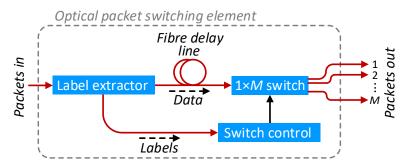

| 2.4 | Principle of optical packet switching                                   | 59 |

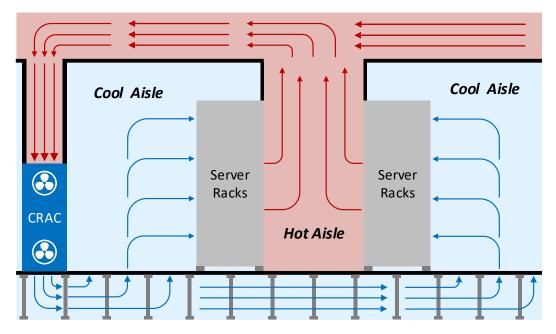

| 2.5 | Hot aisle containment: a typical modern data centre cooling topology    | 62 |

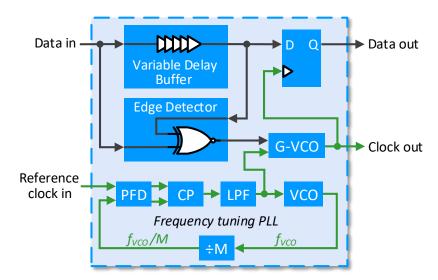

| 3.1 | Gated voltage controlled oscillator (GVCO) CDR architecture             | 66 |

| 3.2 | Oversampling CDR architecture                                           | 68 |

| 3.3 | Phase interpolator (PI) CDR architecture                                | 70 |

| 3.4 | Bang-bang phase detector (BB-PD) metastability due to jitter, a key     |    |

|     | limiter of CDR locking time in digital PI CDRs                          | 70 |

| 3.5 | Networked Optical time division multiplexing (OTDM) experiment          | 75 |

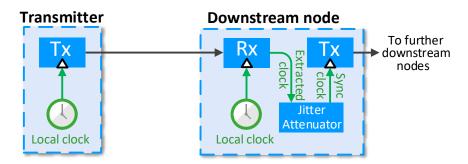

| 3.6  | Distribution of a clock through one hop of a Synchronous Optical              |    |

|------|-------------------------------------------------------------------------------|----|

|      | Networking (SONET) / Synchronous Digital Hierarchy (SDH) /                    |    |

|      | Synchronous Ethernet (Sync-E) clock tree                                      | 76 |

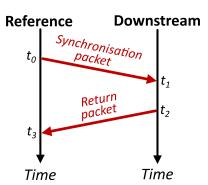

| 3.7  | Concept of time-of-flight measurement with Precision Time Protocol            |    |

|      | (PTP) and Datacentre Time Protocol (DTP)                                      | 77 |

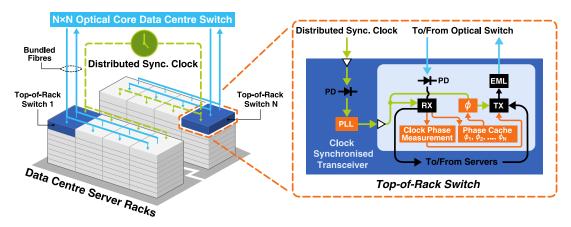

| 3.8  | Clock synchronised optical switch architecture with clock                     |    |

|      | synchronisation assisted clock and data recovery (CSA-CDR)                    | 80 |

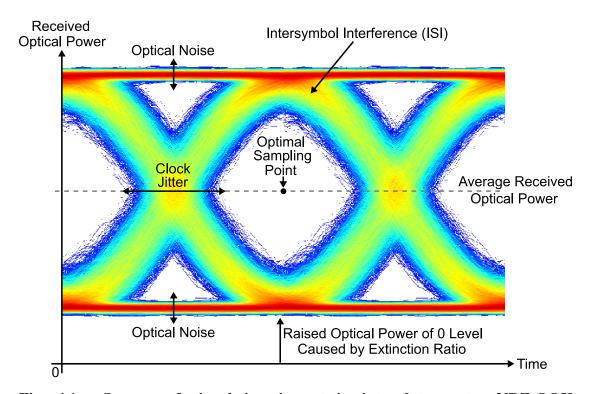

| 4.1  | Sources of signal impairment in intra-data centre non return to zero on       |    |

|      | off keying (NRZ-OOK) transmission                                             | 84 |

| 4.2  | Contribution of fibre refractive index increase and fibre expansion to        |    |

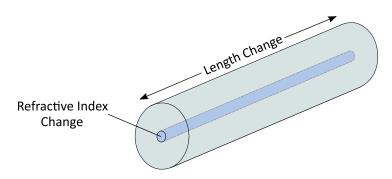

|      | increasing fibre time-of-flight with temperature                              | 85 |

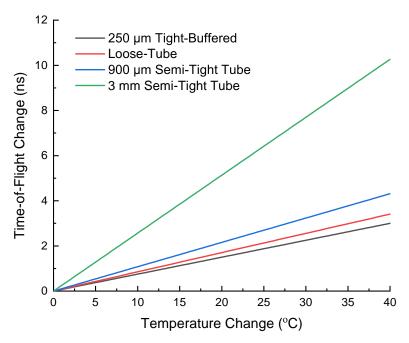

| 4.3  | Time-of-flight changes experienced by 2 km single-mode fibre (SMF-            |    |

|      | 28) fibre with change of temperature, for a variety of typical fibre buffer   |    |

|      | types used in a data centre environment                                       | 87 |

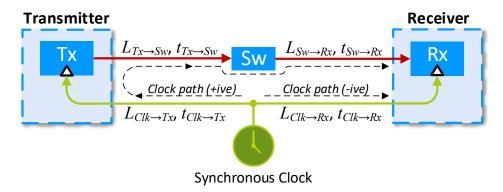

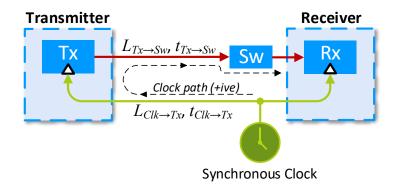

| 4.4  | A single pair of nodes, a transmitter and a receiver, synchronised by a       |    |

|      | central clock source and interconnected through an optical switch             | 88 |

| 4.5  | Worst-case clock phase shift from co-location of the synchronous clock,       |    |

|      | the receiver and the switch                                                   | 89 |

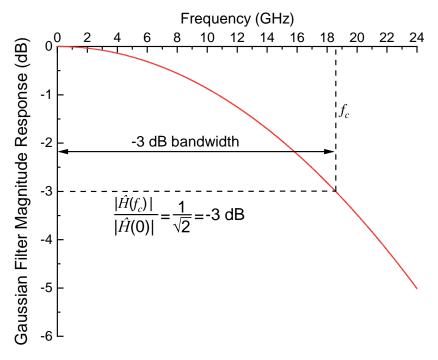

| 4.6  | Gaussian filter magnitude response in the frequency domain                    | 91 |

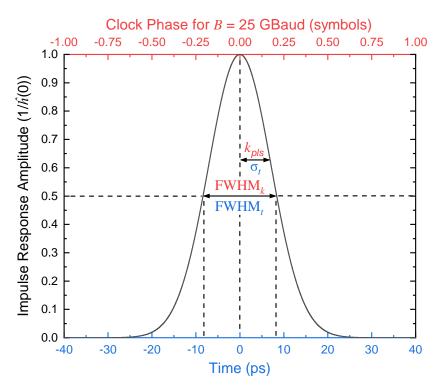

| 4.7  | Gaussian filter impulse response                                              | 93 |

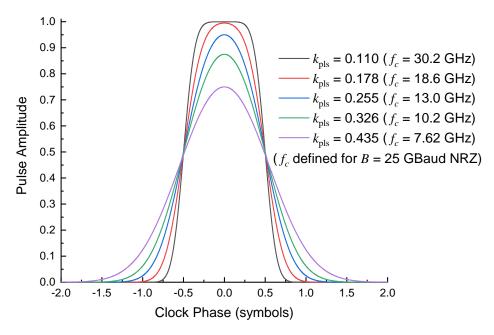

| 4.8  | Gaussian NRZ pulse shape                                                      | 94 |

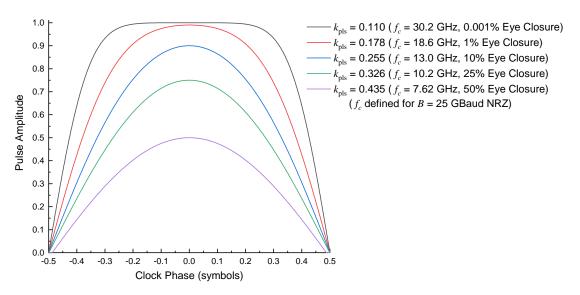

| 4.9  | Gaussian NRZ eye height                                                       | 95 |

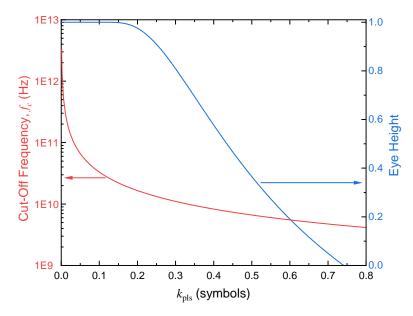

| 4.10 | Peak Gaussian NRZ eye height and cut-off frequency                            | 96 |

| 4.11 | Example pair of NRZ-OOK modulated positive and negative                       |    |

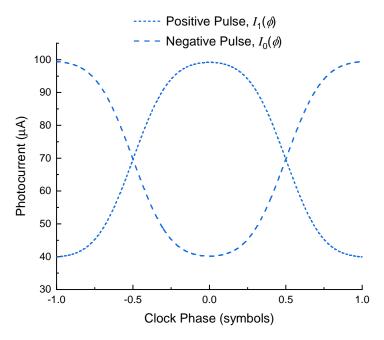

|      | photocurrent pulses                                                           | 01 |

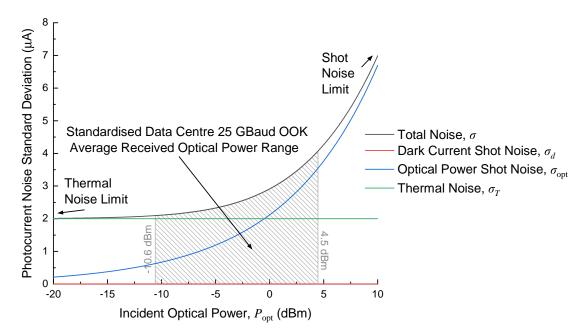

| 4.12 | Total p-i-n junction (PIN) photocurrent noise, as well as its contributors. 1 | 04 |

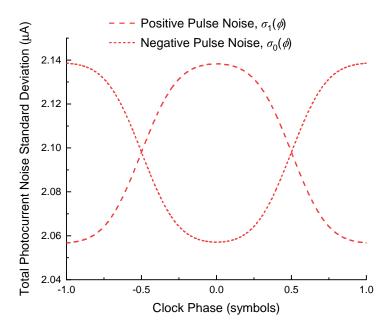

| 4.13 | Standard deviation of the total noise for the example pair of NRZ-OOK         |    |

|      | modulated positive and negative photocurrent pulses shown in Figure 4.11.1    | 06 |

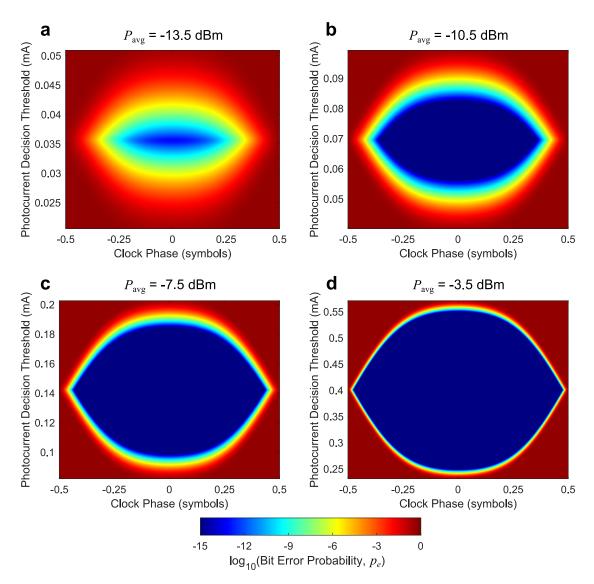

| 4.14 | Analytically modelled receiver eye diagrams                                   | 08 |

| 4.15 | On-off keying (OOK) error probability, $p_e$ , as a function of clock phase   |    |

|      | offset                                                                        | 10 |

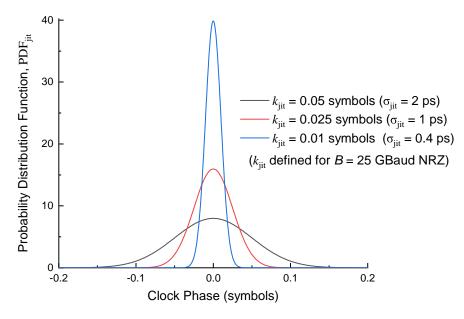

| 4 16 | Probability distribution function of Gaussian (random) iitter                 | 12 |

18 List of Figures

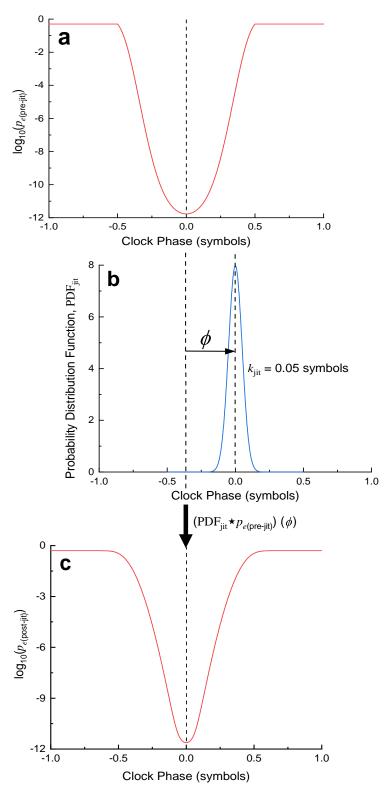

| 4.17 | Cross-correlation between pulse shape and jitter                                    | 13 |

|------|-------------------------------------------------------------------------------------|----|

| 4.18 | Error probability degradation resulting from jitter of the sampling clock           |    |

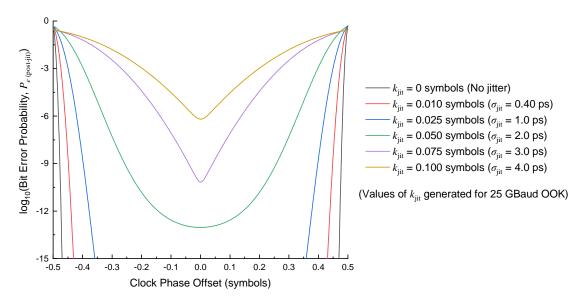

|      | position                                                                            | 14 |

| 4.19 | Analytically modelled receiver eye diagrams showing error probability               |    |

|      | after applying jitter, $p_{e(\text{post-jit})}$                                     | 15 |

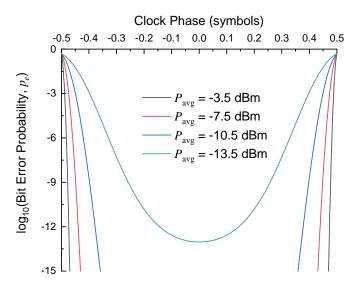

| 4.20 | OOK error probability, $p_e$ , resulting from a Gaussian impulse response,          |    |

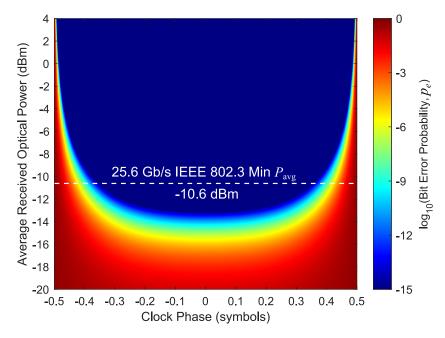

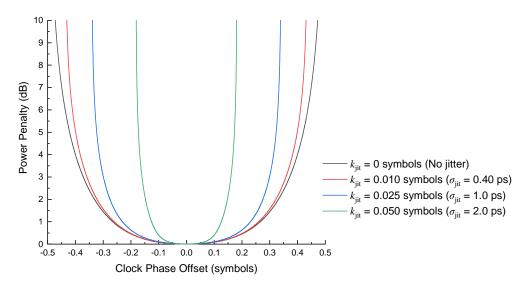

|      | calculated against clock phase offset, $\phi$                                       | 17 |

| 4.21 | Power penalty incurred from operating away from the optimum                         |    |

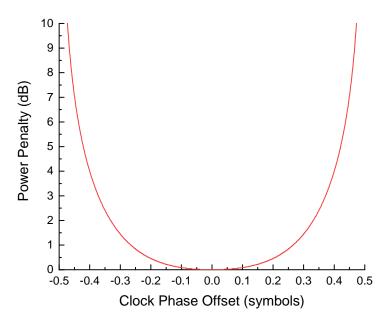

|      | sampling point within the Gaussian OOK signal                                       | 17 |

| 4.22 | Increase in power penalty for a Gaussian NRZ-OOK signal that                        |    |

|      | includes clock jitter, versus the corresponding case without jitter                 |    |

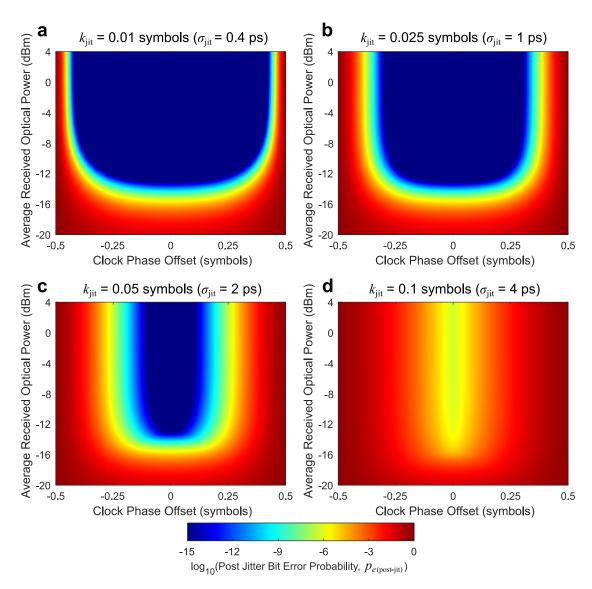

|      | shown in Figure 4.21                                                                | 18 |

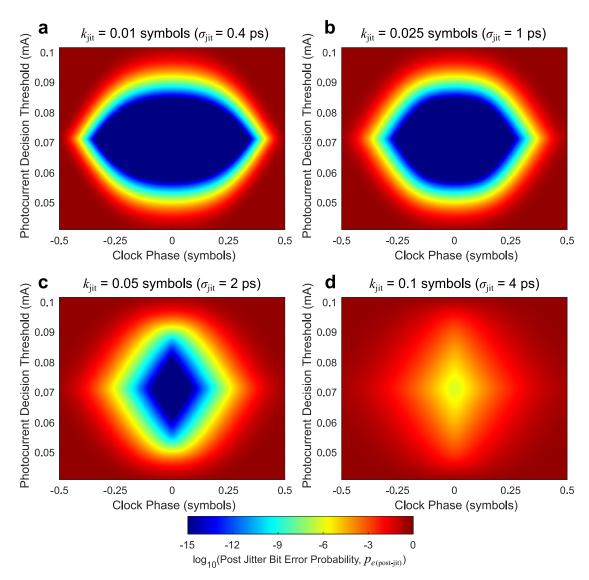

| 4.23 | OOK error probability, $p_{e(\text{post-jit})}$ , as a function of average received |    |

|      | optical power and clock phase offset, including the effect of jitter 1              | 19 |

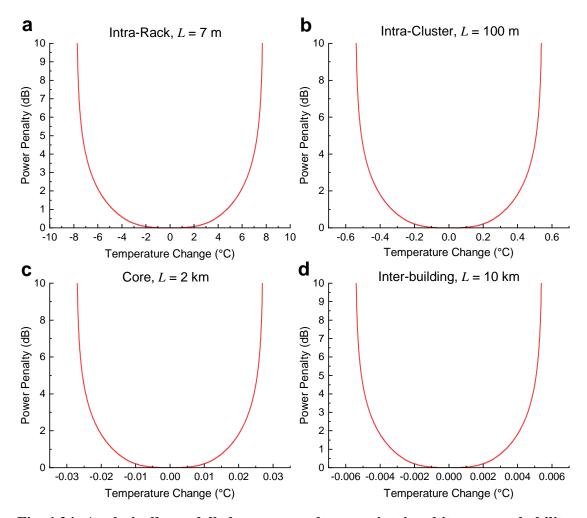

| 4.24 | Analytically modelled power penalty to maintain a bit error probability             |    |

|      | of $10^{-10}$ at a receiver, resulting from temperature change in an optically-     |    |

|      | switched network, operating with single calibration CSA-CDR without                 |    |

|      | packet clock phase tracking                                                         | 22 |

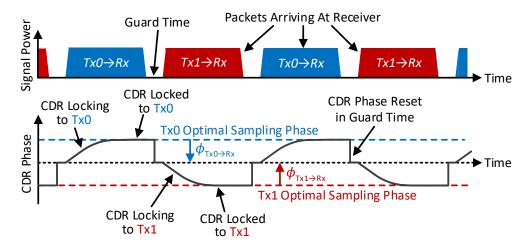

| 5.1  | CDR locking to incoming data packets arriving at a receiver, Rx, from               |    |

|      | two different transmitters, Tx0 and Tx1                                             | 26 |

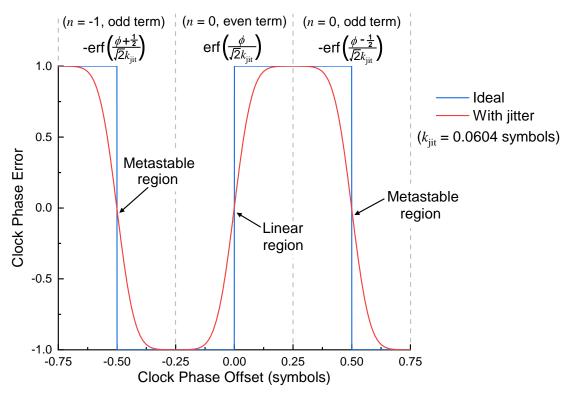

| 5.2  | Bang-bang phase detector phase error                                                | 29 |

| 5.3  | Comparison between the linear approximation to clock phase error and                |    |

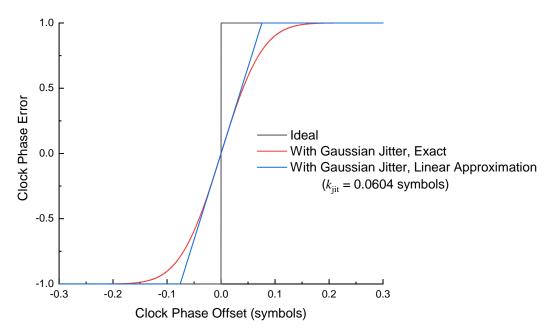

|      | a calculation including jitter                                                      | 32 |

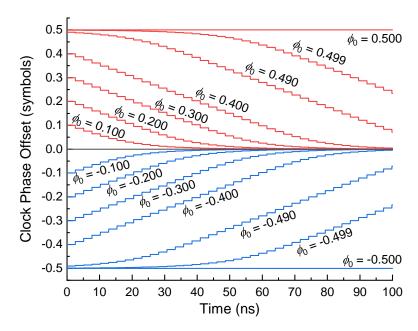

| 5.4  | Clock phase offset as a function of time since the beginning of packet              |    |

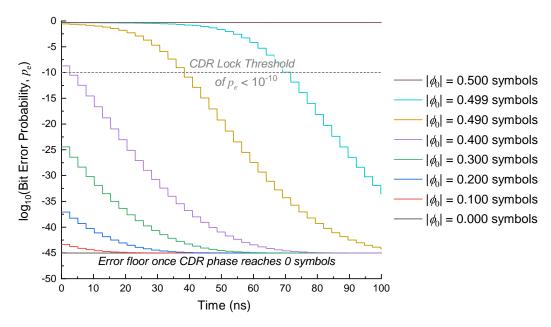

|      | reception, obtained numerically using Equation 5.9                                  | 34 |

| 5.5  | Bit error probability as a function of time since the beginning of packet           |    |

|      | reception                                                                           | 36 |

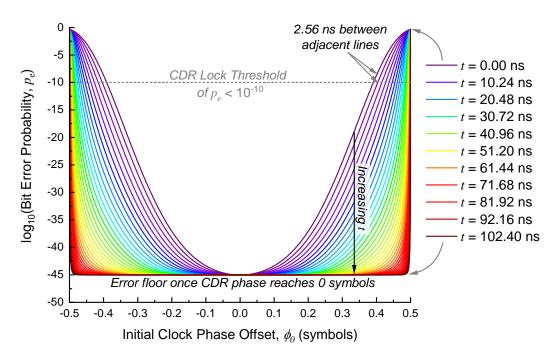

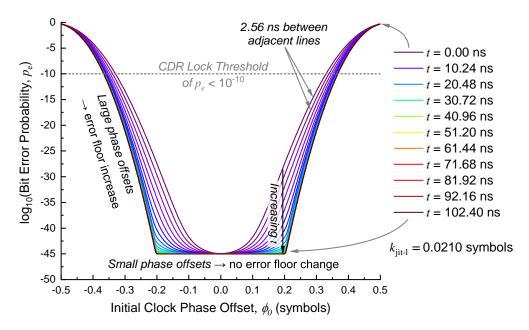

| 5.6  | Bit error probability as a function of initial clock phase offset                   | 37 |

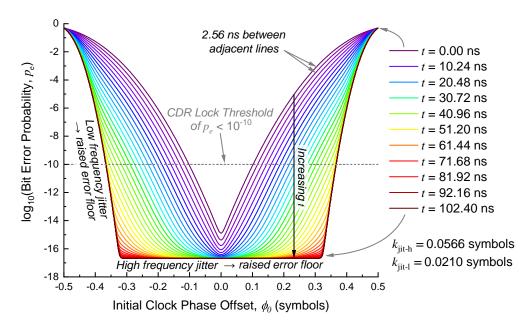

| 5.7  | Bit error probability with high-frequency jitter accounted for, as a                |    |

|      | function of time since the beginning of packet reception                            | 40 |

| 5.8  | Bit error probability with high-frequency jitter accounted for, as a                |    |

|      | function of initial clock phase offset                                              | 40 |

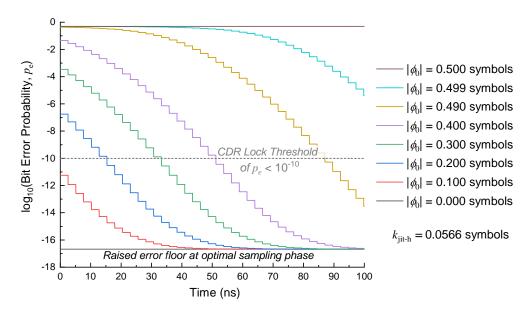

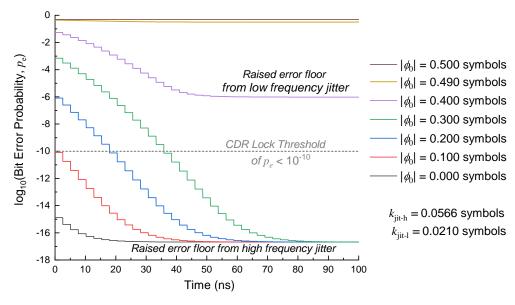

| 5.9  | Bit error probability with low-frequency jitter accounted for, as a       |

|------|---------------------------------------------------------------------------|

|      | function of time since the beginning of packet reception                  |

| 5.10 | Bit error probability with low-frequency jitter accounted for, as a       |

|      | function of initial clock phase offset                                    |

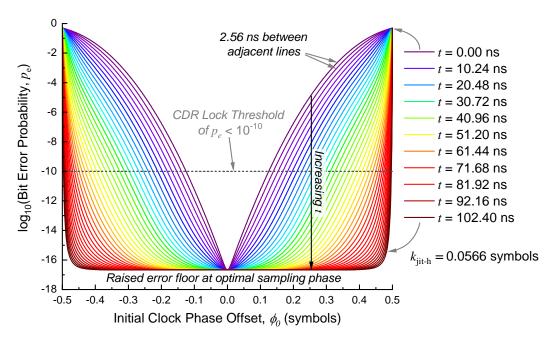

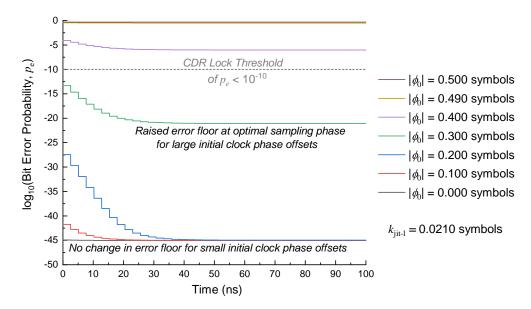

| 5.11 | Bit error probability with low-frequency and high-frequency jitter        |

|      | accounted for, as a function of time since the beginning of packet        |

|      | reception                                                                 |

| 5.12 | Bit error probability with low-frequency and high-frequency jitter        |

|      | accounted for, as a function of initial clock phase offset                |

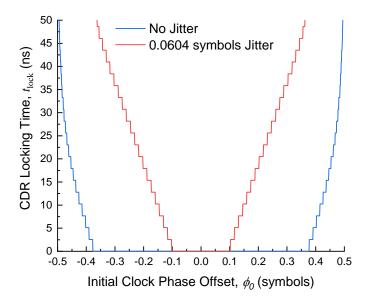

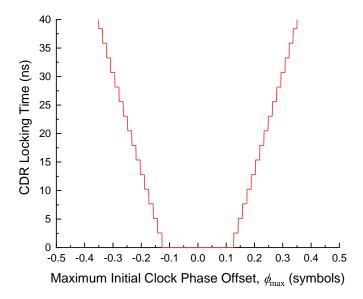

| 5.13 | CDR locking time against initial clock phase offset, for both an ideal    |

|      | case without clock jitter, and a practical case where significant clock   |

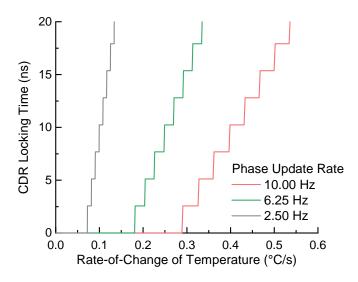

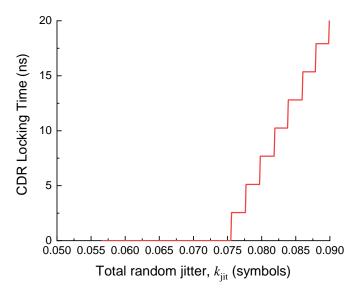

|      | jitter is present                                                         |

| 5.14 | CDR locking time against temperature change since clock phase             |

|      | calibration, including the impact of high and low frequency jitter 148    |

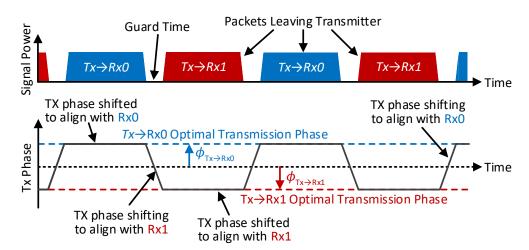

| 6.1  | Operational principle of clock phase caching, showing one clock phase     |

|      | update for one transmitter-receiver pair                                  |

| 6.2  | Illustration of the integrals used to evaluate bit error probability in a |

|      | clock phase cached receiver                                               |

| 6.3  | Bit error probability in a clock phase cached receiver, as a function of  |

|      | time since the beginning of packet reception                              |

| 6.4  | Bit error probability in a clock phase cached receiver, as a function of  |

|      | maximum initial clock phase offset                                        |

| 6.5  | Clock and data recovery locking time in a clock phase cached receiver,    |

|      | as a function of maximum initial clock phase offset                       |

| 6.6  | CDR locking time as a function of rate of temperature and clock phase     |

|      | updates in a clock phase cached receiver                                  |

| 6.7  | Clock and data recovery locking time in a clock phase cached receiver,    |

|      | as a function of total jitter                                             |

| 6.8  | Proof-of-concept experimental demonstration of clock phase caching        |

|      | operating on a 2-to-1 optical switch                                      |

| 6.9  | Transmitter clock phase shift at a transmitter, Tx, to align packets with |

|      | the different reference clocks of two receivers, Rx0 and Rx1 167          |

20 List of Figures

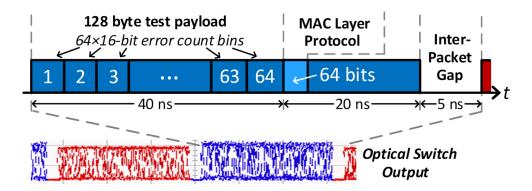

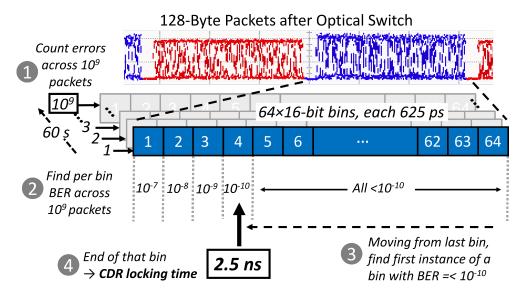

| 6.10 | The structure of the packets used in the clock phase caching proof-of-          |     |

|------|---------------------------------------------------------------------------------|-----|

|      | concept experiment                                                              | 169 |

| 6.11 | The process used to measure CDR locking time in the clock phase                 |     |

|      | caching proof-of-concept experiment                                             | 170 |

| 6.12 | Clock jitter generation and measurement                                         | 172 |

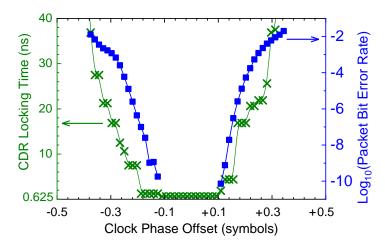

| 6.13 | Impact of clock phase offset on CDR locking time and bit error rate             |     |

|      | (BER) under steady state temperature                                            | 173 |

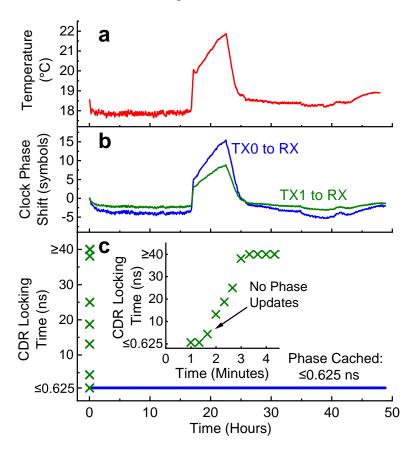

| 6.14 | Stability of clock phase caching over 48 hours of measurement                   | 174 |

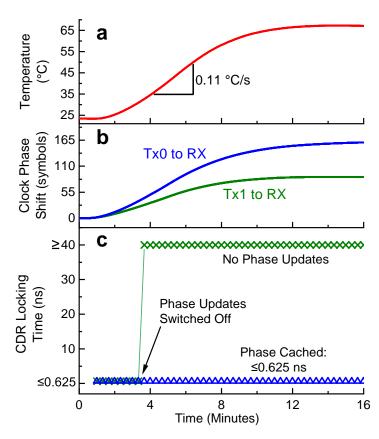

| 6.15 | Stability of clock phase caching under a rapid 0.11 °C/s rate of                |     |

|      | temperature change                                                              | 176 |

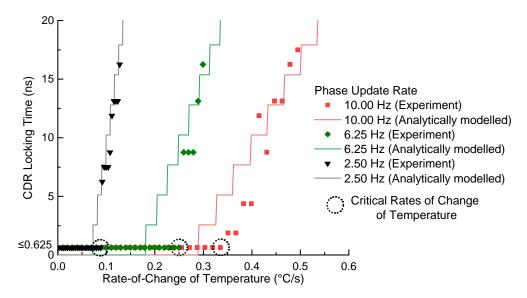

| 6.16 | Impact of rate-of-change of temperature on clock phase caching                  | 178 |

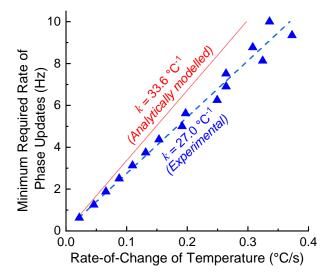

| 6.17 | Minimum required rate of clock phase updates to achieve under 625 ps            |     |

|      | (under 16 symbols) CDR locking time for different rates of temperature          |     |

|      | change across 2 km of SMF-28 clock fibre and 2 km of SMF-28 data                |     |

|      | fibre                                                                           | 178 |

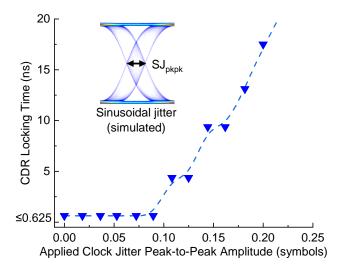

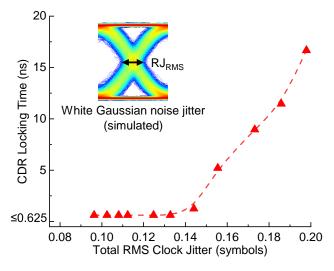

| 6.18 | Impact of 1 MHz sinusoidal jitter on CDR locking time                           | 180 |

| 6.19 | Impact of white Gaussian noise jitter on CDR locking time                       | 180 |

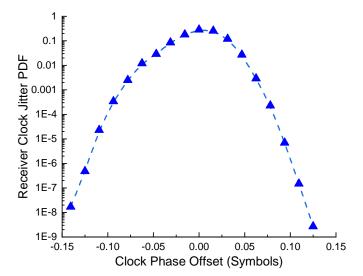

| 6.20 | Receiver CDR recorded clock phase offset value distribution                     | 181 |

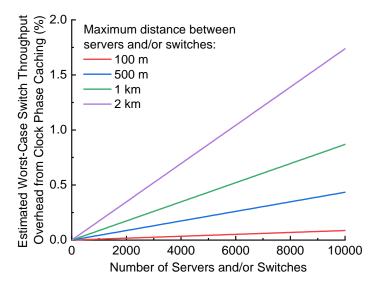

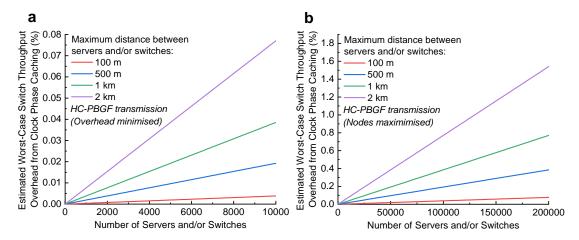

| 6.21 | Estimated worst-case optical switch overhead from clock phase caching.          | 183 |

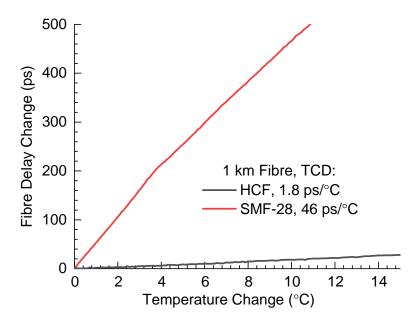

| 7.1  | Measured change of delay versus temperature change for a 1550 nm                |     |

|      | signal propagating through 1 km lengths of SMF-28 and hollow core               |     |

|      | fibre (HCF)                                                                     | 188 |

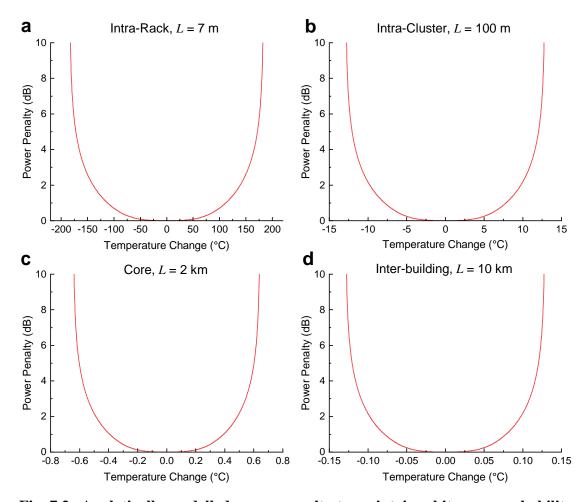

| 7.2  | Analytically modelled power penalty to maintain a bit error probability         |     |

|      | of $10^{-10}$ at a receiver, resulting from temperature change in an optically- |     |

|      | switched network, operating with single calibration CSA-CDR without             |     |

|      | packet clock phase tracking, with HCF clock and data transmission               | 190 |

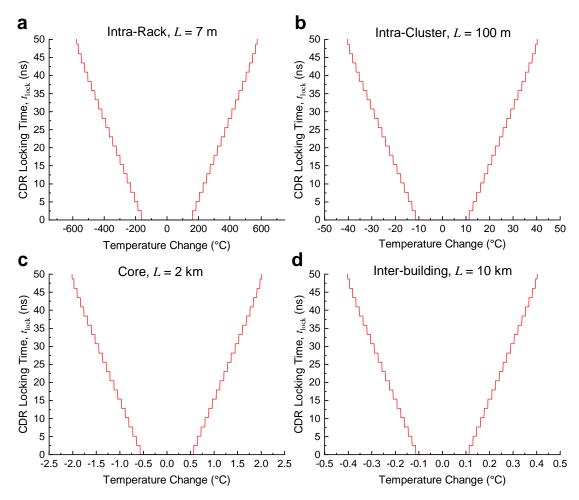

| 7.3  | CDR locking time against temperature change since clock phase                   |     |

|      | calibration, with HCF clock and data transmission                               | 192 |

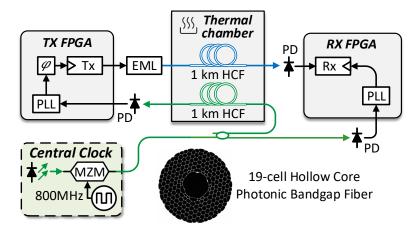

| 7.4  | Synchronous hollow-core photonic bandgap fibre (HC-PBGF)                        |     |

|      | point-to-point transmission experiment to investigate single calibration        |     |

|      | CSA-CDR without packet clock phase tracking                                     | 194 |

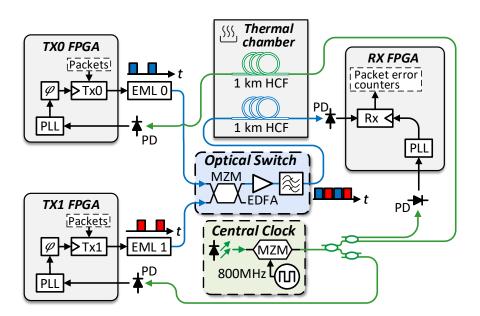

| 7.5 | Synchronous HC-PBGF 2×1 optical switching experimental setup to             |

|-----|-----------------------------------------------------------------------------|

|     | investigate single calibration CSA-CDR with packet clock phase tracking.195 |

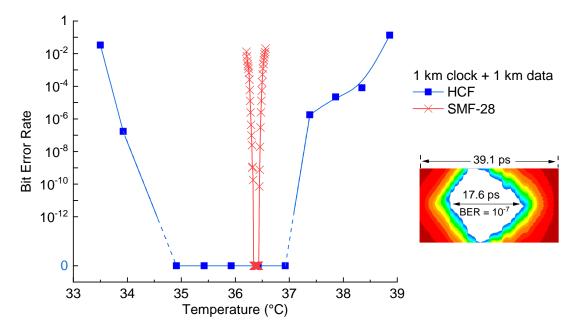

| 7.6 | Impact of temperature variation on the performance of a synchronous         |

|     | HC-PBGF point-to-point transmission system with single calibration          |

|     | CSA-CDR with packet clock phase tracking                                    |

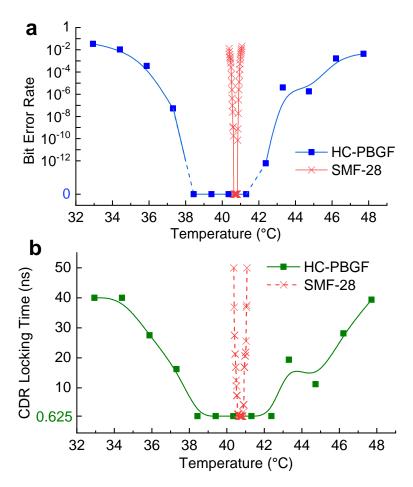

| 7.7 | Impact of temperature variation on the performance of a synchronous         |

|     | HC-PBGF optically-switched system with single calibration clock             |

|     | single calibration CSA-CDR with clock phase tracking                        |

| 7.8 | Estimated worst-case optical switch overhead from clock phase               |

|     | caching, with low-thermal sensitivity HCF transmission 200                  |

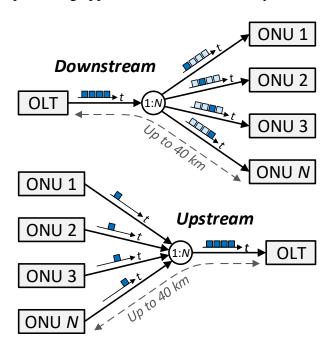

| 8.1 | time division multiplexed passive optical network (TDM-PON)                 |

|     | upstream and downstream links, a method of implementing fibre to the        |

|     | home (FTTH) broadband                                                       |

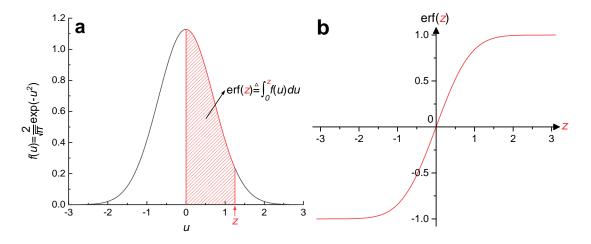

| A.1 | Illustration of the error function                                          |

| B.1 | CSA-CDR field programmable gate array (FPGA) hardware used in               |

|     | Chapters 6 and 7                                                            |

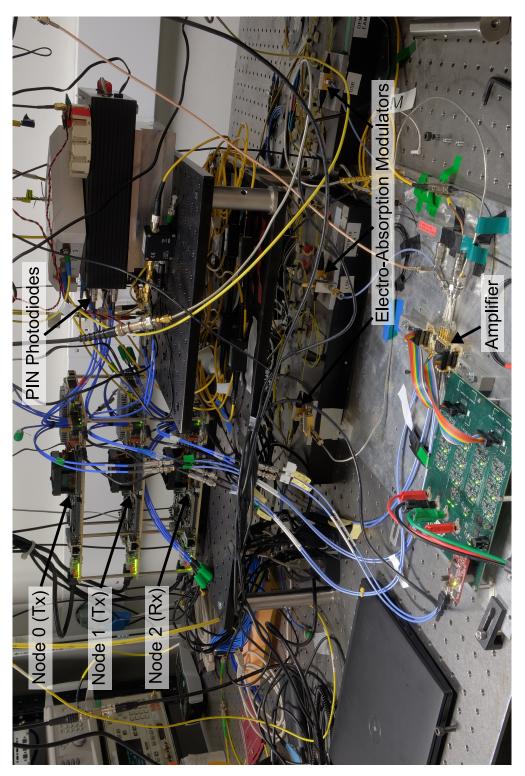

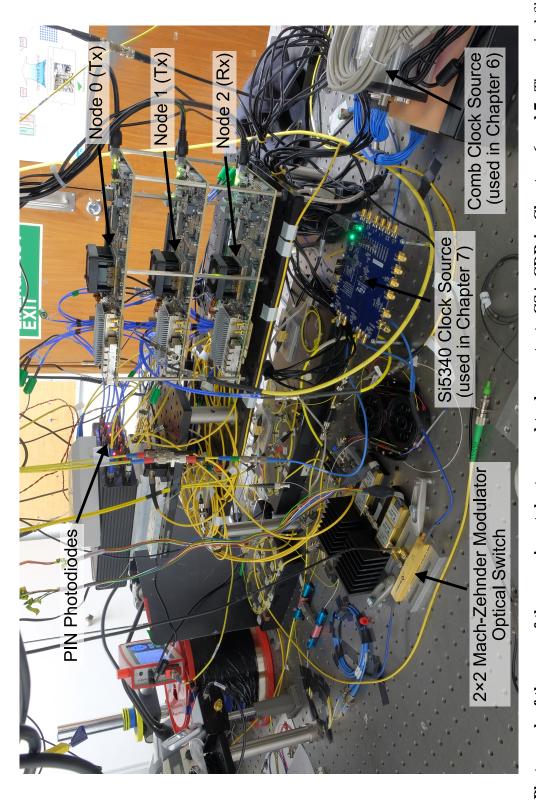

| C.1 | Photograph of the front of the experimental setup used to demonstrate       |

|     | CSA-CDR in Chapters 6 and 7                                                 |

| C.2 | Photograph of the rear of the experimental setup used to demonstrate        |

|     | CSA-CDR in Chapters 6 and 7                                                 |

## **List of Tables**

| 2.1 | Summary of standardised data transmission scales in the data centre        |     |

|-----|----------------------------------------------------------------------------|-----|

|     | environment                                                                | 55  |

| 2.2 | Comparison of data centre network approaches                               | 61  |

| 3.1 | Comparison of burst-mode CDR approaches                                    | 72  |

| 4.1 | Thermal coefficients of delay for different single mode fibre jacket types | 86  |

| 4.2 | Example characteristics of a typical commercial PIN photodiode             |     |

|     | receiver intended for 25 GBaud NRZ-OOK reception                           | 103 |

## **List of Terms and Abbreviations**

| ASHRAE American Society of Heating, Refrigerating and Air-Conditioning                              |

|-----------------------------------------------------------------------------------------------------|

| Engineers                                                                                           |

| ASIC application-specific integrated circuit                                                        |

| <b>AWG</b> arrayed waveguide grating                                                                |

| <b>AWGR</b> arrayed waveguide grating router                                                        |

| <b>BB-PD</b> bang-bang phase detector                                                               |

| <b>BER</b> bit error rate 20, 38, 53, 56, 67, 68, 74, 90, 118, 127, 170, 173, 174, 177 193–198, 238 |

| CDR clock and data recovery                                                                         |

| CID consecutive identical digits                                                                    |

| CPU central processing unit                                                                         |

| CRAC computer room air conditioner                                                                  |

| CRC cyclic redundancy check                                                                         |

| CSA-CDR clock synchronisation assisted clock and data recovery                                      |

| <b>CW</b> continuous wave                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CWDM</b> coarse wavelength division multiplexing                                                                                      |

| <b>DAC</b> digital to analog converter                                                                                                   |

| <b>DDR3 SDRAM</b> Double Data Rate 3 Synchronous Dynamic Random-Access Memory 240                                                        |

| <b>DFB</b> distributed feedback                                                                                                          |

| <b>DMT</b> discrete multi-tone                                                                                                           |

| <b>DSP</b> digital signal processing                                                                                                     |

| <b>DTP</b> Datacentre Time Protocol                                                                                                      |

| <b>DWDM</b> Dense Wavelength Division Multiplexing                                                                                       |

| EAM electro-absorption modulator                                                                                                         |

| <b>EDFA</b> Erbium-doped fibre amplifier                                                                                                 |

| EML externally modulated laser                                                                                                           |

| <b>FEC</b> forward error correction                                                                                                      |

| <b>FIFO</b> first-in first-out queue                                                                                                     |

| <b>FPGA</b> field programmable gate array 21, 42, 43, 56, 69, 78, 109, 121, 124, 147, 151, 163–169, 179, 189, 191, 193, 195–197, 235–240 |

| <b>FTTH</b> fibre to the home                                                                                                            |

| <b>GPS</b> Global Positioning System                                                                                                     |

| <b>GPU</b> graphical processing unit                                                                                                     |

| <b>GVCO</b> gated voltage controlled oscillator                                                                                          |

| <b>HC-NANF</b> hollow-core nested anti-resonant nodeless fiber                                                                           |

| <b>HC-PBGF</b> hollow-core photonic bandgap fibre 20, 21, 188, 194, 195, 197, 198, 200–202, 241–243                                      |

| <b>HCF</b> hollow core fibre 20, 21, 43, 45, 80, 124, 150, 184–202, 204, 207                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| ILA integrated logic analyser                                                                                                                     |

| <b>IM-DD</b> intensity modulation direct detection                                                                                                |

| <b>ISI</b> intersymbol interference                                                                                                               |

| JTAG Joint Test Action Group                                                                                                                      |

| LC-Tank inductor-capacitor tank                                                                                                                   |

| LHC Large Hadron Collider                                                                                                                         |

| MAC media access control                                                                                                                          |

| <b>MCF</b> multi-core fibre                                                                                                                       |

| <b>MEMS</b> microelectro-mechanical system                                                                                                        |

| MFD mode field diameter                                                                                                                           |

| <b>MMF</b> multi-mode fibre                                                                                                                       |

| MZI Mach-Zehnder interferometer                                                                                                                   |

| <b>MZM</b> Mach-Zehnder modulator                                                                                                                 |

| <b>NRZ</b> non-return to zero . 54–56, 90–95, 97–100, 107, 109, 112, 113, 121–123, 133, 135, 143, 189, 193, 228, 229                              |

| <b>NRZ-OOK</b> non return to zero on off keying 17, 18, 22, 42, 49, 54–56, 83, 84, 87, 97, 99–101, 103–112, 114, 115, 117–123, 182, 190, 194, 207 |

| <b>OEO</b> optical-electrical-optical                                                                                                             |

| <b>OOK</b> on-off keying 17, 18, 99, 101, 102, 110, 114, 117, 119, 121, 135, 136, 143, 164                                                        |

| <b>OSNR</b> optical signal-to-noise ratio                                                                                                         |

| <b>OTDM</b> optical time division multiplexing                                                                                                    |

| <b>PAM-4</b> 4-level pulse amplitude modulation                                                                                                   |

| <b>PAM-8</b> 8-level pulse amplitude modulation                                    |

|------------------------------------------------------------------------------------|

| PDF probability distribution function                                              |

| <b>PI</b> phase interpolator                                                       |

| PIC photonic integrated circuit                                                    |

| <b>PIN</b> p-i-n junction 17, 22, 83, 97, 99–108, 110, 120–123, 135, 143, 182, 190 |

| <b>PIPPM</b> phase interpolator parts per million                                  |

| PISO parallel in serial out                                                        |

| <b>PLL</b> phase locked loop                                                       |

| <b>PON</b> passive optical network                                                 |

| <b>ppm</b> parts per million                                                       |

| <b>PRBS</b> pseudo random binary sequence 67, 169, 193, 237–239                    |

| <b>PTP</b> Precision Time Protocol                                                 |

| <b>PVT</b> process voltage temperature                                             |

| <b>QKD</b> quantum key distribution                                                |

| QPLL quad phase locked loop                                                        |

| <b>RMS</b> root mean square                                                        |

| <b>RZ</b> return to zero                                                           |

| <b>SDH</b> Synchronous Digital Hierarchy                                           |

| <b>SDM</b> space division multiplexing                                             |

| <b>SERDES</b> serialiser-deserialiser                                              |

| SFP Small Form Factor Pluggable                                                    |

| SIPO serial-in parallel-out                                                        |

| <b>SMF-28</b> single-mode fibre                                                                   |

|---------------------------------------------------------------------------------------------------|

| 54–56, 62, 80, 81, 85–87, 123, 124, 147, 159, 161, 164, 166, 171, 172, 175, 178,                  |

| 182, 183, 185–189, 191, 193, 196, 197, 199–201, 204, 241–243                                      |

| <b>SOA</b> semi-conductor optical amplifier                                                       |

| <b>SONET</b> Synchronous Optical Networking                                                       |

| <b>SWDM</b> shortwave wavelength division multiplexing                                            |

| <b>Sync-E</b> Synchronous Ethernet                                                                |

| <b>TCD</b> thermal coefficient of delay                                                           |

| <b>TDC</b> temperature delay coefficient                                                          |

| <b>TDM-PON</b> time division multiplexed passive optical network 21, 205, 206, 208                |

| <b>TIA</b> transimpedance amplifier . 83, 97, 100–107, 109, 120–123, 135, 143, 144, 165, 190, 193 |

| <b>ToR</b> top-of-rack                                                                            |

| <b>UART</b> universal asynchronous receiver transmitter                                           |

| UTC Coordinated Universal Time                                                                    |

| VCO voltage controlled oscillator                                                                 |

| VCSEL vertical-cavity surface-emitting laser                                                      |

| VIO virtual input/output                                                                          |

| <b>WDM</b> wavelength division multiplexing                                                       |

### **List of Symbols**

L number of Clos-switch hierarchy layers

k number of bidirectional ports per electronic switch

time, time-of-flight

$n_g$  group refractive index

c speed of light in vacuum

T absolute temperature

L fibre length, distance between nodes

$\frac{dT}{dt}$  rate of change of temperature

$\Delta t$  change in fibre time of flight

$\Delta T$  change in temperature

au fibre thermal coefficient of delay

$\phi, \alpha, \beta$  clock phase

B symbol rate

$\triangleq$  defined as equal to

$\Delta \phi$  change in clock phase

$\omega(\phi)$  ideal square NRZ pulse

f frequency

$f_c$  cut-off frequency (-3 dB frequency)

$\hat{H}(f)$  amplitude normalised Gaussian filter frequency response

$\hat{f}(t)$  amplitude normalised Gaussian filter impulse response

$\sigma_t$  Gaussian filter impulse response standard deviation in terms of

time

FWHM<sub>t</sub> Gaussian filter impulse response full width half maximum in

terms of time

| $\Delta t_{20-80}$          | rise time, 20% to 80%                                                                                   |

|-----------------------------|---------------------------------------------------------------------------------------------------------|

| $\Delta t_{80-20}$          | fall time, 80% to 20%                                                                                   |

| $k_{pls}$                   | Gaussian filter impulse response in terms of symbols                                                    |

| $FWHM_k$                    | Gaussian filter impulse response full width half maximum in terms of symbols                            |

| $v(\phi)$                   | Gaussian filtered NRZ pulse shape in terms of symbols                                                   |

| $\operatorname{erf}(z)$     | error function of $z$                                                                                   |

| $\operatorname{erfc}(z)$    | complementary error function of $z$                                                                     |

| $v_0(\phi)$                 | positive-going Gaussian NRZ pulse in terms of symbols                                                   |

| $v_1(\phi)$                 | negative-going Gaussian NRZ pulse in terms of symbols                                                   |

| $v_{peak}$                  | peak Gaussian NRZ pulse amplitude                                                                       |

| $(v_1-v_0)_{\mathrm{peak}}$ | peak Gaussian NRZ eye height                                                                            |

| $p_e$                       | bit error probability (expectation of the bit error rate)                                               |

| p(0)                        | probability of receiving a 0                                                                            |

| p(1)                        | probability of receiving a 1                                                                            |

| P(0 1)                      | probability of erroneously sampling a 0 instead of a 1                                                  |

| P(1 0)                      | probability of erroneously sampling a 1 instead of a 0                                                  |

| $p_e(\phi)$                 | bit error probability as a function of clock phase offset                                               |

| $P(0 1,\phi)$               | probability of erroneously sampling a 0 instead of a 1 as a function of clock phase offset              |

| $P(1 0,\phi)$               | probability of erroneously sampling a 1 instead of a 0 as a function of clock phase offset              |

| $I(\phi)$                   | sampled photocurrent as a function of sampling clock phase offset                                       |

| $I_D(\phi)$                 | photocurrent decision threshold as a function of sampling clock phase offset                            |

| $I_0(\phi)$                 | mean photocurrent of the positive-going Gaussian NRZ pulse as a function of sampling clock phase offset |

| $I_1(\phi)$                 | mean photocurrent of the negative-going Gaussian NRZ pulse as a function of sampling clock phase offset |

30 List of Symbols

| $\sigma_0(\phi)$ | standard deviation of the photocurrent of the positive-going Gaussian NRZ pulse as a function of sampling clock phase offset |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| $\sigma_1(\phi)$ | standard deviation of the photocurrent of the negative-going Gaussian NRZ pulse as a function of sampling clock phase offset |

| I                | photocurrent                                                                                                                 |

| R                | PIN photodiode responsivity                                                                                                  |

| $P_{opt}$        | incident optical power                                                                                                       |

| $I_{ m max}$     | maximum photocurrent                                                                                                         |

| $I_{ m avg}$     | average photocurrent                                                                                                         |

| $I_{\min}$       | minimum photocurrent                                                                                                         |

| $P_{max}$        | maximum incident optical power                                                                                               |

| $P_{ m avg}$     | average incident optical power                                                                                               |

| $P_{min}$        | minimum incident optical power                                                                                               |

| $r_e$            | extinction ratio                                                                                                             |

| $\sigma_T$       | standard deviation of the photodiode thermal noise                                                                           |

| $\sigma_d$       | standard deviation of the photodiode dark current noise                                                                      |

| $\sigma_s$       | standard deviation of the photodiode shot noise                                                                              |

| $\sigma_{ni}$    | standard deviation of the TIA input referred noise                                                                           |

| $k_B$            | Boltzmann's constant                                                                                                         |

| q                | charge of a single electron                                                                                                  |

| $F_n$            | TIA noise figure                                                                                                             |

| $R_L$            | TIA transimpedance                                                                                                           |

| $I_p$            | photodiode photocurrent                                                                                                      |

| $I_d$            | photodiode dark current                                                                                                      |

| $\sigma^2$       | total PIN photoreceiver noise variance                                                                                       |

| $\sigma_T^2$     | PIN photoreceiver thermal noise variance                                                                                     |

| $\sigma_d^2$     | PIN photoreceiver dark current noise variance                                                                                |

| $\sigma_{opt}^2$ | PIN photoreceiver optical power noise variance                                                                               |

| $\sigma_0^2(\phi)$         | variance of the photocurrent of the positive-going Gaussian NRZ pulse as a function of sampling clock phase offset |

|----------------------------|--------------------------------------------------------------------------------------------------------------------|

| $\sigma_1^2(\phi)$         | variance of the photocurrent of the negative-going Gaussian NRZ pulse as a function of sampling clock phase offset |

| $p_{e(	ext{post-jit})}$    | bit error probability, including the impact of jitter                                                              |

| $p_{e(	ext{pre-jit})}$     | bit error probability, before including the impact of jitter                                                       |

| $PDF_{jit}$                | probability density function of the jitter                                                                         |

| $\sigma_{ m jit}$          | standard deviation of the jitter in terms of time                                                                  |

| $k_{ m jit}$               | standard deviation of the jitter in terms of symbols                                                               |

| $p_e(t)$                   | bit error probability as a function of time since the beginning of data packet reception                           |

| $p_{e(\text{overall})}(t)$ | overall packet bit error probability                                                                               |

| $t_{ m lock}$              | CDR locking time                                                                                                   |

| $p_{e(\mathrm{lock})}$     | bit error probability threshold at which CDR locking is defined as complete                                        |

| $t_{ m pkt	ext{-len}}$     | length of one data packet                                                                                          |

| $\Phi_{	ext{ideal}}(\phi)$ | ideal clock phase error of a bang-bang phase detector                                                              |

| $\Phi_{ m jittered}(\phi)$ | jittered clock phase error of a bang-bang phase detector                                                           |

| $\in$                      | is a member of                                                                                                     |

| $\mathbb{Z}$               | the set of all integers                                                                                            |

| $\mathrm{E}[z]$            | expectation of $z$                                                                                                 |

| $\phi_0$                   | initial clock phase offset                                                                                         |

| $d\phi$                    | small clock phase correction applied by a clock phase interpolator CDR                                             |

| dt                         | clock phase interpolator CDR clock phase offset measurement interval                                               |

| p                          | clock phase interpolator CDR proportional gain constant                                                            |

| $\phi(t)$                  | clock phase offset as a function of time since the beginning of data packet reception                              |

32 List of Symbols

| $I_0(t)$                        | mean photocurrent of the positive-going Gaussian NRZ pulse as a function of time since the beginning of packet reception            |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| $I_1(t)$                        | mean photocurrent of the negative-going Gaussian NRZ pulse as a function of time since the beginning of packet reception            |

| $k_{ m jit	ext{-}h}$            | high frequency jitter standard deviation                                                                                            |

| $k_{ m jit	ext{-}l}$            | low frequency jitter standard deviation                                                                                             |

| PDF <sub>jit-h</sub>            | probability density function of the high frequency jitter                                                                           |

| $\mathrm{PDF}_{\mathrm{jit-l}}$ | probability density function of the low frequency jitter                                                                            |

| $p_{e(	ext{post-jit-h})}(t)$    | bit error probability as a function of time since the beginning of packet reception, including the impact of high frequency jitter  |

| $p_{e(	ext{post-jit-l})}(t)$    | bit error probability as a function of time since the beginning of packet reception, including the impact of low frequency jitter   |

| $p_{e(	ext{post-jit})}(t)$      | bit error probability as a function of time since the beginning of packet reception, including the impact of all jitter frequencies |

| $t^*$                           | time elapsed since last calibration of the clock phase offset (over time scales of magnitude much much greater than $t_{ m pkt}$ )  |

| $\Delta T(t^*)$                 | change in temperature as a function of time since the last calibration of the clock phase offset                                    |

| $f_{\phi}$                      | clock phase update rate                                                                                                             |

| $\phi_{ m min}$                 | minimum initial clock phase offset at the beginning of packet reception                                                             |

| $\phi_{ m max}$                 | maximum initial clock phase offset at the beginning of packet reception                                                             |

| $p_{e({ m ph-cached})}(t)$      | clock phase cached bit error probability as a function of time since the beginning of packet reception                              |

| $\phi_{ m max(thresh)}$         | threshold maximum initial clock phase offset at which bit error probability rises above a defined acceptable threshold              |

| $f_{\phi(	ext{min})}$           | minimum required clock phase update rate                                                                                            |

| k                               | proportionality constant between rate of change of temperature and the minimum required clock phase update rate                     |

| 0                               | throughput overhead from clock phase caching                                                                                        |

| N                               | total number of nodes (servers / switches) connected to an optical switch                                                           |

|                                 |                                                                                                                                     |

n Tx-Rx node pair iterator

$f_{\phi(n)}$  clock phase update rate for Tx-Rx node pair n

$t_{\rm meas}$  time required at a single receiver to perform a single clock phase

update measurement

$t_{\rm update}$  time required at a single transmitter to send a single clock phase

update value

$\tau_n$  fibre thermal coefficient of delay for Tx-Rx node pair n

$L_n$  distance between nodes for Tx-Rx node pair n

$B_n$  symbol rate for Tx-Rx node pair n

$\tau_{\max(\text{thresh},n)}$  threshold maximum initial clock phase offset at which bit error

probability rises above a defined acceptable threshold for Tx-Rx

node pair n

$\left(\frac{dT}{dt}\right)_n$  rate of change of temperature for Tx-Rx node pair n

$o_{\rm max}$  worst-case throughput overhead from clock phase caching

$\Delta T_{\rm max}$  upper bound on the <625 ps (under 16 symbol) CDR locking time

temperature window

$\mathcal{F}^{-1}\{z\}$  inverse Fourier transform of z

### Chapter 1

#### Introduction

### 1.1 Scope of the Thesis

GLOBAL INTERNET TRAFFIC is increasing rapidly, driven primarily by demand from consumers for high bandwidth content such as video traffic [3]. To minimise the use of expensive and high latency inter-continental links, content is increasingly replicated throughout the world and delivered locally from regional data centres. To maximise the energy and cost efficiency of these regional data centres, each data centre typically contains hundreds of thousands of servers, which are interconnected by deep 3 to 5-layer hierarchies of electronic switch application-specific integrated circuits (ASICs). Growth in consumer and business demand, combined with emerging hardware workloads such as the training of deep neural networks and distributed key value stores, is driving a 100% increase of network traffic within these data centres every 12 to 18 months [4].

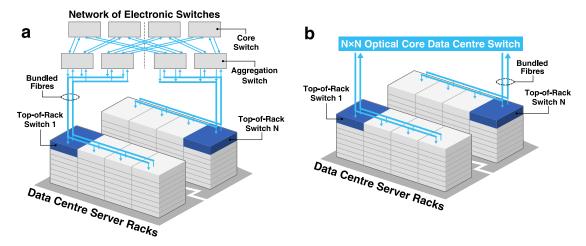

Concurrently, the growth rate of electronic switch ASIC bandwidth is slowing [5], due to the nearing of fundamental physical limits on the achievable power consumption and density of silicon transistors [6]. The impact of this at network scale is that to continue to meet current growth in data centre traffic, increasingly deep hierarchies of electronic switches are required, as shown in Figure 1.1a, with increasingly prohibitive cost, power consumption and latency [7, 8, 9]. For example, a current large data centre would ideally be interconnected by a 100 Pb/s non-blocking network, which would consume 48.7 MW of power, which is more than the 32 MW that is typically allocated for the entire data centre [8, 9]. Consequently, as the scaling of electronic switch ASICs continues to slow, and the gap between the capacity of electronically switched networks and data centre traffic increases, alternative solutions to data centre networking will be required that are less constrained by silicon transistor scalability.

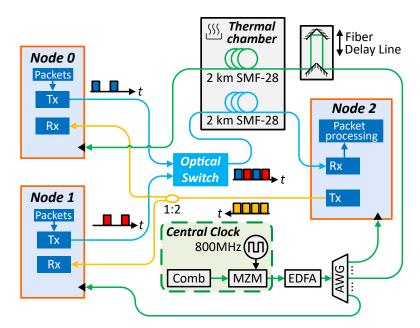

All-optically-switched data centre networking, as shown in Figure 1.1b, is a potential candidate for overcoming this challenge. In all-optical switching, momentary light paths are created to send data packets (64-1500 Bytes [10]) directly between end-points (such as servers or electronic switches) using optical switching elements such as semi-conductor optical amplifiers (SOAs), arrayed waveguide gratings

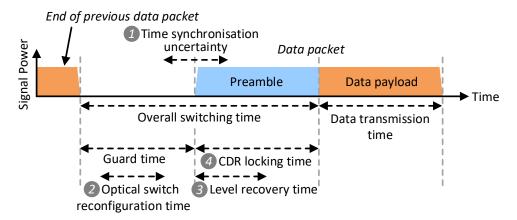

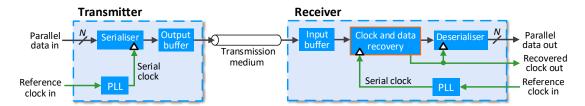

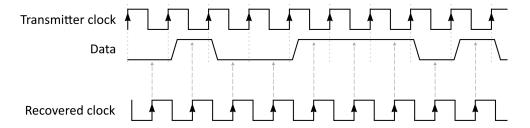

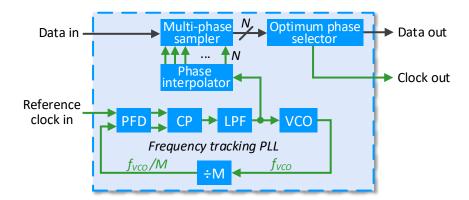

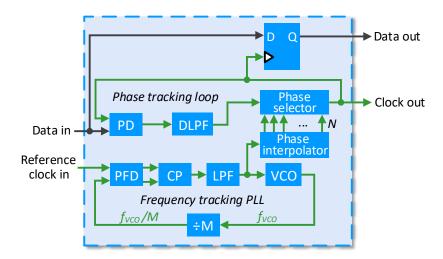

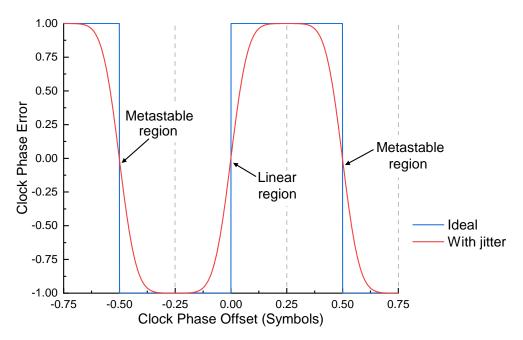

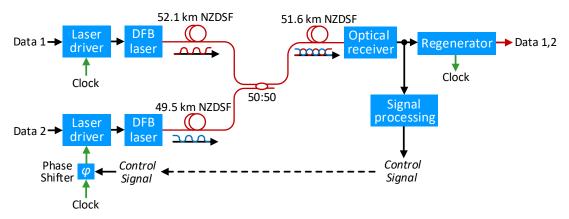

Fig. 1.1: Data centre electronically-switched and all-optically-switched network architectures. a, Current electronically-switched data centre network architecture, which interconnects servers using a deep hierarchy (4 to 5 levels, 3 shown here) of hundreds to thousands of small bandwidth electronic switches. b, A potential future all-optically-switched data centre architecture, which would use a single large port count  $N \times N$  optical switch to interconnect all top-of-rack switches. All-optically-switched architectures promise large improvements in latency, power consumption and capital cost versus the current electronically-switched approach [8, 9].