Escola Tècnica Superior d'Enginyeria de Telecomunicació de Barcelona

## LiveSNN: a new ecosystem

# for HEENS architecture

# A Master's Thesis

# Submitted to the Faculty of the

# Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona

# Universitat Politècnica de Catalunya

## by

# Josep Àngel Oltra Oltra

# In partial fulfilment

# of the requirements for the degree of

# MASTER IN ELECTRONIC ENGINEERING

Advisor: Jordi Madrenas Barcelona, September 2020 Title of the thesis: LiveSNN: a new ecosystem for HEENS architecture

Author: Josep Àngel Oltra

Advisor: Jordi Madrenas

### <u>Abstract</u>

This project proposal and development of a several tools, a communication protocol and an embedded program for giving a neural network called HEENS that it is currently developed by the group ISSET from UPC the capability of being controlled remotely, and to extract the neural. This will provide a faster development, user friendly tools for the development and analysis of spiking neural networks for emulation and verification of biological neural networks and neural models.

As such, three new pieces of software are developed called: LiveSNN protocol, which communicates the HEENS architecture to a remote PC for Supervisory Control And Data Acquisition (SCADA) operations, LiveSNN program, which manages the conections and supervises the activity of the HEENS, and HEENS Toolchain Suite (HTS), which is an upgrade of the previous synthesis and assembler tools in order to allow the implementation of more sophisticated neural networks being easy and be capable of optimise the assembler model of the neuron for the architecture.

With those developments, the time to generate spiking neural networks, to debug them, and emulate them is increased in addition to the reduction of possible human errors due to the increased automation workflow that those programs give to the end user.

Thanks to all the people who helped me and make my day.

「亀の甲より年の功」

(Kame no kou yori toshi no kou)

(Years know more than books)

Japanese proverb

## **Acknowledgements**

Thanks to the help from Jordi Madrenas, who has supervised, give feedback and tested the work that has been done, Diana Mata and Josep Maria Sanchez, who give feedback on the aesthetics and the user interface of the tools, Mireya Zapata and Bernardo Vallejo who have given feedback on the new netlist and the assembler formats.

# **Revision history and approval record**

| Revision | Date       | Purpose           |  |

|----------|------------|-------------------|--|

| 0        | 04/05/2020 | Document creation |  |

| 1        | 18/06/2020 | General format    |  |

| 2        | 27/07/2020 | Content review    |  |

| 3        | 23/08/2020 | Compression test  |  |

| Written by: |                         | Reviewed and approved by: |                    |

|-------------|-------------------------|---------------------------|--------------------|

| Date        | 04/05/2020              | Date                      | 02/09/2020         |

| Name        | Josep Àngel Oltra Oltra | Name                      | Jordi Madrenas     |

| Position    | Project Author          | Position                  | Project Supervisor |

# Table of contents

| 1. Introduction                                       |

|-------------------------------------------------------|

| 1.1. Preliminary concepts15                           |

| 1.1.1. Neural Networks15                              |

| 1.1.2. Artificial Neural Networks17                   |

| 1.1.3. Spiking Neural Networks21                      |

| 1.2. Requirements22                                   |

| 1.3. Objectives                                       |

| 1.4. Organization23                                   |

| 2. State of the art of SNN hardware implementations24 |

| 2.1. TrueNorth24                                      |

| 2.2. SpiNNaker25                                      |

| 2.3. Loihi                                            |

| 2.4. HEENS                                            |

| 2.4.1. Bus AER27                                      |

| 2.4.2. Sequencer                                      |

| 2.4.3. Processing Elements (PE)                       |

| 2.4.3.1. Synapse and Neuron RAM (SN RAM memory)29     |

| 2.4.3.2. Spike decoder (LCL RAM memory)29             |

| 2.4.3.3. Arithmetic Logic Unit (ALU)31                |

| 2.4.3.4. Auxiliary peripherals31                      |

| 3. Methodology / project development                  |

| 3.1. LiveSNN protocol                                 |

| UNIVERSITAT<br>DE CATALUNY<br>BARCELONAT | A T BCN               | 32 |

|------------------------------------------|-----------------------|----|

| 3.1.1.1. Register based                  | d protocol            | 32 |

| 3.1.1.2. Command bas                     | ed protocol           | 33 |

| 3.1.1.3. Summary                         |                       | 33 |

| 3.1.2. Protocol structure                |                       | 34 |

| 3.1.3. Description of the f              | fields                | 34 |

| 3.1.3.1. Transfer ID                     |                       | 34 |

| 3.1.3.2. DataLength fie                  | ld                    | 35 |

| 3.1.3.3. Command field                   | J                     | 35 |

| 3.1.3.4. Payload field                   |                       | 35 |

| 3.1.4. Table of commands                 | S                     | 36 |

| 3.2. LiveSNN program                     |                       | 37 |

| 3.2.1. Selection of the pro              | ogram architecture    | 37 |

| 3.2.1.1. Bare metal                      |                       | 37 |

| 3.2.1.2. Real Time Ope                   | erating System (RTOS) | 38 |

| 3.2.1.3. Linux Operating                 | g System (Petalinux)  | 38 |

| 3.2.1.4. Summary                         |                       |    |

| 3.2.2. Program architectu                | ıre                   | 40 |

| 3.2.2.1. FreeRTOS                        |                       | 41 |

| 3.2.2.2. Context handle                  | er                    | 41 |

| 3.2.2.3. Tasks                           |                       | 42 |

| 3.2.2.4. Shell                           |                       | 45 |

| 3.3. HEENS Toolchain Suite               | e                     | 46 |

| 3.3.1. Netlist V1                        |                       | 46 |

| 3.3.2. Assembler V1                      |                       | 47 |

| 3.3.3. Problems                          |                       | 47 |

| 3.4. Propos                                                                                                            | ed solution: HTS48                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4.1. HE                                                                                                              | ENS Toolchain Suite (HTS)48                                                                                                                                                                                                                                              |

| 3.4.2. HE                                                                                                              | ENS Neural Synthesis (HNS)49                                                                                                                                                                                                                                             |

| 3.4.2.1.                                                                                                               | Configuration section                                                                                                                                                                                                                                                    |

| 3.4.2.2.                                                                                                               | Netlist section51                                                                                                                                                                                                                                                        |

| It is sm                                                                                                               | aller and easier to specify the value of the synapse51                                                                                                                                                                                                                   |

| 3.4.2.3.                                                                                                               | Parameters section                                                                                                                                                                                                                                                       |

| 3.4.3. HE                                                                                                              | ENS Code Assembler (HCA)53                                                                                                                                                                                                                                               |

| 3.4.4. HE                                                                                                              | ENS High Level Neural Synthesis (HLNS)55                                                                                                                                                                                                                                 |

| 3.4.4.1.                                                                                                               | Configuration section55                                                                                                                                                                                                                                                  |

| 3.4.4.2.                                                                                                               | Netlist section55                                                                                                                                                                                                                                                        |

| 3.4.4.3.                                                                                                               | Parameters section                                                                                                                                                                                                                                                       |

| 3.5. HTS de                                                                                                            | sign flow57                                                                                                                                                                                                                                                              |

|                                                                                                                        |                                                                                                                                                                                                                                                                          |

| 3.5.1. HLI                                                                                                             | NS design flow57                                                                                                                                                                                                                                                         |

|                                                                                                                        | NS design flow57<br>Reading the netlist file57                                                                                                                                                                                                                           |

| 3.5.1.1.                                                                                                               | -                                                                                                                                                                                                                                                                        |

| 3.5.1.1.<br>3.5.1.2.                                                                                                   | Reading the netlist file                                                                                                                                                                                                                                                 |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.                                                                                       | Reading the netlist file                                                                                                                                                                                                                                                 |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.<br>3.5.1.4.                                                                           | Reading the netlist file                                                                                                                                                                                                                                                 |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.<br>3.5.1.4.<br>3.5.2. HN                                                              | Reading the netlist file                                                                                                                                                                                                                                                 |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.<br>3.5.1.4.<br>3.5.2. HN<br>3.5.2.1.                                                  | Reading the netlist file                                                                                                                                                                                                                                                 |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.<br>3.5.1.4.<br>3.5.2. HN<br>3.5.2.1.<br>3.5.2.2.                                      | Reading the netlist file57Seeking and load the chips57Place-out: map the synapses to chips57Generation of the specific netlists57S design flow58Reading the netlist file58                                                                                               |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.<br>3.5.1.4.<br>3.5.2. HN<br>3.5.2.1.<br>3.5.2.2.<br>3.5.3. HC                         | Reading the netlist file57Seeking and load the chips57Place-out: map the synapses to chips57Generation of the specific netlists57S design flow58Reading the netlist file58Generation of the memory files and network summary58                                           |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.<br>3.5.1.4.<br>3.5.2. HN<br>3.5.2.1.<br>3.5.2.2.<br>3.5.3. HC<br>3.5.3.1.             | Reading the netlist file.57Seeking and load the chips.57Place-out: map the synapses to chips.57Generation of the specific netlists.57S design flow.58Reading the netlist file.58Generation of the memory files and network summary.58A design flow.59                    |

| 3.5.1.1.<br>3.5.1.2.<br>3.5.1.3.<br>3.5.1.4.<br>3.5.2. HN<br>3.5.2.1.<br>3.5.2.2.<br>3.5.3. HC<br>3.5.3.1.<br>3.5.3.2. | Reading the netlist file.57Seeking and load the chips.57Place-out: map the synapses to chips.57Generation of the specific netlists.57S design flow.58Reading the netlist file.58Generation of the memory files and network summary.58A design flow.59Reading the code.59 |

| 4. Results                              |

|-----------------------------------------|

| 4.1. LiveSNN protocol61                 |

| 4.2. LiveSNN program68                  |

| 4.3. HEENS Toolchain Suite70            |

| 5. Budget72                             |

| 6. Environment Impact73                 |

| 7. Conclusions and future development74 |

| 7.1. Conclusions74                      |

| 7.2. Future work74                      |

| 8. Appendices78                         |

| 8.1. Protocol format structure78        |

| 8.1.1. NULL                             |

| 8.1.2. STATUS                           |

| 8.1.3. CONFIGURATION81                  |

| 8.1.4. DESCRIPTOR82                     |

| 8.1.5. START                            |

| 8.1.6. STOP                             |

| 8.1.7. STEP                             |

| 8.1.8. RESET                            |

| 8.1.9. UPLOAD FIRMWARE                  |

| 8.1.10. DOWNLOAD FIRMWARE               |

| 8.1.11. SPIKE REPORT                    |

|                                         |

| 8.1.12. RASTER REPORT90                 |

| 8.1.12. RASTER REPORT                   |

|                                         |

| 8.   | 1.16. GET SPIKE                        | .96 |

|------|----------------------------------------|-----|

| 8.2. | SEND SPIKE data format                 | .97 |

| 8.3. | Example of the old netlist             | .98 |

| 8.4. | Example of the old code1               | L00 |

| 8.5. | Example of the new high level netlist1 | L04 |

| 8.6. | Example of the new netlist1            | L05 |

| 8.7. | Example of the new code1               | L06 |

# List of Figures

| Figure 1: Neuron cell diagram form [1]15                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Synapse diagram between an axon and a dendrite from [14]16                                                        |

| Figure 3: Structure of a simple Artificial Neural Network from [12]17                                                       |

| Figure 4: Model of a neuron from [9]19                                                                                      |

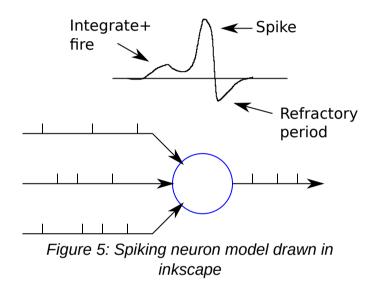

| Figure 5: Spiking neuron model drawn in inkscape21                                                                          |

| Figure 6: TrueNorth board from [13]24                                                                                       |

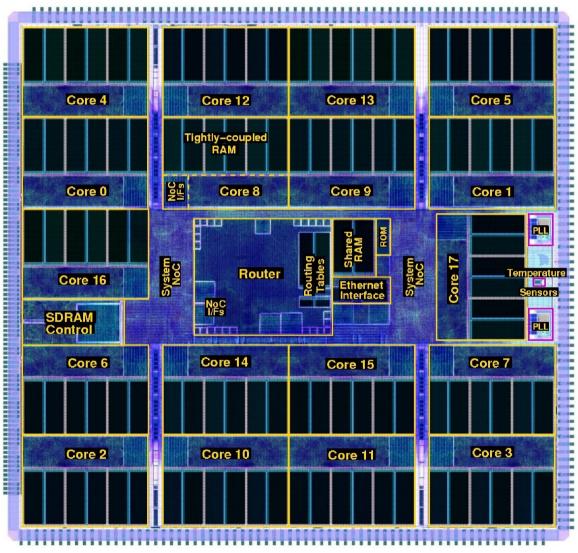

| Figure 7: SpiNNaker IC from [4]25                                                                                           |

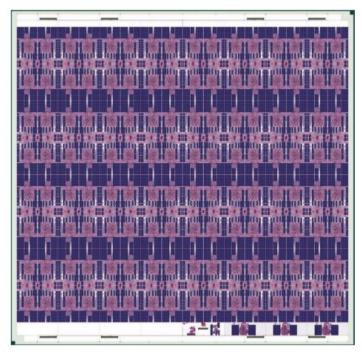

| Figure 8: Loihi silicon floorplan from [10]26                                                                               |

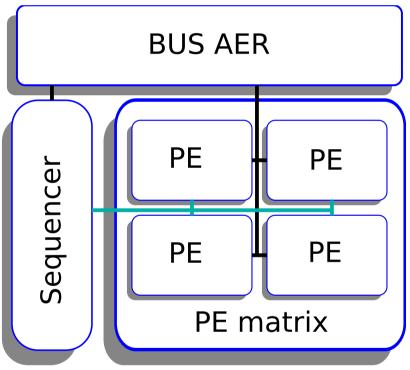

| Figure 9: Block diagram of the HEENS architecture27                                                                         |

| Figure 10: Simple diagram of the Processing Element28                                                                       |

| Figure 11: Neural virtualization in the processing element                                                                  |

| Figure 12: ZYNQ 7 family architecture from [11]40                                                                           |

| Figure 13: Task creation order, where main is the entry point of the ARMs program42                                         |

| Figure 14: HEENS Toolchain Suite (HTS) diagram48                                                                            |

| Figure 15: Communication between PC and ARMs via ethernet61                                                                 |

| Figure 16: Frame of the "Get Descriptor" command62                                                                          |

| Figure 17: Error response result63                                                                                          |

| Figure 18: Frame of the "Heartbeat" command64                                                                               |

| Figure 19: Response of the "Heartbeat" command65                                                                            |

| Figure 20: Frame of the "Get Spikes" command66                                                                              |

| Figure 21: Response of the "Get Spikes" command67                                                                           |

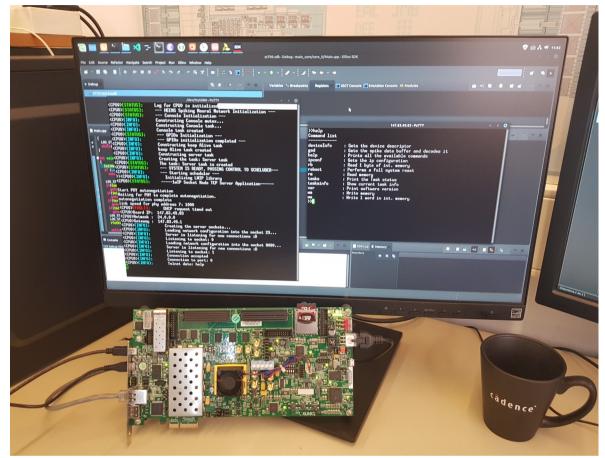

| Figure 22: Setup of the test of the code deployed on the ARMs in the ZC706 with the console and the TELNET connections open |

# List of Tables

| Table 1: Example of activation functions                                             |

|--------------------------------------------------------------------------------------|

| Table 2: Comparison between protocol schemes                                         |

| Table 3: Frame structure of the proposed protocol                                    |

| Table 4: List of commands that will support the first revision of the protocol       |

| Table 5: Comparison between the different approaches to program the ARM processor 38 |

| Table 6: Fields of the context handler structure41                                   |

| Table 7: List of supported commands in the terminal                                  |

| Table 8: Fields of a entry in the old netlist                                        |

| Table 9: Entry format of the low level configuration                                 |

| Table 10: Fields of the configuration section                                        |

| Table 11: Field description of the synapse connection in the low level netlist       |

| Table 12: Field description of the parameter declaration in the low level netlist    |

| Table 13: Keywords reserved to the HCA53                                             |

| Table 14: Field description of the mnemonic instruction set for the HCA              |

| Table 15: Field description of the synapse declaration for the high level netlist    |

| Table 16: Field description for the parameters of the neurons in high level netlist  |

| Table 17: Comparison between the code generated by the old and the new toolchain70   |

| Table 18: Relative difference of the code generated by the different toolchains70    |

| Table 19: Budget of the project                                                      |

| Table 20: LiveSNN NULL command request frame                                         |

| Table 21: LiveSNN STATUS command request frame                                       |

| Table 22: LiveSNN STATUS command response frame                                      |

| Table 23: LiveSNN status bit format                                                  |

| Table 24: LiveSNN CONFIGURATION command request frame      |

|------------------------------------------------------------|

| Table 25: LiveSNN CONFIGURATION command response frame     |

| Table 26: LiveSNN DESCRIPTOR command request frame         |

| Table 27: LiveSNN DESCRIPTOR command response frame        |

| Table 28: LiveSNN START command request frame              |

| Table 29: LiveSNN START command response frame             |

| Table 30: LiveSNN STOP command request frame               |

| Table 31: LiveSNN STOP command response frame              |

| Table 32: LiveSNN STEP command request frame               |

| Table 33: LiveSNN STEP command response frame              |

| Table 34: LiveSNN RESET command request frame              |

| Table 35: LiveSNN RESET command response frame             |

| Table 36: LiveSNN UPLOAD FIRMWARE command request frame    |

| Table 37: LiveSNN UPLOAD FIRMWARE command response frame   |

| Table 38: LiveSNN DOWNLOAD FIRMWARE command request frame  |

| Table 39: LiveSNN DOWNLOAD FIRMWARE command response frame |

| Table 40: LiveSNN SPIKE REPORT command request frame       |

| Table 41: LiveSNN SPIKE REPORT command response frame      |

| Table 42: LiveSNN RASTER REPORT command request frame      |

| Table 43: LiveSNN RASTER REPORT command response frame     |

| Table 44: LiveSNN OTHER PROTOCOL command request frame     |

| Table 45: LiveSNN OTHER PROTOCOL command response frame    |

| Table 46: Peripheral ID definitions                        |

| Table 47: LiveSNN ERROR command response frame             |

| Table 48: LiveSNN HEARTBEAT command request frame          |

| Table 49: LiveSNN HEARTBEAT command response frame         |

| Table 50: LiveSNN GET SPIKE command request frame            | .96 |

|--------------------------------------------------------------|-----|

| Table 51: LiveSNN GET SPIKE command response frame           | .96 |

| Table 52: Serialization format of the spike data for LiveSNN | .97 |

### <u>Glossary</u>

- ALU: Arithmetic Logic Unit

- CAN: Controller Area Network

- JSON: JavaScript Object Notation

- HCA: HEENS Code Assembler

- HLNS: HEENS high Level Netlist Synthesiser

- HNS: HEENS Netlist Synthesiser

- HTC: HEENS Toolchain Compiler

- HTS: HEENS Toolchain Suite

- I2C: Inter-Integrated Circuit

- LiveSNN: Live Spiking Neural Network

- LFSR: Linear Feedback Shift Register

- LSB: Least Significant Bit

- MSB: Most Significant Bit

- NN: Neural Network

- PC: Personal Computer

- PE: Processing Element

- OS: Operating System

- OSI: Open Systems Interconnection

- RLE: Run Length Encoding

- RTOS: Real Time Operating System

- SCADA: Supervisory Control And Data Acquisition

- SNN: Spiking Neural Network

- SoC: System on Chip

- TGF: Trivial Graph Format

- WIP: Work In Progress

### 1. Introduction

In this chapter, a preliminary knowledge will be given as well as the current situation about the interface between neural networks and machines

### **1.1.** Preliminary concepts

In recent years, the idea of emulating a neural system like our brains has been increasing steadily due to the growth of the processing power of the machines and the birth of the big data. In order to process this information where there are governed by complex relationships, neural networks are a good alternative.

These networks rely on the fact that can behave as systems of neurons, and could potentially behave as a brain. This, with techniques of machine learning, neural networks can 'learn' patterns and make decisions even if the case presented is new for the network.

The other important property of neural networks is that could be used as a way of brains and network of biological neurons without the need of having an actual functional brain.

### **1.1.1. Neural Networks**

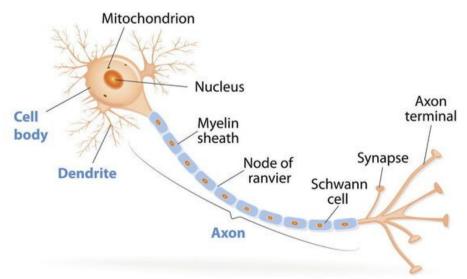

A neural network is a collection of elements called 'neurons' as it is shown in fig [1].

Figure 1: Neuron cell diagram form [1]

A neuron is a cell found in animals. This type of cells in charge of sending and process information in a fast and very controlled way. They use sodium and potassium ions in

order to convert the chemical signals into ion currents and electro-chemical potentials, and vice-versa.

The neurons can be divided into three main parts:

- Dendrites: transforms the chemical signals into ion currents.

- Cell body: process the incoming ion currents and generates an output.

- Axon: transports this output to the input of the other neurons and transforms the ion current into chemical signals.

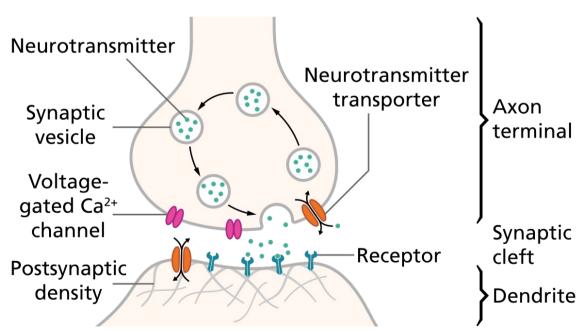

In the interface between neurons and other cells where the information is passed by the chemical signals is called synapse. The operation of one neuron is as follows:

The signals are transform in ion currents. Depending on the type of the chemical used (also called neurotransmitter), the current is increased or decreased. This process is shown in fig. [2].

Figure 2: Synapse diagram between an axon and a dendrite from [14]

Then, all the ion currents converge in the cell body and accumulate, resulting a voltage called neuron potential. This voltage can rise until a threshold is reached, where the ion

channels start to generate a strong output signal and is propagated via to the axon. At the end of the axon, there are the synapses to the other cells.

There are several types of neural networks, but in this document the most common ones will be discussed.

The proposed system tries to copy the structure of the biological neural networks in a non biological implementation. The benefits are in computation speed and simulations of models related to neurons. As it is an artificial, it can be configured as the application needs with a high response. There are several implementations of neural networks, due to the range of applications that they try to solve. In the following points some examples are explained.

#### 1.1.2. Artificial Neural Networks

In this type of networks, the neuron is a mathematical function that has as many inputs as a synapses, and an output that is transmitted to other neurons.

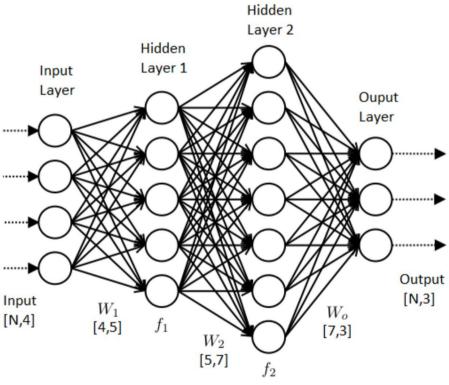

Figure 3: Structure of a simple Artificial Neural Network from [12]

Figure [3] shows an example of artificial neural network. It consists on an Input layer, whose neurons contain the input information. Then the information is passed to the hidden layers 1 and 2 for further processing. Those layers are called hidden because the neurons are internal, i.e., not connected to the input or the output, so they are connected

to other neurons. Finally the data is sent to the output neurons in order to produce the result from the neural network.

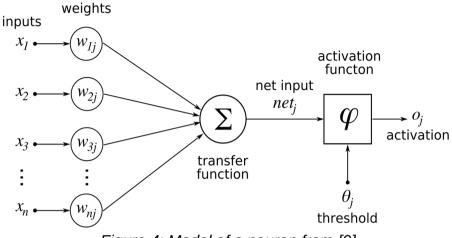

The neuron is modelled as shown in Fig. [4]:

Figure 4: Model of a neuron from [9]

It consists on input connections that are multiplied by some weights, and sum all the values and passed into an activation function.

Typically, the synapses are represented as a matrix. This matrix contains all the weights for all the synapses of each neuron on a given layer. This representation is suitable to run neural networks with processors that work with matrices, like GPUs.

The activation functions that are used on the neural network are well behaved and has a very easy to compute derivative. This is important to be able to teach the network to do a task. The commonly used functions are:

| Function                     | Expression                 | Derivative                                                            |

|------------------------------|----------------------------|-----------------------------------------------------------------------|

| Logistic                     | $f(x) = \frac{1}{1 + e^x}$ | $f'(\mathbf{x}) = f(\mathbf{x})(1 - f(\mathbf{x}))$                   |

| Hyperbolic tangent           | $f(x) = \tanh(x)$          | $f'(x) = 1 - f^2(x)$                                                  |

| Rectified Linear Unit (ReLU) | f(x) = max(0, ax)          | $f'(x) = \begin{cases} a, & if \ x > 0 \\ 0, & otherwise \end{cases}$ |

Table 1: Example of activation functions

This type of neural networks is used in all situations, and in conjunction with other types of neural networks. One example is the use on convolutional neural networks (CNN) as the last processing step on the data, as it is used as a classifier layer to sort the different features, like faces, traffic signals, that the CNN have extracted from the image.

In addition, each layer can be viewed as a vector space, and the all the weights from one layer to the next layer as a linear map. Then, the idea of neural networks is to transform the input vector space and group the vectors following a criteria, and then the output layer needs to classify the grouped values. So, for each hidden layer it is added, the neural network is more capable to sort the data and facilitates the training process.

#### **1.1.3.** Spiking Neural Networks

This type of neural network is the most similar network that emulates a biological network. It works via spikes, like the real neurons. Each neuron contains a model to transform these spikes into analog information that is used to generate the next spike.

The spike represents a neuron transmitting a signal like the biological counterpart. The neuron input spikes are accumulated increasing the membrane potential until it surpasses a threshold. Then an output spike is generated and propagated. An example is as shown in figure [5]:

The behaviour of the neuron depends on the model that it is loaded into each neuron. For example, a simple model is the "Integrate and Fire" model, where the spikes add or subtract a given amount of potential until it reaches the threshold potential. Then a spike is generated and transmitted to the neural network.

This type of neural network is the most similar to a biological one, where the information is encoded in a impulse-frequency basis, mimicking the biological counterpart. The utility of those types of neural networks are for research and emulation of biological systems, due to their similarities, but recently, there have been several attempts to use them in real-world applications.

One example of implementation of this type of neural network is the HEENS architecture, which it is being developed at the Universitat Politècnica de Catalunya.

#### 1.2. Requirements

The HEENS architecture is divided into several subprojects and tools to generate the required files to do a simulation. So the requirements to mitigate time consuming efforts are:

- A protocol that needs to be able to exchange information from and to the HEENS

- A software that can run in embedded processors to control the HEENS

- Back compatibility as much as possible with the older tools.

### 1.3. Objectives

This project tries to accelerate and develop the infrastructure required to operate the HEENS in a more user friendly, yet with a high performance. So the objectives are:

- Develop a communication protocol that will transmit information between the HEENS and the PC via remote access, with a modular structure for quick upgrades that will be appearing.

- Generate a program that take advantage of the ZYNQ Z706 embedded ARM processor units to be able to communicate with the protocol and the HEENS, with analytic capabilities and remote control of the architecture, that in the future will be able to upgrade the system.

- Enhance existing tools to be modular, efficient and easy to use, without reducing the existing capabilities. In addition, automate and optimise (when enabled) the code to be executed. Those tools will be able to be cross -platform.

#### 1.4. Organization

This project is divided in three main sections:

- 1. Define the protocol scheme, which will be set some requirements on the implementation of the code in the ARMs, and specifically the way of handling the messages.

- 2. Implement the code on the ARMs, where most of the time will be consumed by the debugging and validating the code.

- 3. Generate the second generation of the toolchain, that will have the same procedure as the point 2.

## 2. <u>State of the art of SNN hardware implementations</u>

Nowadays, there are different implementations done by different entities like IBM, the university of Manchester, etc. Those implementations are have it's own characteristics in order to test different approaches to how to create a SNN in silicon. So, among all the different implementations, four of them will be explored:

- TrueNorth from DARPA and IBM

- SpiNNaker from University of Manchester

- Loihi from Intel

- HEENS from Universitat Politècnica de Catalunya

### 2.1. TrueNorth

This neural network is designed by DARPA[2] and IBM[3]. It is a chip with a 4096 cores with a total neuron emulation of 1 million neurons and 256 million synapses. It claims to be more efficient and faster due to they use a custom architecture whereas the traditional Von Neumann architecture. A picture of the TrueNorth is shown in the Fig. [6].

Figure 6: TrueNorth board from [13]

#### 2.2. SpiNNaker

This neural network is designed by School of Computer Science at the University of Manchester in UK[4]. It is build in a chip and it has 16 cores to preform the execution on the neural network, 1 for task management, and 1 for fault or backup processor, giving a total of 18 cores. This type of processing emulates in software the neurons in the spiking neural network. It has been scaled up a large SNN unit with 518.400 SpiNNaker processors. The layout of the SpiNNaker is shown in the Fig. [7].

Figure 7: SpiNNaker IC from [4]

### 2.3. Loihi

This neural network is designed by Intel. It is a custom neuromorphic core with the learning process included in the core itself[5]. It is a 128 neuromorphic cores with three x86 processors in order to monitor and configure the neural network. It is divided into bundles of spikes, that then are passed through a tree of neurons. This makes this neural network to have a reduce interconnect between neurons, and a careful planning is needed in order to take advantage of this architecture. A layout of the Loihi is shown in the Fig. [8].

Figure 8: Loihi silicon floorplan from [10]

### 2.4. HEENS

As the world of neural networks advances, there are necessities in the development on more sophisticated architectures. In the niche of the spiking neural networks, the main developments are on software and hardware implementations for quick verification and analysis of the biological neural networks and neurons. The HEENS architecture is a hardware implementation of a spiking neural network. It is deployed on System on Chip of by the Xilinx manufacturer.

HEENS is a spiking neural network implemented by the ISSET research group of the UPC. It is implemented in VHDL and can be deployed in FPGAs and simulators like QuestaSim. This neural network has to work properly a binary file that contains the neuron model to be executed and the binary files containing the synapses. It is divided into 2 main blocks called "sequencer" and "Processing Element array" (PE array). A block diagram is shown in Fig. [9].

Figure 9: Block diagram of the HEENS architecture

### 2.4.1. Bus AER

This bus is used to interconnect different boards that implement the HEENS architecture. As such, it moves the spike information between boards. These spikes are called global spikes, and uses the ID number of the HEENS to sort these spikes.

#### 2.4.2. Sequencer

The sequencer is the part that executes the neuron model and controls in the PEs. It consists on a control unit, with a memory that contains the instructions of the model and several register and memory cells to implement several functions, such as:

This bus is used to interconnect different boards that implement the HEENS architecture. As such, it moves the spike information between boards. These spikes are called global spikes, and uses the ID number of the board to sort these spikes.

- Counter to have value about the current iteration of a loop

- Stack LIFO memory for storing the stack pointers

- Instruction memory witch contains the model and common data values that are shared among all the PEs.

Also, it contains a bus that connects the sequencer to the PE array, which it enables to share the same information with all the PEs. In addition to that, the sequencer contains a pipeline which increases the performance of the neural network.

#### 2.4.3. Processing Elements (PE)

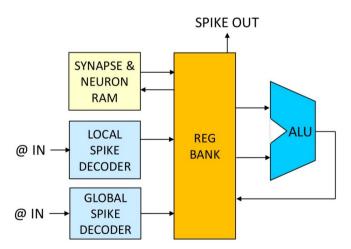

The Processing Element (PE) is the distributed part of the HEENS. It consist on a dedicated Arithmetic Logic Unit (ALU) to execute the spiking model, and a routing logic in order to decode the spikes form the network. A block diagram of the PEis shown in Fig. [10]:

Figure 10: Simple diagram of the Processing Element

#### 2.4.3.1. Synapse and Neuron RAM (SN RAM memory)

This memory is used to store the synaptic and neuronal parameters. It is used as a distributed memory for the PE, which can read specific data related to the instructions in the sequencer. It contains information like synaptical weight, initial seeds for the pseudo random generators, etc.

### 2.4.3.2. Spike decoder (LCL RAM memory)

The spike decoder is a circuit that decodes the incoming spike into an address that the model can access. This is implemented via memories.

The PEs are arranged into a matrix like format, where it contains r rows and c columns. As the memories are normally bigger than the PEs, virtualization layers are added in order to increase the effective number of neurons. So, the neurons with a given row and column are processed in the same PE, in order of the virtual layer number assigned to them. With this, the effective number of neurons are:

$$N = R \cdot C \cdot V \tag{1}$$

Where:

- R is the number of rows of the PE array.

- C is the number of columns of the PE array.

- V is the number of virtual layers that a PE can execute.

This can be viewed graphically as shown in Fig. [11]:

Figure 11: Neural virtualization in the processing element

So, with this, if the SNN is desired to be increased, more area can be dedicated to the PEs to increase the number of PEs, and more time can be spent in order to execute more neurons per PE.

The incoming spike is a number that codifies the spike into 3 parts:

- The virtual layer of the destination neuron.

- The column on the PE array of the destination neuron.

- The row on the PE array of the destination neuron.

This codification as a number and as a an array gives the connexion to the address to store the spike into the memory. If an spike has been produced, it will be stored in the destination PE array memory, in the following address A:

$$A = c + R \cdot (r + V \cdot v) \tag{2}$$

For spikes that come from external sources, like other chips with the HEENS, there is a dedicated memory to translate the id from the current board alongside the spike information in order to route the spike in the correct destination neuron.

This information is stored in the LCL-RAM memory, where the synapse number is stored in the address corresponding to the position of the source neuron.

### 2.4.3.3. Arithmetic Logic Unit (ALU)

The ALU is a circuit that can the arithmetic and logic operations. It calculates 16-bit operations as it has good trade-off between area and precision.

#### 2.4.3.4. Auxiliary peripherals

The PE also contains two register banks of 8 registers each one for intermediate variable storage and modules that help to accelerate certain operations as well as generating useful patterns.

The pattern generator is a Linear Feedback Shift Register (LFSR). This is a series of flipflops that are connected in a daisy chain configuration with some linear operation with the previous state. Moreover, it has 16 registers divided into 2 banks. This is useful in situations like storing the state when a function is called.

## 3. <u>Methodology / project development</u>

This project is called Live Spiking Neural Network (LiveSNN). It is called that way because it will give the HEENS SNN the capability of remote access for SCADA, the way it will communicate with the embedded ARM processors and the code that will be hable to understand this new protocol. It will has three phases:

- Develop of the LiveSNN protocol

- Develop the programs running on the ARM's processors (LiveSNN program)

- Develop advanced toolchain suites for the HEENS architecture

### 3.1. LiveSNN protocol

The neural network needs to communicate with a remote computer to supervise and control the activity of the HEENS processor. As it is a neural network processor, the protocol needs to be designed into the needs of the HEENS, as well as allowing bridge communication between the ARM processor and another electronic devices like sensors, memories, etc, for quick diagnosis and full supervision of the system.

### **3.1.1.** Protocol structure selection

There are different ways to implement the LiveSNN protocol.

### **3.1.1.1. Register based protocol**

This type of protocol scheme uses write and read memory in order to transmit information. It consist on the following sections:

- Address to be read from or written to.

- Read/Write identifier (control bit).

- Data stream

It is very easy to implement in hardware and software, and usually the control bit is combined with another field, like an identification number, in order to have more devices sharing the same bus. This also requires almost no logic at all and it is pretty fast due to it's simplicity.

A few examples of buses using this type of commands are Controller Area Network (CAN), Inter-Integrated Circuit (I2C), etc.

#### **3.1.1.2.** Command based protocol

This type of protocols has the flexibility to convey actions in a part of the frame. These actions are usually called commands. Each command executes the action coded in the command bytes will the help of the optional arguments. This achieves a good development time thanks to executing different things in separate messages with the penalty of having extra logic to decode the frames.

This type of protocol is a superset of the Register based one, due to the fact that it is possible to implement the commands that the Register based protocol have.

#### 3.1.1.3. Summary

The protocol will have an identifier field in order to be able to distinguish among the different neural networks. If c is the number of bytes that the command field has, the following table is build:

|                    | Register based | Command based |

|--------------------|----------------|---------------|

| Frame overhead     | 2              | 2             |

| Number of commands | 2              | 256°          |

| Programming effort | Simple         | Complex       |

Table 2: Comparison between protocol schemes

So, the format chosen is the command based, which will encode different actions in a small, compact form.

#### **3.1.2.** Protocol structure

This protocol needs to interact with the SNN in different ways, in a command-based protocol. It has different commands to manage the several functions in an efficient way. All the fields are stored in big endian (the most significant byte is the first, whereas the least significant byte is last). The message contains metadata in order to send the information. The messages have the following format:

| Byte      | Name       | Description                 |

|-----------|------------|-----------------------------|

| 0         | TransferID | Identification of the frame |

| 1 - 4     | DataLength | Length of the frame         |

| 5         | Command    | Action to be executed       |

| 6 - (n-1) | Payload    | Data related to the command |

Table 3: Frame structure of the proposed protocol

An error detection algorithm is not included because this protocol will be in the session layer in the Open System Interconnection (OSI) model. So, all the problems relating with data routing, and the data integrity are handled by the other layers. In case of the implementation on the ZYNQ SoC, the LiveSNN protocol will use TCI/IP ethernet communication.

The commands are explained in Annex 8.1.

### **3.1.3.** Description of the fields

In this section, the different fields that the protocol implements are explained.

### 3.1.3.1. Transfer ID

It is a message identifier in order to know the arrival of the messages. It is also used as a error checking due to the fact that this number always increments by one (until it overflows). As such, if the transferID does not coincide with the next one, an error is raised. In case that the number is bigger than 255, it simply wraps around and continues from 0. In case of using TCP/IP it is redundant.

#### 3.1.3.2. DataLength field

This field holds the length of the whole frame, which it is used to pre-allocate a buffer for storing the frame. It is counted in bytes, and the possible valid range is between 6 and  $2^{32}$  – 1 bytes. If this value is less than 6, an error is raised as a bad frame has been read. The maximum value is the theoretical upper limit, and depending on the physical layers the real upper limit will be much lower.

#### 3.1.3.3. Command field

This byte encodes the action to be executed to the neural network. Depending of the value, the ARM processor needs to perform an action on the HEENS processor, or perform an action on itself, like rebooting, or just forward the payload into another physical media in order to interact with the environment and get information related to the system. Those actions are classified in 128 values. The MSB is reserved for the protocol, and it shows if the message has been processed. This makes the message self contain, where within itself the protocol knows in every moment if a message is a request (MSB = 0) or a response (MSB = 1).

#### 3.1.3.4. Payload field

Those bytes contain the information carried by the protocol specified by the command. It could be 0 or the entire firmware of the system running on the HEENS

### **3.1.4.** Table of commands

The commands are encoded in one byte, so as mention before, the range is 256 different commands. As the MSB is for detecting if the frame is a request or a response, the effective number of commands are 128. So, the following commands are proposed in order to have control, with room for implementing extra functionalities.

| Value       | Command           | Description                                |

|-------------|-------------------|--------------------------------------------|

| 0x00        | NULL              | Empty message                              |

| 0x01        | STATUS            | Sends the current status                   |

| 0x02        | CONFIGURATION     | Sends the current configuration            |

| 0x03        | DESCRIPTOR        | Sends the descriptor                       |

| 0x04        | START             | Starts the Neural Network (NN)             |

| 0x05        | STOP              | Stops the NN                               |

| 0x06        | STEP              | Executes n steps of the NN                 |

| 0x07        | RESET             | Resets the NN                              |

| 0x08        | UPLOAD FIRMWARE   | Uploads a new firmware to the NN           |

| 0x09        | DOWNLOAD FIRMWARE | Downloads the current firmware of the NN   |

| 0x0A        | SPIKE REPORT      | Downloads the spike report of the NN       |

| 0x0B        | RASTER REPORT     | Downloads the raster report of the NN      |

| 0x0C        | OTHER PROTOCOL    | Send a communication frame to the ports    |

| 0x0D        | ERROR             | An error has occurred                      |

| 0x0E        | HEARTBEAT         | Sends a heart beat signal to test the com. |

| 0x0F        | GET SPIKE         | Gets the new spike that has been generated |

| 0x10 - 0x7F | Reserved          | Reserved for future revisions              |

Table 4: List of commands that will support the first revision of the protocol

### 3.2. LiveSNN program

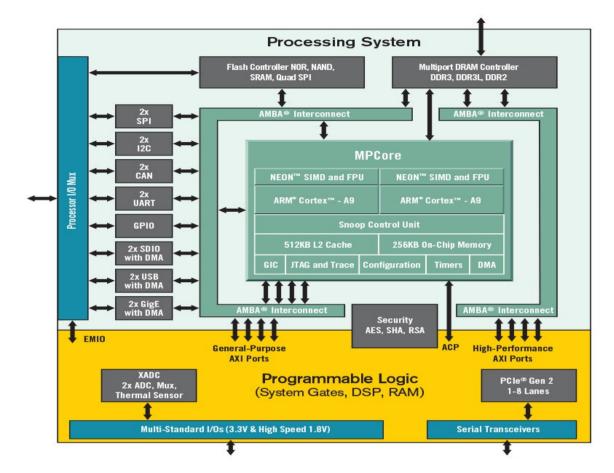

The ZYNQ is a family of System On Chip (SoC) where it contains 2 ARM processor units with a high preformance FPGA, where is capable of designing hardware accelerators to help the ARMS and hardware designs where the ARMS can be used as a monitor and control for the hardware.

As explained before, the HEENS in the ZYNQ has several ARM Cortex processors. With those cores, a diagnostic and SCADA control could be implemented in order to assist the neural network. This logic needs to solve several challenges due to the necessities of the architecture. Those needs are:

- Monitor the HEENS processors

- Update memory banks of the HEENS architecture for updates, debugging, etc

- Supervise and control the architecture

- Bring connectivity from/to the HEENS to a remote computer

As such, and to maintain compatibility between the ZYNQ and the ZYNQ ultrascale+, two cores are used to implement the software.

# **3.2.1.** Selection of the program architecture

The ZYNQ can be programmed in different modes: Linux OS, Real Time OS and bare metal. Each framework have its own characteristics

# **3.2.1.1. Bare metal**

This framework is the most simple one. It is programmed on C, C++ and assembler. In this framework, the code is deterministic because the program follows a sequential flow. It also may contain interrupts, where the sequential execution is broken in order to generate a response from a external signal, that is usually is high priority. For example, in Real Time Operating Systems uses a internal timer called SysTick where it triggers an interruption when certain time has passed in order to execute the scheluder, a piece of code that manages the current active tasks.

# **3.2.1.2. Real Time Operating System (RTOS)**

This type of operating system is focused on having two main characteristics:

- Give processor the capability to execute multiple threads with an scheluder.

- The threads need to be deterministic in time, in order to ensure that the critical tasks are being executed in the required time slots.

One example of this type of RTOS is FreeRTOS[6]. This RTOS is very small, optimized for embedded projects. Some key aspects of this is that it is free and open source, giving this RTOS an advantage among the rest with the huge forum and documentation pages.

# 3.2.1.3. Linux Operating System (Petalinux)

This type of OS is focused on having the same user experience as a normal Linux distro as much as possible taking into account the limitations of the ZYNQ SoC. Petalinux[7] is the OS that the company Xilinx have adapted to their products.

### 3.2.1.4. Summary

By examining the characteristics of each solution for the code in the ARM, the following table is implemented:

| Parameter                             | Petalinux | FreeRTOS   | Baremetal |

|---------------------------------------|-----------|------------|-----------|

| Memory overhead                       | Biggest   | Medium     | None      |

| Time overhead                         | Biggest   | Small      | None      |

| Developing time                       | Shortest  | Normal     | Longest   |

| Code already imp. (libs)              | Most      | Some       | Little    |

| Memory and Execution time determinism | None      | Controlled | Yes       |

| Speed execution                       | Slowest   | Normal     | Fastest   |

| Programming languages                 | All       | C++/C/ASM  | C++/C/ASM |

Table 5: Comparison between the different approaches to program the ARMprocessor

For the characteristics of this project, the FreeRTOS is chosen. It is true that Petalinux has a lot of things readily available, but it uses both cores. Also, it has the biggest penalty on the memory and time overhead, due to all the code that it is being executed. The ZYNQ SoC has two ARM cores, so the second one will be dedicated to the HEENS SNN in order to monitor and transfer information between the core 0 and core 1. As the code needs to be fast and it needs to be fully deterministic, the baremetal framework is chosen.

### **3.2.2. Program architecture**

As the ZYNQ has two cores, the tasks will be split by role. The different tasks between the control of the HEENS and the communications, giving an extra layer of security.

Figure 12: ZYNQ 7 family architecture from [11]

The Fig. [12] shows the diagram of the ZYNQ 7 family with the two ARM cortex A9.

The master core is in charge of the communications. As mentioned before, this core will be implementing the FreeRTOS as working framework. Also, as mentioned before, the slave core is in charge to supervise and control the neural network. As such, it will be programmed in baremetal framework, where there is no operating system nor any compatibility layer between the code and the core itself. This splits the control of the neural network by using specific methods and registers, giving the extra security mentioned before.

With this, the software architecture to be developed follows an asymmetric architecture.

# 3.2.2.1. FreeRTOS

As indicated before, the RTOS used is FreeRTOS[6] due to characteristics. It is a small, fully featured, low level and free RTOS. The communication program doesn't need a lot of features due to the low level processing that needs to be done. As such, the only RTOS elements that will be used are mutex, semaphores and tasks to be able to give service to the different communication protocols that will be handled.

### **3.2.2.2. Context handler**

The context handler is a data structure with pointers to send and receive methods that is commonly used for the different tasks of the main core. The important thing of this structure is that it generalizes the communication ports for STD\_IN and STD\_OUT for code reuse, as the context handler has the information of where the information is coming from and where is leaving to. This produces a layer of isolation between two tasks that communicates to the external world.

A clear example is the shell class. It contains the methods to use a basic shell in some communication port. The TELNET and the serial port uses this class. So, without the context handler, the information is shared among all the instances, and the information of the TELNET session leaks into the serial. That means that the things that are written in the TELNET is also shown in the serial. The problem is also valid in the other way around. The serial can leak information to the TELNET shell.

With context handler, the output and input functions for the data are defined in the context, so the input and output comes with the context, so there is no data leak from telnet to the serial port, because to do that the data must go from one context handler to the other, and this is very difficult, due to the fact that the context handlers are used and instantiated independently in different classes.

| Name    | Туре     | Describe                                           |

|---------|----------|----------------------------------------------------|

| word    | string   | Stores a word from the command stored in str       |

| str     | string   | Stores the command that has been received          |

| lastStr | string   | Stores the previous command that has been executed |

| ix      | uint16_t | Current position of the word in str                |

| handler | int32_t  | ID for the send and receive methods                |

| Sendfnc | sendfn_t | Send function in order to send the responses.      |

Table 6: Fields of the context handler structure

### 3.2.2.3. Tasks

The program needs to handle several scenarios. It is divided in several tasks with the mission to handle each scenario. In addition, a logging system is developed in order to monitor the state of the tasks form the main core and shared to the slave core. With this approach, the programmer will have full state information with only listening one core.

In order to have uniformity between the different tasks, a set of interfaces has been developed in order to keep at minimum code duplication and generalize and add layers of abstraction.

The ITask interface has the following methods to be implemented:

- InitTask(void \*p): This function will be called when the task is started

- Task(void \*p): This function will be called periodically. If the function returns a number different to 0, the task will be finished.

- EndTask(void \*p): This function will be called when the task is finished

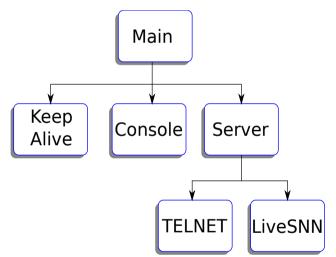

Figure 13: Task creation order, where main is the entry point of the ARMs program

As shown in the Fig. [13], the main block is the entry point of the program, and it creates three different tasks:

- The KeepAlive task, where checks the integrity of the ARM processors

- The Console task: which manages the serial console for debugging

- The Server task: where manages the ethernet connections and spawns the tasks Telnet and LiveSNN tasks to manage the connections from the different ports.

### 3.2.2.3.1. KeepAlive

This task is in charge of monitoring the SoC and make sure that the cores and the HEENS architecture do not stall or have any problem that will lead to the stall of the system. In order to address this problem, the ARMs watchdog is enabled and giving the running signal for the cores and checks the HEENS state if the sequencer has stopped. In addition, for visual inspection, a blinking led is programmed.

In case of partial stall of a core, the watchdog resets the stalled core and notifies the system into recovery mode, where the other core helps to configure the stalled core. In case of the sequencer is stalled, the slave core starts to get the sequencer info and executes a sequencer reset. Then it loads the contents of the sequencer to resume normal operation.

If any error occurs, it is logged into the terminal and in a file in a non volatile storage system like an SD card or USB for further diagnostics.

### 3.2.2.3.2. Console

The mission of this task is to have a low level interaction level between the ZYNQ with a PC via a serial connection. It manages the commands described in the shell section. It also outputs the log data in the command to be able to follow the program execution and have basic diagnostic tools in real time.

The implemented commands are:

| Command    | Name                | Description                               |

|------------|---------------------|-------------------------------------------|

| deviceInfo | Device Information  | Gets the device descriptor                |

| gsd        | Generate Spike Data | Gets the spike data buffer and decodes it |

| help       | Help                | Prints all the available commands         |

| ipconf     | IP Configuration    | Gets the IP configuration                 |

| rb         | Read Byte           | Read 1 byte in the RAM memory of the ARMs |

| reboot     | Reboot              | Performs a full system reset              |

| rm         | Read Memory         | Read memory with the specified length     |

| tasks      | Tasks               | Print the Task status                     |

| tasksInfo  | Tasks Information   | Show current task info                    |

| ver        | Version             | Print software version                    |

| wm         | Write Memory        | Write memory                              |

| ww         | Write Word          | Write 1 word in the memory                |

Table 7: List of supported commands in the terminal

The only commands that require arguments are the read and write operations.

- For the read, the address and then the length (only for the rm) is required.

- For the write is the same as the read, with the last argument being the data to be written.

### 3.2.2.3.3. Server

This task is the most complex of all. It is in charge of setting up the Ethernet stack, manage the connections and sort them between the different ports. In addition, it spawns the TELNET and LiveSNN tasks when a successful connection is detected. As the current configuration, only one connection per port is allowed.

The Ethernet stack is provided by the Lightweight Internet Protocol (LwIP) library provided by Xilinx, but minor bugs have been detected that do not compromise the execution of the task.

### 3.2.2.3.4. TELNET

This task allows the remote access of the console via TELNET protocol. So, the access of the console does not need to be in physical proximity, the only thing is to have Ethernet connection to the SoC. The only drawback of this method is the startup sequence of the processors is not shown due to the Ethernet initialization procedure. The used port is 23.

#### 3.2.2.3.5. LiveSNN

This task manages all the LiveSNN protocol. It has the protocol built in and generalized for any physical media. As such, with the proper context instance, the protocol could be used. The used port is the 8080.

#### 3.2.2.4. Shell

For an easy debug of the cores and the neural network, a lightweight shell is programmed in the software. This shell gives low level control for the ARMs and the neural network.

This shell is context-free, so multiple users can access the shells and work without any information being leaked. The tasks automatically use a mutex in order to protect the different commands that the different users could send.

### **3.3. HEENS Toolchain Suite**

In this chapter, the toolchain developed the HEENS architecture is explained. In the previous version, a common python file contains the properties of the HEENS spiking processor, a assembly code which contains the neuron model, a netlist file containing the synapses in a grid based identification and a CSV with the neural parameters.

# 3.3.1. Netlist V1

The previous version of the netlist synthesis reads two input files, a netlist file and a memory CSV data descriptor.

The netlist contains every synapse of the network. Each row in the netlist is a synapse entry. It specifies everything that is related to that synapse. It is grouped into 4 groups, arranged in a continuous line separated by commas, like an CSV file:

0, 1, 1, 1, 1, 0, 1, 1, 1, 4131127296

1, 0, 1, 1, 0, 2, 0, 1, 2, 4131127296

Each entry has the following format:

| Туре           | Position | Format     | Example    |

|----------------|----------|------------|------------|

| Source neuron  | 0 - 3    | i, v, r, c | 1, 0, 1, 1 |

| Dest. neuron   | 4 - 7    | i, v, r, c | 0, 2, 0, 1 |

| Synapse number | 8        | S          | 2          |

| R0 and R1 data | 9        | data       | 4131127296 |

Table 8: Fields of a entry in the old netlist

The output of the netlisting process takes the synapses and generates the data for the LCL-RAM memories, which preform the input spike decoding.

The other file used in the netlist is a CSV file, where is a memory dump to be loaded in the SN-RAM memories, that contain the local synaptic and neural parameters.

A file example is shown in Annex 8.3.

# 3.3.2. Assembler V1

The assembler used only compiles the code with a given instruction set and generates the compiled version. This process is done in a two step process, where the first step detects the labels, and the second step translates the instruction. In addition, it uses the parameter file to configure the assembler to work properly with the current configuration. The instruction set is described in a CSV file, which it allows to add, modify and remove the instructions in a fast way.

NOP,0b00000,0

LDALL,0b000001,1

A file example is shown in Annex 8.4.

### 3.3.3. Problems

The problem arises on the description of the neural network, that as in this process has as an input 3 different files. Those files contain information that depends on the others. In addition, the assembler code also needs the information of the network in order to operate correctly. So, depending on the application, if a modification is desired, it is probable that a parameter in one of the files has not been updated.

In addition, the debug of the code and/or the network is obfuscated by the fragmented information of the several files used.

# 3.4. <u>Proposed solution: HTS</u>

The problem is the definition of the assembly code and the netlist. The proposal is a redefinition of both files in order to synthesize the same information in a less, more general format. With this, tree toolchains have been develop: the HEENS Code Assembler (HCA), HEENS Neural Synthesis (HNS) and the HEENS high Level Neural Synthesis (HLNS). All the files support comments via the token '\#' and numbering is supported for negative and positive integers, with base 10 and base 16, with the prefix '0x'.

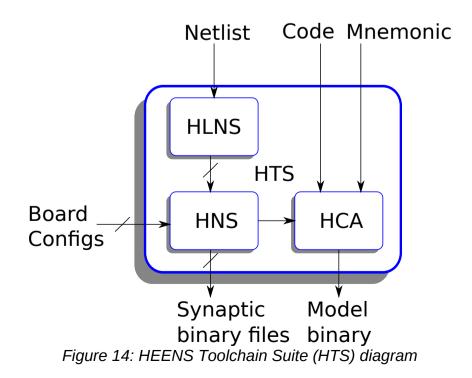

# 3.4.1. HEENS Toolchain Suite (HTS)

This tool is the basic compiler for the HEENS architecture. As input, a netlist descriptor and an assembly code of the model is used. Then, it generates all the memory information for the system. Keywords are used in the assembly to determine all the data related to the network. The toolset organization is shown in Fig. [14].

The HTS process starts with the HEENS Neural Synthesis (HNS), which takes the netlist of the neural network to be synthetized and generates the memory dumps in order to be able to simulate. Then generates tcl scripts to load this information into the vivado project and finally generates a summary for the HEENS Code Assembler (HCA) specifying the necessary info to compile the assembly code into a binary file.

The HEENS High Level Netlist Synthesis (HLNS) is an add-on feature for high-level synthesis that will be explained later.

### 3.4.2. HEENS Neural Synthesis (HNS)

The new proposed format for the netlisting has the same information as the three files. As such, a marker is introduced to differentiate the parts. It is divided into 3 main sections:

- @Config: several rows with the characteristics of the board that is being synthesized with.

- @Netlist: the netlist of the network, with similar structure as the previous version.

- @Params: the parameters that will be inserted into the SN-RAM, with meta information for the HCA tool.

Each section contains the related data in each row. Those rows are called entries.

### 3.4.2.1. Configuration section

This section of the netlist defines the parameters of the architecture version for the neural network to be deployed. It specifies all memories and registers. Each entry has the following format:

| Туре          | Example |

|---------------|---------|

| Variable name | ID      |

| Separator     | =       |

| Variable data | 2       |

Table 9: Entry format of the low level configuration

With this format, it is easy to check and edit the configuration of the architecture to be deployed. All the parameters needed to be specified are:

| Field | Example     | Description                      |

|-------|-------------|----------------------------------|

| Id    | Id = 0      | Id of the chip to be synthesized |

| Rows  | Rows = 4    | Number of rows of the PE         |

| Cols  | Cols = 4    | Number of columns of the PE      |

| VLay  | VLay = 8    | Number of virtual layers         |

| RegS  | RegS = 16   | Register size of the PE in bits  |

| RegN  | RegN = 8    | Number of registers in the PE    |

| SneS  | SneS = 32   | Size of the SN-RAM in bits       |

| SneA  | SneA = 1024 | Address depth of the SN-RAM      |

| LcIS  | LcIS = 7    | Size of the LCL-RAM in bits      |

| LcIA  | LcIA = 128  | Address depth of the LCL-RAM     |

| InsS  | InsS = 16   | Size of the INS-RAM in bits      |

| InsA  | InsA = 1024 | Address depth of the INS-RAM     |

| DlyS  | DlyS = 5    | Size of the DLY-RAM in bits      |

| DlyA  | DlyA = 256  | Address depth of the DLY-RAM     |

| CnvS  | CnvS = 7    | Size of the CNV-RAM in bits      |

| CnvA  | CnvA = 2048 | Address depth of the CNV-RAM     |

| CodS  | CodS = 5    | Size of the COD-RAM in bits      |

| CodA  | CodA = 512  | Address depth of the COD-RAM     |

Table 10: Fields of the configuration section

### 3.4.2.2. Netlist section

The new netlist shares the same definition as the old one, but with two modifications. The first one is that every chip will have it's own netlist file, so the chip ID of the destination neuron is irrelevant due to the fact that the chip id is defined in the @Config section.

The other one is the data part, which holds the synapse. In the old format, the data is merged into a 32bit numeric, containing in the upper half word the R1 value and the lower part the R0 value. In the current models, the synaptic weight is stored in the R1 register, giving a difficult number to deal with. In the proposed format, the register values are kept separated into two fields. The first one contains the R0 register value, where the second one contains the R1 register value. With this, both values are stored in a friendly format, with the capability to use positive and negative numbers, without the fear to override any value in the other register.

| Туре           | Position | Format     | Example    |

|----------------|----------|------------|------------|

| Source neuron  | 0 - 3    | i, v, r, c | 1, 0, 1, 1 |

| Dest. neuron   | 4 - 6    | V, r, C    | 2, 0, 1    |

| Synapse number | 7        | S          | 2          |

| R0 and R1 data | 8 - 9    | data       | 0, -2500   |

Table 11: Field description of the synapse connection in the low level netlist

As an example, a entry will be:

1, 0, 1, 1, 2, 0, 1, 2, 0, -2500

It is smaller and easier to specify the value of the synapse.

### 3.4.2.3. Parameters section

In the last section of the netlist, it appears the parameter definition. The format is simple, it only contains several instances of parameters. Each instance contains a header and a data dump.

The header always starts with a '.' marker, giving a easy way of detecting the start of each instance, followed by the metadata separated by '/'.

| Field    | Example | Description               |  |

|----------|---------|---------------------------|--|

| Address  | 0x3E3   | Address to store the data |  |

| Encoding | 16      | Expected data size        |  |

| Varname  | NEUR    | Associated variable name  |  |

Table 12: Field description of the parameter declaration in the low level netlist

With this, a possible example of a header will be:

#### .0x3E3/16/NEUR

Then, the data to be loaded will be represented in a CSV format, where:

- The number of columns shall match with the number of PEs in the codification of the SneS parameter, with the PEs in ascending order (if size is 32bit, codification of 16bit in a 4x4 array, a list of 32 16-bit numbers is mandatory)

- Each row specifies the address offset, starting with the specified address in the header.

In this way, the user has control on the data on the registers and the address allocation, with the columns giving the PE number and the row giving the offset of the base address.

There are some exceptions for the name of the variables, which are data that generates according common parameters. The excluded words are:

- The mnemonics of the instructions

- NVL: stores the Number of Virtual Layers used

- S\_X: stores the number of Synapses of the layer X

A file example is shown in Annex 8.6.

#### 3.4.3. HEENS Code Assembler (HCA)

The HEENS Code Assembler is specifically design from scratch with the same specifications that the previous one has, with some extra functionalities:

- Dynamic instruction set, which it is specified in a CSV file.

- Macro instructions to be defined also in the CSV to be as flexible as possible.

- Control on the memory placement of the code and variables.

- Optimization levels for efficiency enhancement.

- Virtual variables specified in the netlist.

- Keywords that contain specific data about the neural network.

In order to accomplish those goals, keywords and directives are added to help some functionalities. The directives are the text that starts with a '.'.

| Keyword | Example    | Description                                       |  |

|---------|------------|---------------------------------------------------|--|

| Vx      | LOOPV V0   | Gives the size of the virtual layer x             |  |

| NVL     | LOOP NVL   | Gives the effective virtual layers                |  |

| .org    | .org 0x10  | Sets the origin to start placing the data or code |  |

| .data   | .data 0x04 | Sets the current address for data                 |  |

| .code   | .code      | Sets the current address for code                 |  |

Table 13: Keywords reserved to the HCA

The instruction set is defined in an external CSV file, with 4 elements per row. The codification is as follows:

| Function          | Example             | Description                   |

|-------------------|---------------------|-------------------------------|

| Mnemonic          | LOOPV               | Instruction name              |