**Boston University**

OpenBU

http://open.bu.edu

Theses & Dissertations

Boston University Theses & Dissertations

2021

# Accelerated long range electrostatics computations on single and multiple FPGAs

https://hdl.handle.net/2144/41923 Boston University

## **BOSTON UNIVERSITY**

## COLLEGE OF ENGINEERING

Thesis

## ACCELERATED LONG RANGE ELECTROSTATICS COMPUTATIONS ON SINGLE AND MULTIPLE FPGAS

by

## **ANTHONY DUCIMO**

B.S., Worcester Polytechnic Institute, 2012

Submitted in partial fulfillment of the

requirements for the degree of

Master of Science

2021

© 2021 by ANTHONY DUCIMO All rights reserved

## Approved by

First Reader

Martin C. Herbordt, PhD Professor of Electrical and Computer Engineering

Second Reader

Wenchao Li, PhD Assistant Professor of Electrical and Computer Engineering Assistant Professor of Systems Engineering

Third Reader

Tom VanCourt, PhD Software Engineer Akamai Technologies

Find your light and keep it ever at your front, lest you be resigned to chasing shadows.

— Anonymous

### Acknowledgments

I would like to take this opportunity to thank my advisor, Prof. Martin Herbordt. Despite being a part-time student, never having registered for a course with him, and being candid about a prior unsuccessful project venture, he decided to take me on as an advisee. Shortly thereafter, he tasked me with very fulfilling research work in the MD area. Any and all successes stemming from this thesis are credited to his patience in dealing with my inexpertise and his resourcefulness in playing to my strong suits.

Thank you to my Thesis committee, Professor Wenchao Li and Dr. Tom VanCourt. It means a lot to take time out of your busy schedules to review drafts of this document and assess the accomplishments reported here, not to mention the risk of sponsoring someone you have never met.

Many thanks to my mates in the CAAD lab. They say that saints often realized just how far away they were from Godliness as they seemingly, increasingly approached it. Working with these brilliant people was a great and humbling experience, often times leaving me to desire more from myself. To Tong Geng and Chunshu Wu, my *de facto* project leads, thank you for picking up where my ineptitude or lack of effort left off. To Rushi Patel, thank you for allowing me to take on the effort you started and for the questions answered and advice offered early on in this thesis effort. Thank you to Sahan Lakshitha Bandara for providing solid design implementation advice despite having joined us halfway through this effort. Thank you to Anqi Guo for all the MS Thesis preparation device you offered, I made great use of it. Lastly, but equally as importantly, thank you to Robert Munafo and Pierre-François Wolfe. Though not directly involved in this project, they managed to keep all the infrastructure up and running smoothly so that I could accomplish all of my tasks, including the ones listed here, but perhaps more importantly, the ones that are taken for granted.

I'd like to take this opportunity to thank Intrinsix Corp. who had to put up with my fluid

scheduling not only throughout this effort, but over the 4.5 years of my part-time Master's career. The work opportunities afforded to me as their employee have polished me much like a stone tumbler, but given the results so far, I would not have it any other way. The methods and techniques learned by working on numerous projects were greatly utilized in this thesis effort and allowed me to accomplish many things in a relatively short amount of time.

To my mother, whom I lost in the first year of this 4.5 year journey, I am most thankful to you. Looking back on things, you were solely responsible for instilling in me the desire to learn. Without that, I probably would have never even considered pursuing my Master's degree. It's tragically ironic how this desire to learn, which brought us together in my earliest years, is responsible for the neglect I sent your way in your final couple of years. This guilt I continue to carry will never go away, but I take some some solace in knowing that you are forever proud of all my accomplishments, no matter how trivial they may be.

To my father, though your years of raising a family as a single parent following mom's illness may not earn you any medals or trophies, it is laudable and never goes unappreciated. You kept our family together, made sure that we were all fed and cared for, and continued to push education as the end goal for all of us kids. Thank you always being there and for continuing to be there for us even if we are all well into our adulthood.

Lastly, thank you to all my friends, coworkers, and family who I have not already mentioned. Your constant encouragement did not go unnoticed and your striving to keep me sane in some of the more hectic moments of this Master's career is something I cannot and will not forget.

## ACCELERATED LONG RANGE ELECTROSTATICS COMPUTATIONS ON SINGLE AND MULTIPLE FPGAS

## **ANTHONY DUCIMO**

### ABSTRACT

Classical Molecular Dynamics simulation (MD) models the interactions of thousands to millions of particles through the iterative application of basic Physics. MD is one of the core methods in High Performance Computing (HPC). While MD is critical to many high-profile applications, e.g. drug discovery and design, it suffers from the strong scaling problem, that is, while large computer systems can efficiently model large ensembles of particles, it is extremely challenging for *any* computer system to increase the timescale, even for small ensembles. This strong scaling problem can be mitigated with low-latency, direct communication. Of all Commercial Off the Shelf (COTS) Integrated Circuits (ICs), Field Programmable Gate Arrays (FPGAs) are the computational component uniquely applicable here: they have unmatched parallel communication capability both within the chip and externally to couple clusters of FPGAs. This thesis focuses on the acceleration of the long range (LR) force, the part of MD most difficult to scale, by using FPGAs.

This thesis first optimizes LR acceleration on a single-FPGA to eliminate the amount of on-chip communication required to complete a single LR computation iteration while maintaining as much parallelism as possible. This is achieved by designing around application specific memory architectures. Doing so introduces data movement issues overcome by pipelined, toroidal-shift multiplexing (MUXing) and pipelined staggering of memory access subsets. This design is then evaluated comprehensively and comparatively, deriving equations for performance and resource consumption and drawing metrics from previously developed LR hardware designs. Using this single-FPGA LR architecture as a base, FPGA network strategies to compute the LR portion of larger sized MD problems are then theorized and analyzed.

This thesis has seven chapters. Chapter one formally introduces the topic with additional detail. Chapter two provides the theoretical background for MD, honing in on LR and its computational approximations while highlighting related work that either directly or indirectly sets the foundation for the single-FPGA LR hardware design. Chapter three discusses the single-FPGA LR accelerator hardware, detailing architectural the features as they relate to the theoretical background of MD and system performance. Chapter four evaluates the hardware, providing performance and resource consumption metrics from actual FPGA implementations, while drawing comparisons to pre-existing hardware solutions. It also provides a means of extrapolating both performance and resource consumption to larger MD sizes. Chapter five discusses single-development-board solutions to MD sizes that cannot fit on a single-FPGA alone. Chapter six expands hardware solutions for large MD sizes to networks of FPGA-boards. Chapter seven draws conclusions on the hardware designs, both developed and theorized, and lays out future work to be performed as a result of what was accomplished in this thesis.

## Contents

| 1 | Intr | oduction                                              | 1  |  |  |  |  |  |

|---|------|-------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1  | Molecular Dynamics acceleration for strong scaling    |    |  |  |  |  |  |

|   | 1.2  | Real World Applicability                              |    |  |  |  |  |  |

|   | 1.3  | Contributions                                         | 5  |  |  |  |  |  |

|   | 1.4  | Outline                                               | 6  |  |  |  |  |  |

| 2 | Bac  | ground                                                | 7  |  |  |  |  |  |

|   | 2.1  | Molecular Dynamics Overview                           | 7  |  |  |  |  |  |

|   | 2.2  | Computing the Long Range Force                        | 9  |  |  |  |  |  |

|   | 2.3  | Previous Work and Design in FPGA Acceleration of MD   | 0  |  |  |  |  |  |

|   |      | 2.3.1 FPGA Architecture for HPC                       | 0  |  |  |  |  |  |

|   |      | 2.3.2 FPGA Acceleration of HPC                        | 1  |  |  |  |  |  |

|   |      | 2.3.3 FPGA Acceleration of MD                         | 2  |  |  |  |  |  |

|   | 2.4  | Previous Work and Design in FPGA Acceleration of LR 1 | 2  |  |  |  |  |  |

|   |      | 2.4.1 Overview of Previous LR Design                  | 2  |  |  |  |  |  |

|   |      | 2.4.2 3D FFT                                          | 3  |  |  |  |  |  |

|   |      | 2.4.3 Particle to Grid Mapping                        | 4  |  |  |  |  |  |

|   |      | 2.4.4 Grid Memory Network                             | 5  |  |  |  |  |  |

| 3 | Sing | le-FPGA LR Design 1                                   | 7  |  |  |  |  |  |

|   | 3.1  | Particle Info Memory                                  | 8  |  |  |  |  |  |

|   | 3.2  | Charge Mapping                                        | 9  |  |  |  |  |  |

|   | 3.3  | Grid Memory                                           | .1 |  |  |  |  |  |

|        |                                                            | 3.3.1                                                                                              | Clustered Grid Memory                                                | 22                                                                                                                     |

|--------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|        | 3.4                                                        | FFT/II                                                                                             | ŦΤ                                                                   | 26                                                                                                                     |

|        | 3.5                                                        | Green'                                                                                             | s Function                                                           | 28                                                                                                                     |

|        | 3.6                                                        | Force                                                                                              | Computation                                                          | 29                                                                                                                     |

|        |                                                            | 3.6.1                                                                                              | Coefficient Generation                                               | 30                                                                                                                     |

|        |                                                            | 3.6.2                                                                                              | МАС                                                                  | 31                                                                                                                     |

|        | 3.7                                                        | Hardw                                                                                              | are Development Summary                                              | 31                                                                                                                     |

| 4      | Sing                                                       | le-FPG                                                                                             | A LR Evaluation                                                      | 33                                                                                                                     |

|        | 4.1                                                        | Impler                                                                                             | nentation Details                                                    | 33                                                                                                                     |

|        | 4.2                                                        | Compu                                                                                              | utation Details                                                      | 39                                                                                                                     |

|        |                                                            | 4.2.1                                                                                              | System Equations                                                     | 40                                                                                                                     |

|        |                                                            | 4.2.2                                                                                              | Computation run-time                                                 | 42                                                                                                                     |

|        | 4.3                                                        | Evalua                                                                                             | tion Discussion                                                      | 42                                                                                                                     |

|        |                                                            |                                                                                                    |                                                                      |                                                                                                                        |

| 5      | Exte                                                       | ending S                                                                                           | Single-FPGA LR Designs: Off Chip Memory                              | 49                                                                                                                     |

| 5      | <b>Exte</b><br>5.1                                         | U                                                                                                  | Single-FPGA LR Designs: Off Chip Memory         for Particle Mapping |                                                                                                                        |

| 5      |                                                            | U                                                                                                  |                                                                      | 49                                                                                                                     |

| 5      |                                                            | HBMs                                                                                               | for Particle Mapping                                                 | 49<br>50                                                                                                               |

| 5      |                                                            | HBMs<br>5.1.1                                                                                      | for Particle Mapping                                                 | 49<br>50<br>50                                                                                                         |

| 5      |                                                            | HBMs<br>5.1.1<br>5.1.2<br>5.1.3                                                                    | for Particle Mapping                                                 | 49<br>50<br>50<br>51                                                                                                   |

| 5      | 5.1                                                        | HBMs<br>5.1.1<br>5.1.2<br>5.1.3<br>HBMs                                                            | for Particle Mapping                                                 | 49<br>50<br>50<br>51<br>51                                                                                             |

| 5<br>6 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>              | HBMs<br>5.1.1<br>5.1.2<br>5.1.3<br>HBMs<br>Viabili                                                 | for Particle Mapping                                                 | 49<br>50<br>50<br>51<br>51                                                                                             |

|        | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>              | HBMs<br>5.1.1<br>5.1.2<br>5.1.3<br>HBMs<br>Viabili                                                 | for Particle Mapping                                                 | 49<br>50<br>50<br>51<br>51<br>52                                                                                       |

|        | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Beyo</li></ul> | HBMs<br>5.1.1<br>5.1.2<br>5.1.3<br>HBMs<br>Viabili                                                 | for Particle Mapping                                                 | <ul> <li>49</li> <li>50</li> <li>50</li> <li>51</li> <li>51</li> <li>52</li> <li>54</li> </ul>                         |

|        | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Beyo</li></ul> | HBMs<br>5.1.1<br>5.1.2<br>5.1.3<br>HBMs<br>Viabili                                                 | for Particle Mapping                                                 | <ul> <li>49</li> <li>50</li> <li>50</li> <li>51</li> <li>51</li> <li>52</li> <li>54</li> <li>54</li> <li>55</li> </ul> |

|        | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Beyo</li></ul> | HBMs<br>5.1.1<br>5.1.2<br>5.1.3<br>HBMs<br>Viabili<br><b>ond Sing</b><br>Direct-<br>6.1.1<br>6.1.2 | for Particle Mapping                                                 | <ul> <li>49</li> <li>50</li> <li>50</li> <li>51</li> <li>51</li> <li>52</li> <li>54</li> <li>54</li> </ul>             |

| Cı | Curriculum Vitae 9                      |        |                      |    |  |  |  |  |

|----|-----------------------------------------|--------|----------------------|----|--|--|--|--|

| Re | References                              |        |                      |    |  |  |  |  |

| A  | A Ring Network Orthogonal FFT Messaging |        |                      |    |  |  |  |  |

|    | 7.2                                     | Future | Work                 | 79 |  |  |  |  |

|    | 7.1                                     | Conclu | usion                | 78 |  |  |  |  |

| 7  | 7 Conclusions and Future Work           |        |                      |    |  |  |  |  |

|    | 6.5                                     | Discus | ssion                | 73 |  |  |  |  |

|    | 6.4                                     | Perfor | mance Analysis       | 68 |  |  |  |  |

|    |                                         | 6.3.2  | Inter-FPGA Messaging | 65 |  |  |  |  |

|    |                                         | 6.3.1  | Architecture         | 64 |  |  |  |  |

|    | 6.3                                     | Bidire | ctional Ring         | 64 |  |  |  |  |

|    |                                         | 6.2.2  | Inter-FPGA Messaging | 60 |  |  |  |  |

## **List of Tables**

| 1.1 Computational Biology MD Modeling Examples. Table adapted from (Sh |                                                                |   |  |  |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------|---|--|--|--|--|

|                                                                        | et al., 2007; Proctor et al., 2011; Shirvanyants et al., 2012) | 4 |  |  |  |  |

| 4.1                                                                    | Configuration Summary of Single-FPGA LR Implementations        | 3 |  |  |  |  |

| 4.2                                                                    | Run-Times Following DSP Resource Redistribution                | 8 |  |  |  |  |

## **List of Figures**

| 2.1 | Lennard-Jones Force Plot                                                 | 8  |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | LR Evaluation Architecture Overview (Yang et al., 2019a)                 | 12 |

| 2.3 | Block Diagram for 3D FFT Design (Humphries et al., 2014)                 | 14 |

| 2.4 | Previously Developed Particle-to-Grid-Memory Flow (Yang et al., 2019a) . | 15 |

| 2.5 | 2D Example Motivating an Alignment Network (Gu and Herbordt, 2007) .     | 16 |

| 3.1 | Enhanced Single-FPGA LR System Block Diagram                             | 17 |

| 3.2 | Particle Positioning (Sanaullah et al., 2016c)                           | 19 |

| 3.3 | Memory Access Patterns for Charge Mapping in 3D                          | 24 |

| 3.4 | Three-Stage Toroidal-Shift MUXing Pipeline for Memory Access Alignment   | 25 |

| 3.5 | Memory Access Cluster Slice Staggering for Optimum FFT Throughput        | 27 |

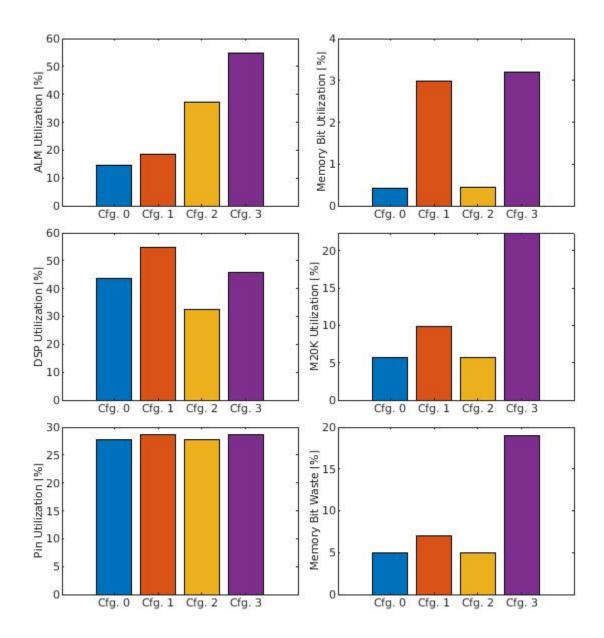

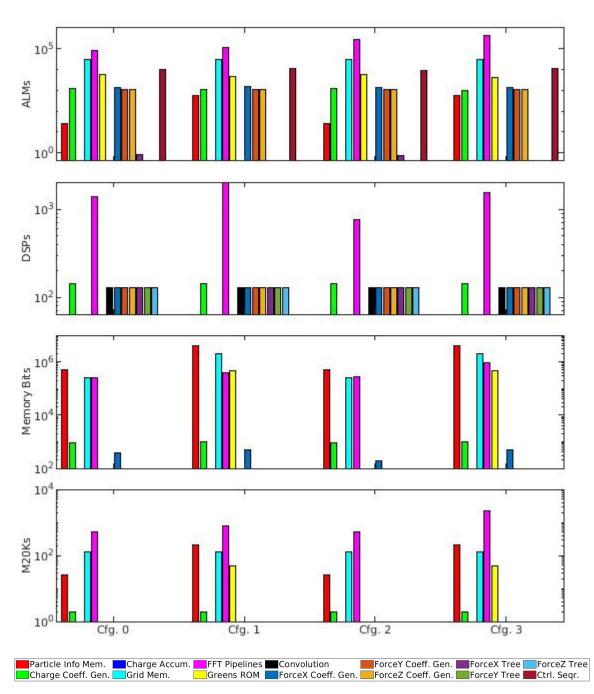

| 4.1 | Device Resource Consumption per Single-FPGA LR Implementation            | 34 |

| 4.2 | Per-Implementation LR Design Resource Consumption Breakdown              | 36 |

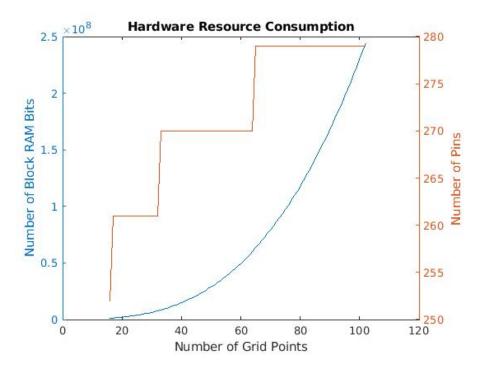

| 4.3 | LR Design Hardware Resource Consumption vs. $gsize_{1D}$                 | 39 |

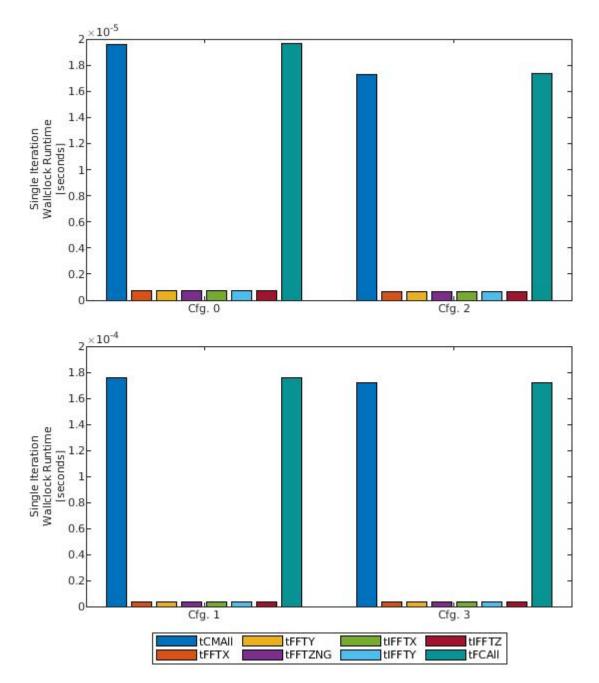

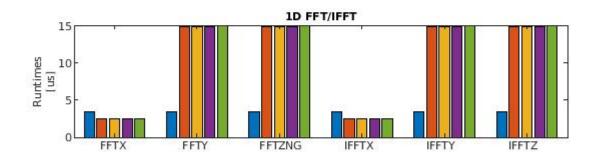

| 4.4 | LR Design Performance Breakdown                                          | 43 |

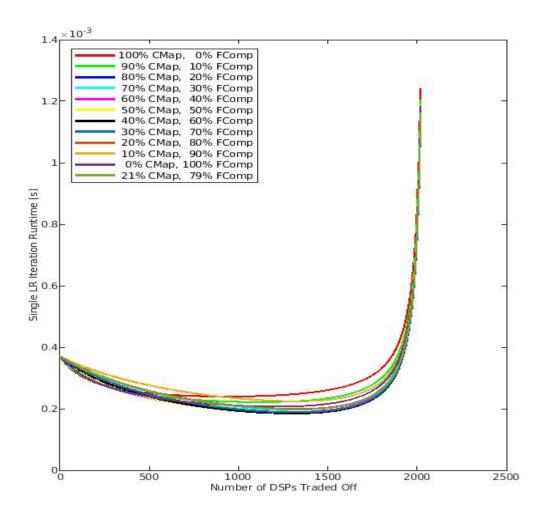

| 4.5 | LR Run-Times vs. DSP Tradeoffs                                           | 47 |

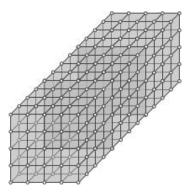

| 6.1 | 2D Direct-Connect Toroidal FPGA Cluster Network                          | 55 |

| 6.2 | FPGA Cluster Node Grid-Prism                                             | 56 |

| 6.3 | Direct-Connect Particle Info Messaging                                   | 56 |

| 6.4 | Direct-Connect Last Particle Info Messaging                              | 57 |

| 6.5 | Direct-Connect Second Dimension FFT Messaging                            | 58 |

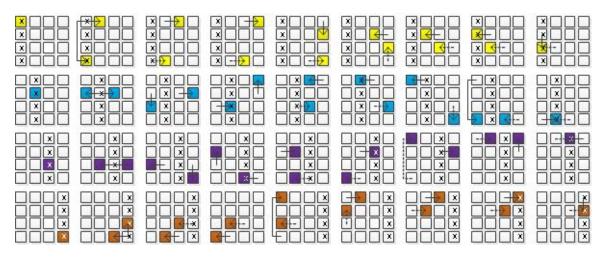

| 6.6  | Direct-Connect Force Computation Messaging                    | 59 |

|------|---------------------------------------------------------------|----|

| 6.7  | All-to-All Two-Link Particle Info Messaging                   | 61 |

| 6.8  | All-to-All Two-Link Last Particle Info Messaging              | 61 |

| 6.9  | All-to-All One-Link Particle Info Messaging                   | 62 |

| 6.10 | All-to-All One-Link Last Particle Info Messaging              | 62 |

| 6.11 | All-to-All One-Link Second Dimension FFT Messaging            | 63 |

| 6.12 | All-to-All Force Computation Messaging                        | 64 |

| 6.13 | Ring-Connected 2D Matrix FPGA Cluster Network                 | 65 |

| 6.14 | Ring Unidirectional Particle Info Messaging                   | 65 |

| 6.15 | Ring Bidirectional Particle Info Messaging                    | 66 |

| 6.16 | Ring Orthogonal FFT Messaging                                 | 67 |

| 6.17 | Ring Force Computation Messaging                              | 68 |

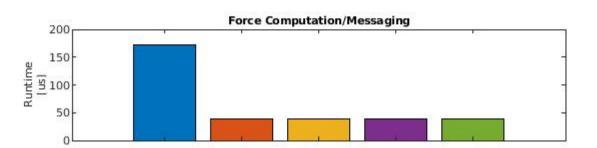

| 6.18 | Single-FPGA and Multi-FPGA LR Design Performance Comparisons  | 74 |

| A·1  | FFT Messaging Table for Ring-Connected 2D Matrix FPGA Cluster | 83 |

## **List of Abbreviations**

| 1D              |                               | One-Dimensional                         |

|-----------------|-------------------------------|-----------------------------------------|

| 2D              |                               | Two-Dimensional                         |

| $\overline{3D}$ |                               | Three-Dimensional                       |

| ALM             |                               | Adaptive Logic Module                   |

| ASIC            |                               | Application-Specific Integrated Circuit |

| BRAM            |                               | Block RAM                               |

| COTS            |                               | Commercial Off the Shelf                |

| CPU             |                               | Central Processing Unit                 |

| DFT             |                               | Design for Test                         |

| DSP             |                               | Design for Test                         |

|                 | ••••                          | Digital Signal Processor                |

| FCC             | • • • • • • • • • • • • • • • | FPGA-Centric Cluster                    |

| FFT             | • • • • • • • • • • • • • •   | Fast Fourier Transform                  |

| FIFO            | • • • • • • • • • • • • • •   | First-In-First-Out                      |

| FLOPS           |                               | Floating-Point Operations per Second    |

| FPGA            |                               | Field Programmable Gate Array           |

| FS              |                               | Femtoseconds                            |

| GBS             |                               | Gigabits per second                     |

| GPU             |                               | Graphics Processor Unit                 |

| HDL             |                               | Hardware Description Language           |

| HBM             |                               | High Bandwidth Memories                 |

| IC              |                               | Integrated Circuit                      |

| IFFT            |                               | Inverse Fast Fourier Transform          |

| IO              |                               | Input/Output                            |

| LR              |                               | Long Range                              |

| MAC             |                               | Multiply-Accumulate                     |

| MD              |                               | Molecular Dynamics                      |

| MGT             |                               | Multi-Gigabit Transceiver               |

| MUX             |                               | Multiplex                               |

| MS              |                               | Milliseconds                            |

| NS              |                               | Nanoseconds                             |

| PME             |                               | Particle Mesh Ewald                     |

| RAM             |                               | Random Access Memory                    |

| RAW             |                               | Read-After-Write                        |

| RL              |                               | Range Limited                           |

| SV              | •••••                         | SystemVerilog                           |

| S V             | • • • • • • • • • • • • • • • | SystemVerilog                           |

## Chapter 1 Introduction

## **1.1 Molecular Dynamics acceleration for strong scaling**

Molecular Dynamics simulation (MD) is a central method in high performance computing (HPC) with applications throughout engineering and science. MD uses an iterative application of Newtonian mechanics on ensembles of atoms and molecules (Rapaport, 2004). Ac*celeration* of MD is a critical problem — there is a many order-of-magnitude gap between the largest current simulations and the potential physical systems to be studied (Tajkhorshid et al., 2003; Shirvanyants et al., 2012). There are dozens of MD packages in production use, e.g. (Case et al., 2005; Phillips et al., 2005; van der Spoel et al., 2005; Eastman and Pande, 2010; Plimpton, 1995), all of which exist in parallel versions and many of which have been accelerated with GPUs. While many of these packages support efficient *weak scaling*, i.e. performance scales with computing resources as long as the problem size scales in proportion, strong scaling remains problematic. That is, for fixed, modest problem sizes, adding significant computing resources does not result in an increase in performance. The failure to support strong scaling is, in large part, the cause of the performance gap. For instance, small problem sizes (20K-50K particles) are common in drug discovery and design (Cournia et al., 2017; NVIDIA, 2017). There, long timescales, on the order of milliseconds per day, would be extremely beneficial, but only hundreds of nanoseconds per day are currently being achieved (Yang et al., 2019a).

The strong scaling problem arises in MD because of the necessarily iterative nature of the application. Each timestep (of force computation and motion update) simulates roughly two femtoseconds (E-15s) of reality; thus simulating a millisecond of reality per day requires that each timestep be computed in hundreds of nanoseconds. The critical path lies with the Long Range Force computation (LR), which requires global communication; this makes accelerating LR a classic strong scaling problem. Large numbers of processors are required to generate sufficient FLOPs, but then proportionally increase the communication time. This disconnect becomes overwhelming when simulating small molecules: applying large computing resources is both unhelpful and extremely wasteful.

The only way to address the strong scaling problem is to reduce communication latency to the barest minimum which, in the end, requires direct communication links–application layer to application layer–among the integrated circuits (ICs) in the cluster. This approach was originally taken by the Grape family of ASIC-based MD processors (Ohmura et al., 2014), but currently being used (with great success) by DE Shaw with the Anton family (Shaw, D.E., et al., 2007; Young et al., 2009; Grossman et al., 2015). But while ASIC-based solutions can have orders-of-magnitude better performance than commodity clusters, they also have issues with general availability, prohibitive cost, plus all the problems inherent with small-run ASIC-based systems.

As is often the case when looking for cost-effective ASIC replacement, FPGAs provide a viable alternative (Gokhale and Graham, 2005; Herbordt et al., 2007; Hauck and DeHon, 2008; Herbordt et al., 2008a; VanCourt and Herbordt, 2009; Benkrid and Vanderbauwhede, 2013). FPGAs have been explored as possible MD accelerators for many years (Azizi et al., 2004; Hamada and Nakasato, 2005; Gu et al., 2006a; Gu et al., 2006c; Gu et al., 2006b; Alam et al., 2007); see (Schaffner and Benini, 2018) for a survey. The first generation of complete FPGA/MD systems accelerated only the range limited (RL) force and used CPUs for the rest of the computation (Gu et al., 2005a; Gu et al., 2005b; Kindratenko and Pointer, 2006; Scrofano et al., 2008). While performance was sometimes competitive, high cost and lack of availability of FPGA systems meant that they were never in production use. In the last few years, however, proof-of-concept studies have shown that FPGA clusters (Pascoe et al., 2010; Khan and Herbordt, 2012; Sheng et al., 2015; George et al., 2016; Sheng et al., 2017a; Plessl, 2018; Miyajima et al., 2018; Boku et al., 2019) can have performance approaching that of ASIC clusters for LR (Sheng et al., 2014; Sheng et al., 2017b; Lawande et al., 2016). These studies, however, only implement the critical path as little more than a microbenchmark; creating a complete LR, even for a single FPGA, remains unstudied.

In this thesis, a state-of-the-art, single-FPGA LR architecture is developed and evaluated. Following the evaluation of this single-FPGA design, the accommodation of larger grid sizes using both a single FPGA coupled with off-chip but on-board memory and a network of FPGAs are explored.

### **1.2 Real World Applicability**

MD can be found at the core of computational chemistry and is central to computational biology. Variations in particle ensemble size are used to model differing biological constructs. Typically, the more complex the structure, the more particles in the ensemble. Over time, these particle interactions can model various biological processes, with more complex processes requiring longer timescales. Table 1.1 lists some of these structures and processes.

Directly applying the equations from Newtonian physics, MD simulations of any particle ensemble size over any timescale can be achieved, but it may take decades, if not centuries, to do so. Single time-steps (typically  $2 * 10^{-15}$ s or 2fs) of reality can be simulated on a single core in around a second for small particle ensembles (< 100*K*). Staying at the protein level, thousand-core and small multi-GPU systems (2-4 GPUs) have been able to simulate 500ns of reality in a single day. Anton 2, a 512-ASIC processor, has been able to model these ensembles for hundreds of microseconds and milliseconds of reality in a day and 16 days, respectively (Grossman et al., 2015). We now give an example of how a physical application requirement translates into a computational requirement. Protein folding involves proteins (10s of thousands of particles) and folding (100s of microseconds to seconds). With a 2fs MD timestep, simulating 20ms of reality requires E13 timesteps. If MD is executed for, say, 10 days, then reality must be simulated at 2ms per day. This translates to E12 timesteps per day or roughly E7 timesteps per second or 1 timestep every 100ns.

| Biological Construct                 |                           |  |  |  |  |

|--------------------------------------|---------------------------|--|--|--|--|

| Туре                                 | Ensemble Size [particles] |  |  |  |  |

| Protein                              | $10^4 - 10^5$             |  |  |  |  |

| Virus                                | $10^{6} - 10^{7}$         |  |  |  |  |

| Chromotophore                        | 10 <sup>8</sup>           |  |  |  |  |

| Bacteria                             | $10^{10}$                 |  |  |  |  |

| Eukaryote                            | 10 <sup>13</sup>          |  |  |  |  |

| Biological Pro                       |                           |  |  |  |  |

| Туре                                 | Timescale Range [s]       |  |  |  |  |

| Chemical Reactions                   | $10^{-15} \cdot 10^{-14}$ |  |  |  |  |

| Backbone Librations                  | $10^{-12} - 10^{-10}$     |  |  |  |  |

| Side-Chain Motions                   | $10^{-11}$ - $10^{-8}$    |  |  |  |  |

| Aromatic Ring Flipping               | $10^{-7} - 10^{-5}$       |  |  |  |  |

| Large Conformational Changes         | $10^{-5} - 10^{-3}$       |  |  |  |  |

| Protein Folding                      | $10^{-4}$ - $10^{1}$      |  |  |  |  |

| Protein Association and Dissociation | $10^{0}$ - $10^{4}$       |  |  |  |  |

| Protein Aggregation                  | $10^3 - 10^4$             |  |  |  |  |

**Table 1.1:** Computational Biology MD Modeling Examples. Table adapted from (Sharma et al., 2007; Proctor et al., 2011; Shirvanyants et al., 2012).

Two observations are made from these results. The first is that adding cores or GPUs does not improve the timescales achieved for small simulations; this is the MD strong scaling problem already described. The second is that there is a factor of 100 difference in performance between the best performance using off-the-shelf processing and the best performance using *heroic* dedicated technology developed at, conservatively, several orders of magnitude greater cost.

This thesis aims to explore the gap between the off-the-shelf and the heroic implementations of MD. The end goal, beyond the current scope, is to implement tightly coupled FPGA clusters with dozens to hundreds of FPGAs. Such a cluster may achieve performance somewhat comparable to Anton 2 — but without having to design a full ASIC or develop such an ASIC network — while using much more recent technology. But the critical next step in this program is to address, on a single FPGA, the most difficult hurdle to achieving MD strong scaling: the efficient evaluation of the long-range force.

### **1.3** Contributions

Contributions of this thesis are as follows:

- LR friendly memory architecture. Application-specific memory interleaving is implemented to simultaneously support a single particle's mapping to its 64 nearestneighboring grid-points in three dimensions and remove the need for the transposition of data prior to successive 1D FFT calculations.

- Novel 1D FFT parallelization. Given the inherent constraints of the applicationspecific memory architecture, a memory access pattern was developed to maximize the parallelization of 1D FFTs.

- 3. **Single-FPGA LR accelerators.** Reusing portions of previously developed designs and deploying some of the above contributions, working single-FPGA LR accelerators were implemented for multiple MD grid sizes and particle ensembles. Solutions for both a 16x16x16 MD grid accommodating 16<sup>3</sup> particles and a 32x32x32 accommodating 32<sup>3</sup> particles were successfully implemented with data suggesting the feasibility for a solution for a 64x64x64 grid accommodating 64<sup>3</sup> particles.

- Better Performance vs. Hardware Tradeoffs. The single-FPGA LR accelerator developed here reduces the LR critical path of MD, enabling the simulation of ensembles on the order of 10<sup>5</sup> particles over hundreds of nanoseconds of reality to

complete in a single day. This performance is achieved with a single FPGA, avoiding the prohibitive resource costs of multi-core systems or ASIC design.

5. Extensions to FPGA clusters. Leveraging some of the features deployed in the single-FPGA accelerators, three multi-node network architectures are proposed to accelerate LR even further. Each network proposal includes high-level analysis of the messaging methods required for the various phases of LR acceleration.

### 1.4 Outline

The remainder of this thesis is broken up into 6 chapters. Chapter 2 provides additional MD background information and discusses prior work. Chapter 3 details the architecture of the single-FPGA LR design. Chapter 4 evaluates the single-FPGA LR design. Chapter 5 discusses the plausibility of using off-chip memory to accommodate larger grid sizes while keeping the entire LR design on a single FPGA board. Chapter 6 proposes multiple FPGA network topologies to distribute large-grid-sized LR problems over. In chapter 7 conclusions are drawn and future work is discussed.

## Chapter 2

## Background

This chapter provides an MD overview. First it is approached from a pure theoretical physics standpoint. Then, methods of MD approximation are introduced along with their aptitude for hardware acceleration. Having laid the groundwork for hardware accelerated MD, this chapter goes on to detail prior work used as the foundation for the design developed in conjunction with this thesis.

## 2.1 Molecular Dynamics Overview

This overview follows material found in similar presentations in a number of excellent texts and surveys, e.g., (Allen and Tildesley, 1987; Haile, 1997; Frenkel and Smit, 2002; Schlick, 2002; Rapaport, 2004). MD models interactions between ensembles of particles by iteratively calculating the forces acting on each particle exhibited by the remaining particles in the ensemble and the movement of each particle caused by the forces acting upon it. The forces computed depend on the system being simulated, but include bonded and non-bonded terms (Haile, 1997):

$$\mathbf{F}^{\text{total}} = F^{bond} + F^{angle} + F^{dihedral} + F^{non-bonded}$$

(2.1)

Direct computation of the first three force components, the bonded forces, each have a complexity of  $O(n_p)$ , whereas direct computation of the non-bonded force is  $O(n_p^2)$ , where  $n_p$ is the number of particles in the ensemble. In order to reduce the computational complexity, computation of the non-bonded forces is typically approximated as discussed below. And because it represents over 99% of the FLOPs it is the part most likely to be performed by hardware accelerators (Essmann et al., 1995; Lee, 2005; Herbordt, 2013).

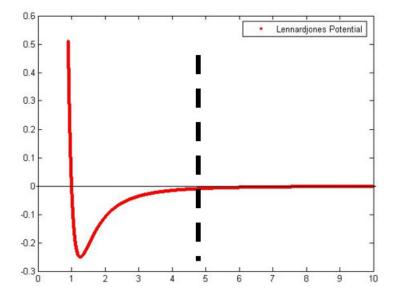

The non-bonded force can be broken up into two forces (Haile, 1997), the Lennard-Jones force :

$$\frac{F_i^{LJ}}{r_{ji}} = \sum_{j \neq i} \frac{\varepsilon_{ab}}{\sigma_{ab}} \left\{ 12 \left( \frac{\sigma_{ab}}{|r_{ji}|} \right)^{14} - 6 \left( \frac{\sigma_{ab}}{|r_{ji}|} \right)^8 \right\}$$

(2.2)

which, as seen in Figure  $2 \cdot 1$ , decays quickly as the radial distance between two particles in the pair increases and the Coulombic Force:

$$\frac{F_i^C}{r_{ji}} = q_i \sum_{j \neq i} \left( \frac{q_j}{|r_{ji}|^3} \right)$$

(2.3)

which does not decay with radial distance. This Coulombic force can be further

Figure 2.1: Lennard-Jones Force Plot

approximated by partitioning it into short-range and long-range components (Haile, 1997). The short-range component of the Coulombic force can be combined with the Lennard-Jones force as the range limited (RL) force, while the long-range component of the Coulombic force is computed on its own as the long range (LR) force.

## 2.2 Computing the Long Range Force

The LR force is calculated by solving the Poisson Equation for the given charge distribution (Haile, 1997).

$$\mathbf{F}_{\mathbf{i}}^{\mathbf{LR}} = \sum_{j \neq i} \frac{q_j}{|r_{ji}|} \vec{\mathbf{r}}_{ji}$$

(2.4)

LR force is often calculated with a grid-based map of the smoothing function converted from continuous space to a discrete grid coordinate system (Young et al., 2009). This method reduces the asymptotic complexity from  $O(n_p^2)$  to  $O(n_g \log n_g)$ , where  $n_g$  is the number of grid-points, and results in the following equation (Procacci, 2009):

$$\mathbf{F}^{LR} \approx \sum_{x=0}^{K_x-1} \sum_{y=0}^{K_y-1} \sum_{z=0}^{K_z-1} \frac{\partial Q(x,y,z)}{\partial r_{ji}} \Theta_{i \ rec} * Q(x,y,z)$$

(2.5)

Each particle is interpolated to grid-points (Q(x, y, z)) by applying the following third-order basis function for charge density calculation (Skeel et al., 2002):

$$\phi(\xi) = \begin{cases} (1 - |\xi|)(1 + |\xi| - \frac{3}{2}\xi^2) & |\xi| \le 1\\ -\frac{1}{2}(|\xi| - 1)(2 - |\xi|)^2 & 1 \le |\xi| \le 2\\ 0 & 2 \le |\xi| \end{cases}$$

(2.6)

where  $\xi$  is the distance between the particle and any grid-point. Grid-points obtain their charge densities from neighboring particles within a range of two grid points in each direction. The resulting charge grid is then convolved with a Green's function ( $\Theta_{irec} * Q(x, y, z)$ )) to transform it into a grid of electrostatic potentials. To simplify convolution, the charge grid is converted from a spatial domain to the Fourier Domain, where convolution becomes a simple multiplication, and then converted back to the spatial domain. The Fast Fourier Transform (FFT) is used to convert to the Fourier domain and the inverse FFT (IFFT) is used to convert back to the spatial domain. Once the grid of electrostatics has been generated, the three directional forces on each particle is calculated by taking the partial derivatives of the mapping function, multiplying the corresponding electrostatic potential grid-points, and summing across all grid points in 3D.

Overall, LR has the following phases.

- 1. Map particles into a charge grid

- 2. Perform 3D FFT

- 3. Perform convolution by multiplication

- 4. Perform 3D IFFT to create force grid

- 5. Map forces onto particles.

### 2.3 Previous Work and Design in FPGA Acceleration of MD

#### 2.3.1 FPGA Architecture for HPC

FPGAs are well-known as ICs with configurable logic; the image is often of a sea of available logic configurable with an appropriate description. More accurate is that the FPGA is actually mostly VLSI building blocks embedded in a sea of configurable interconnects. The three most important building blocks are (i) DSP units, basically multipliers or floating point units; (ii) Block Rams (BRAMs), which are small (1KB) independently accessible multiported memories; and (iii) multi gigabit transceivers (MGTs) for I/O. There are on the order of 10,000 DSPs and BRAMs and 100 MGTs.

A typical FPGA/HPC design uses some fraction of the FPGA's resources in the following design pattern. The working set of data is stored in BRAMs (scratchpads). Computation is performed by custom logic pipelines constructed from DSPs and random logic. Data is streamed from scratchpads through one or more compute pipelines and back to scratch pads. The datapaths among scratchpads and pipelines can be almost arbitrarily complex. The power of FPGA/HPC comes from the efficiency with which applications can be mapped to the hardware. Since control is embedded into the logic, every cycle generates payload. Pipelines are exactly what is required by the application and can be trivially short or hundreds of stages. Data types can be any precision or mode using only the logic needed. Since there are many thousands of scratchpads and DSPs, there can be that many data streams running in parallel. These scratchpads and compute pipelines can be interconnected chip-wide in almost any configuration. Of course some methods are more efficient than others; the most performant FPGA/HPC design patterns are described, e.g., in (Sanaullah and Herbordt, 2018a).

#### 2.3.2 FPGA Acceleration of HPC

While not yet having the penetration of GPUs in HPC, FPGAs have been shown to be a likely component of future HPC systems. Other types of Molecular Modeling accelerated with FPGAs include Molecular Dynamics using Discrete Event Simulation, rather than the timestep driven studies here (Model and Herbordt, 2007; Herbordt et al., 2008b; Herbordt et al., 2009; Khan and Herbordt, 2011) and Molecular Docking, which often uses MD as one of its functions (VanCourt et al., 2004; VanCourt and Herbordt, 2005; VanCourt and Herbordt, 2006b; Sukhwani and Herbordt, 2008; Sukhwani and Herbordt, 2010). Other scientific applications include Adaptive Mesh Refinement (Wang et al., 2019b; Wang et al., 2019a) and Algebraic Multigrid (Haghi et al., 2020b). Of particular interest for FPGA use in computation, especially in data centers, is Machine Learning (Liu et al., 2016; Sanaullah et al., 2018b; Geng et al., 2018b; Geng et al., 2018a; Geng et al., 2019c; Geng et al., 2019b; Geng et al., 2019a; Geng et al., 2020a; Geng et al., 2020b; Li et al., 2019; Shi et al., 2020; Wang et al., 2020a; Wu et al., 2020; Geng et al., 2021). Programmability has often been a problem, but has recently been addressed in design tools (Sanaullah and Herbordt, 2018c; Sanaullah and Herbordt, 2018a; Sanaullah et al., 2018a; Herbordt, 2019) and middleware (Xiong et al., 2018b; Xiong et al., 2018a; Xiong et al., 2019; Xiong et al., 2020; Stern et al.,

2018; Haghi et al., 2020c; Haghi et al., 2020a).

#### 2.3.3 FPGA Acceleration of MD

Prior MD/FPGA studies not otherwise mentioned here include surveys, (Chiu et al., 2008; Sukhwani and Herbordt, 2009; Chiu and Herbordt, 2010b; Herbordt, 2013; Khan et al., 2013), integration (Gu et al., 2006c), RL datapath optimization (Gu et al., 2008), handling neighbor lists in RL (Chiu and Herbordt, 2009; Chiu and Herbordt, 2010a; Chiu et al., 2011), the bonded force (Xiong and Herbordt, 2017), parallel implementations (Pascoe et al., 2020), and complete FPGA integration (Yang et al., 2019b; Yang et al., 2019a).

## 2.4 Previous Work and Design in FPGA Acceleration of LR

#### 2.4.1 Overview of Previous LR Design

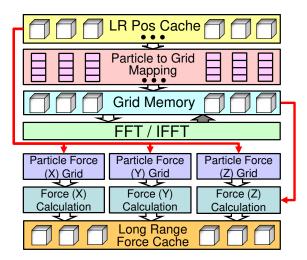

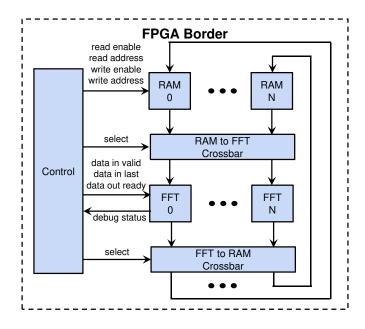

Figure 2.2 depicts LR computation hardware that was previously under development.

Figure 2.2: LR Evaluation Architecture Overview (Yang et al., 2019a)

Computation begins with the caching of position and charge data. Position and charge information is used when mapping changes to the grid and when calculating the forces exhibited on each particle. The caching of particle positions and charges allows a host to

offload data to this accelerator and perform other tasks why LR computations are taking place. Particle charges are evaluated and assigned to 64 neighboring cell locations using a third order basis function, with results stored in *grid memory*. After all particle data is consumed, the FFT evaluation runs on the resulting grid (through each axis X, Y, and Z). Resulting data, after multiplying with the Green's function, is replaced in the memory grid only a few cycles after evaluation. This is possible because of the pipeline implementation of the FFT. The inverse FFT is then performed on each dimension. Finally, forces are calculated for each individual particle using the final FFT grid results and the starting particle position information saved previously in the position cache. These are then saved into a force cache which is used during the motion update phase to apply long-range forces to the particle positions.

#### 2.4.2 3D FFT

The initial design of the FFT subsystem is based on previous work (Humphries et al., 2014) and performs calculations in parallel using vendor supplied FFT cores. This work was later extended to clusters and clouds of tightly coupled FPGAs (Sheng et al., 2014) and used for OpenCL case studies (Sanaullah and Herbordt, 2017; Yang et al., 2017; Sanaullah and Herbordt, 2018b). Recent work has created an efficient version of the 3D FFT for a small cluster of FPGAs and implemented in OpenCL (Stewart et al., 2020).

The FFT units are assigned to specific banks of the grid memory to ensure high throughput memory access. As a result, grid data can be continuously streamed through all FFT cores in parallel. While output is being generated for a given vector, a new input is sent for the next set of calculations. Each dimension is performed sequentially until all three dimensions are completed on the memory grid. Once all three dimensions are evaluated and converted into the Fourier-domain, the grid is multiplied with Green's function, before proceeding to the inverse FFT stage going through each dimension again and converting back. Final values at each grid-point are used to compute the LR force for each particle based on its position.

Figure 2.3 shows a block diagram of the logic used. The Crossbars work in conjunction with the RAMs to select the flow of data so as to affect transpose and reverse-transpose as needed. The Controller is a large state machine that drives all of the inputs to the RAMs, Crossbars, and FFT Pipelines. The FFT pipelines are 1D and supplied by the vendors with standard packages.

Figure 2.3: Block Diagram for 3D FFT Design (Humphries et al., 2014)

#### 2.4.3 Particle to Grid Mapping

The third order basis functions in Equation 2.7 are used to spread particle charges to the four closest grid points, based on particle position data, and can be independently evaluated for each dimension. The following were used in (Gu and Herbordt, 2007). Previous work on particle-grid mapping can be found in (Sanaullah et al., 2016a; Sanaullah et al., 2016c;

Sanaullah et al., 2016b).

$$\begin{cases} \phi_0(oi) = -\frac{1}{2}oi^3 + oi^2 - \frac{1}{2}oi \\ \phi_1(oi) = \frac{3}{2}oi^3 - \frac{5}{2}oi^2 + 1 \\ \phi_2(oi) = -\frac{3}{2}oi^3 + 2oi^2 + \frac{1}{2}oi \\ \phi_3(oi) = \frac{1}{2}oi^3 - \frac{1}{2}oi^2 \end{cases}$$

$$(2.7)$$

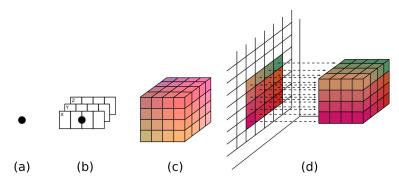

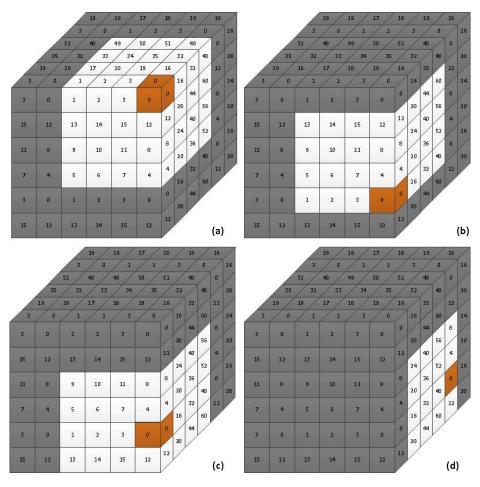

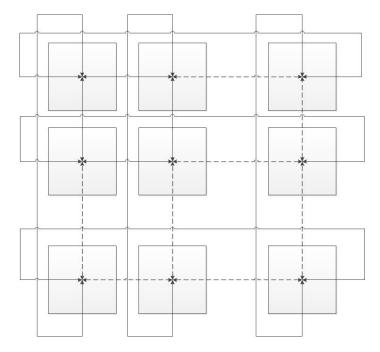

After a particle is evaluated in each dimension, values are assigned to 64 neighboring cells and each result is accumulated into grid memory locations. Figure 2.4 shows the process of a single particle's influence on 64 neighbor cells and their mapping to a prior work's grid memory structure. Starting with a particle's initial position and charge (a), it mapped to its nearest neighboring 4 grid-point in each of the three dimensions (b), permuting the combinations of 1D mappings to 3D, a cube of 3D grid-points is created (c), and finally mapped to 64 address locations within 16 independent memory units.

**Figure 2**·4: Previously Developed Particle-to-Grid-Memory Flow (Yang et al., 2019a)

### 2.4.4 Grid Memory Network

One issue with the particle-grid converter is that a large number of grid points must be accessed on every cycle; this requires both high bandwidth and highly parallel addressing logic. Fortunately, modern FPGAs, with their thousands of independent BRAMs, have just such capability. The interleaved memory design described in (VanCourt and Herbordt, 2006a) is one such example. Figure 2.5 motivates the need for this network.

| 1 |   |    |    | → <sup>2</sup> | Κ  |    |    |    |    |

|---|---|----|----|----------------|----|----|----|----|----|

|   |   | 00 | 01 | 02             | 03 | 00 | 01 | 02 | 03 |

|   |   | 10 | 11 | 12             | 13 | 10 | 11 | 12 | 13 |

| Y | 7 | 20 | 21 | 22             | 23 | 20 | 21 | 22 | 23 |

| I |   | 30 | 31 | 32             | 33 | 30 | 31 | 32 | 33 |

|   |   | 00 | 01 | 02             | 03 | 00 | 01 | 02 | 03 |

|   |   | 10 | 11 | 12             | 13 | 10 | 11 | 12 | 13 |

|   |   | 20 | 21 | 22             | 23 | 20 | 21 | 22 | 23 |

|   |   | 30 | 31 | 32             | 33 | 30 | 31 | 32 | 33 |

**Figure 2.5:** 2D Example Motivating an Alignment Network (Gu and Herbordt, 2007)

Given an address reference (x,y), the grid points within a 4x4 window, i.e. (x,y), (x,y+1), ..., (x+3,y+3), must be accessed. Obviously, 16 independent memory accesses are required for each interleaved memory access. As shown in Figure 8, when grid points are stored in 16 separate banks marked from 00 to 33, any 4x4 access window contains exactly one grid points from each bank. The bank's index is either the same as that of the bank of the reference address, or the one greater than that in the X and/or Y dimension, respectively. The outputs from memory banks are shifted (with rotation) in both X and Y based on the reference address. 3D interleaving memory is analogous.

## Chapter 3 Single-FPGA LR Design

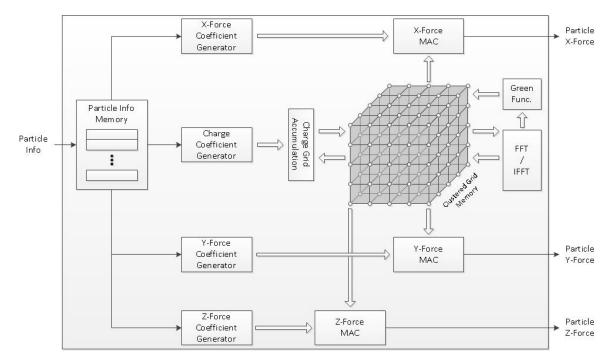

Part of this thesis builds an improved and parameterized LR architecture using resources on a single FPGA. Figure 3.1 depicts a high-level block diagram of the new LR architecture.

Figure 3.1: Enhanced Single-FPGA LR System Block Diagram

Particle position and charge information are loaded into a particle info memory (analogous to the particle position cache in Figure 2.2) through a ready-valid handshaking interface with a 'last' indicator to inform the system when the last of the particle information is transferred. As previously mentioned, this particle info memory is used in the charge mapping and force calculation phases of the LR computation. Expanding on (VanCourt and

Herbordt, 2006a), a 3D-interleaving of BRAMs is used to implement the grid memory. This 3D interleaving of BRAMs offers up some algorithmic performance enhancements, details of which can be found in section 3.3. Once mapped, the resulting charge-grid is transformed into a grid of Coulombic potentials by passing through a 3D FFT, passing through a Green's function immediately following the 3D FFT, and lastly passing through a 3D IFFT. The grid of potentials is then combined with the cached particle position and charge to calculate the three one-dimensional force vectors acting on each particle. The final force values are offloaded to the host using a separate ready-valid handshaking interface also equipped with a 'last' indicator to inform the host when the last particle's force vectors are transferred.

The LR design developed during this thesis leverages Hardware Description Language (HDL) code used to build the system in Figure 2.2. Upon review of the HDL, it was found that the Green's function implementation was incomplete. The new LR design completes that, adds the two ready-valid handshaking interfaces, implements 3D-interleaved grid memory, and implements FFT pipelines that complement the structure of this new grid memory. Only the coefficient generators and force multiply-accumulate (MAC) blocks were found to be reusable. Though reusable, they were enhanced to reduce the amount of FPGA resources they consume (see Sections 3.2 and 3.6).

The remainder of this chapter discusses the architectural details of the various submodules that comprise the single-FPGA LR design.

### **3.1** Particle Info Memory

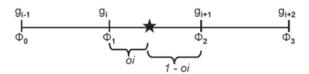

LR computation begins with the loading of particle position and charge information into a memory. Information is transferred over a ready-valid interface equipped with a 'last' indicator to inform the system when the last of the information is transmitted by an offchip host. The particle information transmitted includes the position of particle and its charge. A particle's position relative to neighboring grid-points is illustrated in Figure 3.2.

Figure 3.2: Particle Positioning (Sanaullah et al., 2016c)

The particle's true position is denoted by the  $\star$  but can be broken up into a nearest-floorgrid-point,  $\phi_1$  and the offset from that nearest-floor-grid-point, *oi*.  $\phi_1$  is stored as an unsigned integer whose width is dependent on the number of grid-points in the given dimension. In this design offsets are stored in an unsigned Q27 fixed-point format and charge values are stored in a signed Q5.27 fixed-point format.

Since LR involves running per-timestep LR computations, the grid memory needs to be cleared prior to charge mapping. This grid clearing happens, grid-point by grid-point, as particle information is transferred from the host. This clearing mechanism imposes that the number of particles to be mapped be greater than or equal to the number of grid-points in the simulation. Though this is a reasonable assumption, future hardware could leverage the parallelized nature of grid memory access (see section 3.3) to clear the grid over fewer particle information transfers.

## 3.2 Charge Mapping

Charge mapping interpolates charge densities at grid-points using a particle's charge value (Sanaullah et al., 2016a). Charge density values are calculated with Equation 3.1.

$$\rho_g = \sum_p Q_p \phi(|x_g - x_p|) \phi(|y_g - y_p|) \phi(|z_g - z_p|)$$

(3.1)

These  $\phi$  functions are a result of plugging in the definition of a particle's position relative to its nearest neighbors (see Figure 3.2) into Equation 2.6, resulting in the functions defined

in Equation 2.7. Expanding across three dimensions, a single particle is mapped to 64 gridpoints. The charge coefficient generator sub-module pipelines this spreading of charge across all 64 nearest-neighboring grid-points, utilizing the FPGA's floating point (FP) IP to perform the arithmetic operations implied by Equations 2.7 and 3.1.

The accumulation of charge densities interpolated from separate particles requires readmodify-write operations to be performed on data in the grid memory. This requirement, coupled with the pipelined nature of the charge mapping, introduces the possibility of data hazards. A read-after-write (RAW) hazard occurs if a grid-point to be updated with accumulated charge data is required to be read out for the mapping of a subsequent particle. Currently, the hardware stalls the pipeline to avoid these hazards. If particle charge and position information were to be sorted prior to being cached, such that particles mapping to overlapping sets of grid-points were spaced out to avoid these RAW hazards, this stalling could be removed. Alternatively, additional hardware could be implemented to provide a means of data forwarding where possible. However, to simplify the complexity and verification of this design in the face of time constraints, it was decided to move forward with pipeline stalling. It is well known that stalling is detrimental to the pipeline performance. For this design to be viable, stalling should be replaced with a better hazard resolution strategy.

As previously mentioned, the coefficient generator block is implemented through partial reuse of pre-existing HDL files. The sub-module design is enhanced to reduce the number of FPGA FP resources consumed based on the coefficients of the functions in Equation 2.7 by:

- 1. Driving pipeline stage outputs to zero when portions of the algebraic equation call for multiplications by zero.

- 2. Replacing FP IP with pipeline register stages when portions of the algebraic equation call for additions of zero.

3. Replacing FP IP with pipeline register stages when portions of the algebraic equation call for multiplications by one.

This is performed using SystemVerilog (SV) parameters and generate statements (SVLRM, 2018). Utilizing SV parameters and generate statements allows for easy hardware implementation updates if the basis functions were to change. It also allows this block to be reused when mapping particle forces (see section 3.6).

A few notes for anyone that plans to reuse/enhance the charge mapping hardware. Work was performed to verify the hardware against OpenMM models (OpenMM, 2020). It was found that the OpenMM modeling utilized the the following third-order basis functions (when configured for third-order polynomial interpolation):

$$\begin{cases} \phi_0(oi) = -\frac{1}{6}oi^3 + \frac{1}{2}oi^2 - \frac{1}{2}oi + \frac{1}{6} \\ \phi_1(oi) = \frac{1}{2}oi^3 - oi^2 + 4 \\ \phi_2(oi) = -\frac{1}{2}oi^3 + \frac{1}{2}oi^2 + \frac{1}{2}oi + \frac{1}{6} \\ \phi_3(oi) = \frac{1}{6}oi^3 \end{cases}$$

$$(3.2)$$

This change in interpolation function and therefore all the hardware built around it, simply required changes to the SV parameters defined in the charge mapping module. The generate statements process the parameter changes to make up-front hardware optimizations.

## 3.3 Grid Memory

The storage of grid-point data affects the operation of all phases of LR computation, from the number of grid-points that can be mapped per clock-cycle (assuming RAW hazards are taken care of), to the number of FFT pipelines that can run in parallel, to the number of grid-points that can be read out per clock cycle when performing the force interpolations. Previously explored architectures lent themselves well to performing the 3D FFT, but often required transposing the stored grid-point values between one or more 1D FFT phases to maximize the number of parallel 1D FFT computations (Humphries et al., 2014; Sanaullah and Herbordt, 2017; Sanaullah and Herbordt, 2018b). Even an architecture comprised of  $X_G$  by  $Y_G$  blocks, each with a depth of  $Z_G$ , where  $X_G$ ,  $Y_G$ , and  $Z_G$  are the number of grid-points in the X, Y, and Z dimensions, respectively, requires transposing stored data. With that in mind, the clustered grid memory is an interleaving of FPGA block RAMs designed to:

- Store 64-bits of data for each grid-point in the system. 64 bits are needed to store two 32-bit, single-precision, floating-point values for the real and complex components of grid-point data.

- Support the mapping of one particle to its 64 nearest-neighboring grid-points in 3D per clock cycle.

- 3. Avoid the need for data reordering prior to performing 1D FFTs over the grid-points of charge data.

Meeting requirement 1 is trivial. To meet requirement 1 imposes that the memory architecture have at least 64 two-port (one read, one write) memories. Meeting requirement 3 imposes that the same mechanism used to access grid-points sequentially placed along any one of the three dimensions be agnostic to the direction of that dimension. Meeting requirements 2 and 3 is achieved by expanding on (VanCourt and Herbordt, 2006a) making use of low-order address interleaving.

### **3.3.1** Clustered Grid Memory

The clustered grid memory is comprised of 64 memory units (neighbors), one unit per a particle's nearest-neighbor in 3D, with each unit possibly being comprised of multiple FPGA BRAMs. The ordered triplet used to specify the location of the grid-point in 3D space is the address for the data at that grid-point. Partitioning the grid memory into 4x4x4

neighborhoods, the location of a grid-point can be thought of in terms of a neighborhood ID and a neighbor ID, where the neighbor ID is used to choose among the 64 memory units and the neighborhood ID is used to index into each memory unit. The lower two bits of each coordinate concatenated form the neighbor ID, while upper address bits of each coordinate concatenated for the neighborhood ID. The following is an example of how the ordered triplet of a grid-point in a 32x32x32 grid is decomposed into its cluster ID and neighbor ID.

$$= 11,23,8$$

= (01011<sub>2</sub>,10111<sub>2</sub>,01000<sub>2</sub>)

= (010<sub>2</sub>,101<sub>2</sub>,010<sub>2</sub>).(11<sub>2</sub>,11<sub>2</sub>,00<sub>2</sub>)

= (2,5,2).(3,3,0)

In a 32x32x32 grid, grid-point (11,23,8) refers to neighbor (3,3,0) inside of neighborhood (2,5,2).

The clustered grid memory presents 64 two-port access channels in the form of a cluster to the rest of the LR system. Figure 3.3 depicts the access cluster access in the context of the grid memory. The figure depicts how the access cluster moves about to access neighbors from neighborhoods, thereby accessing grid-points from the grid. Neighbor IDs range from 0-64 and are associated with neighborhoods based on their 3D position. Neighbors accessed by the access cluster appear as lighter shades of gray or orange. From (a) to (b) to (c), the access cluster moves along the *Y* dimension. From (c) to (d) the access cluster moves along the *Z* dimension.

Notice that each neighbor ID appears at most once inside of an access cluster. Notice also that the access cluster is not required to be neighborhood-aligned, that is, the access cluster can access some neighbors from one neighborhood while accessing neighbors from other neighborhoods. This lack of alignment requirement means that any neighbor ID

Figure 3.3: Memory Access Patterns for Charge Mapping in 3D

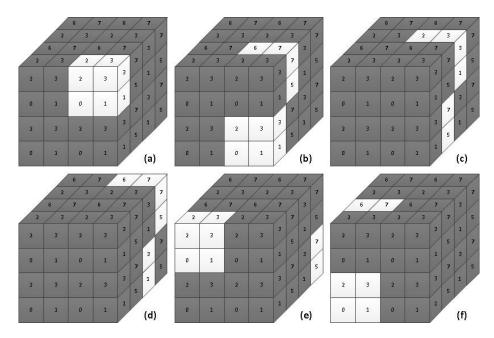

can appear on any of the ports in the access cluster. This is evidenced by the location of neighbor 0 (potentially from different neighborhoods) relative to a port within the access cluster as the access cluster moves around in 3D space. Achieving this flexibility requires all-access-cluster-port-to-all-neighbor connectivity. Originally, this all-to-all connectivity was performed in a single clock cycle and proved to be the critical path when attempting to target the system for a 100MHz operating frequency. To improve performance, this all-to-all connectivity was pipelined. Figure 3.4 depicts a three-stage, toroidal, shift MUX used to pipeline the all-to-all connectivity from access cluster ports to neighbor memories.

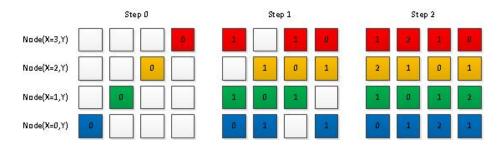

**Figure 3.4:** Three-Stage Toroidal-Shift MUXing Pipeline for Memory Access Alignment

The figure depicts how an non-neighborhood-aligned access is aligned in each dimension. The top row of the figure depicts alignment in the X dimension while the second and third rows depict alignment along the Y and Z dimensions, respectively. Once control information is aligned, the data read from the neighbors is re-unaligned before arriving back at the access ports so the rest of the system sees the data on the same ports it originally requested the access over.

Alignment in each dimension is performed in one clock cycle. Alignment in one dimension involves looking at the appropriate 1D component of the neighbor ID and comparing it to the appropriate 1D component of the access port ID. If these components match, no realignment is required. If these components do not match, a toroidal shift occurs such that the 1D ID components will match following the next clock edge.

The clustered grid memory was parameterized to handle various 3D grid sizes. Grids are not required to be cubic, but each dimension of the grid is required to be a power of 2. To support this flexibility the toroidal shift MUXing was performed using one-hot MUXing. This one-hot MUXing may not prove to be the best performing MUXing architecture, but accommodating various grid sizes would require HDL file modification rather than the overriding of SV parameters.

## 3.4 FFT/IFFT

Once the mapping of all particle charges is complete, the resultant charge grid is then transformed into a grid of Coulombic potential energies by:

- 1. Converting the charge data from the spatial domain to the Fourier domain by running it through a 3D FFT.

- 2. Convolving the result of the 3D FFT with the 3D FFT of a Green's function.

- 3. Running a 3D IFFT over the results of the convolution.

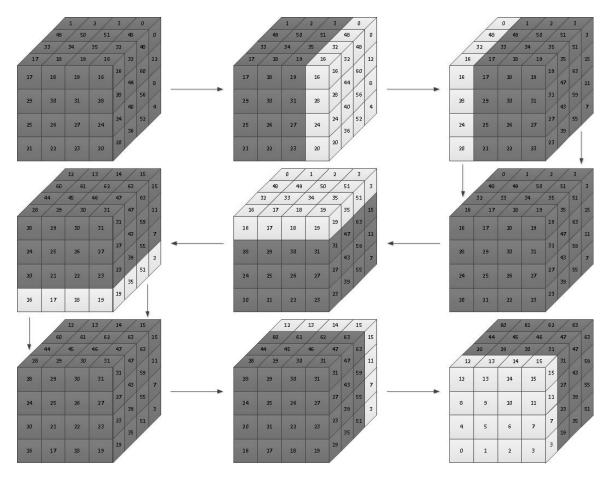

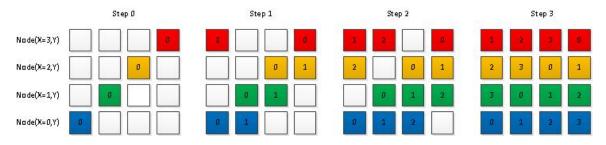

The 3D FFT (and IFFT) is decomposed into sequential 1D FFTs (IFFTs), one in each dimension. The LR design makes use of FPGA DSP resources that stream in FFT inputs into a pipeline and some number of clock cycles later stream out the FFT results sequentially. Preservation of 1D FFT (and IFFT) input data is not required, so the clustered grid memory is used to temporarily store the results of each 1D FFT (and IFFT). Before the results of the third 1D FFT are written back to the clustered grid memory, they are first convolved with the 3D FFT of a Green's function. This convolution equates to a simple multiplication in the Fourier domain and therefore leverages additional FPGA FP resources. With the ability to read and write 64 clustered grid memory addresses simultaneously, implementing 64 FFT pipelines maximizes data throughput and reduces the overall 1D FFT execution time. Unfortunately, the access structure of the clustered grid memory supports accessing a 3D, 4x4x4 set of grid-points where each port is required to access a unique neighbor. This is not conducive to the FPGA DSP resources, which require FFT points to be inputted in a specific order. This order is configurable when building the hardware (Intel, 2017) and is chosen to be natural. To work around this limitation, 1D FFTs (and IFFTs) are performed by staggering 2D slices of the access cluster and mapping these access-cluster slices to neighbor memories from neighborhoods in different districts, where a district is an array of neighborhoods in a given dimension. Figure 3.5 illustrates how this staggering of access cluster slices works on a 4x4x4 grid with a 2x2x2 access cluster.

Figure 3.5: Memory Access Cluster Slice Staggering for Optimum FFT Throughput

In this figure the x-axis trends positive in a westerly direction, the y-axis trends positive in a southerly direction, and the z-axis trends positive moving into the paper (this was done intentionally for illustrative purposes). The FFT access scheme moves from (a) to (f). In

the first clock cycle (a), access-cluster ports 0-3 are mapped to neighbors-memories 0-3 of neighborhood (0,0,0). In the second clock cycle (b), ports 0-3 are mapped to neighbors 4-7 of neighborhood (0,0,0) while ports 4-7 are mapped to neighbors 0-3 of neighborhood (0,1,0). When a 2D access slice is accessing neighbor 4-7 of the last neighborhood in of a district (d and e), it will access neighbors 0-3 of the first neighborhood of a previously unaccessed district (e and f). This pattern continues until neighbors 4-7 of the last neighborhood of the last district are accessed.

Originally it was planned to configure the FFT resources to be bidirectional, but simulations of the IFFT revealed that the ordering of IFFT outputs were not consistent with the documentation. To workaround this setback, IFFTs are implemented with forwarddirection FFT resources (Lyons, 2015). Doing so, requires:

- 1. Modifications to the boundary checking conditions of the access-cluster-slice staggering. This modification is only required in the inverse FFT direction only.

- 2. Dividing the outputs of the FFT pipeline. Since the IP uses floating-point values and any dimension of the grid is a power of two, this division is performed by a subtraction of the exponential bits in the floating-point value.

Later on, it was determined that this subtraction could be removed due to compensations made inside the Green's function (see section 3.5).

## 3.5 Green's Function

The Green's function is dependent on the position of the grid-point, the true volume of the grid, the order of the basis function used to map the particle charges, and a convergence parameter (Procacci, 2009). Thus, the values of the Green's function at each grid-point can be computed offline and programmed into ROM as the rest of the FPGA logic is being programmed. This Green's ROM architecture is similar to the clustered grid memory with

the one exception: the Green's function value at each grid-point is only 32 bits wide. Since the Green's ROM is only ever accessed during the 1D FFT in the Z dimension using the staggering of 2D access cluster slices, alignment in the X and Y dimensions is guaranteed. This guarantee does allow for the reduction toroidal shift MUX pipeline stages from 6 to 2, but for developmental expedience, this reduction was not implemented.

When comparisons of this accelerator were compared against OpenMM modeling it was found that since:

- 1. The computation of the Green's function requires multiplication by  $X_G Y_G Z_G$ .

- 2. 3D IFFTs using FFT require a division by  $X_G Y_G Z_G$ .

- 3. FFT/IFFTs are linear functions.

the computation of Green's ROM values could omit the multiplication step allowing for the removal of the division steps of IFFT using FFT (OpenMM, 2020).

## **3.6 Force Computation**

Computing the forces acting on each particle in each dimension uses the following three equations:

$$\vec{\mathbf{F}_{p,x}} = \sum_{g} \phi_g \partial \phi(|x_g - x_p|) \phi(|y_g - y_p|) \phi(|z_g - z_p|)$$

(3.3)

$$\vec{\mathbf{F}_{p,y}} = \sum_{g} \phi_{g} \phi(|x_{g} - x_{p}|) \partial \phi(|y_{g} - y_{p}|) \phi(|z_{g} - z_{p}|)$$

(3.4)

$$\vec{\mathbf{F}_{\mathbf{p},\mathbf{z}}} = \sum_{g} \phi_{g} \phi(|x_{g} - x_{p}|) \phi(|y_{g} - y_{p}|) \partial \phi(|z_{g} - z_{p}|)$$

(3.5)

where *p* refers to a particle, *g* refers to a grid-point, and  $\varphi_g$  refers to the subset of electrostatic potential grid-points that map to the particle in question. For completeness, the

derivative if *phi* is listed below:

$$\begin{cases} \frac{d\phi_0}{doi} = -\frac{3}{2}oi^2 + 2oi - \frac{1}{2} \\ \frac{d\phi_1}{doi} = \frac{9}{2}oi^2 - 5oi + 1 \\ \frac{d\phi_2}{doi} = -\frac{9}{2}oi^2 + 4oi + \frac{1}{2} \\ \frac{d\phi_3}{doi} = \frac{3}{2}oi^2 - oi \end{cases}$$

(3.6)

With that, force computation can be broken into two stages:

- 1. Coefficient generation mapping the particle to the grid using the partial derivatives of the mapping function in each dimension.

- 2. MAC Multiplying the results of the mapping function by the subset of electrostatic grid-points that the particle maps to and summing the products across all grid-points in that subset.

A couple notes for those that plan to reuse/enhance the force computation sub-modules: When the interpolation function was changed to verify the design against OpenMM modeling, the the derivative if *phi* became:

$$\begin{cases} \frac{d\phi_0}{doi} = -\frac{1}{2}oi^2 + oi - \frac{1}{2} \\ \frac{d\phi_1}{doi} = \frac{3}{2}oi^2 - 2oi \\ \frac{d\phi_2}{doi} = -\frac{3}{2}oi^2 + oi + \frac{1}{2} \\ \frac{d\phi_3}{doi} = \frac{1}{2}oi^2 \end{cases}$$

(3.7)

Again, that hardware change was made made painlessly by changing parameter settings and having SV generate statements take care of the rest.

## **3.6.1** Coefficient Generation

Coefficient generation involves the same mapping process that mapped particle charges to the grid, but uses the derivative of the functions in Equation 2.7 in one of the three dimensions. To this effect, the same coefficient generator HDL used in charge mapping is used to generate the Force coefficients in each of the three dimensions. The coefficient generator is implemented 3 additional times, but the configuration of each sub-module instance is fixed at implementation by choosing between the coefficients of 2.7 and 3.6 based on the direction of the force to be calculated.

It should be noted that FPGA DSP resources could be saved by implementing only 3 coefficient generators with one of them being used for both charge mapping and force coefficient generation. Doing so however, would require a different coefficient generator architecture that is run-time programmable.

## 3.6.2 MAC