Air Force Institute of Technology AFIT Scholar

Theses and Dissertations

Student Graduate Works

3-1-2002

## Design and Fabrication of Micro-Electro-Mechanical Structures for Tunable Micro-Optical Devices

Michael C. Harvey

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Electro-Mechanical Systems Commons, and the Electronic Devices and Semiconductor Manufacturing Commons

#### **Recommended Citation**

Harvey, Michael C., "Design and Fabrication of Micro-Electro-Mechanical Structures for Tunable Micro-Optical Devices" (2002). *Theses and Dissertations*. 4368. https://scholar.afit.edu/etd/4368

This Thesis is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact richard.mansfield@afit.edu.

AFIT/ENG/GEO-02M-01

### DESIGN AND FABRICATION OF MICRO-ELECTRO-MECHANICAL STRUCTURES FOR TUNABLE MICRO-OPTICAL DEVICES

THESIS Michael C. Harvey Captain, USAF

AFIT/ENG/GEO-02M-01

DEPARTMENT OF THE AIR FORCE AIR UNIVERSITY

AIR FORCE INSTITUTE OF TECHNOLOGY

Wright-Patterson Air Force Base, Ohio

Approved for public release; distribution unlimited.

| Report Documentation Page                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Report Date<br>18 Mar 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>Report Type</b><br>Final                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Dates Covered (from to)<br>Jun 01 - Mar 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Title and Subtitle                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Contract Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Design and Fabrication of M<br>Structures for Tunable Micr                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Grant Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Program Element Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Author(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Project Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Capt Michael C. Harvey, USAF Task Number Work Unit Number                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Task Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Work Unit Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Performing Organization Name(s) and Address(es)</b><br>Air Force Institute of Technology Graduate School of<br>Engineering and Management (AFIT/EN) 2950 P<br>Street, Bldg 640 WPAFB, OH 45433-7765                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Performing Organization Report Number</b><br>AFIT/GEO/ENG/02M-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Sponsoring/Monitoring Ag<br>Address(es)                                                                                                                                                                                                                                                                                                                                                                                                                                                 | gency Name(s) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Sponsor/Monitor's Acronym(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AFRL/SNND Mr. Thomas R. Nelson 2241 Avionics<br>Circle, RM C2G69 WPAFB OH 45433-7322                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Sponsor/Monitor's Report Number(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Distribution/Availability S<br>Approved for public release                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Supplementary Notes<br>The original document conta                                                                                                                                                                                                                                                                                                                                                                                                                                      | ains color images.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| this research I seek to optim<br>III-V semiconductor micro-<br>of a Fabry-Perot etalon or ve<br>actuation voltage to the ME<br>demonstrate tunable devices<br>design for a Fabry-Perot eta<br>range of 44nm, both achieve<br>planned a new microelectron<br>peak central emission wavel<br>distinct device designs, all v<br>gold MEM flexure with a Si<br>all-semiconductor VCSEL of<br>test structures using the clear<br>the Air Force Research Labo<br>voltages as low as 1.8 V, wh | ize the design of a microele<br>optical device. The resonan-<br>ertical cavity surface emittin<br>M Flexure, thereby altering<br>s compatible with conventio<br>lon has a theoretical tuning<br>ed with actuation voltages a<br>nics fabrication process to r<br>length at 980nm. I designed<br>within a die size of one squa<br>i3N4/Si02 dielectric distribu-<br>or Fabry-Perot substrate. I su-<br>nroom laboratory facilities<br>oratory (AFRL). The initial<br>nich is comparable to existin<br>oped improvements to my 1<br>lts form the fundamental ba | for future military optical communication systems. In<br>etromechanical (MEM) structure integrated with a<br>t frequency of an integrated optical device, consisting<br>ing laser (VCSEL), may be tuned by applying an<br>the device's optical cavity length. From my analysis<br>and silicon 5V integrated circuit technology. My<br>range of 200 nm, and my VCSEL design has a tuning<br>s low as 4V. Utilizing my theoretical device designs I<br>ealize a set of prototype MEM-tunable devices with a<br>a mask set consisting of 8 mask levels and 252<br>re centimeter. My unique fabrication process utilizes a<br>ted Bragg reflector (DBR) mirror, grown on an<br>uccessfuly fabricated a complete set of MEM-tunable<br>at the Air Force Institute of Technology (AFIT) and<br>devices display minimum electrostatic actuation<br>ing MEM tunable VCSEL designs. In order to enhance<br>aboratory process for incorporation in future<br>sis for advanced development of manufacturable |

| Subject Terms<br>Microelectromechanical Systems, Aluminum Gallium Arsenide, Oxidation, Micromaching<br>Micro-Opto-Electro-Mechanical Systems, Vertical Cavity Surface Emitting Lasers |                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|

| <b>Report Classification</b>                                                                                                                                                          | <b>Classification of this page</b> |  |

| unclassified                                                                                                                                                                          | unclassified                       |  |

| Classification of Abstract                                                                                                                                                            | <b>Limitation of Abstract</b>      |  |

| unclassified                                                                                                                                                                          | UU                                 |  |

| Number of Pages<br>217                                                                                                                                                                |                                    |  |

The views expressed in this thesis are those of the author and do not reflect the official policy or position of the United States Air Force, the United States Department of Defense, or the United States Government.

AFIT/ENG/GEO-02M-01

# DESIGN AND FABRICATION OF MICRO-ELECTRO-MECHANICAL STRUCTURES FOR TUNABLE MICRO-OPTICAL DEVICES

#### THESIS

Presented to the Faculty of the Graduate School of Engineering and Management of the Air Force Institute of Technology Air University

> In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

> > Michael C. Harvey, B.S.E.E. Captain, USAF

> > > $26 \ \mathrm{March} \ 2002$

Approved for public release; distribution unlimited.

AFIT/ENG/GEO-02M-01

## DESIGN AND FABRICATION OF MICRO-ELECTRO-MECHANICAL STRUCTURES FOR TUNABLE MICRO-OPTICAL DEVICES

#### THESIS

Michael C. Harvey, B.S.E.E.

Captain, USAF

Approved:

It Col James A. Lott, Ph.D.

18MAROZ

15MAROZ

Date

Professor of Electrical Engineering Thesis Advisor

a.e.

Date

Capt Paul E. Kladitis, Ph. D. Assistant Professor of Electrical Engineering Committee Member

Lt Col Michael A. Marciniak, Ph.D. Assistant Professor of Physics Committee Member

R. Nelson S. Thomas

15 March 02

15 Mar 02

Thomas R. Nelson, Jr., Ph. D. Air Force Research Laboratory Committee Member

Date

Date

### Acknowledgements

"If we knew what it was we were doing, it would not be called research, would it"

Albert Einstein (1879 - 1955)

First I would like to thank my fiance for her loving support and patience throughout my thesis research. She wasn't expecting to move into an empty house while I spent my days and nights working in the lab.

I would also to thank my thesis advisor, Lt Col Lott, for providing me the knowledge and resources I needed to conduct my research, and then allowing me to work independently.

Special thanks go out to my sponsor, Dr. Nelson, for all of his good advice and willingness to put in the long hours supporting of my efforts to get this project working.

To the scientists, engineers, and laboratory technicians at the Air Force Research Laboratory Sensors Directorate, I give my heartfelt appreciation. I look forward to working with these dedicated professionals in the years to come.

## Table of Contents

|                                                     | Page  |

|-----------------------------------------------------|-------|

| Acknowledgements                                    | iii   |

| List of Figures                                     | ix    |

| List of Tables                                      | xxii  |

| List of Symbols                                     | xxiii |

| List of Abbreviations                               | XXV   |

| Abstract                                            | xxvii |

| I. Introduction                                     | 1-1   |

| 1.1 Motivation $\ldots$                             | 1-1   |

| 1.2 Tunable Vertical Cavity Surface Emitting Lasers | 1-1   |

| 1.3 Problem Statement                               | 1-3   |

| 1.4 Research and Scope of Thesis                    | 1-3   |

| 1.5 Methodology                                     | 1-4   |

| 1.6 Main Results                                    | 1-4   |

| 1.7 Sponsor                                         | 1-5   |

| 1.8 Thesis Organization                             | 1-5   |

| Bibliography                                        | 1-6   |

| II. Background                                      | 2-1   |

| 2.1 Chapter Overview                                | 2-1   |

| 2.2 MEMS Overview                                   | 2-1   |

| 2.2.1 Bulk Micromachining                           | 2-1   |

### Page

|                | 2.2.2     | Surface Micromachining              | 2-2  |

|----------------|-----------|-------------------------------------|------|

| 2.3            | Electros  | static Actuation                    | 2-5  |

|                | 2.3.1     | Membrane Deflections                | 2-6  |

|                | 2.3.2     | Piston Micromirrors                 | 2-7  |

| 2.4            | VCSEL     | Design                              | 2-12 |

|                | 2.4.1     | Fabry-Perot Etalon                  | 2-12 |

|                | 2.4.2     | Resonator Cavity Losses             | 2-14 |

|                | 2.4.3     | Distributed Bragg Reflectors        | 2-16 |

|                | 2.4.4     | Resonant Periodic Gain              | 2-21 |

|                | 2.4.5     | VCSEL Threshold Conditions          | 2-26 |

|                | 2.4.6     | Tunable VCSEL                       | 2-27 |

| 2.5            | Current   | Research                            | 2-28 |

|                | 2.5.1     | Membrane VCSEL Devices              | 2-29 |

|                | 2.5.2     | Half-Symmetric Cavity VCSEL Devices | 2-32 |

| 2.6            | Conclus   | $\sin$                              | 2-35 |

| Bibliography . |           |                                     | 2-37 |

| III. Modelin   | ng and De | evice Design                        | 3-1  |

| 3.1            | Device    | Modeling Introduction               | 3-1  |

| 3.2            | VCSEL     | Lasing Requirements                 | 3-2  |

|                | 3.2.1     | VCSEL Bottom DBR Design             | 3-2  |

|                | 3.2.2     | Coupled Cavity Optical Resonator    | 3-4  |

|                | 3.2.3     | VCSEL Top DBR Design                | 3-6  |

|                | 3.2.4     | Electromagnetic Standing Wave       | 3-8  |

| 3.3            | Airgap    | Tuning                              | 3-10 |

| 3.4            | Tunable   | e Fabry-Perot Etalon                | 3-23 |

| 3.5            | Error C   | alculations                         | 3-27 |

|                                         | Page |

|-----------------------------------------|------|

| 3.6 Actuation Voltage Design Range      | 3-28 |

| 3.7 Conclusion                          | 3-30 |

| Bibliography                            | 3-33 |

| IV. Mask Design and Fabrication Process | 4-1  |

| 4.1 Chapter Overview                    | 4-1  |

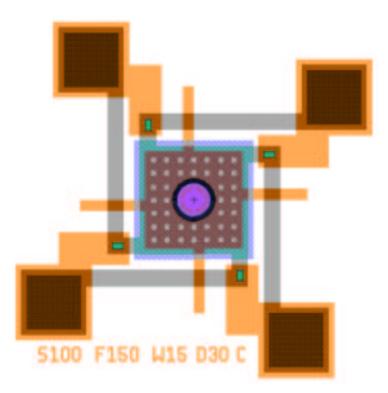

| 4.2 Ohmic Metal Deposition              | 4-2  |

| 4.2.1 Bond Pads                         | 4-2  |

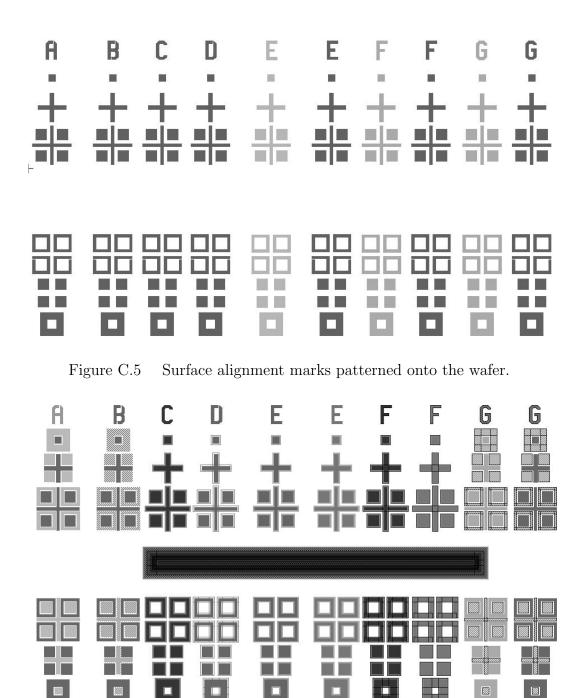

| 4.2.2 Alignment Marks                   | 4-5  |

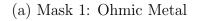

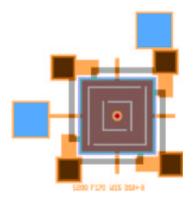

| 4.3 Oxidation Etch                      | 4-6  |

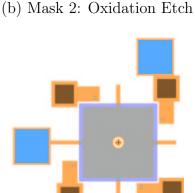

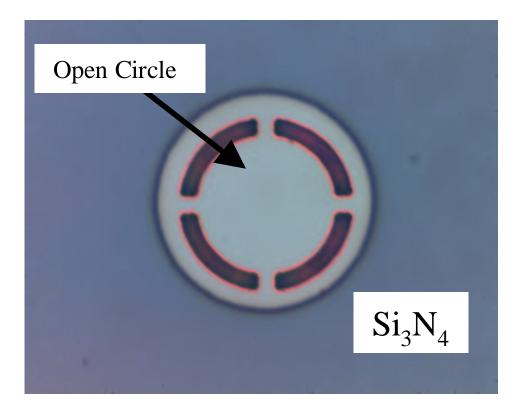

| 4.4 Silicon Nitride                     | 4-9  |

| 4.5 Anchor                              | 4-10 |

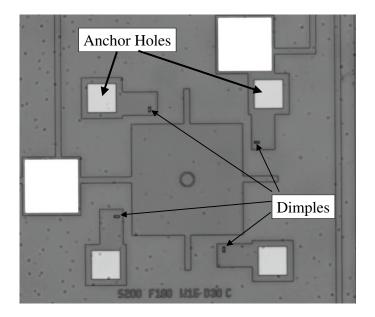

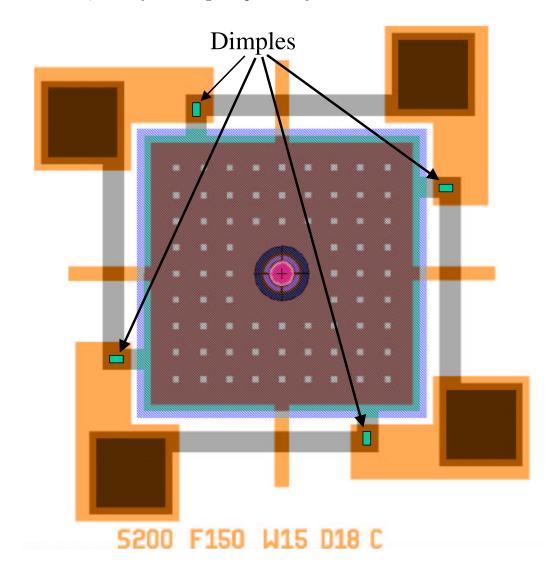

| 4.6 Dimple                              | 4-16 |

| 4.7 Membrane Evaporation                | 4-17 |

| 4.8 Dielectric DBR Mirror Deposition    | 4-19 |

| 4.9 Backside Metallization              | 4-21 |

| 4.10 Device Packaging                   | 4-21 |

| 4.11 Removal of Sacrificial PMGI        | 4-21 |

| 4.12 Conclusion                         | 4-23 |

| Bibliography                            | 4-25 |

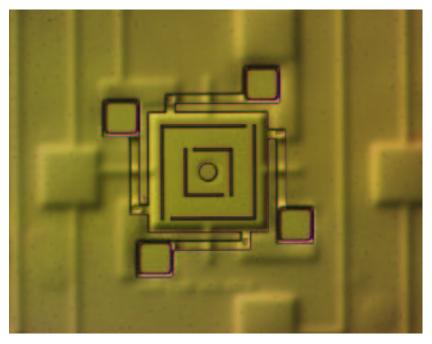

| V. Results and Analysis                 | 5-1  |

| 5.1 Chapter Overview                    | 5-1  |

| 5.2 Fabrication Issues                  | 5-1  |

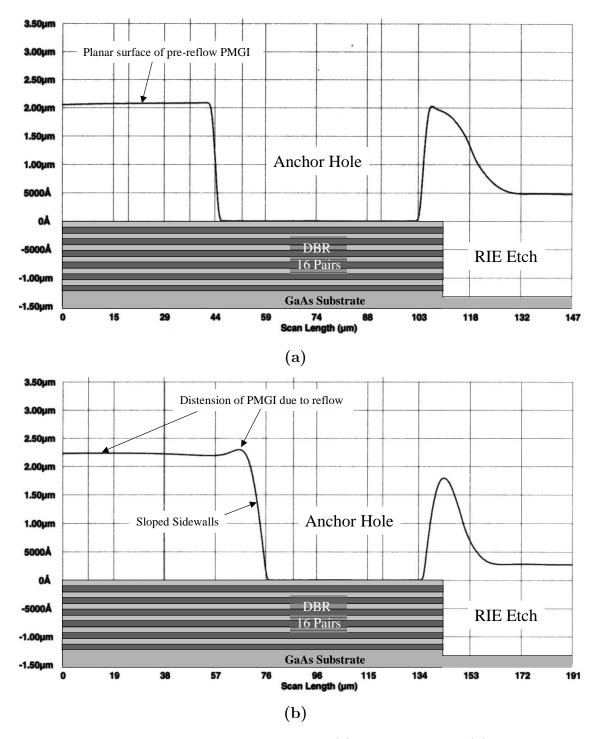

| 5.2.1 PMGI Behavior                     | 5-1  |

| 5.2.2 PMGI Process Improvements         | 5-4  |

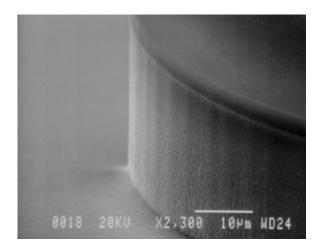

| 5.2.3 Metal Lift-off                    | 5-4  |

|                |                                                 | Page         |

|----------------|-------------------------------------------------|--------------|

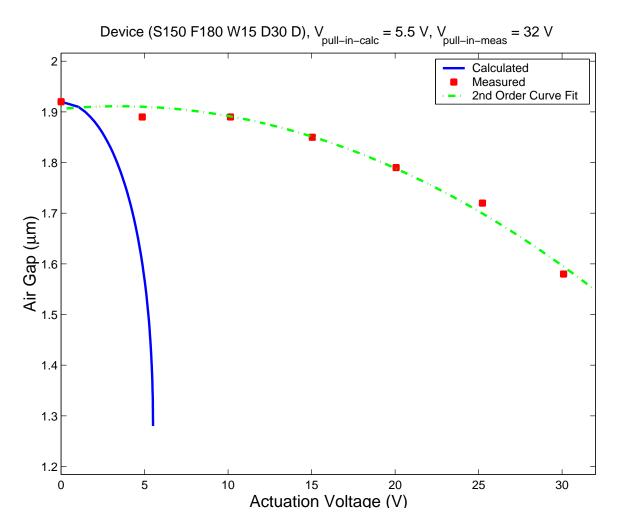

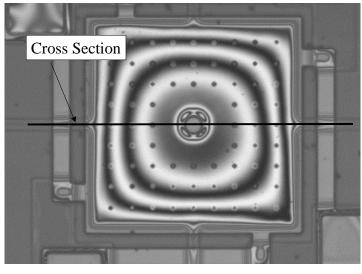

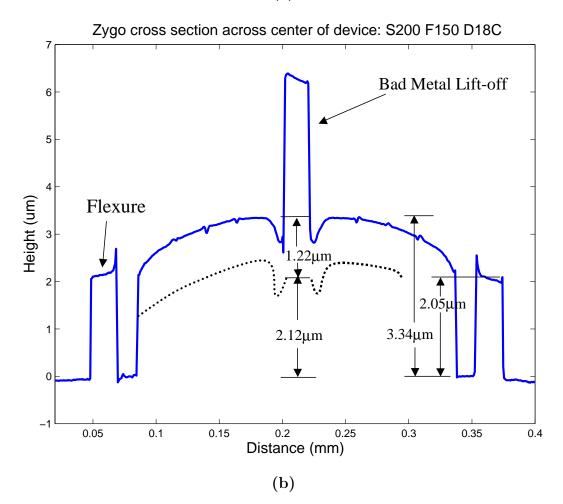

| 5.3            | Electrostatic Actuation Measurements            | 5-10         |

| 5.4            | Alternate Fabrication Technique                 | 5-22         |

| 5.5            | Conclusion                                      | 5-24         |

| Bibliography . |                                                 | 5-26         |

| VI. Conclus    | ions, Recommendations, and Future Work          | 6-1          |

| 6.1            | Summary                                         | 6-1          |

| 6.2            | Recommendations and Future Work                 | 6-2          |

| Appendix A.    | Fabrication Process                             | A-1          |

| Appendix B.    | Molecular Beam Epitaxy Growth Sheets            | B-1          |

| Appendix C.    | Fabrication Techniques                          | C-1          |

| C.1            | Introduction                                    | C-1          |

| C.2            | Thin Film Deposition                            | C-1          |

|                | C.2.1 Spin-on Thin Films                        | C-1          |

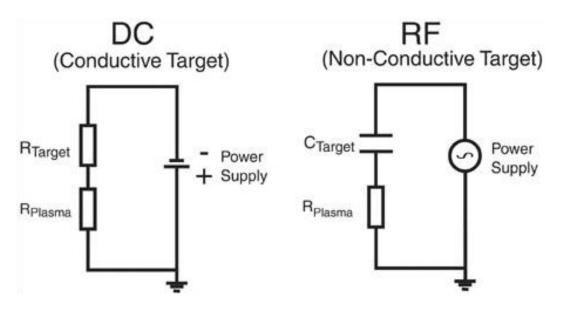

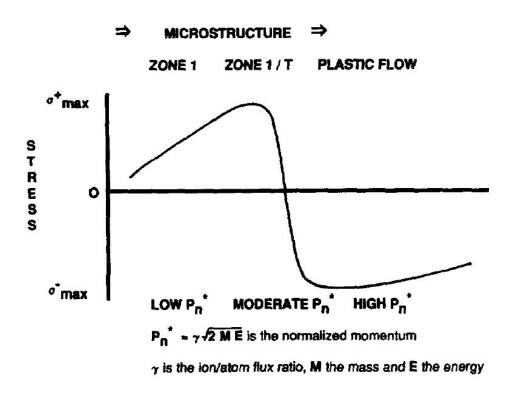

|                | C.2.2 Sputter Deposition                        | C-1          |

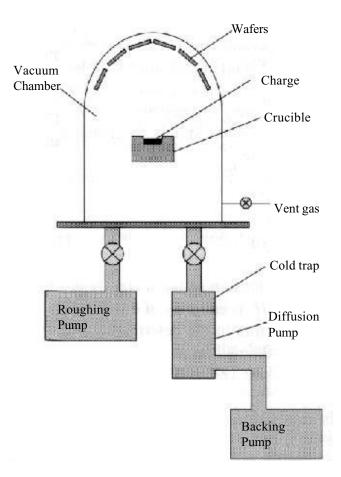

|                | C.2.3 Evaporation                               | C-3          |

|                | C.2.4 Plasma Enhanced Chemical Vapor Deposition | C-4          |

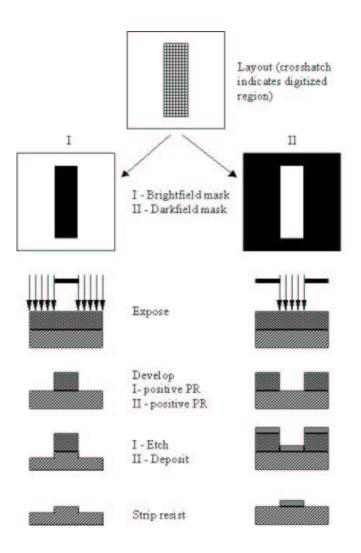

| C.3            | Photolithography                                | C-5          |

|                | C.3.1 Mask Fabrication                          | C-6          |

|                | C.3.2 Aligning multiple photolithography steps  | C-7          |

| C.4            | Wafer Patterning                                | C-8          |

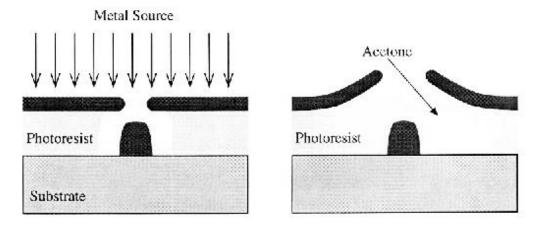

|                | C.4.1 Lift-off                                  | C-8          |

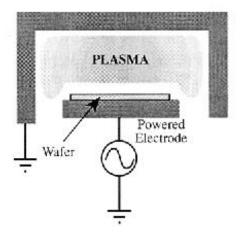

|                | C.4.2 Reactive Ion Etching                      | C-10         |

| C.5            | Ellipsometry                                    | C-12         |

| Bibliography . |                                                 | <b>C-</b> 15 |

|             |                           | Page   |

|-------------|---------------------------|--------|

| Appendix D. | Laboratory Equipment List | D-1    |

| Appendix E. | Matlab Application Code   | E-1    |

| Vita        |                           | VITA-1 |

## List of Figures

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

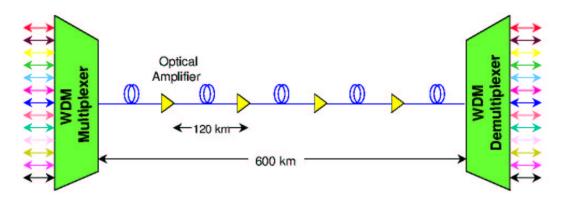

| 1.1.   | Simplified schematic overview of Wavelength Division Multiplexing (WDM). Multiple laser frequencies share the same optical fiber, thereby vastly increasing the available transmission bandwidth.                                                                                                                                                                                                                                               | 1-2  |

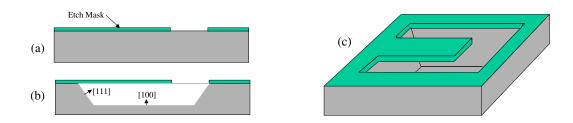

| 2.1.   | Cantilever fabricated by the wet etching of single crystal semiconductor using a crystal plane selective etchant, after $[9]$                                                                                                                                                                                                                                                                                                                   | 2-2  |

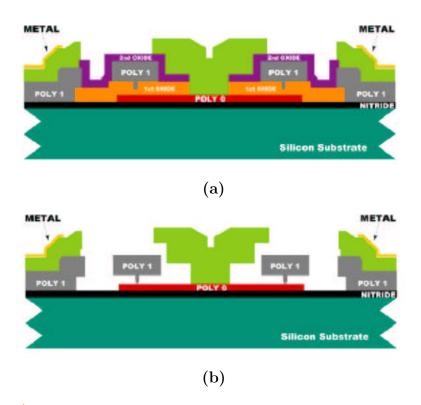

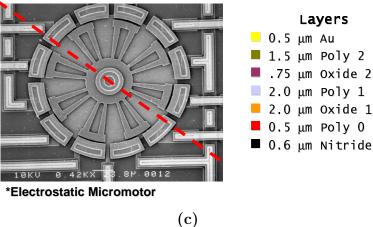

| 2.2.   | Example of a surface micromachining process showing the cross-section<br>of a MUMPs <sup>®</sup> fabricated electrostatic motor (a) before and (b) after<br>release. (c) is a top view of the completed device. Note the conformal<br>nature of the deposited mechanical layers. The structure is released<br>by the removal of the oxide sacrificial layers [8]                                                                                | 2-3  |

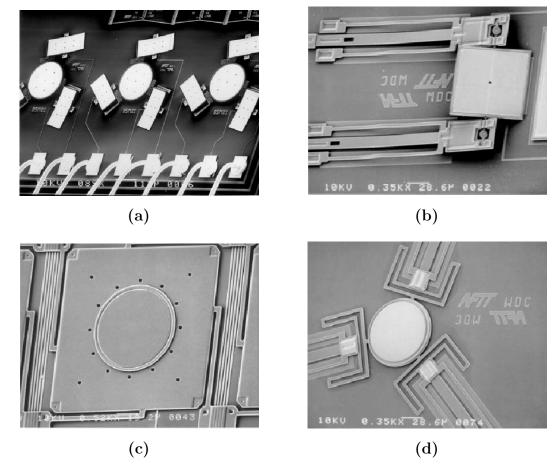

| 2.3.   | Example complex surface micromachined devices using the $MUMPs^{\mathbb{R}}$                                                                                                                                                                                                                                                                                                                                                                    |      |

|        | foundry process [4]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                      | 2-4  |

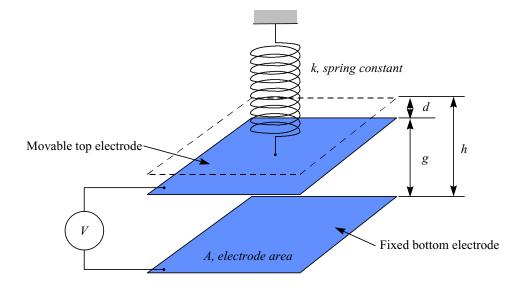

| 2.4.   | Schematic view of basic electrostatic piston micromirror [4]. $\ldots$                                                                                                                                                                                                                                                                                                                                                                          | 2-7  |

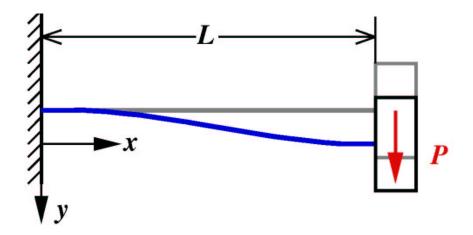

| 2.5.   | Deflection of a flexure beam with a single fixed end $[22]$                                                                                                                                                                                                                                                                                                                                                                                     | 2-10 |

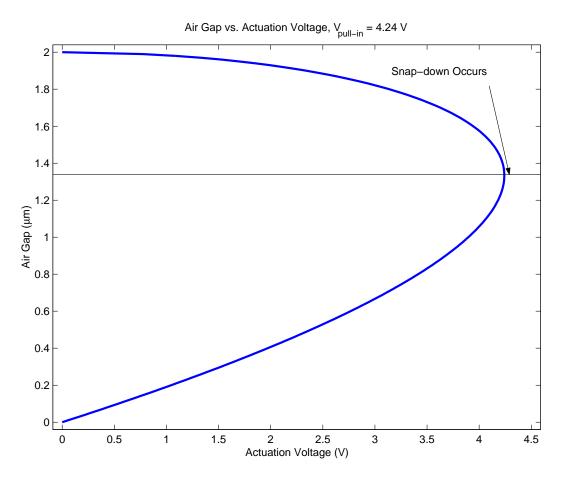

| 2.6.   | Calculated voltage vs. deflection for a 150 $\mu$ m × 150 $\mu$ m mirror<br>with four 150 $\mu$ m flexures, and a 2 $\mu$ m starting airgap. The flexure<br>material is 1 $\mu$ m thick gold (Au) with $E = 79$ GPa. Note that<br>this piston mirror is expected to "snap-down" to the substrate after<br>deflecting 1/3 of the airgap distance. Snap down voltage (4.2 V as<br>shown) is the figure of merit determined from this calculation. | 2-12 |

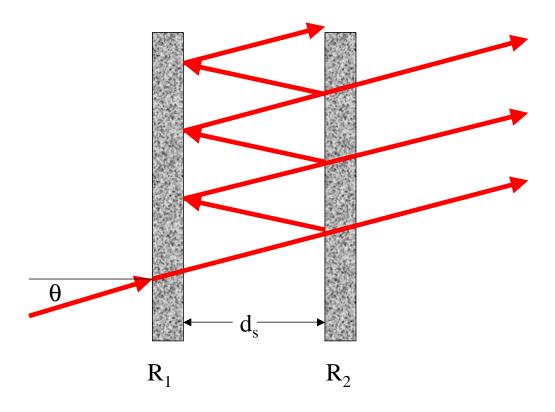

| 2.7.   | Basic Fabry-Perot etalon structure. Light rays that are only slightly<br>inclined eventually escape. Rays will also escape if the mirrors are not<br>perfectly parallel                                                                                                                                                                                                                                                                         | 0 12 |

| 2.0    | perfectly parallel.                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-13 |

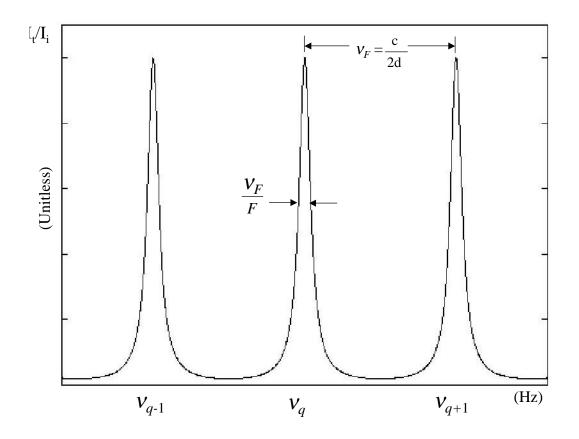

| 2.8.   | Transmission spectra of a Fabry-Perot resonant cavity showing three<br>peaks separated by the Free Spectral Range $(\nu_F)$                                                                                                                                                                                                                                                                                                                     | 2-15 |

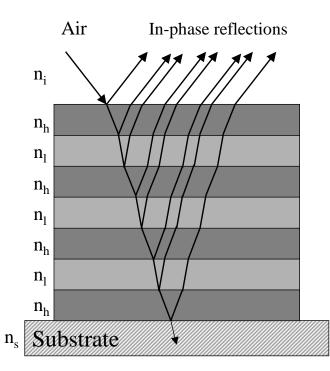

| 2.9.   | Schematic of a basic DBR structure of the form HLHLHLH [7]. $\therefore$                                                                                                                                                                                                                                                                                                                                                                        | 2-17 |

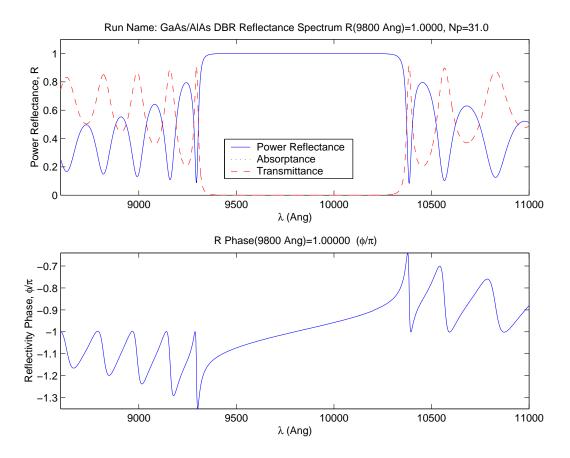

| 2.10. | Power reflectance and reflectivity phase plots of a 31 period GaAs/AlAs<br>quarter-wave DBR stack on a GaAs substrate. The design wavelength<br>is $\lambda_o = 980 \ nm$ .                                                                                                                                                                                                                                                                                                                                 | 2-20 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

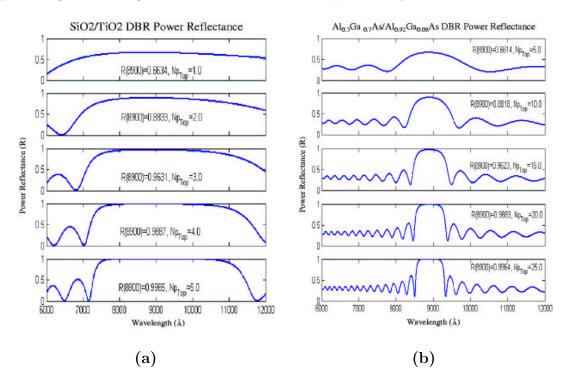

| 2.11. | Comparison of the number of (a) dielectric DBR periods to (b) semi-<br>conductor periods in order to achieve a given power reflectance. This<br>example was calculated using a $SiO_2/TiO_2$ dielectric stack, and an<br>$Al_{0.3}Ga_{0.7}As/Al_{0.92}Ga_{0.08}As$ semiconductor quarter-wave stack, both<br>on a GaAs substrate. It requires five times as many semiconductor<br>periods to match the reflectance of this dielectric stack. In addition,<br>note the large bandwidth of the dielectric DBR | 2-21 |

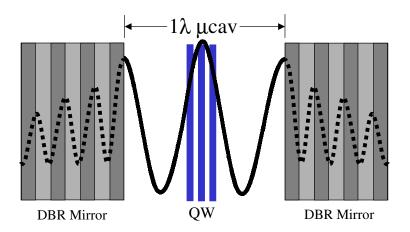

| 2.12. | Resonant electromagnetic standing wave in $1\lambda$ optical cavity resulting<br>from counter-propagating waves between the highly reflective DBR<br>mirrors. Since the DBR is not a perfect mirror at the cavity interface,<br>phase penetration of wave into the DBR stack occurs. The peak<br>antinode of this standing wave overlaps the active gain region                                                                                                                                             | 2-22 |

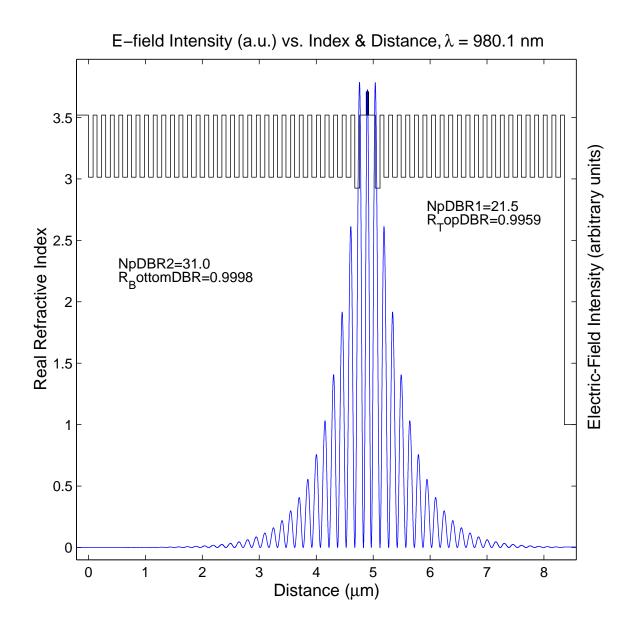

| 2.13. | Calculated electromagnetic standing wave for $1\lambda$ optical cavity with 99.9% reflective semiconductor DBR mirrors. The peak antinode of this standing wave overlaps the active gain region of the VCSEL.                                                                                                                                                                                                                                                                                               | 2-25 |

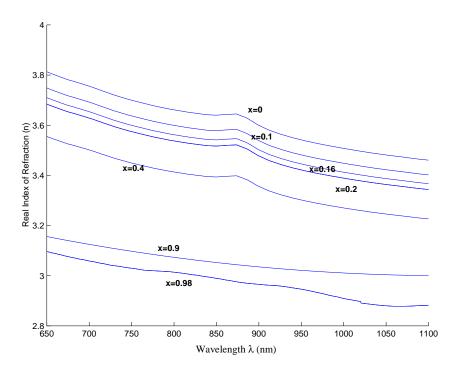

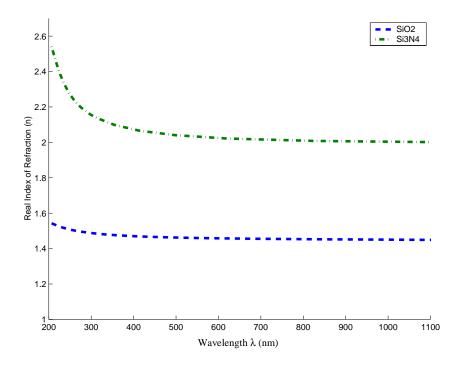

| 2.14. | Calculated resonant frequency vs. airgap thickness of a MEM tunable VCSEL device with a $Si_3N_4/SiO_2$ top DBR mirror                                                                                                                                                                                                                                                                                                                                                                                      | 2-28 |

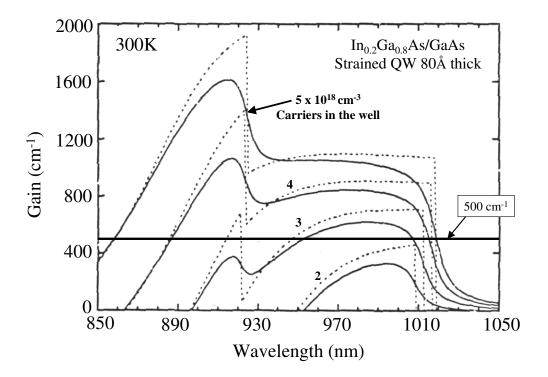

| 2.15. | Calculated gain bandwidth spectra for 80 Å $In_{0.2}Ga_{0.8}As$ QW with<br>multiple carrier densities [11]. Note the bandwidth range at $g_{th} =$<br>500 $cm^{-1}$ is 950 nm to 1010 nm ( $\Delta\lambda = 60$ nm)                                                                                                                                                                                                                                                                                         | 2-29 |

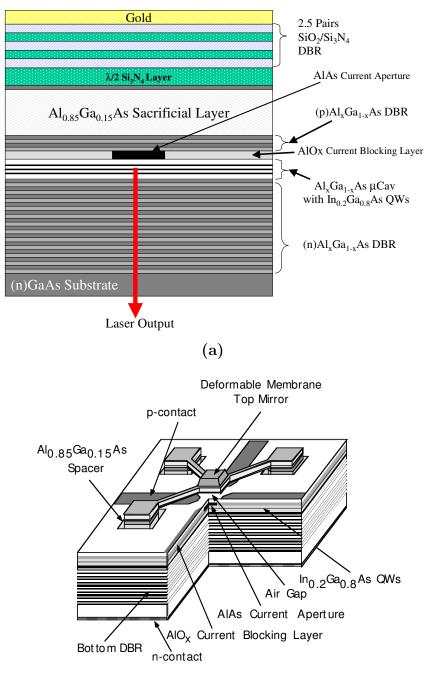

| 2.16. | Schematic diagrams of the Stanford MEM tunable VCSEL (a) pre-<br>fabrication material cross section, and (b) completed device [17].                                                                                                                                                                                                                                                                                                                                                                         | 2-30 |

| 2.17. | Step by step device fabrication schematic for Stanford MEMS tunable VCSEL [17].                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-31 |

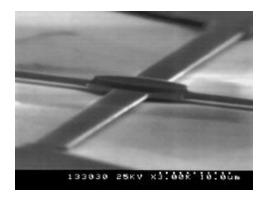

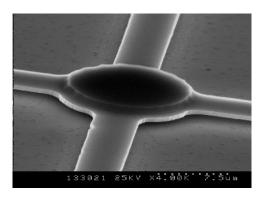

| 2.18. | SEM images of completed membrane VCSEL device [21]                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-33 |

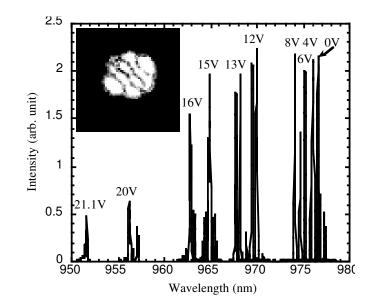

| 2.19. | Membrane VCSEL lasing wavelength vs. tuning voltage. This device<br>has an active tuning range of approximately 30 nm centered at 965                                                                                                                                                                                                                                                                                                                                                                       |      |

|       | nm. [17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-34 |

| Figure |                                                                                                                                                                                                                                                                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

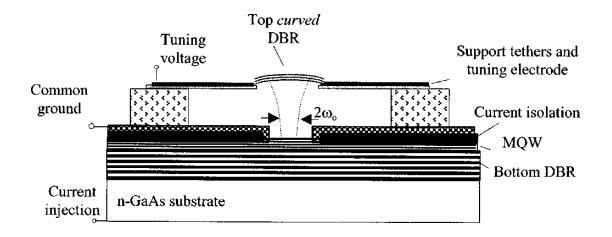

| 2.20.  | Schematic diagram of a Half-Symmetric Cavity tunable VCSEL device centered at 960 nm [21].                                                                                                                                                                                                                                                  | 2-35 |

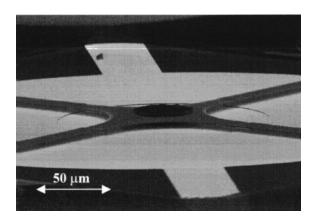

| 2.21.  | Scanning Electron Microscope image of a Half-Symmetric Cavity tun-<br>able VCSEL device centered at 960 nm [21].                                                                                                                                                                                                                            | 2-35 |

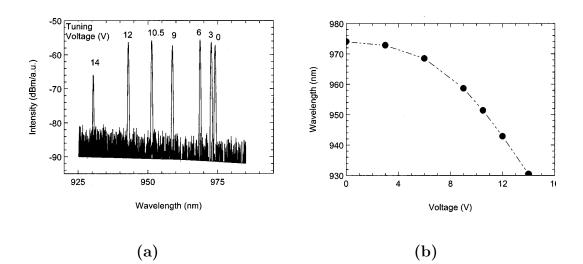

| 2.22.  | Tuning spectra (a) and tuning curve (b) of the half-symmetric tunable VCSEL device centered at 960 nm [21].                                                                                                                                                                                                                                 | 2-36 |

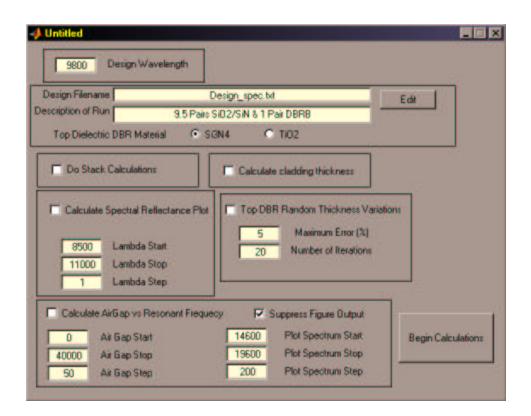

| 3.1.   | Application developed by the author to simplify modeling of optical devices.                                                                                                                                                                                                                                                                | 3-2  |

| 3.2.   | Three 80 $\mathring{A}$ quantum wells centered at an antinode in a $1\lambda$ -thick microcavity.                                                                                                                                                                                                                                           | 3-3  |

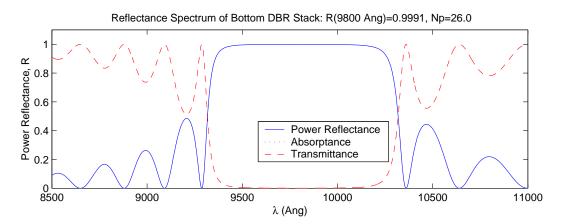

| 3.3.   | Calculated reflectance spectrum of a bottom DBR stack with a design<br>wavelength of $\lambda = 980nm$ , consisting of 26 alternating quarter-wave<br>Al <sub>0.90</sub> Ga <sub>0.10</sub> As/GaAs pairs, on a GaAs substrate.                                                                                                             | 3-4  |

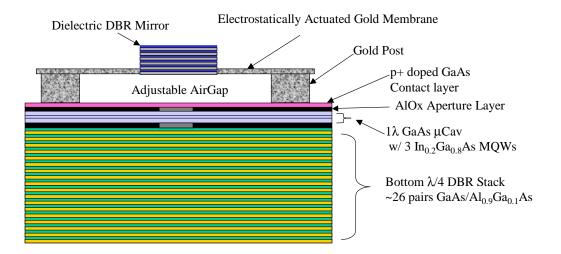

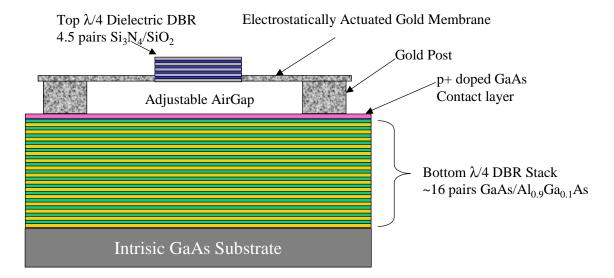

| 3.4.   | Simplified schematic of the desired tunable VCSEL design. Tuning<br>occurs by electrically actuating the top membrane, which reduces the<br>airgap between the top dielectric mirror $(SiO_2/Si_3N_4)$ and the highly<br>doped p+ top contact layer.                                                                                        | 3-5  |

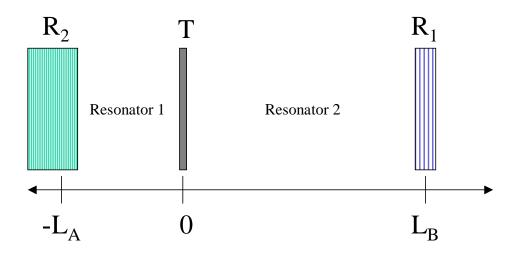

| 3.5.   | Two coupled optical resonators. The three mirrors are located at $z=-L_A$ , $L_B$ , and 0, respectively [1]. The shared mirror with transmittance T controls the amount of coupling between resonators                                                                                                                                      | 3-5  |

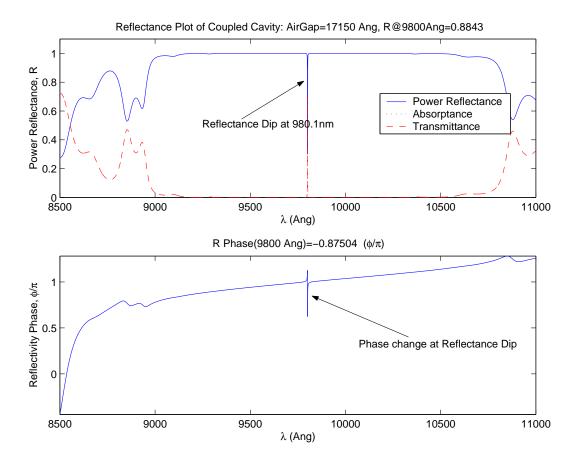

| 3.6.   | Reflectance spectrum of two coupled optical resonators separated by<br>a single pair of quarter-wave mirrors. The resonant frequency is de-<br>termined by the location of the reflectance dip. In this case the airgap<br>has a width of 17500 Å, and the resulting resonant frequency is found<br>at $\lambda = 9801$ Å.                  | 3-6  |

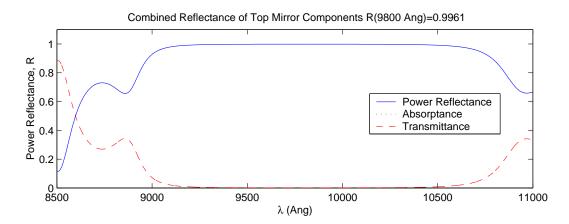

| 3.7.   | Reflectance spectrum of combined top mirror consisting of one quarter-<br>wave pair $Al_{0.98}Ga_{0.02}As/GaAs$ layers, a 17150 Å airgap, and 8.5 pairs<br>of quarter-wave $Si_3N_4/SiO_2$ . The top limit of the plot is determined<br>by the wavelength range of measured index data for the dielectric<br>materials (6500 Å to 11000 Å). | 3-7  |

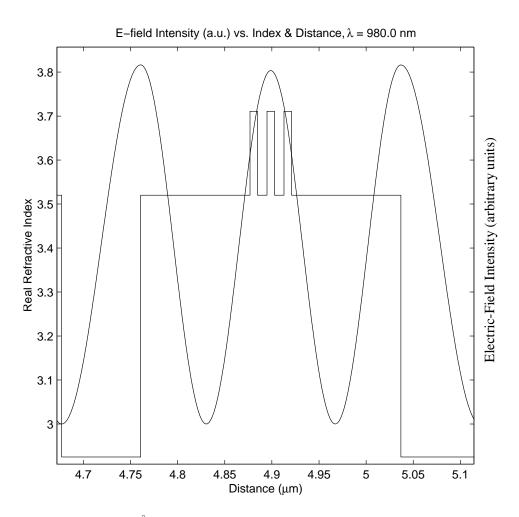

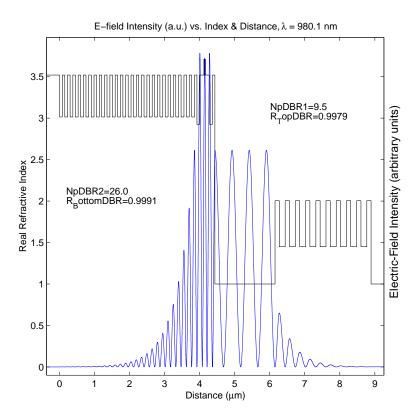

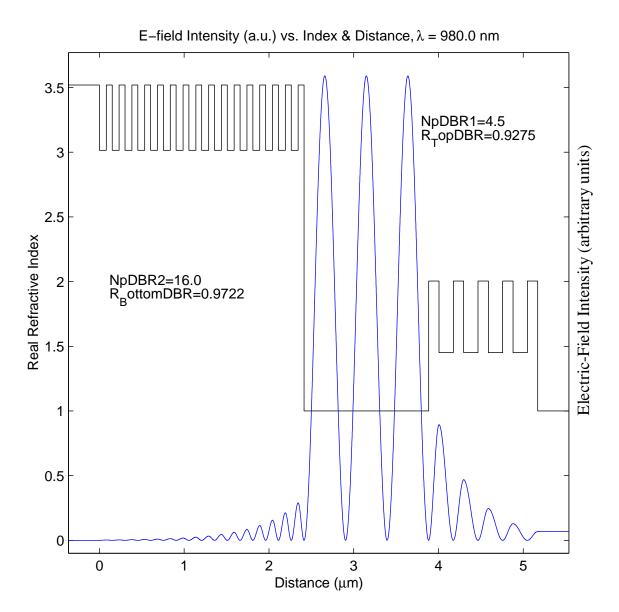

| 3.8.   | Electromagnetic standing wave pattern of a complete MEM tunable VCSEL device.                                                                                                                                                                                                                                                               | 3-8  |

xi

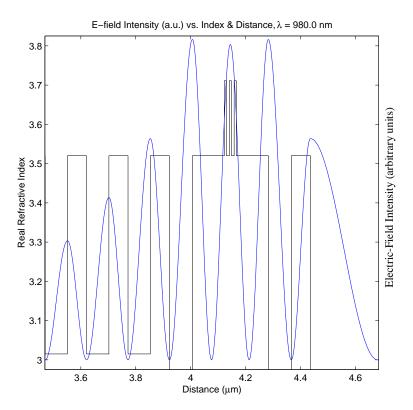

| 3.9.  | Correct placement of quantum wells at the center of a $1\lambda$ optical<br>cavity standing wave antinode. The FWHM of the central antinode<br>is calculated as $\nu_F = 700$ Å.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-9  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

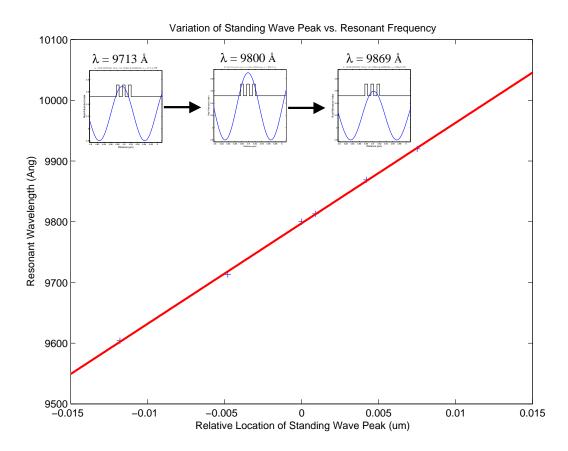

| 3.10. | Location of standing wave antinode relative to center of quantum<br>well as the resonant frequency is tuned. The relationship between<br>tuning frequency and peak location fits a linear relationship described<br>by $d = 0.604\lambda - 0.592 \ \mu m$ , where d is the shift from the central<br>QW in $\mu m$ . The inset figures shows the shifting central antinode for<br>$\lambda = 9713$ Å, 9800 Å, and 9869 Å.                                                                                                                                                                                                                                                                                                                                                                             | 3-10 |

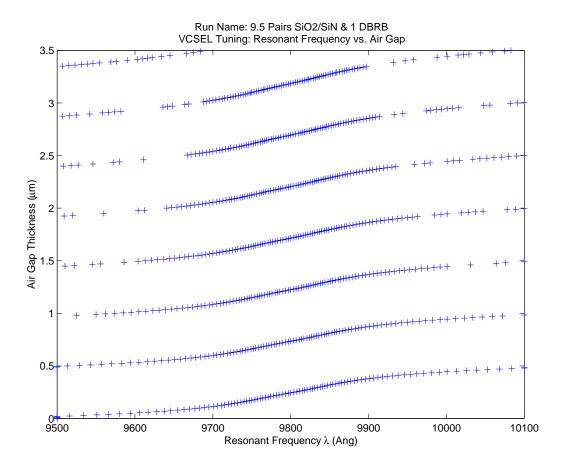

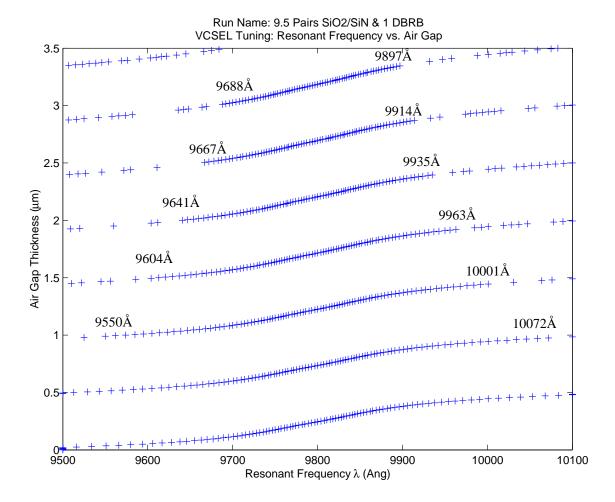

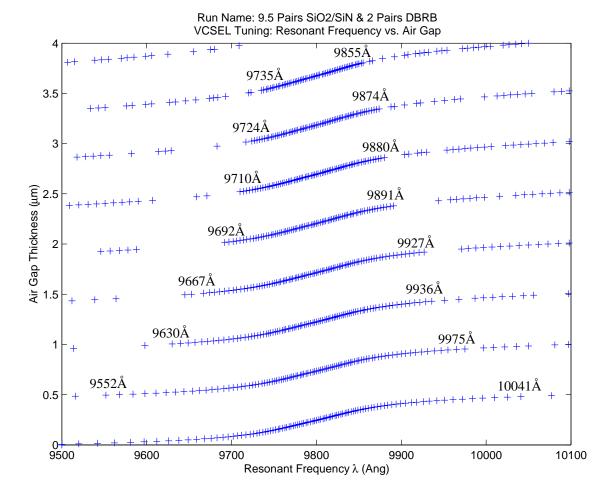

| 3.11. | Run #1 resonant frequency of the coupled cavity vs. airgap thickness.<br>This structure consists of a top DBR composed of <b>9.5 pairs</b> of $SiO_2$<br>and $Si_3N_4$ quarter-wave layers and <b>one pair</b> of quarter-wave layers<br>in the coupling stack. The bottom DBR is constructed of 26 pairs<br>of GaAs and Al <sub>0.9</sub> Ga <sub>0.1</sub> As quarter-wave layers on a GaAs substrate.<br>The $1\lambda$ -thick $\mu$ Cavity consists of GaAs cladding surrounding three<br>In <sub>0.2</sub> Ga <sub>0.8</sub> AsQWs. As the airgap increases, the FSR of the coupled<br>cavity decreases, defining a narrowing series of tuning bands. The<br>minimum and maximum resonant frequency for each tuning range is                                                                     |      |

|       | shown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-13 |

| 3.12. | Run #2 resonant frequency of the coupled cavity vs. airgap thickness.<br>This structure consists of a top DBR composed of <b>9.5 pairs</b> of <b>SiO</b> <sub>2</sub><br>and <b>Si</b> <sub>3</sub> <b>N</b> <sub>4</sub> quarter-wave layers and <b>two pairs</b> of quarter-wave layers<br>in the coupling stack. The bottom DBR is constructed of 26 pairs<br>of GaAs and Al <sub>0.9</sub> Ga <sub>0.1</sub> As quarter-wave layers on a GaAs substrate.<br>The <b>1</b> $\lambda$ - <b>thick</b> $\mu$ Cavity consists of GaAs cladding surrounding three<br>In <sub>0.2</sub> Ga <sub>0.8</sub> AsQWs. As the airgap increases, the FSR of the coupled<br>cavity decreases, defining a narrowing series of tuning bands. The<br>minimum and maximum resonant frequency for each tuning range is |      |

|       | shown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-14 |

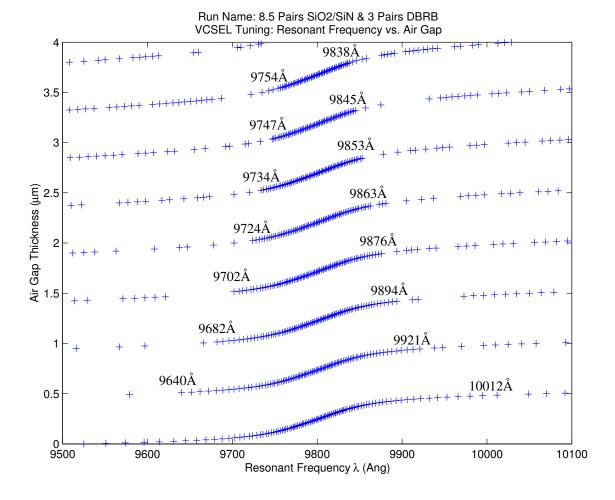

| 3.13. | Run #3 resonant frequency of the coupled cavity vs. airgap thickness.<br>This structure consists of a top DBR composed of 8.5 pairs of $SiO_2$<br>and $Si_3N_4$ quarter-wave layers and three pairs of quarter-wave lay-<br>ers in the coupling stack. The bottom DBR is constructed of 26 pairs<br>of GaAs and $Al_{0.9}Ga_{0.1}As$ quarter-wave layers on a GaAs substrate.<br>The $1\lambda$ -thick $\mu$ Cavity consists of GaAs cladding surrounding three<br>In <sub>0.2</sub> Ga <sub>0.8</sub> AsQWs. As the airgap increases, the FSR of the coupled<br>cavity decreases, defining a narrowing series of tuning bands. The<br>minimum and maximum resonant frequency for each tuning range is |      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

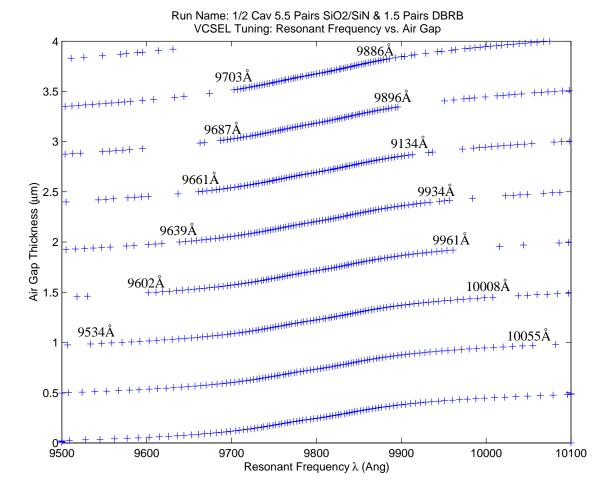

| 3.14. | shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-15 |

|       | This structure consists of a top DBR composed of <b>5.5 pairs</b> of $SiO_2$<br>and $Si_3N_4$ quarter-wave layers and <b>1.5 pairs</b> of quarter-wave layers<br>in the coupling stack. The bottom DBR is constructed of 26 pairs<br>of GaAs and Al <sub>0.9</sub> Ga <sub>0.1</sub> As quarter-wave layers on a GaAs substrate.<br>The $\lambda/2$ -thick $\mu$ Cavity consists of GaAs cladding surrounding three<br>In <sub>0.2</sub> Ga <sub>0.8</sub> AsQWs. As the airgap increases, the FSR of the coupled<br>cavity decreases, defining a narrowing series of tuning bands. The<br>minimum and maximum resonant frequency for each tuning range is                                             |      |

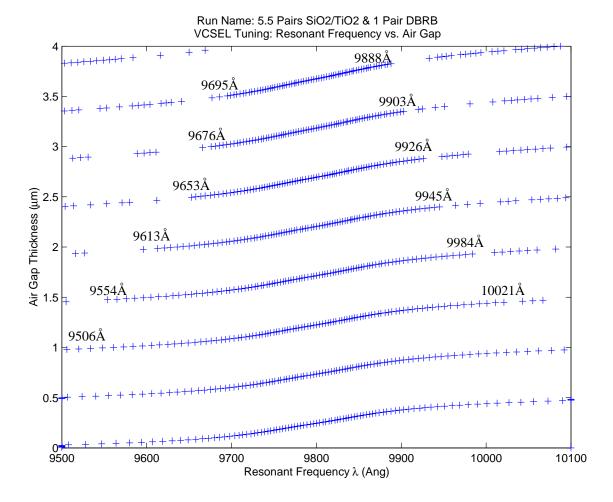

| 3.15. | shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-16 |

|       | shown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-17 |

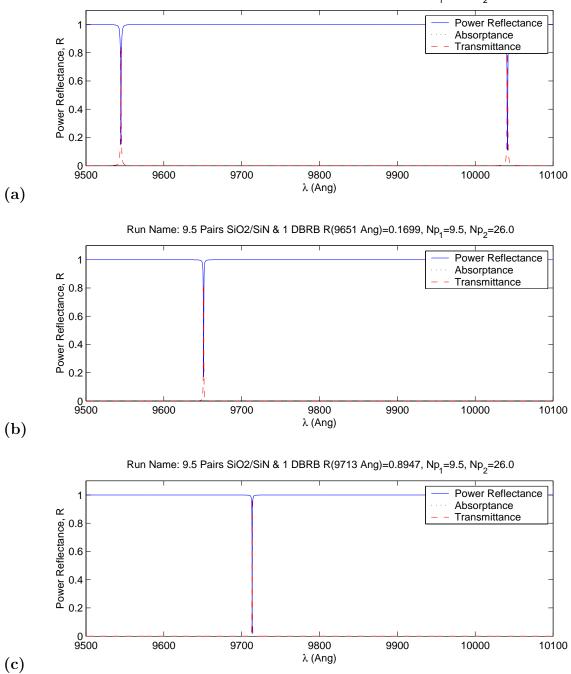

| 3.16. | Run #1 calculated reflectance dip for different airgap thicknesses: (a)<br>when the airgap = 14650 Å then $\lambda_{dip} = 9545$ Å and 10040 Å, (b) if the<br>airgap = 15250 Å then $\lambda_{dip} = 9651$ Å (c) and if the airgap = 15850 Å                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|       | then $\lambda_{dip} = 9713$ Å.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-18 |

xiii

| Page |

|------|

|------|

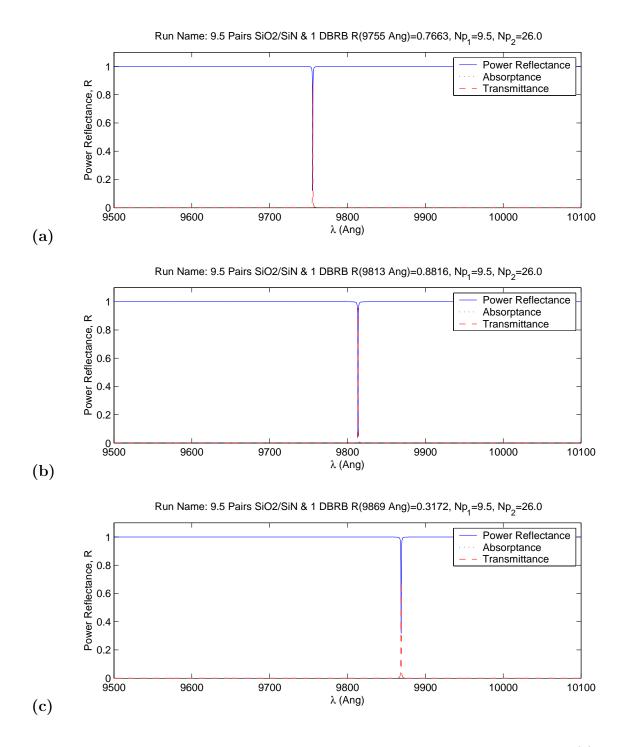

| 3.17. | Run #1 calculated reflectance dip for different airgap thicknesses: (a)<br>when the airgap = 16450 Å then $\lambda_{dip} = 9755$ Å, (b) if the airgap =<br>17350 Å then $\lambda_{dip} = 9813$ Å (c) and if the airgap = 18250 Å then $\lambda_{dip}$<br>= 9869 Å.                                                                                                                                           | 3-19 |

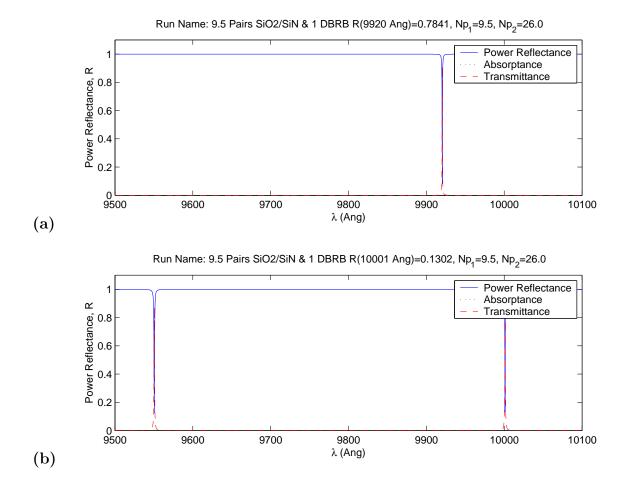

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.18. | Run #1 calculated reflectance dip for different airgap thicknesses: (a)<br>when the airgap = 18850 Å then $\lambda_{dip} = 9920$ Å, (b) and if the airgap<br>= 19450 Å then $\lambda_{dip} = 9550$ Å and 10001 Å                                                                                                                                                                                             | 3-20 |

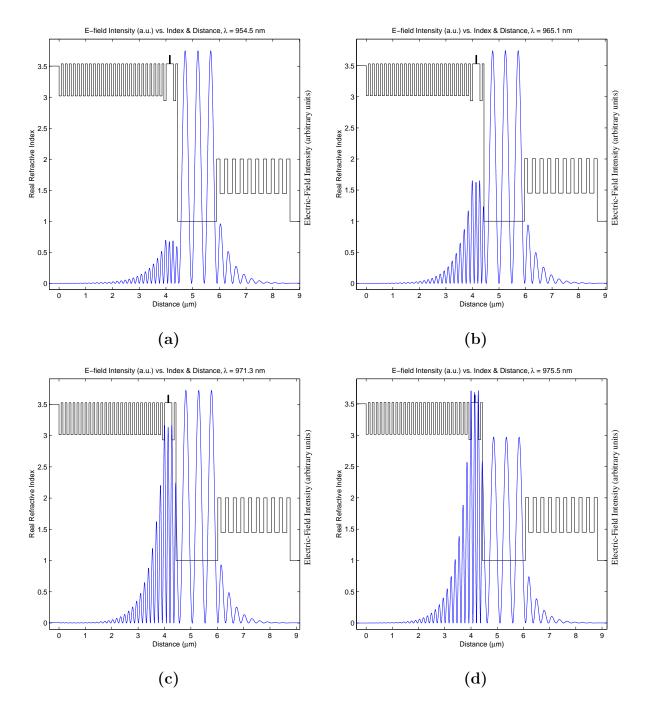

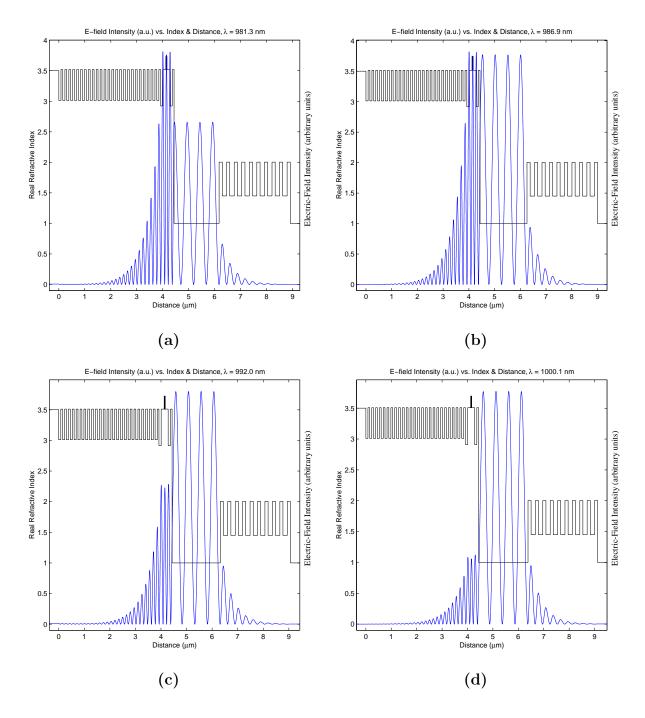

| 3.19. | Calculated standing wave for MEM tunable VCSEL design run #1 for<br>different airgaps: (a) when the airgap = 14650 Å then $\lambda = 9545$ Å, (b)<br>if the airgap = 15250 Å then $\lambda = 9651$ Å, (c) if the airgap = 15850 Å<br>then $\lambda = 0712$ Å (d) and if the airgap = 16450 Å then $\lambda = 0755$ Å                                                                                         | 3-21 |

| 3.20. | then $\lambda = 9713$ Å, (d) and if the airgap = 16450 Å then $\lambda = 9755$ Å.<br>Calculated standing wave for MEM tunable VCSEL design run #1 for<br>different airgaps: (a) when the airgap = 17350 Å then $\lambda = 9813$ Å, (b)<br>if the airgap = 18250 Å then $\lambda = 9869$ Å, (c) if the airgap = 18850 Å<br>then $\lambda = 9920$ Å, (d) and if the airgap = 19450 Å then $\lambda = 10001$ Å. | 3-21 |

| 3.21. | Simplified schematic of a tunable Fabry-Perot design. Tuning occurs<br>by electrically actuating the the gold membrane and causing it to flex<br>downward toward the highly doped p+ top contact layer. This is<br>identical to the VCSEL design, except for lower reflectivity mirrors<br>and no active gain region.                                                                                        | 3-23 |

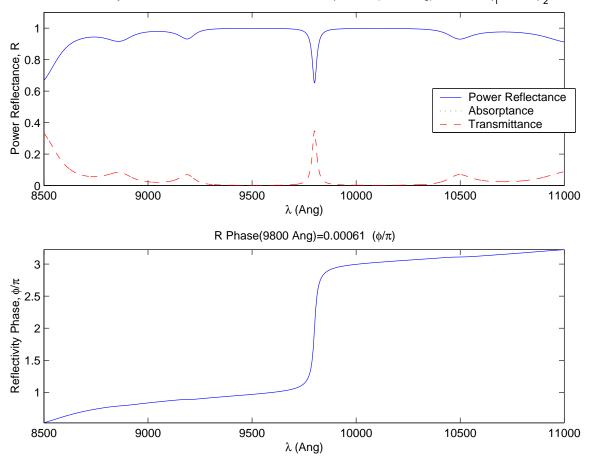

| 3.22. | Spectral reflectance plot of resonant Fabry-Perot etalon with bottom DBR consisting of 16 pairs $GaAs/Al_{0.9}Ga_{0.1}As$ and top DBR fabricated from 4.5 pairs $Si_3N_4/SiO_2$ . The air optical cavity has a thickness of 14700Å.                                                                                                                                                                          | 3-24 |

| 3.23. | Electromagnetic standing wave of a multilayer Fabry-Perot etalon<br>with bottom DBR consisting of 16 pairs $GaAs/Al_{0.9}Ga_{0.1}As$ on a<br>GaAs substrate and top DBR fabricated from 4.5 pairs $Si_3N_4/SiO_2$ .<br>The air optical cavity has a thickness of 14700 Å.                                                                                                                                    | 3-25 |

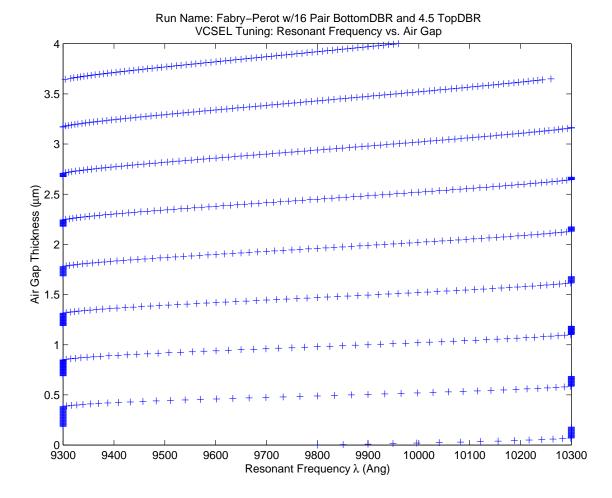

| 3.24. | Resonant frequency of Fabry-Perot etalon vs. airgap thickness for the structure shown in figure 3.21. Note this plot only shows a resonant frequency range from $\lambda = 9300$ Å to 10300 Å due to computing limitations. The bottom tuning band extends from 8500 Å to 11000 Å.                                                                                                                           |      |

|       | As the airgap increases the FSR of the tuning bands decreases                                                                                                                                                                                                                                                                                                                                                | 3-26 |

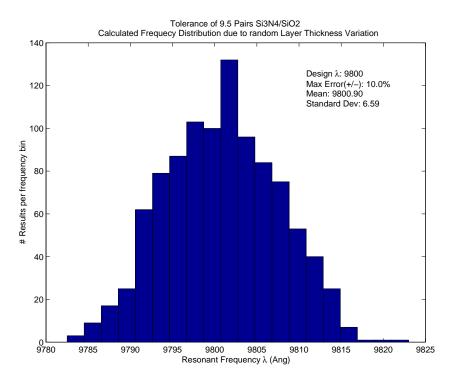

| 3.25. | Monte-Carlo analysis of VCSEL resonant frequency distribution due<br>to random thickness variations in the dielectric DBR layers. Maximum<br>imposed error is $\pm 10\%$ , which translates into $\pm 167$ Åfor the SiO <sub>2</sub>                                                                                                                                                                                           |      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

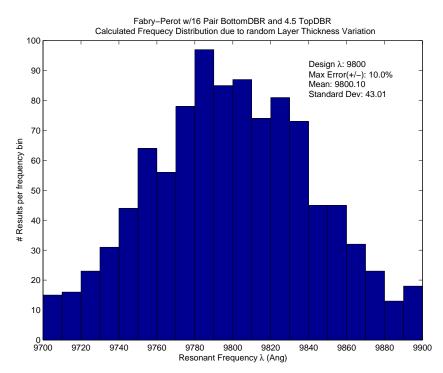

| 3.26. | layers, and $\pm 122$ Åfor the Si <sub>3</sub> N <sub>4</sub> layers                                                                                                                                                                                                                                                                                                                                                           | 3-27 |

| 3.20. | tion due to random thickness variations in the dielectric DBR layers (for the design shown in figure 3.4). The maximum possible error is $\pm 10\%$ , which translates into $\pm 167$ Åfor the SiO <sub>2</sub> layers, and $\pm 122$ Åfor the Si <sub>3</sub> N <sub>4</sub> layers. The deviation of the Fabry-Perot resonant frequency                                                                                      |      |

| 2.07  | is much larger than the VCSEL deviation.                                                                                                                                                                                                                                                                                                                                                                                       | 3-28 |

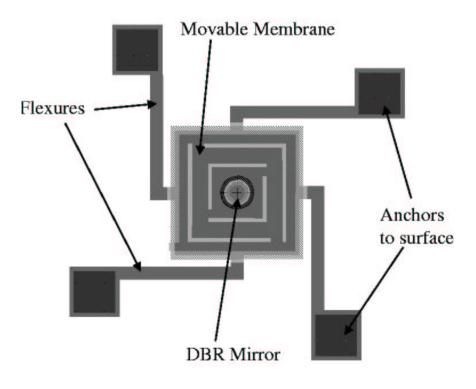

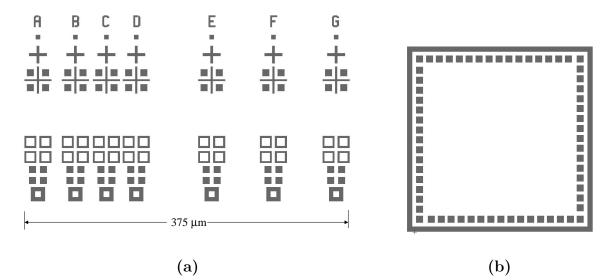

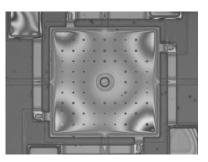

| 3.27. | Schematic layout of MEM device with four flexures attached to the wafer surface and a 150 $\mu m$ $\times$ 150 $\mu m$ mechanical membrane                                                                                                                                                                                                                                                                                     | 3-29 |

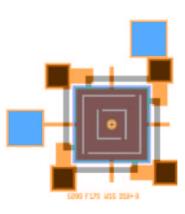

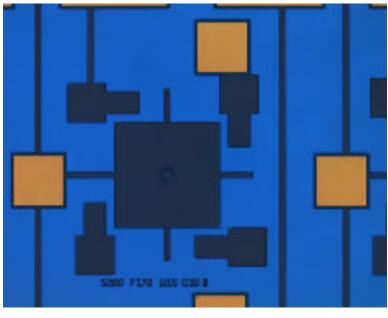

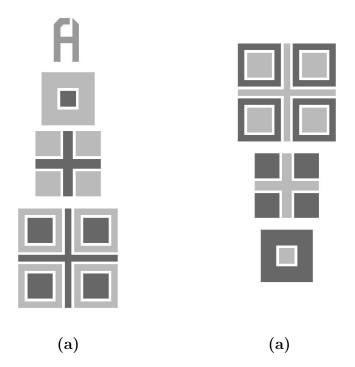

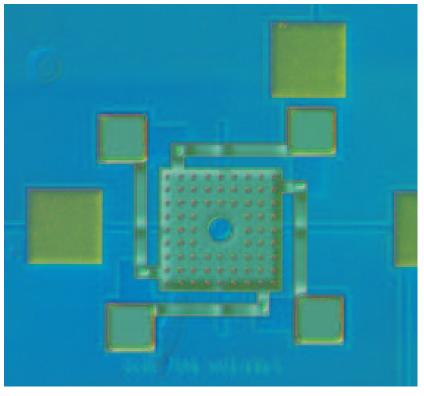

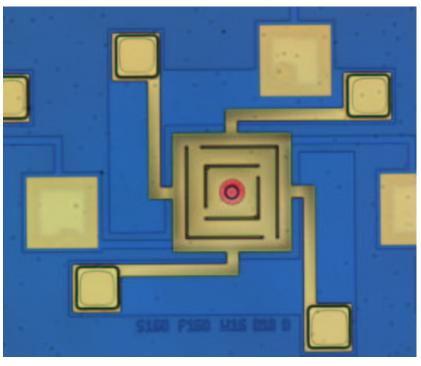

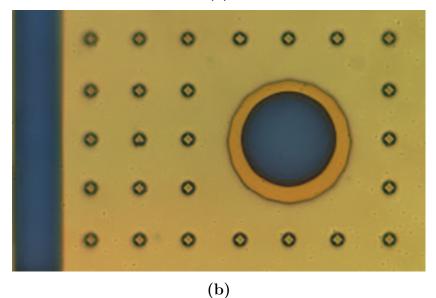

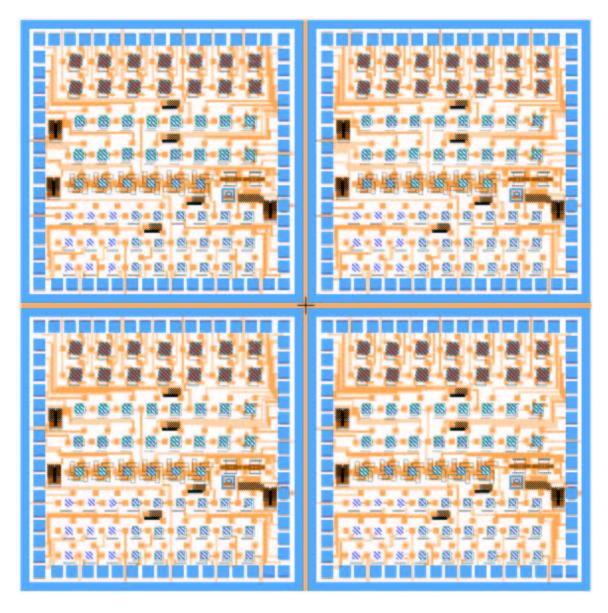

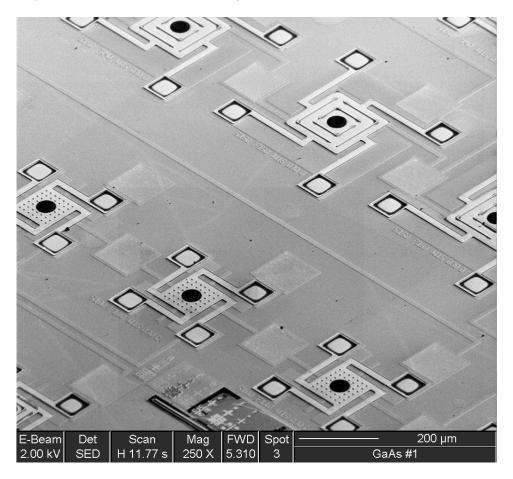

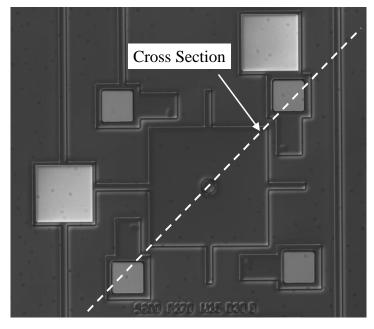

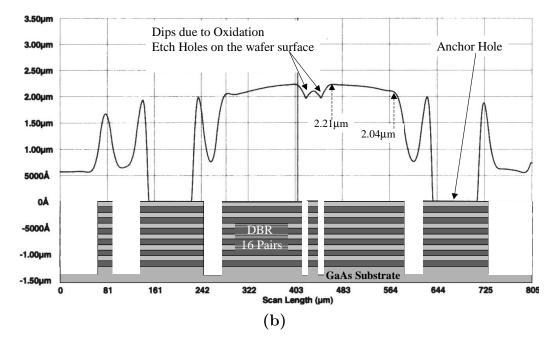

| 4.1.  | Schematic top view of a seven layer mask layout for an example MTV device.                                                                                                                                                                                                                                                                                                                                                     | 4-1  |

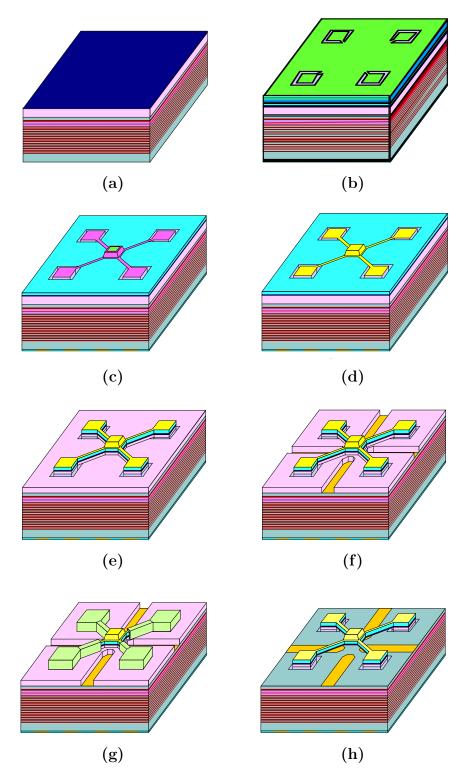

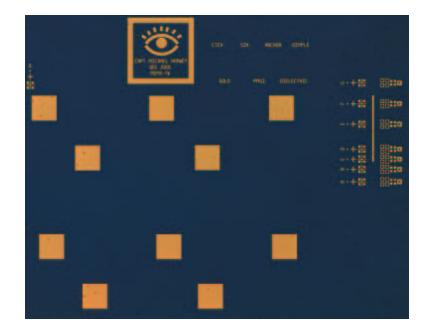

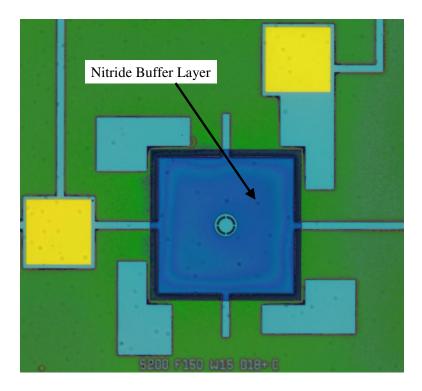

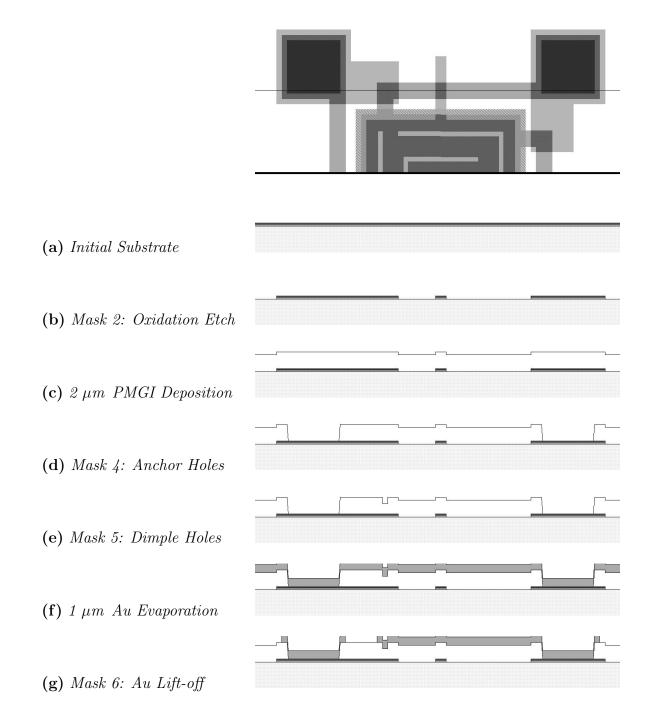

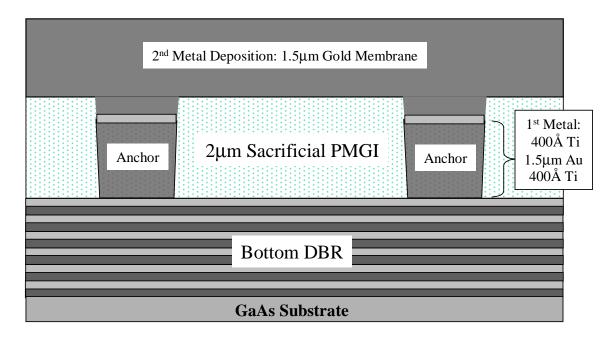

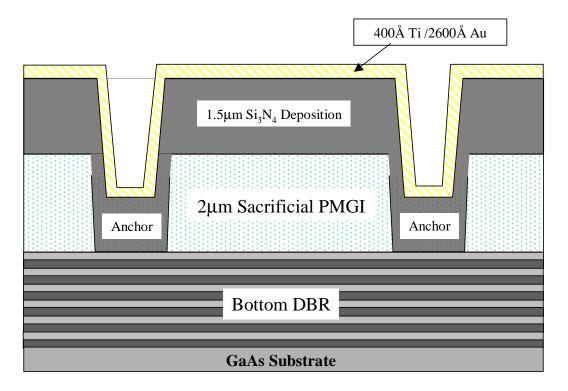

| 4.2.  | Process flow for MTV fabrication. Sacrificial PMGI, 2 $\mu$ m-thick, is<br>spun-on between deposition of the silicon nitride buffer layer (mask                                                                                                                                                                                                                                                                                |      |

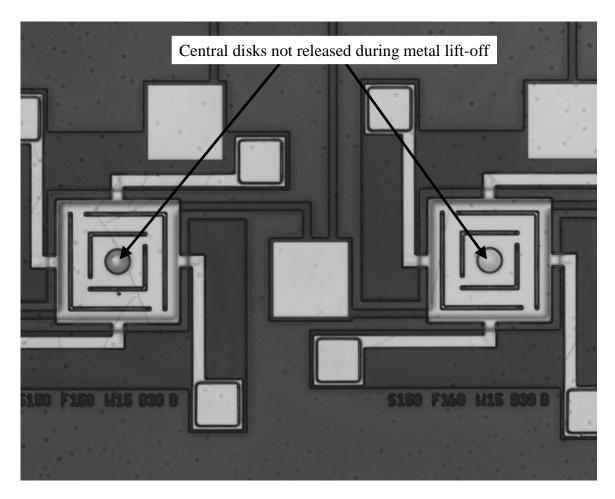

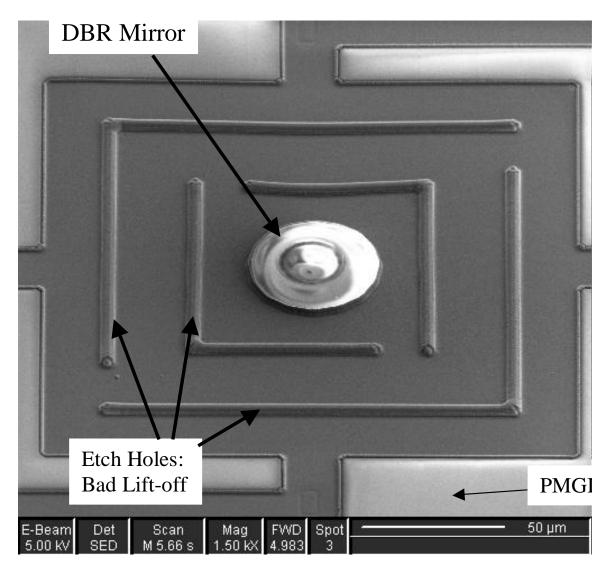

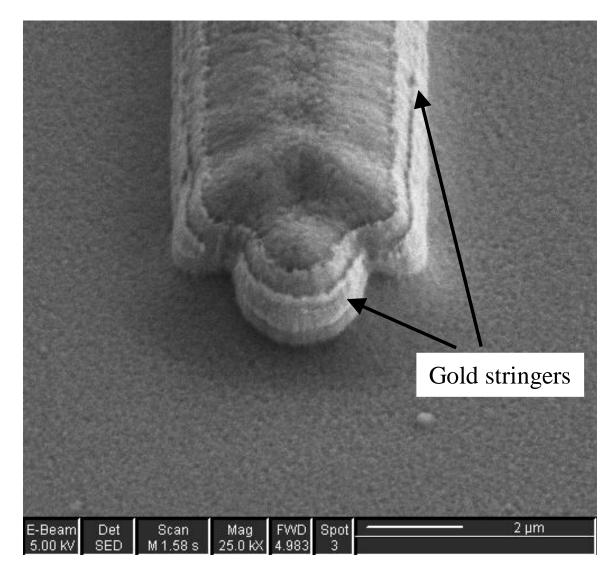

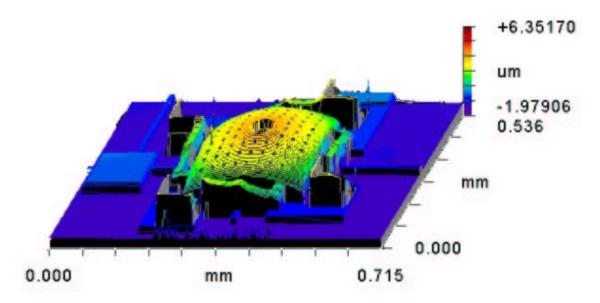

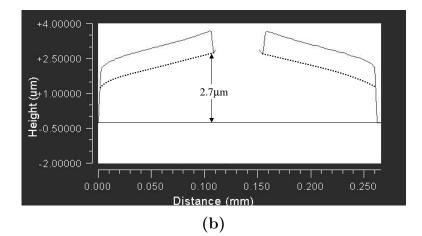

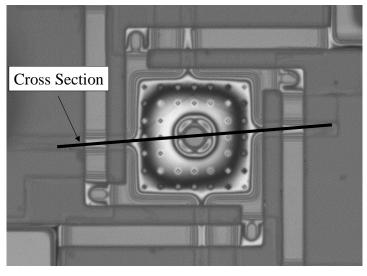

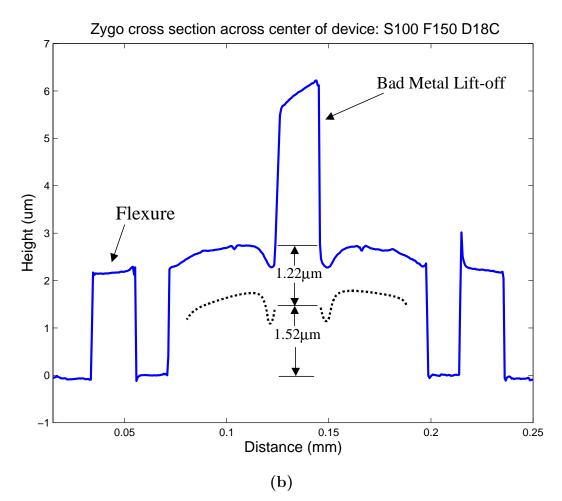

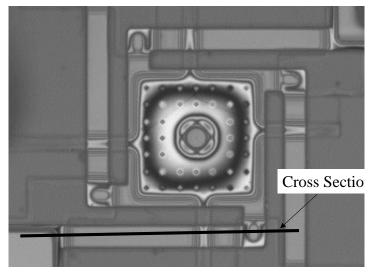

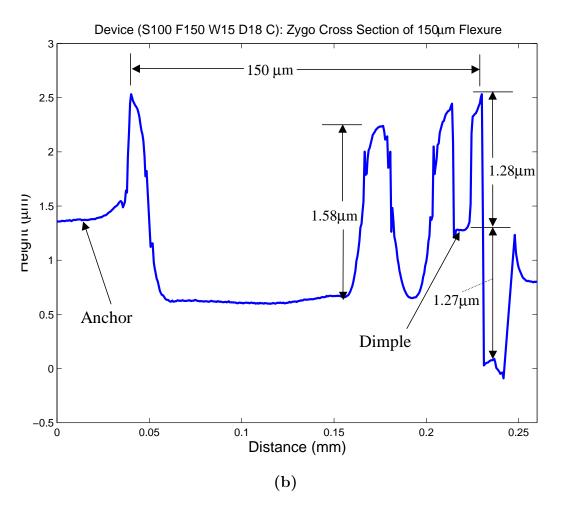

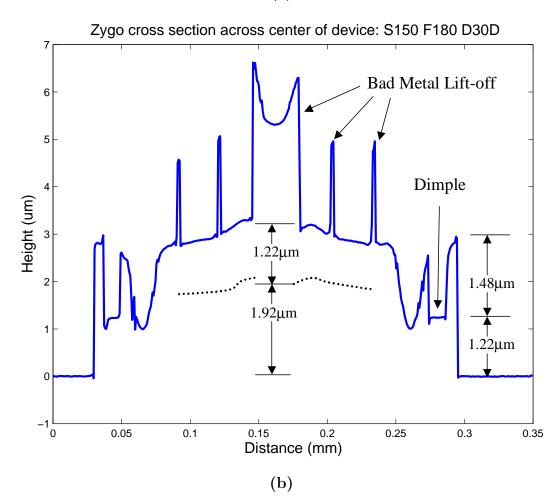

|       | #3) and the anchor etch (mask #4). $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                         | 4-3  |