## Novel Synthesis Methodology in Digital IC Design and Automation to Reduce NRE costs and Time-to-Market

Basireddy Karunakar Reddy

A Dissertation Submitted to

Indian Institute of Technology Hyderabad

In Partial Fulfillment of the Requirements for

The Degree of Master of Technology

Department of Electrical Engineering

#### **Declaration**

I declare that this written submission represents my ideas in my own words, and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources that have thus not been properly cited, or from whom proper permission has not been taken when needed.

18. Kellurckel Redoly

(Signature)

Basireddy Karunakar Reddy

EE12M1006

### Approval Sheet

This thesis entitled "Novel Synthesis Methodology in Digital IC Design and Automation to Reduce NRE costs and Time-to-Market" by Basireddy Karunakar Reddy is approved for the degree of Master of Technology from IIT Hyderabad.

| -018U                             |

|-----------------------------------|

| External Examiner                 |

| V- Le Pene Entre                  |

| Internal Examiner Ashrolet Dontha |

| Adviser                           |

| Co-Adviser                        |

| Chairman                          |

### Acknowledgements

I am thankful to Dr. Amit Acharyya for patiently listening to my foolish ideas, and guiding and supporting me to make them innovative ideas.

I would like to thank Dr. Asudeb Dutta, Dr. Shiv Govind Singh, and Dr. Siva Rama Krishna for providing me the required theoretical knowledge through the courses and projects.

I also want to thank Mr. Srinivas Sabbavarapu for helping me through out in my project.

Finally, I would like to thank my friends who always helped me to shape my character.

| Dedicated | to |

|-----------|----|

|-----------|----|

Kṛṣṇa, My Family and Friends......

#### Abstract

The number of incremental and iterative steps in the digital IC design & automation methodology will decide the non-recurring-engineering (NRE) costs and time-to-market (TTM). Since the aforementioned factors are the major driving factors of the IC design industry, many algorithms were proposed in the last few decades to minimize/optimize the number of design steps in the conventional digital IC design & automation methodology. However, the conventional frontend and backend designs have been carried out separately, which has limited the further minimization of design steps. Here we propose a novel digital IC design & automation methodology, which reduces the NRE costs and TTM by merging the frontend and backend designs partially. It maps the input RTL description directly to their corresponding physical layouts (derived using the existing CAD tools and stored in a pre-computed library) without going through the all the steps in conventional logic and physical synthesis process. As part of the proposed methodology, we use a pre-computed library which stores all required physical layouts and their Boolean functions. We have exploited the functional symmetry and negation-permutation-negation (NPN) class representations to decoct the library size and number of comparisons. The functional symmetry reduced the number of required pre-computed circuits in our experiments from 1031 to 222 (464.4% reduction in the memory size) and helps in maintaining the regularity in the design, which is a major concern for engineering change order.

To minimize the number steps further, complexity and memory requirements, we have proposed a new graph data structure called Shannon Factor Graph (SFG) and cut-less mapping technique for technology dependent mapping. The preliminary findings show the effectiveness of the proposed methodology.

## **Contents**

|     | Decl  | aration                                                            | ii  |

|-----|-------|--------------------------------------------------------------------|-----|

|     | Appı  | roval Sheet                                                        | iii |

|     | Ackı  | nowledgements                                                      | iiv |

|     | Abst  | ract                                                               | vi  |

| 1   | Intro | oduction                                                           | 1   |

|     | 1.1   | Conventional Digital IC Design and Automation Methodology          | 1   |

|     | 1.2   | Proposed Digital IC Design and Automation Methodologies            | 4   |

|     |       | 1.2.1 Cut-based methodology                                        | 4   |

|     |       | 1.2.2 Cut-less methodology                                         | 5   |

|     | 1.3   | Thesis Outline.                                                    | 6   |

| 2 . | And-  | -Inverter Graph (AIG) and Shannon Factor Graph (SFG)               | 7   |

|     | 2.1   | And-Inverter Graph (AIG)                                           | 7   |

|     |       | 2.1.1 Definition                                                   | 7   |

|     |       | 2.1.2 AIG construction.                                            | 8   |

|     | 2.2   | Functionall Reduced AIGs (FRAIGs)                                  | 9   |

|     | 2.3   | Shannon Decomposition Theorem.                                     | 10  |

|     | 2.4   | Brief Introduction to Binary Decision Diagrams (BDD)               | 10  |

|     | 2.5   | Proposed Shannon Factor Graph (SFG)                                | 10  |

|     |       | 2.5.1 Non-decomposed, constant one, constant zero and shared nodes | 11  |

|     |       | 2.5.2 Construction of Propose SFG.                                 | 11  |

|     |       | 2.5.2.1 SFG construction without considering the nature of nodes   | 11  |

|     |       | 2.5.2.2 SFG Construction-considering the nature of nodes           | 14  |

|     |       | 2.5.2.3 SFG construction for multiple outputs                      | 15  |

|     |       | 2.5.2.4 Comparison of the algorithm 2.1 & 2.2.                     | 17  |

|     |       | 2.5.3 Comparison of SFG with AIG and BDD.                          | 19  |

|     | 2.6 S | SFG for Cut-less Technology Mapping                                | 21  |

| 3   | Cut-  | based Technology Mapping                                           | 22  |

|     | 3.1   | Cut-computation                                                    | 22  |

|     |       | 3.1. k-feasible cut.                                               | 22  |

|     | 3 2   | Technology Manning                                                 | 23  |

| 3.3         | Drawbacks of the Cut-based Technology Mapping                                        | 24   |

|-------------|--------------------------------------------------------------------------------------|------|

| 4 Nega      | ation-Permutation-Negation (NPN) Classes and Functional Symmetr                      | ry25 |

| 4.1         | Negation-Permutation (NPN) Class                                                     | 25   |

|             | 4.1.1 Implementations of n-input functions                                           | 26   |

|             | 4.1.2 Concept of P class.                                                            | 27   |

|             | 4.1.3 The Concept of NPN class.                                                      | 28   |

|             | 4.1.4 NPN semi-canonical algorithm.                                                  | 29   |

| 4.2         | Canonical Representation-Functional Symmetry.                                        | 29   |

|             | 4.2.1 Functional Symmetry along with the proposed modification                       | 31   |

| 5 Prop      | posed Cut-based Digital IC Design and Automation Methodology                         | 33   |

| 5.1         | Pre-Computed Library                                                                 | 33   |

| 5.2         | Boolean Matching                                                                     | 34   |

| 5.3         | Mapping Without Considering the Functional Symmetry                                  | 34   |

| 5.4         | Results and Discussion.                                                              | 37   |

| 5.5         | Mapping with Functional Symmetry                                                     | 39   |

| 6 Prop      | posed Cut-less Digital IC Design and Automation Methodology                          | 43   |

| 6.1         | Cut-less Technology Mapping.                                                         | 44   |

| 6.2<br>Tool | Modified Digital IC Design and Automation Methodology Using Cut-less hnology Mapping | 15   |

| 6.3         | Results and Discussion.                                                              |      |

| 7 Con       | clusion and Future Scope of Work                                                     |      |

| 7.1         | Conclusion                                                                           |      |

|             | Future Scope of Work.                                                                |      |

|             | ıres                                                                                 |      |

| 8.1         | Gajski-Kuhn chart                                                                    |      |

| 8.2         | Simplified conventional digital IC design & automation methodology                   |      |

| 8.3         | AIG Graph                                                                            |      |

| 8.4         | Shannon Cofactor and cube cofactor computation                                       |      |

| 8.5         | Basic structure of the Shannon Factor Graph (SFG).                                   |      |

|             |                                                                                      |      |

| 8.6         | Illustration of K-feasible cuts of an AIG graph                                      | 23   |

| 8.7         | Detailed design flow of the proposed cut-based design and automation                 | 3/1  |

| R | efere | nces                                                            | 60 |

|---|-------|-----------------------------------------------------------------|----|

|   | 8.10  | Modified design and automation methodology                      | 45 |

|   | 8.9   | Illustration of proposed cut-less technology mapping technique  | 14 |

|   | 8.8   | The variation of average runtime with number of input variables | 41 |

## Chapter 1

## Introduction

#### 1.1 Conventional digital IC design and automation methodology

The Non-Recurring Engineering (NRE) costs, which is one time investment for Computer-Aided Design (CAD) tools, design effort, mask generation, and design time (which is part of the NRE cost) have been considered as major factors to decide the product cost and productivity. With continued technology scaling, the design of current and future generations of digital integrated circuits (ICs) is increasingly becoming more complex. Due to such complexity, meeting design cost constraints with high productivity at the same time is a truly daunting task [1]. According to [2] "cost of design is the greatest challenge to continuation of the semiconductor roadmap" and the annual tool costs (part of NRE) per designer increase 3.9% per year. Hence if the NRE costs can be cut down, overall price of the product will reduce, leading to increased demand for the product. On the other hand, when the design time of a product goes up, consequently its demand and revenue earned will be reduced. As for example, delay of half of the design time in productivity will lead to reduction in demand and revenue by 75% [2]. Therefore significant amount of research is going on in the IC design industry and academia to reduce the NRE cost and time-to-market.

These two factors are majorly influenced by design & automation methodologies/flows that one follow during the design of any system (digital in our case). Therefore, we start our discussion with conventional digital IC design and automation methodology [3].

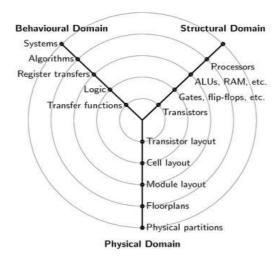

Conventional industry-standard IC design methodology includes hierarchical design and automated synthesis steps. The design abstraction usually starts from the register transfer-level (RTL) with an aim to obtain the final IC layout through logic synthesis (frontend design) and physical synthesis (backend design). The design methodology follows the original Y-chart representation proposed by Gajski and Kuhn [3], also known as the Gajski Chart (shown in Fig. 1.1). The basic premise of this methodology is to use separate the frontend and backend CAD tools in incremental and iterative steps to achieve the final

design layout. Frontend CAD tools convert the RTL description of a design to the gate level netlist through translation, optimization and technology mapping [4, 5] and the backend converts the netlist into final IC layout through floor planning, placement and routing [1, 3]. This whole process is termed as clockwise Gajski chart flow. The clockwise Gajski chart flow represents the design in three hierarchical domains, functional/behavioral, structural and physical/geometrical, and refinement is conducted in steps as shown in Fig. 1.1.

**Functional representation:** At highest level of abstraction, the designer will consider what the chip does. For instance, the Boolean expression y=ab + (ab)' tells us about only its function where its output is 'y' and inputs are 'a' and 'b', but does not say anything about its implementation and structure of the cell. Functional representation of a design may be captured on several levels.

**Structural representation:** It's a bridge between functional representation and geometrical representation. The Boolean function is mapped to the corresponding components (ex: NAND) and connections based some objective function (are, delay... etc.) however it doesn't say anything about the physical parameters, like positions of the components on the printed circuit board silicon chip. Depending upon the design entry structural representation may serve the functional/behavioral representation.

**Geometrical representation:** The final representation ignores, as much as possible, what the design is supposed to do and binds its structure in space (physical design) or to silicon (geometrical design).

Each of the above representations may have several local representations as shown in the Fig. 1.2.

Figure 1.1: Gajski-Kuhn chart

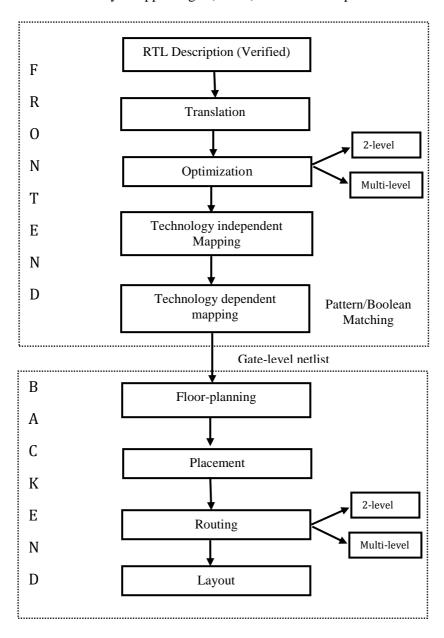

The conventional design automation methodology, shown in Fig. 2, consists of incremental and iterative steps from RTL description to final physical. At each design step a separate algorithm should be run by the respective CAD tools to convert the RTL design description to corresponding gate level netlist (fig.1). The translated logic is optimized to get best performance in terms of area, delay and power. Before mapping the optimized logic to the target technology gates, a technology independent mapping is done, later possible logic optimizations are done through local transformations. Based on the given specifications this process is carried iteratively. Mapped logic (netlist) is fed as the input to the backend tools

Figure 1.2: Simplified conventional digital IC design & automation methodology

and they mostly carry out the floorplan, placement and routing iteratively. Initial floorplan and placement influence the final routing congestion. The routing tool has to route wires among the gates of a block (intra routing) and also among the different blocks (inter routing). Routing within the block decides the congestion probability. To do all this, different algorithms have to be run by the tool at each step iteratively. So we can conclude that we need different tools for frontend and backend, and large design time to get a quality product.

Therefore with high productivity and low cost target, there has been growing research interest in CAD tools development domain to reduce the NRE costs for complex systems design and also to simplify design steps to improve time-to-market. However meeting such conflicting design trade-offs among the design complexity, high productivity and low cost requirements is highly challenging.

To address the design complexity various techniques have been proposed so far. A unified model of the design representation is proposed in [3] where the design is described in three hierarchical domains (behavioral, structural, physical) with different levels of abstraction. The circuit-performance including power consumption, area and delay depends on the quality of the logic synthesis [6]. Therefore the main research focus has been on the optimization of logic synthesis process [4, 5, 7-9], mainly the Graph based logic synthesis using Binary Decision Diagrams (BDD) and And-Invert-Graphs (AIG) which have already been proven to be an effective way for logic optimization and technology mapping. Recently in [10], a shift from the logic synthesis is observed, where the new circuit/netlist structure is retrieved from the pre-computed library, instead deriving it each time by skipping the optimization phase. Although this is an unconventional attempt, but the number of circuits to be stored using this approach is significantly large. Moreover the corresponding library has to be loaded with new circuits, when they are not found in the existing library. Therefore large memory is required for such design strategy to store all industrial benchmark circuits, which increases search space and design time. Therefore, we envisage a design automation methodology with reduced number of steps combining these two to reduce NRE costs and time-to-market, which is discussed next.

#### 1.2 Proposed Digital IC Design and Automation Methodologies

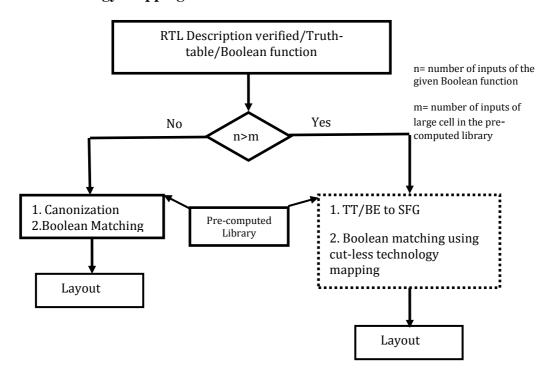

We have proposed two methodologies, one is cut-based and another one is cut-less.

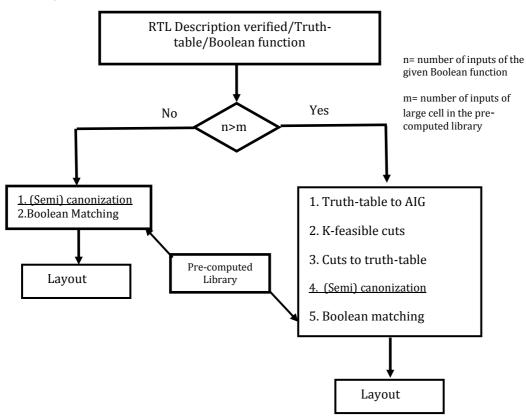

#### 1.2.1 Cut-based methodology

We propose a novel, unconventional and unified design methodology [12] by merging the logic synthesis (frontend) with physical design (backend) partially. Our proposed

methodology benefits from reduced number of design steps by creating a direct link from the RTL/behavioral description to the physical design in the original Gajski chart [3]. The direct physical design step is facilitated through the previously stored and pre-computed technology libraries. To minimize the storage requirements only the physical designs of negation-permutation-negation (NPN) class functions along with their Boolean expressions [11] are stored instead of the extensive industrial benchmarks as proposed in [10]. Thus it drastically reduces the iterative loading and re-loading overheads used in the conventional design methodology. As for an example, 1478 NPN class functions are needed in [10] to represent only the 4-input frequently appearing industrial circuits, whereas our proposed methodology reduced this number to 1031 (a reduction of 30%), which can be used to map any Boolean expression without any limitation on number of input variables of the function. We have also exploited the functional symmetry along with the NPN class representation to minimize the library size further and to improve the regularity of the We show that due to such unified design methodology with reduced complexity, NRE costs and Time-to-market are reduced significantly. The functional symmetry reduced the number of required precomputed circuits in our experiments from 1031 to 222 (464.4% reduction in the memory size) and helps in maintaining the regularity in the design, which is a major concern for engineering change order.

The aforementioned methodology uses the cut-based technology mapping technique for mapping the input RTL/Boolean expressions/truth-tables to the cells of the pre-computed library. The following proposed methodology points out the drawbacks of the cut-based methodology and shows a possible solution for solving them.

#### 1.2.2 Cut-less methodology

The methodology proposed in [11-14] are cut-based methodologies, which require cut-enumeration, storing of cuts and computation of canonical form for mapping. The cut-enumeration is computationally complex and requires more memory for storing the cuts. If there are n number of nodes and k is the cut size, then the possible number of cuts is  $O(n^k)$ , which is exponentially growing with the cut size and number of nodes. Due to this the runtime and required memory grows exponentially, thereby it affects the overall design cycle for highly complex designs. Here, we propose a cut-less mapping technique and a new graph data structure [15], called Shannon Factor Graph (SFG), for mapping the input RTL/behavioral description directly to their final physical layouts. The information stored at each node of the SFG can be used to map the nodes to the technology dependent cells without enumerating the cuts. The embedded intelligence of the SFG takes the advantage of the library cell's size. This feature of the SFG minimizes the graph building time and

required memory significantly. The proposed cut-less mapping technique can improve the design time and required memory further, which will reduce the time to market and NRE costs significantly.

#### 1.3 Thesis Outline

The thesis is organized as follows. Chapter 2 describes the AIG and its construction, functionally reduced AIG (FRAIG), then proposed Shannon Factor Graph (SFG) for cutless mapping. Chapter 3 talks about the cut-based technology mapping and its drawbacks. Chapter 4 explains the Negation-Permutation-Negation (NPN) class representation and functional symmetry along with the proposed modification. Chapter 5 presents the proposed cut-based design and automation methodology. Chapter 6 describes the proposed cut-less design and automation methodology. Chapter 7 concludes the discussion with the future scope of work.

## Chapter 2

# And-Inverter Graph (AIG) and Shannon Factor Graph (SFG)

#### 2.1 And-Inverter Graph (AIG)

AIGs were introduced by Kuehlmann and Krohm for combinational equivalence checking [16]. There are several data structures used for representation of the subject graph, which is technology independent one used for mapping to the technology dependent standard cells. Here the subject graph is represented as AIG for proposed cut-based methodology.

#### 2.1.1 Definition

Let (X, A),  $A \le X \times X$ , be a directed acyclic graph where each node  $n \in X$  has either no incoming arcs or exactly two incoming arc, are called Inputs. Nodes with two incoming arcs are called 'And' nodes. Let inv be a function from A to the set  $\{0, 1\}$ . The tuple G = (X, A, inv) is called an And Inverter Graph (AIG). If inv(a) = 1 then arc a is said to be inverted. Inverted arcs indicated with a bubble on solid line, and uninverted arcs with a solid line (see Fig. 2.1).

Figure 2.1: AIG graph

Every node and edge in an AIG corresponds to a Boolean function, called the function of the node or edge. Every Input node n of an AIG is associated with a formal Boolean variable Xn. The functions of the other nodes and edges are defined in terms of these Boolean variables.

Formally, the semantics of an AIG G is specified by defining a valuation function f that maps every node and edge of G to a Boolean function. If e is the edge (n, i), we define

$$f(e) = \begin{cases} f(n) & \text{if } i = 0 \\ -f(n) & \text{if } i = 1 \end{cases}$$

If n is a node, we define

$$If(n) = \begin{cases} 0 & \text{if } n \text{ is the zero node} \\ X_n & \text{if } n \text{ is an input mode} \\ f(e_l).f(e_r) & \text{otherwise } (n \text{ is an And node with input edges } e_l \text{ and } e_r) \end{cases}$$

This recursive definition of f is well-formed since the nodes in an AIG can be topologically ordered (as it is a directed acyclic graph). An AIG G that has exactly one node n with no out-going arcs is called a single output AIG. In this case we often abuse terminology and talk of the function of G. This should be understood to be the function of n.

#### 2.1.2 AIG construction

AIGs for Boolean functions can be constructed starting from different functional representation [17]

**SOP:** Given an SOP representation of a function, it can be factored [18] and the factored form can be converted into the AIGs. Each two-input OR-gate is converted into a two-input AND-gate using the DeMorgan rule.

**Circuit:** Given a circuit representation of a (multi-output) Boolean function, the (multi-output) AIG is constructed in a bottom-up fashion, by calling a recursive construction procedure for each PO of the circuit. When called for a PI node, the procedure returns the elementary AIG variable. Otherwise, it first calls itself for the fanins of a node and then builds the AIG for the node using the factored form of the node. When an AIG is constructed from a circuit, the number of AIG nodes does not exceed the number of literals in the factored forms.

When the AIG is constructed from a BDD, the number of AIG nodes does not exceed three times the BDD number since each MUX can be represented using three ANDs. It follows that the size of the AIG is proportional to the size of the circuit or BDD.

Quantifications performed on AIGs have an exponential complexity in the number of quantified variables because quantifying each variable is done by ORing the cofactors and can potentially duplicate the graph size. Except for quantification, Boolean computation is more robust with AIGs than with BDDs. This is because Boolean operations on AIGs lead to the resulting graphs whose size is bounded by the sum of the sizes of their arguments, while in the case of BDDs the worst case complexity of the result is equal to the product of the sizes of the arguments.

#### 2.2 Functionally Reduced AIGs (FRAIGs) [17]

FRAIGs are "semi-canonical" because no two nodes in a FRAIG structure have the same function in terms of the primary inputs, but the same function may have different FRAIGs structures.

**Canonicity:** A representation of a Boolean function is canonical if, for any function, the representation is unique.

AIGs are not canonical, that is, the same function can be represented by two functionally equivalent AIGs with different structure. Although in general it is computationally expensive to remove redundancies in an AIG (detecting if two nodes compute the same function is Co-NP Complete), in practical implementations some easily detected redundancies are prohibited by enforcing the following conditions:

**Structural Hashing:** There is at most only one And node with a given pair of edges as inputs (since two nodes with same inputs compute the same function).

**Redundant And Elimination:** There is no And node with both inputs the same.

**Constant Zero Elimination:** There is no And node with an edge and its complement (since it computes the same function as the Zero node).

**Constant Zero Propagation:** There is no And node with the Zero edge as an input (since it computes the same function as the Zero node).

**Constant One Propagation:** There is no And node with the One edge as an input (since it computes the same function as the other input).

We abuse terminology and refer to these conditions collectively as structural hashing conditions. An AIG that satisfies these conditions is said to be structurally hashed. We generally assume that an AIG is structurally hashed.

The aforementioned AIG based subject graph can be used for cut-based technology mapping, but, when it comes to the cut-less technology mapping the AIGs give inferior results [19]. However, there were attempts to minimize the number of cuts [20] to reduce the complexity and memory requirement (will be discussed in chapter 4).

We propose a new graph data structure for representing the subject graph called, Shannon Factor Graph (SFG), to facilitate the cut-less technology mapping, which is equally applicable to LUT-based and standard cell based mapping.

#### **2.3** Shannon Decomposition Theorem [21]

A Shannon Decomposition is a method to represent any Boolean function as the sum of two sub-functions of the original function. A cofactor is a sub element of a Shannon decomposition generated by setting the value of a given variable to either "0" or "1". A cofactor, which is generated for a function F by setting a variable xi to 0 is called the negative cofactor of the function F with respect to xi, otherwise it is called positive cofactor (setting to "1"). A cube-cofactor is obtained by setting more than one variable to "0" and/or "1", i.e a cube-factor is a cofactor from a cofactor. Equation (1) shows the mathematical representation of Shannon decomposition theorem.

$$F(x0, x1, x2, ..., xi) = x0 * F(1, x1, x2, ..., xi) + x0' * F(0, x1, x2, ..., xi)------(1)$$

Where \* and ' represent the AND and NOT functions respectively. For an example, the negative cofactor of the function  $F(x0, x1, x2, x3) = x0*(x1+x2) + x3$  with respect to  $x0$  is  $x3$ , whereas the cube-cofactor with respect to  $x0(=0)$  and  $x3(=1)$  is 1.

#### 2.4 Brief Introduction to Binary Decision (BDD)

For BDD construction, we can start with the truth-table (2n values) or with more compact representations, like Boolean expression. In the case of Boolean expressions, a top-down procedure can be used to derive the diagram by repeated applications of the classical Shannon decomposition formula (1).

Consider a 5-variable function, G=x1\*(x0\*x2+x2\*x4) + x4\*(x0\*x1+x1\*x3).

We begin by setting x0=0 in G (without considering the proper variable ordering for BDD size reduction) to obtain the function G0, which must be realized below the x0=0 branch. We then do for x0=1 to obtain the function G1. Similarly the procedure should be repeated until the Shannon cofactor values are constant "1" or "0". The size of the BDD and construction time increases exponentially with the number of variables and converting them to a canonical representation is again an exponential complex problem. The other problem with the BDDs is, its structure does not represent the final target graph. So to overcome the problems associated with the AIG and BDD representation we come up with a new graph representation, whose construction is more like a BDD. More details on BDD can be found in [22-26]

#### 2.5 Proposed Shannon Factor Graph (SFG) [15]

The nodes of the SFG represent the Cofactors or cube cofactors value and the level, which will be used as node ID for finding the appropriate cell in the pre-computed library, and edges represent the connecting wires among the nodes. Unlike Binary Decision Diagrams (BDD) [22-26] and AIG [6, 27], the structure of the SFG helps in eliminating the cut-

enumeration and pruning, computation of truth-tables and Negation-permutation-Negation (NPN) class representatives [11, 28] for each cut. We propose two different algorithms for SFG construction, which can be used for cut-less mapping, to improve the runtime, graph size and required memory. Thereby it improves the runtime and reduces the required memory drastically.

We found that, computation of constant zero and one, non-decomposed, and shared nodes (explained in next section) is critical in minimizing the runtime and graph size for complex circuits. By considering the nature of nodes while constructing the graph makes the SFG semi-canonical, because the nodes at each level of the SFG will have uniquely represented nodes. The proposed SFG construction algorithm (algorithm 2) computes the constant one and zero, non-decomposed and shared nodes on-the-fly, thereby it improves the overall size of the graph, which in turn reduces the final area and building time.

#### 2.5.1 Non-decomposed, constant one, constant zero and shared nodes

Non-decomposed, constant one and zero, and shared nodes represent the nature of SFG nodes. A non-decomposed node is the node which has similar node(s) in the SFG, which have the same cofactor or cube cofactor value and level. Non-decomposed nodes improve the logic sharing, minimize the graph size and final area. If the building time of a non-decomposed is  $t_b$  and the number of non-decomposed nodes in the SFG is L, then the building time and graph size will be reduced by a factor (L-1)\* $t_b$  and L-1 respectively. A node which receives two constant zeros (ones) is called constant zero (one) node, i.e. the constant zero (one) node will have all zeros (ones) in its corresponding truth-table. If there are no constant zeros or ones as input to the node, then the node represents function of a typical Shannon cofactor (two AND gates, one inverter and one OR gate), otherwise the node represents an AND gate or AND gate followed by an OR gate. If the two primary outputs have the nodes, which have the same functionality and level, then those nodes are called shared nodes. Shared nodes minimize the size of the SFG.

#### 2.5.2 Construction of proposed SFG

The proposed SFG can be built with and without considering the nature of nodes.

#### 2.5.2.1 SFG construction without considering the nature of nodes

Algorithm 1 shows the pseudo code for the SFG construction without considering the non-decomposed, constant one and zero, and shared nodes. The input to the SFG construction algorithm is truth-table and input size of the largest cells (MaxCellSize) available in the library. Using the equation (1) the Shannon cofactors and cube cofactors of the given truth-tables will be computed by successively dividing the truth-table.

Consider the 4- input truth-table given in the Fig. 2.2 The variables will be selected depending the order they appear in the truth-table. For calculating the Shannon cofactors of the variable X3, the truth-table will be partitioned into two equal. The first half values in the output (F0) represent the negative cofactor F00 and the remaining half represent the positive cofactor F01. Now each half (F00 and F01) will be decomposed, which is nothing but finding the cofactor of the cofactor (cube cofactor). First half of the F00 is the cube cofactor F000 of the function F0, when the variables X3=0 and X2=0.

Figure 2.2: Shannon Cofactor and cube cofactor computation by successively decomposing the Truth-table.

This process continues till the cofactors/cube cofactors of all variables are calculated. Decimal values of the computed Shannon cofactors/ cube cofactors and their levels (number of primary input variables that are in the fan-in cone of a node) will be used as the node IDs. Table 2.1 helps to classify the nodes and to determine the leaf value (carries the bottom node value to the node from which it is decomposed). Column I represents the positive/negative cofactor value of the node (leaves), the Column II and III determine the leaf value when the number of primary inputs are more than two and equal to two respectively.

Table 2.1 Determining the Values of the Leaves of the Node

| Cofactor value (binary) | Leaf value (n>2) | Leaf value (n=2) |

|-------------------------|------------------|------------------|

| All zeros               | Constant zero    | Constant zero    |

| All ones                | Constant one     | Constant one     |

| 01                      | -                | a' (literal)     |

| 10                      | -                | a (literal)      |

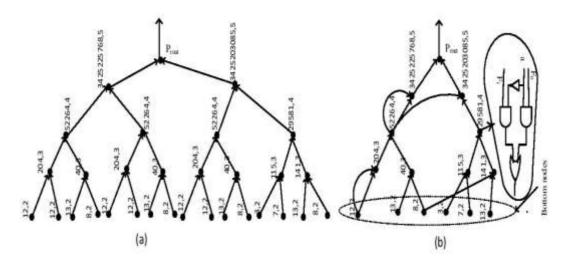

Since the size of the truth-table grows exponentially with the number of variables, Boolean expressions are taken as input for the large functions (number of variables >16). In case of Boolean expressions, cofactors/cube cofactors are computed by substituting 0/1 in place of the selected variable (s). Then, Boolean expression of the cofactors and cube cofactors are used as the node IDs, which will be used for mapping and finding the nature of nodes (whether nodes are receiving constant one or zero, non-decomposed nodes and shared nodes) [15]. The SFG has embedded intelligence, it considers the input size of the precomputed library cells and constructs the graph till the number of inputs to the bottom nodes of the graph is equal to the input size of the pre-computed library cells. Once the whole SFG is constructed IDs of the nodes, except for bottom nodes, will be deleted to free up the memory (explained in detail in next section). Unlike the Binary Decision Diagrams (BDD), the proposed SFG contains fewer nodes (see Table 2.2) and requires less graph building time due to its on-the-fly size reduction [15] and its structure reflects the final target graph, which is technology dependent. Fig. 2.3 (a) shows the basic structure of the SFG, without considering the nature of nodes, for an arbitrary 6-input Boolean function F.

SFG construction algorithm takes the advantage of the size of the library cells during graph construction to improve the graph size and runtime. The SFG is constructed to a level that the bottom most nodes of the SFG will have a level of MaxCellSize. This is because of the fact that the nodes which receive inputs from MaxCellSize number of primary input variables can be mapped with the library cells whose size is not less than MaxCellSize. For an instance, if F is a 10-input Boolean function and MaxCellSize is 4, then the bottom most nodes of SFG of the Boolean function F will have a level of 4, i.e. only 6-variables are considered for the Shannon decomposition. Since bottom most nodes have a level 4, they can be mapped directly with the 4-input library cells. In this way, by considering the size of the library cells, the SFG construction algorithm reduces the graph size and improves the graph building time. The SFG constructed using the algorithm 2.1 is not canonical, because it has nodes which are redundant. In order to make the SFG semi-canonical, there should not

be any constant one and zero, shared and non-decomposed nodes. The proposed algorithm 2.2 takes this into consideration and makes the SFG semi-canonical.

# Algorithm 2.1 SFG Construction without considering the non-decomposed, constant one and zero, and shared nodes

```

1: int Truth2ShannonFactorGraph(truthtable, MaxCellSize)

2: {

3: int j,f, numvar, truthlength;

4: tempTruth=truthtable;

5: truthlength=length of the tempTruth;

6: numvar=log2(truthlength);

7: compute the decimal value of tempTruth save in f;

8: for j=1 to numvar-MaxCellSize

9: {

10: compute the Shannon cofactors and cube cofactors by successively dividing the tempTruth;

11: compute the decimal values of the cofactors and cube-cofactors and save in f;

12: }

13: return f;

14: }

```

#### 2.5.2.2 SFG construction-considering the nature of nodes

Algorithm 2.2 shows the pseudo code for the SFG construction and computing the non-decomposed, constant one and zero, and shared nodes on-the-fly. It considers the size of the library cells and nature of nodes to minimize the graph building time and size. Fig. 3.3 (b) shows the basic structure of the SFG, with considering the nature of nodes, for an arbitrary 6-input Boolean function F. At every level, the value of Shannon cofactors or cube cofactors are checked to find the non-decomposed, constant one and zero nodes before proceeding to the next phase of decomposition. The cofactor or cube cofactor values of the nodes having the same level will be compared, then the nodes which are having the same cofactor or cube cofactor value in their truth-table (output decimal value) are classified as non-decomposed nodes and only one out of all non-decomposed nodes will be considered for the next phase of Shannon decomposition. If there are m number of non-decomposed nodes, then only one out of 'm' will be considered for the decomposition and the remaining 'm-1' will be implemented from the decomposed node. So, there is no need to spend time to decompose all 'm' non-decomposed nodes, which is runtime overhead. As the number of non-decomposed nodes increases, the graph building time and size decrease.

Figure 2.3: Basic structure of the Shannon Factor Graph (SFG), assuming that size of the largest cells in the pre-computed library is 2 (MaxCellSize) (a) without considering the nature of nodes and (b) considering the nature of nodes of a 6-input Boolean function F.

The constant one and zero nodes are found by identifying the nodes whose cofactors have all zeros or ones in their truth-table or corresponding decimal value. Once the constant one or zero nodes are found, they are no more considered for the Shannon decomposition and will be used to simplify their parent nodes. Even if the constant one or zero nodes are decomposed, the resulting nodes (children) will also be constant one or zero nodes. So considering the constant one or zero nodes for decomposition is redundant, runtime overhead and increases the graph size. The shared nodes among the primary outputs are determined by comparing the nodes of one primary output with the other primary output. If there are any shared nodes, only one of them will be considered for the Shannon decomposition and remaining nodes will be implemented from the decomposed node. From the Fig. 2.3 it is clear that, the size of the SFG can be minimized significantly even for small functions by identifying the nature of nodes on-the-fly (from 31 to 15) and experimental results show that, the reduction in SFG size is more prominent for bigger functions.

#### 2.5.2.3 SFG construction for multiple outputs

Generally the functionally equivalent nodes (Non-decomposed nodes), Non-Shannon nodes in the DAG will be calculated after constructing the graph, which is a runtime overhead. However, finding the functionally equivalent/non-decomposed nodes on-the-fly at every level of the SFG construction can reduce the graph building time and memory significantly. Algorithm 1 & 2 shows the pseudo code for constructing the proposed SFG for single output functions and finding the non-decomposed nodes and constant one or zero nodes on-the-fly and it is generalized for multi-output functions, which is presented in algorithm 2.3. The

# Algorithm 2.2 SFG construction and computation of non-decomposed, constant one and zero nodes on-the-fly

```

1: graphconstruct(int truth_table, int MaxCellSize)

2: {

3: num_previousCubecofactor ←1

4: number_of_variables=log2(length(truth_table);

5: temp_truthtable=truth_table;

6: temTruth=truth table;

7: for i = 2 to num_of_variables-MaxCellSize+1

8: {

9: if all Cube_cofactors are constant one/zeros

10: Break;

11: for j = 1 to num_previousCubecofactor

13: ShannonCofactor(i,k)=temp truthtable(1:end/2);

14: k=k+1;

15: ShannonCofactor(i,k)=temp truthtable((end/2+1):end);

16: k=k+1;

17: }

18: num previousCubecofactor ← number of co-factors in the Shannon Cofactor for i

19: Compare all the Cubecofactors and remove non-decomposed nodes and Constant one or

zero Nodes

20: }

21:}

```

nodes which have the same level will be compared to find the non-decomposed nodes. Similarly, the constant one and zero node will be computed based on their cofactor value. If a node has all zeros (ones) then it will be considered as constant zero (one) node. The constant one or zero nodes being found during the SFG construction, will not be decomposed further and these nodes will be used for simplifying the functionality of the parent node. A node which receives only one constant node represents an OR-gate and a node which receive the constant one and constant zero represents the primary input variable. Similarly a node receiving only one constant zero represents the AND gate. For common cofactors (non-decomposed nodes), which are having the same truth-table (output decimal value), only one of them will be decomposed and the remaining nodes will be implemented from the cube cofactors of the decomposed node. Computation of non-decomposed nodes

#### Algorithm 2.3 Algorithm for Multi-output functions to find Shared nodes

```

1: t←number of primary outputs

2: for j=1 to t

3: {

4: read truth_table(j);

5: Temp_truth=truth_truth(j);

6: graphconstruct(Temp_truth);

7: Multi_Cofactor(t)=ShannonCofactor;

8: }

9: for i=1 to t-1

10: for k=i + 1 to t {

11: out1=Multi_Cofactor(i);

12: out2=Multi_Cofactor(k);

13: compare cofactor of out1 and out2

14: if common nodes are there, keep one and make all NULL

15: }

```

will take O(M) time, where M is the number of nodes in the SFG decomposition at a particular level.

For multi-output functions, the Shannon cofactors will be computed for each primary output. Then the cofactors and cube cofactors of each primary output will be compared with the cofactors and cube cofactors of the remaining primary outputs having the same level (lines 9-14 of the algorithm 2.3). If there are any shared nodes, which are having the truth-table will be grouped and only one from each group will be implemented. This will reduce the graph size, memory and improves the final circuit area, but the delay will remain the same. Algorithm 2.3 will take O(mn) time to find out the shared nodes, where m and n represent the number of primary outputs and the number of cofactors at each level of graph for each primary output.

#### 2.5.2.4 Comparison of the algorithms 2.1 & 2.2

We extensively verified the proposed algorithms for SFG construction with the standard benchmark circuits [29,30]. The proposed algorithms are implemented in MATLAB running on a Xeon processor (3.4GHZ, 4GB RAM) operating in Linux-based environment. The benchmark circuits taken from [30] (circuits 10-14 in Table I), which are PLA format, converted into truth-tables manually and using the Simple-Solver [31]. Benchmark circuits taken from [29] (circuits 1-9 in Table I), which are in verilog format, converted into

Boolean equations using the ABC tool [32], then truth-tables are harvested from the Boolean equations.

Table 2.2 shows the variation of graph size and runtime (graph building time) of the SFG with and without considering the non-decomposed, constant one and zero, and shared nodes. Column 1 represents the standard benchmark circuit name. Column 2 shows the number of primary inputs and outputs of the benchmark circuit. Column 4 and 5 represent the time taken to build the SFG and number of nodes of the SFG (graph size) without considering the nature of the nodes (non-decomposed, constant one and zero, and shared) respectively. Column 6 and 7 gives the graph size and time taken to build the SFG, considering the nature of nodes.

We considered 3-input library cells, so the SFG is decomposed to a level where the bottom most nodes will have a level of 3. The size of the SFG graph increases drastically, when the non-decomposed, constant one (zero) and shared nodes are not considered in constructing the SFG. This is because, these nodes will also be considered for the Shannon decomposition, which augments the graph building time and size of the SFG. Since the non-decomposed nodes will have a representative node, which will be considered for the decomposition, all these nodes can be implemented from the decomposed node assuming that there is no fan-out limitation on a node. Thus, by considering only one representative for m nodes can improve the runtime and graph size significantly.

Assume that there are m sets of non-decomposed nodes, each set has n nodes (level and decimal values of the cofactors are same) and td is the time required to decompose each node. Now each set can be implemented ('n-1' nodes) from a single node, which is considered for the Shannon decomposition. So the total time taken to decompose the nodes will be m\*td, which saves O(m\*n) ((n-1)\*m\*td) time and reduces the graph size of similar amount. Same is applicable for shared nodes case also. Non-decomposed nodes represent the nodes within a primary output, whereas shared nodes represent among the primary outputs.

If any constant one or zero nodes are found during the SFG construction at any level, then those nodes will not be considered for the decomposition to minimize the graph building time and size of the SFG. The Shannon decomposition of constant one or zero nodes (parent) results in constant one or zero (children), which are redundant to consider for the further decomposition. Constant one and zero nodes reduce the size and graph building time of the SFG drastically compared to the non-decomposed and shared nodes. Column 8 shows the runtime ration with and without considering the nature of nodes. At an average non-decomposed, constant one and zero, and shared nodes minimize the runtime by a factor 5.5

(for few circuits it is around 100). But the interesting observation is for few circuits, the runtime ratio is 1, this is due to the presence of the constant one or zero and non-decomposed nodes near the bottom most nodes which increases the runtime. Similarly for

Table 2.2 Comparison of Runtime and Graph Sizes of the Proposed SFG With and Without Considering nature of nodes

| S. | Circuit                 | No. of         | SFG without NCS |                       | SFG with NCS    |                       | Speed         | Reduction                |

|----|-------------------------|----------------|-----------------|-----------------------|-----------------|-----------------------|---------------|--------------------------|

| No | name                    | inputs/outputs | Runtime<br>(R1) | Graph<br>Size<br>(S1) | Runtime<br>(R2) | Graph<br>Size<br>(S2) | up<br>(R1/R2) | in Graph<br>size (S1/S2) |

| 1  | cm138                   | 6/9            | 0.013           | 135                   | 0.005           | 27                    | 2.6           | 5                        |

| 2  | cmb                     | 16/4           | 0.58            | 65532                 | 0.039           | 85                    | 15.2          | 770                      |

| 3  | cm163a                  | 16/5           | 0.72            | 81915                 | 0.12            | 131                   | 6.2           | 625                      |

| 4  | cm162a                  | 14/5           | 0.17            | 20475                 | 0.077           | 96                    | 106           | 193                      |

| 5  | cm152a                  | 11/1           | 0.007           | 511                   | 0.006           | 88                    | 1.2           | 5.8                      |

| 6  | alu2                    | 10/6           | 0.011           | 1536                  | 0.01            | 271                   | 1.1           | 5.7                      |

| 7  | cm151a                  | 12/2           | 0.02            | 2046                  | 0.02            | 118                   | 1             | 17                       |

| 8  | ex4                     | 6/9            | 0.02            | 135                   | 0.0083          | 101                   | 2.2           | 1.4                      |

| 9  | ex1                     | 9/19           | 0.64            | 2413                  | 0.11            | 376                   | 5.7           | 6.4                      |

| 10 | max46                   | 9/1            | 0.002           | 127                   | 0.003           | 72                    | 0.67          | 1.8                      |

| 11 | 7-bit<br>even<br>parity | 7/1            | 5.7e-4          | 31                    | 5.2e-4          | 5                     | 1.12          | 6.2                      |

| 12 | mux4                    | 6/1            | 3.7e-4          | 15                    | 3.1e-4          | 9                     | 1.2           | 1.67                     |

| 13 | majority                | 5/1            | 2.4e-4          | 7                     | 2e-4            | 6                     | 1.2           | 1.2                      |

| 14 | 4gt13                   | 4/1            | 2.4e-4          | 3                     | 2.4e-4          | 3                     | 1             | 1                        |

|    | Total                   |                | ~2.2            | 174881                | ~0.4            | 1388                  |               |                          |

few circuits the variation in the graph size (circuits 8, 11-14) is minimum, this is because of the input size of the benchmark circuits is almost equal to the size of the library cells. At an average, considering the constant one and zero, shared, non-decomposed nodes during graph construction reduces the size of the SFG by a factor of 126 (for a few circuits it is around 700). So, by finding the nature of nodes on-the-fly makes the SFG semi-canonical, which in turn minimizes the graph size and runtime.

#### 2.5.3 Comparison of SFG with AIG and BDD

To verify the superiority of the proposed SFG, We compared with AIG and BDD using the standard benchmark circuits [29], taken from the different publicly available benchmarks. First, the Boolean equations of the benchmark circuits were computed using the ABC tool [32], then the truth-tables of each Boolean equations were harvested using a simple

program. For the sequential circuits, only the combinational part of the logic is taken by cutting at the register edges.

Table 2. 3 shows the comparison of SFG with AIG and BDD in terms of graph size and variation of graph size and runtime for different variable sizes of the library circuits . Column I represents the benchmark circuit name, column II and column III show the graph size for AIG and BDD for different circuits respectively, computed using the ABC tool [32]. Column IV represents the SFG size and runtime for different values of m. In column IV, m represents the input size of the cells stored in the pre-computed library. The value m=0 signifies that the construction algorithm does not consider the variable size of the

Table 2.3 Comparison of the Proposed SFG with AIGI and BDD in Terms of Graph Size and Variation of Graph Size and Runtime for Different MaxCellSizes

| Circuit name | BDD size | AIG size | Proposed Shannon Factor Graph size |                   |       |                   |       |                   |       |                    |

|--------------|----------|----------|------------------------------------|-------------------|-------|-------------------|-------|-------------------|-------|--------------------|

|              |          |          | m=0                                | Runtime           | m=3   | Runtime           | m=4   | Runtime           | m=6   | Runtime            |

| alu2         | 923      | 547      | 270                                | 0.001             | 263   | $0.89e^{-3}$      | 227   | $0.79e^{-3}$      | 87    | $0.32e^{-3}$       |

| alu4         | 5059     | 1023     | 843                                | 0.008             | 802   | 0.006             | 741   | 0.002             | 670   | 0.001              |

| bigkey       | 4548     | 6805     | 5409                               | 0.06              | 5020  | 0.06              | 4571  | 0.04              | 4302  | 0.03               |

| b9           | 204      | 139      | 127                                | 0.031             | 120   | 0.024             | 94    | 0.018             | 76    | 0.012              |

| c8           | 255      | 312      | 291                                | 78e <sup>-6</sup> | 214   | 71e <sup>-6</sup> | 201   | 60e <sup>-6</sup> | 180   | 52e <sup>-</sup> 6 |

| c499         | 368      | 414      | 320                                | 0.003             | 301   | 0.0026            | 273   | 0.002             | 241   | 0.002              |

| c880         | 640      | 383      | 263                                | 0.008             | 241   | 0.006             | 210   | 0.003             | 185   | 0.001              |

| cm150        | 54       | 76       | 61                                 | 0.009             | 53    | 0.007             | 47    | 0.006             | 43    | 0.004              |

| cm151        | 26       | 36       | 27                                 | 0.01              | 23    | 0.008             | 18    | 0.008             | 13    | 0.007              |

| cm162        | 58       | 55       | 60                                 | 0.009             | 43    | 0.008             | 28    | 0.006             | 22    | 0.006              |

| cm163        | 53       | 53       | 61                                 | 0.006             | 58    | 0.006             | 38    | 0.004             | -     | -                  |

| ex1          | 485      | 412      | 491                                | 0.02              | 436   | 0.016             | 421   | 0.012             | 383   | 0.009              |

| ex2          | 245      | 205      | 92                                 | 0.01              | 76    | 0.005             | 55    | 0.004             | -     | -                  |

| ex3          | 105      | 81       | 72                                 | 0.01              | 55    | 0.004             | 37    | 0.003             | -     | -                  |

| ex4          | 130      | 101      | 92                                 | 0.017             | 83    | 0.01              | 42    | 0.0029            | -     | -                  |

| ex5          | 104      | 82       | 52                                 | 0.016             | 40    | 0.012             | 26    | 0.008             | -     | -                  |

| Cu           | 83       | 60       | 26                                 | 0.01              | 16    | 0.01              | 10    | -                 | -     | -                  |

| Total        | 25343    | 17644    | 14070                              | 0.358             | 12824 | 0.301             | 11441 | 0.203             | 10104 | 0.157              |

pre-computed library cells while building the SFG (or assumes that there is no information available about the variable size of pre-computed library cells). Even without considering the size of the pre-computed library cells, the size of the proposed SFG is significantly less than the AIG and BDD. The reduction in the graph size simplifies the mapping problem and decreases the runtime and the required memory size. The graph size and runtime can be further minimized by considering input variable size of the pre-computed library cells. As the value of 'm' increases, then the depth to which the Boolean function to be decomposed will be reduced. This is because the cube cofactor(s) which has 'm' variables after decomposing the function with respect to 'n-m' number of variables (where n represents the number of variables of the function) can be mapped with the m-input pre-computed library cells. The algorithm finds out the common nodes at every level before decomposing it further, which helps in improving the graph building time. The average number of nodes of the proposed SFG is 74% and 150% less than AIG and BDD respectively.

In general the size of the AIG is less than the BDD, but for a few circuits (6 out of 22) BDD has fewer nodes than the AIG. However, for such cases also size of the proposed SFG is smaller than the AIG (except for ex1 circuit), but slightly higher than the BDD. This is due to the less number of non-decomposed nodes in the SFG of the circuits and we did not consider simplification of nodes while calculating the number of nodes.

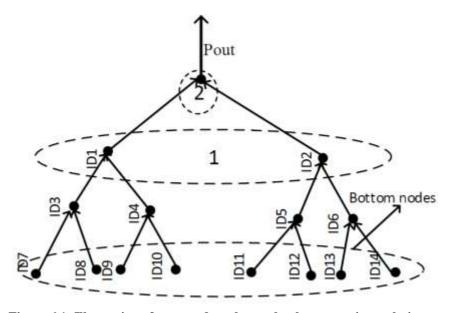

#### 2.6 SFG for Cut-less Technology Mapping

The unique representation of the nodes of SFG facilitates the cut-less technology mapping. The mapping of the SFG to the library cells starts from the bottom most nodes. The decimal value and level of the bottom nodes of the SFG will be compared with the output decimal value and size of the library cells to find the appropriate match for each node. Once the bottom nodes are mapped with the library cells, then the level of the graph will be reordered to get the actual level of each node. Now, the nodes above the bottom most nodes are selected based on the multiplexers size that are presented in the library. Every node of the SFG will have hidden variable which can be used as selection line of the multiplexer. Therefore, once the bottom most nodes are mapped with the library cells, the remaining nodes are mapped with the appropriate library cells (multiplexers) in a bottom-up fashion. Mapping continues till all nodes in the each primary output are covered. The detailed discussion is postponed to chapter 6.

## Chapter 3

# **Cut-based Technology Mapping**

#### 3.1 Cut-computation

Given an AIG, the first step of matching is to enumerate cuts of size k or less, called k-feasible cuts, in G. Intuitively, a k-feasible cut corresponds to a single output subnetwork of G (with k inputs) which may be implemented by a gate or a LUT in the mapped network. For LUT-based FPGA mapping, cut enumeration is the only step for matching: each k-feasible cut can be implemented by a k-LUT. For standard cells, more work is needed to determine if a cut can be implemented by a library gate. This is discussed in Chapter 5. In this chapter, we discuss the complete flow involved in the cut-based technology mapping

#### 3.1.1 k-feasible cut

Let n be a node in an AIG. A feasible cut of a node n in the AIG is a set of nodes {xi} in the transitive fan-in cone of n such that an arbitrary assignment of values to xi completely determines the value of n. A feasible cut is redundant if the value of a node in the cut is completely determined by an assignment of values to the other nodes in the cut. A k-feasible cut is a feasible cut of size at most k that is not redundant. The cut composed of node n alone is always a k-feasible cut of node n (for any k>1) and is called the trivial cut.

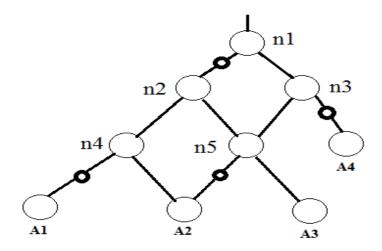

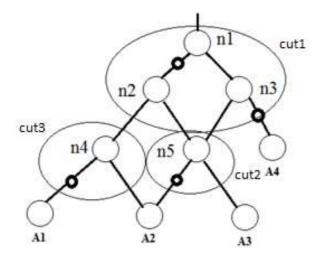

**Example 3.1**: The Fig. 3.1 illustrates the k-feasible cuts of an AIG. A1-A4 are primary input nodes. The 3-feasible cuts for n1 are {n1}, {n2, n3}, {n2, n5, A4}, {n4, n5, n3}, {n4, n5, A4}.

#### **3.2** Technology Mapping [6]

We have used Boolean matching for technology mapping. The input to the mapping procedure is an And-Inverter graph (AIG) [27]. An AIG is a DAG whose nodes represent either AND gates or primary inputs (PIs). Its edges represent wires. Inverters are represented by bubbles on the edges. Given an AIG, the mapping is done in 5 steps.

Figure 3.1: Illustration of K-feasible cuts of an AIG graph

**Step 1. Compute k-feasible cuts:** A feasible cut of a node N in the AIG is a set of nodes  $\{Xi\}$  in the transitive fan-in cone of N such that an arbitrary assignment of values to Xi completely determines the value of N. A feasible cut is redundant if the value of a node in the cut is completely determined by an assignment of values to the other nodes in the cut. A k-feasible cut is a feasible cut of size at most k that is not redundant. The cut  $\{N\}$  is always a k-feasible cut of node N (for any k) and is called the trivial cut. Let P(N) denote the set of k-feasible cuts of node N. If N is a PI, then  $P(N) = \{\{N\}\}$ . If N is a AND node with children A and B, then

$P(N) = \{ \{N\} \} U \{ u U v | u E P(A), v E P(B), |u U v | \le k \}$

We compute all 5-feasible cuts of every node in the network by the simple bottom-up traversal based on the above recursion. Although in general a graph may have O(n<sup>5</sup>) 5-feasible cuts, we found that most test-cases have between 20 and 30 5-feasible cuts per node. We restrict our attention to 5-feasible cuts since our experiments show that the total number of cuts increases very quickly with k. Pruning techniques have to be applied, and the mapping results are not significantly better (since the pruning is quite arbitrary).

**Step 2. Compute truth-tables of cuts:** The next step is to compute the local function of a node in terms of its cut. This is done for every non-trivial k-feasible cut of every node in the network. Given a node N, and a cut {Xi} of that node, formal variables are assigned to the each cut node (in no particular order). Using these variables, the functionality of the node is computed symbolically. Since usually only 5-feasible cuts are considered, this symbolic function computation can be performed efficiently using 32-bit integers to represent the truth-tables. In what follows we use the words "function" and "truth-table" interchangeably.

**Step 3. Boolean Matching:** For each node in the network, for every cut, an appropriate gate (if one exists) is chosen from the library. Each gate thus chosen is called a match for the node. Our matching procedure uses the traditional approach, which is based on NPN class representation (detailed in Chapter 4)

**Step 4. Compute best arrival time at each node:** Starting from the PIs and working in topological order towards the outputs, the best arrival time is computed for each node from amongst all its matches.

**Step 5. Choose the best cover:** In the reverse topological order, the best gate for each primary output is chosen. Next, the best gates implementing the inputs of these gates are chosen and so on until all primary inputs have been reached.

#### 3.3 Drawbacks of the Cut-based Technology Mapping

Computation of all cuts is typically a run-time and memory bottleneck [36]. Even though there are efficient algorithms to compute the cuts [36-39], the number of cuts increases exponentially with the cut size (number of leaves) and the number of nodes. So, the time to compute the cuts and finding the best cut among them increases exponentially with the cut size, for example if the size of the cut is k and the number of nodes in the AIG is n, then the number of possible cuts will be  $O(n^K)$ . In [19], a new technique has been proposed to reduce the number of cuts to be enumerated. However, still the cut computation is required. We will address this problem by proposing a cut-less technology mapping technique in chapter 6.

## **Chapter 4**

# Negation-Permutation-Negation (NPN) Classes and Functional Symmetry

#### 4.1 Negation-Permutation (NPN) Class [11]

The design of digital circuits involves a deep understanding of the concept of Boolean Functions. There are many operations usually applied in the digital circuit synthesis process. Many of these operations depend on the search space under consideration. This is the case of the matching phase performed during technology mapping [33], where a function (or only part of it) to be implemented is matched against cells from a library. NPN class representation provides a solution for reducing the search space.

For a given number of input variables, say n, there are 2^(2^n) well-defined number of functions. Each n variable function has 2^n possible minterms, resulting in a truth table with 2^n lines. This is shown in Table 4.1 for the case of 2-input Boolean functions. The 2^n possible minterms, or lines of the truth table, give the number of bits in each column of the truth table. This way, the output columns of the truth tables characterize a given Boolean function as a binary number of 2^n bits. As there are 2^(2^n) numbers of 2^n bits, there are 2^(2^n) possible different functions of n inputs. This is also shown in Table 4.1 for the case of 2- input functions.

AB  $f_1$  $f_3$  $f_4$ f<sub>5</sub>  $f_6$ f7  $f_{12}$ f<sub>14</sub> **f**15 fo  $f_2$ f8 **f**9 f10  $f_{11}$  $f_{13}$

Table 4.1 All the 16 Different 2-input Functions

Table 4.2 shows the number of n-input functions for n varying from 2 to 4. We can see that for the case of 4-input functions the search space is almost intractable if many operations need to be repeated.

Table 4.2 Possible Number of Functions for 2, 3, 4 and n -Inputs

| Number of inputs | Number of functions |

|------------------|---------------------|

| 2                | 16                  |

| 3                | 256                 |

| 4                | 65536               |

| n                | 2^(2^n)             |

The n-input functions can be classified into different classes (set of functions) in order to reduce the search space. The number of functions is the first number to be considered in the classification of the set of n-input functions. Other two numbers that could be used in the classification of n-input functions are the numbers of P and NPN equivalence classes. As it will be discussed later, P classes group functions that are equivalent under input permutation while NPN classes group functions that are equivalent under input negation/permutation as well as output negation.

The functional equivalence can be verified using the Binary Decision Diagrams (BDDs) [23] or by manipulating the truth-tables. BDDs are the most used form to represent Boolean functions in Electronic Design Automation. There are many specific kinds of BDDs, depending on its use. Reduced Ordered Binary Decision Diagrams (ROBDDs) are commonly used to compare Boolean functions using the ROBDD strong canonical form (unique representation) presented in [24].

We use the truth-table based verification for checking the functional equivalence. The canonical form of the functions will be computed by manipulating the truth-table by using the Shannon decomposition theorem [21]. This canonical form is necessary to verify the equivalence of the functions and group them into a common equivalence class.

#### **4.1.1** Implementations of n-input functions

Table 4.3 shows the gate implementations of all the 2-input functions.

Table 4.3 Implementations for All the 16 Different 2-input Functions

| pr.                              |                                                       |                 |

|----------------------------------|-------------------------------------------------------|-----------------|

| $f_0 =$                          | 0                                                     | ndm -           |

| $f_0 = f_1 = f_1$                | $\overline{A}$ . $\overline{B}$                       | <b>=</b> D-     |

| $f_2 =$                          | Ā . B                                                 | <b>=D</b> -     |

| $f_{\scriptscriptstyle \beta} =$ | Ā                                                     | -b>-            |

| $f_{4} =$                        | $A \cdot \overline{B}$                                | <b>⊅</b> -      |

| $f_5 =$                          | $\overline{\mathrm{B}}$                               | - <b>D</b> o-   |

| $f_6 =$                          | A⊕ B                                                  | ⇒D-             |

| $f_7 =$                          | A . B                                                 | ₽               |

| $f_8 =$                          | A . B                                                 | <del>-</del> D- |

| $f_9 =$                          | A⊕B                                                   | ⇒⊳              |

| $f_{10} =$                       | В                                                     | in_             |

| $f_{II} =$                       | $\overline{A \cdot \overline{B}}$                     | <b>⊅</b>        |

| $f_{12} =$                       | A                                                     | i <u>n</u>      |

|                                  | <del>A</del> . B                                      | <b>⇒</b>        |

| $f_{l4} =$                       | $\overline{\overline{A}}$ . $\overline{\overline{B}}$ | \$>             |

| r                                | 1                                                     | <u>r_</u>       |

|                                  |                                                       |                 |

#### 4.1.2 Concept of P class

The fact that many different 2-input functions may have the same gate-level implementations naturally introduces the concept of P equivalence. P equivalence between 2 functions is obtained when it is possible to achieve identical values for both truth table outputs by permuting the function inputs. Functions that are P equivalent can be grouped into P classes Table 4.4 shows all the 12 different P classes of 2-input functions. It is important to note that despite the existence of 16 different 2-input functions, there are only 12 different 2-input P classes. The circuits used to implement each P class are also shown in Table 4.4. Four P classes are composed by 2 functions, while eight P classes are composed by only one function. The most important property of P equivalent functions is that they can always be implemented with the same circuit (or cell from a library). Therefore, it is

possible to implement any of the 2-input functions with a single cell from a library composed of one gate implementation for each P class.

Table 4.4 The 12 Different 2-input P Classes

| $f_o$                                                   | alla .            |

|---------------------------------------------------------|-------------------|

| $egin{array}{c} f_o \ f_I \end{array}$                  | ₩-                |

| $f_2$ $f_4$                                             | ±₽-               |

|                                                         | ->>-              |

| $f_3$ $f_5$ $f_6$                                       | ⇒D-               |

| $f_{7}$                                                 | $\forall$         |

| $f_8$                                                   | ₽                 |

| $f_{g}$                                                 | ⇒D≻               |

| $f_{\scriptscriptstyle 10}$ $f_{\scriptscriptstyle 12}$ | i <u>n</u>        |

| $f_{_{II}}$ $f_{_{I3}}$                                 | $\Leftrightarrow$ |

| $f_{{}_{I4}}$                                           | ⇔                 |

| $f_{I5}$                                                | Ľ                 |

#### 4.1.3 The Concept of NPN class

From Fig. 4.5, it is possible to see that even P classes may have similar implementations. For instance, functions  $f_1$ ,  $f_2$ ,  $f_4$ ,  $f_7$ ,  $f_8$ ,  $f_{11}$ ,  $f_{13}$  and  $f_{14}$  have gate implementations based on a single nand gate plus some inverters. These functions may be grouped into a NPN equivalence class. NPN equivalence between 2 functions is obtained when it is possible to achieve identical values for both truth table outputs by permutation and/or negation of the function inputs and/or negation of the function output. Figure 4 shows all the 4 different NPN classes of 2-input functions, one NPN class per line. It is important to note that despite the existence of 16 different 2-input functions, there are only 4 different 2-input NPN classes. There are 2 NPN classes composed of 2 functions, one NPN class composed of 4 functions, and one NPN class composed of 8 functions. NPN equivalent functions can be

implemented with the same circuit plus some inverters (used in the negation operations for the inputs and the output, if necessary). This way, it is possible to use a smaller library composed of one representative gate for each NPN class plus one inverter cell.

Table 4.5 The 4 Different 2-input NPN Classes

| $f_{\scriptscriptstyle 0}$ | F                          | $f_{l}$ | 5 Y                        |          |       |   |         |           |             |          |   |          |   |

|----------------------------|----------------------------|---------|----------------------------|----------|-------|---|---------|-----------|-------------|----------|---|----------|---|

| $f_{_{I}}$                 | <b>=</b> D-                | $f_2$   | $f_{\scriptscriptstyle 4}$ | ₽        | $f_7$ | ⊅ | $f_{s}$ | $\forall$ | $f_{_{II}}$ | $f_{13}$ | ⊅ | $f_{l4}$ | ⊅ |

| $f_{_{\mathcal{J}}}$       | $f_{\scriptscriptstyle 5}$ | ->      | $f_{l0}$                   | $f_{l2}$ | in    |   |         |           | 1.1         |          |   |          |   |

| $f_{\epsilon}$             | <b>⇒</b> D-                | $f_{g}$ | ⇒                          |          |       |   |         |           |             |          |   |          |   |

This approach is especially useful when the cost of the inverter is very low. The NPN classes are also called semi-canonical representation.

#### 4.1.4 NPN semi-canonical algorithm

The input to our NPN semi-canonical algorithm is truth-table. The number of 1s in the output bit stream of the truth-table is taken into consideration. The output phase is decided in such a way that the expression has lesser number of 1's. In case of a tie, the phase which results a lesser value of the decimal equivalent of the truth-table is considered.

The polarity of each variable is determined by considering the number of 1s in the Shannon cofactors of the function with respect to that variable. The negative cofactor is required to contain fewer 1s than the positive cofactor to keep the phase intact, otherwise the phase will be inverted. In case of a tie, the phase which results a lesser value of the decimal equivalent of the truth-table is considered.

The ordering of variables is determined using the number of 1s in the cofactors with respect to each variable. For this, we require that variables were ordered in the increasing order of the number of 1s in the negative cofactor. If any two variables have same number of 1s in the negative cofactor, then swap is done if swapping results in lower value of decimal equivalent of the truth-table. The pseudo code of the implemented algorithm is presented in algorithm 4.1.

#### 4.2 Canonical Representation-Functional Symmetry

The NPN classes are not completely canonical representations as they can be further reduced. To make the representation canonical we exploit the functional symmetry along with the NPN classes

#### Algorithm 4.1 Pseudo code for semi-canonizing

```