#### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

Graduate School

5-2020

### A PUF based Lightweight Hardware Security Architecture for IoT

Mesbah Uddin University of Tennessee, muddin6@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

#### **Recommended Citation**

Uddin, Mesbah, "A PUF based Lightweight Hardware Security Architecture for IoT." PhD diss., University of Tennessee, 2020.

https://trace.tennessee.edu/utk\_graddiss/5813

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Mesbah Uddin entitled "A PUF based Lightweight Hardware Security Architecture for IoT." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Engineering.

Garrett Rose, Major Professor

We have read this dissertation and recommend its acceptance:

Nicole McFarlane, Jinyuan Sun, Andy Sarles

Accepted for the Council:

Dixie L. Thompson

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# A PUF based Lightweight Hardware Security Architecture for IoT

A Dissertation Proposal Presented for the Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Mesbah Uddin

May 2020

© by Mesbah Uddin, 2020 All Rights Reserved.

# Dedication

This research is dedicated to my parents who have been supportive in my whole life,  $Md\ Mohi\ Uddin$  and  $Shahina\ Akter$

# Acknowledgments

I would like thank to my Advisor, Dr. Garrett Rose for his immense support throughout my Ph.D. career. He has always given me guidance, encouragement, financial support and has always put his trust in me.

I would like to extend my gratitude to Dr. Nicole McFarlane, Dr. Jinyuan Stella Sun and Dr. Andy Sarles for finding time to serve on my Ph.D. committee. I would also like to thank Dr. Syed Islam for his guidance as a Professor and as a guardian for Bangladeshi students at UT.

I am very grateful to the EECS department and all its staff especially Dana Bryson and Melanie Kelley for helping me in any academic issues. I would also like to thank my lab-mates Md Badruddoja Majumder, Gangotree Chakma, Sherif Amer, Md Musabbir Adnan, Sagarvarma Sayyaparaju, Ryan Weiss, Md Sakib Hasan and all others for their cooperation and friendship.

I am very grateful to my wife, Anika Zaman for always being there for me. I have always had the deepest support and encouragement from my parents, Md Mohi Uddin and Mrs Shahina Akter, my brother Md Meftah Uddin and my sister Maliha Ibnat. I am also grateful for the Bangladesh student community of Knoxville and all its members and the various organizations of UT like International House, RUF International, Bridges International etc. for making my life at Knoxville easier and enjoyable during my Ph.D.

# Abstract

With an increasing number of hand-held electronics, gadgets, and other smart devices, data is present in a large number of platforms, thereby increasing the risk of security, privacy, and safety breach than ever before. Due to the extreme lightweight nature of these devices, commonly referred to as IoT or 'Internet of Things', providing any kind of security is prohibitive due to high overhead associated with any traditional and mathematically robust cryptographic techniques. Therefore, researchers have searched for alternative intuitive solutions for such devices. Hardware security, unlike traditional cryptography, can provide unique device-specific security solutions with little overhead, address vulnerability in hardware and, therefore, are attractive in this domain.

As Moore's law is almost at its end, different emerging devices are being explored more by researchers as they present opportunities to build better application specific devices along with their challenges compared to CMOS technology. In this work, we have proposed emerging nanotechnology based hardware security as a security solution for resource constrained IoT domain. Specifically, we have built two hardware security primitives i.e. physical unclonable function (PUF) and true random number generator (TRNG) and used these components as part of a security protocol proposed in this work as well. Both PUF and TRNG are built from metal oxide memristors, an emerging nanoscale device and are generally lightweight compared to their CMOS counterparts in terms of area, power, and delay. Design challenges associated with designing these hardware security primitives and with memristive devices are properly addressed. Finally, a complete security protocol is proposed where all of these different pieces come together to provide a practical, robust, and device-specific security for resource-limited IoT systems.

# Table of Contents

| 1 | Intr | oducti | ion                                                    | 1  |

|---|------|--------|--------------------------------------------------------|----|

|   | 1.1  | Motiva | ation                                                  | 1  |

|   | 1.2  | Resear | rch Goal and Summary                                   | 2  |

|   | 1.3  | Origin | al Contributions                                       | 2  |

|   | 1.4  | Disser | tation Overview                                        | 3  |

| 2 | Bac  | kgrour | $\operatorname{ad}$                                    | 5  |

|   | 2.1  | Intern | et of Things (IoT)                                     | 5  |

|   | 2.2  | Emerg  | ging Nanoscale Technology: Memristor                   | 7  |

|   |      | 2.2.1  | Emerging Devices                                       | 7  |

|   |      | 2.2.2  | Memristor                                              | 10 |

|   | 2.3  | Hardw  | vare Security as IoT Security                          | 13 |

|   |      | 2.3.1  | Traditional Security: Cryptography                     | 13 |

|   |      | 2.3.2  | Introduction to Hardware Security                      | 15 |

|   |      | 2.3.3  | Physical Unclonable Function (PUF)                     | 15 |

|   |      | 2.3.4  | True Random Number Generator (TRNG)                    | 24 |

| 3 | Des  | ign an | d Analysis of Fundamental Hardware Security Components | 27 |

|   | 3.1  | Memri  | istor Crossbar PUF                                     | 27 |

|   |      | 3.1.1  | Introduction to HfO2 Memristor                         | 27 |

|   |      | 3.1.2  | Environmental Modeling of a HfO2 Memristor             | 28 |

|   |      | 3.1.3  | Working Principle of XbarPUF                           | 32 |

|   |      | 3.1.4  | Clock Frequency and Other Parameter Selection          | 34 |

|   |     | 3.1.5  | Choice of Load Resistance                                        | 35         |

|---|-----|--------|------------------------------------------------------------------|------------|

|   |     | 3.1.6  | Shift Back to Fixed Challenge Scheme                             | 36         |

|   |     | 3.1.7  | Reverse Read Scheme                                              | 38         |

|   |     | 3.1.8  | Sense Amplifier                                                  | 38         |

|   | 3.2 | Specia | lized Peripherals for Memristor based Circuits                   | 39         |

|   |     | 3.2.1  | Current Compliance                                               | 39         |

|   |     | 3.2.2  | Forming Circuitry                                                | 40         |

|   |     | 3.2.3  | Memristor Read-Write-Form Circuitry                              | 41         |

|   |     | 3.2.4  | Sense Amplifier for Memristor Crossbar Circuits                  | 46         |

|   | 3.3 | Design | of Twin Memristor TRNG                                           | 61         |

|   |     | 3.3.1  | Motivation                                                       | 61         |

|   |     | 3.3.2  | Our Design                                                       | 61         |

|   |     | 3.3.3  | Effect of Environmental and Process variation on Existing Single |            |

|   |     |        | Memristor TRNG                                                   | 63         |

|   |     | 3.3.4  | Variation Modeling for Our Designed TRNG                         | 67         |

|   |     | 3.3.5  | Results and Analyses of Designed Twin-Memristor TRNG             | 69         |

|   |     | 3.3.6  | Output Correction                                                | 71         |

| 4 | Des | ign an | d Robustness Analysis of XbarPUF                                 | <b>7</b> 3 |

|   | 4.1 | Design | Analysis of XbarPUF                                              | 73         |

|   |     | 4.1.1  | Noise Margin Analysis                                            | 73         |

|   |     | 4.1.2  | Security Analysis of the XbarPUF                                 | 75         |

|   |     | 4.1.3  | Detailed Reliability Analysis                                    | 79         |

|   |     | 4.1.4  | Performance Overhead Analysis                                    | 82         |

|   |     | 4.1.5  | Overhead analysis for Other Memristors                           | 83         |

|   |     | 4.1.6  | On-Chip Design                                                   | 87         |

|   | 4.2 | Robus  | tness Analysis Against ML (Machine Learning) based Attacks       | 87         |

|   |     | 4.2.1  | Development of High Level Behavioral Model of Memristor          | 89         |

|   |     | 4.2.2  | Development of High Level Behavioral Model of XbarPUF            | 90         |

|   |     | 4.2.3  | Introduction to Machine Learning Attack Models                   | 91         |

|   |      | 4.2.4        | Experimental Setup                                  | 92  |

|---|------|--------------|-----------------------------------------------------|-----|

|   |      | 4.2.5        | Modeling Attack on an XbarPUF                       | 92  |

|   |      | 4.2.6        | Mitigation of ML Attacks                            | 93  |

|   |      | 4.2.7        | Results and Discussions                             | 94  |

| 5 | Ligl | htweigl      | ht Security for IoT/Embedded System                 | 98  |

|   | 5.1  | Motiva       | ation                                               | 98  |

|   | 5.2  | Securi       | ty vulnerability of IoT processor                   | 99  |

|   | 5.3  | Our S        | ecurity Solution                                    | 99  |

|   | 5.4  | Our S        | ecurity Protocol                                    | 102 |

|   | 5.5  | System       | m Implementation                                    | 107 |

|   |      | 5.5.1        | One Time Pad Implementation                         | 107 |

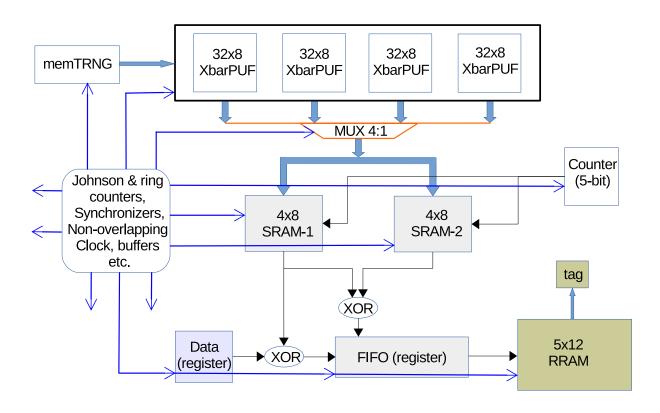

|   |      | 5.5.2        | True Random Number Generator (TRNG)                 | 110 |

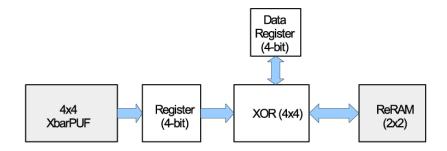

|   |      | 5.5.3        | Redesigned XbarPUF for IoT                          | 110 |

|   |      | 5.5.4        | RRAM for Non-Volatile Storage                       | 111 |

|   |      | 5.5.5        | Time Multiplexing of PUF to Lower Power Consumption | 112 |

|   |      | 5.5.6        | SRAM as Part of Reliability Enhancement Block       | 112 |

|   |      | 5.5.7        | Sneak-Path based Integrity Checking                 | 113 |

|   |      | 5.5.8        | Control Circuit Design                              | 113 |

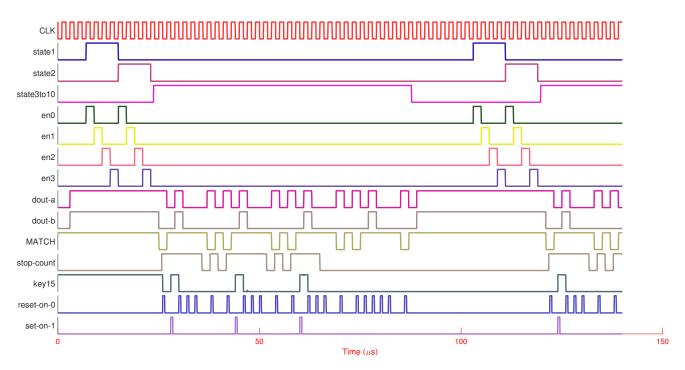

|   | 5.6  | Initial      | Design without Reliability Correction               | 117 |

|   |      | 5.6.1        | Overview                                            | 117 |

|   |      | 5.6.2        | Results for Initial Prototype                       | 118 |

|   | 5.7  | Reliab       | ility Enhancement Technique                         | 120 |

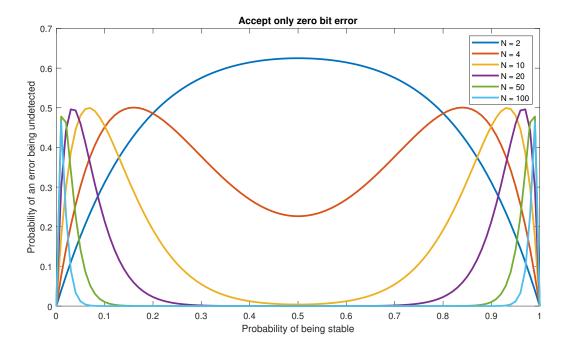

|   |      | 5.7.1        | All-Agree Voting/Veto Technique                     | 120 |

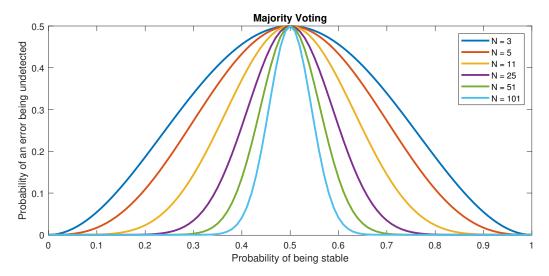

|   |      | 5.7.2        | Majority Voting                                     | 122 |

|   |      | 5.7.3        | Chosen Reliability Enhancement Technique            | 124 |

|   | 5.8  | Worki        | ng Principle                                        | 125 |

|   | 5.9  | Possib       | le Attack Scenarios                                 | 126 |

|   |      | 5.9.1        | Malicious read                                      | 126 |

|   |      | <b>F</b> 0 0 | M. P. J 337 17 .                                    | 107 |

|    |       | 5.9.3   | Readout or Alteration of the PUF Challenge or Secure Tag     | 128 |

|----|-------|---------|--------------------------------------------------------------|-----|

|    |       | 5.9.4   | Modeling Attacks                                             | 129 |

|    | 5.10  | Results | s: PUF Security Analysis                                     | 129 |

|    | 5.11  | Overal  | l Security Evaluation                                        | 134 |

|    |       | 5.11.1  | Malicious Read                                               | 134 |

|    |       | 5.11.2  | Malicious Write                                              | 135 |

|    |       | 5.11.3  | Modeling Attacks                                             | 136 |

|    |       | 5.11.4  | Readout/Alteration of Secure Information                     | 137 |

|    | 5.12  | Overal  | l Performance Analysis                                       | 138 |

| 6  | Con   | clusior | and Future Plan                                              | 144 |

|    | 6.1   | Future  | Works                                                        | 144 |

|    | 6.2   | Summa   | ary                                                          | 145 |

| Bi | bliog | raphy   |                                                              | 147 |

| Aı | ppen  | dices   |                                                              | 158 |

|    | A     | Calcula | ation of Optimal Load Resistance for XbarPUF                 | 159 |

|    | В     | Memri   | stor (HfO <sub>2</sub> ) Model Used in This Work             | 160 |

|    |       | B.1     | Verilog-A Model for $HfO_2$ Memristor:                       | 160 |

|    |       | B.2     | MATLAB Model of a Memristor for Quick Behavioral Simulation: | 169 |

|    | C     | Behavi  | oral XbarPUF Model Used for Response Generation and Power    |     |

|    |       | Calcula | ation                                                        | 171 |

|    | D     | How to  | Perform Tests on the Chip                                    | 179 |

|    |       | D.1     | Setting up the Probepad Connection                           | 179 |

|    |       | D.2     | PSOC Microcontroller and Source Meter to Generate Inputs     | 179 |

|    |       | D.3     | Setting up the Connection with Probepads                     | 182 |

|    |       | D.4     | Performing Simple Functionality Test                         | 182 |

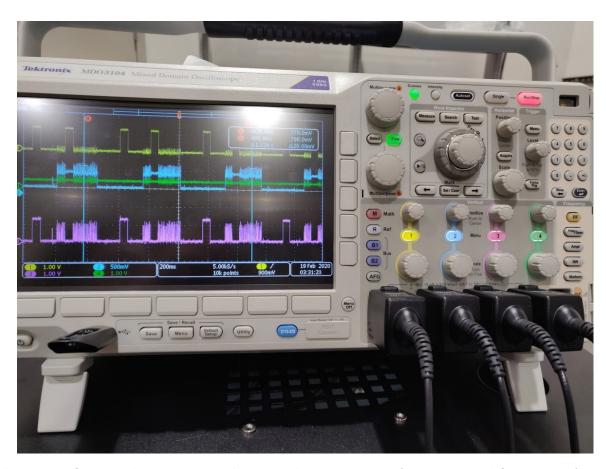

|    |       | D.5     | Oscilloscope to View and Collect the Output                  | 183 |

|    | E     | Probab  | oility of Error with Majority Voting Technique               | 185 |

| Vi | ta    |         |                                                              | 187 |

# List of Tables

| 3.1 | Mean and standard deviation for device level parameters of a $HfO_2$ memristor        |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | considered in this work [69]                                                          | 31 |

| 3.2 | Temperature coefficients for different memristor parameters [69]                      | 31 |

| 3.3 | Comparison of our designed SA with different circuits from different topology         |    |

|     | [73]                                                                                  | 55 |

| 3.4 | Percent yield of our designed SA for different transistor sizes and supply            |    |

|     | voltage [73]                                                                          | 57 |

| 3.5 | Sensing delay $(nS)$ of our designed SA for different transistor sizes and supply     |    |

|     | voltage [73]                                                                          | 57 |

| 3.6 | Energy(Joule) per cycle of our designed SA for different transistor sizes and         |    |

|     | supply voltage [73]                                                                   | 57 |

| 3.7 | Percentage of 0's to the sum of 0's and 1's for different operating conditions [67]   | 71 |

| 4.1 | Impact of 2% variation of load resistance on the security properties of a $32\times2$ |    |

|     | XORed XbarPUF [69]                                                                    | 80 |

| 4.2 | Performance of the XORed XbarPUF with variable temperature ( $10^{o}$ C-              |    |

|     | $100^{o}$ C) and with different cycle-to-cycle variation for the memristor parame-    |    |

|     | ters [69]                                                                             | 80 |

| 4.3 | Power estimation of a $\mathrm{HfO}_x$ memristor based XbarPUF from MATLAB and        |    |

|     | cadence [71]                                                                          | 84 |

| 4.4 | Switching Parameters for Metal-Oxide Memristors [71]                                  | 86 |

| 4.5 | Power Consumption during different phases of a 32×2 XbarPHF [71]                      | 86 |

| 4.6 | Results from modeling attacks on basic XbarPUF (no mitigation) for different     |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | machine learning algorithms                                                      | 93  |

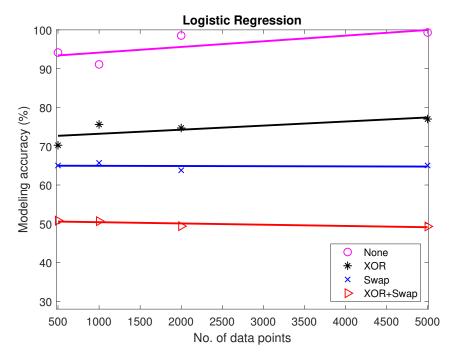

| 4.7 | Column swapping logic implemented in this demonstration [71]                     | 94  |

| 4.8 | Results from modeling attacks after mitigation techniques applied for different  |     |

|     | machine learning algorithms                                                      | 96  |

| 5.1 | Switching Parameters (mean value) for $TiO_x$ Memristors [48]                    | 115 |

| 5.2 | Performance of modified XbarPUF used in this design [74]                         | 119 |

| 5.3 | Overhead in different phases of the system [74]                                  | 120 |

| 5.4 | Security properties of the tag generation method                                 | 135 |

| 5.5 | Results from modeling attacks using different machine learning algorithms        |     |

|     | against TiO <sub>2</sub> memristor based XbarPUF [70]                            | 138 |

| 5.6 | Total area in terms of transistor count for different components of our security |     |

|     | architecture [70]                                                                | 141 |

| 5.7 | Power consumption of the security architecture in different stages (State 1      |     |

|     | and 2 involve a reset of the whole memristor crossbar, 64×64 at once and         |     |

|     | thus have large static current) [70]                                             | 141 |

| 5.8 | Delay overhead of the system in different stages of operation                    | 142 |

| 5.9 | Performance comparison with state-of-the-art lightweight hardware security       |     |

|     | techniques [70]                                                                  | 143 |

# List of Figures

| 2.1 | The Internet of things (IoT) [68]                                             | 6  |

|-----|-------------------------------------------------------------------------------|----|

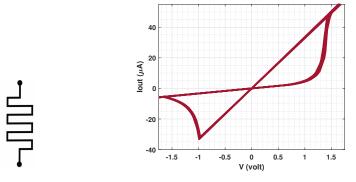

| 2.2 | Memristor symbol (left) and its IV curve showing hysteresis (right)           | 11 |

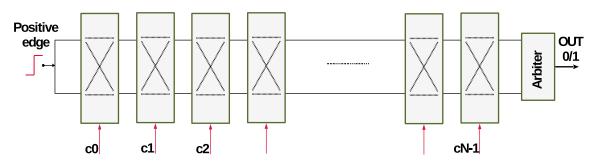

| 2.3 | Arbiter PUF                                                                   | 17 |

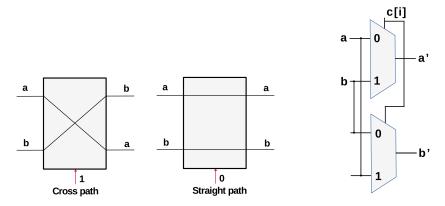

| 2.4 | Two input/two output switch (left two) and its simple implementation with     |    |

|     | two MUXes (right)                                                             | 18 |

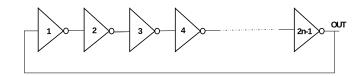

| 2.5 | Ring oscillator: a chain of an odd number of inverters                        | 19 |

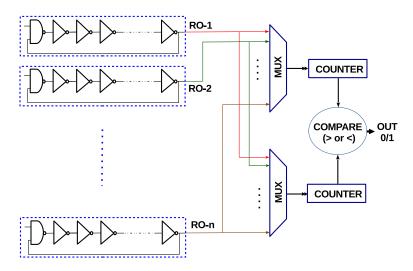

| 2.6 | A ring oscillator PUF                                                         | 19 |

| 2.7 | Standard metrics used for the evaluation of a PUF                             | 21 |

| 2.8 | TRNG sources: clock jitter, noise, metastability                              | 26 |

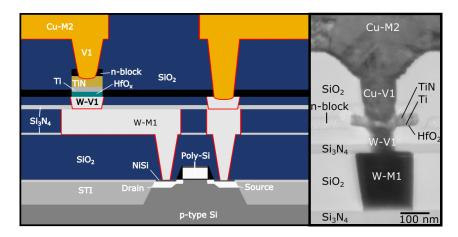

| 3.1 | Illustration (left) and TEM (transmission electron microscopy) image (right)  |    |

|     | of a hafnium-oxide memristor embedded between the M1 and M2 layers.           |    |

|     | In addition, the Illustration depicts a seamless integrated 1 memristor 1     |    |

|     | transistor (1M1T) structure where the transistor acts as the current limiting |    |

|     | device [8, 69]                                                                | 28 |

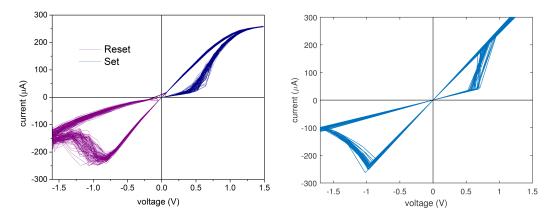

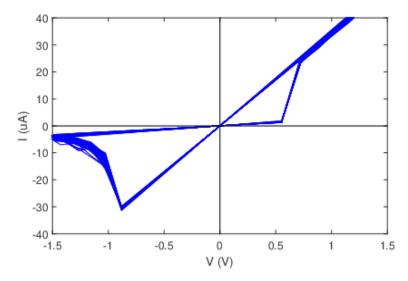

| 3.2 | IV measurements of a memristor (left) and simulated IV characteristics using  |    |

|     | our memristor model (right) [69]                                              | 30 |

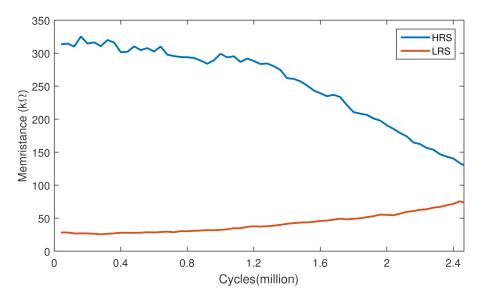

| 3.3 | Simulated effect of (worst case) aging on both HRS and LRS of a memristor     |    |

|     | over time [69]                                                                | 32 |

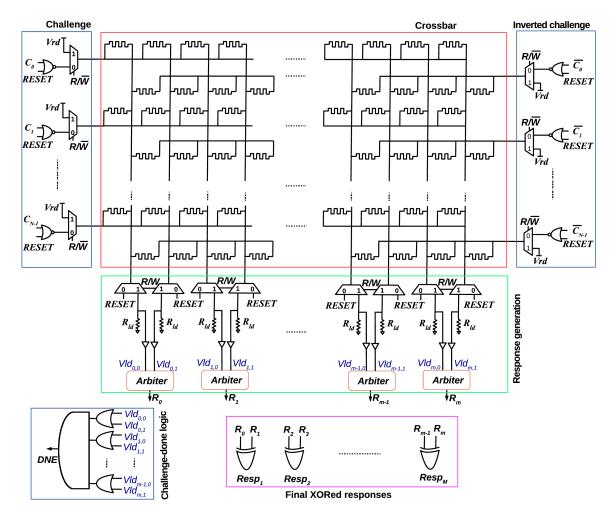

| 3.4 | Schematic of a $N \times M$ XbarPUF circuit (with XORing) [72, 71]            | 33 |

| 3.5 | Two resistance in series, one is the equivalent memristance of a crossbar     |    |

|     | column and another is the load resistance [69]                                | 36 |

| 3.0  | Read-monitored write approach to gradually check memristance of a pair of                      |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | memristors until one finishes switching                                                        | 37 |

| 3.7  | An NMOS transistor with appropriate gate voltage to control the current                        |    |

|      | through a memristor during set                                                                 | 40 |

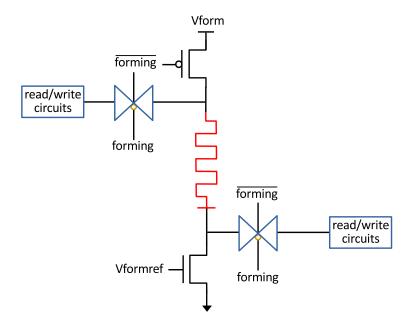

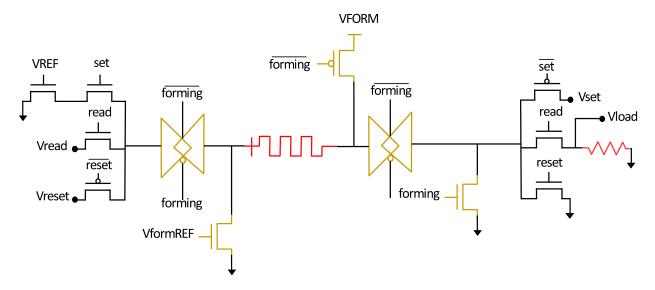

| 3.8  | Forming circuitry of a $HfO_2$ memristor with 65nm CMOS technology                             | 41 |

| 3.9  | Schematic of the the read, write and forming circuitry for the $HfO_2$ memristor               |    |

|      | used in this work                                                                              | 42 |

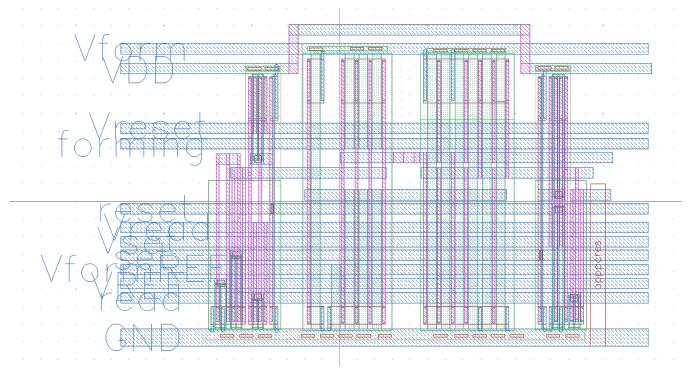

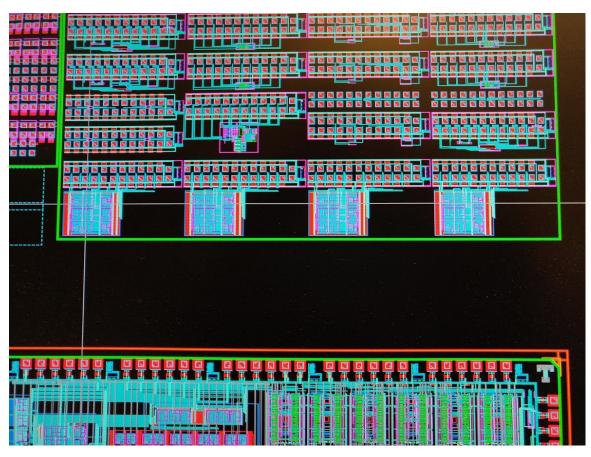

| 3.10 | Layout of the designed read, write and forming circuitry for the ${\rm HfO_2}$                 |    |

|      | memristor $(18.31\mu\text{m} \times 22.60\mu\text{m})$                                         | 43 |

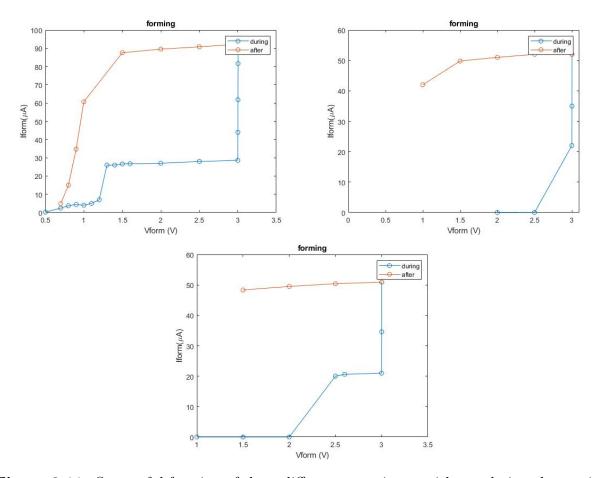

| 3.11 | Successful forming of three different memristors with our designed memristor                   |    |

|      | read-write-form circuitry. The forming can be easily identified by the presence                |    |

|      | of a sudden increase in current in the IV plots. The gate voltage to control                   |    |

|      | the current compliance transistor is also varied to demonstrate forming at                     |    |

|      | different levels which is why there are multiple forming-like spikes in these plots            | 44 |

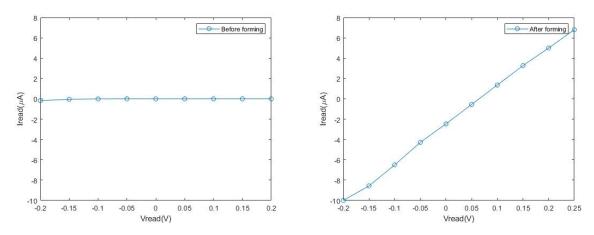

| 3.12 | The current before (left figure) and after forming (right figure) is performed.                |    |

|      | The current is very low ( $\sim$ pA) before forming but was high ( $\sim$ 50-70 $\mu$ A) after |    |

|      | forming                                                                                        | 44 |

| 3.13 | This plot shows a successful reset of a memristor with our read-write-form                     |    |

|      | circuitry. The plot clearly shows how current increases linearly with increasing               |    |

|      | reset voltage voltage i.e. there is no change in memristance or resistance.                    |    |

|      | After when reset voltage (-0.5V) is reached, memristors finally resets to a                    |    |

|      | high resistance where there is a sudden and noticeable drop in current                         | 45 |

| 3.14 | Plot shows the stable current through the memristor when formed using                          |    |

|      | several different current compliance control voltage (Vref). These several                     |    |

|      | different current levels prove the ability to form these memristors at different               |    |

|      | LRS values with confidence                                                                     | 45 |

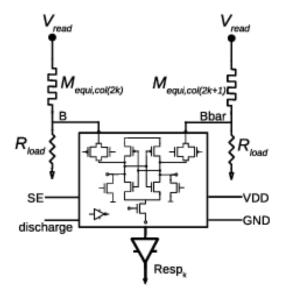

| 3.15 | Schematic diagram of the our designed sense amplifier circuit suitable for                     |    |

|      | memristor based crossbar architectures [73]                                                    | 51 |

| 3.16 | Application of the our designed sense amplifier for the XbarPUF [73]                           | 52 |

| 5.17 | An equivalent input-output circuit for our sense ampliner circuit when used            |    |

|------|----------------------------------------------------------------------------------------|----|

|      | in an XbarPUF [73]                                                                     | 52 |

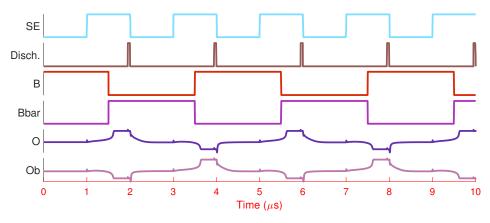

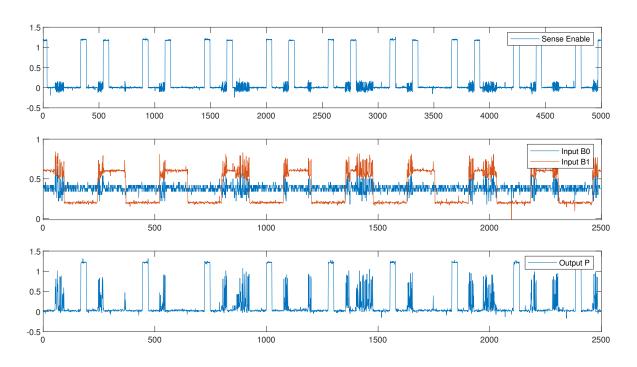

| 3.18 | Waveform for transient simulation of proposed SA for input bit-line voltages           |    |

|      | of 150mV and 155mV with VDD = $0.4V$ [73]                                              | 56 |

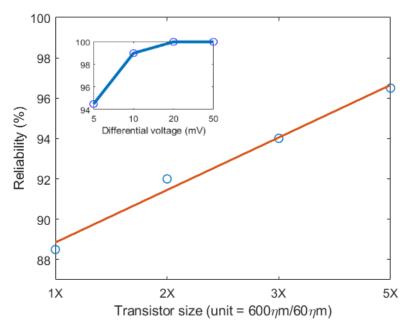

| 3.19 | Reliability across multiple evaluations of our sense amplifier for different           |    |

|      | transistor size and differential voltage                                               | 59 |

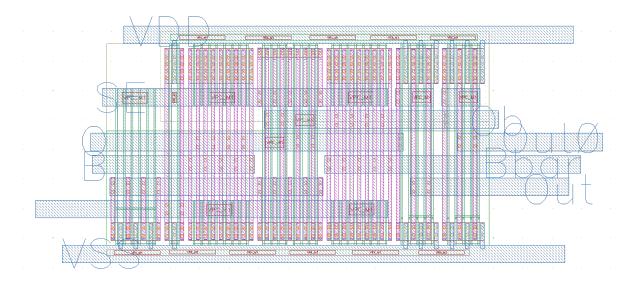

| 3.20 | Layout of the designed sense amplifier $(8.049\mu\text{m}\times13.03\mu\text{m})$      | 60 |

| 3.21 | On-chip test results from our designed sense amplifier                                 | 60 |

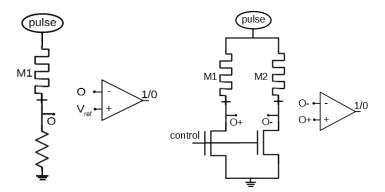

| 3.22 | Conceptual circuit diagram of (left) existing switching time based single              |    |

|      | memristor TRNG [26], and (right) our designed twin memristor TRNG based                |    |

|      | on HRS difference [67]                                                                 | 62 |

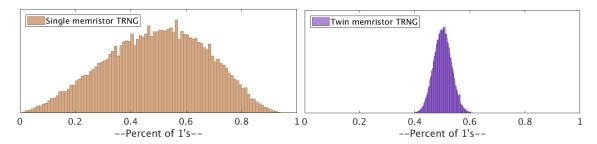

| 3.23 | Histogram of bit bias with process variation for (top) existing single memristor       |    |

|      | design and (bottom) proposed twin memristor design [67]                                | 72 |

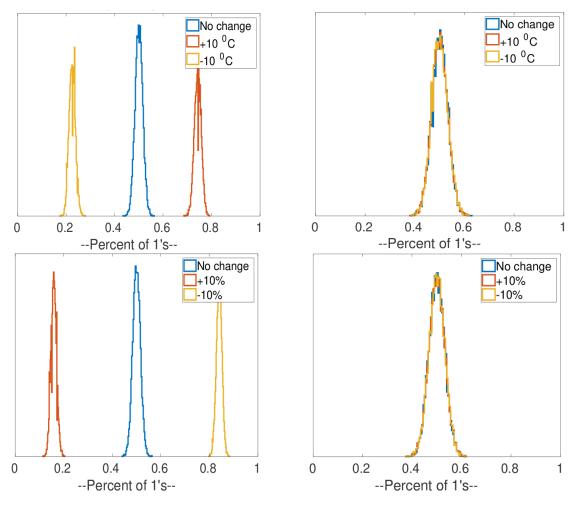

| 3.24 | Histogram plot showing the trend for shift in distribution with temperature            |    |

|      | and voltage variation for both single memristor TRNG (left two figures) and            |    |

|      | our designed twin memristor TRNG (right two figures). Top two figures                  |    |

|      | represent variation due to temperature for single and twin memristor TRNG,             |    |

|      | respectively while bottom two figures are for voltage variation. Existing single       |    |

|      | memristor TRNG displays a large variation while our design almost unchanged            |    |

|      | [67]                                                                                   | 72 |

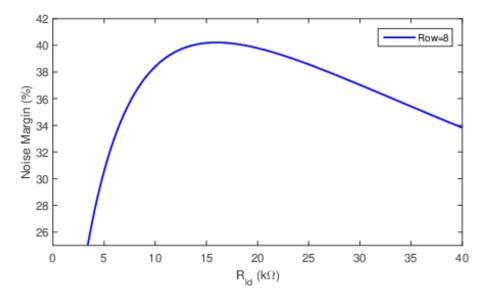

| 4.1  | Relationship between noise margin and the load resistance [69]                         | 74 |

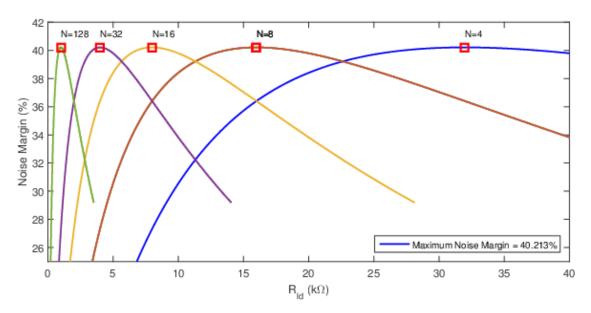

| 4.2  | Relationship between maximum achievable noise margin and the number of                 |    |

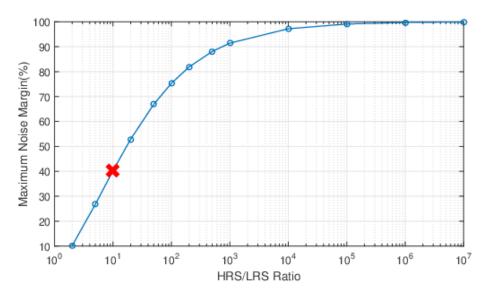

|      | rows (N) [69]                                                                          | 75 |

| 4.3  | Relationship between the maximum achievable noise margin and HRS/LRS                   |    |

|      | ratio [69]                                                                             | 76 |

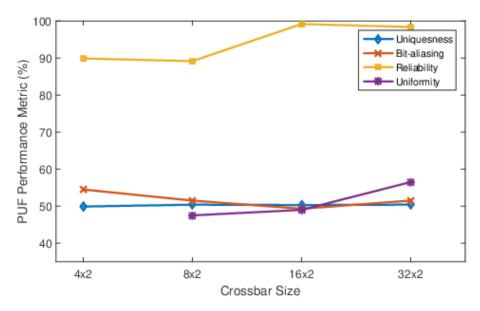

| 4.4  | Security performance of XORed XbarPUF for different crossbar size [69]                 | 77 |

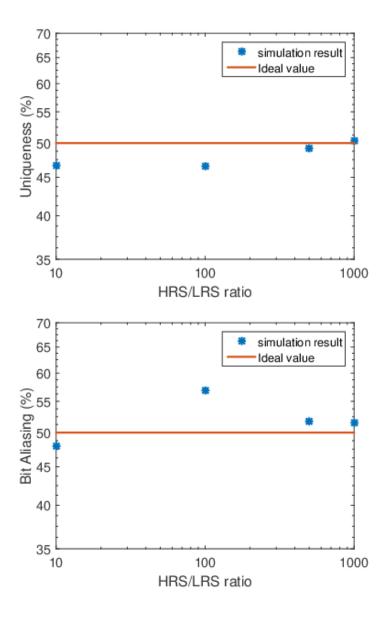

| 4.5  | Dependence of uniqueness (left) and bit-aliasing (right) with HRS/LRS ratio            |    |

|      | and the absolute values of HRS and LRS. The base LRS was $30\mathrm{K}\Omega$ for both |    |

|      | of these plots [69]                                                                    | 78 |

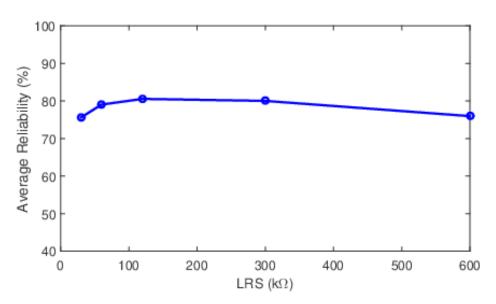

| 4.6  | Reliability of the XbarPUF with respect to increasing LRS [69]                            | 81  |

|------|-------------------------------------------------------------------------------------------|-----|

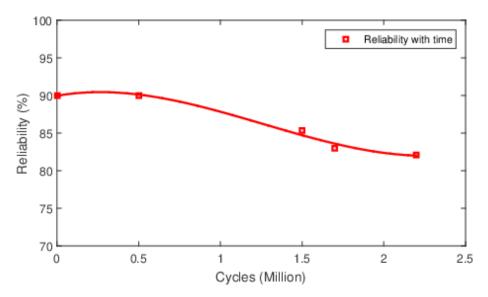

| 4.7  | Reliability of the XbarPUF with age [69]                                                  | 81  |

| 4.8  | Dependence of average power on HRS/LRS ratio and the absolute values of                   |     |

|      | HRS and LRS [69]                                                                          | 83  |

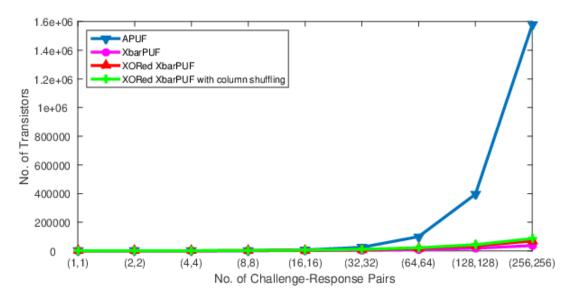

| 4.9  | Area comparison of XbarPUF with Arbiter PUF [69]                                          | 84  |

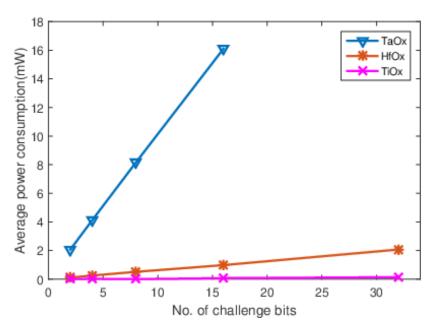

| 4.10 | Relationship between average static power consumption and size of the                     |     |

|      | XbarPUF [71]                                                                              | 87  |

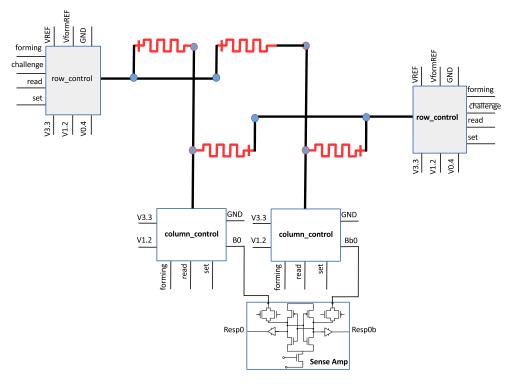

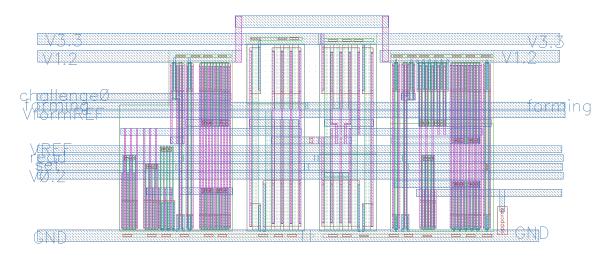

| 4.11 | Schematic of the designed 1-bit memristor crossbar PUF                                    | 88  |

| 4.12 | Layout of the designed 1-bit memristor crossbar PUF (19.59 $\mu m \times 33.63 \mu m)~$ . | 88  |

| 4.13 | Simulated IV characteristics of a metal-oxide ( $HfO_x$ ) memristor for 200               |     |

|      | set/reset cycles for a 100kHz clock. [71]                                                 | 90  |

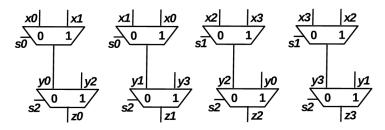

| 4.14 | An implementation of column swapping circuit [71]                                         | 94  |

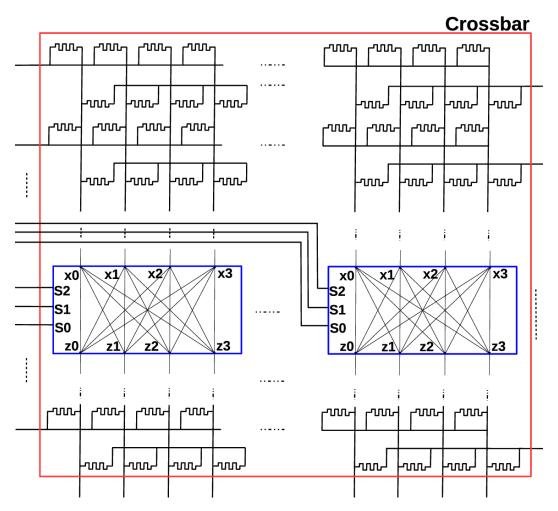

| 4.15 | XbarPUF with the inclusion of column swapping logic [71]                                  | 95  |

| 4.16 | Modeling accuracy of LR vs. the size of dataset [71]                                      | 97  |

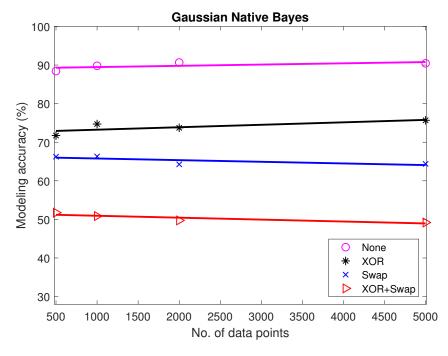

| 4.17 | Modeling accuracy of Gaussian Native Bayes vs. the size of dataset [71]                   | 97  |

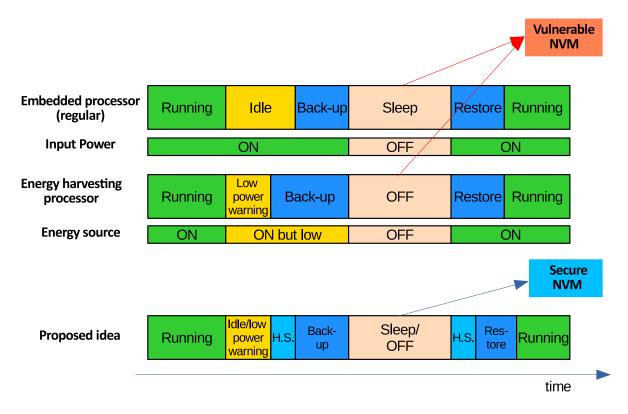

| 5.1  | An embedded processor (either regular or energy harvesting) backs-up data                 |     |

| 0.1  | for data-forwarding but the data left on NVM is unprotected                               | 100 |

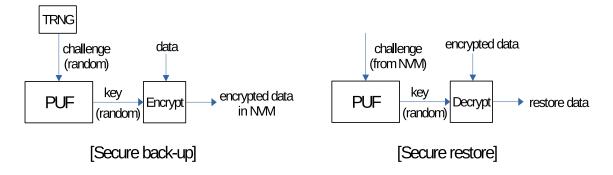

| 5.2  | A unique random challenge is applied to a PUF to generate a cryptographic                 | 100 |

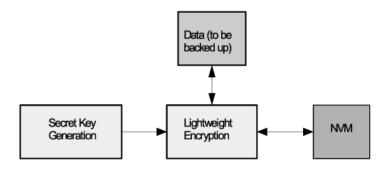

| 0.4  | key for secure back-up and restoration of data in an embedded processor                   | 100 |

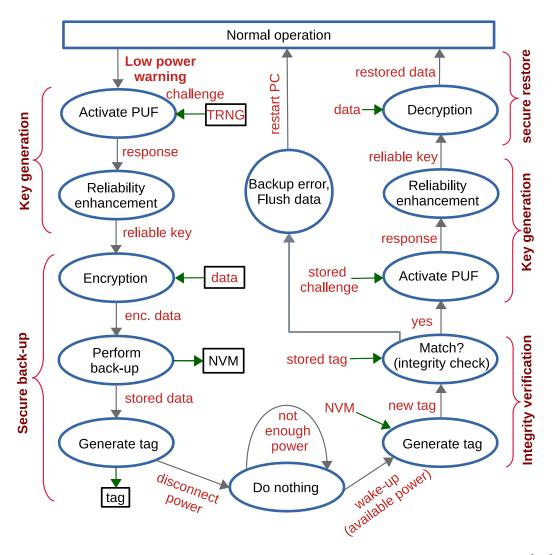

| 5.3  | Control flow graph for our secure back-up and restore protocol [70]                       | 100 |

|      |                                                                                           | 100 |

| 5.4  | System block diagram showing different components of our designed security protocol [70]  | 100 |

| E E  |                                                                                           | 109 |

| 5.5  | High-level conceptual block diagram of the initial security system [74]                   | 118 |

| 5.6  | Block diagram of the initially designed prototype system [74]                             | 118 |

| 5.7  | 'All-agree' reliability enhancement technique for different number of evalua-             |     |

|      | tions for different bit-flip probability. It is more efficient at detecting highly        |     |

|      | unstable bits with increasing number of evaluations [70]                                  | 123 |

| 5.8  | Effectiveness of majority voting for reliability enhancement technique for                |     |

|      | different number of evaluations and with different bit-flip probability [70]              | 124 |

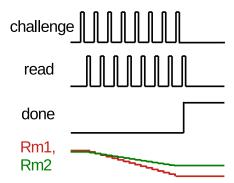

| 5.9      | waveform for a complete secure backup and restore cycle snowing now                    |     |

|----------|----------------------------------------------------------------------------------------|-----|

|          | different states control different operations of the system. Counter keeps track       |     |

|          | of the number of valid or legal key bits and stops each time a bit error occurs        | 127 |

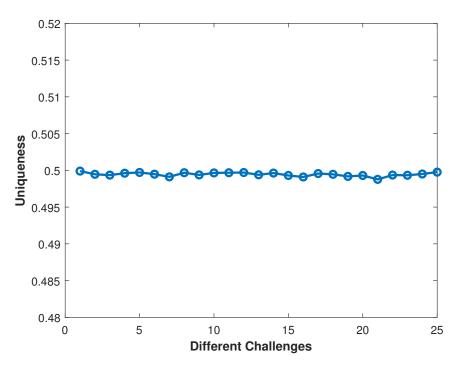

| 5.10     | This figure shows average uniqueness results for 500 different chips [70]. Even        |     |

|          | for different challenges, this value is very close to ideal value of 0.5               | 131 |

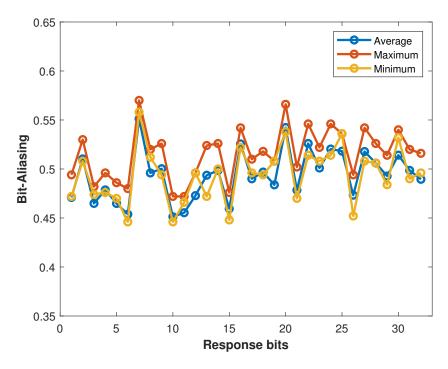

| 5.11     | Summary of results for bit-aliasing for all 32 bits from 500 different chips.          |     |

|          | The minimum and maximum value for each bit are also shown [70]                         | 131 |

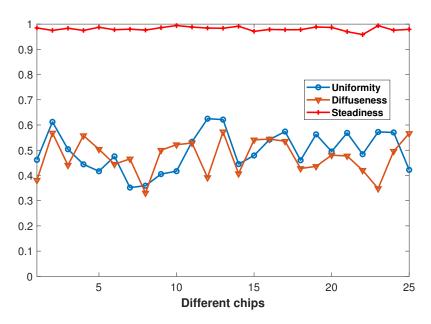

| 5.12     | Summary of results for average uniformity, diffuseness and steadiness from             |     |

|          | 500 different challenges and for 25 different chips [70]                               | 132 |

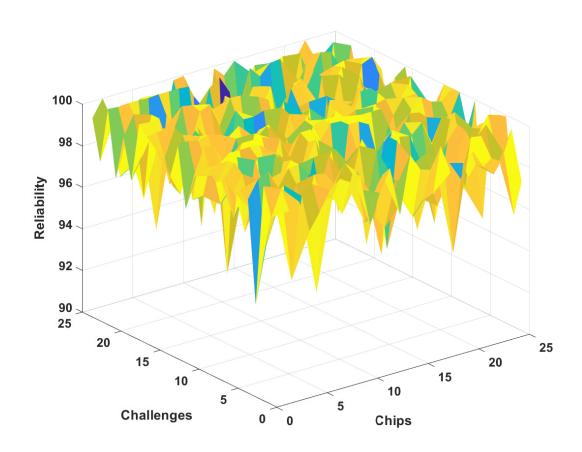

| 5.13     | Detailed reliability results generated from 500 different cycles for 25 different      |     |

|          | chips and 25 different challenges [70]                                                 | 133 |

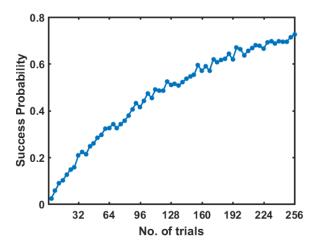

| 5.14     | Probability of success in a spoofing attack with number of trials. The more            |     |

|          | trials an attacker can perform, the higher the chance that the data matches            |     |

|          | the tag. No. of effective trial is 1 in this protocol since the tag is updated on      |     |

|          | each cycle [70]                                                                        | 136 |

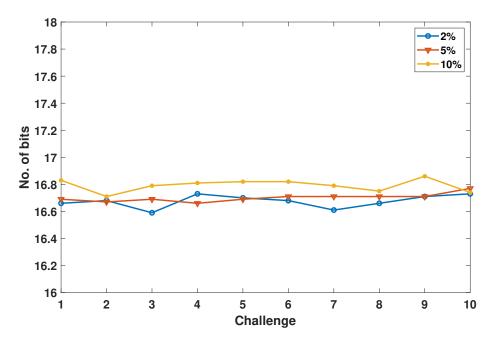

| 5.15     | Figure shows the average number of bits to produce 16 'good' bits from 50              |     |

|          | different chips. The results are generated for three different cycle-to-cycle          |     |

|          | variations and a 50°C temperature change [70]                                          | 139 |

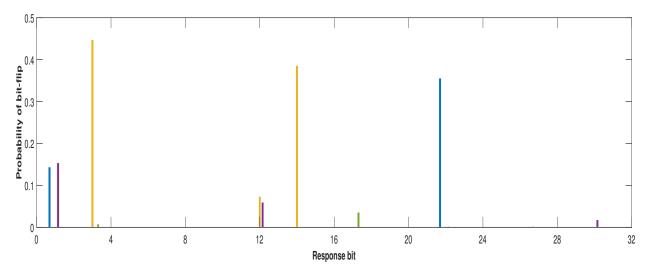

| 5.16     | Probability of bit-flip for a same chip for 10 unique challenges. Plots showing        |     |

|          | the bit-flip probabilities for all 32 bits from a PUF response, evaluated for 500      |     |

|          | cycles. Different challenges cause different bits to flip i.e. there is no single      |     |

|          | set of globally unreliable bit [70]                                                    | 140 |

| 1        | Partial snapshot of the layout of the chip where it contains a $12\times2$ probepad    |     |

| 1        | for the sense amplifier circuit.                                                       | 180 |

| 2        | $12\times2$ probepad connection to a test circuit inside of a probe station, the image | 100 |

| <u> </u> | is taken from a microscopic view                                                       | 181 |

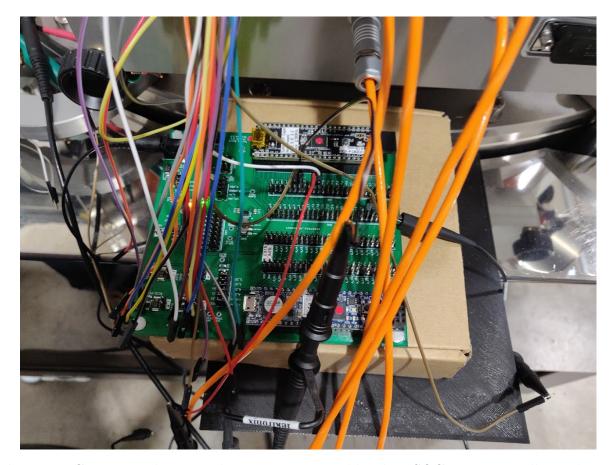

| 3        | Connection between the inputs generated by the PSOC microcontroller and                | 101 |

| J        | wires coming from the probepad                                                         | 183 |

|          | WILES COMING HOME THE DIODEDAG                                                         | 10. |

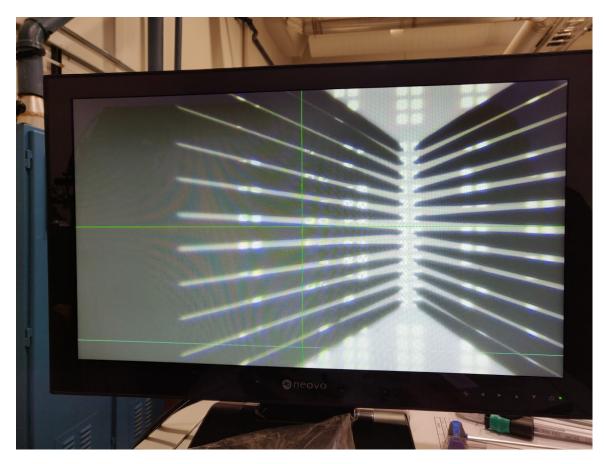

| 4 | Output shown on a oscilloscope during testing of a sense amplifier circuit from |     |

|---|---------------------------------------------------------------------------------|-----|

|   | a fabricated chip                                                               | 184 |

# Chapter 1

# Introduction

### 1.1 Motivation

Traditional cryptography has been providing security solution for decades and are mathematically robust but they introduce a large overhead to a system. For a large system, this overhead may be negligible but with the emergence of smart devices and small embedded systems i.e. Internet of Things (IoT), there is a growing need of providing security for these extremely resource limited systems. As traditional cryptography or software based security is impractical due to their heavy overhead, innovative solution using hardware based security are becoming more and more important. Physical unclonable function (PUF) [53] is a hardware security primitive that has been a highly researched topic in the past 20 years (since 2001). PUF can generate random, unique hardware-specific signatures that can be used in many security applications and thus researchers have proposed hundreds of different PUFs. On the other hand, with Moore's law [50] neared to its end since early 2000s, several new emerging technologies are being explored extensively. Among those, metal-oxide memristors [63] are very promising because of their non-volatility, CMOS integration, low read/write energy, high on-off ratio, usability in both logic and memory circuits. Thus the future is going towards post-CMOS era where these novel nano-devices like memristors would be in use in a lot of electronic designs and hardware based security solutions would be necessary for these billions of smart small devices. Thus there is a growing need for development of hardware security primitives like PUFs using emerging nano-devices like memristors. These novel devices and hardware specific security measures introduce different forms of challenges and thus the research scope is huge in this domain.

### 1.2 Research Goal and Summary

The goal of this work is to develop a very lightweight hardware security architecture for resource constrained IoT domain leveraging the solutions and opportunities provided by emerging nanoscale devices.

The research is specifically focused greatly on the design and analysis of a hardware security primitive called the PUF. The PUF itself is built from memristors. The memristor itself is an emerging nano-device with a high manufacturing variability which is used as the source of entropy for the memristive PUF circuits that we have used in this work. The initial work is focused on improving a practical model of HfO<sub>2</sub> memristor by including environmental effects and aging on its characteristics. Then a detailed device and circuit level parameter exploration based on security and overhead performance of memristive PUF is performed. A machine learning based modeling attack is also implemented on this PUF and further circuit level modification is done to mitigate this vulnerability. Different peripheral circuits, especially memristor's read-write-form circuity and a practical sense amplifier for memristor PUF is also designed. Besides, another hardware security primitive called true random number generator (TRNG) is also designed from memristor and is shown to be robust against environmental changes compared to existing designs. Finally, a complete security architecture is built from memristor based PUF, TRNG, and RRAM (resistive random access memory). Memristor PUF along with our designed reliability enhancement technique is used to provide secret and unique key to a resource-limited embedded or IoT system to provide robust security for its back-up data at the absence or scarcity of power.

### 1.3 Original Contributions

The original contributions of my doctoral work until now are listed below:

- Environmental modeling of HfO<sub>2</sub> memristors, specifically inclusion of temperature change, aging, and also stochasticity in its characteristics

- Security analysis of memristor crossbar PUF against varying device parameters, size and temperature

- Scalability and overhead analysis of memristor crossbar PUF

- Design of abstract model for memristor and memristor crossbar PUF and application of machine learning based modeling attack on PUFs

- Successful demonstration of modeling attack on memristor crossbar PUF and circuit redesign to improve robustness against machine learning based attacks

- Design of a practical sense amplifier for memristor based PUFs and read-write-form circuitry for memristors

- Comprehensive theoretical analysis of memristor based true random number generator (TRNG) and designing an improved twin memristor based TRNG

- Design and analysis of a run-time reliability enhancement technique for memristor crossbar PUF

- A complete security protocol and transistor level architecture design for resourceconstrained IoT or embedded processors

### 1.4 Dissertation Overview

This dissertation is divided into six chapters. Chapter 1 or this chapter provides some context about the research and lists out original contributions of my doctoral work. Chapter 2 provides background on emerging nanoscale devices like memristors, and hardware security primitive like PUF and TRNG. Chapter 3 introduces circuit design works for memristor XbarPUF, different peripheral circuits (e.g. sense amplifier) for XbarPUF, the TRNG and analyzed against manufacturing process variation and environmental changes. Chapter 4 provides a thorough design analysis of XbarPUF and also analyzes its robustness or

vulnerability against machine learning based algorithms along with mitigation techniques against these attacks. Chapter 5 uses all the designed components and knowledge so far to provide a robust and lightweight hardware security protocol and architecture to secure the non-volatile memory of an embedded processor or IoT device. Finally, chapter 6 provides a summary of the works done for this dissertation and future work extensions are discussed.

# Chapter 2

# Background

## 2.1 Internet of Things (IoT)

The internet of things or IoT has been a buzzword for the past few years as the world has seen a rapid growth in this domain. IoT generally refers to embedded devices, sensors etc. which can gather data, send information via a channel or the internet to somewhere else to make a decision based on its gathered data. Smart home appliances, smart medical devices, smart automotive, sensor devices that can communicate, connected embedded processors. etc. all can be considered as IoT. In most cases, IoT devices are interconnected in an environment and share data with each other to ease making decisions. For example, in a smart home, many different such devices like smart smart bulb, thermostats, refrigerator, microwave oven, fans etc. can be controlled via a smartphone which ease the way of our life. This is illustrated in Figure 2.1 [68, 58]. IoT is the fastest growing field in the world right now, with global spending expected to cross 1.4 trillion by the end of this year (2020). In 2019, there were more than 26 billions IoT devices worldwide and the number is expected to reach 75 billions within the next 6 years, by 2025 [17].

With all the ease and comfort IoT brings to us, there are some serious potential risks involved with it. IoT devices often store our data to help make decisions for ourselves but that data might be sensitive if it leaks out. Since there are billions of IoT devices out there, with our data being stored and processed on a number of such devices, with communication via internet or other potentially less secure networks, IoT are posing a huge security, privacy,

Figure 2.1: The Internet of things (IoT) [68]

and safety risks. Specifically smart medical implants and automotive devices can cause safety concerns while private data storage media and smartphones can create privacy risks. Among all these, security could be the main concern as because of its fast growing nature along with its very low cost production, security was not thought of as an essential feature. At the early stages of IoT, many argue that maybe these devices may not need security at all since the information they carry are so little or insignificant like someone's preferred room temperature or state of a fan or bulb. However, with the rapid increase of IoT, these devices find their way into many applications in our everyday life and process our data. Now that billions of these devices are everywhere with little to no security in them despite containing a huge amount of data, makes them the main target for an attacker. Therefore, governments and industries alike are concerned about the security of these devices and this is one of main research topics now.

One of big difficulties applying security mechanism is the resource constrained nature of such devices. Most of these devices are tiny with a very small silicon footprint, and consuming a very little amount of power to run their operations. Some of these devices are employed in places where it requires them to strengthen their life as much as possible by draining as less energy as possible from their batteries. Pacemaker is one such example where you don't want it to run out of energy of often, requiring another tiresome and difficult heart operation very soon to replace that device. Many sensor devices are employed in field where they can be deployed for years and thus may depend on the harvested energy for most of their life. Embedded processors in such devices often employ aggressive energy saving techniques, going to a low power mode i.e. sleep or hibernation to save power. Employed embedded processors might spend most of their life in such sleep or hibernation to extend their battery life or to minimize the amount of power they harvest from different energy sources like solar, WiFi, wind etc. Therefore, The processor usually shuts off power to most of its components while using a little (or even zero) amount of energy to maintain its state.

Since IoT devices are often resource limited this way, this makes it very difficult to employ any rigorous security since they might require a good amount of silicon area and power that these devices can't provide. Any traditional cryptographic solution are thus often impractical for most devices in this domain. Lightweight cryptographic techniques are being developed but even those can be very resource heavy for a low power embedded processor or a small smart sensor. Moreover, employing the same security techniques with billions of such devices out there might make all of them vulnerable at once on the event of an attack, This are some of the main reasons why researchers are looking at alternative techniques like hardware security which would provide the required practical level of security, while complying with the limited resources of such devices.

### 2.2 Emerging Nanoscale Technology: Memristor

### 2.2.1 Emerging Devices

With the slow-down of Moore's law as we are approaching the physical limit of CMOS, researchers have developed a number of different post-CMOS devices. Among these, some technologies like NAND or NOR flash are more mature and have already found real-world

applications. However, there are a number of emerging devices especially nano-devices which are being researched with the goal of replacing conventional CMOS. International Technology Roadmap for Semiconductors (ITRS) has published and listed the most promising emerging technologies in their report in 2013 [2] and in 2015 [3]. These devices offer various advantages over traditional CMOS while but there is a need for a lot more research to overcome their limitations and use them effectively in current infrastructure.

Memory based on ferroelectric properties of matters have been known for many years and FeRAM (Ferroelectric RAM) is already being considered a mature technology. However, to overcome the shortcomings of FeRAM like destructive read and low read stability, other devices built from ferroelectric materials are being considered. Ferroelectric transistors or FEFET [3, 14] is one such device which is very similar to conventional except the oxide layer is replaced by a ferroelectric layer which helps to retain its state using residual polarization even when the power is disconnected. The polarization of the ferroelectric can be controlled by applying voltage at the metal gate contact. By applying voltage or electric field of sufficient magnitude, the magnetization in the ferroelectric layer is altered. The current or capacitance of the this ferroelectric FET shows a typical hysteresis loop if the applied voltage at the gate terminal is swept through a range. Even if the electric field is removed, a sufficient residual polarization remains in the ferroelectric and, therefore, this system can be used as a non-volatile 1-bit memory. Doped  $HfO_x$  is the most promising material that offers ferroeletricity. FEFET offers high speed, low power, non-volatility, full CMOS compatibility but has relatively high switching voltage and low endurance. Ferroelectric tunnel function or FTJ is another emerging device built from ferroelectric layer sandwiched between two metal layers which is ultra-thin and thus displays tunneling electroresistance (TER) even at room temperature for some complex ferroelectric oxides [2].

Phase change memory (PCM) [19] is another emerging device which displays resistive switching behavior. Its basic mechanism is Joule heating which transforms the internal state of a matter between crystalline and amorphous states. The resistivity of a PCM is high when the underlying material is in amorphous state and is low when it is in a crystalline state. Chalcogenide materials display this phase change property at relatively low temperature of around 600°C. Both of these phases are stable at room temperature, thereby enabling them

to function as non-volatile memories. The physics of PCM is very well-understood compared to many other emerging devices. It offers high speed, high on/off ratio, long endurance but suffers from high switching current as well as limited scalability mainly due to the size of the access device required.

Spin-transfer-toque RAM or STT-RAM is another promising emerging memory technology based on traditional MRAM (magnetoresistive RAM). The memory cell of an MRAM consists of a magnetic tunnel junctions (MTJ) along with a regular MOSFET as the access transistor. A thin tunnel insulator, such as MgO (magnesium oxide) is sandwiched between two ferromagnetic layers to create an MTJ. One of the two layers has a fixed magnetic polarization, called as the 'fixed layer'. The other layer is called the 'free layer' and its magnetization can be easily rotated. When the polarization of these two magnetic layers are in the same direction i.e. parallel, the resistance of the cell is low and is considered a binary value of '1'. When the magnetic orientation is anti-parallel between these two layers, the resistance is higher. Write is performed by passing a current through both of these layers to change the magnetization of the free with respect to the fixed layer. The writing current and energy of a traditional MRAM is very high, thereby limiting their scalability. STT-RAM tries to improve upon this problem by using a low energy spin-torque action for write. It induces a spin-aligned current to control the magnetization of the free layer, reducing the current density compared to MRAM. MRAMs have very high switching speed, data retention, and endurance. However, STT-RAM suffers from small on/off resistance ratio and sensitive to fabrication process.

Redox (reduction-oxidation) based RAM or resistive RAM (RRAM), also known as memristors are a class of metal oxides which can display resistance switching among different states [19]. The basic structure of a ReAM is a thin oxide film between two metal electrodes. RRAM can be created from a variety of materials and composition. Perovskite oxides or binary oxides both can work as RRAM. CB-RAM or conductive-bridge RAMs are another class of RRAM where reative electrode supplies mobile ions to migrate across the dielectric to form a conducting path during on state. However, typically considered RRAM operate differently, by creating oxygen vacancies and in the oxide layer. They can be bipolar or non-polar (current in both or one direction for switching). There are even volatile memristors

which when programmed spontaneously reset back to its high resistance state. RRAM have fast switching speed, low energy, good endurance, retention time but suffers from reliability and larger process variation. Also, the device physics of RRAM is also not well-understood yet. Many RRAMs require an initial forming step where an initial high electric field is applied to initiate this switching behavior. Researchers are also trying to reduce this required forming voltage and create 'forming-free' RRAM which would reduce the circuit design complexity.

Besides these technologies, there are carbon based memory memory devices like carbon nanotubes and graphene based FET, Mott memory, molecular memory and so on [2]. All of these different technologies provide some advantages over existing techniques while showing some challenges in some others, thus there is a need for further research in device engineering, infrastructure building, and finding suitable applications.

#### 2.2.2 Memristor

#### Introduction

Memristor or RRAM is one of the most promising nanoscale devices of the last decade or so that is being explored extensively due to its several advantages over traditional CMOS. Although the term could mean a number of different resistance switching devices as mentioned earlier, we would only mean metal-oxide memristors, specifically those from transition metal-oxides (TMO) throughout this book when we use this term. Memristors are usually non-volatile where the resistance of an insulating oxide can be altered between high and low resistances states via the application of an external field. The physics of metal-oxide memristors are different compared to its close counterpart like CBRAM (conductive-bridge RAM) or phase-change memory. In a memristor, the number of oxygen vacancies created inside the insulating dielectric oxide is the source of conduction. Memristors display typical hysteresis in their I-V curve as shown in Figure 2.2 below along with its common symbol notation. Researchers have shown the use of memristors in many different applications ranging from memory devices, logic circuits [61, 20], neuromorphic computing, hardware security [57, 26] and so on.

Figure 2.2: Memristor symbol (left) and its IV curve showing hysteresis (right)

#### History

The term 'memristor' is coined by Professor Dr. Leon Chua in his 1971 paper [15] when he predicted the presence of a fourth fundamental circuit element alongside resistor, capacitor, and inductor. He predicted this from the relationship among voltage, current, flux, and charge among the fundamental devices and later also projected some other characteristics of memristors or memristor-like devices [16].

The relationship between the flux linkage  $\delta \phi$  and  $\delta q$  is expressed as the memristance (M), the property of a new fundamental circuit element, memristor. It can be implied that at a certain time, the memristance defines a linear relationship between voltage and current just like a resistor. Thus, memristor can actually be represented as a variable resistor. This relationships are shown in these equations below:

$$M = \frac{\Delta\phi}{\Delta q} \tag{2.1}$$

$$= \frac{\Delta \phi / \Delta t}{\Delta q / \Delta t} = \frac{\Delta v}{\Delta i} \tag{2.2}$$

$$\implies \Delta v = (M)\Delta i$$

Although, metal-oxide based switching devices are well-known for many years, memristors only have gained attention after a research team from Hewlett-Packard lab published a paper where the tie the characteristics of a TiO<sub>2</sub> MIM (metal-oxide-metal) device to that of an

Chua memristor in 2008 [63]. After that, memristors have gained a massive attention and a lot of research effort is ongoing for its device engineering, fabrication techniques, and a broad range of applications.

#### **Memristor Characteristics**

As mentioned earlier, we are considering transition metal-oxides which are non-volatile, and bi-polar. They show different resistive or memristive states i.e. memristors show hysteresis in their I-V characteristics as shown in Figure 2.2. Binary memristors have two stable resistive states, called the high resistance state (HRS) and the low resistance state (LRS). HRS and LRS are also known as OFF and ON states, respectively as well. Each of these two states can be reached by applying a voltage of appropriate magnitude and duration across a memristor. The minimum magnitude and duration of voltage applied across a memristor to reach LRS from HRS are called the set voltage or positive threshold voltage ( $V_{thp}$ ), and positive switching time ( $t_{swp}$ ), respectively. On the other hand, the minimum magnitude and duration of voltage required to go to HRS from LRS are called the reset voltage or negative threshold voltage ( $V_{thn}$ ), and negative switching time ( $t_{swn}$ ), respectively. These six parameters HRS, LRS,  $V_{thp}$ ,  $V_{thn}$ ,  $t_{swp}$ , and  $t_{swn}$  define the high level characteristics of a binary memristor.

Metal-oxide memristors are usually CMOS (complimentary metal-oxide semiconductor) compatible, can be fabricated on the back-end of the silicon together with CMOS on front. The size of a memristor is also very small (a few nanometers) which makes them an attractive choice for many applications.

The physics of memristors are not fully understood yet as memristive properties vary a lot depending on the type of oxide as well as the conductive materials used. The thickness and area of these materials, current limiting devices etc. control the memristive parameters. Thus different memristors reported in literature vary a quite a bit from each other in their resistive states, operating voltages and speed of operation.  $TiO_x$ ,  $HfO_x$ ,  $TaO_x$  are among of the most promising memristor devices because of their high on/off ratio, speed, retention time, endurance, and CMOS compatibility. Moreover, their switching process is stochastic and thus, memristors display cycle-to-cycle variation in their characteristics which makes it

challenging for circuit designers. Techniques are being explored to confine the characteristics of a memristor and make their switching operation much more consistent to reduce variability.

## 2.3 Hardware Security as IoT Security

Usually for any system, security choices can be divided into two broad categories, software and hardware. Software security usually refers to some algorithmic implementation of mathematically rigorous encryption or hash functions. They algorithms are usually very robust and hard to break, providing practically the best security for a system. However, these algorithms usually take many clock cycles for their implementation and thus also consume a larger amount of power. Therefore, implementing them for a small system where area, power and delay are very limited, can be impractical. As these systems have limited power budget, small in size and sometimes real-time in nature (and thus small delay), any security add-on must have very low overhead but these rigorous algorithms fail to fulfill that criteria. That's where hardware security comes.

### 2.3.1 Traditional Security: Cryptography

Cryptography is the technique of securing a data communication in the presence of an adversary. Usually using some kind of a key, cryptography allows a message to be encoded in such a way that only the intended receiver with the correct key would be able to decode the message. Cryptoghaphy has been used in human history for a long time including Caesar cipher, polyalphabetic cipher, Vigenére cipher etc. In the computer era, modern day cryptography is much more secure and based on rigorous mathematical analysis where a brute force attack would take an incredibly huge amount of time which is not possible in practice. Cryptography can be classified into two broad categories: symmetric key and public key cryptography. In a symmetric key cryptography, the same key is used for both encryption and decryption, easing the hardware implementation while being very secure. AES (advanced encryption standard), DES (data encryption standard), triple DES are examples of symmetric key cryptography. Public key or asymmetric key cryptography, on the other hand, relies on two keys: one public key and one private key. One key is known

to all and anyone can use to encrypt his/her message. The private key is only known to the intended receiver and only he/she can decrypt that message using this key. RSA (Rivest-Shamir-Adleman) is the most well-know public key cryotographic alogorith. While this is very secure, main disadvantage is the associated huge resource overhead. Thus while AES are used everywhere for secure data communication, RSA is only used for secure key exchange or digital signature.

Besides securing data communication, cryptography is also used to verify the authenticity of received data by means of a hash. A hash function is any algorithm can convert a large message to a fixed-length token of that message. Simple hash includes checksum, parity check etc. which can find bit-errors and thus verify the authenticity of the data. Cryotographic hash functions are one-way functions that fulfills some crytographic requirements like: pre-image and second pre-image resistance, collision resistance, despite the hash being easy to computer. The basic idea is that it should be very difficult to find two messages with the same hash given either the hash or the message and almost half of the bits of the hash should change if just one bit of the data is changed. Popular cryptographic hash algorithms include MD5, SHA-1, SHA-2, SHA-3 etc. All these hash algorithms are computationally expensive.

Algorithms like AES, RSA etc. are based on discrete mathematics with brute force attack resistance in billions of years of computing resources. However, when these algorithms are implemented on an embedded platform, the hardware can leak information like power consumption, delay in different stages of the algorithm runs. In fact, researchers have shown that these side-channels like power, timing, sound, EM (electromagnetic emission) can be used to perform so-called side-channel attack to break the security of cryptographic algorithms. For example, using simple (SPA) and differential power analysis (DPA) of side channel power, security of AES implemented on an embedded microcontroller can be broken [30, 31]. Fault injection is another very effective technique to attack otherwise secure cryptographic implementations [5]. Probing attacks [76] or EM attacks [1] can also be performed to read the stored secret keys to break a cryptographic algorithm as well.

Thus, although traditional cryptography is theoretically secure, their security can be compromised using the vulnerability of the underlying hardware implementations. Moreover, because these algorithms are mathematically rigorous, their resource requirement i.e. power,

area, and delay overhead are high. Therefore, researchers have worked on lightweight implementations of these algorithms as well as different new lightweight algorithms like SIMON, Piccolo, KATAN, PRESENT etc. [43] to tackle this issue. However, in the era of IoT, there are now billions of devices being produced each year and most of those are extremely resource limited, running on a battery or harvested energy alone. Therefore, traditional cryptographic algorithms would be either impractical or too resource hungry for these of types of devices.

### 2.3.2 Introduction to Hardware Security

We now know that even mathematically secure algorithms can be broken by exploiting the vulnerability in their hardware implementations. Moreover, IP piracy, reverse engineering, counterfeit etc. cause losses on the order of billions of dollars each year. Software based security solutions are not enough to prevent an adversary from copying a design and reproduce illegally. Therefore, researchers have been working on different hardware level modifications which improves the security of an IC and restrict overproduction, recycling, or counterfeit products on the market. Hardware security refers to any such technique that uses the hardware and modifies it to provide security solutions. Usually these techniques are specific to some particular security threat. For example, logic encryption and IC camouflaging techniques significantly reduce an adversary's ability to reverse-engineer a design, thereby mitigating piracy and counterfeit. Thus, hardware security provides innovative solutions to improve security of a device which may otherwise be vulnerable. Two very common hardware security primitives are physical unclonable function and true random number generator. They can generate hardware specific truly random keys that is otherwise impossible to generate from software alone.

## 2.3.3 Physical Unclonable Function (PUF)

Physically unclonable function or PUF is a hardware security primitive that exploit tiny variations among the chips with same functional implementation and use that variation to generate hardware specific signatures. These intrinsic variations originate from uncontrollable manufacturing process variation and PUFs try to enlarge these variations to generate keys unique to that hardware only. Thus PUFs are usually represented as a challenge-response system where the challenge (C) is the input to the PUF that is used to extract process variation from a hardware and response (R) is the output key generated from that hardware using that PUF.

In this sense, PUF is analogous to a mathematical one-way function. One-way function is any function which is very easy to evaluate in one direction, but very hard to compute in reverse. For example, multiplication of two large prime numbers to get a composite number is easy, however factoring that composite number to get its prime factors is not straightforward and usually time-consuming. Thus applying a challenge to a PUF to generate its response is easy but determining the timest process variations that cause a particular PUF to generate a particular response is not very difficult to determine. Just like a software based security like encryption or hash algorithms use mathematical one-way function to implement the algorithms and thus ensure security, PUF based hardware security are essentially a low cost and natural way of implementing the same concept. Pappu et.al. first demonstrated a physical one-way function using variation in scattering pattern in [53] which later known as physical unclonable function or PUF. A PUF has to fulfill these requirements: (1) the PUF response must be raondom, (2) the process variation must not uncontrollable, and (3) PUF functionality or underlying process variation is unclonable.

#### Previous Relevant Works on PUF

Traditional cryptographic algorithms depend on some mathematical one-way function to provide security. However, most commonly used one-way functions are either based on unproven conjectures or have practical vulnerabilities in their implementations. To overcome these issues of algorithmic one-way functions, Pappu *et.al.* first proposed a physical one-way function (POWF) in 2001 [53] which relies on simultaneous multiple scattering from inhomogeneous structure to implement the one-way function.

Later in 2002, Gassend et.al. proposed a silicon physical random function and coined the term 'PUF' [21]. It was the first PUF implemented in silicon using electrical properties which is path delay in this case. Since then, many researchers have worked on many variations

and implementations of PUF. Arbiter PUF or APUF can be considered the first electrical PUF and the most well-studied PUF [34, 35], proposed in early few years after the POWF was established. APUF utilizes variation in propagation delay due to manufacturing process variation of two identically laid out circuits to implement PUF functionality [66]. Figure 2.3 shows a high level block diagram of an arbiter PUF. Here, two-input/two-output switches are chained together to create a circuit with two identical but separate path for a signal to propagate through. Process variations dictate that a single input signal will propagate through one path faster than the other. An arbiter or flip-flop is then used to compare that delay differences and a response is generated.

For an n-challenge arbiter PUF, each path consists of n such identically laid out two input/two output switches. Each switch has one selector input - one bit of the challenge. If the challenge bit is 0, then the path is straight-through and if the challenge bit is 1, the path is criss-crossed. Figure 2.4 (left two) shows the logical diagram of such a switch. This switch can be implemented easily by a pair of multiplexers (MUXes) as shown in Figure 2.4 (right). The two multiplexers share the same selector signal which is one bit of the challenge set. If it is 0, then input 'a' goes to output 'y1' and input 'b' to 'y2'. If it is an 1, then 'a' goes to 'y2' and 'b' goes to 'y1', thus implementing this switch.

At the end of the signal propagation, an arbiter is used to determine which path is faster compared to the other. A D latch or a D flip-flop can be used as the arbiter. The two arbiter PUF paths are connected to the 'D' and 'clock' input. If the first path ('D') is faster, the PUF response is 1, otherwise it is 0. Thus the arbiter converts the analog delay difference into digital signatures.

Figure 2.3: Arbiter PUF

Figure 2.4: Two input/two output switch (left two) and its simple implementation with two MUXes (right)

Ring-oscillator PUF (RO-PUF) [65] is another very commonly used PUF, which can be easily implemented in both ASIC (Application Specific Integrated Circuit) and FPGA (Field Programmable Gate Array). A ring oscillator is a long chain of odd number of inverters connected in a ring such that the output oscillates between high and low voltage level, as shown in Figure 2.5. Thus a ring oscillator configuration can create a particular frequency where the clock period is sum of all individual delays of the inverters in the chain. Due to inherent process variation, the inverters would have slightly different delays and thus two identically laid out ring oscillators would have slightly different frequencies. A counter and comparator can be used to measure the difference between these two frequencies and convert into digital signatures. An RO-PUF is shown in Figure 2.6.

Both the arbiter PUF and RO-PUF are delay based PUFs since they use electrical delay as the property to implement PUF functionality. Any other electrical properties that are subject to uncontrollable process variation can be used to build a PUF. In an SRAM (static random access memory) PUF [22], random initial state of each SRAM cell during power-up is used to generate PUF signatures. In each SRAM cell, there is a cross-coupled inverter pair which are identical by design. During power-up when there are no externally exerted signal to an SRAM cell, due to slight voltage difference arising from parametric variation of these transistors would be amplified by cross-coupled inverter action and thus would show a tendency towards logic '1' (high) or '0' (low). Thus all the SRAM cells in a memory would give such random initial values during start-up which can be used as a signature of that chip.

Figure 2.5: Ring oscillator: a chain of an odd number of inverters

Figure 2.6: A ring oscillator PUF

Since CMOS scaling has become very slow in recent years, researchers have been looking for alternative technologies to provide application specific unique solutions. These emerging devices display switching variations and can be exploited to implement different memory based PUFs like memristor PUF [32], STT-MRAM (Spin transfer torque magnetic random access memory) PUF [83], PCM (Phase change memory) based re-configurable PUF [84] etc.

#### Memristor based PUF

A simple PUF based on the stochastic switching time of a memristor is first proposed in Rose et.al. in [60]. Memristors display stochastic switching behavior i.e. even if the same voltage, greater than its threshold voltage is applied to a memristor, it may or may not switch. First a mean switching time of a set of memristors are evaluated and then that a voltage is applied equal to the duration of that mean switching time to have a 50% switching probability. This is named as write-time based memristive PUF (WTMPUF) [59] which was later fabricated

and demonstrated experimentally in [45]. Kavehei et.al. demonstrated a PUF which use both memristors and ring oscillators, called the mrPUF [27].

Since WTMPUF uses absolute write-time of memristors as the source of entropy to implement a PUF, it could be subject to errors due to environmental changes. relative nature of measurement of APUF and RO-PUF make them robust against such environmental variations, a memristor PUF circuit built from a crossbar array of memristors where relative write-time of a pair of memristors are compared to generate a PUF response [57]. This memristor crossbar PUF or the XbarPUF [57] use a read-monitored-write approach developed in [42] to implement a PUF challenge and thus gradually nudge the memristors from one memristive state to another before one memristor column reaches to the other state faster than its adjacent column of memristors. Just like an arbiter PUF, this XbarPUF also uses an arbiter to determine which crossbar column of memristors were faster in its pair and as soon as read-monitored-write approach completes a complete write (transition from one state to another), a response is generated. Thus this PUF generates a complete response when all the crossbar column pairs are resolved. This XbarPUF shows a huge improvement in area in terms of transistor count compared to CMOS PUF (APUF) and its uniqueness and uniformity are very close to the ideal value of 50%. However, the biggest concern about PUF, the reliability metric wasn't reported in this work and data to generate these other results do not directly comply with any particular memristor. Therefore, my first work was to gather data from a HfO<sub>2</sub> memristor to build more a more realistic model and evaluate the XbarPUF performance using this real data.

#### **PUF Performance Metrics**

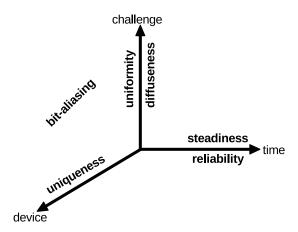

In order to gauge the degree of security provided by a PUF and to be able to fairly compare it with other PUF implementations, standardized performance metrics have been devised. Maiti et al. [39] and Hori et al. [23] have discussed several metrics to quantify a PUF's performance. The major six metrics are: uniqueness, reliability, bit-aliasing, uniformity, steadiness, and diffuseness. As shown in Figure 2.7, these metrics are used to quantify a PUF's performance across multiple device dimensions: inter-chip space, intra-chip space, and

Figure 2.7: Standard metrics used for the evaluation of a PUF

time. They have become standards in hardware security research everywhere to quantify a PUF's performance.

1) <u>Uniqueness</u>: It is a measure of a PUF's ability to produce a unique ID in terms of its challenge-response pairs which are a specific function of its implementation on a given chip. To be able to efficiently distinguish every IC chip (from other equivalent ones) with a PUF circuit, the uniqueness must be tending to 50. That means, for a given challenge set, almost half the responses produced by two PUFs should be different from each other. Uniqueness or also known as inter-chip hamming distance is defined as:

$$Uniqueness(\%) = 100 * \frac{2}{N_{chips}.(N_{chips} - 1)} \sum_{i=1}^{N_{chips}-1} \sum_{j=i+1}^{N_{chips}} r_i \oplus r_j,$$

(2.3)

for each response bit and each challenge set, where  $N_{chips}$  is the number of PUFs or chips to be measured,  $resp_i$  and  $resp_j$  are responses from the i-th and j-th chip respectively.

2) <u>Uniformity</u>: Another PUF performance metric which measures a PUF's ability to produce distinct responses across a set of challenges is the uniformity. With the flipping of even a single bit of the challenge, nearly half of the response bits are expected to flip. Effectively, uniformity is a measure of the ratio of 0's and 1's across the whole of the response set of the PUF. A PUF with poor uniformity would allow the attacker to reduce the possible response space and get a better prediction. This metric is defined as:

$$Uniformity(\%) = 100 * \frac{1}{N_{challenges}} \sum_{c=1}^{N_{challenges}} resp_c, \tag{2.4}$$

for each response bit and each chip, where  $N_{challenges}$  is the number of challenges applied to a single PUF and  $r_c$  is the response for c-th challenge.

3) <u>Reliability</u>: Also represented as intra-chip hamming distance, this metric quantifies a PUF's consistency over time. If a PUF is unable to produce the same response every time for a given challenge, then the PUF is considered unreliable and may require error-correction. Reliability, as a metric is defined as:

$$Reliability(\%) = 100 - 100 * \frac{2}{N_{cycles} \cdot (N_{cycles} - 1)} \sum_{t=1}^{N_{cycles} - 1} \sum_{it=t+1}^{N_{cycles}} resp_t \oplus resp_{it}, \qquad (2.5)$$

per response bit and chip, where  $N_{cycles}$  is the number of times of applying a challenge and measuring a response.

4) <u>Bit-Aliasing</u>: Different PUFs might produce similar responses for certain challenges. This would decrease the unpredictability of the PUF. Bit aliasing measures the average hamming distance for the k-th response bit of different PUFs. This metric is defined as:

$$BitAliasing_k(\%) = 100 * \frac{1}{N_{chips}} \sum_{m=1}^{N_{chips}} resp_{k,m}, \qquad (2.6)$$

for each bit k of a response.

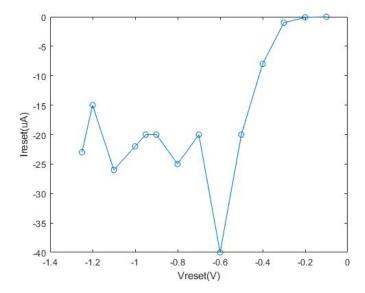

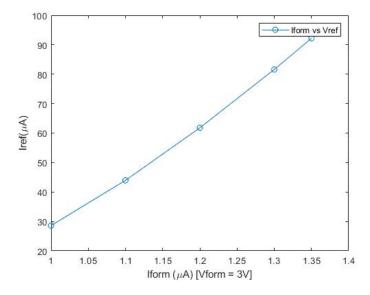

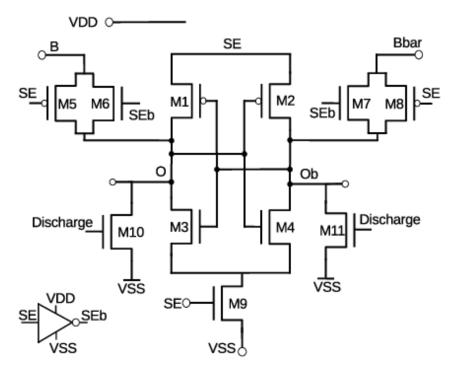

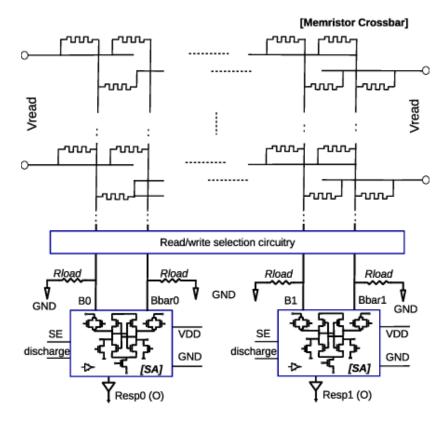

5) <u>Diffuseness</u>: The same PUF should generate different uncorrelated responses if different challenges are applied, especially for PUFs with large CRPs. Diffuseness measures this degree of different among different responses generated from a single PUF for different challenges. Diffuseness is evaluated by measuring the hamming distance among all different response vectors generated by a single chip and is defined below: