### **Doctoral Thesis**

### Shibaura Institute of Technology

Power Line Noise Suppression using N-path Notch Filter in ECG Signal Acquisition

2020/September

Khilda Afifah

## POWER LINE NOISE SUPPRESSION USING N-PATH NOTCH FILTER IN ECG SIGNAL ACQUISITION

Author:

Khilda AFIFAH

Supervisor: Prof. Nicodimus RETDIAN

A thesis submitted in fulfillment of the requirements for the award of the degree of Doctor of Engineering

Shibaura Institute of Technology

2020/September

### **Declaration of Authorship**

I, Khilda AFIFAH, declare that this thesis titled, "POWER LINE NOISE SUPPRES-SION USING N-PATH NOTCH FILTER IN ECG SIGNAL ACQUISITION" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

v

### Abstract

### POWER LINE NOISE SUPPRESSION USING N-PATH NOTCH FILTER IN ECG SIGNAL ACQUISITION

by Khilda AFIFAH

Bio-sensing activities such as electrocardiogram (ECG) and electroencephalography (EEG) are challenging to obtain high-quality electrical signals because biomedical signals have small amplitude and low frequency. When performing a biomedical signal acquisition, common-mode noise such as power line interference appears near the desired biomedical signal. It has made a problem when the power line interference has amplitude higher than the primary signal.

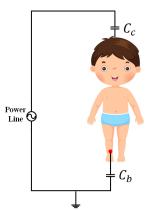

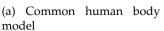

Common-mode noise reduction has been recognized as important research. The driven right leg (DRL) circuit was significant and effective to suppress common-mode noise. However, in the actual ECG measurements using DRL circuit, some-times noise still appears at the output and mismatching in the electrode impedance makes an impact to convert common-mode noise into a differential input voltage. The body in DRL circuit is expressed as a single node and cannot be used to simulate the effect of the electrode impedance mismatch. Therefore, a new body model is needed to be able to analyze the effect of electrode impedance mismatch and other problem with common body model.

The proposed DRL circuit is an improved circuit from common DRL circuit. The first improved DRL circuit, biomedical signal is expressed by current source in parallel with electrode impedance. The simulation results of improved circuit show mismatch between right and left electrode impedance makes noise appears at the output signal. The common human body from DRL circuit represented skin-electrode impedance as a single node. The second improved circuit, the skin-electrode impedance is expressed by resistance and stray capacitance are on each electrode. The simulation results of this improved circuit show the proposed circuit achieved smaller noise when stray capacitance in the arm and right leg are the same. Combination between proposed human body model and DRL circuit achieved output of the circuit is noise

appear in the output signal. Therefore, human body model with DRL circuit still need another filter to get high quality biomedical signal (noise free signal).

The other techniques to suppress common-mode noise have been proposed by using digital and analog notch filters. The technique to suppress common-mode noise used a digital notch filter, but it requires an analog front-end with a wide dynamic range since the noise contaminated input signal need to be converted to digital signal. The techniques with analog notch filter such as conventional N-path notch filters have disadvantage because these techniques require  $3G\Omega$  switches off-resistance and 18 paths to reach notch depth target. The problem to implement previous N-path notch filter is the difficulty in implementing switch with off-resistance. On-chip implementation of the system is also a challenge in the realization of portable ECG devices because the notch filter has a large time constant in which requires large capacitance and high resistance.

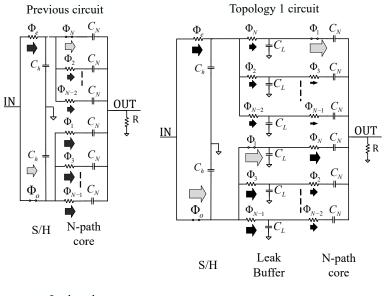

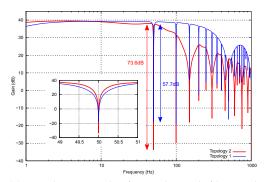

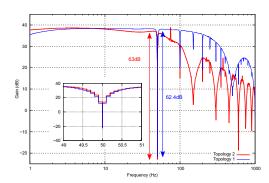

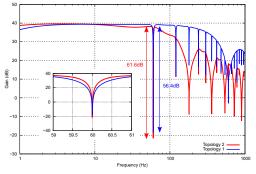

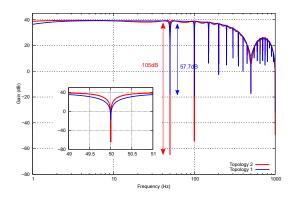

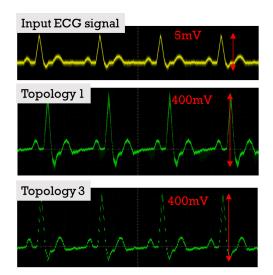

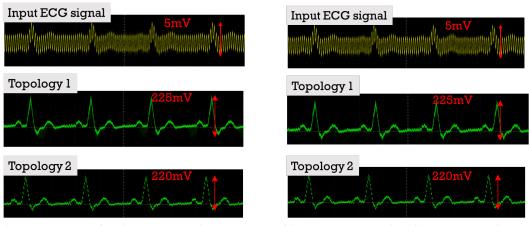

Two topologies of N-path notch filter with leak buffer circuit have been proposed. The proposed N-path notch filters are Topology 1 and Topology 2. Topology 1 and Topology 2 achieved notch depth of 62.4dB and 63dB in measurement results with sampling frequency 50Hz, even if the proposed circuits use less number of path and small of switches off-resistance. Topology 1 and Topology 2 are verified using artificial ECG signal with 2Hz which is contaminated by power line interference with frequency 50Hz or 60Hz. Experiment results show that the proposed circuit significantly reduces the power line noise.

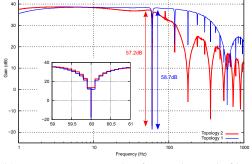

Topology 1 and Topology 2 N-path notch filters achieved notch depth higher than notch depth target, but have a problem in the size of capacitor. The total capacitance for Topology 1 and Topology 2 are 2.3 µF and 930nF, respectively. Therefore, the next proposed circuit aims to propose a new technique of N-path notch filter with switched capacitance scaling to decrease the total capacitance for a fully on-chip implementation. The proposed N-path notch filter replace the resistor in N-path core into resistor equivalent of switched-capacitor to reduce the total capacitance. Topology 1 and Topology 2 with capacitor scaling and also Topology 3 using CMOS switch with total capacitance for all topologies equal to 1nF achieved notch depth higher than 40dB.

Topology 1 and Topology 2 using CMOS switch with scaling factor 1000 achieved

notch depth of 64dB and 68dB, respectively. The total capacitance of Topology 1 and Topology 2 using CMOS switch with scaling factor 1000 are 2.34nF and 930pF, respectively. Below are advantage and disadvantage of Topology 1, Topology 2, and Topology 3 with/without capacitance scaling. Topology 1 with capacitor scaling is more effective in the total capacitance for on-chip implementation because of to achieve notch depth around 44dB. It used the smallest total capacitance than the other topologies.

### Acknowledgements

In the name of Allah, most Gracious and Merciful. I am very grateful with his permission; I was able to accomplish my Doctoral thesis.

A special thanks to my supervisor, Prof. Nicodimus Retdian from Global Course on Engineering and Science, Shibaura Institute of Technology. His insightful comments, guidance and all the useful discussion are very much appreciated. Without his encouragement and persistent help, this thesis would not have been possible. And a special thanks to Prof. Nobukazu Takai from Gunma University and dr. Hirohito Shima, M.D., Ph.D. from Departement of Pediatrics Sendai City Hospital, their insightful comments and guidance are very much appreciated. Not forgetting my defense committee members: Prof. Eiji Watanabe from Shibaura Institute of Technology, Prof. Kazunori Mano from Shibaura Institute of Technology, Prof. Naohiko Tanaka from Shibaura Institute of Technology, Prof. Takeshi Shima from Kanagawa University and Prof. Nobuhiko Nakano from Keio University. Thank you for your attention, advice and constructive feedback.

Very special thanks to Japan International Cooperation Agency for giving me opportunity to carry out doctoral program for their scholarship support and also to all my friends; Those who supported me during the completion of the thesis. Thank you so much.

I would also like to express gratitude to my parents, my husband and the rest of my families for unconditional love and constant support.

## Contents

| De | eclara  | ntion of Authorship          | iii   |

|----|---------|------------------------------|-------|

| Ał | ostrac  | ct                           | vii   |

| Ac | knov    | wledgements                  | xi    |

| Co | onten   | ts                           | xiii  |

| Li | st of ] | Figures                      | xvii  |

| Li | st of [ | Tables                       | xxi   |

| Li | st of A | Abbreviations                | xxiii |

| Ph | ysica   | al Constants                 | xxv   |

| Li | st of S | Symbols                      | xxvii |

| 1  | INT     | RODUCTION                    | 1     |

|    | 1.1     | Research Background          | . 1   |

|    | 1.2     | Research Questions           | . 3   |

|    | 1.3     | Problem Statement            | . 4   |

|    | 1.4     | Research Objectives          | . 5   |

|    | 1.5     | Scope of Work                | . 5   |

|    | 1.6     | Significance of the Research | . 5   |

|    | 1.7     | Thesis Organization          | . 6   |

| 2  | LIT     | ERATURE REVIEW               | 7     |

|    | 2.1     | Driven Right Leg Circuit     | . 7   |

|    | 2.2     | Digital Notch Filter         | . 13  |

|   | 2.3  | Analog Notch Filter                                                | 14 |

|---|------|--------------------------------------------------------------------|----|

|   | 2.4  | N-path Notch Filter                                                | 17 |

|   | 2.5  | Previous Work on N-path Notch filter                               | 20 |

|   | 2.6  | Conclusion                                                         | 23 |

| 3 | INV  | ESTIGATION ON BIOMEDICAL BODY MODEL                                | 27 |

|   | 3.1  | Improved ECG Body Model with DRL Circuit                           | 28 |

|   |      | 3.1.1 Electrode Impedance                                          | 30 |

|   |      | 3.1.2 Gain of differential amplifier and feedback amplifier $A_3$  | 33 |

|   | 3.2  | Proposed Human Body Model                                          | 34 |

|   | 3.3  | Skin-Electrode Impedance                                           | 37 |

|   | 3.4  | Investigation on Human Body Model                                  | 42 |

|   | 3.5  | Discussion                                                         | 44 |

|   | 3.6  | Conclusion                                                         | 45 |

| 4 | PRC  | DPOSED N-PATH NOTCH FILTER                                         | 47 |

|   | 4.1  | N-path Notch Filter with Leak Buffer Circuit                       | 48 |

|   |      | 4.1.1 Topology 1                                                   | 48 |

|   |      | 4.1.2 Topology 2                                                   | 50 |

|   | 4.2  | Simulation and Measurement Result                                  | 51 |

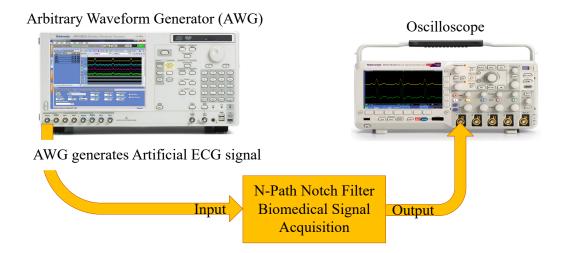

|   | 4.3  | Experiment Investigation                                           | 54 |

|   | 4.4  | Discussion                                                         | 56 |

|   | 4.5  | Conclusion                                                         | 57 |

| 5 | N-P. | ATH NOTCH FILTER WITH CAPACITANCE SCALING                          | 59 |

|   | 5.1  | N-path Notch Filter with Capacitor Scaling                         | 60 |

|   |      | 5.1.1 Basic Design                                                 | 60 |

|   |      | 5.1.2 Implementation of Capacitor Scaling in Topology 1 and Topol- |    |

|   |      | ogy 2                                                              | 63 |

|   | 5.2  | Simulation Results                                                 | 63 |

|   |      | 5.2.1 Case 1                                                       | 64 |

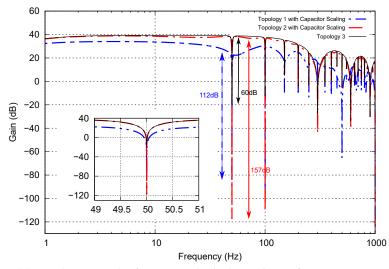

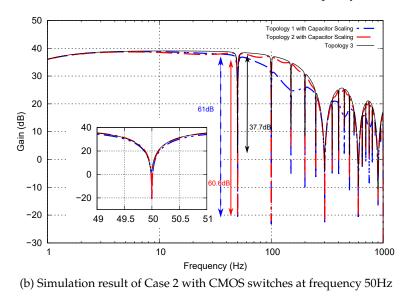

|   |      | 5.2.2 Case 2                                                       | 67 |

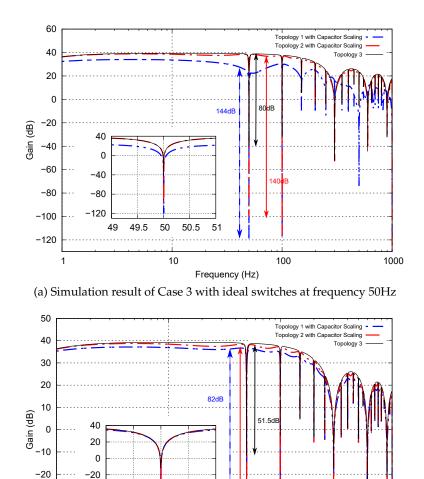

|   |      | 5.2.3 Case 3                                                       | 68 |

xiv

|   | 5.3 | Discussion                           | 69 |

|---|-----|--------------------------------------|----|

|   | 5.4 | Conclusion                           | 70 |

|   |     |                                      |    |

| 6 | COI | NCLUSIONS AND RECOMMENDATION         | 73 |

|   | 6.1 | Overall Conclusion                   | 73 |

|   | 6.2 | Contributions                        | 75 |

|   | 6.3 | Future Work                          | 76 |

|   | T : | of Dublications                      | 77 |

| A |     | of Publications                      |    |

|   | A.1 | List of Journals                     | 77 |

|   | A.2 | List of Published Conference Papers  | 77 |

|   |     | A.2.1 International Conference Paper | 77 |

|   |     | A.2.2 Domestic Conference Paper      | 78 |

|   |     |                                      |    |

#### Bibliography

# **List of Figures**

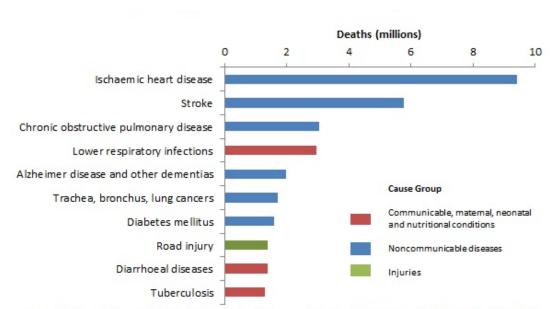

| 1.1  | Top 10 global cause of deaths, 2016                                                      | 2  |

|------|------------------------------------------------------------------------------------------|----|

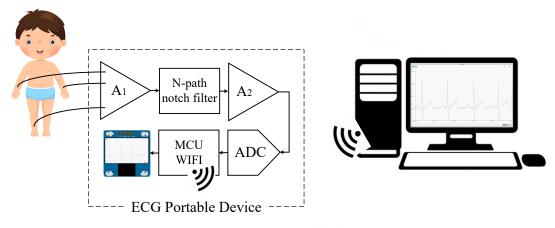

| 1.2  | ECG portable design.                                                                     | 2  |

| 2.1  | ECG signal acquisition circuit with parasitic capacitors and electrode                   |    |

|      | resistances and its equivalent circuit of common-mode voltage                            | 8  |

| 2.2  | Simulation resul of common-mode voltage from Fig. 2.1                                    | 9  |

| 2.3  | Grounding circuit to reduce common-mode voltage                                          | 10 |

| 2.4  | Driven Right Leg circuit with parasitic capacitors and electrode resis-                  |    |

|      | tances and its equivalent circuit of common-mode voltage                                 | 11 |

| 2.5  | Simulation resul of common-mode voltage from Fig. 2.4                                    | 12 |

| 2.6  | A 60Hz time contant multiplier notch filter with compensation circuit                    |    |

|      | [19]                                                                                     | 14 |

| 2.7  | 5 <sup>th</sup> -order single-ended low-pass notch filter circuit [2]                    | 15 |

| 2.8  | Measured frequency responses of 5 <sup>th</sup> -order single-ended lowpass notch        |    |

|      | filter [2]                                                                               | 15 |

| 2.9  | The fully differential notch filter with the added output circuitry of                   |    |

|      | one balanced OTA (BOTA) [7]                                                              | 16 |

| 2.10 | Measured result of fully differential notch filter with the added output                 |    |

|      | circuitry of one balanced OTA (BOTA) [7]                                                 | 17 |

| 2.11 | Conventional N-path notch filter                                                         | 18 |

| 2.12 | The relation between the number of path $N$ and notch depth $H_N$ in                     |    |

|      | the conventional N-path notch filter.                                                    | 20 |

| 2.13 | Analog front-end for biomedical signals acquisition                                      | 21 |

| 2.14 | The conventional of 10-phase N-path notch filter [4]                                     | 22 |

| 2.15 | Mechanism in the first path when $\phi_o$ and $\phi_1$ are closed $\ldots \ldots \ldots$ | 23 |

| 2.16 | Simulation and Measurement result of previous N-path notch filter at                            |            |

|------|-------------------------------------------------------------------------------------------------|------------|

|      | frequency 50Hz                                                                                  | 23         |

| 2.17 | Measurement investigation of previous N-path notch filter circuit                               | 24         |

| 2.18 | The simulation result of relation between switch off-resistance and                             |            |

|      | notch depth in conventional circuit.                                                            | 24         |

| 3.1  | Measurement result of ECG instrumentation using DRL circuit                                     | 28         |

| 3.2  | Simulation circuit of Driven Right Leg circuit with parasitic capacitors                        |            |

|      | and electrode resistances as shown in Fig.2.4 (a)                                               | 28         |

| 3.3  | Proposed DRL circuit with parasitic capacitors and electrode resis-                             |            |

| 0.0  | tances and its simulation circuit.                                                              | 30         |

| 3.4  | Output of ECG body model of ECG measurement using DRL circuit.                                  |            |

| 3.5  | $v_{out}$ when $R_{E1} = 30$ K $\Omega$ and $R_{E2} = 100$ K $\Omega$                           |            |

| 3.6  | Comparation the effect of electrode impedance mismatch between                                  | 01         |

| 0.0  | common and proposed ECG signal acquisition with DRL circuit.                                    | 32         |

| 3.7  | Effect of $R_{E1}$ in the output when $R_{E2} = R_{DRL} = 100 \text{k}\Omega$ .                 |            |

| 3.8  | Relation between $R_{E1,2}$ and $v_{cm} - v_{out}$ when $R_{E1} = R_{E2}$ and $R_{DRL} =$       | 00         |

| 0.0  | $100k\Omega.$                                                                                   | 34         |

| 3.9  | Relation between $R_{DRL}$ and $v_{cm} - v_{out}$ when $R_{E1} = R_{E2} = 100 \text{K}\Omega$ . |            |

|      | Relation between $A_3$ and $v_{cm}$                                                             |            |

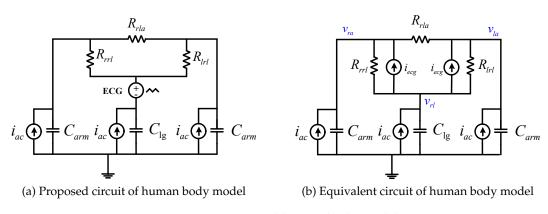

|      | Human body model.                                                                               |            |

|      | Proposed human body model.                                                                      |            |

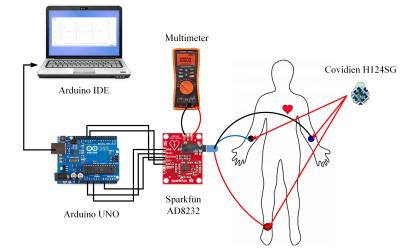

|      | Implementation of skin-electrode measurement                                                    | 38         |

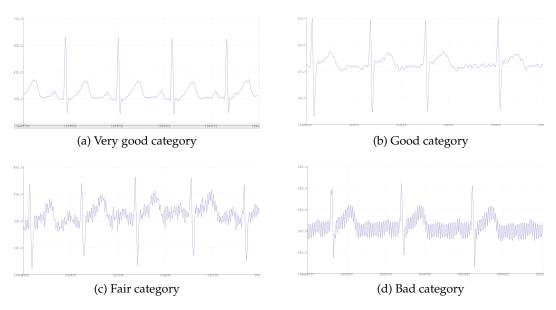

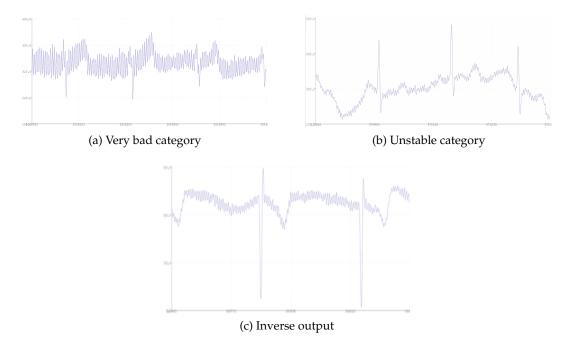

|      | Category of output ECG signal acquisition with AD8232.                                          | 39         |

|      | Category and output of ECG signal acquisition with AD8232.                                      |            |

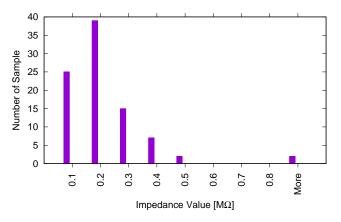

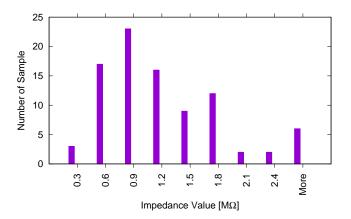

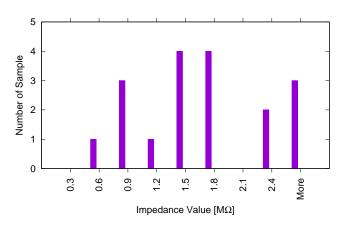

|      | Result of skin-electrode impedance in right arm and left arm $R_{rla}$ from                     | 57         |

| 5.10 | ECG signal acquisition with AD8232                                                              | <i>4</i> 1 |

| 3 17 | Result of skin-elecrode impedance in right arm and right leg $R_{rrl}$ from                     | TI         |

| 5.17 | ECG signal acquisition with AD8232                                                              | 41         |

| 210  |                                                                                                 | 41         |

| 3.18 | Result of skin-electode impedance in left arm and right leg $R_{lrl}$ from                      | 40         |

|      | ECG signal acquisition with AD8232                                                              | 42         |

| 3.19 | Simulation result of $v_{in}$ when ECG current source and $i_{ac}$ are added       |    |

|------|------------------------------------------------------------------------------------|----|

|      | separately                                                                         | 43 |

| 3.20 | Simulation result of $v_{in}$ when ECG current source and $i_{ac}$ are added       |    |

|      | at the same time.                                                                  | 43 |

| 3.21 | Proposed human body model                                                          | 44 |

| 3.22 | Human body model with DRL circuit                                                  | 44 |

| 3.23 | Simulation result of human body model with DRL circuit                             | 45 |

| 4 1  |                                                                                    | 40 |

| 4.1  | Design of Topology 1                                                               | 48 |

| 4.2  | Mechanism of leak path in previous N-path notch filter circuit and                 |    |

|      | Topology 1 when $\phi_o$ and $\phi_1$ are closed and its equivalent circuit of the |    |

|      | first path of Topology 1                                                           | 49 |

| 4.3  | Design of Topology 2                                                               | 50 |

| 4.4  | Mechanism of leak path in Topology 1 and Topology 2 when $\phi_o$ and              |    |

|      | $\phi_1$ are closed                                                                | 51 |

| 4.5  | Simulation and measurement results of N-path notch filter with leak                |    |

|      | buffer circuit for power line frequency of 50Hz                                    | 52 |

| 4.6  | Simulation and measurement results of N-path notch filter with leak                |    |

|      | buffer circuit at frequency 60Hz                                                   | 53 |

| 4.7  | Relation between of switch off-resistance and notch depth with fre-                |    |

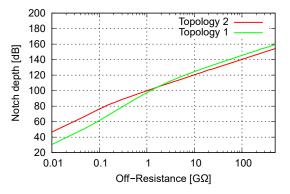

|      | quency 50Hz                                                                        | 53 |

| 4.8  | Comparison between Topology 1 and Topology 2 with N=10                             | 54 |

| 4.9  | Method of experiment investigation                                                 | 54 |

| 4.10 | Measurement result investigation in the ECG signal acquisition with-               |    |

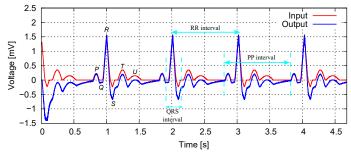

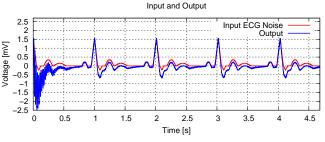

|      | out noise interference                                                             | 55 |

| 4.11 | Measurement result investigation in the ECG signal acquisition with                |    |

|      | noise interference                                                                 | 55 |

| 4.12 | Simulation investigation of N-path notch filter with leak buffer circuit           |    |

|      | by adding U wave                                                                   | 56 |

|      |                                                                                    |    |

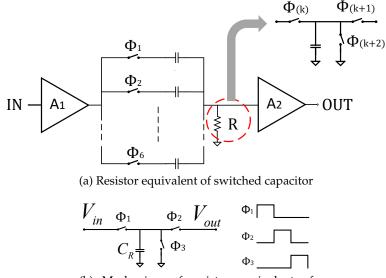

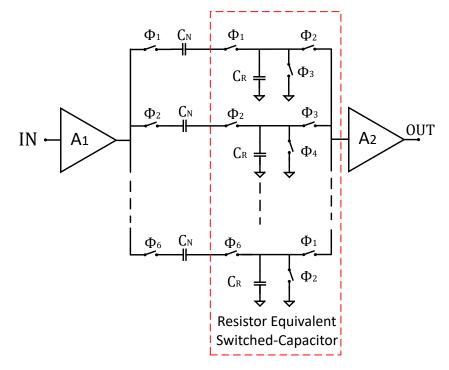

| 5.1  | Resistor equivalent of switched capacitor                                          | 60 |

| 5.2  | Topology 3 circuit                                                                 | 62 |

| 5.3 | Circuit in the first path of 4-phase N-path notch filter circuit when $\phi_1$ |    |

|-----|--------------------------------------------------------------------------------|----|

|     | is closed                                                                      | 63 |

| 5.4 | Implementation of resistor equivalent switched-capacitor in N-path             |    |

|     | notch filter with leak buffer circuit.                                         | 64 |

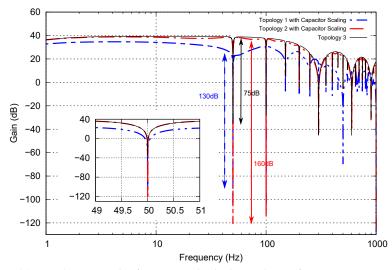

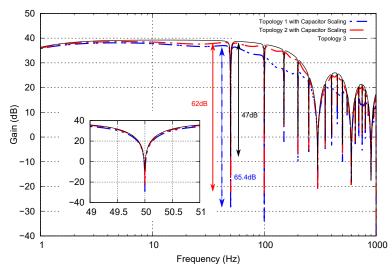

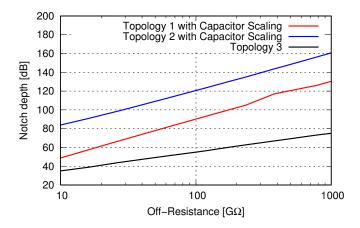

| 5.5 | Simulation result of Case 1 at frequency 50Hz                                  | 66 |

| 5.6 | Relation between notch depth and off-resistance in Case 1                      | 66 |

| 5.7 | Simulation result of Case 2 at frequency 50Hz                                  | 68 |

| 5.8 | Simulation result of Case 3 at frequency 50Hz                                  | 70 |

## List of Tables

| 1.1 | Biomedical signals frequency and amplitude                             | 2  |

|-----|------------------------------------------------------------------------|----|

| 2.1 | Comparison of analog notch filter                                      | 17 |

| 2.2 | Simulation and measurement condition of previous N-path notch filter   | 22 |

| 3.1 | Simulation conditions of ECG Body Model                                | 29 |

| 3.2 | Survey Participants                                                    | 40 |

| 3.3 | Simulation conditions of human body model                              | 42 |

| 4.1 | Simulation and measurement condition of N-path notch filter with       |    |

|     | leak buffer circuit                                                    | 52 |

| 4.2 | Comparison of other reports                                            | 57 |

| 4.3 | Comparison of input and output filter to other works                   | 58 |

| 5.1 | Simulation condition of Case 1 in N-path notch filter with capacitance |    |

|     | scaling                                                                | 65 |

| 5.2 | Simulation condition of Case 2 in N-path notch filter with capacitance |    |

|     | scaling                                                                | 67 |

| 5.3 | Simulation condition of Case 3 in N-path notch filter with capacitance |    |

|     | scaling                                                                | 69 |

| 5.4 | Simulation condition of Case 4 in N-path notch filter with capacitance |    |

|     | scaling                                                                | 69 |

| 5.5 | Comparison of N-path notch filter implementation                       | 71 |

|     |                                                                        |    |

## List of Abbreviations

| AFE   | Analog Front End                                 |

|-------|--------------------------------------------------|

| BOTA  | Balanced Operational Transconductance Amplifier  |

| СМ    | Common-mode                                      |

| CMOS  | Complementary Metal Oxide Semiconductor          |

| CMRR  | Common Mode Rejection Ratio                      |

| CSI   | Current Steering Integrator                      |

| CVDs  | Cardiovascular Diseases                          |

| DRL   | Driven Right Leg                                 |

| ECG   | Electrocardiogram                                |

| EEG   | Electroencephalogram                             |

| FIR   | Finite Impulse Response                          |

| FPGA  | Field Programmable Gate Array                    |

| Gm-C  | Operational Transconductance Amplifier Capacitor |

| IC    | Integrated Circuit                               |

| IIR   | Infinite Impulse Response                        |

| LC    | Inductor Capacitor                               |

| LPF   | Low Pass Filter                                  |

| LPN   | Low Pass Notch                                   |

| OTA   | Operational Transconductance Amplifier           |

| OTA-C | Operational Transconductance Amplifier Capacitor |

| S/H   | Sample and Hold                                  |

| SNR   | Signal to Noise Ratio                            |

| WHO   | World Health Organization                        |

|       |                                                  |

## **Physical Constants**

The unit capacitance of MIM capacitor  $= 1 fF / \mu m^2$

# **List of Symbols**

| Ω                                                              | Unit of resistance                                                                                          | ohm                                                              |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| F                                                              | Unit of capacitance                                                                                         | farad                                                            |

| f                                                              | Clock frequency                                                                                             | hertz (Hz)                                                       |

| $f_s$                                                          | Sampling frequency                                                                                          | hertz (Hz)                                                       |

| С                                                              | Capacitor                                                                                                   | farad (F)                                                        |

| $C_h$                                                          | Capacitor in S/H circuit                                                                                    | farad (F)                                                        |

| $C_L$                                                          | Capacitor in leak buffer circuit                                                                            | farad (F)                                                        |

| $C_N$                                                          | Capacitor in N-path core circuit                                                                            | farad (F)                                                        |

| $C_R$                                                          | Capacitor in resistor equivalent switched-capacitor                                                         | farad (F)                                                        |

| R                                                              | Resistor                                                                                                    | ohm (Ω)                                                          |

|                                                                |                                                                                                             |                                                                  |

| <i>R</i> <sub>off</sub>                                        | Switch off-Resistance                                                                                       | ohm (Ω)                                                          |

| R <sub>off</sub><br>R <sub>on</sub>                            | Switch off-Resistance<br>Switch on-Resistance                                                               | ohm (Ω)<br>ohm (Ω)                                               |

|                                                                |                                                                                                             |                                                                  |

| Ron                                                            | Switch on-Resistance                                                                                        | ohm (Ω)                                                          |

| R <sub>on</sub><br>v <sub>cm</sub>                             | Switch on-Resistance<br>Common-mode voltage                                                                 | ohm (Ω)<br>volt (V)                                              |

| R <sub>on</sub><br>v <sub>cm</sub><br>v <sub>p</sub>           | Switch on-Resistance<br>Common-mode voltage<br>Power line voltage                                           | ohm (Ω)<br>volt (V)<br>volt (V)                                  |

| R <sub>on</sub><br>v <sub>cm</sub><br>v <sub>p</sub><br>k      | Switch on-Resistance<br>Common-mode voltage<br>Power line voltage<br>Relative permittivity                  | ohm (Ω)<br>volt (V)<br>volt (V)<br><i>Fm</i> <sup>-</sup> 1      |

| R <sub>on</sub><br>v <sub>cm</sub><br>v <sub>p</sub><br>k<br>A | Switch on-Resistance<br>Common-mode voltage<br>Power line voltage<br>Relative permittivity<br>Area of plate | ohm ( $\Omega$ )<br>volt (V)<br>volt (V)<br>$Fm^{-1}$<br>$m^{2}$ |

### Chapter 1

### INTRODUCTION

#### 1.1 Research Background

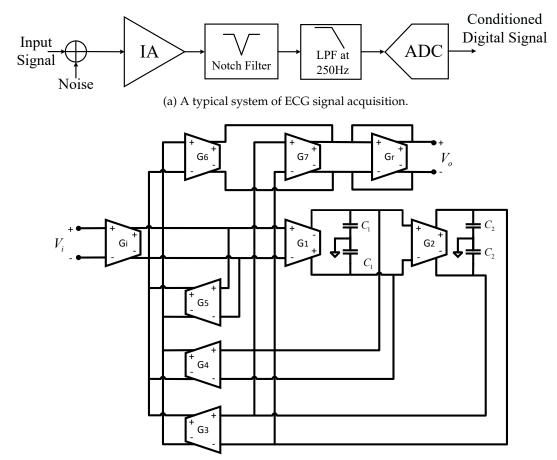

As data from the world health organization (WHO) in 2017 as shown in Fig. 1.1, cardiovascular diseases (CVDs) are the number one cause of death globally. An estimated in 2016, 9 million people in the world died cause of CVDs. Therefore, the prevention and diagnosis of cardiovascular disease become one of the primary issues for medician today. Furthermore, measuring body information continuously is very important to monitor the condition or abnormal function in the organ. With the introduction of prevention-oriented healthcare technologies, the realization of a portable device as shown in Fig. 1.2 for electroencephalography (EEG)/ electrocardiogram (ECG) recording is essential for monitoring body physiological signals from humans without restricting their mobility. Figure 1.2 shows ECG portable device. It can use wherever patients need to monitor their heart rate and can be seen on the computer.

However, bio-sensing activities such as ECG and EEG are challenging to obtain high-quality electrical signals because biomedical signals have small amplitude and low frequency. In the primary organ such as heart signal, the wrong diagnostic can make fatal to the patient. Accordingly, the reliability of biomedical signal acquisition is needed to minimize the wrong diagnosis. Table 1.1 shown a detail of frequency and amplitude from biomedical signals.

As shown in Table 1.1, a typical ECG potential on the body is about 0.1 - 5mV and frequency 0.05 - 150Hz. The common-mode noise such as power line noise contaminates ECG signal which has an amplitude in a common environment as large as

Source: Global Health Estimates 2016: Deaths by Cause, Age, Sex, by Country and by Region, 2000-2016. Geneva, World Health Organization; 2018.

Figure 1.1: Top 10 global cause of deaths, 2016.

Figure 1.2: ECG portable design.

Table 1.1: Biomedical signals frequency and amplitude

|           | ECG [1]      | EEG [2]    |

|-----------|--------------|------------|

| Frequency | 0.05 - 150Hz | 0.5 - 30Hz |

| Amplitude | 0.1 - 5mV    | 20-70 µV   |

a few millivolts up to tens of millivolts at a frequency 50Hz or 60Hz. It is envisaged that the power line interference is a significant noise source during physiological signal recording and is ubiquitous in most clinical situations. Power line noise could be easily picked up through electrode cables, electrical devices and the patient being monitored.

Common-mode noise reduction has been recognized as important research. The

techniques to reduce common-mode noise use differential amplifiers with CMRR higher than 80dB, but it has a problem if there is different values of impedance between two electrodes. The other proposed are shielding, isolation, and driven right leg (DRL) configuration. The DRL techniques effective to reduce the influence of stray currents through the body. However, noise still appears even measurement used the DRL circuit.

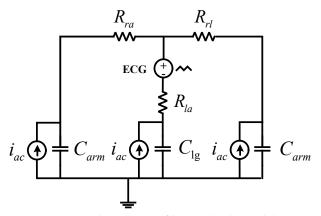

As shown in Table 1.1, the other techniques to suppress common-mode noise have been proposed by using analog and digital notch filters. The signal-to-noise ratio (SNR) calculation between power line noise's amplitude and biosignal's amplitude as shown in Table 1.1, shows that the minimum notch depth for ECG and EEG are 30dB [3] and 40dB [4] respectively.

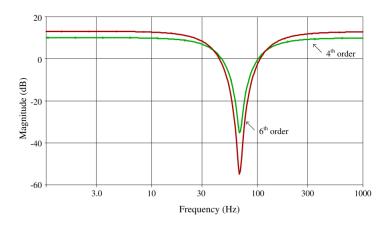

The solution using digital signal processing [5] and IIR digital notch filters [6] have been proposed. However, these techniques require an AFE with a wide dynamic range because it processes the input signal, including noise in the digital domain. The other techniques using analog notch filters such as low-pass notch filter (LPN) [2] and Gm-C notch filter [7] have been proposed to suppress power line interference. The techniques with LPN filter performed 66dB attenuation in the simulation and experiment; however, this circuit only uses in EEG signal acquisition. The solution with 6<sup>th</sup>-order Gm-C notch filter achieved a 68dB notch depth in the experiment, but the circuit needs sixth-order OTAs which consumes power. The previous techniques to suppress power line interference use N-path notch filter as described in [4] and [8]. However, the technique from [4] requires around  $3G\Omega$  switches off-resistance to reach a 40dB notch depth.

#### **1.2 Research Questions**

In the biomedical signal acquisition, common-mode noise has become an interference to obtain a high-quality signal. One technique to suppress common-mode noise uses the DRL circuit. It was significant and effective to suppress common-mode noise. However, in the actual ECG measurements using DRL circuit, sometimes noise still appears at the output. The other techniques to suppress common-mode noise have been proposed as described in section 1.1. The previous works [4] to suppress power line interference used N-path notch filter. However, the circuits assume impractical switch off-resistance ( $1T\Omega$ ) or need a higher number of path to obtain a sufficient notch depth.

Several research questions that would arise when designing biomedical signal acquisition system are listed below:

- Why does noise still appear even though the measurement is done using DRL circuit?

- What is the appropriate design for practical implementation of N-path notch filter to suppress common-mode noise?

#### **1.3 Problem Statement**

Driven right leg circuit has been proposed to reduce common-mode noise in the [9]. It described mismatching in the electrode impedance makes an impact to convert common-mode noise into a differential input voltage. However, the body is expressed as a single node and cannot be used to simulate the effect of the electrode impedance mismatch. As a result, the reason why power line, electrode impedance, patient skin, etc. can interference biomedical signal acquisition can be express with a new body model. Therefore, a new body model is needed to be able to analyze the effect of electrode impedance mismatch and other problem with common body model.

Another technique to suppress common-mode noise used a digital notch filter, but it requires an analog front-end with a wide dynamic range since the noise contaminated input signal need to be converted to digital signal. The methods with LPN filter performed 66dB attenuation of power line interference in the simulation and experiment; however, this circuit only can be used in EEG signal acquisition. The solution with Gm-C notch filter achieved a 68dB attenuation of power line interference in the experiment with sixth-order OTAs. Therefore, this technique requires more components and power consumption. The previous N-path notch filters [4] and [8] require  $3G\Omega$  switches off-resistance and 18 paths to reach 40dB notch depth. The problem to implement previous N-path notch filter is the difficulty in implementing switch with off-resistance. On-chip implementation of the system is also a challenge in the realization of portable ECG devices because the notch filter has a large time constant in which requires large capacitance and high resistance.

#### **1.4 Research Objectives**

The objectives of this research are as follows:

- To propose a body model with the DRL circuit that can express the effect of skin-electrode impedance to the output signal

- To propose N-path notch filter topologies which are suitable for practical realization either using discrete components or fully on-chip implementations.

#### **1.5** Scope of Work

The scopes of the research are listed below:

- The verification of a new body model to be used in the analysis of the impact of electrode impedance mismatching and patient skin impedance.

- The design and verification of N-path notch filter to suppress common-mode noise in ECG signal acquisition with a suppression level of at least 40dB.

- The design of a fully on-chip N-path notch filter for common-mode noise suppression in ECG signal acquisition.

#### **1.6** Significance of the Research

As described in the previous section, cardiovascular diseases are the number one cause of death globally. Therefore, the prevention and diagnosis of cardiovascular disease become one of the primary issues for medician today. Furthermore, measuring body information continuously is very important to monitor the condition or abnormal function in the organ. Common-mode noise makes interference causes noise appear in the output signal and reduce the signal quality. Furthermore, the complexity of biological tissue, which makes modeling of skin-electrode impedance very hard increases the difficulties in the analysis of problems in the biomedical measurement systems. Therefore, this research aims to the realization of a portable device with N-path Notch filter to suppress power line interference for electroencephalography (EEG)/ electrocardiogram (ECG) recording. It is essential for monitoring body physiological signals from humans without restricting their mobility. For the researcher, the new ECG body model can be used to find and analyze why is biomedical signal acquisition achieved poor signals and how to fix it.

#### **1.7** Thesis Organization

This thesis is organized into six chapters. Chapter two presents a collection of literature from previous research works to suppress power line interference in biomedical signal acquisition.

Chapter three discusses the proposed body model of biomedical signal acquisition to improve conventional body model of DRL circuit and also describes measurement skin-electrode impedance on the patient. Chapter four describes the proposed N-path notch filter with leak buffer circuit to reach notch depth at least 40dB. Chapter five focuses on the scaling capacitor in N-path notch filter circuit because the proposed N-path notch filter with leak buffer circuit has a problem with the capacitor size when on-chip implementation. Chapter six concludes this research. Additionally, several ideas for future works are also proposed.

## Chapter 2

## LITERATURE REVIEW

In the biomedical signal acquisition, common-mode (CM) noise is one of critical problems to obtain a high-quality biomedical signal. This chapter focuses on a review of previous techniques to reduce common-mode noise with driven right leg circuit, digital notch filter, and analog notch filter. The method to suppress common-mode noise, especially power line interference in digital notch filters used IIR and FIR notch filter. In the analog filters, a low-pass notch filter [2] and Gm-C notch filter [7] are use to suppress power line interference. The other notch filter that can be used to suppress power line interference is N-path notch filter, which is build base on the switched high-pass filter. The signal to noise ratio (SNR) calculation between power line noise's amplitude and biosignal's amplitude as shown in Table 1.1, the minimum notch depth for ECG and EEG are 30dB [3] and 40dB [4] respectively. A power line interference suppression level of at least 40dB is required to guarantee the biosignal's quality.

## 2.1 Driven Right Leg Circuit

The common-mode noise, such as power line noise, could be easily picked up through electrode cables and the patient being monitored. Here are some interferences that can contaminate the ECG signal as described in [10]-[11]:

- 1. A magnetic field can pass to the loops formed by electrode leads and induce interference electric and magnetic fields (EMFs).

- 2. An electric field induces into the electrode leads to a displacement current that flows to earth through the skin-electrode impedance. This condition creates

a skin-electrode imbalance, therefore, result of common-mode to differentialmode conversion.

3. The current induced  $(i_d)$  into the patient creates a voltage between the two recording electrodes and is referred as common-mode voltage  $(v_{cm})$ . When the common-mode rejection ratio (CMRR) of the amplifier is not high enough, it makes common-mode noise appear in the output.

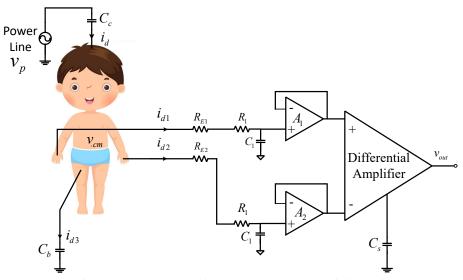

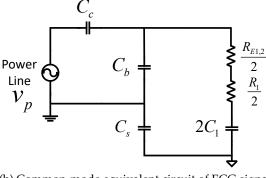

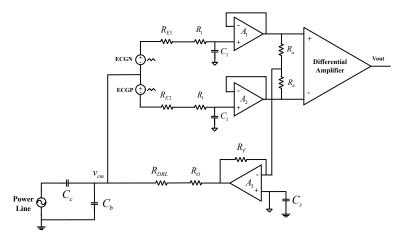

(a) ECG signal acquisition circuit with parasitic capacitors and electrode resistances.

(b) Common-mode equivalent circuit of ECG signal acquisition circuit.

Figure 2.1: ECG signal acquisition circuit with parasitic capacitors and electrode resistances and its equivalent circuit of common-mode voltage.

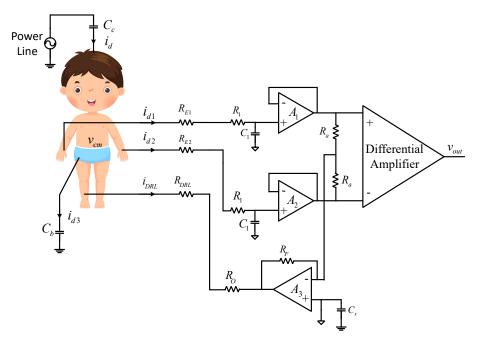

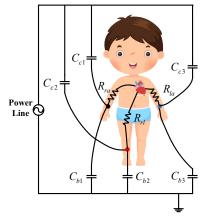

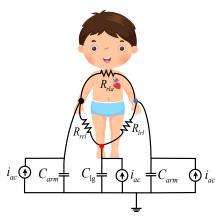

As a point of interference in the above, Driven Right Leg circuit with parasitic capacitors and electrode resistances can be illustrated as Fig. 2.1. There is small interference current to flow through the body because of stray capacitance between the patient, power line, and earth. The stray capacitance between the power line and the patient's body  $C_c$  is taken to be 2pF, and the stray capacitance between the

body and earth  $C_b$  is taken to be 200pF [9]. If the body connects with the electrode and ECG instrumentation, there is electrode impedance between the body and ECG instrumentation  $R_{E1,2}$  usually has value of 100k $\Omega$ . And also, there is the capacitance between the instrument amplifier (differential amplifier) and ground  $C_s$  is taken to be 200pF.  $R_1$  and  $C_1$  are low-pass filter that has a value of 1K $\Omega$  and 200pF respectively. The cut-off frequency of low-pass filter is 800KHz.  $A_1$  and  $A_2$  are amplifiers that are used as voltage buffers.

As shown in Fig. 2.1 (b), the common-mode voltage  $v_{cm}$  is given by

$$v_{cm} = \frac{(s^2\tau_0 + sC_3)sC_c}{((s^2\tau_0 + sC_3)sC_b) + ((s^2\tau_0 + sC_3) + s^2C_4)}v_p$$

(2.1)

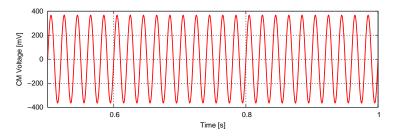

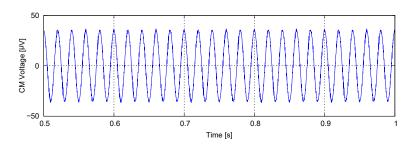

where  $v_p$  is power line voltage,  $\tau_0 = C_2 R_0$ ,  $C_2 = C_0 C_S$ ,  $R_0 = (R_1 + R_{E1,2})/2$ ,  $C_0 = 2C_1$ ,  $C_3 = C_s + C_0$ , and  $C_4 = C_1 C_s$ . Using the value of stray capacitance and resistance that described above, then the value of  $v_{cm}$  is 331mV with the amplitude and frequency of  $v_p$  is 141V and 50Hz, respectively. The simulation result of Fig. 2.1 shown in Fig. 2.2.

Figure 2.2: Simulation resul of common-mode voltage from Fig. 2.1.

As described in [12], there are two causes why common-mode voltage can appear at the output of ECG instrumentation. The first cause is the limited common-mode rejection ratio (CMRR) of the differential amplifier. The minimum requirement of differential amplifier CMRR in ECG signal acquisition is 80dB, hence this limit is not often problematic because in most cases the CMRR of differential amplifier is higher than 80dB. The second cause is mistmatch in electrode impedance ( $R_{E1,2}$ ) which converts common-mode voltage into a differential input voltage. This is also known as " the potential divider effect " [9].

The techniques to reduce common-mode voltage are shielding, isolation, and

driven right leg (DRL) configuration. Shielding combined with guarding techniques is a proper technique to prevent interference currents, but most of the commercially available electrode systems do not provide standard shielded. The good isolation can be improved with isolation between the device ground and the earth. However, low capacitances are usually not easy to achieve, and isolation must be improved patient safety [12]. More effective to reduce common-mode voltage is by placing a third electrode on the patient, to provide a low-impedance path to ground for displacement current. However, the third electrode cannot be connected directly to the ground because the patient must be protected from any currents higher than  $20 \,\mu$ A.

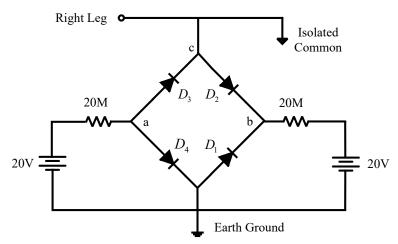

Figure 2.3: Grounding circuit to reduce common-mode voltage

The other way to reduce common-mode voltage by placing the third electrode with the circuit shown in Fig. 2.3, which makes node **c** as a virtual ground. To keep the currents under 1  $\mu$ A, diodes  $D_1$  and  $D_4$  conduct and clamp node **a** and **b** potentials close to the ground. The impedance from node **c** to the ground is the forward bias resistance of diodes  $D_2$  and  $D_3$  plus the forward bias resistance of  $D_1$ and  $D_4$ . The impedance to ground is typically around 150 k $\Omega$ . However, to reach currents above 1  $\mu$ A, diodes  $D_1$  and  $D_3$  are reverse biased, and the impedance to ground increases to 20M $\Omega$ .

The most effective way to connect the third electrode to the ECG instrumentation system is to use a driven right leg (DRL) circuit where it can reduce common-mode voltage to a few tenths of a millivolt. Figure 2.4 shows ECG signal acquisition with

(a) Driven Right Leg circuit with parasitic capacitors and electrode resistances.

(b) Common-mode equivalent circuit of the Driven Right Leg circuit.

Figure 2.4: Driven Right Leg circuit with parasitic capacitors and electrode resistances and its equivalent circuit of common-mode voltage.

the DRL circuit. As shown in Fig. 2.4, two resistors  $R_a$  are used to extract commonmode voltage from the differential input signals. The third amplifier  $A_3$ , which is connected to the right leg, amplifies common-mode voltage and inverts it. After that, it feeds common-mode voltage back to the body via the right leg electrode.  $R_o$  and  $R_{DRL}$  are current limiting and electrode-skin impedance in the DRL circuit, respectively. As described in [13], the transfer function from power line voltage  $v_p$  is given by

$$\frac{v_{cm}}{v_p} = K_c s \frac{\frac{(1+s\tau_0)R_S}{(1+s\tau_0)(1+s\tau_1)+s\tau_2}}{1+\frac{A(s)}{(1+s\tau_0)(1+s\tau_1)+s\tau_2}}$$

(2.2)

where  $R_0 = (R_1 + R_{E1,2})/2$ ;  $R_S = R_o + R_{DRL}$ ;  $C_0 = 2C_1$ ;  $\tau_0 = R_0C_0$ ;  $\tau_1 = R_SC_N$ ;  $\tau_2 = R_SC_0$ ; and also

$$K_c = \frac{C_c C_s}{C_s + C_c + C_b};\tag{2.3}$$

$$C_N = \frac{C_s(C_c + C_b)}{C_s + C_c + C_b}.$$

(2.4)

Figure 2.5: Simulation resul of common-mode voltage from Fig. 2.4.

As described before,  $A_3$  works as an inverting amplifier such that  $A(s) = -2(R_F/R_a)$ . Figure 2.5 shows simulation result of common-mode voltage and the value of  $v_{cm}$  is 35 µV. Comparing Figs. 2.5 and 2.2, the DRL circuit has a significant effect on reducing common-mode voltage. This result shows that the DRL circuit can effectively reduce common-mode voltage as far as the ECG amplifier is concerned and effectively ground the patient [14]. However, the DRL circuit has the stability problem of the right leg amplifier when using high gain. Circuit stability is dependent on a number of variables such as isolation capacitance and electrode resistances.

## 2.2 Digital Notch Filter

The application of digital filters has been growing since the advent of computing technology achieves cost-effective. The function of filters is to suppress the unwanted frequency signal. Based on their frequency response, filters are divided into low pass, high pass, bandpass, and bandstop filters. Out of these, the bandstop filter having a very narrow bandwidth is defined as the notch filter. This notch filter can be used to reduce common-mode noise, especially power line interference. The notch response from the notch filter removes interference from 50Hz/60Hz as power line frequency even in presences of the potential divider effect. It is more effective than the DRL circuit that has the stability problem of the right leg configuration, leading to much higher power line interference attenuation while maintaining low power consumption [15].

A digital notch filter can be implemented as Infinite Impulse Response (IIR) or Finite Impulse Response (FIR) filter. IIR filters are recursive filters that can give very narrow bandwidths but might be unstable under some conditions. On the other hand, FIR filters are non-recursive filters and cannot achieve bandwidth as narrow as IIR filters, but its a better stability and linear phase. IIR filters require lower orders to obtain narrower bandwidth at the notch frequency [16].

As described in [17], a second-order efficient digital IIR notch filter is designed to suppress powerline interference. The performance of the designed filter has been investigated with a ECG signal contaminated by a 50Hz pure sinusoid signal of 1mV on field-programmable gate array (FPGA) in the LabVIEW environment. In the implemented design on FPGA, a PSD of -26dB was obtained for ECG at 50Hz and -26dB for sinusoidal signals, respectively.

FIR filters with a linear phase property are used to obtain power line noise reduction without introducing the phase distortion [18]. In this design, the notch filter is implemented with a pole/zero canceling method, the comb notch filter with a pole/zero canceling method, and the equiripple notch filter with the usage of the Parks-McClellan algorithm. The equiripple notch filter effectively to reduce power line interference but require a higher-order filter. It achieved notch depth 93.5dB with 52<sup>th</sup> order FIR notch filter. A higher order filter uses more CPU time and consumes more power.

## 2.3 Analog Notch Filter

The techniques with digital notch filters such as IIR and FIR notch filters, which are described in the section 2.2, are useful when the powerline interference is smaller than the actual signal. However, the techniques with digital notch filters require an AFE with a wide dynamic range because it processes the input signal, including noise in the digital domain.

Figure 2.6: A 60Hz time contant multiplier notch filter with compensation circuit [19]

As described in [19], it design notch filter based on first-order all-pass networks uses time constant multiplication circuitry to achieve large time constants using resistors and capacitors that can be integrated into the IC. This design used a time constant multiplier (TCM) with ten opamps, as shown in Fig. 2.6. The additional TCM compensator circuit is shown in Fig. 2.6 as (a) sign, gives a second-order transfer function that has two imaginary zero. The most noticeable of these second-order effects is due to the unity gain buffer's corner frequency. Not only does the TCM circuit reduce the 3-dB point of the low-pass, but it also decreases the buffer's corner frequency by the same factor. This effect causes the attenuation compensation stage to create an extra phase shift above the notch frequency. As a result, the highfrequency gain will fall off dramatically. A phase compensator must be added to fix gain degradation, as in Fig. 2.6 as (b) sign. By using chopper stabilized opamps with low noise and offsets, these filters can be designed to have a notch depth and dynamic range exceeding 60dB at 60Hz.

Figure 2.7: 5<sup>th</sup>-order single-ended low-pass notch filter circuit [2]

Figure 2.8: Measured frequency responses of 5<sup>th</sup>-order single-ended lowpass notch filter [2]

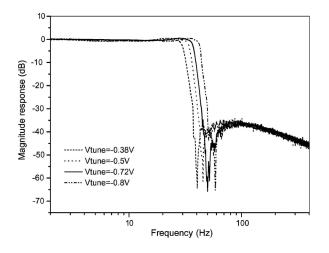

A CMOS continuous-time OTA-C low-pass notch filter for EEG application is described [2]. The single-ended low-pass notch filter design is based on a standard 5<sup>th</sup>-order elliptic LC-ladder prototype as shown in Fig. 2.7. All OTAs have the same transconductance and the value of capacitor range from 1 to 15pF. The elliptic filter has equal ripples in the pass-band and stop-band. The 5<sup>th</sup>-order elliptic filter has two finite zeros in the stop-band. The narrow notches appear in the frequency response of the filter at the null frequencies. To make the design less sensitive to paracitic capacitance and other parameters, the elliptic filter has been modified. The two notches of filter are design to be close enough so that the filter shows only one notch at 50Hz. The circuit achieved 66dB attenuation at frequency 50Hz as shown in Fig. 2.8. This circuit performed high notch depth in the simulation and experiment;

however, this circuit only can be used in EEG application.

A novel continuous-time notch filter based on the current steering integrator (CSI) technique was described in [20]. The second-order notch filter consisted of two integrators, one unity-gain inverter and two alpha blocks that were fully integrated onto a silicon chip. This proposed with 2<sup>nd</sup> order circuit achieved notch depth of 55.4dB at 50Hz in the simulation.

(b) Design of The fully differential notch filter with the added output circuitry of one balanced OTA (BOTA)

Figure 2.9: The fully differential notch filter with the added output circuitry of one balanced OTA (BOTA) [7].

The other work [21] uses a chopper notch filter, which is modified from a simple LC notch filter with the inductor *L* being implemented by active circuitry: transistor, resistor, and capacitor for silicon-area reduction. This circuit achieved notch depth of 41dB at 50Hz in the simulation. Another work [15] proposed a fully integrated notch filter based on Tow-Thomas Biquad with an active-RC. This design was replacing passive resistors by R-2R ladders for area-saving of approximately 120 times. It achieved a notch depth of 43dB (78dB for 4<sup>th</sup>-order).

An operational transconductance amplifier-C (OTA-C) notch filter with 6<sup>th</sup>-order cascaded filter for a portable Electrocardiogram (ECG) detection system proposed in [7]. This circuit used a design system and 6<sup>th</sup>-order notch filter circuit, as shown in Fig. 2.9. The 6<sup>th</sup>-order notch filter provides a notch depth of 65dB (43dB for 4<sup>th</sup>-order) as shown in Fig. 2.10. The adopted LPF filter must be capable of attenuating the out of band interference and suitable for ECG signal characteristics. Therefore, a 5<sup>th</sup>-order OTAC Butterworth LPF that was designed precisely to meet the ECG detection system criteria with a cut-off frequency of 250Hz is selected. However, this design requires more components and consumes more power. Table 2.1 shows a comparison of the analog notch filters.

Figure 2.10: Measured result of fully differential notch filter with the added output circuitry of one balanced OTA (BOTA) [7].

| Ref.        | [19]    | [2]     | [20]                      | [21]    | [15]                    | [7]                     |

|-------------|---------|---------|---------------------------|---------|-------------------------|-------------------------|

| Technology  | 2 µm    | 0.35 µm | 0.18 µm                   | 90nm    | 0.18 µm                 | 0.25 µm                 |

| Frequency   | 60Hz    | 50Hz    | 50Hz                      | 50Hz    | 60Hz                    | 50-60Hz                 |

| Stucture    | Chopper | OTA-C   | CSI                       | Chopper | R-2R                    | OTA-C                   |

| Notch depth | 60dB    | 66dB    | 55.4dB (2 <sup>nd</sup> ) | 41dB    | 78dB (4 <sup>th</sup> ) | 68dB (6 <sup>th</sup> ) |

| Result      | Sim.    | Exp.    | Sim.                      | Sim.    | Exp.                    | Sim.                    |

Table 2.1: Comparison of analog notch filter

## 2.4 N-path Notch Filter

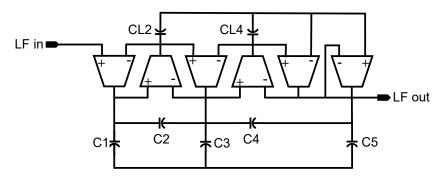

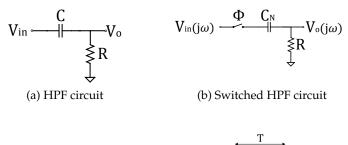

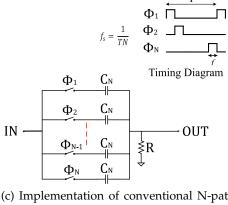

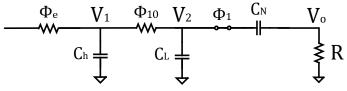

Another technique to suppress power line interference is N-path notch filter. The conventional N-path notch filter is implemented by a switched high-pass filter (HPF) [8] as shown in Fig. 2.11 (c) which is base on HPF circuit as shown in Fig. 2.11 (a). By

switching the capacitors, each of capacitors only connects to the input in a limited period (T/N) where T is the clock period and N is the number of path. As a result, each of capacitors will only have a constant part of the input signal as its input when the input signal frequency is equal to the clock frequency or its harmonics. Thus, the signal transfer from the input to the output is reduced to create notch characteristics on the transfer function.

(c) Implementation of conventional N-path notch filter

Figure 2.11: Conventional N-path notch filter.

As described in [4] the output voltage of  $V_o(j\omega)$  as shown in Fig. 2.11 is given by

$$\begin{split} V_o(j\omega) &= V_i(j\omega) - V_{Cs}(j\omega) \\ &= V_i(j\omega) - \sum_{k=-\infty}^{\infty} H_k(j\omega) V_i(j(\omega - k\omega_s)) \\ &= (1 - H_0(j\omega)) V_i(j\omega) - \sum_{k=-\infty, k\neq 0}^{\infty} H_k(j\omega) V_i(j(\omega - k\omega_s)) \end{split}$$

where  $V_{Cs}(j\omega)$  is the voltage across capacitor  $C_s$ . For an N-path, the transfer function for each harmonics  $H_k(j\omega)$  is

$$H_k(j\omega) = \sum_{l=1}^{N} e^{(jk\omega_s \delta_l)} H_{k,l}(j\omega)$$

(2.5)

where  $H_{k,l}(j\omega)$  is the *k*-th order harmonic transfer function of *l*-th path. In other words,  $H_{k,l}(j\omega)$  is the transfer characteristic around  $k \times f_s$  harmonic where  $f_s = 1/T_s$  is the clock frequency of switches. In case of a single-end topology,

$$H_{k,l}(j\omega) = \frac{1 - e^{-jk\omega_s\tau_l}}{j2\pi k(1 + j\omega/\omega_{rc,l})} + \frac{1 - e^{-j(\omega - k\omega_s)(T_s - \tau_l) - jn\omega_s\tau_l}}{2\pi\omega_{rc,l}/\omega_s(1 + j\omega/\omega_{rc,l})}G(j\omega)$$

$$G(j\omega) = \frac{e^{j(\omega - k\omega_s)} - e^{-\omega_{rc,l}\tau_l}}{e^{j2\pi(\omega - k\omega_s)/\omega_{rc}} - e^{-\omega_{rc,l}\tau_l}}x\frac{1}{1 + j(\omega - k\omega_s)/\omega_{rc,l}}G(j\omega)$$

(2.6)

$\omega_{rc,l} = 1/(RC_l)$  and  $\tau_l$  is the aperture (the period where the switch is truned on) of switch  $\Phi_l$ . Finally,  $H_0(j\omega)$  is given by

$$H_{0}(j\omega) = (1 - ND) + \frac{N}{1 + j\omega/\omega_{rc}} \left( D + \frac{1 - e^{j\omega(T_{s} - \tau)}}{2\pi\omega_{rc}/\omega_{s}} x \left( \frac{e^{j\omega\tau} - e^{\omega_{rc}\tau}}{e^{j2\pi\omega/\omega_{s}} - e^{-\omega_{rc}\tau}} \frac{1}{1 + j\omega/\omega_{rc}} \right) \right)$$

$$(2.7)$$

where  $C_1 = ... = C_N = C/N$ ,  $\omega_{rc} = N/(RC)$ ,  $\tau_1 = ... = \tau_N = DT_s$  and *D* is the clock duty ratio. Assuming  $\omega_s \gg \omega_{rc}$  and D = 1/N, the notch depth  $H_N$  of the N-path notch filter appoximately

$$H_N \approx 1 + \frac{N \sin^2(\pi D) + D\pi^2(1 - ND)}{N((D\pi)^2 - \sin^2(\pi D))}.$$

(2.8)

If D = 1/N then

$$H_N \approx 1 + \frac{N^2 \sin^2(\frac{\pi}{N})}{\pi^2 - N^2 \sin^2(\frac{\pi}{N})} = \frac{1}{1 - \operatorname{sinc}^2\left(\frac{1}{N}\right)}$$

(2.9)

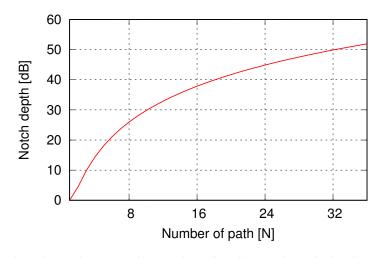

where  $\operatorname{sin}(x) = \frac{\operatorname{sin}(\pi x)}{\pi x}$ . For larger *N*,  $\operatorname{sinc}(1/N)$  approaches 1 and  $H_N$  increases rapidly. From Eq. (2.9), the relation between the number of path *N* and notch depth  $H_N$  is illustrated in Fig. 2.12. As described at introduction, a minimum power line interference attenuation of 40dB is necessary. Therefore, the convention N-path notch filter requires at least *N* = 18 to achieve notch depth of 40dB.

Figure 2.12: The relation between the number of path *N* and notch depth  $H_N$  in the conventional N-path notch filter.

## 2.5 Previous Work on N-path Notch filter

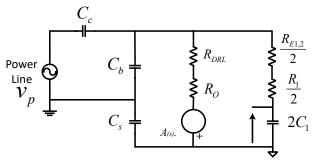

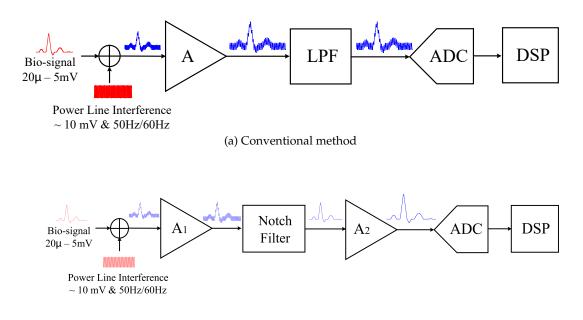

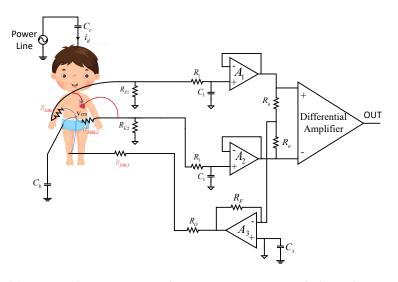

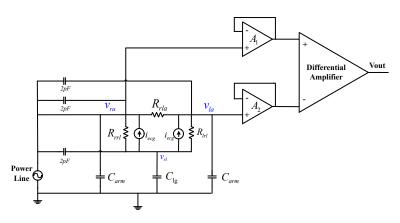

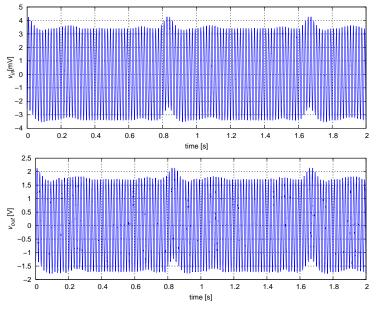

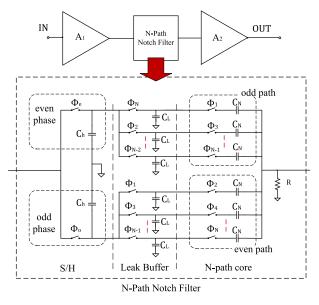

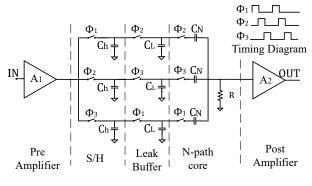

Figure 2.13 (a) shows a typical AFE for signal acquisition, which is less efficient in filtering power line interference because power line interference exists in the output of the filter [22]. While this approach is suitable for filtering high-frequency noise, the signal that goes to ADC still has power line interference component. It is amplified by the high gain amplifier, decreasing the number of effective bits of ADC which are consumed by the noise. Figure 2.13 (b) shows the system method, using N-path notch filter, which ensures the hum noise reduction from the signal before A/D conversion. The pre-amplifier ( $A_1$ ) is introduced to make sure the signal reaches an appropriate voltage level, while also amplified the hum noise which will be removed in the next stage. The post-amplifier ( $A_2$ ) amplifies the signal which has the hum noise suppressed by notch filter.

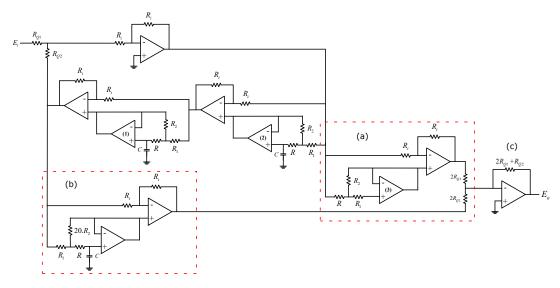

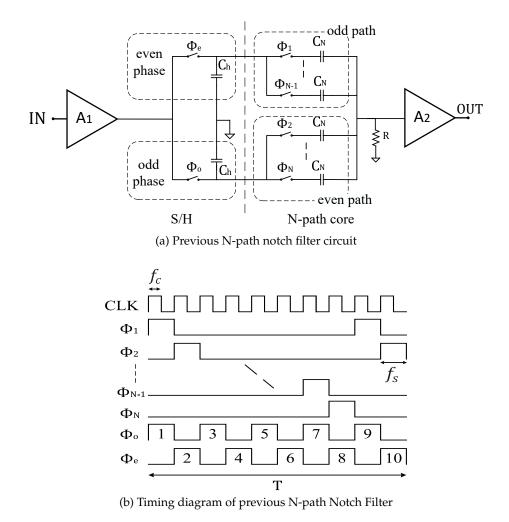

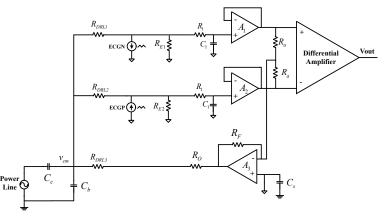

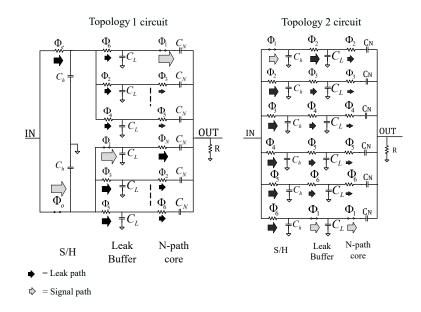

The notch filter is implemented using an N-path notch filter circuit, which is shown in Fig. 2.14 (a). The previous N-path notch filter circuit is implemented by adding a sample-and-hold (S/H) circuit before conventional N-path notch filter, as described in the section 2.4. Two S/H circuits are added at the front of the N-path notch filter to hold the input signal at the even and odd phase of the N-path core circuit sequentially. The even phase of the S/H circuit is connected to the odd paths of the N-path filter core and vice versa. As a result input signal will be held by S/H circuit before passed it into N-path core circuit. Therefore, the input signal in this circuit is a discrete-time signal.

#### (b) Proposed method

Figure 2.13: Analog front-end for biomedical signals acquisition

The even paths is defined by switching frequency  $\phi_N$  where N = [1, 3, ..., N - 1] while the odd paths is defined where N = [2, 4, ..., N]. Figure 2.14 (b) shows an example of timing diagram with a number of paths are 10. As shown in timing diagram, frequency of the clock  $f_c$  is half of sampling frequency of each path  $f_s$  or  $f_c = 1/2TN$ .

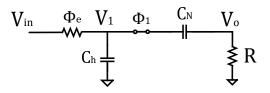

Figure 2.14a shows when  $\phi_o$  and  $\phi_1$  of the switch are close. The opened switches are represented by their off-resistance. The transfer function of this mechanism is given by

$$\frac{V_o}{V_{in}} = \frac{s\tau_1}{s^2\tau_1\tau_3 + s\tau_3 + s\tau_2 + 1}$$

(2.10)

where

$$\tau_1 = C_N R$$

$$\tau_2 = C_N R_{off}$$

$$\tau_3 = C_h R_{off}.$$

(2.11)

*R*<sub>off</sub> is switches off-resistance when switch is opened.

Simulation and measurement conditions of previous N-path notch filter shows

Figure 2.14: The conventional of 10-phase N-path notch filter [4]

Table 2.2: Simulation and measurement condition of previous N-path notch filter

| Parameter | Value      |  |

|-----------|------------|--|

| N         | 10         |  |

| BW        | 2Hz        |  |

| $C_h$     | 1μF        |  |

| $C_N$     | 15nF       |  |

| R         | $1M\Omega$ |  |

| $A_1$     | 20dB       |  |

| $A_2$     | 20dB       |  |

| Switches  |            |  |

| Ron       | $35\Omega$ |  |

| Roff      | 80MΩ       |  |

|           |            |  |

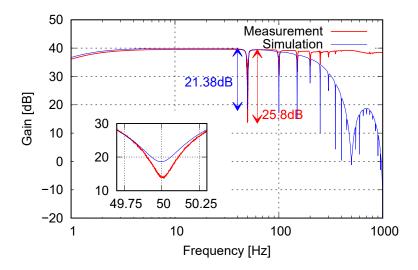

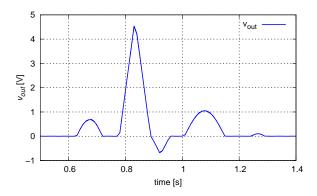

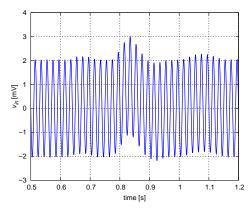

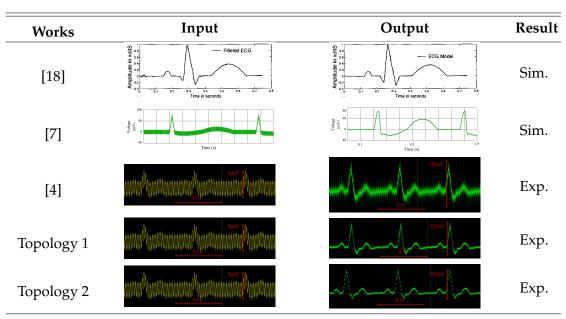

in Table 2.2. Figure 2.16 shows simulation and measurement result of previous N-path notch filter. It shows a notch depth of 21dB in the simulation and 25dB in measurement at 50Hz.

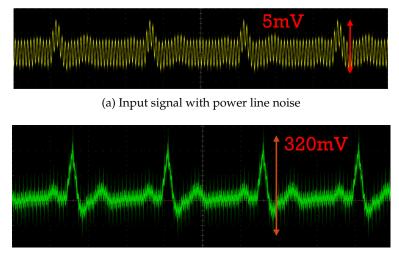

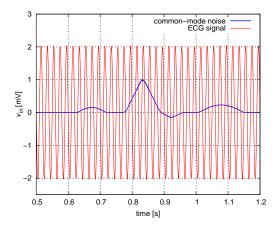

Figure 2.17 shows measurement investigation of previous N-path notch filter. In

Figure 2.15: Mechanism in the first path when  $\phi_o$  and  $\phi_1$  are closed

Figure 2.16: Simulation and Measurement result of previous N-path notch filter at frequency 50Hz

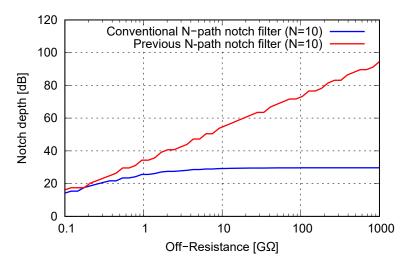

the measurement result, when the input signal is contaminated by power line noise with an amplitude ratio between the input signal and noise are the same as shown in Fig. 2.17 (a). The noise still appears in the output, as shown in Fig. 2.17 (b). It happened because of the value of switches off-resistance less than under 1G $\Omega$ . The filter achieved a notch depth around 20dB, as shown in Fig. 2.18. As shown in Fig. 2.18, the previous N-path notch filter needs to increase switch off-resistance at least to 3G $\Omega$  to reach notch depth of 40dB. It makes a problem if the previous N-path notch filter implemented with a discrete component because of the value of switch off-resistance is around a hundred ohms. Likewise, the conventional N-path notch filter as described in section 2.4 needs at least 18 paths to meet the target. Therefore, both circuits are less efficient in suppressing power line noise.

## 2.6 Conclusion

Common-mode noise is one of the critical problems in biomedical signal acquisition. The DLR circuit has a significant effect of lowering common-mode noise. However,

(b) Output signal of previous N-path notch filter

Figure 2.17: Measurement investigation of previous N-path notch filter circuit

Figure 2.18: The simulation result of relation between switch off-resistance and notch depth in conventional circuit.

the DRL circuit has a stability problem when the gain in the third amplifier is too high. Notch response from the notch filter removes interference from 50Hz/60Hz even in presences of the potential divider effect caused by the mismatch between two electrodes impedance. The notch filter can be implemented either using digital or analog filters.

The techniques with digital notch filters such as IIR and FIR notch filters are useful when the powerline interference is smaller than the actual signal. The techniques with digital notch filters require an AFE with a wide dynamic range because it processes the input signal, including noise in the digital domain. The analog notch filter, such as with Gm-C and Chopper opamp, achieved higher notch depth compared to IIR notch filter. However, it requires more components. The conventional and previous N-path notch filters depend on a high number of paths or high switches off-resistance to 40dB.

## Chapter 3

# INVESTIGATION ON BIOMEDICAL BODY MODEL

Most of the medicians have experience when biomedical instrumentation cannot read body signals. When it happened, they try to fix the problem by adjusting the biomedical signal monitor to replacing all the electrodes, lead wires or cables and even call biomedical engineering to fix it. All of that takes time, increases costs, adds more staff, and sometimes makes patient frustration or may place the patient at risk.

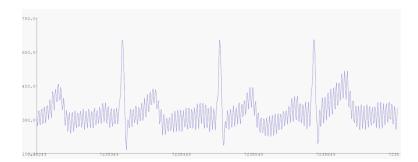

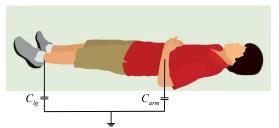

As described in chapter 1, the DRL circuit effectively reduces common-mode voltage. However, sometimes noise still appears even ECG instrumentation such as AD8232 used DRL circuit, as shown in Fig. 3.1. And also, as described in [23], a new survey shows lowering patient skin impedance can significantly reduce biomedical signal artifacts because the skin contributes to noise or artifact associated with electrode impedance. However, the common biomedical body model assumed the body as express a single node. Another problem with the common biomedical body model is when there is a difference between the two electrodes impedance in the left and right arm, the output of the body model still noise-free signal. However, the difference between the two electrodes impedance in the left and right arm, the output of the body model still noise-free signal. However, the difference between the two electrodes impedance will convert the common-mode noise into the differential input voltage makes noise appear at the output.

This chapter will describe a proposed body model to find the detail of how power lines, electrode impedance, patient skin, etc. can cause interference with biomedical signals and how it affects the output of the signal. In this chapter, the biomedical signal acquisition that will be used is the ECG signal acquisition. However, the methods and calculations outlined here are not restricted to ECG signal acquisition

Figure 3.1: Measurement result of ECG instrumentation using DRL circuit

and could be applied to any biomedical signal acquisition system.

## 3.1 Improved ECG Body Model with DRL Circuit

Figure 3.2: Simulation circuit of Driven Right Leg circuit with parasitic capacitors and electrode resistances as shown in Fig.2.4 (a)

Figure 3.2 shows a circuit for the simulation of ECG acquisition with the DRL circuit. As described in section 2.1, stray capacitance, electrode impedance, DRL circuit, etc. have an impact on the output signal. There are two types of ground in this biomedical signal acquisition with or without the DRL circuit. The first is the earth as the global ground of the measurement system and the second is the device ground. The device ground is connected to the earth with a capacitor of a few pF. The two voltage sources (ECGP and ECGN) are put before the left and right electrode impedance as a biomedical signal. However, this circuit cannot express why body model components have an impact on the output signal. It is because of the value of lowpass filter between  $R_{E1}/R_{E2}$ ,  $R_1$ , and  $C_1$ . If the value of  $R_{E1} = R_{E2} = 100 \, k\Omega$  so it achieve cut-off frequency 7.2 kHz and it is higher than 50 Hz. Therefore,

it makes the output of the DRL circuit is a noise-free signal. If  $R_{E1} = 10k\Omega$  so that the cut-off frequency is 40kHz and it still higher than 50Hz, that makes the output of the DRL circuit is a noise-free signal. The cut-off frequency will smaller than 50Hz that makes noise appear in the output if  $R_{E1} = 10M\Omega$ . However, the maximum value  $R_{E1}/R_{E2} = 2M\Omega$ .

Therefore, this section introduces an improved body model to investigate from the biomedical body model how the mismatch between electrode impedance would convert common-mode noise into differential input voltage and how much gain needed in differential and feedback amplifiers. Since the output of a biomedical signal is in millivolts or microvolts range, the voltage gain value of the differential amplifier should be high. The feedback amplifier is used to keep common-mode voltage as small as possible.

Figure 3.3 (a) shows an improved circuit model including skin impedances for driven right leg circuit with parasitic capacitors and electrode resistances. In the improved DRL circuit, biomedical signal is expressed by current source in parallel with electrode impedance  $R_{E1,2}$ . Meanwhile, Fig. 3.3 (b) shows simulation circuit using the improved DRL circuit. Figure 3.4 shows the output of ECG signal acquisition with simulation condition that is shown in Table 3.1. There is noise in the output, but it is not visible because it is too small (around 2.4mV when output signal is 4.5V) if compared with output voltage.

Table 3.1: Simulation conditions of ECG Body Model

| Parameter                 | Value                 |

|---------------------------|-----------------------|

| v <sub>p</sub>            | 141V                  |

| Frequency                 | 50Hz                  |

| $C_c$                     | 2pF                   |

| $R_{E1}, R_{E2}, R_{DRL}$ | $100k\Omega$          |

| $R_1, R_a, R_o$           | $10 \mathrm{k}\Omega$ |

| $C_1, C_b, C_s$           | 200pF                 |

| $R_F$                     | $1M\Omega$            |

| Diff. Amp.                | 60dB                  |

| $A_3$                     | 60dB                  |

|                           |                       |

(a) Improved DRL circuit with parasitic capacitors and electrode resistances.

(b) Simulation circuit of improved DRL circuit with parasitic capacitors and electrode resistances.

Figure 3.3: Proposed DRL circuit with parasitic capacitors and electrode resistances and its simulation circuit.

### 3.1.1 Electrode Impedance

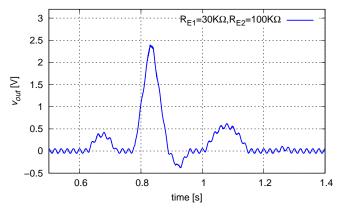

As described in Chapter 2, mismatch between electrode impedance converts commonmode voltage into differential voltage. However, simulation result with common ECG signal acquisition with DRL circuit as shown in Fig. 3.4, shows that the output is noise-free signal. A severe mismatch in the electrode impedances causes the potential to be higher at one input than the other [12]. That problem makes commonmode noise appears at the output. Figure 3.5 shows simulation result, when the value of  $R_{E1} = 30k\Omega$ ,  $R_{E2} = 100k\Omega$ , and  $R_{DRL} = 100k\Omega$  ( $R_{E2}$  match with  $R_{DRL}$ ). As shown in Fig. 3.5, there is noise at the output. The amplitude of common-mode voltage at the output is 40mV. It appears because the value of impedance from two

Figure 3.4: Output of ECG body model of ECG measurement using DRL circuit.

electrodes are mismatched. Even if this circuit use DRL circuit to reduce commonmode noise, the noise still appears at the output signal.

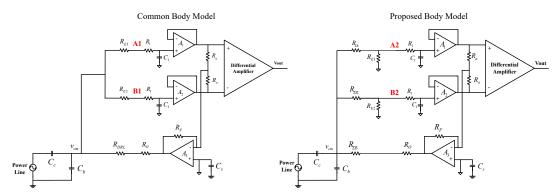

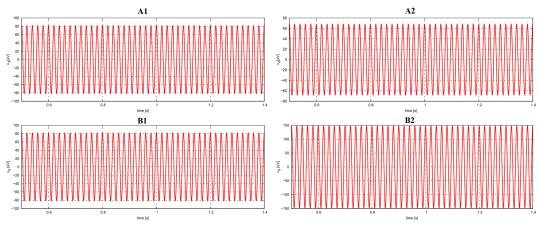

Figure 3.6 shows why the common body model cannot express the effect of electrode impedance mismatch that makes noise appear at the output, but the proposed circuit can express it. Figure 3.6 (a) shows circuit comparation with voltage and current sources are not added to each other. Figure 3.6 (b) show simulation result of voltage between nodes A1 and B1 are the same even  $R_{E1}$  and  $R_{E2}$  mismatch each other. While the voltage between the nodes A2 and B2 is not the same, it proves why the noise appears in the output signal.

Figure 3.5:  $v_{out}$  when  $R_{E1} = 30 \text{K}\Omega$  and  $R_{E2} = 100 \text{K}\Omega$

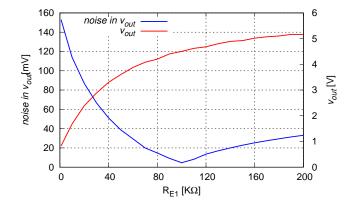

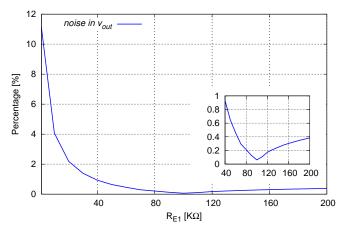

Figure 3.7 (a) shows relation between one of electrode impedance in the arm  $(R_{E1} \text{ or } R_{E2})$  with  $v_{out}$  and noise in the output. The condition of that figure is the same as the previous simulation. The difference is this simulation sweep the value of impedance  $R_{E1}$  to see the result if mismatch between two electrodes increases. As shown in Fig. 3.7, increasing the value of mismatch (a gap between  $R_{E1}$  and  $R_{E2}$ ), will increase the common-mode noise in the output. Increasing the value of  $R_{E1}$  or

(a) Circuit design for comparation the effect of electrode impedance mismatch between common and proposed ECG signal acquisition with DRL circuit.

(b) Simulation result of comparation the effect of electrode impedance mismatch between common and proposed ECG signal acquisition with DRL circuit.

Figure 3.6: Comparation the effect of electrode impedance mismatch between common and proposed ECG signal acquisition with DRL circuit.

$R_{E2}$  increase the output voltage magnitude. Fig. 3.7 (b) shows the percentage of noise in the output. If the maximum tolerance noise in the output is 1 percent of the desired signal, hence the maximum mismatch between two electrodes is 20K $\Omega$  ( $R_{E1}$  = 80K $\Omega$  and  $R_{E2}$  = 100K $\Omega$ ).

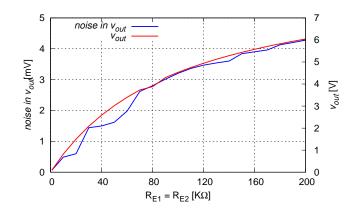

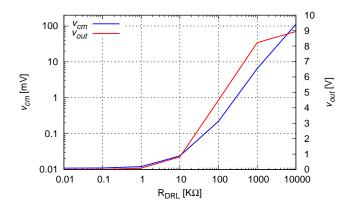

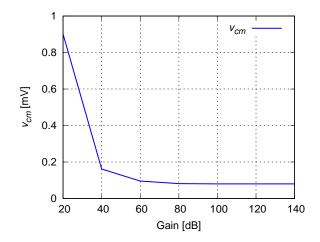

Figure 3.8 shows relation between  $R_{E1,2}$  and  $v_{cm} - v_{out}$ . The condition of this simulation is when  $R_{E1} = R_{E2}$  and  $R_{DRL} = 100$ k $\Omega$ . As shown in Fig. 3.8, noise in the output still small when the value of  $R_{E1}$  and  $R_{E2}$  are the same. If the value of  $R_{E1}$  and  $R_{E2}$  increase and match each other, then output voltage would increase.