## **Technical Disclosure Commons**

**Defensive Publications Series**

December 2020

# Readability Enhancements for Device Displays used in Bright-Lighting Conditions

Sangmoo Choi

Jyothi Karri

Follow this and additional works at: https://www.tdcommons.org/dpubs\_series

#### **Recommended Citation**

Choi, Sangmoo and Karri, Jyothi, "Readability Enhancements for Device Displays used in Bright-Lighting Conditions", Technical Disclosure Commons, (December 10, 2020) https://www.tdcommons.org/dpubs\_series/3871

This work is licensed under a Creative Commons Attribution 4.0 License.

This Article is brought to you for free and open access by Technical Disclosure Commons. It has been accepted for inclusion in Defensive Publications Series by an authorized administrator of Technical Disclosure Commons.

#### **Readability Enhancements for Device Displays used in Bright-Lighting Conditions**

#### Abstract:

This publication describes apparatuses for enhancing the readability of content on the display of a computing device when accessed by a user in bright ambient lighting conditions. In an aspect, the apparatus is a display panel configured to block ambient light from entering and/or being reflected out of vertical interconnect access (VIA) holes (e.g., reflective, electrical bridges that connect conductive layers within the device display) present in a layer of the display panel. To enhance display readability of content in bright ambient lighting conditions, VIA holes may be covered to enhance a display contrast ratio (e.g., the display luminance of a white image versus the display luminance of a black image). The display panel may include a metal or polymer layer positioned over VIA holes within the display layers (e.g., positioned on a layer of the display) and shaped to block reflected light but not block emissive light (e.g., from red/green/blue subpixels).

#### **Keywords:**

Vertical interconnect access (VIA) hole, VIA trench, VIA groove, block, limit, enhance readability, outdoor display, touch layer, luminance, brightness, visibility, device display, display panel, display structure, AMOLED, pixel, polarizer, lighting condition

#### **Background:**

Users frequently view the display screen of their computing device (e.g., smartphone) in bright ambient lighting conditions where readability of content on the display screen may be hindered by ambient light. For example, a smartphone may have a contrast ratio (e.g., the display luminance of a white image versus the display luminance of a black image) of 7,000,000:1 indoors, where the device is used in low levels of ambient light. However, the contrast ratio (C/R) may be reduced to 701:1 when used in bright ambient lighting conditions due to reflected light within the layers of the display panel, impacting the readability of the content on the display screen for the user.

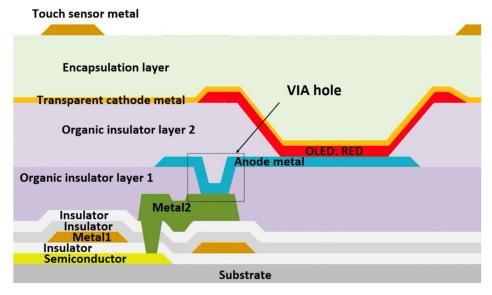

Red pixel cross-sectional view

## Figure 1

One source of reflected light may include internal reflections (e.g., diffuse reflections) from vertical interconnect access (VIA) holes in a display panel layer as illustrated in Figure 1. A VIA hole may be an electrical interconnection bridge between conducting layers, separated by an organic or polymer insulator layer(s). As illustrated in Figure 1, an example VIA hole connects an anode metal to a second metal across an organic insulator layer and may occur at least once per subpixel (e.g., red/green/blue subpixel). Incident ambient light upon the VIA hole may reflect back towards the source, decreasing the C/R of the display panel and accounting for up to 5% of internal reflections within the display panel. As a result, there are barriers to high readability of

content on display screens of computing devices when used in bright ambient lighting conditions by a user.

#### **Description:**

This publication describes apparatuses for enhancing the readability of content on the display of a computing device when accessed by a user in bright ambient lighting conditions. When a computing device is used in bright conditions, ambient light may be internally reflected off VIA holes, thereby reducing the C/R of the display and diminishing the readability of content on the computing device. The apparatuses described herein is configured to block ambient light (e.g., when the display is used in bright ambient lighting conditions by a user) from entering and/or being reflected out of VIA holes.

While the example computing devices described in this publication is a smartphone, other types of computing devices may also support the techniques described herein. A computing device may include one or more processors, transceivers, a computer-readable medium (CRM), and/or an input/output device (e.g., a display panel).

The display panel may be composed of a layered structure of one or more layers or groups of layers (collectively "layers"). For example, a display panel may include a pixel layer that includes light-emitting elements and a display backplane layer (e.g., a display backplane) for driving the light-emitting elements of the display panel. The display panel may be a flexible, organic, light-emitting, diode-based display. The layered structure may further include a substrate layer on which the display backplane of the display panel is formed (e.g., deposited). The substrate supports the display panel and provides mechanical stability. Furthermore, a display panel may include conductive layers (e.g., metal layers) electrically connected by VIA holes across an insulator layer(s). These VIA holes may include, for example, reflective materials (e.g., metals) and/or a non-uniform structure (e.g., a cavity).

The light-emitting elements of the display panel are configured to emit light to generate a display on the display screen of a computing device. The light-emitting elements may include, for example, one or more organic active layers (e.g., emitting layer, emissive layer, an array of organic light-emitting diodes), a cathode, and an anode deposited on the substrate. The layered structure of the display panel may include one or more other layers, for example, a touch layer (e.g., metal touch sensor panel) for detecting physical touch, a polarizer layer (e.g., polarization filter, polarizer film, circular polarizer) for reducing reflections, and an encapsulation layer (e.g., glass layer, glass substrate, window, film) for protecting one or more layers of the display device.

Even though some devices use an active-matrix organic light-emitting diode (AMOLED) display with high C/R, readability may still be reduced, for example, when a device is used in bright ambient lighting conditions. An AMOLED display includes an active matrix of organic light-emitting diode pixels that generate luminescence upon electrical activation and may be deposited on a thin-film transistor (e.g., a type of metal-oxide-semiconductor field-effect transistor comprising an active semiconductor layer, a dielectric layer, a metallic layer, and a non-conductive substrate like glass). While the example display panel in this publication is an AMOLED display panel, other types of display panels may support the apparatuses described herein. Examples of computing display panels may include, but are not limited to, organic light-emitting diode (OLED) display modules, light-emitting diode (LED) display modules, liquid crystal display (LCD) display modules, microLED display modules, display technologies with individually-controllable pixels, thin-film technology display modules, and the like.

The display panel described herein includes an optically opaque structure, located within one or more layers of a display panel and configured to block reflected ambient light from VIA holes. The optically opaque structure may include a metal layer, a polymer layer, or any reflecting surface that does not electrically affect the display mechanics.

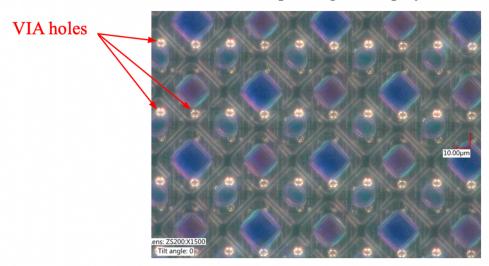

The display panel is further configured to prevent blockage of emissive regions of the display panel (e.g., the red/green/blue subpixel emissive regions). In aspects, the emissive regions may range in size, for example, from 10-30 microns in diameter, and the VIA holes may range in size from 3-4 microns in diameter as illustrated in Figure 2. The optically opaque structure may be configured to cover the diameter of a VIA hole without blocking luminance from subpixels on the display panel. For example, an optically opaque structure of diameter 2 microns may not cover the VIA hole sufficiently. Whereas, an optically opaque structure of diameter 50 microns, for example, may cover the VIA hole sufficiently but block emissive light from subpixels.

## Microscope image of display

## Figure 2

The optically opaque structure may be provided at various positions within one or more layers of the display panel, for example, within the touch sensor metal layer, underneath the touch sensor metal layer, above the touch sensor metal layer, directly on top of the cathode layer, on the encapsulation glass of rigid AMOLED displays, and the like. To reduce the distance between the optically opaque structure and the VIA hole, the optically opaque structure may be positioned on the cathode layer instead of the encapsulation layer. In this example, the optically opaque structure may need to have openings for emissive regions and the optically opaque structure is too large in diameter, it may cover an emissive subpixel and reduce the readability of content on the display screen.

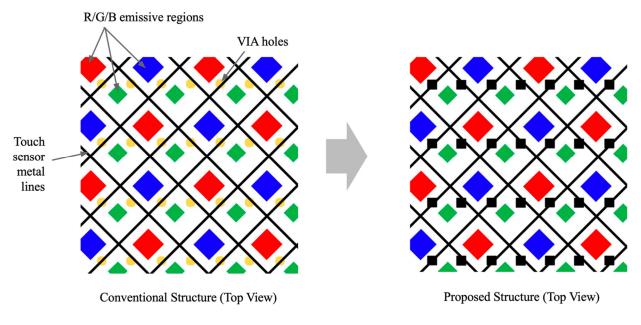

In an example, the structure may be positioned on the touch sensor metal layer. For flexible AMOLED displays, the touch sensor metal layer may be deposited on top of the thin-film encapsulation layer as illustrated in Figure 3. In this example, the touch sensor metal lines are positioned between red/green/blue emissive regions from subpixels without decreasing luminance. The VIA hole regions may be covered by a structure that includes a modified touch sensor metal pattern design, as illustrated in Figure 4, with additional metal covers at the position of each VIA hole. Preliminary data suggests this structure may reduce reflected ambient light by 5% and increase the C/R of a display from 700:1 (for a device used outside with uncovered VIA holes) to 738:1, a C/R increase of 5.2% without an additional increase of power consumption by the computing device.

In another example not illustrated, if the encapsulation layer includes a rigid material (e.g., glass) instead of a flexible material, the thickness of the encapsulation layer may increase (e.g., to 500 microns in thickness or more). If the structure is positioned on top of the encapsulation layer, the distance between the optically opaque structure and the VIA holes may be larger with the thick, rigid material than with the previous example of a flexible display panel. As the distance between

the optically opaque structure and the VIA holes increases, the efficiency of the optically opaque structure to block reflected light is reduced. For example, a display panel with an optically opaque structure positioned on top of a thick encapsulation layer may allow for ambient light to pass behind the optically opaque structure and be reflected back towards the source (e.g., the direction of the user). In this example, it would be better to move the optically opaque structure closer to the VIA holes (e.g., on a different layer of the display) to increase the C/R and enhance the readability of content on the display screen of the device in bright ambient lighting conditions.

Figure 3

Figure 4

## **References:**

[1] Patent Publication: US20100207860A1. Via Design for Use in Displays. Priority Date: February 13, 2009.

[2] Patent Publication: US20200273919A1. Display Panel and Display Apparatus. Priority Date: February 26, 2019.

[3] Patent Publication: US20170062547A1. Narrow Border Organic Light-emitting Diode Display. Priority Date: August 17, 2012.

[4] Patent Publication: KR20060124209A. Electron Emission Device and Method for Manufacturing the Same Capable of Obtaining Light Emitting Uniformity Among Pixels. Priority Date: May 31, 2005.

[5] Patent Publication: KR20120120098A. Cover Window One Body Style Touch Screen and Manufacturing Method. Priority Date: September 20, 2012.

[6] Patent Literature: US20020050958A1. Contrast enhancement for an electronic display device by using a black matrix and lens array on outer surface of display. Priority Date: February 17, 1998.