## Inline and Sideline Approaches for Low-cost Memory Safety in C

Myoung Jin Nam

Selwyn College

November 2020

This dissertation is submitted for the degree of Doctor of Philosophy

This thesis is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text. It is not substantially the same as any that I have submitted, or, is being concurrently submitted for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my thesis has already been submitted, or, is being concurrently submitted for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. This thesis does not exceed the regulation length of sixty thousand words.

#### Copyright © November 2020 by Myoung Jin Nam

#### Inline and Sideline Approaches for Low-cost Memory Safety in C

Myoung Jin Nam

System languages such as C or C++ are widely used for their high performance, however the allowance of arbitrary pointer arithmetic and typecast introduces a risk of memory corruptions. These memory errors cause unexpected termination of programs, or even worse, attackers can exploit them to alter the behavior of programs or leak crucial data.

Despite advances in memory safety solutions, high and unpredictable overhead remains a major challenge. Accepting that it is extremely difficult to achieve complete memory safety with the performance level suitable for production deployment, researchers attempt to strike a balance between performance, detection coverage, interoperability, precision, and detection timing. Some properties are much more desirable, e.g. the interoperability with pre-compiled libraries. Comparatively less critical properties are sacrificed for performance, for example, tolerating longer detection delay or narrowing down detection coverage by performing approximate or probabilistic checking or detecting only certain errors. Modern solutions compete for performance.

The performance matrix of memory safety solutions have two major assessment criteria – run-time and memory overheads. Researchers trade-off and balance performance metrics depending on its purpose or placement. Many of them tolerate the increase in memory use for better speed, since memory safety enforcement is more desirable for troubleshooting or testing during development, where a memory resource is not the main issue. Run-time overhead, considered more critical, is impacted by cache misses, dynamic instructions, DRAM row activations, branch predictions and other factors.

This research proposes, implements, and evaluates *MIU: Memory Integrity Utilities* containing three solutions – MemPatrol, FRAMER and spaceMiu. *MIU* suggests new techniques for practical deployment of memory safety by exploiting free resources with the following focuses: (1) achieving memory safety with overhead < 1% by using concurrency and 4

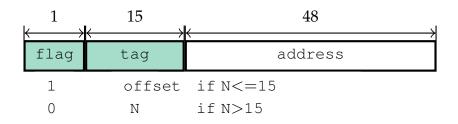

trading off prompt detection and coverage; but yet providing eventual detection by a monitor isolation design of an in-register monitor process and the use of AES instructions (2) complete memory safety with near-zero false negatives focusing on eliminating overhead, that hardware support cannot resolve, by using a new tagged-pointer representation utilising the top unused bits of a pointer.

- Myoung Jin Nam, Periklis Akritidis, and David J Greaves. FRAMER: Fast Per-object Metadata Management for Memory Safety. Paper presented at the Annual Arm Research Summit, 2018. Cited on pages 23, 53, and 58.

- Myoung Jin Nam, Periklis Akritidis, and David J Greaves. FRAMER: A Tagged-Pointer Capability System with Memory Safety Applications. In Proceedings of the 35th Annual Computer Security Applications Conference, ACSAC '19, page 612626, New York, NY, USA, 2019. Association for Computing Machinery. Cited on pages 23, 53, and 58.

- Myoung Jin Nam, Wonhong Nam, Jin-Young Choi, and Periklis Akritidis. MemPatrol: Reliable Sideline Integrity Monitoring for High-Performance Systems. In Michalis Polychronakis and Michael Meier, editors, *Detection of Intrusions and Malware, and Vulnerability Assessment*, pages 48–69, Cham, 2017. Springer International Publishing. Cited on pages 23, 54, and 123.

First of all, the completion of my PhD would not have been possible without all the support of my supervisor Dr. David J. Greaves. I would like to express my gratitude for his support, advice, and patience.

I would like to extend my gratitude to my examiners, Prof. Jon Crowcroft and Prof. Alastair F. Donaldson at Imperial College London, for sharing their valuable ideas and filling the viva with kindness.

My sincere thanks also go to Prof. Lawrence C. Paulson, Prof. Byron Cook at University College London, and Dr. Sean B. Holden for their constant encouragement and help.

I am indebted to Dr. Periklis Akritidis at Niometrics for his insightful guidance, support, and profound belief in my work and me, along with constructive criticism that pushed me to become a better version of myself.

My gratitude extends to Dr. Stephen Kell at University of Kent, Prof. Guy Lemieux at University of British Columbia, Prof. Jin-Young Choi at Korea University, Prof. Wonhong Nam at KonKuk University, Christos Rikoudis at Niometrics, and Dr. Matt Staats at Google for their support and helpful advice that improved my work.

I gratefully acknowledge the funding from the Research Foundation of Korea.

I would like to thank my former lab mates from the Networks and Operating Systems Group and Automated Reasoning Group and friends for their company and care that made my life in Cambridge a wonderful time, especially (I will omit titles of 'Dr' from this point. Sorry, Doctors!) – Julien Quintard, Martin A. Ruehl, Cecile Ritte, Bence Pasztor, Shu Yan Chan, Atif Alvi, Aisha Elsafty, Jordan Auge, Jean E. Martina, Damien Fay, Ilias Leontiadis, Charalampos Rotsos, Thomas Tuerk, Joon Woong Kim, Maria Rita Massaro, Foula Vagena, Mina Brimpari, Daniel Holland, Tony Coleby, Nicole Coleby, and Vassilis Laganakos.

I am also thankful to dear friends for their company during my time in Seoul and Singapore – Hyunyoung Kil, Jeongeun Suh, So Jin Ahn, Nickos Ventouras, Miyoung Kang, Chong Yi, and many more.

My deepest gratitude goes to my parents and two brothers for their support and everything.

And finally, this thesis is dedicated to my dearest Miu – my little girl, my fur angel – in heaven.

### Contents

| Ał | ostrac  | et      |                                            | 3  |

|----|---------|---------|--------------------------------------------|----|

| Pu | ıblica  | tions   |                                            | 7  |

| Ac | cknov   | vledgei | ments                                      | 9  |

| Та | ble o   | f conte | nts                                        | 14 |

| Li | st of : | figures |                                            | 15 |

| Li | st of   | tables  |                                            | 17 |

| 1  | Intr    | oductio | on                                         | 19 |

|    | 1.1     | Contri  | ibutions                                   | 22 |

| 2  | Bacl    | kgroun  | d                                          | 25 |

|    | 2.1     | Memo    | pry Safety                                 | 28 |

|    |         | 2.1.1   | Spatial Memory Safety                      | 29 |

|    |         | 2.1.2   | Temporal Memory Safety                     | 35 |

|    |         | 2.1.3   | Architectural Support and Capability Model | 37 |

|    | 2.2     | Type S  | Safety                                     | 41 |

|    | 2.3     | Contro  | ol-Flow Protection                         | 45 |

|    | 2.4     | Concu   | urrent Monitoring                          | 48 |

|    |         | 2.4.1   | Monitor Isolation                          | 50 |

|    |         | 2.4.2   | Kernel Integrity Monitors                  | 50 |

|    |         | 2.4.3   | Cryptographic Key Protection               | 50 |

| 3  | Ove     | rview   |                                            | 53 |

|    | 3.1     | FRAM    | 1ER                                        | 53 |

|    | 3.2     | spacel  | Miu                                        | 54 |

|    | 3.3     | MemF    | Patrol                                     | 54 |

| 4 | FRA  | MER:    | A Tagged-Pointer Capability System with Memory                                      |    |

|---|------|---------|-------------------------------------------------------------------------------------|----|

|   | Safe | ety App | lications                                                                           | 57 |

|   | 4.1  | Overv   | iew                                                                                 | 57 |

|   | 4.2  | FRAM    | IER Approach $\ldots$ $\epsilon$                                                    | 50 |

|   |      | 4.2.1   | Frame Definitions                                                                   | 50 |

|   |      | 4.2.2   | Frame Selection                                                                     | 52 |

|   |      | 4.2.3   | Metadata Storage Management                                                         | 53 |

|   | 4.3  | FRAM    | IER Implementation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\epsilon$ | 58 |

|   |      | 4.3.1   | Overview                                                                            | 58 |

|   |      | 4.3.2   | Memory Allocation Transformations                                                   | 59 |

|   |      | 4.3.3   | Memory Access                                                                       | 71 |

|   |      | 4.3.4   | Interoperability                                                                    | 72 |

|   | 4.4  | FRAM    | IER Applications                                                                    | 73 |

|   |      | 4.4.1   | Spatial Memory Safety                                                               | 73 |

|   |      | 4.4.2   | Temporal Memory Safety                                                              | 76 |

|   | 4.5  | Optim   | lisations                                                                           | 77 |

|   | 4.6  | Evalua  | ation                                                                               | 79 |

|   |      | 4.6.1   | Memory Overhead                                                                     | 79 |

|   |      | 4.6.2   | Slowdown                                                                            | 31 |

|   |      | 4.6.3   | Data Cache Misses                                                                   | 33 |

|   |      | 4.6.4   | Instructions Executed                                                               | 35 |

|   |      | 4.6.5   | Branch Misses                                                                       | 36 |

|   | 4.7  | Discus  | ssion                                                                               | 87 |

|   |      | 4.7.1   | Comparison with Other Approaches                                                    | 87 |

|   |      | 4.7.2   |                                                                                     | 39 |

|   |      | 4.7.3   | Additional Optimisations                                                            | 39 |

|   | 4.8  | Conclu  | usion                                                                               | 90 |

| 5 | Spa  | ceMiu:  | Practical Type Safety for C                                                         | 91 |

|   | 5.1  | Overv   | iew                                                                                 | 91 |

|   | 5.2  |         |                                                                                     | 93 |

|   |      | 5.2.1   |                                                                                     | 93 |

|   |      | 5.2.2   |                                                                                     | 94 |

|   |      | 5.2.3   |                                                                                     | 95 |

|   |      |         |                                                                                     |    |

|   | 5.3 | Run-T   | ime Typecast Checking                              | 96  |

|---|-----|---------|----------------------------------------------------|-----|

|   |     | 5.3.1   | Object-to-type Mapping                             | 98  |

|   |     | 5.3.2   | Per-object Metadata Management and Pointer-to-     |     |

|   |     |         | Type Mapping                                       | 100 |

|   |     | 5.3.3   | Type Confusion Checking                            | 102 |

|   | 5.4 | Union   | а Туре                                             | 103 |

|   | 5.5 | spacel  | Miu Implementation                                 | 106 |

|   |     | 5.5.1   | Creation of Type Descriptors                       | 107 |

|   |     | 5.5.2   | Program Initialisation                             | 108 |

|   |     | 5.5.3   | Memory Allocation                                  | 108 |

|   |     | 5.5.4   | Type Cast                                          | 110 |

|   |     | 5.5.5   | Memory Access                                      | 111 |

|   |     | 5.5.6   | String Functions                                   | 111 |

|   | 5.6 | Evalua  | ation                                              | 111 |

|   |     | 5.6.1   | Memory Overheads                                   | 112 |

|   |     | 5.6.2   | Slowdown                                           | 114 |

|   |     | 5.6.3   | Executed Instructions                              | 115 |

|   |     | 5.6.4   | L1 D-cache Misses                                  | 116 |

|   |     | 5.6.5   | Branch Prediction                                  | 117 |

|   | 5.7 | Discus  | ssion                                              | 118 |

|   |     | 5.7.1   | Effective Type Detection for Heap Objects          | 118 |

|   |     | 5.7.2   | String Functions and Effective Type                | 118 |

|   |     | 5.7.3   | Aliasing Rules                                     | 119 |

|   |     | 5.7.4   | Per-object Metadata Placement                      | 120 |

|   | 5.8 | Concl   | usion                                              | 120 |

| 6 | Mor | nDatrol | : Reliable Sideline Integrity Monitoring for High- |     |

| 0 |     |         | ce Systems                                         | 123 |

|   | 6.1 |         | riew                                               | 123 |

|   | 6.2 |         | t Model                                            | 125 |

|   | 0.2 | 6.2.1   | Sideline Integrity Monitoring                      | 125 |

|   |     | 6.2.2   | Heap Integrity                                     | 125 |

|   | 6.3 |         | or Thread Isolation                                | 120 |

|   | 0.0 | 6.3.1   | Protection of Data Structures in Memory            | 127 |

|   |     | 6.3.2   | Protection of Code                                 | 120 |

|   |     | 0.0.2   |                                                    | 101 |

|    |       | 6.3.3   | Terminating or Tracing the Monitor Thread    | 132 |

|----|-------|---------|----------------------------------------------|-----|

|    |       | 6.3.4   | Faking Application Termination               | 133 |

|    |       | 6.3.5   | Detection of Normal and Abnormal Termination | 133 |

|    |       | 6.3.6   | Minimizing Performance Impact                | 134 |

|    |       | 6.3.7   | Limitations                                  | 135 |

|    | 6.4   | Case S  | Study: Heap Integrity                        | 135 |

|    |       | 6.4.1   | Memory Pools                                 | 136 |

|    |       | 6.4.2   | Integration with the Monitored Application   | 137 |

|    |       | 6.4.3   | Cryptographically Generated Canary Values    | 138 |

|    |       | 6.4.4   | Canary Recycling                             | 139 |

|    | 6.5   | Evalua  | ntion                                        | 139 |

|    |       | 6.5.1   | Integration with NCORE                       | 139 |

|    |       | 6.5.2   | Experimental Results                         | 140 |

|    | 6.6   | Discus  | sions                                        | 144 |

|    |       | 6.6.1   | Tunable Overhead                             | 144 |

|    |       | 6.6.2   | Memory Safety                                | 145 |

|    | 6.7   | Conclu  | asion                                        | 145 |

| 7  | Con   | clusion | IS                                           | 147 |

| 8  | Арр   | endix   |                                              | 149 |

|    | 8.1   | Proofs  |                                              | 149 |

|    |       | 8.1.1   | Proof 1                                      | 149 |

|    |       | 8.1.2   | Proof 2                                      | 149 |

| Bi | bliog | raphy   |                                              | 151 |

| 2.1  | Embedded Metadata                                         | 28  |

|------|-----------------------------------------------------------|-----|

| 2.2  | Off-by-one byte                                           | 32  |

| 2.3  | Disjoint metadata structures of Address Sanitizer and MPX | 33  |

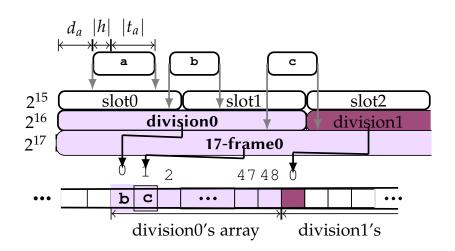

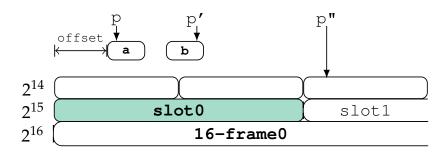

| 4.1  | Aligned frames in memory space                            | 61  |

| 4.2  | Tagged pointer                                            | 64  |

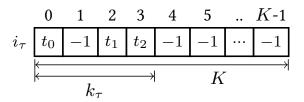

| 4.3  | Access to division array                                  | 66  |

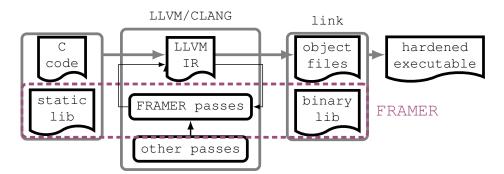

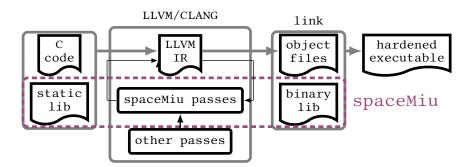

| 4.4  | Overall architecture of FRAMER                            | 68  |

| 4.5  | In-frame checking at pointer arithmetic                   | 75  |

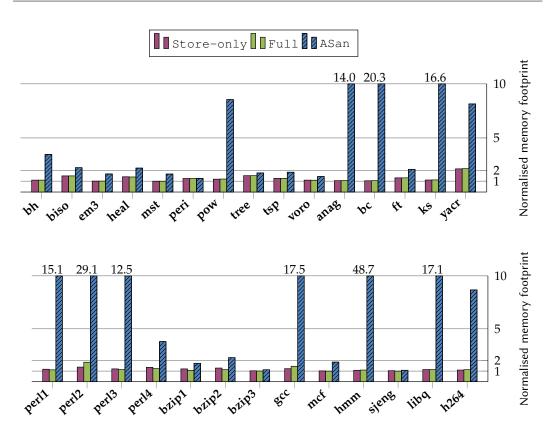

| 4.6  | Normalised memory footprint (maximum resident set size)   | 80  |

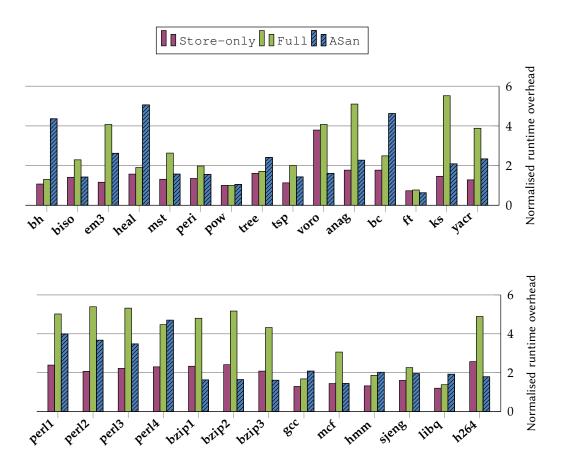

| 4.7  | Normalised runtime overhead                               | 81  |

| 4.8  | Runtime overheads for metadata management and retrieval   | 82  |

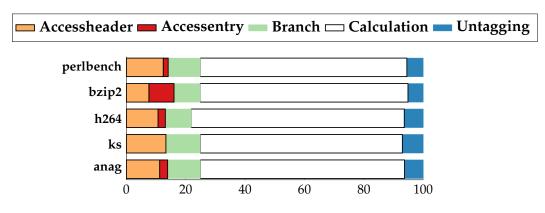

| 4.9  | Normalised L1 D-cache load misses per 1000 instructions   |     |

|      | (MPKI)                                                    | 84  |

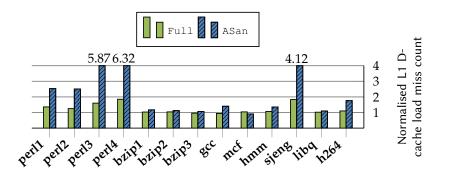

| 4.10 | Normalised L1 D-cache load miss count                     | 85  |

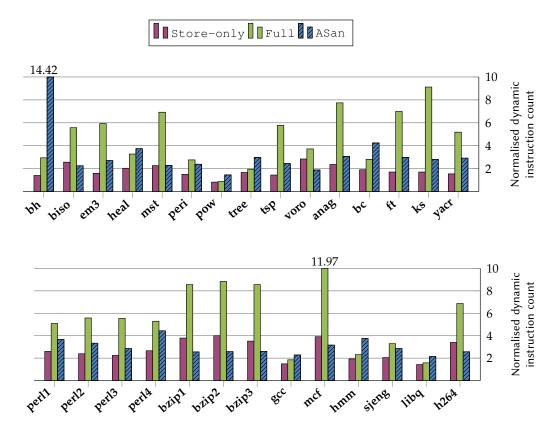

| 4.11 | Normalised dynamic instruction count                      | 87  |

| 5.1  | C example with typecasts                                  | 92  |

| 5.2  | Atomic Types                                              | 94  |

| 5.3  | Aggregated Types                                          | 94  |

| 5.4  | Physical Equality                                         | 95  |

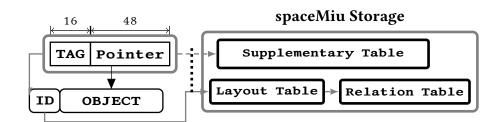

| 5.5  | Metadata Storage and Type Descriptors                     | 98  |

| 5.6  | Entries of Type Descriptors                               | 102 |

| 5.7  | Union's safecast                                          | 106 |

| 5.8  | Overall architecture of spaceMiu                          | 107 |

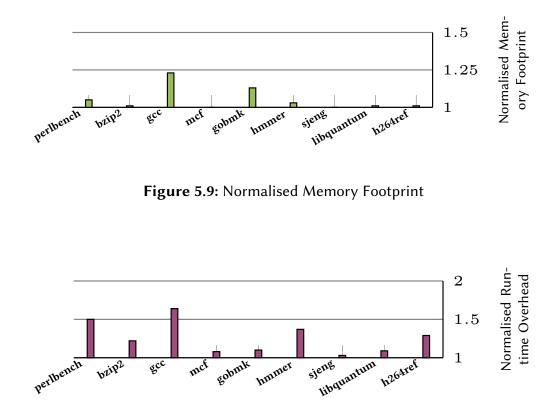

| 5.9  | Normalised Memory Footprint                               | 112 |

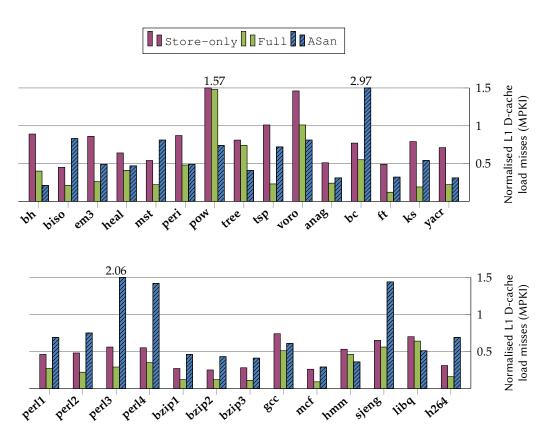

| 5.10 | Normalised runtime overhead                               | 112 |

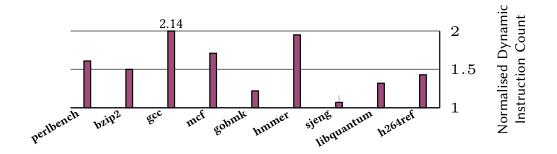

| 5.11 | Normalised Dynamic Instruction Count Overhead             | 113 |

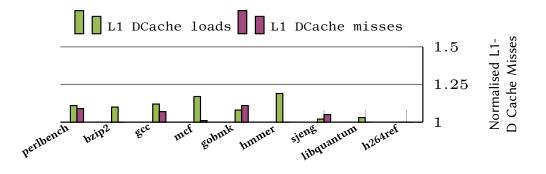

| 5.12 | Normalised L1-D Cache Miss Count Overhead                 | 113 |

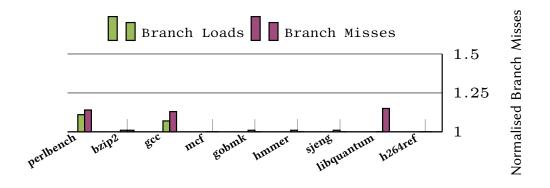

| 5.13 | Normalised Branch Miss Count Overhead                     | 114 |

| 5.14 | String functions and effective type                 | 119 |

|------|-----------------------------------------------------|-----|

| 6.1  | Protection of data in memory                        | 128 |

| 6.2  | Untrusted-memory data type and access routines      | 130 |

| 6.3  | Canary-monitoring integration API                   | 137 |

| 6.4  | Secure canary checking                              | 138 |

| 6.5  | Relation between system read throughput and maximum |     |

|      | detection latency                                   | 142 |

| 4.1 | Instrumented codes                   | 71  |

|-----|--------------------------------------|-----|

| 4.2 | Summary averages over all benchmarks | 79  |

|     |                                      |     |

| 6.1 | Cache hit rates                      | 141 |

| 6.2 | NUMA effects                         | 143 |

# Introduction

C/C++ languages have *low-level* features such as providing a set of bit manipulators, allowing assumptions about the underlying hardware architecture to take advantages of hardware-specific behaviors/features, and compiler support for inline assembly language. Especially C/C++ has *pointers* which allow (and often require) direct manipulation of memory contents.

The visibility of memory layout in C or C++ has been two sides of the coin – it provides high performance however the allowance of arbitrary pointer arithmetic and type casting imposes the danger of memory corruption, which makes C/C++ languages *unsafe*. Those memory errors may cause unexpected termination of programs. Even worse, security exploits use memory safety vulnerabilities to corrupt or leak sensitive data, and hijack a vulnerable program's control flow.

Despite advances in software defenses, exploitation of systems code written in C or C++ is still possible [82, 122, 129, 23]. In response, several defence techniques have been proposed to make software exploitation hard.

Current defenses fall in two basic categories: those that let memory corruption happen, but harden the program to prevent exploitation, and those that try to detect and block memory corruption in the first place. In the first category, for instance, Control-flow Integrity (CFI) [1, 75, 149, 150, 151] models all allowable control flows in a statically-computed Control-flow Graph (CFG), while Address Space Layout Randomization (ASLR) [102] hides the available CFG when the process executes. Both approaches can be bypassed [41, 120], since memory corruption can still occur, albeit exploitation is much harder. The second category, providing fine-grained and strong memory safety enforcement, includes approaches that detect and block memory safety violations. The approaches instrument the program and maintain runtime metadata for access rights to block unintended accesses at runtime [6, 35, 53, 88, 36, 93, 114, 25]. Most of these systems are based on an *inline reference monitor* [112, 37] offering deterministic guarantees by preventing memory corruption in the first place. By embedding checks into the binary code during compilation or via binary rewriting, inline reference monitors can enforce integrity guarantees for the program's memory accesses or control-flow. Violations are detected promptly, with the instruction at fault identified, which greatly facilitates debugging. These memory safety solutions, based on inline monitors, are indispensable for finding memory errors in C/C++ programs during development and testing [94, 114].

Unfortunately for production deployment as an *always-on* solution, those approaches checking individual memory access are still heavy [122]. Their tracking of all objects (or pointers) incurs heavy performance overheads. Performance is critical for adoption since unsafe languages like C/C++ are employed for performance-sensitive applications.

Whilst pushing the limit of performance with novel techniques, researchers have made trade-offs among properties of memory safety enforcement: detection coverage [4, 146, 5], detection timing [141], compatibility [11, 93, 57] and performance. Some early techniques trade off *compatibility* for high locality of reference. One example is so-called *fat pointers* [11, 93, 57], a new pointer representation that stores extra metadata with the address of an object that the pointer points to. Fat pointers provide the best speed, but unfortunately impose binary incompatibility issues with external modules especially pre-compiled libraries. It is desirable to minimise the disruption owing to tacit assumptions by programmers and compatibility with existing code or libraries that cannot be recompiled.

To avoid breaking binary compatibility by changing object memory layout, more recent approaches inevitably chose to bear some performance degradation. Some of them decouple metadata from a pointer representation and store them in a *disjoint metadata*. The cost of such fine-grained memory safety storing per-object [33, 6, 114] (or per-pointer) [88, 143, 53, 87] metadata in a remote region is dominated by metadata updates and lookups, making efficient metadata management the key for minimizing performance impact. These solutions focus on reducing run-time overheads by (1) sacrificing detection coverage of memory errors [4, 146, 5] or precision [6, 9, 8]; or (2) wasting memory space with excessive alignment or large *shadow memory spaces* [6, 47, 89, 114] referring to a memory region as a mirror copy of an application space. Some other solutions trade accuracy for speed by allowing false negatives, and hence are more useful for troubleshooting than security. They still provide wide detection coverage but have evolved to keep the performance degradation as little as possible to reduce the time for software testing during development.

In most cases, it is reasonable to prioritise speed over efficiency in space amongst these two main performance assessment criteria, considering that memory safety solutions are normally used during development and it is more critical to reduce time scale than memory resources. However this perspective invites debates for production deployment. There are systems whose memory efficiency is as important as time, such as embedded systems with limited memory space or I/O server systems. In addition, some causes of run-time overheads can be easily resolved with hardware acceleration e.g customised instruction sets, while memory overhead cannot go away even with the hardware support.

Unfortunately inline reference monitors providing fine-grained memory protection have not fully resolved overheads caused by tracking individual memory allocations and accesses to them despite the advances in the techniques and trade-offs. For light-weight memory safety enforcement, researchers proposed replacing inline security enforcement with *concurrent* monitors [148, 125, 111, 109, 81]. In principle, such approaches can minimize the performance overhead on the protected application by offloading checks to the concurrent monitor. Detection, however, now happens asynchronously, introducing a detection delay. This weaker security guarantee is nevertheless still useful. For example, in the case of passive network monitoring systems, it helps validate the integrity of the system's past reports.

These proposals, however, face significant challenges. For some, the delay introduced before the detection of memory safety violations opens up a vulnerability window during which the attackers have control of the program's execution and may attempt to disable the detection system. This undermines the guarantee of *eventual* detection, even worse, security that those protections aim to achieve by sacrificing spontaneous detection of memory errors. For others, attempts to isolate the monitor during the vulnerability window degrade performance. Finally, these solutions have been designed for general purpose systems, and their communication and synchronization overheads between the monitor and the application threads can be prohibitive for high-performance applications.

#### 1.1 Contributions

This research demonstrates trade-offs between detection coverage, detection timing and performance; pushes the limit of performance metrics to extreme depending on the deployment; and improves memory safety. We propose and implement *Memory Integrity Utilities* (MIU), run-time verification systems for low-cost memory safety enforcement, that exploit free resources. Each approach sacrifices a subset of properties for others depending on the goal, and lowers overhead that is expensive or difficult to resolve with hardware support.

MIU proposes both:

- (1) an *inline* monitor prioritising near-complete memory safety with similar increase in run-time overhead to existing approaches but much lower space overhead.

- (2) a *sideline* monitor providing the minimal performance degradation by sacrificing timely and immediate detection.

Firstly, our inline monitor statically instruments an application and halts program execution at security violations. The goal of the monitor is to provide *fine-grained* and *deterministic* memory protection without relying on probability, so that it can also be used during development stage. For its deployment in practice, overhead must be kept low. Compared to existing approaches, our solution provides higher efficiency in data cache and memory footprint by utilising the top unused bits in 64-bit pointers. In our experiments, Address Sanitizer [114] is faster, however both cause 2x slowdown, and the run-time overhead for our approach will be resolved with hardware acceleration (customised instruction sets). While keeping overheads for memory and data cache low, we remove false negatives that may incur in some previous approaches thus guarantee near-complete memory safety. Another advantage of this approach is its scalability: it can be used for memory safety, type safety, thread safety and garbage collection, or any solution that needs to map pointers to metadata.

This inline reference monitor is evaluated on two use cases with run-time verification systems for C programs detecting:

- (i) FRAMER: array-out-of bounds and some cases of dangling pointers

- (ii) spaceMiu: type confusions in C programs.

The first system, FRAMER [90, 91], illustrates the use of the capability framework on *spatial memory safety* that guarantees near-zero false negatives, allowing inexpensive validation of pointer dereferences by associating pointers to object metadata containing bounds information. The second system, spaceMiu, presents the application of the tagged pointer capability model to *type safety* detecting unsafe type casts, that also violate spatial memory safety. This work defines a type relation for the C language, that does not support type hierarchy, and *unsafe* type conversion in C programs, inspired by CCured [93]; and implements run-time type confusion verifier utilising efficient per-object type information.

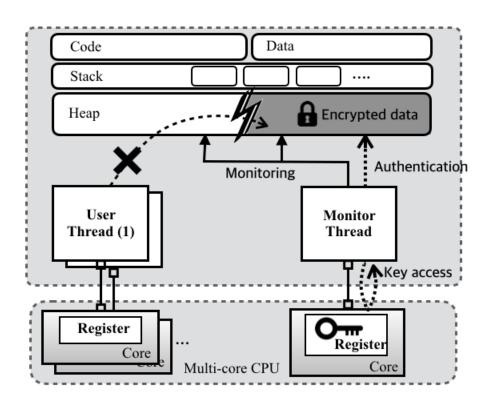

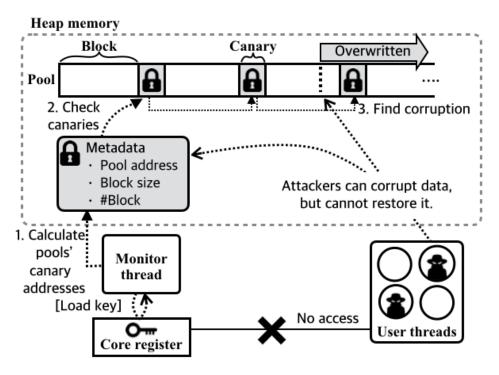

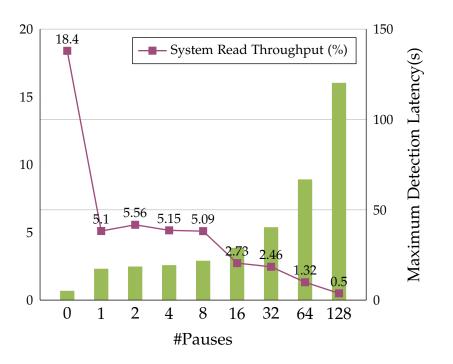

Another contribution of this dissertation is a *sideline* monitoring system, *MemPatrol* [92], for practical deployment for high-performance systems. This system realises very low performance degradation by pushing other memory safety properties (immediate detection and error coverage) to extreme. *MemPatrol* does not detect errors in timely order, yet detects them *eventually*. The trade-off drops the overhead down to < 1%, which is lower than 5%, that is commonly acceptable for production deployment. *MemPatrol* implements a *concurrent* monitor detecting memory errors, and using concurrency minimises the performance impact to a target program while allowing *configurable* overheads, that can be useful for any systems. This work addresses one of the challenges of concurrent monitors – a monitor

being compromised by attackers through memory corruptions during the detection delay caused by concurrency – by monitor isolation techniques that leverage CPU registers. It takes advantage of the AES instruction set of Intel processors [45] to implement CPU-only cryptographic message authentication codes (MACs), and stores critical information in regular registers of user-mode programs.

This dissertation proposes, designs and evaluates these three run-time verification approaches that improve memory safety.

# 2 Background

There are two major categories in security enforcement depending on their goal. The first category is to detect and defend memory corruption in the first place by enforcing memory safety, offering stronger security guarantees. The second category aims at a favourable *security-to-overhead* ratio rather than complete memory safety. Those approaches in the second category let memory corruption occur in the first place but they harden a program execution, making it difficult to exploit memory corruptions for attackers, however exploitations are still possible with well-structured attacks.

*Probabilistic* solutions are usually based on *randomization* or *encryption* e.g. Instruction Set Randomization, Address Space Randomization, or Data Space *Randomization*. Randomization protections introduce entropy to prevent exploits of safety violations. For instance, Data Space Randomization makes it difficult for attackers to know how to replace values in code pointers by randomizing representation of all data. Address Space Layout Randomization (ASLR) [102, 40] hides the available Control-Flow Graph (CFG) when the process executes. It mitigates control-flow hijacking attacks by randomizing the location of code and data and thus the potential payload address. Both approaches can be bypassed [41, 120] e.g. initial information leakage of a code pointer and guessing attacks expose a program in memory and enable attackers to construct exploits to bypass ASLR however they can block the majority of attacks. The overhead of ASLR is negligible so it has been used in practice but the case to enforce full ASLR on Linux shows 10-25% overhead, which prevents deployment. The overhead comes from Position Independent Executables (relocatable executables) on 32-bit machines and so ASLR should be enforced only for libraries by default on most distributions. Many protections with probability are in the second category that prevents attackers from exploiting memory corruptions rather than detecting vulnerabilities.

However some of protections built on a probabilistic model belong to the first category of preventing memory corruptions. Stack smashing protection, such as StackGuard [26], uses random values for stack cookies (or canaries) to detect memory overwrites to return addresses (§ 2.3). Although the detection coverage is not as wide as other memory protection solutions, e.g. it cannot detect data reads beyond boundaries, these solutions using encrypted cookies are widely deployed due to their very low overhead and great compatibility.

The other approaches enforce a *deterministic* safety policy by implementing a low-level reference monitor [37, 112]. A reference monitor observes the program execution and halts it whenever it is about to violate the given security policy, helping remove security vulnerabilities. While traditional reference monitors enforce higher-level policies, such as file system permissions, and are implemented in the kernel (e.g., system calls), more recent reference monitors enforce lower-level policies, e.g., memory safety or control-flow integrity. They can be implemented in two ways: (1) in hardware or (2) by embedding the reference monitor into the code through instrumentation. For instance, Code Integrity + Non-executable Data is enforced by the hardware, as modern processors support both non-writable and non-executable page permissions [79, 80]. Hardware support for protection with coarse granularity causes negligible overhead, however hardware acceleration may not resolve overhead of low-level monitors with fine granularity. We discuss hardware implementation especially architectural support for low-level monitoring in § 2.1.3.

The alternative to hardware support is adding the reference monitor dynamically or statically to the code. In this section, we focus only on solutions which transform existing programs to enforce various policies.

Firstly, *dynamic* (binary) instrumentation [94, 77, 16, 103] can be used to dynamically insert run-time checks into unsafe binaries at run-time. It supports arbitrary transformations but introduces some additional slowdown due to the dynamic translation process. Simple reference monitors, how-

ever, can be implemented with low overhead: for instance, a *shadow stack* costs less than 6.5% performance for SPEC CPU2006 in [103]. More so-phisticated reference monitors like *Taint Checking* [14] or *ROP detectors* [28] causes overheads that exceed 100% and are unlikely to be deployed in practice.

*Static* instrumentation inlines reference monitors at compile time. This can be done by the compiler or by static binary rewriting. Inline reference monitors can implement any safety policy and are usually more efficient than software dynamic solutions, since the instrumentation is not carried out at run-time. Those approaches provide deterministic and immediate detection of memory errors with fine granularity, however their high overhead is one of the biggest challenges to deploy them in practice. Other performance-optimised solutions for inline monitoring also incur high and unpredictable overheads [52].

The most widely used security protections implementing an inline reference monitor are static Control-Flow Integrity (CFI) and memory safety. CFI restricts the control-flow of an application to valid execution traces by monitoring the program at runtime and comparing its state to a set of precomputed valid states. CFI is a defense that leverages run-time monitors to detect specific attack vectors (control-flow hijacks for CFI) and flags exploit attempts at run time. All modern compilers implement a form of CFI with low overhead but different security guarantees. If security properties are violated i.e. an invalid state is detected, an alert is raised; reference monitors usually terminate the application. Control-flow hijacking is usually the primary goal of attacks and many CFI techniques defend them at the cost acceptable to practical deployment (<5%). We discuss more about CFI in § 2.3.

On the other hand, memory safety monitors pointer dereferences. It usually tracks memory allocation (or pointers) and compares a pointer to be dereferenced with stored metadata such as bounds information or memory allocation status (alive or de-allocated). Unfortunately inline reference monitors enforcing memory safety suffer from high overheads (100%), since they check every memory allocation/release and access. So they often target development settings when testing a program. Memory corruption can be exploited to carry out other types of attacks as well and memory

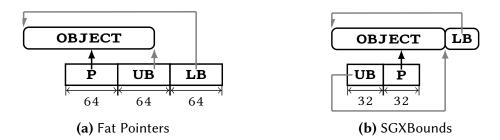

Figure 2.1: Embedded Metadata: P, UB, and LB represent a pointer itself, upper bound, and lower bound, respectively.

safety provides a wider range of protection. However the overhead has not been fully resolved yet and performance is one of the main challenges of memory protection mechanisms.

In the following subsections, we discuss different software security vulnerabilities and identify the approaches to detecting the vulnerabilities and mitigating exploits.

#### 2.1 Memory Safety

Enforcing memory safety stops all memory corruption exploits. Our focus is to enforce memory safety based on low-level, inline reference monitors embedding checks that prevent memory errors by transforming existing unsafe code. The instrumentation may be in the source code, intermediate representation, or binary level. For complete memory safety, both *spatial* and *temporal* errors must be prevented without false negatives. In addition, high-rate false alarms are critical for practical deployment, so they must be kept very low. Unfortunately it is extremely expensive to guarantee complete memory safety especially for system languages such as C/C++.

§ 2.1 reviews prior approaches for memory safety based on inline reference monitor that either track objects or pointers by instrumentation and discusses their trade-offs between detection coverage and performance. Another kind of software vulnerabilities, *type confusions*, will be discussed in § 2.2 separately.

#### 2.1.1 Spatial Memory Safety

*Spatial* memory errors refer to *buffer overflows*. Buffer overwrites (out-ofbounds writes) can corrupt the content of adjacent objects, or internal data (like bookkeeping information for the heap) or return addresses. Similarly, buffer overreads may can reveal sensitive data or help attackers bypass address space layout randomization.

The only way to enforce complete *spatial memory safety* is to keep track of pointer bounds – the lowest and highest valid address it can point to. Many approaches have been proposed to enforce spatial memory safety in C/C++ programs. Some of these solutions offer extensive memory protection, but they slow down applications significantly.

Spatial memory safety solutions are divided into two categories depending on whether they associate bounds information with individual pointers or objects.

#### **Pointer-based Tracking**

Approaches tracking pointers associate each individual *pointer* with its metadata holding a valid address range that the pointer is allowed to point to [87]. Metadata is assigned to a pointer at pointer assignment and bounds checking is performed *only* at memory access unlike object-based approaches that may require optional extra-checks at pointer arithmetic operations (as discussed later in § 2.1.1). Holding an address range (the base address ~ upper bound) provides protection with *byte-granularity* and this permits creation of *out-of-bounds* pointers <sup>1</sup> and pointers to sub-objects that are allowed in C/C++. This makes it easier to detect *internal overflows* such as an array out-of-bounds inside a structure. As long as tracked pointers act inside instrumented codes, pointer-based approaches do not produce false violations. However, if instrumented pointers passed to un-instrumented external libraries are updated there and returned, they lose track of the pointers (this occurs when the non-instrumented code modifies the pointer and does not properly update the bounds metadata).

<sup>&</sup>lt;sup>1</sup>Out-of-bounds pointers refer to pointers with a value that goes out of bounds of an object that they point to.

Pointer-based approaches are often implemented using *fat pointers* [11, 57, 93, 25]. They define a new pointer representation that embeds metadata (the base and upper bound) with itself as presented in Fig. 2.1a), thus increasing spatial locality of references by removing accesses to retrieve metadata in a remote memory region at run-time checking. Unfortunately the approaches sacrifice *binary compatibility*. Since fat pointers increase the number of bytes used to hold a pointer, they require modification of the memory layout and this damages compatibility with non-instrumented code.

CCured [93], which implements fat pointers, statically annotates a *pointer qualifier* (safe, seq, and wild) on pointers discovered by constraint rules and applies instrumentation depending on the pointer kind. Pointers involved with pointer arithmetic (seq) or typecast (wild) are equipped with two extra words holding the base and upper bound and especially wild pointers cause more overheads. All break binary compatibility. This requires wrapper annotations for calls to external libraries and imposes a conservative garbage collector. Cyclone [57] avoids using garbage collector in favour of region-based memory management, but also diverges more markedly from C. Moreover, updates to fat pointers spanning multiple words are not atomic, while some parallel programs rely on this.

Several pointer-based approaches [143, 89, 53, 87] choose memory layout compatibility over the speed with high locality. Using *disjoint metadata* achieves compatibility by decoupling metadata from a pointer representation and storing metadata in a remote memory region. SoftBound [89] implements both a hash table or shadow memory space to map pointers to the metadata. Unfortunately, the performance overhead of SoftBound is comparably high, 79% on average [89].

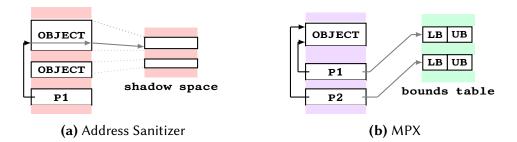

Hardware support [30, 53, 100, 135, 63] does not remove this overhead. Intel MPX [53, 87, 99] is an ISA extension that provides hardwareaccelerated pointer-checking, using disjoint metadata in a *bounds table* holding per-pointer metadata as illustrated in Fig. 2.3b. Reportedly, MPX suffers due to lack of memory even with small working sets [66], and has turned out to be slow for pointer-intensive programs, owing to exhausting the limited number of special-purpose bounds registers (four registers), requiring spill operations from regions of memory that themselves require management and consume D-cache bandwidth and capacity.

Pointer-tracking approaches provide strong memory protection with near-zero false positives/negatives, but it comes with the additional runtime overhead from metadata copy and update at pointer assignment, while object-based approaches update metadata only at memory allocation/release. In addition, the number of pointers is typically larger than that of allocated objects, so pointer-intensive programs may suffer from heavier runtime overheads. More importantly, it is difficult to achieve full compatibility with them – if a pointer created by the instrumented module is passed to and modified in an un-instrumented module, the correspond-ing metadata is not updated, causing false violations.

#### **Object-based Tracking**

Due to the compatibility and cost of per-pointer metadata, most techniques track objects. *Object-based* approaches [6, 114, 33, 58, 9, 66, 35, 65, 147] store metadata *per object* and also make a trade-off against complete memory safety. They offer *compatibility* with current source and pre-compiled legacy libraries by not changing the memory layout of objects. In addition, per-object metadata is updated only at memory allocation/release so even if a pointer is updated in an un-instrumented module, the metadata does not go out-of-sync.

Per-object metadata management supports binary compatibility however it has some drawbacks. First of all, the approach does not enforce complete memory safety. For instance, it is more difficult to detect internal overflows compared to using per-pointer metadata management that can simply set up a pointer's metadata with the address range of a sub-object.

One of the disadvantages of object-tracking is that it may not detect memory access violation when pointers exceed the bounds of *right* object (*intended referent*) [58] by pointer arithmetic and then land in the valid range of *another* object. Memory access with these pointer can be seen *valid* in many object bounds-based approaches. Knowing only the bounds of objects is not enough to catch errors at pointer dereferences, because we do not know if the pointer points to the intended referent. To keep track of them, object-tracking approaches may have to check bounds at pointer arithmetic [58]. However, performing bounds checks only at pointer arithmetic may therefore cause *false positives*, where a pointer going out-of-bounds by pointer arithmetic is not dereferenced as follows:

```

1 int *p;

2 int *a = malloc(100 * sizeof(int));

3 for (p = a; p < &a[100]; p++) *p = 0;</pre>

```

#### Figure 2.2: Off-by-one byte

On exiting the for loop, p goes out-of-bounds yet is not dereferenced – this is valid according to the C standard.

Therefore, object-based approaches should take a special care for outof-bounds pointers. The early approach J&K [58] addressed violation of intended referents by padding objects with extra one byte (*off-by-one byte*). This still caused false positives when a pointer legitimately goes beyond more than one byte. A more generic solution to this problem was later provided by CRED [110]. Baggy Bounds Checking [6] instead performs bounds checking at pointer arithmetic, not pointer dereferences, and marks the out-of-bounds pointers so that errors are reported when those are dereferenced.

Object-tracking approaches store a valid range of allocation, so it requires *address range lookups*, while pointer-tracking allows access the corresponding entry using the address of a pointer as a *key* in the metadata table. Performing lookup on the address range of objects is more expensive than lookup by key, or different representations. J&K [58] used a splay tree to reduce the overhead of the range lookup but unfortunately the slowdown is still high (11x-12x). The approach [33] applied *automatic pool allocation* that partitions the memory space using static points-to analysis and stores metadata for each partition. This technique improved the performance up to 120% by reducing the number of bounds lookups.

Modern approaches avoid range lookups and reduce slowdown using a *shadow space* [6, 114, 147, 24, 47, 94, 5]. Shadow space allows single direct *ar-ray access* to metadata and this reduces the increase in executed instructions for metadata access, removing metadata lookup in a data structure. Necula

Figure 2.3: Disjoint metadata structures of Address Sanitizer and MPX

and Xu [93] creates a mirror copy of a data structure, i.e. *byte-to-byte* mapping, and SoftBound [89] used both a hashtable and shadow space, and showed that using shadow space reduces runtime overhead, on average, by 2/3 compared with using table lookup.

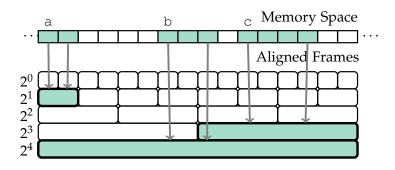

Beyond byte-to-byte mapping of the application space used by early techniques, recent techniques reduced the size of shadow space with compact encoding, at the cost of minimum allocation size or loss of some precision. An example is Baggy bounds checking (BBC) [6]. BBC divides the memory space into *fixed-sized* blocks and mandates object alignment to the base of a block, to prevent metadata conflicts caused by multiple objects in one block. Consequently it pads each object to the *next* power of two, so that each one-byte sized entry stores only log<sub>2</sub>(padded object size). This allows compact bounds information and fast lookup by sacrificing memory efficiency. BBC addresses violation of intended referents by checking bounds at pointer arithmetic, not at memory access, and marking pointers going out of padded bounds so that they are detected at dereference. This can cause false positives when an illegal pointer comes back within their valid range without being dereferenced. BBC performs approximate bounds checking which tolerates pointers going out-of-bounds yet within the padded bound. Memory access with those pointers violates spatial memory safety however it still enforces security, preventing exploits.

Address Sanitizer [114] (ASan) utilizes shadow space differently. Like BBC, it also re-aligns and pads each object but it pads an object with *red-zones* front and back as shown in Fig. 2.3a. While BBC stores  $log_2$  (padded object size) in a corresponding entry in the shadow space and tolerates access to the pad, ASan considers access to redzones as out-of-bounds,

providing greater precision. The errors are identified by the value in the corresponding entry in the shadow. At memory access, ASan derives the address of its corresponding entry from a pointer, and the entry tells if the address is addressable. ASan also prevents some dangling pointers by forcing freed objects to stay in a so-called quarantine zone for a while. A disadvantage of ASan is that its error detection relies on spatial or temporal distance. It loses track of pointers going far beyond the redzone and reaching another object's valid range and it makes it tricky to address false negatives caused by violation of intended referents. ASan addresses this issue by enlarging the space between objects. The wider the redzone, the more errors ASan detects. In addition, use-after-free errors cannot be detected, in the cases where dangling pointers are used to access objects after the pointer is freed from the quarantine. ASan detects most errors, but it is less deterministic in theory and trades-off memory space for detection coverage. In our experiments comparing ASan and our prototype, ASan and FRAMER's normalised memory footprints are 8.84 and 1.23, respectively.

Rather than fat pointers or shadow space, *tagged pointers* [65, 66] can instead be used since there are unused bits in a pointer e.g. top 16 bits in a 64-bit pointer. SGXBounds [66] trades-off *address space* for speed and nearcomplete memory safety. SGXBounds makes objects carry their metadata in a *footer* as shown in Fig. 2.1b, and utilizes the higher 32 bits of a pointer to hold the metadata location. The location is the upper bound of its referent at the same time and object size information is stored in the footer. Storing the absolute address of bounds frees SGXBounds from violation of intended referents that challenge many object-tracking approaches. However this approach works when there are enough spare bits in pointers, which is the case with SGX enclaves, where only 36 bits of virtual address space are currently supported.

Hardware-accelerated tagged pointers are available without sacrificing address space. ARM v8.5 ISA [9, 8] introduces the Memory Tagging Extension (MTE). This assigns a 4-bit tag to each 16 bytes at memory allocation, and tapping memory accesses with incorrect tags in the pointer. However, this approach has 1/16 chance of false negatives at each memory access when the tags in the memory and a pointer match. In case of a real-world exploitation, the random 1/16th chance on an individual access rapidly disappears to an acceptable level over the course of tens of operations but still provides a usable channel that can be exploited over multiple similar systems in a structured attack. However this solution still relies on probability for memory safety.

In the above subsections, we have discussed approaches to prevent spatial memory errors especially on buffer overflows. Similarly, uninitialised pointers containing garbage values may happen to point at a valid object, so we make sure that pointers are initialised. Lastly, it is difficult to track sub-objects such as an array in a structure or in an outer array, so it may require to manage additional information such as type information.

#### 2.1.2 Temporal Memory Safety

Temporal memory safety violations (*dangling pointers*) include null pointer deferences, *use-after-free*, or *double-free* errors. Dangling pointers arise when pointers are dereferenced (used) after the memory area they try to dereference has been deallocated and returned to the memory management system. Attacks exploiting vulnerable pointers after referent objects are released are as strong as spatial memory safety violation, letting the pointers deference attacker-controlled data.

Dangling pointers often occur in attempts to access *freed* heap objects and tend to be exploited in conjunction with *type confusion* errors. Assume a dangling pointer pointing to a new object tries to read memory with the freed object's type. When a virtual function of the freed object is called and the virtual function pointer is looked up, the content of the new object will be interpreted as the vtable pointer of the old object. This allows the corruption of the fake vtable pointer, comparable to exploiting a spatial write error, but in this case the dangling pointer is only dereferenced for a read. An additional aspect of this attack is that the new object may contain sensitive information that can be leaked when read through the dangling pointer of the old objects type.

Temporal memory errors also occurs in *stack-allocated* objects. Pointers to a local variable, that are assigned to a global or heap pointers, become dangling when the function of the local variable returns while the pointer is still alive. In this case, dangling pointers are exploited to overwrite sen-

sitive data. Writing through a dangling pointer is similarly exploitable as an out-of-bounds pointer by corrupting other pointers or data inside the new object. When the dangling pointer is an escaped pointer to a local variable and points to the stack, it may be exploited to overwrite sensitive data, such as a return address.

Like spatial memory safety solutions, approaches to ensure temporal memory safety [4, 88, 86, 118, 2, 32] can be divided into two categories: (1) to block temporal memory errors in the first place and (2) to prevent exploitations of dangling pointers.

Like spatial memory safety enforcements (§ 2.1.1), the approaches in the first category also track live objects or pointers to detect dangling pointers. Valgrind's Memcheck [94] and Address Sanitizer (Asan) [114] track *objects* and mark their status in corresponding entries in the shadow memory. These tools can detect dangling pointers attempting to access after their referent object is de-allocated, as long as new objects are not yet allocated in the locations. However they produce false negatives when the memory region is re-allocated; the area is registered again and the invalid access remains undetected. ASan removes some false negatives by keeping freed objects in the *quarantine* area to prevent use-after-free errors during limited period of time but still may miss some errors. Object-tracking approaches provides less complete temporal memory safety compared to pointer-based approaches like spatial memory safety. Unfortunately, their overheads are quite high. Valgrind, based on dynamic instrumentation, causes higher overhead (10x), while ASan built on LLVM causes around 2x.

Pointer-tracking approaches provide stronger protection. A pointer is associated with allocation/release status information along with bounds information for complete memory safety. A pointer needs to uniquify live objects i.e. to distinguish not only two objects in different memory regions but also two *temporally-distinctive* objects allocated in the same memory area. CETS [88] assigns a unique ID to each live object and a pointer to the object is associated with the ID. The IDs are stored in a global dictionary. Together with SoftBound [89], a pointer-based spatial memory safety solution, CETS guarantees near complete memory safety. The average overhead is 48% solely and with SoftBound+CETS is 2x. As mentioned

in § 2.1.1, these tools have false violations when pointers are updated in external un-instrumented modules.

Approaches in both categories are still heavy for practical deployment and even for debugging for some benchmarks. Some approaches narrow detection coverage down for low run-time and memory overheads. Cling [4] suggests a customised dynamic memory allocator replacing malloc routines. It enforces type-safe memory re-use among only objects with same type and alignment. It does not target detection of all dangling pointers; instead it aims at preventing use-after-free attack exploiting combined vulnerabilities: dangling pointers and type confusion errors. Since it is embodied in the memory allocator, it detects only temporal memory errors of heap objects.

#### 2.1.3 Architectural Support and Capability Model

Memory protection systems such as Mondrian Memory Protection [139], Hardbound [30], Capability Hardware Enhanced RISC Instructions (CHERI) [135], M-Machine [21], and industrial approaches such as Intel's Memory Protection Extensions (iMPX) [53] and Arm's Memory Tagging Extension (MTE) [8, 9] have been proposed for architectural support for *fine*-grained memory safety.

Mondrian [139] is a memory protection model layered atop page-based virtual memory, to facilitate multiple protection domains. The page table is supplemented by a Protection Look-aside Buffer (PLB) for managing permissions and a set of sidecar registers are paired with general-purpose registers to reduce PLB pressure. This removes requiring userspace ISA changes to support Mondrian, enhancing incremental deployment.

Mondrian provides *address validity* that associates protection properties with regions of *address space* (mentioned in § 2.1.1) rather than a perpointer basis. It pads all *allocations* to introduce *guard regions* like MMU guard pages. Smaller pads are possible than with pages, while reducing the threshold at which most overflows can be detected. This however prevents the approach from providing protection for sub-allocations such as array entries or individual stack frames, and this may undermine finergrained protection. This is particularly a concern today when many classes of exploitable security vulnerabilities are premised on overflows with attacker control over inputs to arithmetic. In addition, Mondrian relies on supervisor mode to manage its protection table. This demands a domain switch for each allocation and free event so protection-domain scalability is limited – each domain requires its own complete protection table, each with substantial memory and initialization expense.

Hardbound [30] is a hardware-assisted *fat-pointer*. The approach provides pointer-based memory safety, not address validation or object-based safety, thus provides finer-grained protection than Mondrian. Hardbound utilises a *shadow space* to store the base and bounds for each pointer-aligned virtual memory location, and another metadata space of *tag bits* to identify pointers in order to reduce the overhead of non-pointers. Bounds information is initialized by the modified software – a memory allocator for heap objects and ideally also by a compiler for stack and global objects. The metadata are then propagated and validated by the hardware i.e. a simulated in-order processor propagates bounds into the shadow table via registers and verifies bounds, when pointers are dereferenced. Un-instrumented libraries and applications will experience less mitigation.

Hardbound provides compatibility: its executables can run on legacy hardware and ABIs are maintained by retaining native pointer size. However its fat pointers are *forgeable*: an instruction adding or modifying the bounds information allows arbitrary bounds, and the tables are accessible via virtual memory. As a result, Hardbound pointers do not constitute a protection domain. Hardbound is also a *CISC* design that proposes a microcode implementation, and requires transactional memory to write to three table entries atomically.

Intels Memory Protection Extensions (iMPX) [53] provides Instruction Set Architecture (ISA) for spatial memory safety. They describe additions to the x86 ISA to provide hardware-acceleration for compiler-based memory protection with *disjoint metadata*. As with Hardbound, bounds information *per pointer* is stored in architecturally-supported shadow tables or also in software-defined locations (adjacent to the pointer itself) and bounds checking is performed using explicit instructions.

MPX does not support pointer compression. Each 64-bit pointer consumes four metadata: base, upper bounds, the expected pointer value, and 64 reserved bits. The expected pointer is used for comparison with a pointer value after a pointer returns back from external modules. If there is a mismatch, MPX drops tracking the pointer. MPX sacrifices memory efficiency for compatibility with legacy code which may not update bounds, unlike Hardbound. MPX does not address use-after-free errors but supports typecast checking, making it one of the strongest spatial memory safety enforcements.

Armv8.5-A [8, 9] introduced a new feature called Memory Tagging. ARMv8.5-MemTag (MTE) provides architectural support for memory protection using lock and key access to memory. Tagging memory implements the lock and pointers (virtual addresses) are modified to contain the key. Memory access is permitted only if the key matches the lock. Memory locations are tagged by adding *four* bits of metadata to each 16 bytes of physical memory (Tag Granule). MTE supports random tag generation and pseudorandom tag generation based on a seed. Due to the limited number of tag bits available (4 bits), the same tag may be allocated for different memory allocations for any specific execution, which causes false negatives. In the aspect of exploitations, the random 1/16th chance on an individual access rapidly disappears to an acceptable level over the course of tens of operations but still provides a usable channel that can be exploited over multiple similar systems in a structured attack. In order to implement the key bits without requiring larger pointers, MTE uses the Top Byte Ignore (TBI) feature of the Armv8-A Architecture. With TBI enabled, the top byte of a virtual address is ignored when using it as an input for address translation. This allows the top byte to store metadata and four bits of the top byte are used to provide the key.

The memory bandwidth impact will depend greatly on the underlying hardware architecture and could be close to zero if the tags are largely implemented in separate hardware resources and blocks are normally cleared on allocation. In addition, the code overheads for heap operations is small but users may prefer to avoid the run-time management overheads by disabling MTE for stack operations.

*Capability-based security* is a different concept of security models. First of all, a *capability* (known as a key) is a communicable and unforgeable token of authority and capability-based security refers to the principle of designing user programs such that they directly share capabilities with each other according to the principle of least privilege, and to the operating system infrastructure necessary to make the transactions secure.

A capability defines a protected *object reference* which grants a user process *access rights* to interact with an object e.g. reading data associated with an object, modifying the object, and executing the data in the object as a process. The capability logically consists of a reference that uniquely identifies a particular object and a set of access rights and a user program must use the capability to access an object. This capability model can be implemented in a number of different ways: operating systems [29, 62, 137, 115], languages [3, 84], and hardware [140].

M-Machine [21], one of the early systems, is a 64-bit tagged-memory capability system implementing *guarded pointers* tracking pointers (§ 2.1.1). M-Machine pointers are unforgeable. They define a protection domain within a single address space, and support protection-domain switching. It compresses a fat pointer to 64 bits: only power-of-two aligned and sized segments are supported therefore padding is required for common structures that break binary layouts.

Capability Hardware Enhanced RISC Instructions (CHERI) [140] is a hybrid capability model that extends the 64-bit MIPS ISA with *byte*granularity memory protection. The key features are a capability coprocessor and tagged memory. The coprocessor supports 32 compiler-managed capability registers, each 256-bit wide, holding capabilities. For memory safety, CHERI implements hardware fat pointers in the form of capabilities. Each memory capability holds the base and length fields, describing a segment of memory, and the permissions field indicating an allowed permission for the region such as load data, store data, execute, and load and store for capabilities. It avoids race conditions, which challenged fat pointers, by updating capability fields and tags atomically.

Capability models must preserve *capability integrity*, while allowing userspace management, i.e. capabilities in memory must not be corrupted by general-purpose stores. CHERI implements *tagged memory* to protect inmemory capabilities. Valid capabilities are identified by an extra tag bit associated with each 256-bit location. Any non-capability store clears this bit, protecting capabilities in memory without appealing to kernel mode. Regional separation [137, 62] is another way to protect capabilities: defining memory regions that can store capabilities distinct from those that can store data. This has limitations, since most programming languages allow pointers and user data neighboring.

Incremental adoption of memory protection systems is critical but compatibility has challenged the deployment of capability systems. CHERI improves earlier capability systems with limited adoption, by hybridizing capability-based addressing with a RISC ISA and MMU-based virtual memory. It provides both *fine*-grained protection as well as *compatibility*.

# 2.2 Type Safety

A program is called *type-safe* when it never explicitly or implicitly converts values from one type to another. One way to ensure type safety of a program is to use type-safe languages. However due to the comparably poor performance of those languages, unsafe system languages such as C or C++ are still widely used for high-performance systems.

Type conversion in C/C++ is sometimes required and useful despite its risk to undermine the integrity/safety of a program. For example, implicit type conversion from an array to a pointer to the 1st element of it (array decay), the result of a floating pointer operations stored in an int-typed variable, or unsigned int value passed to a function taking a signed int. These unsafe type conversions may cause data loss or re-interpretation of a value, therefore we make sure that every memory object including a variable, function argument, and function return value hold an acceptable kind of data; and operations involving values of different types, informally speaking, *make sense* and do not cause data loss, incorrect interpretation of bit patterns, or memory corruption. Type confusions are often combined with dangling pointers for attacks – the memory area of the deallocated object (the old object) is reused by another object (new object). The type mismatch between the old and new object can allow the attacker to access unintended memory.

Several approaches [36, 46, 56, 60, 69] have been proposed to prevent violations of *spatial* memory safety through unsafe typecasting. Those can be

categorised into two depending on if they are based on per-object (pointer) metadata or vtable pointers.

One kind of approach [15, 31, 124, 149] is based on vtable pointers embedded in objects in C++. These approaches save run-time overhead by avoiding manipulation of per-object (or pointer) metadata, that significantly slows down many run-time verification systems. However they usually do not support type checking between non-polymorphic classes, not having a vtable, without breaking binary compatibility. Control-Flow Integrity (CFI) [128, 54, 130, 39] prevents some of these exploits by verifying all indirect control flow transfers within a program to detect control-flow hijacking. However, these techniques address the type confusion problem only partially if control flow is hijacked, i.e., they detect usage of the corrupted vtable pointer, ignoring any preceding data corruption.

The other approaches [46, 93, 56, 60] are based on tracking live objects or pointers. The solutions track individual objects or pointers and store/utilise per-object (per-pointer) type information. Most of them, except fat pointers, secure interoperability with un-instrumented modules and support non-polymorphic classes. However, they incur high run-time overhead to manage metadata. Like deterministic bounds checking, the approaches suggested their own metadata management mechanism to reduce performance loss. This research focuses on the second category of type confusion verification based on per-object (or pointer) metadata.

Type safety enforcements based on per-object/pointer type metadata focus type conversions taking advantage of features of type hierarchy, since the majority of typecasts in C/C++ programs are either *upcasts* (conversion from a descendant type to its ancestor type) or *downcasts* (in the opposite direction). Upcasts are considered safe, and this can be verified at compile time, since if a source type of upcasts is a descendant type, then the type of the allocated object at runtime is also a descendant type.

In contrast, the target type of a downcast may mismatch the run-time type. If a target type is a descendant type of the target type, an access to the object after downcasts may cause *type confusion*, a security vulnerability including internal overflows. Recognition of the run-time type is undecidable, so downcasts require run-time checking to prevent type confusion.

One of the challenges of run-time typecast verification is *pointer-to type mapping*. Typecast pointers to different types may have moved to one of the sub-fields of its referent object and run-time checkers should map the pointer to the corresponding type at the offset. This requires an efficient management of both (1) per-object type information and (2) per-type memory layout. We need to associate an individual object (or pointer) with its object type and map a pointer to the object's type using type information in the metadata storage, which unfortunately causes high overheads. A pointer then should be mapped to a type at the offset to a target type is *safe*.

Another challenge is to determine what type conversion is *safe* e.g. to define what upcasts and downcasts are in C language. First of all, since C language does not support type hierarchy, unlike C++, we should define the hierarchy in C and their relation with other types. For example, arbitrary pointers are frequently converted to void\* and passed inter-functionally as an argument, which is allowed and considered safe. In CCured [93], void is considered to be an *empty* structure and a *prefix* of any type, that is, any type is a *sub-type* of void. Under this definition of sub-typing, it is allowed to *upcast* from a pointer in any type into void\*. The pointer is then typecast from void\* to other types (desirably restoring its type) for access, requiring type confusion checking at runtime. It is more tricky to judge valid casts between non-void types. Strict rules on type conversion can cause false positives, while loosening them can bring false negatives.

CCured [93] ensures both memory and type safety enforcements (§ 2.1.1). This approach observed that most typecasts in real programs are *safe upcasts* (from a pointer to object to a pointer to the first sub-object), and the rest is mostly *downcasts* (in the opposite direction) in C programs written in the object-oriented style. CCured adopted *physical sub-typing* [22] defining type hierarchy in C by flattening aggregate types to *primitives (atomics)* to reduce wild pointers (§ 5.2).

CCured is based on *fat pointers* [11, 57, 93]. Approaches tracking an individual pointer [89, 53, 87] provide strong and precise memory/type safety allowing to associate a pointer with any corresponding type i.e. a higher composite type or sub-type. However it suffers heavier run-time overhead

to manipulate per-pointer metadata. In addition, embedding metadata inside objects opens a vulnerability of polluting metadata through memory writes following bad typecasts. CCured addresses this by updating/checking tags at memory access, causing further overhead. Although amongst pointer-tracking approaches, using fat pointers guarantees the high performance, the compatibility issue has not been resolved yet. More modern memory/type safety enforcements store per-object information in disjoint metadata storage to secure the compatibility.

TypeSan [46] is designed for an always-on solution for explicit type checks in C++. This approach, inspired by CaVer [69], focuses on conversion from an instance of a parent class to a descendant class. Downcasting is frequently used if the parent class lacks some of the fields or virtual functions of the descendant class. When the program subsequently uses the fields or functions of the descendant class that do not exist for a given object, it may use data as a regular field in one context and as a virtual function table (vtable) pointer in another.

TypeSan uses the per-allocation (per-object) paradigm [18, 33, 6, 47, 114] and is composed of two services: type management and metadata storage. Firstly, type management service is responsible for associating type layout with each allocation site and validating downcast operations with these layouts. This service includes (1) a type layout table holding mappings of unique offsets to data fields corresponding to nested types and (2) a type relation table holding compatible types for each class. The second service is metadata storage mapping from object base addresses to type layout tables. Like many other modern run-time verification tracking objects or pointers, the approach creates shadow space [6, 47, 68, 89, 114] for *pointer-to-type* mapping. TypeSan is based on *variable* compression ratio memory shadowing [47]. It allows more detailed memory allocation than other shadow space but it also mandates a uniform alignment. Approaches using shadow space spend more memory space to reduce the run-time overheads with the small increase in dynamic instructions. The trade-off can be merely an issue for debugging/testing during development, but still makes it less useful as an always-on solution on memory-intensive systems such as on embedded systems or IO-servers.

Other approaches [60, 105] exploit debugging infrastructure and instrument the programs allocators. Their analysis is invoked from a debugger, rather than running continuously during execution. Unlike other approaches checking at typecasts followed by pointer dereferences, Libcrunch [60] checks pointer creations not uses, reducing the number of run-time checks, since pointer creations are much less frequent than dereferences. This imposes false negatives since a pointer can be typecast before use. In addition, it unwraps structure type only one level, unlike CCured or one of our prototypes (spaceMiu) unrolling down to primitive types as in physical sub-typing. Libcrunch's check is relatively strict, because there are hardly real code which requires the full permissiveness of physical typing. Some other approaches [19, 76] attach physical types to machine words, unfortunately causes high overheads ( $10x \sim 100x$ ) [145].

One of the challenges of type safety enforcement is to define type hierarchy for C programs and safe/unsafe typecast unlike array out-ofbounds checking which has more straightforward definitions of valid/invalid memory access. Judgements of typecasts in C programs may differ depending on C programmers' coding style and intention.

## 2.3 Control-Flow Protection