# Design And Implementation Of Multibit Flip-Flop Utilizing Verilog Hdl

SHAIK HAFEEJA BEGUM

M.Tech Student, Dept of ECE, Priyadarshini Institute of Technology and Management, Pulladigunta, Guntur, A.P, India S.VIJAY

Assistant Professor, Dept of ECE, Priyadarshini Institute of Technology and Management, Pulladigunta, Guntur, A.P, India

*Abstract:* Power consumption is an important issue in modern low-power, high-frequency VLSI design. Joining these methods that group account flows and settings also allows money control. We are considering the MBFF alignment and its collaborative energy with the FF information for clock change probabilities. A probabilistic model is triggered to increase normal vital sign buffers by collecting FFs by extending your request for information to the probabilities of turning the clock. Front-end configuration flow, guided by reflections on the physical design of a 65nm 32-bit 28nm MIPS mechanical system processor. It was shown in 24% and 18% individually, contrasting and specifically with the common FF. On mutual funds it was due to the DDCG format in the MBFF.

Keywords: Clock Power Reduction; SBFF; MBFF; Merging; FIR Filter; Multipliers; Adders;

## INTRODUCTION

You don't want the benefits of free MBFFs. By sharing the normal controllers, the clock rotation becomes corrupted, causing a larger tide and a longer flow from the clock to the Q, delaying the tpCQ. To remedy this, the internal MBFF drives can be increased with some additional power. Provided the implementation of MBFF at the RTL configuration level to avoid design inference hurdles caused by displaying MBFF in the backend configuration order. Since the normal to hourly information change ratio of FFs is small, it does not extend from 0.01 to 0.1, the clock control reserve funds reliably exceed the short force penalty. MBFF brings together reflections of logical, useful and FF action [1]. While the assembly of the FFs was considered entirely at the coordination level, the initial implications of the size of the MBFF group and how it affects the clock gate (CG) have attracted little attention. This summary answers two queries. The first is that the ideal k-segment set should be MBFFs (DDCGs) pooled throughout the day. The second is the way mutual funds operate in light of the 24-hour information exchange rate (also called the probability of action and information change). Each FF joins the threads obtained from the 1-bit FF model. The cables and information related to FF are related to their rationality, while the conditions of FF can move without taking position. This locale displays mobile data for FTF and MBFF integration. The combination of 2-MBFF is detailed as a combined FF promoter. Various reflections for the clock tree design. In addition to energy savings, the CG was introduced, however, the relationship between the CG technique and exercise and PA pooling was not definitive. Wang et al. Represents another work center calculation that has been verified to alter the information to measure normal force [2]. Although

information exchange is used as an optional standard in FF post-position collection, our procedure is to use it as a main aggregation procedure and do it at the RTL level for preposition. Additionally, it has dramatically reduced layout space by linking affinity with design proximity, while incorporating RTL is free of such needs. Equally important, having standardized design coordination as a key component reduces the mapping of the driving force to MBFF. Our basis is to distinguish between the MBFF clock and the advancement in the RTL setting level, in light of the basic and compositional movement reflections, and in particular, the FF.

## RELATED STUDY

Initially, due to the development of the built circle, this prophecy was long expected to be important to this day. Its functions are generally considered Moore's laws. The effects of Moore's Law were deliberately studied and at the end of the investigation it was concluded that due to the number of sections of the chip, the energy significantly discoverv will increase [3]. Furthermore, the intensity of the intensity is expected to be equivalent to the heat of the rocket channel. Therefore, reducing the control in existing VLSI engineers has become an important component. By changing the order cells to a rectangular area, the covered language was effectively recorded. Put each molecule in a group at the beginning. Among the groups, two groups that had smaller gaps were chosen. These groups were very close. This procedure was modified so that the group only had one group. This mounting procedure limits the length of the cable. In conventional assembly calculations, the recommended assembly calculation gave a tradeoff between a decrease in the number of cut pieces and an increase in the length of the flag wire.

Lower flag wire length. A robust two-stage approach has been proposed to incorporate 1-bit flip-flops that can be reached on some multiple bits. Amid the convergence of two flip-flops on a multi-piece core, excess reflectors were evacuated. An iterative merging process has been suggested to create multi-bit binding flip-flops. Each grouped chart header was initially organized in the expansion request [4]. Mix sets are integrated into the header with the smallest score. The merge scheme has been modified by removing the selected headers and including the merge heads. The spacing of each flap was treated to determine the length of the flat wire. Table reserved to observe lemonade. From the table, groupings were obtained for the extracted rate. The MBFF assembly problem was changed after FF layout of a segment using MBFF. Timing-Violation-Distance (TVFD) was used to obtain the possible language. By combining one-piece FF with TVFR, optimal strength and area were obtained. The MBFF pooling loads based on the crossover diagram have been expanded to find the largest pool and a decreasing MBFF pooling rate. Target groups of the MBFF work [5]. The length of the flag wire has also been considered. The progression was phases, for example, a simplified research step and a separate refinement step. The continuous and differential objective work is framed in the explanatory optimization step. In the post-position MBFF assembly techniques, a limited capacity of the proposed approach of 20% was used, as well as a reduction in cable length by 25%. The negative recession networks were assigned higher net weights than the positive depression networks. The movement of the flip-flops is based on the results of the MBFF aggregation for position. There were several major emphases on mixing individual slippers. The bit power output cell was considered as the ideal estimate of the internal circuit. The ends were arranged in three species, for example, inner circles larger than average, free of defects, and small in size. A larger than average group produced a pure measurement faction. The smaller club has joined forces with the perfectly sized flip lemon faction. Each handful of flip flops was given fickle dogs with constipation. Each flip flops was connected to remain using two pseudo-networks. Coverage between cells was limited [6]. To deal with cell insufficiency, a stirring clutch was sent. The overall site flow was moderated with a cover file

#### AN OVERVIEW OF PROPOSED SYSTEM

The proper answer is input, which means that we make the circuits in the circuit diagrams indirectly give estimates based on them. If this criticism is true, then the circuit has steady states and, in the absence of negative, the circuit tends to influence. For now, let's think about what happens from 1 to 0. For this to work, accept that the information continues as before in the middle of a short period of time just before the timestamp changes. The main thing that happens and the inputs to the contribution kills, that is, heartless to the additional changes in the input. The clock began to evolve. A minute later, he changed the reflective clock flag on the slave's doors and gates. These inputs are opened, allowing x. AC yields protein at the x value of the slave. Estimating x for Slave, and therefore, each flip-flop is guessing the input before starting the rotation. We can say that the clock converts the multiplying contributions into returns to circulation. As such, there is no quick method available to earn income at any given time. Income is due to progression from 1 to 0 years. Finally, let's see what happens when the clock goes from 0 to 1. To start, open and enter the ace din position. When the D grade reaches ace, the flag change reaches the slave's doors and gates and shuts them down before it receives the reasonably modified slaves. Therefore, the slave maintains his old reputation. All things are taken into account, because the income does not change because nothing is seen. Instead of starting now and in the future, the certificate authority is available to change the information.

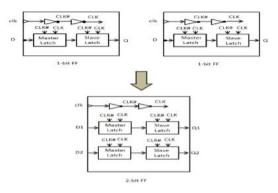

Fig.3.1. Merging two 1-bit FFs to one 2-bit FF.

Affinity for 1-bit FF is implemented using the clock tree topology. Through position assertions, the FFs dynamically converge indicating the first topology of the clock tree. This methodology provides a reduction of control without spoiling the execution of the plan; however it contains limitations that must be addressed in true schemes of convergence of financial elements...

## CONCLUSION

The Knowledge Driven Clock (DDCG) and Multi-City Flip-flops (MBFF) are two independently managed systems of low control plans. Joining these methods that group account flows and settings also allows money control. We are considering the MBFF alignment and its collaborative energy with the FF information for clock change probabilities. A probabilistic model is

triggered to increase normal vital sign buffers by collecting FFs by extending your request for information to the probabilities of turning the clock. Front-end configuration flow, guided by reflections on the physical design of a 65nm 32-bit 28nm MIPS mechanical system processor.

### REFERENCES

- K.- J. Cho, K.- C. Lee, J.- G. Chung, and K. K. Parham, "Plan of low-blunder settled width adjusted corner multiplier," IEEE Trans. Large Scale Integr. (VLSI) Syst., vol. 12, no. 5, pp. 522–531, May 2004.

- [2] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-roused uncertain computational squares for effective VLSI execution of delicate figuring applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 850–862, Apr. 2010.

- [3] A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Plan and examination of inexact blowers for duplication," IEEE Trans. Comput., vol. 64, no. 4, pp. 984–994, Apr. 2015.

- [4] S. Narayanamoorthy, H. A. Moghaddam, Z. Liu, T. Stop, and N. S. Kim,"Energyeffective inexact augmentation for computerized flag preparing and grouping applications," IEEE Trans. Large Scale Integr. (VLSI) Syst., vol. 23, no. 6, pp. 1180–1184, Jun. 2015.

- [5] G. Zervakis, K. Tsoumanis, S. Xydis, D. Soudris, and K. Pekmestzi, "Outline proficient surmised increase circuits through halfway item aperture," IEEE Trans. Large Scale Integer. (VLSI) Syst., vol. 24, no. 10, pp. 3105–3117, Oct. 2016.

- [6] P. Kulkarni, P. Gupta, and M. D. Ercegovac, "Exchanging precision for control in a multiplier engineering," J. Low Power Electron., vol. 7, no. 4,pp. 490– 501, 2011.