# ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ

#### ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟϔΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# Optimizing ECG Signal Analysis by building FPGA-based accelerators using High Level Synthesis

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

της

Κωνσταντίνας Ι. Κολιογεώργη

Επιβλέπων: Δημήτριος Ι. Σούντρης

Αναπληρωτής Καθηγητής

#### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟϔΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

#### Optimizing ECG Signal Analysis by building FPGA-based accelerators using High Level Synthesis

#### $\Delta$ ΙΠΛΩΜΑΤΙΚΉ ΕΡΓΑΣΙΑ

της

Κωνσταντίνας Ι. Κολιογεώργη

Επιβλέπων: Δημήτριος Ι. Σούντρης Αναπληρωτής Καθηγητής

Εγκρίθηκε από την τριμελή επιτροπή την 22η Ιανουαρίου 2016.

Δημήτριος Ι. Σούντρης Κιαμάλ Ζ. Πεκμεστζή

Αναπληρωτής Καθηγητής

Καθηγητής

Γιώργος Οιχονομάχος Επίκουρος Καθηγητής

Αθήνα, Ιανουάριος 2016.

Κωνσταντίνα Ι. Κολιογεώργη Διπλωματούχος Φοιτήτρια Εθνιχού Μετσόβιου Πολυτεχνείου

Copyright@ Κωνσταντίνα Ι. Κολιογεώργη, 2016

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοποκό σκοπό πρέπει να απευθύνονται προς την συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν την συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

# Contents

| $\mathbf{\Sigma}$ | ύντο         | ρμη περίληψη                                                                     | vi            |

|-------------------|--------------|----------------------------------------------------------------------------------|---------------|

| A                 | bstra        | act                                                                              | vii           |

| $\mathbf{E}$ :    | κτετ         | αμένη Περίληψη                                                                   | r <b>ii</b> i |

| $\mathbf{A}$      | ckno         | wledgements                                                                      | ʻ <b>ii</b> i |

| Li                | st of        | Figures                                                                          | ix            |

| Li                | ${ m st}$ of | Tables                                                                           | xii           |

| 1                 | Inti         | roduction                                                                        | 1             |

| 2                 | Pro          | blem Overview                                                                    | 3             |

|                   | 2.1          | ECG Analysis Flow                                                                | 3             |

|                   | 2.2          | Related Work                                                                     | 7             |

| 3                 | The          | eoritical Background                                                             | 9             |

|                   | 3.1          | Background Information on SVM classifier                                         | S             |

|                   | 3.2          | High Level Synthesis                                                             | 11            |

|                   | 3.3          | Zynq Evaluation and Development Board Specifications                             | 16            |

| 4                 | Cod          | de Restructuring for HLS                                                         | 18            |

|                   | 4.1          | Advancing Coarse Level Parallelism in HLS                                        | 18            |

|                   |              | 4.1.1 Parallelization Technique                                                  | 18            |

|                   |              | 4.1.2 Results                                                                    | 22            |

|                   | 4.2          | Advancing Instruction Level Parallelism through arithmetic operation reshaping . | 25            |

|                   |              | 4.2.1 Parallelization Technique                                                  | 25            |

|                   |              | 4.2.2 Results                                                                    | 28            |

| 5  | Exp   | ploration of HLS Directives          | 30 |

|----|-------|--------------------------------------|----|

|    | 5.1   | Selection of Optimization Directives | 30 |

|    | 5.2   | Application on Original Code         | 32 |

|    |       | 5.2.1 Impact of each directive       | 33 |

|    | 5.3   | Comparison of Implementations        | 44 |

|    | 5.4   | Optimal Configurations               | 47 |

| 6  | Imp   | olementation on Zedboard             | 50 |

|    | 6.1   | Implementation Description           | 50 |

|    | 6.2   | Results                              | 55 |

| 7  | Cor   | nclusion                             | 57 |

|    | 7.1   | Summary                              | 57 |

|    | 7.2   | Future Work                          | 58 |

| Re | efere | nces                                 | 59 |

## Σύντομη Περίληψη

Το ηλεκτροκαρδιογράφημα (ΗΚΓ) λόγω της στενής συνάφειάς του με τη φυσιολογία της καρδιάς είναι από τα βασικά βιοσήματα που χρησιμοποιούνται για την παρακολούθηση της κατάστασης της υγείας ενός ανθρώπου. Συνεπώς, η ανάλυσή του και η ερμηνεία του έχουν καθιερωθεί ως ένας σημαντικός κλάδος στη σύγχρονη ιατρική και αυτό έχει οδηγήσει στην εκπόνηση πολλών μελετών σχετικών με τη ψηφιαχή επεξεργασία του. Λόγω της πολυπλοχότητας της δημιουργίας μοντέλων αχριβείας για την αξιολόγηση και την πρόβλεψη της κατάστασης της καρδιάς, οι Τεχνικές Μηχανικής Εκμάθησης έχουν επιχρατήσει στον τομέα της Ανάλυσης του ΗΚΓ. Οι Μηχανές Διανυσμάτων Υποστήριξης (Support Vector Machines- SVM) συγκεκριμένα είναι ιδιαιτέρως διαδεδομένες λόγω της ακριβούς πρόβλεψης και της ενδιαφέρουσας υπολογιστικής δομής τους. Επιπρόσθετα η ανάγκη συνεχούς παρακολούθησης της κατάστασης της καρδιάς και μάλιστα σε πραγματικό χρόνο έχουν αυξήσει τις απαιτήσεις για επιτάχυνση της ψηφιαχής ανάλυσης του ΗΚΓ και πραγματοποίησής της σε σύστημα χαμηλής κατανάλωσης ενέργειας. Στόχος αυτής της διπλωματικής εργασίας είναι η αξιοποίηση των δυνατοτήτων του HLS για τη δημιουργία αποδοτικών SVM ως επιταχυντές σε υλικό. Μελετάται ο εντοπισμός αρρυθμιών στο ΗΚΓ χρησιμοποιώντας ως βάση δεδομένων μια βάση δεδομένων για ΗΚΓ που έχει αναπτυχθεί μέσω κοινής συνεργασίας των πανεπιστημίων ΜΙΤ και ΒΙΗ. Σε πρώτο επίπεδο ο αρχικός κώδικας αναδομείται με χριτήριο την επιτάχυνση ώστε να δημιουργηθεί αποδοτιχός επιταχυντής. Σε δεύτερο επίπεδο εξερευνώνται οι τεχνικές βελτιστοποίησης του εργαλείου HLS οι οποίες εφαρμόζονται στον αρχικό και στον τροποποιημένο κώδικα για περαιτέρω βελτίωση του ως προς μετρικές επίδοσης και χρησιμοποίησης πόρων. Ο συνδυασμός των δύο επιπέδων επιφέρει κέρδος έως και 98% σε χρόνο εκτέλεσης σε σύγχριση με το χρόνο εχτέλεσης του αρχιχού χώδιχα ενώ παρέχονται στο σχεδιαστή τα βέλτιστα σημεία κατά Pareto με βάση τα οποία μπορεί να επιλέξει μια υλοποίηση ανάλογα με τις απαιτήσεις της εκάστοτε εφαρμογής σε ταχύτητα εκτέλεσης και χρησιμοποίηση πόρων.

Λέξεις Κλειδιά: Σχεδιασμός Ιατρικών Ενσωματωμένων Συστημάτων, Ανάλυση Ηλεκτροκαρδιογραφήματος, Τεχνικές Μηχανικής Μάθησης, Μηχανές Διανυσμάτων Υποστήριξης, HW/SW σχεδιασμός, Αναπτυξιακή Πλακέτα Zynq Evaluation and Development Board, Εργαλεία Σύνθεσης Υψηλού Επιπέδου (HLS)

#### Abstract

One of the most fundamental and crucial biological signals for monitoring and assessing the health condition of a person is the Electrocardiogram (ECG) due to its inherent relation to heart physiology. Consequently, its analysis and interpretation has been established as an important field in modern medicine and this in turn has spawned various inter-disciplinary studies including digital processing analysis of the signal. Given the complexity of deriving exact models for assessing and predicting the heart's condition, machine learning techniques have recently dominated the field of ECG analysis. Support Vector Machines based classifiers especially, have grown very popular as the key element of machine learning based ECG analysis due to their capability of accurate prediction and their interesting computational structure. Last but not least, constant monitoring and real-time heart condition assessment have imposed new requirements for acceleration and low power execution of a digital ECG analysis flow system. Taking all these into consideration, in this work we focus on utilizing High Level Synthesis capabilities to produce efficient SVM hardware accelerators. Our case study is arrhythmia detection using MIT-BIH ECG signal medical database. We show that as a first step, the original code under acceleration can be re-structured in order to create instances which are efficiently transformed into a HW accelerator. As a second step, an exploration is performed on the transformed code in order to determine which HLS directives produce the best outcome in terms of various performance and resources utilization metrics. Our combined analysis shows that we can achieve results of up to 99% execution latency gain compared to the original SVM code and the designer is given a set of Pareto Optimal design points in order to decide the best trade-off between gains in latency and increase in utilized FPGA HW resources.

Keywords: Medical embedded system design, ECG analysis, machine learning, Support Vector Machines, HW/SW codesign, Zynq Evaluation and Development Board, High Level Synthesis

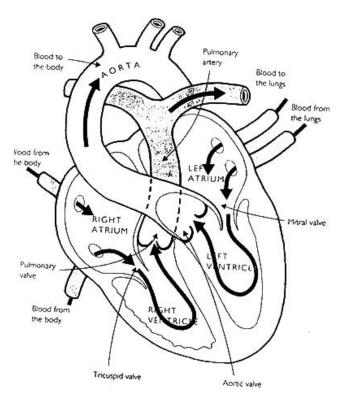

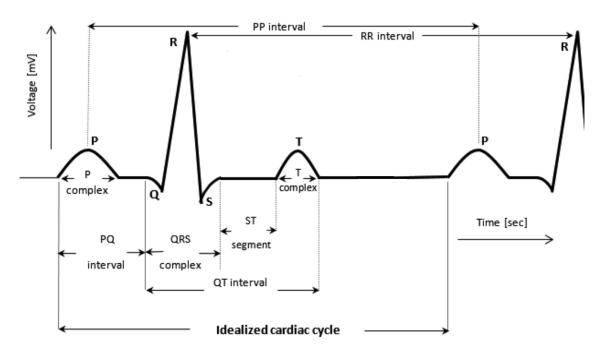

## Ροή Ανάλυσης του ΗΚΓ

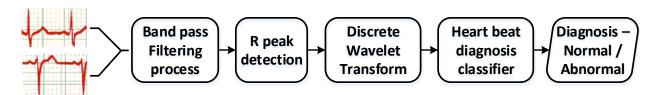

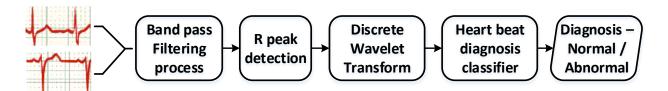

Η μορφή του ΗΚΓ και ο καρδιακός ρυθμός που εξάγεται από το ΗΚΓ είναι δηλωτικά της κατάστασης της καρδιάς. Στην ουσία το ΗΚΓ αποτυπώνει διαδογικούς καρδιακούς κύκλους. Ο καρδιακός κύκλος (διαστολή, συστολή, ηρεμία) συντονίζεται από ηλεκτρικά σήματα που παράγονται από κατάλληλα κέντρα διέγερσης της καρδιάς. Υπάρχουν τρία βασικά ηλεκτρικά σήματα που εμφανίζονται στο ΗΚΓ: το έπαρμα P, το σύμπλεγμα QRS που αποτελείται από τις κορυφές Q,R,S και το έπαρμα Τ. Αυτά τα σήματα είναι στην πραγματικότητα μεταβολές του ηλεκτρικού δυναμικού διαφόρων περιοχών της καρδιάς και άρα το ΗΚΓ απειχονίζει την ηλεχτρική δραστηριότητα της χαρδιάς. Τα επάρματα αυτά χαι οι αποστάσεις μεταξύ τους έχουν συγκεκριμένη χρονική διάρκεια και μορφολογία. Οποιαδήποτε παρέκκλιση από τη φυσιολογική μορφολογία τους πρέπει να μελετηθεί καθώς μπορεί να είναι δείγμα παθολογικής βλάβης. Η καρδιακή αρρυθμία είναι η πιο συνηθισμένη καρδιακή βλάβη και είναι η διαταραχή του καρδιακού ρυθμού. Η αρρυθμία μπορεί να είναι από ασυμπτωματική μέχρι κρίσιμη για την ανθρώπινη ζωή. Για αυτό το λόγο χρίνεται απαραίτητη η μελέτη του ΗΚΓ, ως μέσο διάγνωσης αρρυθμιών. Οι αρρυθμίες είναι μεμονωμένα περιστατικά που εκδηλώνονται σε τυχαίες χρονικές στιγμές. Επομένως είναι αναγκαία η μελέτη του ΗΚΓ μεγάλων χρονικών διαστημάτων. Ο μεγάλος όγκος δεδομένων προς μελέτη καθιστά απαραίτητη τη χρήση τεχνικών μηχανικής μάθησης για την επεξεργασία του. Ταξινομητές βασίζονται σε τεχνικές μηχανικής μάθησης για την εκπαίδευσή τους με αυτό το μεγάλο σύνολο δεδομένων ώστε τελικά να μπορούν να διαγνώσουν σωστά την ύπαρξη ή μη αρρυθμίας σε ένα νέο σύνολο δεδομένων ΗΚΓ. Στη συγκεκριμένη εργασία χρησιμοποιείται η βάση δεδομένων αρρυθμίας ΜΙΤ-ΒΙΗ Arrhythmia Database, η οποία περιλαμβάνει παλμούς για τους οποίους έχει γίνει διάγνωση από καρδιολόγους. Η διαδιχασία επεξεργασίας και ανάλυσης του ΗΚΓ για την εξαγωγή των επιμέρους παλμών και των χαρακτηριστικών τους ώστε τελικά να γίνει η διάγνωση χρησιμοποιώντας μοντέλα τεχνικής μηχανικής μάθησης παρουσιάζεται ακολούθως και απεικονίζεται στο Σχ.1.

- Αποθορυβοποίηση: Το σήμα του ΗΚΓ φιλτράρεται για την απομάχρυνση θορύβου που προέρχεται χυρίως από την τροφοδοσία και τις κινήσεις του ασθενή.

- Εντοπισμός κορυφών : Σε αυτό το στάδιο ανιχνεύονται οι παλμοί που απαρτίζουν το φιλτραρισμένο πια σήμα. Η ανίχνευση των παλμών επιτυγχάνεται μέσω της ανίχνευσης των κορυφών R με τη χρήση ειδικών συναρτήσεων.

- Εξαγωγή χαρακτηριστικών: Σε αυτό το στάδιο γίνεται η εξαγωγή χαρακτηριστικών κάθε παλμού, βάσει των οποίων θα γίνει σε επόμενο στάδιο η διάγνωση. Στη συγκεκριμένη διπλωματική ο Μετασχηματισμός Κυματιδίων (Wavelet Transform WT) εφαρμόζεται σε κάθε παλμό ώστε το σήμα να μελετηθεί στο πεδίο της συχνότητας και του χρόνου ταυτόχρονα. Οι συντελεστές που προκύπτουν από το μετασχηματισμό αυτό για κάθε παλμό σχηματίζουν το διάνυσμα

των χαρακτηριστικών κάθε παλμού.

• Ταξινόμηση-Διάγνωση: Σε αυτό το στάδιο το διάνυσμα των χαρακτηριστικών που δημιουργήθηκε στο προηγούμενο στάδιο για τον τρέχοντα παλμό χρησιμοποιείται ως είσοδος σε έναν ταξινομητή για να πραγματοποιηθεί η διάγνωση. Ο ταξινομητής προηγουμένως έχει εκπαιδευτεί χρησιμοποιώντας ένα μεγάλο σύνολο διανυσμάτων χαρακτηριστικών όμοιων με αυτά του προηγούμενου σταδίου. Σε αυτή τη διπλωματική ο ταξινομητής βασίζεται σε Μηχανές Διανυσμάτων Υποστήριξης.

Σχήμα 1: Ροή Ανάλυσης ΗΚΓ

## Θεωρητικό Υπόβαθρο

#### Θεωρία Μηχανών Διανυσμάτων Υποστήριξης

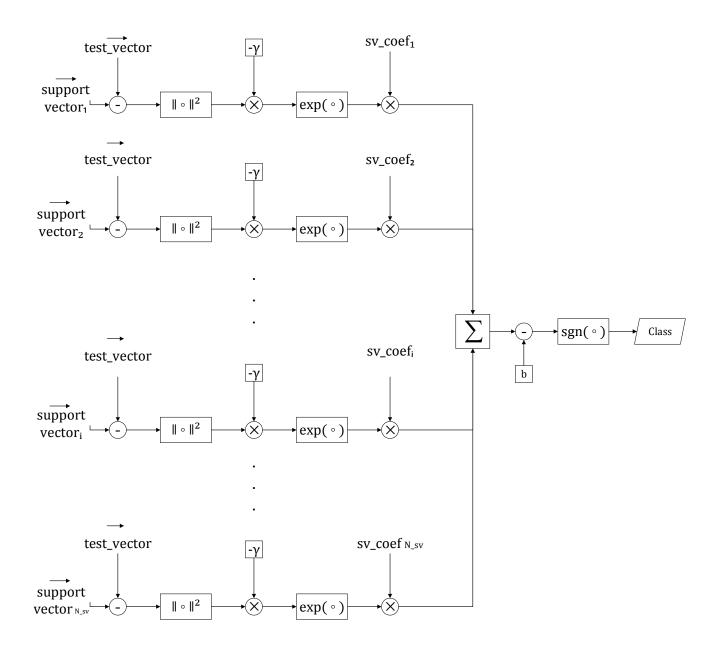

Οι Μηχανές Διανυσμάτων Υποστήριξης (Support Vector Machines -SVM) είναι μοντέλα επιβλεπόμενης μάθησης που εκπαιδεύονται με ένα μεγάλο σύνολο δεδομένων και είναι κατάλληλη για την ταξινόμηση των νέων εισόδων σε δύο υποψήφιες κλάσεις συμπληρωματικές μεταξύ τους. Το σύνολο εκπαίδευσης αποτελείται από διανύσματα με συγκεκριμένα χαρακτηριστικά καθένα από τα οποία διαθέται μια ετικέτα δηλωτικής της κλάσης στην οποία ανήκει. Ένα σύνολο από άλλα διανύσματα με τα ίδια χαρακτηριστικά και γνωστές τις ετικέτες χρησιμοποιείται για να ελεχθεί η ακρίβεια της πρόβλεψης.

Τα SVM εφαρμόζουν αρχικά μια συνάρτηση πυρήνα που ανάγει τα διανύσματα σε ένα χώρο περισσότερων διαστάσεων, όπου είναι πιο εύκολος ο διαχωρισμός τους. Στο χώρο αυτό βρίσκουν ένα υπερεπίπεδο το οποίο αποτελείται από τα διανύσματα που απέχουν μέγιστα από τα διανύσματα που ανήκουν σε κάθε κλάση. Κάθε νέο διάνυσμα ανάγεται σε αυτόν το χώρο, υπολογίζεται η απόσταση του από το υπερεπίπεδο και άρα με βάση τη θέση του σε σχέση με αυτό ταξινομείται στην αντίστοιχη κλάση. Η συνάρτηση πυρήνα είναι καθοριστική για την ακρίβεια και την πολυπλοκότητα του μοντέλου. Λόγω των μη γραμμικών σχέσεων μεταξύ των χαρακτηριστικών του διανύσματος κάθε παλμού χρησιμοποιούμε μη γραμμική συνάρτηση πυρήνα και συγκεκριμένα εκθετικής φύσης.

Ακολουθεί η μαθηματική εξίσωση που περιγράφει τον υπολογιστικό πυρήνα του ταξινομητή και ο αντίστοιχος κώδικας C που την υλοποιεί:

$$Class = sgn(\sum_{i=1}^{N\_sv} (y_i * a_i * exp(-\gamma || \mathbf{x} - \mathbf{sup\_vector}_i ||^2)) - b)$$

(1)

όπου K είναι η συνάρτηση πυρήνα,  $\mathbf x$  είναι το διάνυσμα του παλμού προς ταξινόμηση,  $\mathbf {sup\_vector}_i$  είναι το  $\mathbf i$ -οστό διάνυσμα υποστήριξης και  $y_i, a_i$  είναι τιμές διαφορετικές για κάθε διάνυσμα υποστήριξης και προέκυψαν κατά την εκπαίδευση. Η μεταβλητή b είναι μια μεταβλητή σύγκρισης, αποτέλεσμα της εκπαίδευσης και σταθερή για όλα τα διανύσματα υποστήριξης.

Listing 1: Αρχικός κώδικας ταξινομητή.

const float sv\_coef [N\_sv];

Στον Κώδικα 1 η μεταβλητή  $sv\_coef$  ισοδυναμεί με το γινόμενο  $y\_i$  και  $\alpha\_i$  της εξίσωσης 1. Ο αριθμός των διανυσμάτων υποστήριξης  $N\_sv$  και ο αριθμός των χαρακτηριστικών $D\_sv$  όπως και η επιλογή συνάρτησης πυρήνα έχουν μεγάλη επίδραση στην πολυπλοκότητα. Στην έρευνα αυτή, η εκπαίδευση κατέληξε σε  $N\_sv$  ίσο με 1274 και  $D\_sv$  ίσο με 18.

#### High Level Synthesis

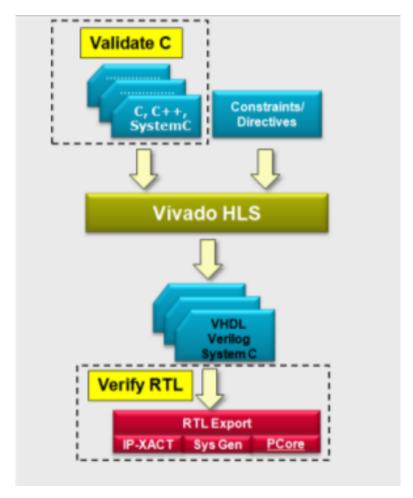

Το HLS είναι ένα σχεδιαστικό εργαλείο που δημιουργεί μονάδες hardware ειδικού σκοπού λαμβάνοντας ως είσοδο την περιγραφή της λειτουργικότητάς τους σε C. Παρέχει έτσι τη δυνατότητα στους προγραμματιστές να επιταχύνουν τα υπολογιστικά απαιτητικά κομμάτια των εφαρμογών τους υλοποιώντας τα ως ξεχωριστές μονάδες σε Field Programmable Gate Array (FPGA). Έτσι μια εφαρμογή μπορεί να εκτελείται στον επεξεργαστή του συστήματος και να καλεί τον επιταχυντή που έχει υλοποιηθεί σε hardware για το πιο απαιτητικό κομμάτι της.

Το πρώτο βήμα χρησιμοποίησης του HLS είναι η ανάπτυξη της εφαρμογής σε γλώσσα προγραμματισμού C, καθιστώντας έτσι πιο εύκολο τον έλεγχο της ορθότητας από ό,τι υλοποιώντας την εφαρμογή σε

γλώσσα περιγραφής υλικού. Ακολουθεί η διαδικασία της σύνθεσης, στο τέλος της οποίας παράγεται η περιγραφή της λειτουργικότητας σε επίπεδο καταχωρητή (Register Transfer Level - RTL). Κατά τη σύνθεση το HLS χρονοδρομολογεί τις εντολές-λειτουργίες του κώδικα και δεσμεύει τους αναγκαίους πόρους για την υλοποίησή τους. Διαθέτει τεχνικές βελτιστοποίησης τις οποίες εφαρμόζει είτε αυτομάτως είτε μετά από εντολή του χρήστη. Δημιουργεί έτσι υλοποιήσεις με υψηλές επιδόσεις και αποδοτική χρησιμοποίηση των διαθέσιμων πόρων. Οι πληροφορίες αυτές υπάρχουν στην αναφορά που παράγεται κατά τη διάρκεια τη σύνθεσης. Με βάση αυτές ο χρήστης μπορεί να διερευνήσει τις παρεχύμενες τεχνικές για να κατασκευάσει μία μονάδα που να ικανοποιεί τις προδιαγραφές σε αποδοτικότητα ταχύτητας και πόρων. Οι μετρικές που χρησιμοποιούνται για την αξιολόγηση του αποτελέσματος αφορούν τον εμβαδόν (area: LUTs, registers, block-RAM, DSPs, flip flops), το χρόνο απόκρισης του επιταχυντή (latency) και το χρόνο που πρέπει να παρέλθει μέχρι η μονάδα να μπορεί να επεξεργαστεί νέα δεδομένα. Οι τεχνικές βελτιστοποίησης αυτών των μετρικών εφαρμόζονται σε διάφορα μέρη του κώδικα, όπως σε συναρτήσεις, βρόχους, πίνακες και περιοχές που περιλαμβάνουν κάποια ή όλα τα παραπάνω μέρη. Όταν ολοκληρωθεί η διαδικασία επιτάχυνσης της μονάδας, εξάγεται σε κατάλληλο φορμάτ για να συμπεριληφθεί στην αρχιτεκτονική άλλων σχεδιαστικών εργαλείων.

Αυτά τα χαρακτηριστικά του HLS το καθιστούν ιδανική επιλογή για τη δημιουργία του ταξινομητή ως επιταχυντή στο FPGA κομμάτι του Zedboard. Χρησιμοποιώντας τον κώδικα του ταξινομητή θα εφαρμόσουμε σε αυτόν δομικές αλλαγές και τις τεχνικές βελτιστοποίησης που παρέχει το HLS προκειμένου να επιτύχουμε τις απαιτήσεις σε χρόνο εκτέλεσης της ανίχνευσης αρρυθμίας. Τα πρώτα στάδια θα εκτελούνται στον επεξεργαστή της πλακέτας και η ταξινόμηση-διάγνωση στον επιταχυντή στο FPGA.

#### Zedboard

Το Zedboard είναι μια αναπτυξιακή πλακέτα χαμηλού κόστους. Είναι ένα σύστημα υλοποιημένο σε ολοκληρωμένο κύκλωμα (SoC) που ανήκει στην οικογένεια Zynq-7000 της Xilinx. Συνδυάζει την ύπαρξη Υπολογιστικού Συστήματος με δύο επεξεργαστές ARM με την ύπαρξη Επαναπρογραμματιζόμενης Λογικής. Υποστηρίζει την υλοποίηση Linux, Android, Windows, OS/RTOS εφαρμογών. Τα κύρια χαρακτηριστικά του είναι:

- Μνήμη: δυναμική (DDR3) και στατική μνήμη (SPI Flash,SD Card Interface)

- USB: USB-to-UART σύνδεση, λειτουργικότητα JTAG, προστασία κυκλωμάτων USB

- Οθόνη και Ήχος:HDMI Transmitter, Analog Device Audio Codec, OLED Display

- Clock Sources: 33.3333 MHz ρολόι για το Υπολογιστικό Σύστημα ενώ το Υολογιστικό Σύστημα παράγει έως 4 ρολόγια για το Επαναπρογραμματιζόμενο μέρος της πλακέτας

- Reset Sources: εξωτερικοί διακόπτες για επανεκκίνηση της πλακέτας και επαναπρογραμματισμό του FPGA

- User I/O: 7 user GPIO push button, 8 user dip switches, 8 LEDs.

- 10/100/1000 Ethernet PHY: Ethernet θύρα για σύνδεση στο διαδίχτυο

- PS και PL I/Ο επεκτάσεις

Στόχος της δουλειάς αυτής είναι η επιτάχυνση του λογισμικού χτίζοντας έναν επιταχυντή στην Επαναπρογραμματιζόμενη Λογική (PL). Ο επιταχυντής θα πρέπει ακόμα να επικοινωνεί με το Υπολογιστικό Σύστημα, για αυτό το ενδιαφέρον μας επικεντρώνεται στους πόρους της επαναπρογραμματιζόμενης λογικής και στα χαρακτηριστικά τοψ τρόπου διασύνδεσης των δύο μερών της πλακέτας. Συγκεκριμένα το Zedboard διαθέτει έναν δίαυλο επικοινωνίας με το υπολογιστικό τμήμα, ο οποίος εξασφαλίζει επικοινωνία κλιμακώμενης απόδοσης και υψηλών επιδόσεων (High bandwidth AMBA interconnect). Οι διαθέσιμοι πόροι του FPGA αναφέρονται στον Πίνακα 1.

Πίνακας 1: Διαθέσιμοι πόροι του Zedboard.

| Πόροι              | BRAM_18K | DSP48E | FF     | LUT   |

|--------------------|----------|--------|--------|-------|

| $\Delta$ ιαθέσιμοι | 280      | 220    | 106400 | 53200 |

## Αναδόμηση Κώδικα για το HLS

#### Ανάπτυξη Παραλληλισμού σε Επίπεδο Μπλοκ

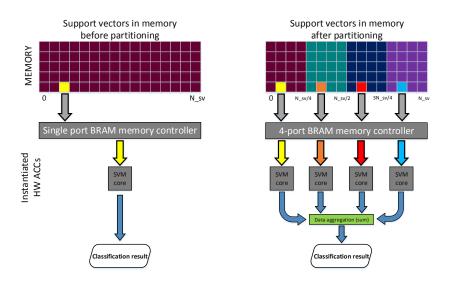

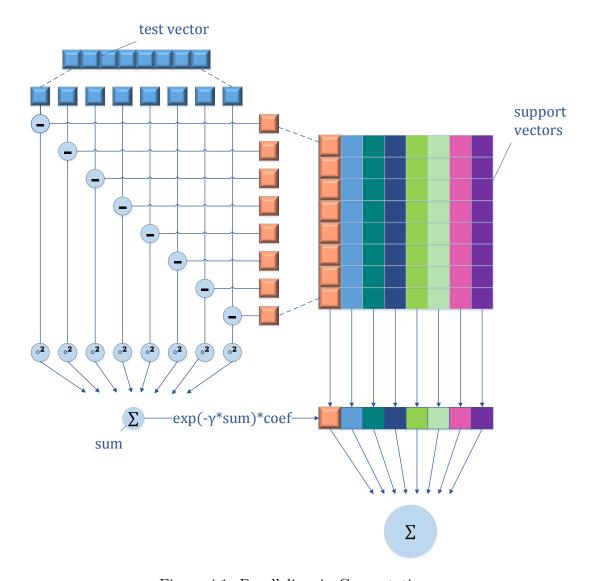

Αρχικά επιδιώκουμε την εξαγωγή παραλληλισμού σε επίπεδο συνάρτησης. Για να το επιτύχουμε αυτό εχμεταλλευόμαστε τον εγγενή παραλληλισμό του αλγορίθμου. Το διάνυσμα εισόδου του τρέχοντος παλμού υλοποιείται ως ένας πίναχας-γραμμή με 18 στοιχεία-χαραχτηριστικά. Τα διανύσματα υποστήριξης υλοποιούνται ως ένας δισδιάστατος πίναχας με τόσες στήλες όσο το πλήθος των διανυσμάτων υποστήριξης ενώ κάθε στήλη έχει τόσα στοιχεία όσα είναι τα χαρακτηριστικά που μελετώνται. Σύμφωνα με τον κώδικα 1 για κάθε διάνυσμα εισόδου προς ταξινόμηση, υπολογίζεται η ευκλείδια απόστασή του από κάθε διάνυσμα υποστήριξης και υψώνεται στο τετράγωνο. Στη συνέχεια εφαρμόζεται σε αυτή τη τιμή η συνάρτηση πυρήνα και η νέα τιμή που προκύπτει πολλαπλασιάζεται με τον αντίστοιχο παράγοντα κάθε διανύσματος υποστήριξης. Οι τιμές που προκύπτουν από τους υπολογισμούς με κάθε διάνυσμα υποστήριξης αθροίζονται και το τελικό αποτέλεσμα συγκρίνεται με τη τιμή βιας για την ταξινόμηση σε μια από τις δύο κλάσεις. Οι πράξεις που απαιτούνται μεταξύ του διανύσματος εισόδου και κάθε διανύσματος υποστήριξης είναι ανεξάρτητες μεταξύ τους. Μπορούν λοιπόν να εκτελούνται παράλληλα. Σε αυτή την έμφυτη παραλληλία βασίζεται η προτεινόμενη τεχνική. Ο πίνακας των διανυσμάτων υποστήριξης μπορεί να επιμεριστεί σε μικρότερους πίνακες, καθένας από τους οποίους περιέχει λιγότερα διανύσματα υποστήριξης. Οι πράξεις για τον υπολογισμό του μεριχού αθροίσματος με το οποίο συνεισφέρει το κάθε κομμάτι πίνακα στο τελικό άθροισμα εκτελούνται παράλληλα. Επιτύχαμε λοιπόν την εκτέλεση του ίδιου υπολογιστικού πυρήνα πολλές φορές παράλληλα μόνο που κάθε μία από αυτές δρα σε μικρότερο σύνολο δεδομένων. Η τεχνική απεικονίζεται στο Σχ.2.

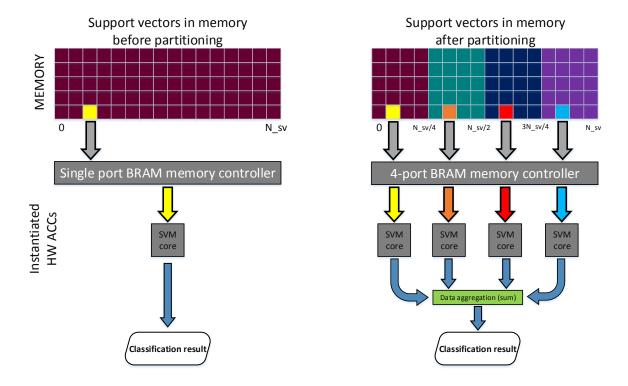

Η υλοποίηση της παραπάνω ιδέας απαιτεί αλλαγές στον χώδιχα σε δομιχό επίπεδο αλλά χαι τη χρήση των τεχνιχών βελτιστοποίησης που προσφέρει το HLS. Συγχεχριμένα ο υπολογιστιχός πυρήνας του ταξινομητή υλοποιείται ως συνάρτηση η οποία χαλείται από την χύρια συνάρτηση τόσες φορές όσες φορές έχει επιμεριστεί ο πίναχας. Ο πίναχας των διανυσμάτων υποστήριξης χαι ο πίναχας των παραγόντων τους επιμερίζονται επίσης σε υποπίναχες με χρήση των χατάλληλων αυτόματων τεχνιχών που παρέχει το εργαλείο. Σε διαφορετιχή περίπτωση θα δημιουργούνταν αντίτυπα των πινάχων για να είναι εφιχτή η πρόσβαση σε πάνω από δύο στοιχεία του χάθε πίναχα τη φορά, περιορισμός που επιβάλλεται λόγω της υλοποίησης των πινάχων ως BRAM με δύο θύρες ανάγνωσης. Κάθε στιγμιότυπο της συνάρτησης έχει πρόσβαση στα στοιχεία μόνο ενός μέρους του επιμερισμένου πίναχα. Ο τροποποιημένος χώδιχας παρατίθεται στον Κώδιχα 2.

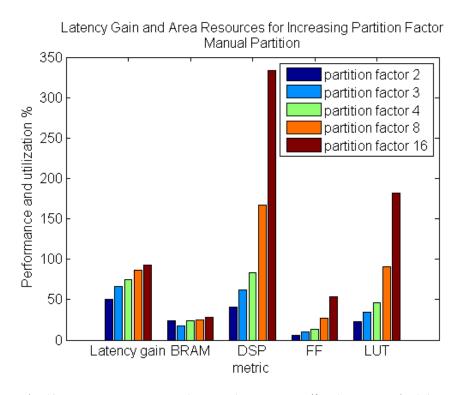

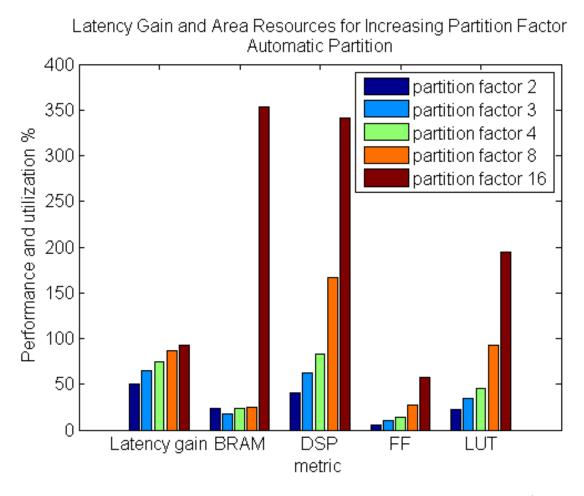

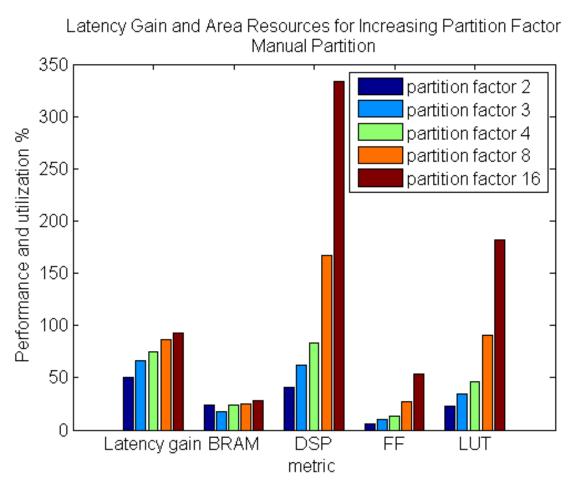

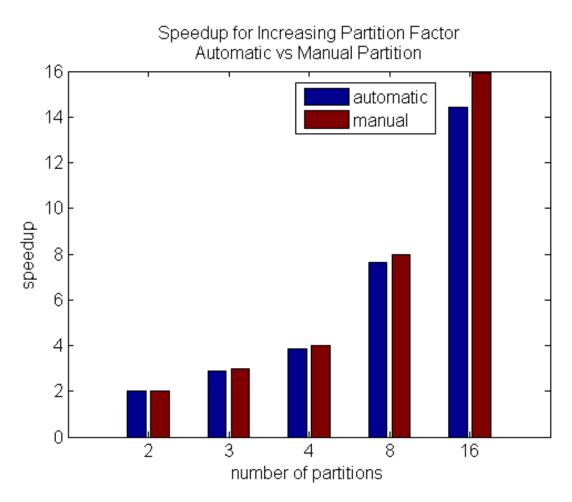

Αυτή η ιδέα υλοποιήθηκε για επιμερισμό του πίνακα σε 2,3,4,8 και 16 μέρη. Η βελτίωση του latency ήταν η αναμενόμενη, δηλαδή ο χρόνος εκτέλεσης διαιρέθηκε σχεδόν κατά έναν παράγοντα 2,3,4,8 και 16. Η χρησιμοποίηση σε DSP πολλαπλασιάστηκε κατά αυτόν τον παράγοντα ενώ υπήρχε σταδιακή αύξηση

Σχήμα 2: Παραλληλισμός σε Επίπεδο Μπλοκ

και στη χρησιμοποίηση LUT και Flip Flop. Η μνήμη παρέμεινε σταθερή εκτός από την τελευταία περίπτωση όπου σημειώθηκε μια απότομη αύξηση. Δοκιμάζοντας να χωρίσουμε τους πίνακες με το χέρι, δηλώνοντας τους εξαρχής χωριστά, πετύχαμε ακόμα μεγαλύτερη επιτάχυνση (ακόμα πιο κοντά στον ιδανικό παράγοντα 2,3,4,8,16 αντιστοίχως) και εξαλείφθηκε το πρόβλημα με την απότομη αύξηση σε BRAM. Τα αποτελέσματα απεικονίζονται στο Σχ.3.

Σχήμα 3: Απόδοση και Χρησιμοποίηση Πόρων για αυξανόμενο αριθμό διαμερίσεων (μη αυτόματη)

```

Listing 2: Τροποποιημένος κώδικας για τον μπλοκ παραλληλισμό.

#include <math.h>

#include "svm.h"

#include <stdio.h>

#define gamma 8

void foo(int width, int offset, float *sum, float test_vector[D_sv],

float sv_coef[N_sv], float sup_vectors[D_sv][N_sv]){

int i, j;

float diff;

float norma=0;

*sum=0;

loop_i: for (i=0; i< width; i++){

loop_{-j}: for (j=0; j<D_sv; j++){

diff=test_vector[j]-sup_vectors[j][i+offset];

norma = norma + diff*diff;

*sum = *sum + exp(-gamma*norma)*sv_coef[i+offset];

norma=0;

}

}

void classify(int * y){

const float sv_coef[N_sv]={

#include "sv_coef.dat"

};

const float test_vector [D_sv]={

#include "test_vector.dat"

};

const float support_vectors [D_sv][N_sv]={

#include "support_vectors.dat"

};

float diff;

float sum1, sum2, sum;

foo(N_sv/2,0,&sum1,test_vector,sv_coef,support_vectors);

foo(N_sv/2, N_sv/2, &sum2, test_vector, sv_coef, support_vectors);

sum = sum1 + sum2 - b;

if (sum<0) *y = -1;

else *y = 1;

```

}

# Ανάπτυξη Παραλληλισμού σε Επίπεδο Εντολών μέσω μετασχηματισμού αριθμητικών υπολογισμών

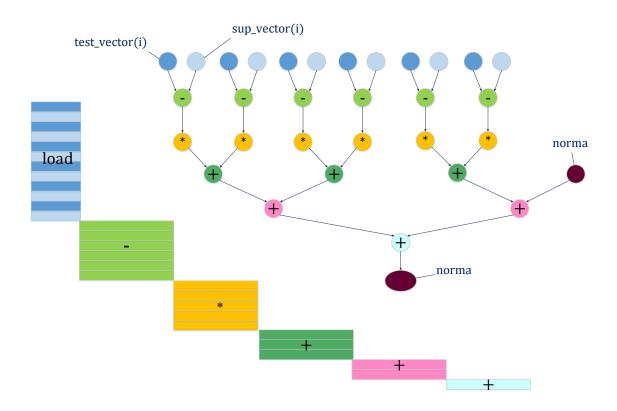

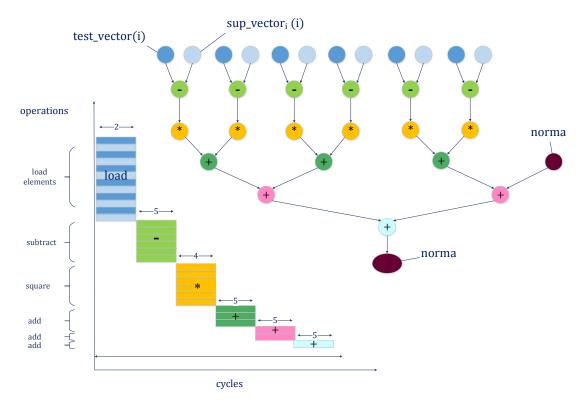

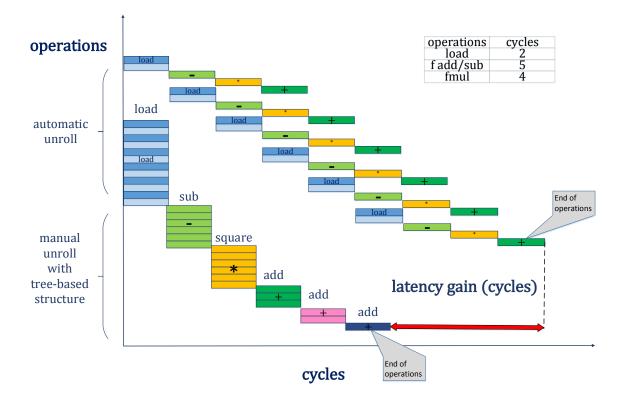

Σε αυτό το χομμάτι θα εξετάσουμε την παραλληλοποίηση σε επίπεδο εντολών. Συγχεχριμένα θα ασχοληθούμε με την παραλληλοποίηση του εσωτεριχού βρόχου του ταξινομητή. Αυτός ο βρόχος είναι υπεύθυνος για τον υπολογισμό της ευχλείδειας απόστασης του διανύσματος από ένα διάνυσμα υποστήριξης υψωμένης στο τετράγωνο. Σε κάθε επανάληψη υπολογίζεται η διαφορά μεταξύ των αντίστοιχων χαραχτηριστικών των δύο διανυσμάτων και υψώνεται στο τετράγωνο. Αντί να υπολογίζεται κάθε φορά μία μόνο διαφορά θα μπορούσαν να υπολογίζονται περισσότερες και να αθροίζονται σταδιακά σε μια μεταβλητή η οποία στο τέλος του βρόχου θα περιέχει την τετραγωνισμένη νόρμα. Η άθροιση όμως πολλών αριθμών χινητής υποδιαστολής συνεπάγεται μεγάλο χρίσιμο μονοπάτι επειδή οι προσθέσεις γίνονται σειριακά αν και δεν υπάρχει εξάρτηση μεταξύ των προσθετέων. Η πρόσθεση μπορεί να υλοποιηθεί αποδοτικά αν χρησιμοποιηθεί μια δενδρική μορφή. Ο εσωτερικός βρόχος εκτυλίσσεται τόσες φορές όσες διαφορές θα υπολογιστούν ταυτόχρονα. Οι διαφορές υπολογίζονται παράλληλα μεταξύ τους όπως και οι υψώσεις των διαφορών στο τετράγωνο. Στη συνέχεια οι διαθέσιμες τιμές προστίθενται ανά δύο και τα αποτελέσματα κρατώνται σε προσωρινές μεταβλητές. Αυτές προστίθενται και πάλι ανά δύο κ.ο.κ. μέχρι τον υπολογισμό της ολικής νόρμας στο τετράγωνο. Η δενδρική δομή και η χρονοδρομολόγηση του εργαλείου απειχονίζονται στο  $\Sigma$ χ.4 ενώ οι αλλαγές στην υλοποίηση στον Κώδιχα 3στην περίπτωση που ο βρόχος εκτυλίσσεται κατά έναν παράγοντα ίσο με 6.

Σχήμα 4: Δενδρικής δομής υπολογισμοί και χρονοδρομολόγηση.

Listing 3: Κώδικας με εκτύλιξη του εσωτερικού βρόχου και δενδρική υλοποίηση των υπολογισμών.

```

#define gamma 8

const float sv_coef[N_sv];

const float sup_vectors[D_sv][N_sv];

void SVM_predict (int *y, float test_vector[D_sv]){

loop_i: for (i=0; i< N_sv; i++) {

loop_{-j}: for (j=0; j< D_{sv}; j=j+6)

d1=test_vector[j]-sup_vectors[j][i];

d2=test\_vector[j+1]-sup\_vectors[j+1][i];

d3=test\_vector[j+2]-sup\_vectors[j+2][i];

d4 = test\_vector[j+3] - sup\_vectors[j+3][i];

d5 = test\_vector[j+4] - sup\_vectors[j+4][i];

d6 = test\_vector[j+5] - sup\_vectors[j+5][i];

sq_prod1=d1*d1;

sq_prod2=d2*d2;

sq_prod3=d3*d3;

sq_prod4=d4*d4;

sq_prod5=d5*d5;

sq_prod6=d6*d6;

tmp_sum1=sq_prod1+sq_prod2;

tmp_sum2=sq_prod3+sq_prod4;

tmp_sum3=sq_prod5+sq_prod6;

tmp_sum4=tmp_sum1+tmp_sum2;

norma = norma + tmp\_sum3;

norma = norma + tmp\_sum4;

}

sum = sum + exp(-gamma*norma)*sv_coef[i];

norma=0;

}

sum = sum - b;

if (sum < 0)

*y = -1;

else

*y = 1;

}

```

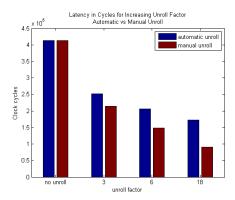

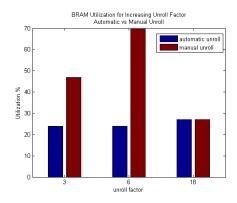

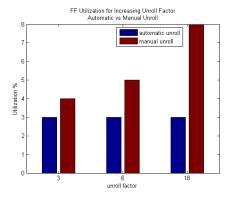

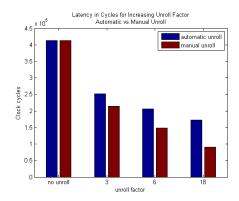

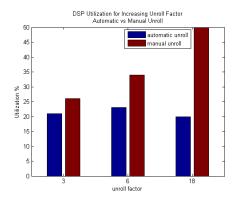

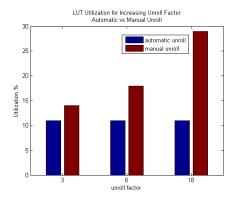

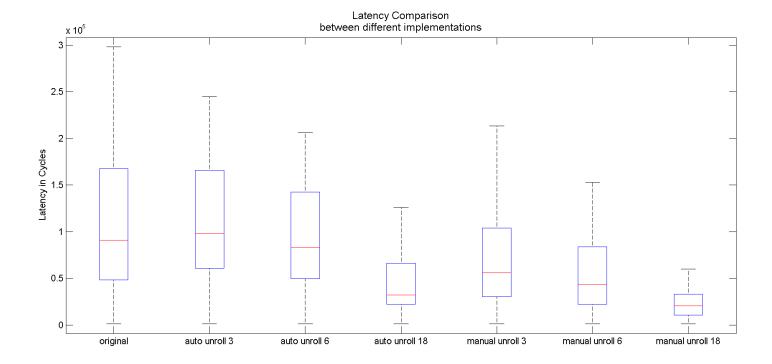

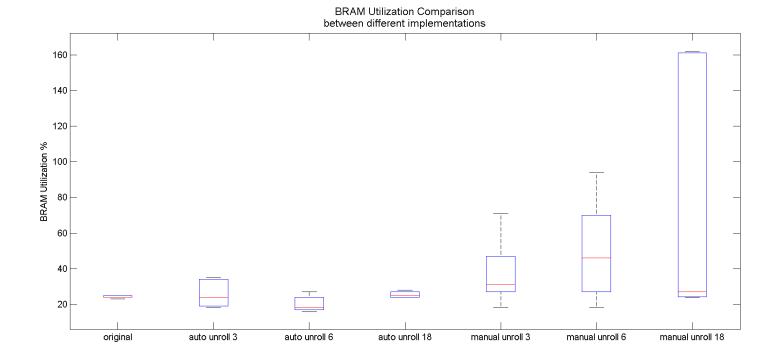

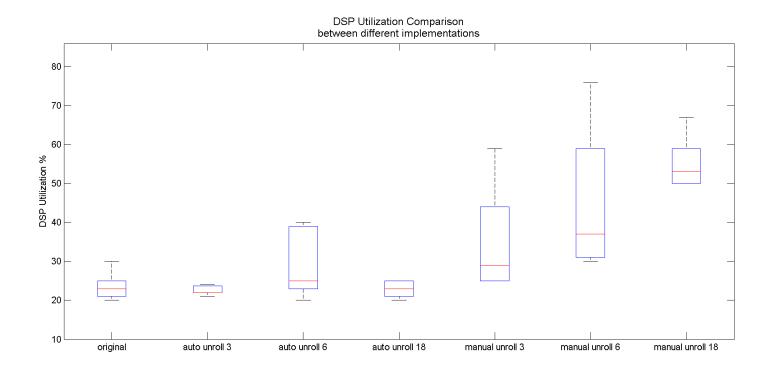

Η παραπάνω ιδέα υλοποιήθηκε για εκτύλιξη του εσωτερικού βρόχου 3,6 και 18 φορές που αντιστοιχεί σε πλήρη εκτύλιξη. Τα αποτελέσματα συγκεντρώνονται στον Πίνακα 2, όπου πραγματοποιείται σύγκριση μεταξύ εκτύλιξης του βρόχου με το χέρι, χρησιμοποιώντας δενδρική δομή και εκτύλιξης του βρόχου με τις αυτόματες τεχνικές του εργαλείου.

Πίνακας 2: Σύγκριση μετρικών μεταξύ αυτόματης και προτεινόμενης εκτύλιξης βρόχου

| εκδοχή   | Παράγοντας | Αυτόματη |          |     |     | Προτεινόμενη |          |      |     |     |         |

|----------|------------|----------|----------|-----|-----|--------------|----------|------|-----|-----|---------|

|          | εκτύλιξης  |          | εκτύλιξη |     |     | εκτύλιξη     |          |      |     |     |         |

|          |            | latency  | BRAM     | DSP | FF  | LUT          | latency  | BRAM | DSP | FF  | LUT (%) |

|          |            | (cycles) | (%)      | (%) | (%) | (%)          | (cycles) | (%)  | (%) | (%) | (%)     |

| initial  | -          | 412783   | 24       | 20  | 3   | 11           | 412783   | 24   | 20  | 3   | 11      |

| unrolled | 3          | 252259   | 24       | 21  | 3   | 11           | 214039   | 47   | 26  | 4   | 14      |

| unrolled | 6          | 206395   | 24       | 23  | 3   | 11           | 149065   | 70   | 34  | 5   | 18      |

| unrolled | 18         | 173271   | 27       | 20  | 3   | 11           | 90461    | 27   | 50  | 8   | 29      |

Παρατηρείται σημαντική βελτίωση στο latency όταν η εκτύλιξη γίνεται με το χέρι και μάλιστα η διαφορά μεγαλώνει όσο μεγαλώνει και ο παράγοντας της εκτύλιξης. Η χρησιμοποίηση των DSP, LUTs και Flip Flop αυξάνεται καθώς η αντιγραφή του σώματος του εσωτερικού βρόχου οδηγεί στην δέσμευση περισσότερων πόρων προκειμένου οι πράξεις να δρομολογηθούν ταυτόχρονα. Ένα μη αναμενόμενο αποτέλεσμα είναι οι διακυμάνσεις στη χρησιμοποίηση της μνήμης. Οφείλονται ωστόσο στη δημιουργία αντιγράφων των πινάκων από το HLS για να είναι δυνατές πολλές προσβάσεις στον ίδιο πίνακα ταυτόχρονα. Στην τελευταία περίπτωση δεν υπάρχει αύξηση επειδή το HLS σπάει αυτόματα τον πίνακα των διανυσμάτων υποστήριξης κατα μήκος των γραμμών. Το πρόβλημα επιλύεται με σπάσιμο του πίνακα σε όλες τιε περιπτώσεις στην κατάλληλη διάσταση και με τον κατάλληλο τρόπο με τις κατάλληλες τεχνικές που προσφέρει το HLS στο χρήστη.

## Εξερεύνηση HLS directives

#### Επιλογή directives

Οι τεχνικές που παρουσιάστηκαν εξασφάλισαν ένα πρώτο επίπεδο παραλληλισμού. Η απόδοση μπορεί να βελτιωθεί περαιτέρω από το συνδυασμό των προηγούμενων τεχνικών με τις ενσωματωμένες αυτόματες τεχνικές βελτιστοποίησης που παρέχει το HLS και ονομάζονται directives.

Η επιλογή αυτών εξαρτάται από την εγγενή παραλληλία του αλγορίθμου και τον τρόπο με τον οποίο αυτή μπορεί να αξιοποιηθεί. Στον συγκεκριμένο ταξινομητή οι τεχνικές που επιλέγονται στοχεύουν στην παραλληλοποίηση του εσωτερικού βρόχου. Όπως έχει αναφερθεί τα τετράγωνα της διαφοράς των στοιχείων των διανυσμάτων εισόδου και υποστήριξης συνθέτουν την ευκλείδια νόρμα και μπορούν να υπολογιστούν παράλληλα. Αυτό προϋποθέτει την ξετύλιξη του βρόχου και οδηγεί στην ανάγκη ανάγνωσης περισσότερων από δύο στοιχείων κάθε πίνακα τη φορά. Απαιτείται έτσι η αλλαγή της δομής των πινάκων για να καταστεί αυτό δυνατό. Με το ίδιο σκεπτικό μπορούμε να ξετυλίξουμε τον εξωτερικό βρόχο και να τροποποιήσουμε τους πίνακες που προσπελάζονται σε αυτό για να αυξήσουμε την παραλληλία. Ακολουθούν τα directives και ο λόγος για τον οποίο επιλέχθηκαν.

**Pipeline**: Αυτή η τεχνική εφαρμόζεται σε όλους τους βρόχους. Οι πράξεις των επαναλήψεων εκτελούνται παράλληλα κι όχι σειριακά χρησιμοποιώντας όλους τους πόρους κάθε χρονική στιγμή.

**Εκτύλιξη βρόχου**: Εφαρμόζεται σε όλους τους βρόχους. Δημιουργούνται αντίγραφα του σώματος του βρόχου ενώ μειώνεται ο αριθμός εκτελέσεων.

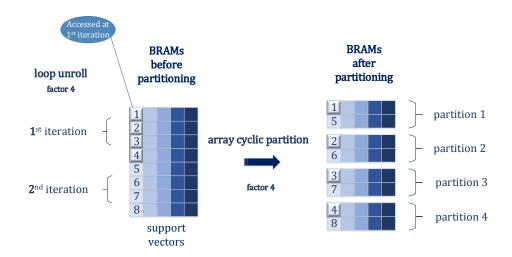

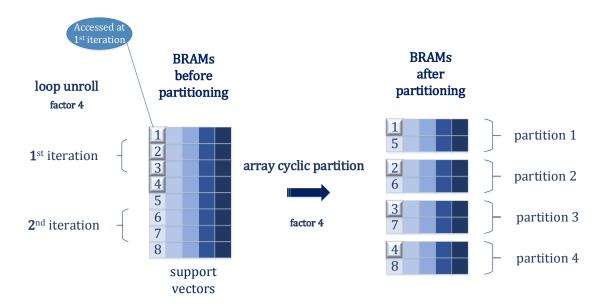

Διαίρεση Πίνακα: Εφαρμόζεται στους πίνακες sup\_vector και sv\_coef arrays. Διαιρεί τους πίνακες σε πίνακες μικρότερου μεγέθους κι άρα αυξάνεται ο αριθμός των θυρών ανάγνωσης. Έτσι όταν ξετυλίγεται ο εσωτερικός βρόχος είναι δυνατή η πρόσβαση σε περισσότερα από δύο στοιχεία του πίνακα και άρα μπορεί να παραλληλοποιηθεί ο υπολογισμός της ευκλείδιας απόστασης των διανυσμάτων. Η διαίρεση γίνεται κυκλικά (ανά κάποιο παράγοντα τα στοιχεία ανήκουν στην ίδια υποδιαίρεση πίνακα) ώστε να είναι δυνατή η ταυτόχρονη πρόσβαση σε διαδοχικά στοιχεία του αρχικού πίνακα με τη σειρά που αυτά χρειάζονται και στο βρόχο. Στο Σχ.5 απεικονίζεται η διαίρεση του πίνακα.

Σχήμα 5: Σχηματική Αναπαράσταση της Διαίρεσης Πίνακα

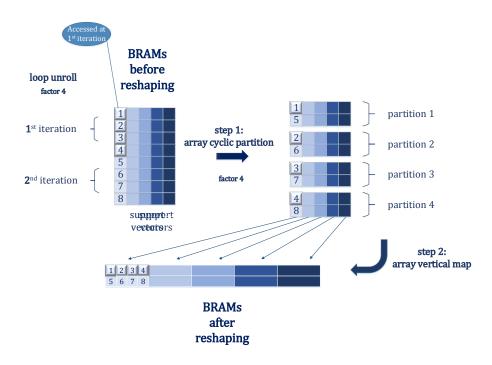

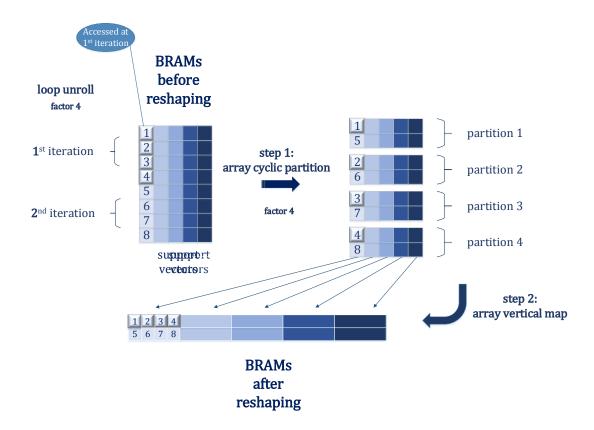

Μορφοποίηση Πίνακα: Εφαρμόζεται στους ίδιους πίνακες με την προηγούμενη τεχνική και για τον ίδιο σκοπό. Η διαφορά είναι ότι οι μικρότεροι πίνακες ενώνονται και πάλι σε έναν πίνακα ώστε ένα στοιχείου του νέου πίνακα να αποτελείται από όλα τα αντίστοιχα στοιχεία των μικρότερων πινάκων. Έτσι μειώνεται ο αριθμός των BRAM ενώ παράλληλα με μια πρόσβαση έχουμε στη διάθεσή μας περισσότερα στοιχεία. Η τεχνική απεικονίζεται στο Σχ.6

Σχήμα 6: Σχηματική Αναπαράσταση της Μορφοποίησης Πίνακα

Έχουν διερευνηθεί όλοι οι συνδυασμοί των επιλεγμένων τεχνικών που έχουν νόημα και αυτοί που δεν αποκλείονται λόγω δικών μας παραδοχών. Επίσης κάθε τεχνική εξετάζεται και ως προς την αλλαγή των τιμών των παραμέτρων της. Οι τελικοί συνδυασμοί που προκύπτουν εφαρμόστηκαν σε τέσσερις

εκδοχές του αλγορίθμου:την αρχική και τρεις εκδοχές στις οποίες έχει εκτυλιχθεί ο εσωτερικός βρόχος με τον τρόπο που προτάθηκε στο Κεφάλαιο κατά 3, 6 και 18 φορές αντίστοιχα.

#### Αποτελέσματα

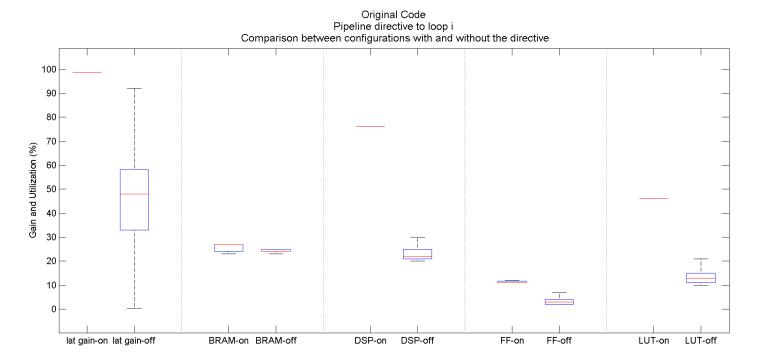

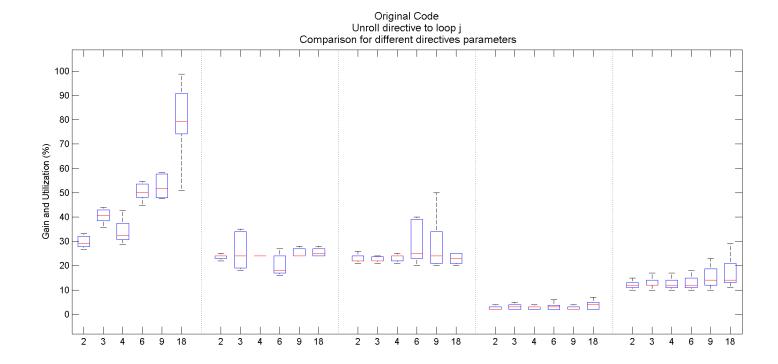

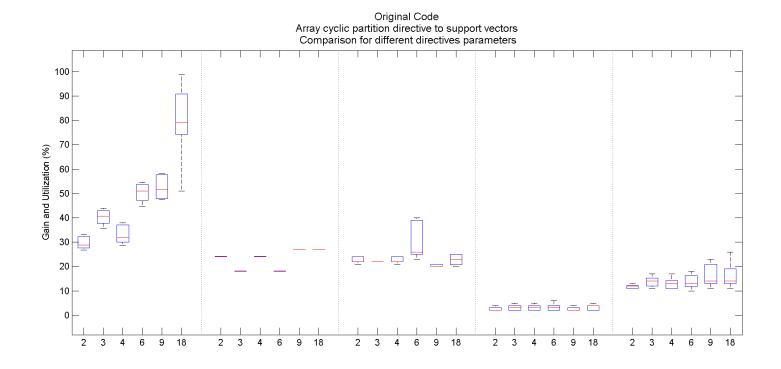

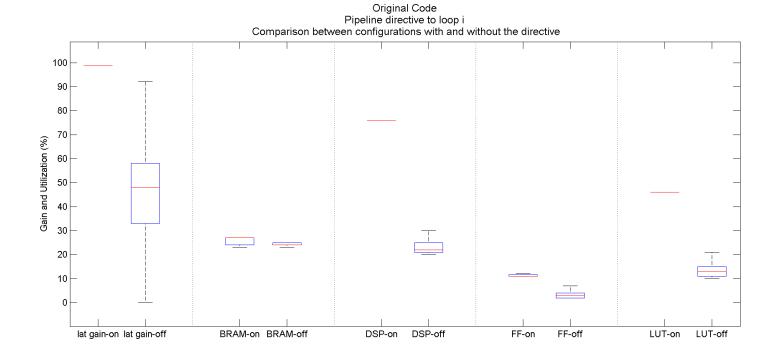

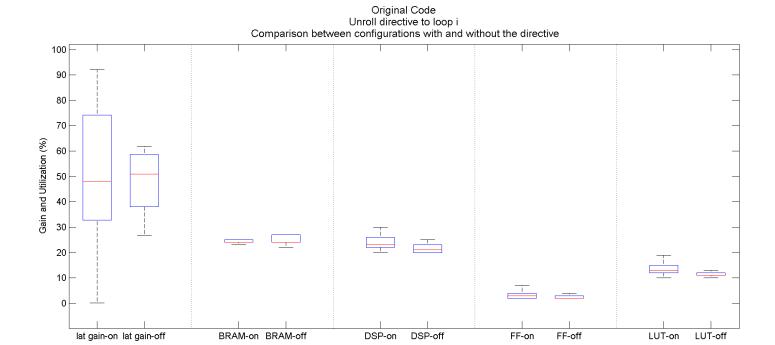

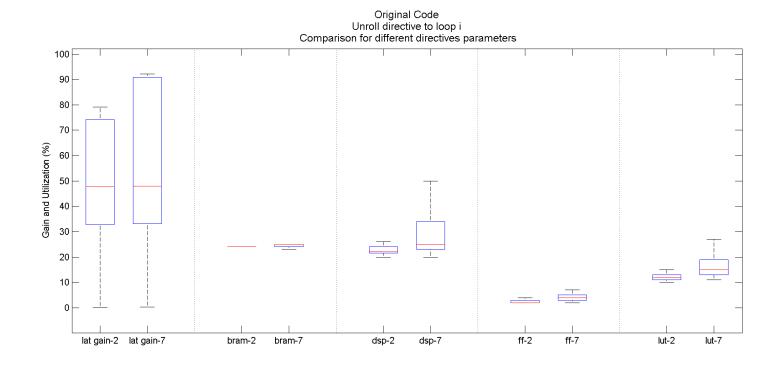

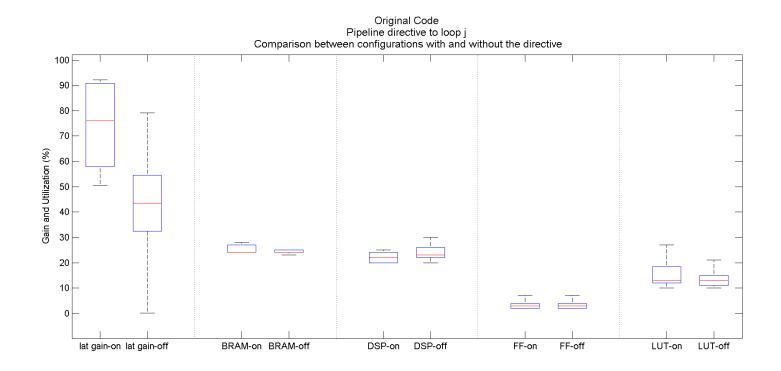

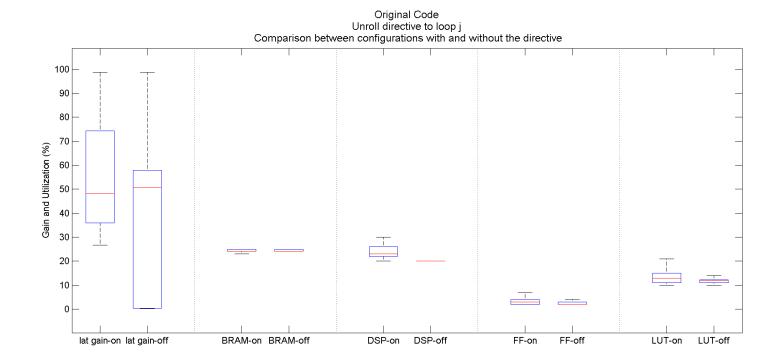

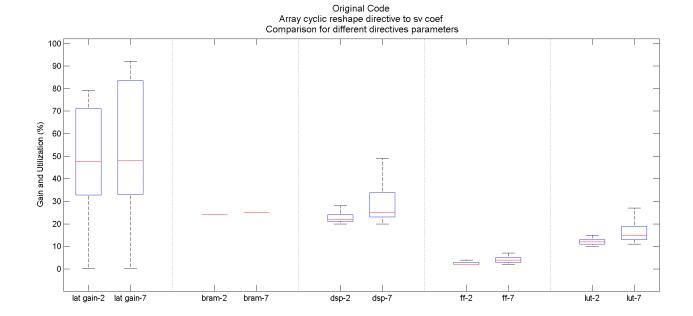

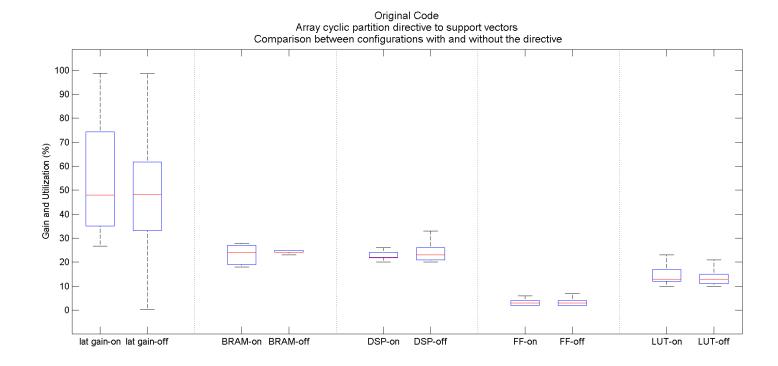

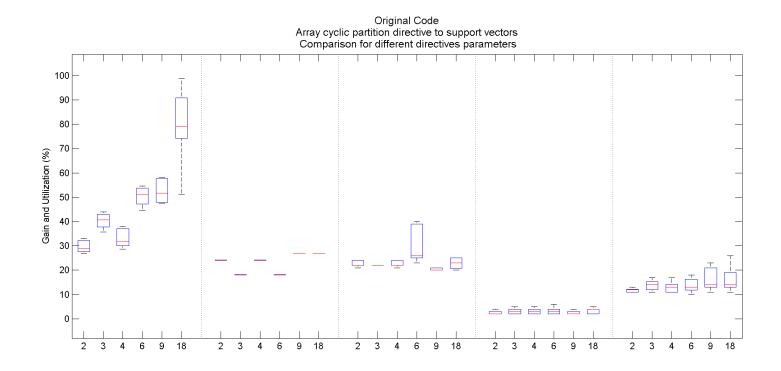

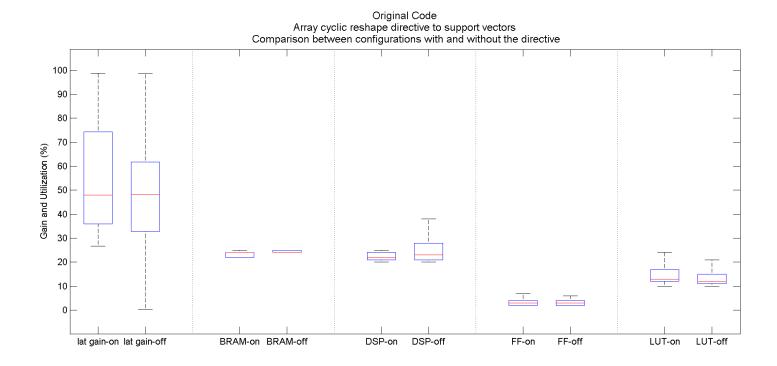

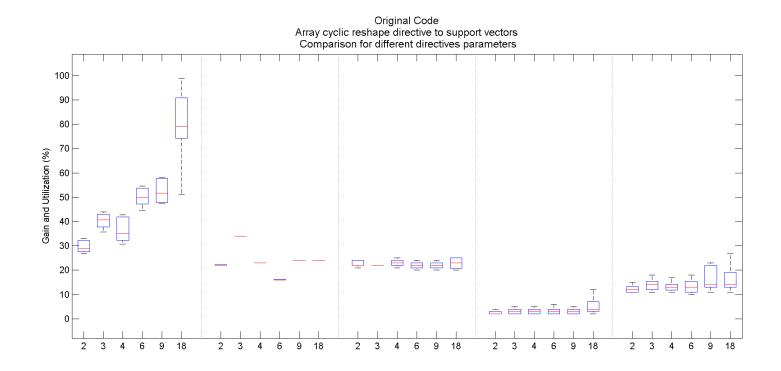

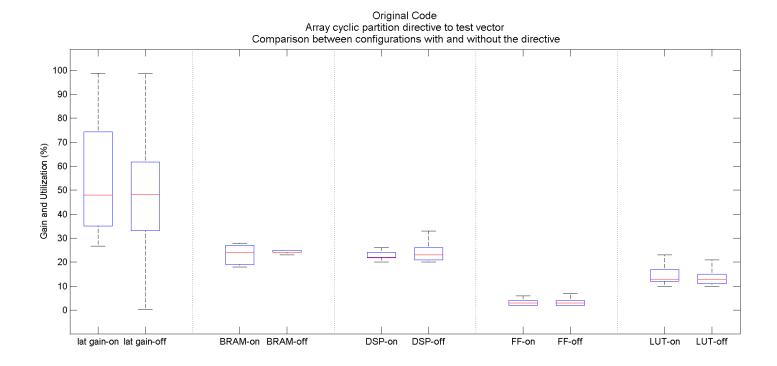

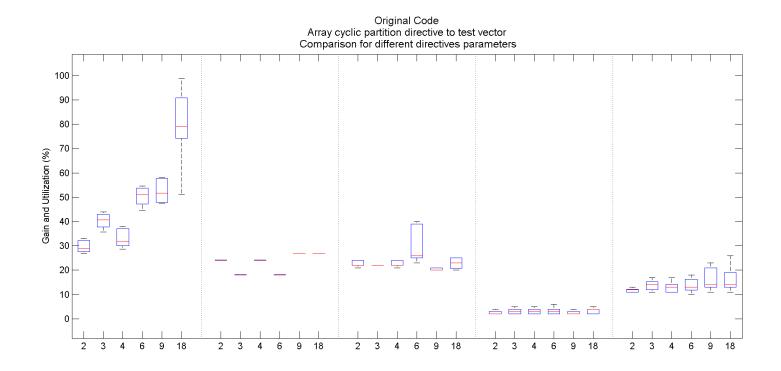

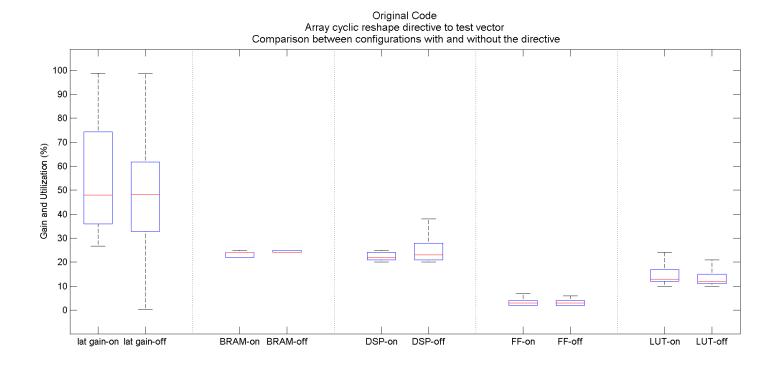

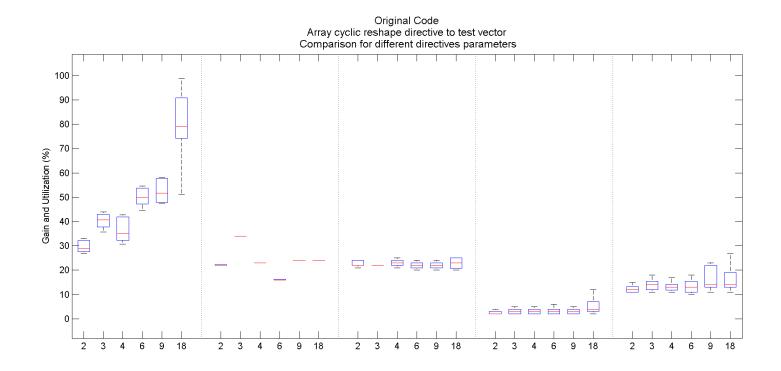

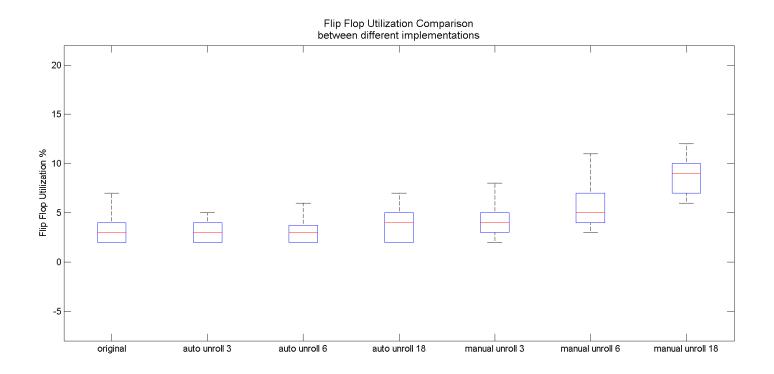

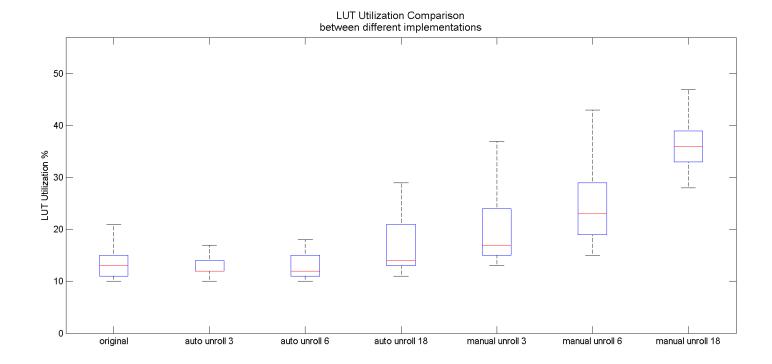

Στα  $\Sigma$ χ.7-9 αναπαριστώνται τα αποτελέσματα των βασικότερων τεχνικών που χρησιμοποιήθηκαν.

Σχήμα 7: Pipeline εξωτερικού βρόχου

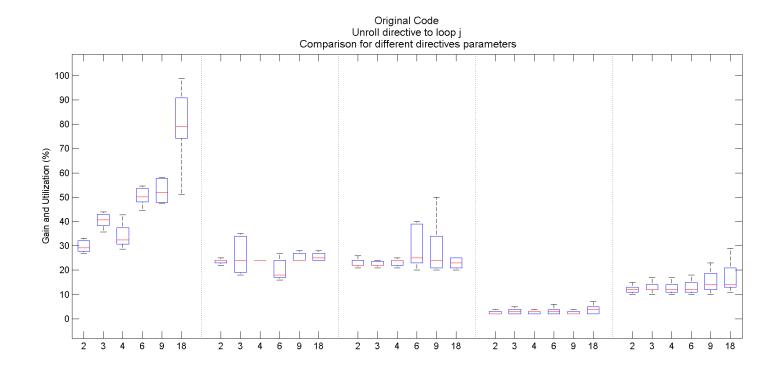

Σχήμα 8: Εκτύλιξη εσωτερικού βρόχου κατά διαφορετικό παράγοντα. Στήλες αριστερά προς τα δεξιά:κέρδος χρόνου εκτέλεσης, BRAM,DSP,FF,LUT.

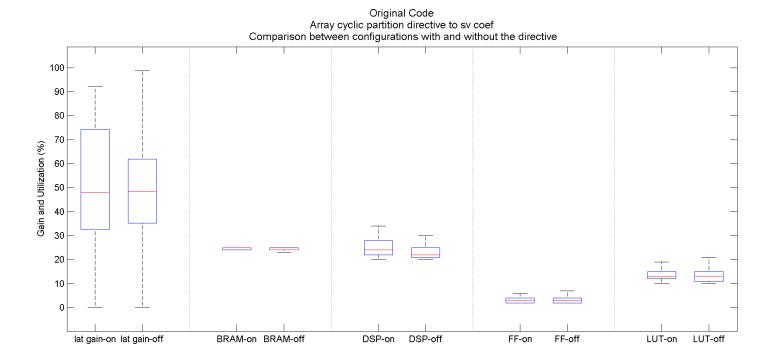

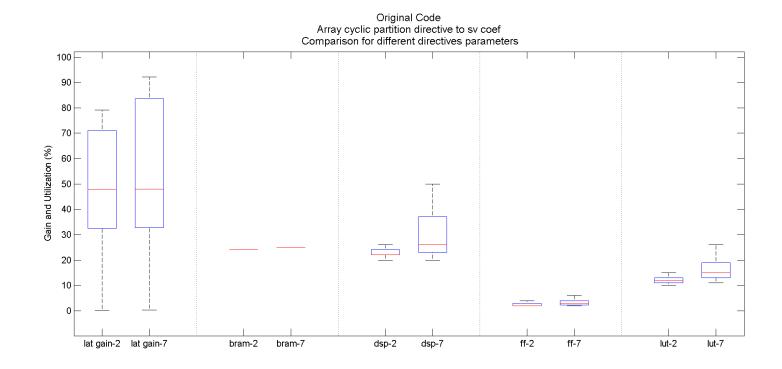

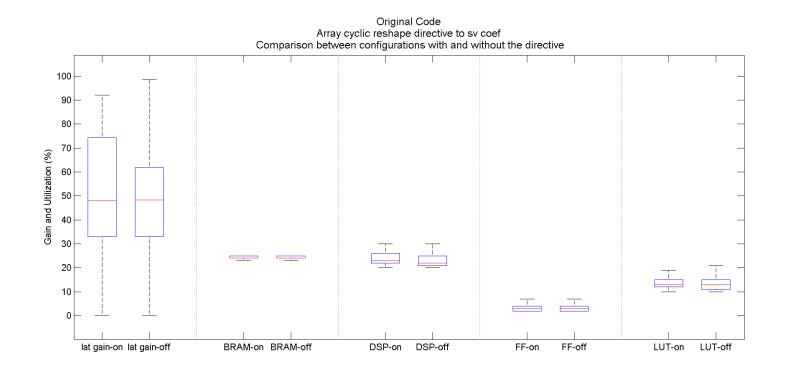

Σχήμα 9: Διαίρεση πίνακα support vector. Στήλες αριστερά προς τα δεξιά:κέρδος χρόνου εκτέλεσης, BRAM,DSP,FF,LUT

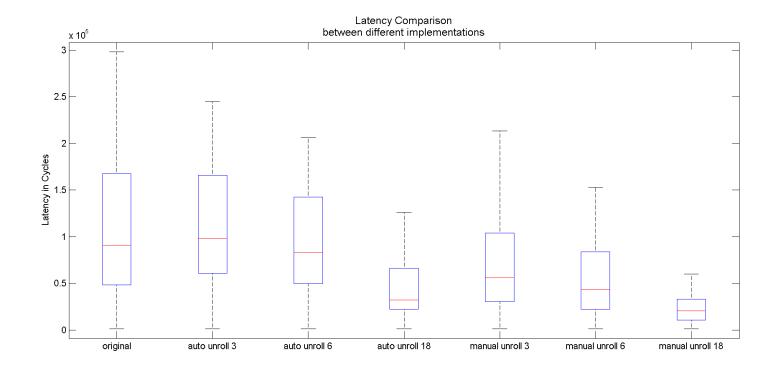

Η διαφορά στα αποτελέσματα ανά διαφορετική υλοποίηση φαίνεται στο Σχ.10, όπου απεικονίζεται ο

Σχήμα 10: Σύγκριση επιτάχυνσης μεταξύ όλων των υλοποιήσεων

χρόνος εκτέλεσης σε κύκλους ανά υλοποίηση. Η πρώτη υλοποίηση είναι η αρχική. Ακολουθούν τρεις εκδοχές αυτής που έχουν δημιουργηθεί έχοντας εκτυλίξει τον εσωτερικό βρόχο με τον αυτόματο τρόπο που παρέχεται από το εργαλείο. Οι τρεις επόμενες αντιστοιχούν στις εκτυλίξεις του βρόχου με τον προτεινόμενο τρόπο που συνδυάζει την εκτύλιξη με δενδρική υλοποίηση των αριθμητικών υπολογισμών. Είναι προφανές ότι η εκτύλιξη του εσωτερικού βρόχου έχει καθοριστικό αντίκτυπο στη μείωση του χρόνου εκτέλεσης. Όσο μεγαλύτερος είναι ο παράγοντας εκτύλιξης τόσο πιο έντονη είναι η επίδρασή του. Τα boxplot για μεγαλύτερους παράγοντες είναι μετατοπισμένα σε χαμηλότερους χρόνους, έχουν μικρότερο εύρος ενώ ο μέσος έχει φθίνουσα πορεία. Είναι ακόμα προφανές ότι ο προτεινόμενος τρόπος εκτύλιξης είναι πιο αποδοτικός. Επιτυγχάνει ακόμα μικρότερο εύρος boxplot, τιμές που κυμαίνονται σε χαμηλότερους χρόνους και μικρότερους μέσους. Είναι χαρακτηριστικό ότι η προτεινόμενη υλοποίηση για εκτύλιξη κατά 3 έχει καλύτερα αποτελέσματα από την αυτόματη κατά παράγοντα 6.

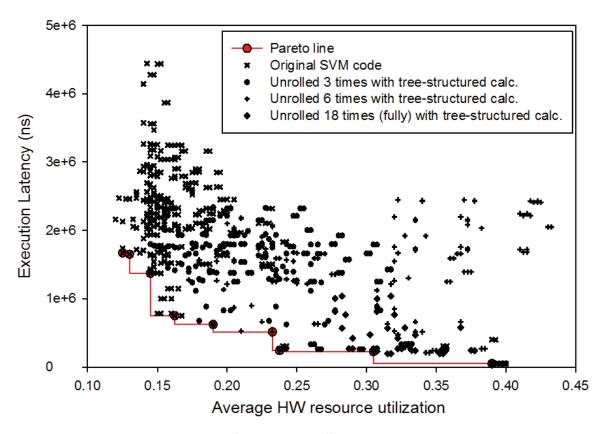

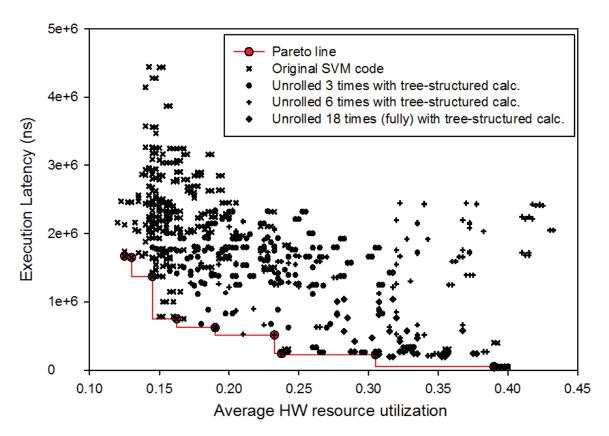

Ιδιαίτερα σημαντικό είναι το ότι παρέχεται στο σχεδιαστή μια μεγάλη ποικιλία αρχιτεκτονικών επιλογών, από τις οποίες μπορεί να διαλέξει ανάλογα με τις απαιτήσεις και τους περιορισμούς της εκάστοτε εφαρμογής. Στο Σχ.11 παρουσιάζεται ο χώρος εξερεύνησης για όλες τις εκδοχές υλοποιήσεων που χρησιμοποιήσαμε. Στον άξονα Χ μετράται η χρησιμοποίηση πόρων από κάθε προτυτοποίηση ενώ στον άξονα Υ η απόδοση ως προς το χρόνο εκτέλεσης. Η κάθε προτυτοποίηση έχει διαφορετικά χαρακτηριστικά. Για παράδειγμα τα βέλτιστα σημεία προς τα αριστερά εξασφαλίζουν ελάχιστη χρησιμοποίηση πόρων και ικανοποιητική επιτάχυνση. Αυτά προκύπτουν κυρίως από τον αρχικό κώδικα που δεν είναι εξίσου βελτιστοποιημένος με τους άλλους. Ο χρόνος εκτέλεσης είναι μικρότερος αλλά λόγω απλής δομής απαιτείται περιορισμένος αριθμός πόρων. Το αντίθετο συμβαίνει με τους τροποποιημένους κώδικες,

που επιτυγχάνουν υψηλά επίπεδα επιτάχυνσης με μια επιβάρυνση όμως στη χρησιμοποίηση πόρων.

Σχήμα 11: Καμπύλη Pareto

## Υλοποίηση στην πλακέτα

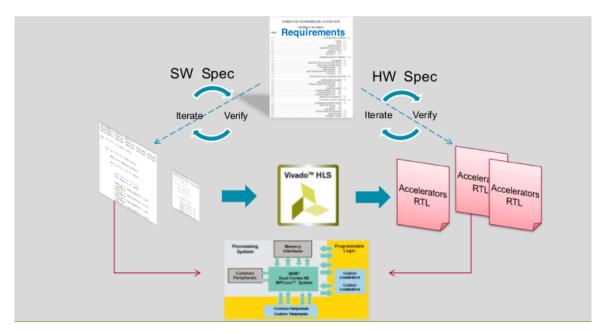

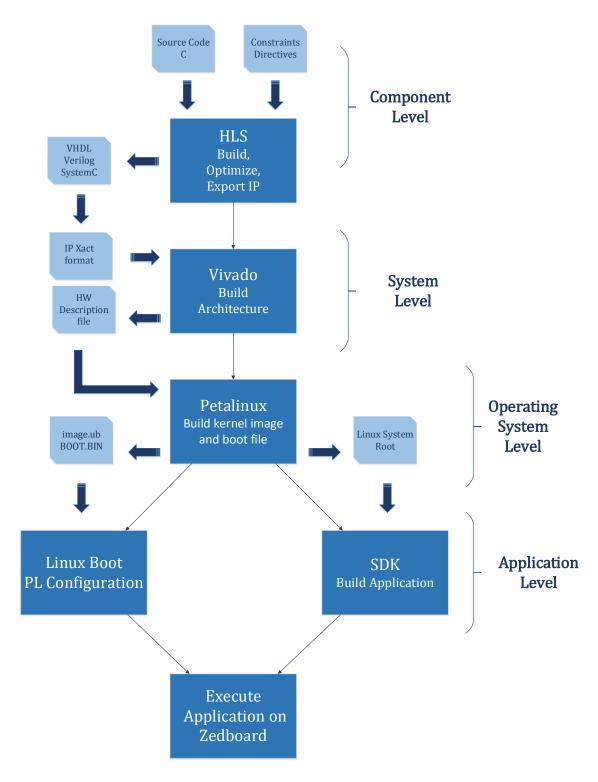

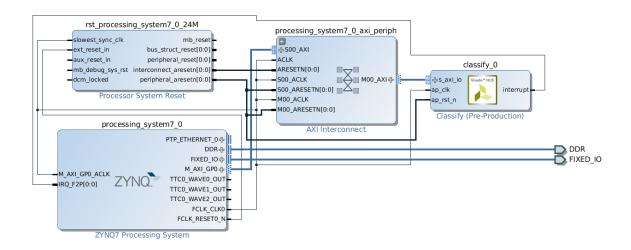

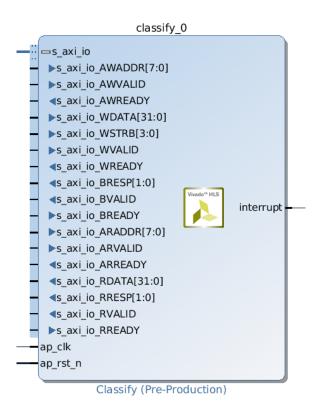

Ακολουθεί η περιγραφή της υλοποίησης της εφαρμογής στην πλακέτα και τα αποτελέσματα αυτής. Τα βήματα που ακολουθήσαμε και τα εργαλεία που χρησιμοποιήθηκαν σε κάθε σχήμα είναι τα εξής:

- High Level Synthesis: Σε αυτό το στάδιο γίνεται η κατασκευή του επιταχυντή. Χρησιμοποιείται το εργαλείο Vivado High Level Synthesis 2014.4 της Xilinx. Το εργαλείο λαμβάνει ως είσοδο κώδικα C, τροποποιημένο πρώτα από το σχεδιαστή ή όχι, περιορισμούς του χρήστη και directives. Η έξοδος είναι ο επιταχυντής σε γλώσσα περιγραφής υλικού. Μετά από εξερεύνηση ο σχεδιαστής καταλήγει στην προτυτοποίηση που πληροί τις απαιτήσεις και τις προδιαγραφές της εφαρμογής του. Εκτός από τα directives που έχουν σκοπό την βελτιστοποίηση του επιταχυντή, εφαρμόζονται και directives για την ένταξη και επικοινωνία του επιταχυντή με ένα ευρύτερο αρχιτεκτονικό σύστημα και το υπολογιστικό σύστημα. Εξάγεται λοιπόν ως έξοδος ο επιταχυντής και σε κατάλληλο φορμάτ ώστε να μπορεί να χρησιμοποιηθεί σε κατάλληλο περιβάλλον για τη δημιουργία της συνολικής αρχιτεκτονικής.

- Κατασκευή πλήρους αρχιτεκτονικής: Σε αυτό το στάδιο κατασκευάζεται η πλήρης αρχιτεκτονική του συστήματος, που αποτελείται από το Υπολογιστικό Σύστημα, τον επιταχυντή στην Προγραμματιστική Λογική και το δίαυλο επικοινωνίας αυτών μεταξύ τους. Χρησιμοποείται το Xilinx Vivado Design Suite 2014.4. Στο τέλος της διαδικασίας παράγεται το hw description file.

- Δημιουργία Λειτουργικού Συστήματος: Το επόμενο βήμα είναι η δημιουργία λειτουργικού συστήματος linux που να εκκινεί στην πλακέτα. Χρησιμοποιείται το Petalinux 2014.4. Για το χτίσιμο του είναι απαραίτητες πληροφορίες για την αρχιτεκτονική του Zedboard και ό,τι υλοποιήθηκε από το χρήστη στο FPGA, επομένως χρειάζεται το hw description file που παρήχθηκε από το Vivado. Ο πυρήνας των linux μπορεί να προτυτοποιηθεί αναλόγως με τις απαιτήσεις του συστήματος. Στο τέλος αυτού του βήματος παράγεται το image του πυρήνα και το BOOT.BIN αρχείο οπότε μπορεί να εκκινήσει το λειτουργικό στην πλακέτα και να προτυποποιηθεί το FPGA.

- Ανάπτυξη εφαρμογής: Αυτό είναι το τελευταίο βήμα κατά το οποίο αναπτύσσεται η εφαρμογή. Τα χαρακτηριστικά κάθε παλμού στέλνονται στον επιταχυντή και αυτός επιστρέφει το αποτέλεσμα. Ο επιταχυντής ελέγχεται και χειρίζεται από το Υπολογιστικό Σύστημα ως συσκευή που γίνεται map σε χώρο διευθύνσεων του χρήστη και ανοίγει ως αρχείο.

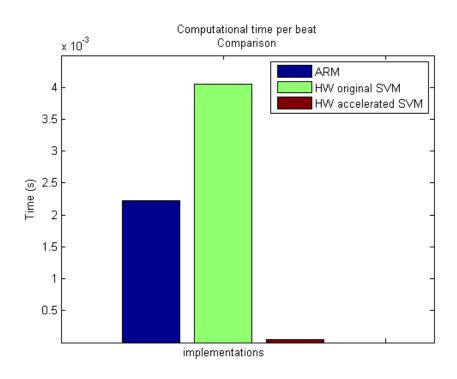

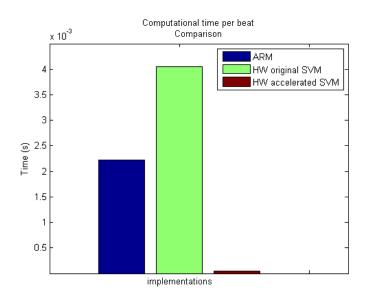

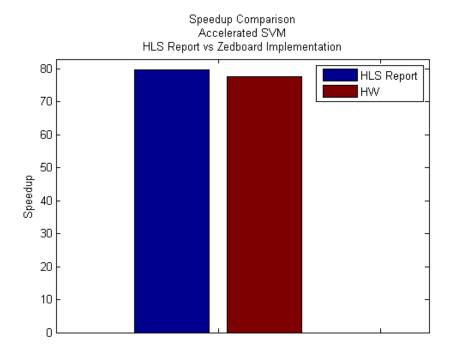

Ακολουθώντας τα παραπάνω βήματα υλοποιούμε στην πλακέτα την αρχική και τη βέλτιστη υλοποίηση ενώ εκτελούμε και τον αλγόριθμο μόνο στο Υπολογιστικό Σύστημα. Η βέλτιστη υλοποίηση είναι πιο γρήγορη και από τον αρχική και από αυτήν που τρέχει μόνο σε sw. Τα αποτελέσματα είναι κοντά στα θεωρητικά αναμενόμενα.

Πίνακας 3: Μετρήσεις χρόνου για τις υλοποιήσεις

|           | S                                                                          | W           | HW c           | ιρχική         | HW βέλτιστη    |                |  |

|-----------|----------------------------------------------------------------------------|-------------|----------------|----------------|----------------|----------------|--|

|           | Χρόνος Χρόνος<br>Επικοινωνίας Υπολογισμού<br>(δευτερόλεπτα) (δευτερόλεπτα) |             | Χρόνος         | Χρόνος         | Χρόνος         | Χρόνος         |  |

|           |                                                                            |             | Επικοινωνίας   | Υπολογισμού    | Επικοινωνίας   | Υπολογισμού    |  |

|           |                                                                            |             | (δευτερόλεπτα) | (δευτερόλεπτα) | (δευτερόλεπτα) | (δευτερόλεπτα) |  |

| ανά παλμό | -                                                                          | 0.002223635 | 0.00000449943  | 0.004047181    | 0.0000110643   | 0.0000521259   |  |

| συνολικά  | -                                                                          | 116.2761016 | 0.2352798      | 211.6311248    | 0.5785634      | 2.7257132      |  |

Σχήμα 12: Χρόνος υπολογισμών για SW και HW υλοποιήσεις.

### Acknowledgments

The current thesis is the result of my work in collaboration with the Microprocessors and Digital Systems Laboratory (MicroLab) of NTUA. I would like to thank my supervisor, Prof. Dimitrios Soudris for the trust he showed in me and for his guidance and encouragement throughout the conduction of the thesis. The educational opportunities that he offered me undoubtedly helped me evolve both on a professional and personal level. I would also like to sincerely thank Postdoctoral Researcher Sotiris Xydis for his contribution and precious guidance. His insightful comments and constructive criticism were determinative for the completion of my work. I am also grateful to Doctoral Student Vasileios Tsoutsouras for his invaluable contribution. His guidance and advice as well as his constant support and encouragement helped me cope with the challenges that occurred. Both their work has been a true inspiration for me. I would also like to thank all the members of the laboratory with whom I have interacted during the course of my thesis conduction. Their friendliness and sincere will to help have made these last months one of the fondest memories I have from my studies in NTUA.

I would also like to thank my fellow students and especially my closest friends for being an integral part of my life during these last five years. Finally I would like to wholeheartedly thank my family for their love and support throughout all the challenges of my life.

## List of Figures

| 1   | Ροή Ανάλυσης ΗΚΓ                                                                                                              | ix    |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-------|

| 2   | Παραλληλισμός σε Επίπεδο Μπλοκ                                                                                                | XV    |

| 3   | Απόδοση και Χρησιμοποίηση Πόρων για αυξανόμενο αριθμό διαμερίσεων (μη αυ-                                                     |       |

|     | τόματη)                                                                                                                       | XV    |

| 4   | $\Delta$ ενδρικής δομής υπολογισμοί και χρονοδρομολόγηση                                                                      | xvii  |

| 5   | Σχηματική Αναπαράσταση της Διαίρεσης Πίνακα                                                                                   | xxi   |

| 6   | Σχηματική Αναπαράσταση της Μορφοποίησης Πίνακα                                                                                | xxi   |

| 7   | Pipeline εξωτερικού βρόχου                                                                                                    | xxii  |

| 8   | Εκτύλιξη εσωτερικού βρόχου κατά διαφορετικό παράγοντα. Στήλες αριστερά προς τα δεξιά:κέρδος χρόνου εκτέλεσης, BRAM,DSP,FF,LUT | xxiii |

| 9   | $\Delta$ ιαίρεση πίνακα support vector. Στήλες αριστερά προς τα δεξιά:κέρδος χρόνου εκτέλεσης, BRAM,DSP,FF,LUT                | xxiii |

| 10  | Σύγχριση επιτάχυνσης μεταξύ όλων των υλοποιήσεων                                                                              | xxiv  |

| 11  | Καμπύλη Pareto                                                                                                                | xxv   |

| 12  | Χρόνος υπολογισμών για SW και HW υλοποιήσεις                                                                                  | xxvii |

| 2.1 | Heart Physiology [1]                                                                                                          | 4     |

| 2.2 | ECG Waveform Typical Morphology [2]                                                                                           | 5     |

| 2.3 | ECG analysis flow                                                                                                             | 6     |

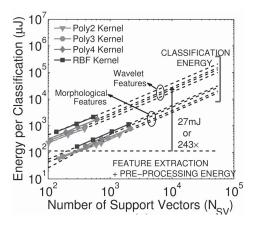

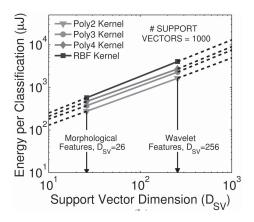

| 2.4 | Classification energy scales with N_sv [3]                                                                                    | 7     |

| 2.5 | Classification energy scales with D_sv [3]                                                                                    | 7     |

| 3.1 | SVM based classification                                                                                                      | 12    |

| 3.2 | Algorithmic C to Co-Processing Accelerator Integration [4]                                                                    | 13    |

| 3.3 | Vivado HLS Tiered Verification Flow [4]                                                                                       | 14    |

| 3.4 | HLS Proposed Work Flow                                                                                                        | 15    |

| 4.1 | Parallelism in Computations                                                                                                   | 19    |

| 4.2 | Coarse Level Parallelism                                                                                                      | 20    |

| 43  | Performance and utilization for increasing number of partitions (automatic)                                                   | 22    |

| 4.4  | Performance and utilization for increasing number of partitions (manual)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.5  | Speedup gain comparison (automatic vs manual)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24         |

| 4.6  | Tree based computations for manual unrolling and HLS scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26         |

| 4.7  | Scheduling Comparison between manual and automatic unrolling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26         |

| 4.8  | Latency in Cycles for Automatic vs Manual Unroll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29         |

| 4.9  | Latency Gain for Automatic vs Manual Unroll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29         |

| 4.10 | BRAM Utilization for Automatic vs Manual Unroll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29         |

| 4.11 | DSP Utilization for Automatic vs Manual Unroll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29         |

| 4.12 | Flip Flop Utilization for Automatic vs Manual Unroll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29         |

| 4.13 | LUT Utilization for Automatic vs Manual Unroll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29         |

| 5.1  | Array partition schematically                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31         |

| 5.2  | Array reshape schematically                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32         |

| 5.3  | $\label{thm:pipelining-loop_in_thm} Pipelining\ loop\_i.\ Columns\ from\ left\ to\ right: Latency\ gain\ and\ BRAM, DSP, FF, LUCCON, and the pipelining loop\_in and left to\ right: Latency\ gain\ and\ BRAM, DSP, FF, LUCCON, and the pipelining\ loop\_in\ depth and left to\ right: Latency\ gain\ and\ BRAM, DSP, FF, LUCCON, and the pipelining\ loop\_in\ depth and\ left to\ right: Latency\ gain\ and\ BRAM, DSP, FF, LUCCON, and the pipelining\ loop\_in\ depth and\ left to\ right: Latency\ gain\ and\ BRAM, DSP, FF, LUCCON, and\ loop\_in\ depth and\ loop\ loop\_in\ depth and\ loop\ loop$ | JT         |

|      | utilization with and without the directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33         |

| 5.4  | Unrolling loop_i. Columns from left to right:Latency gain and BRAM,DSP,FF,LU utilization with and without the directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | T<br>34    |