### National Technical University of Athens School of Electrical and Computer Engineering Division of Computer Science Microprocessors and Digital Systems Laboratory

# Cross-Layer Rapid Prototyping and Synthesis of Application-Specific and Reconfigurable Many-accelerator Platforms

## Dissertation Dionysios Diamantopoulos

Athens, 2015

### National Technical University of Athens School of Electrical and Computer Engineering Division of Computer Science Microprocessors and Digital Systems Laboratory

## Cross-Layer Rapid Prototyping and Synthesis of Application-Specific and Reconfigurable Many-accelerator Platforms

### Dissertation

of

### **Dionysios Diamantopoulos**

Submitted to the

School of Electrical and Computer Engineering

of National Technical University of Athens

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Athens, 2015

### National Technical University of Athens School of Electrical and Computer Engineering Division of Computer Science Microprocessors and Digital Systems Laboratory

# Cross-Layer Rapid Prototyping and Synthesis of Application-Specific and Reconfigurable Many-accelerator Platforms

| Advisory Committee                             |                                          |                                                |  |  |

|------------------------------------------------|------------------------------------------|------------------------------------------------|--|--|

| Dimitrios Soudris<br>Assoc. Professor. N.T.U.A | Kiamal Pekmestzi<br>Professor N.T.U.A.   | George Economakos<br>Assis. Professor N.T.U.A. |  |  |

| Pro                                            | omotion Committee                        |                                                |  |  |

| Dimitrios Soudris<br>Assoc. Professor N.T.U.A. | Kiamal Pekmestzi<br>Professor N.T.U.A.   | George Economakos<br>Assis. Professor N.T.U.A. |  |  |

| George Theodo<br>Assis. Professor U.           | ridis Dionysios<br>Patras Assoc. Profess |                                                |  |  |

| <br>Michael Hübn<br>Professor RU               |                                          |                                                |  |  |

### Dionysios Diamantopoulos

PhD, School of Electrical and Computer Engineering National Technical University of Athens, Greece Diploma, Computer Engineering & Informatics Department Polytechnic School, University of Patras, Greece

#### Copyright © 2015 Dionysios Diamantopoulos

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

This dissertation was co-financed by the research programs of European Space Agency (ESA), "SPAring Robotics Technologies For Autonomous Navigation (SPARTAN)" (ESA / ESTEC ITT Reference AO / 1-6512 / 10 / NL / EK), "Spartan EXTension Activity" (SEXTANT) (ESA / ESTEC ITT Reference 4000103357 / 11 / NL / EK) and "Code Optimisation Modication Partitioning" (COMPASS) (ESA / ESTEC ITT Reference). Also form European research programs FP7-248716 2PARMA and FP7-215244 MOSART. Finally, part of this dissertation was partially financed from national resources and the National Strategic Reference Framework (NSRF) 2007-2013 for the project "Next Generation Millimeter Wave Backhaul Radio".

Electronic version of this dissertation is available online at:

http://nestor.microlab.ntua.gr/

Figure 1 Thesis word cloud, after lexical analysis with Detex v2.6 & IBM Word Cloud build 32.

### **Abstract**

echnological advances of recent years laid the foundation consolidation of informatisation of society, impacting on economic, political, cultural and social dimensions. At the peak of this realization, today, more and more everyday devices are connected to the web, giving the term "Internet of Things". The future holds the full connection and interaction of IT and communications systems to the natural world, delimiting the transition to natural cyber systems and offering meta-services in the physical world, such as personalized medical care, autonomous transportation, smart energy cities etc... Outlining the necessities of this dynamically evolving market, computer engineers are required to implement computing platforms that incorporate both increased systemic complexity and also cover a wide range of meta-characteristics, such as the cost and design time, reliability and reuse, which are prescribed by a conflicting set of functional, technical and construction constraints. This thesis aims to address these design challenges by developing methodologies and hardware/software co-design tools that enable the rapid implementation and efficient synthesis of architectural solutions, which specify operating meta-features required by the modern market. Specifically, this thesis presents a) methodologies to accelerate the design flow for both reconfigurable and application-specific architectures, b) coarse-grain heterogeneous architectural templates for processing and communication acceleration and c) efficient multiobjective synthesis techniques both at high abstraction level of programming and physical silicon level.

Regarding to the acceleration of the design flow, the proposed methodology employs virtual platforms in order to hide architectural details and drastically reduce simulation time. An extension of this framework introduces the systemic co-simulation using reconfigurable acceleration platforms as co-emulation intermediate platforms. Thus, the development cycle of a hardware/software product is accelerated by moving from a vertical serial flow to a circular interactive loop. Moreover the simulation capabilities are enriched with efficient detection and correction techniques of design errors, as well as control methods of performance metrics of the system according to the desired specifications, during all phases of the system development. In orthogonal correlation with the aforementioned methodological framework, a new architectural template is proposed, aiming at bridging the gap between design complexity and technological productivity using specialized hardware accelerators in heterogeneous systems-on-chip and networkon-chip platforms. It is presented a novel co-design methodology for the hardware accelerators and their respective programming software, including the tasks allocation to the available resources of the system/network. The introduced framework provides implementation techniques for the accelerators, using either conventional programming flows with hardware description language or abstract programming model flows, using techniques from high-level synthesis. In any case, it is provided the option of systemic measures optimization, such as the processing speed, the throughput, the reliability, the power consumption and the design silicon area. Finally, on addressing the increased complexity in design tools of reconfigurable systems, there are proposed novel multi-objective optimization evolutionary algorithms which exploit the modern multicore processors and the coarse-grain nature of multithreaded programming environments (e.g. OpenMP) in order to reduce the placement time, while by simultaneously grouping the applications based on their intrinsic characteristics, the effectively explore the design space effectively.

The efficiency of the proposed architectural templates, design tools and methodology flows is evaluated in relation to the existing edge solutions with applications from typical computing domains, such as digital signal processing, multimedia and arithmetic complexity, as well as from systemic heterogeneous environments, such as a computer vision system for autonomous robotic space navigation and many-accelerator systems for HPC and workstations/datacenters. The results strengthen the belief of the author, that this thesis provides competitive expertise to address complex modern - and projected future - design challenges.

### Contents

| Al | ostra | ct      |                                                       | ix   |

|----|-------|---------|-------------------------------------------------------|------|

| Li | st of | Figure  | es                                                    | xv   |

| Li | st of | Table   | s                                                     | xxi  |

| N  | omer  | clatur  | re                                                    | xxv  |

| 1  |       | oduct   | <del></del>                                           | 1    |

|    |       |         | s Research Background                                 |      |

|    | 1.2   |         | rtation Overview                                      |      |

|    |       |         | Chapters Organization                                 |      |

|    | Refe  | erences | 8                                                     | . 11 |

| 2  | Rap   | id Pro  | totyping Exploiting Hybrid-Virtual System-on-Chips    | 15   |

|    |       |         | rch Motivation for Virtual Prototyping                | . 15 |

|    | 2.2   |         | ng approaches for system modeling with virtual plat-  |      |

|    |       |         |                                                       |      |

|    |       |         | Communication between Host PC and Virtual Platform    | . 18 |

|    |       | 2.2.2   | Communication between Virtual Platform and Target     | 0.1  |

|    | 0.0   | D ( )   | Hardware                                              |      |

|    | 2.3   |         | typing Methodology                                    | . 22 |

|    |       | 2.3.1   | frastructure                                          | 25   |

|    |       |         | 2.3.1.1 Host2VP                                       |      |

|    |       |         | 2.3.1.2 VP2HW                                         |      |

|    |       |         | 2.3.1.3 Implementation of the HotTalk FPGA Transactor | _    |

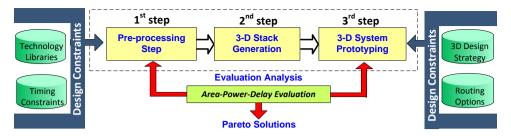

|    |       | 2.3.2   | Evaluation of 3-D Embedded Systems                    | _    |

|    |       |         | 2.3.2.1 Pre-processing                                |      |

|    |       |         | 2.3.2.2 3-D Stack Generation                          |      |

|    |       |         | 2.3.2.3 3-D System Prototyping                        |      |

|    | 2.4   | Exper   | rimental Results                                      |      |

|    |       | 2.4.1   | Evaluation of Communication Infrastructure            | . 35 |

|    |       | 2.4.2   | Evaluating the 3-D OpenRISC                           | . 38 |

|    |       | 2.4.3   | Apply Plug&Chip to a Heterogeneous Embedded Sys-      |      |

|    |       |         | tem - The SPARTAN Project                             |      |

|    | 2.5   | Concl   | usion                                                 | . 45 |

|    | Refe  | erences | 8                                                     | . 45 |

xii Contents

| 3 | Cro | ss-Lay | er Syntl  | nesis of Heterogenous Architectures            | 49    |

|---|-----|--------|-----------|------------------------------------------------|-------|

|   | 3.1 | Thern  | nal and I | Reliability Aware SDR Architectures            | . 49  |

|   |     | 3.1.1  | Introdu   | ction                                          | . 49  |

|   |     | 3.1.2  | Target S  | SDR Architecture                               | . 52  |

|   |     |        |           | ion                                            |       |

|   |     |        |           | rchitectural Considerations                    |       |

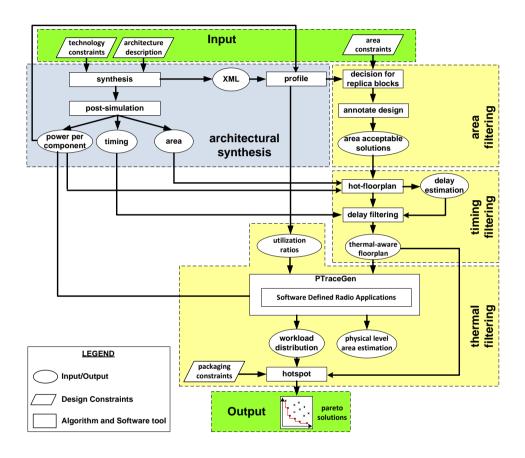

|   |     | 3.1.5  |           | ed Methodology                                 |       |

|   |     |        |           | Architecture Synthesis                         |       |

|   |     |        |           | Area Filtering                                 |       |

|   |     |        |           | Timing Filtering                               |       |

|   |     |        |           | Thermal Filtering                              |       |

|   |     | 3.1.6  | -         | nental Results                                 |       |

|   |     |        | 3.1.6.1   | Impact of Selective Replication on Temperature |       |

|   |     |        |           | Impact of Temperature on Reliability           |       |

|   |     |        |           | On designing chip multiprocessors for SDR      |       |

|   |     |        |           | sions                                          |       |

|   | 3.2 |        | _         | Network-on-Chip Multimedia Architectures       |       |

|   |     |        |           | ction                                          |       |

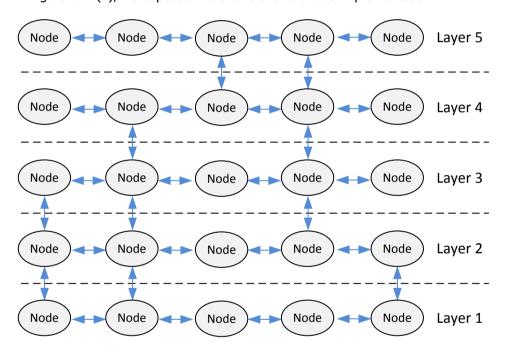

|   |     | 3.2.2  |           | cture of the Proposed Interconnection Scheme.  |       |

|   |     | 2 2 2  | 3.2.2.1   | Designing 2-D and 3-D Routers                  |       |

|   |     |        | _         | ed Methodology                                 |       |

|   |     | 3.2.4  |           | egration                                       |       |

|   |     |        |           | Pre-processing Step                            |       |

|   |     |        |           | 3-D Stack Generation                           |       |

|   |     | 205    |           | 3-D System Prototyping                         |       |

|   |     |        | _         | nental Results                                 |       |

|   | 3.3 |        |           | sions                                          |       |

|   | 5.5 | -      |           | ction                                          |       |

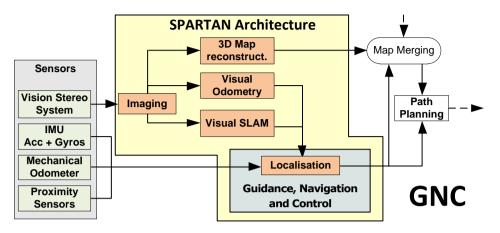

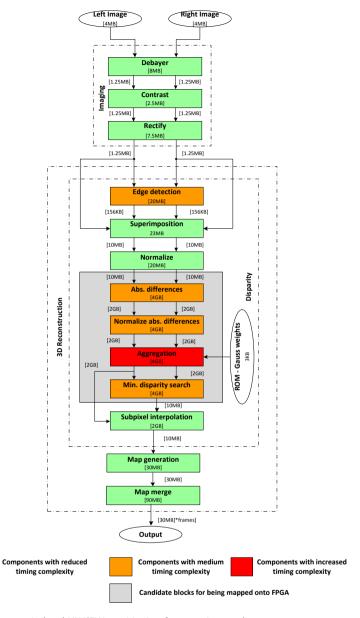

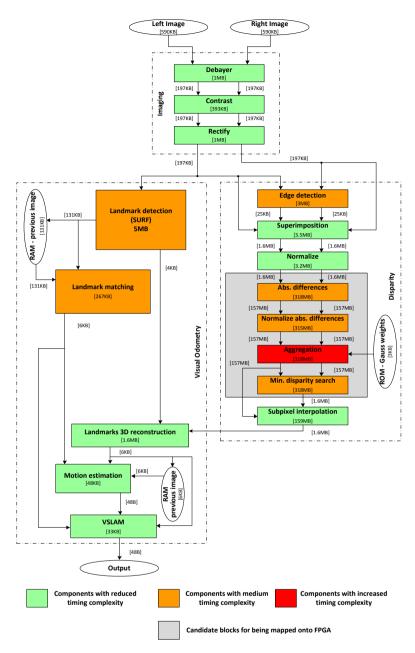

|   |     |        |           | cture of SPARTAN System                        |       |

|   |     |        |           | re/Software Co-Design Methodology              |       |

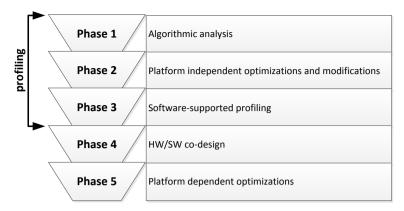

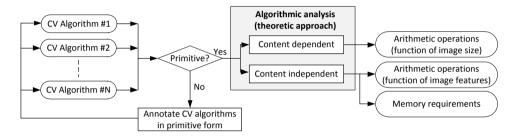

|   |     | 0.0.0  |           | Phase 1: Algorithmic analysis                  |       |

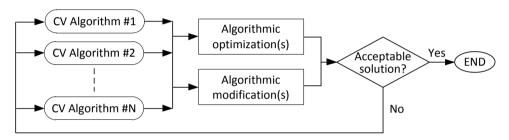

|   |     |        | 3.3.3.2   | · · · · · · · · · · · · · · · · · · ·          |       |

|   |     |        | 0.0.0.2   | Modifications                                  | . 101 |

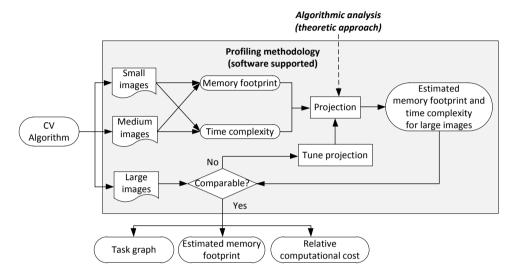

|   |     |        | 3.3.3.3   | Phase III: Software-Supported Profiling        |       |

|   |     |        | 3.3.3.4   | Phase IV: HW/SW Co-Design                      |       |

|   |     |        | 3.3.3.5   | Phase V: Platform Dependent Optimizations      |       |

|   |     | 3.3.4  | Experin   | nental Results                                 |       |

|   |     |        | 3.3.4.1   | Overall profiling results                      |       |

|   |     |        |           | Data Life-Time                                 |       |

|   |     |        |           | Estimations about HW/SW Partitioning           |       |

|   |     |        |           | Data-flow Analysis                             |       |

|   |     | 3.3.5  |           | sions                                          |       |

Contents xiii

|   | 3.4  | 3-D Integration for Digital Signal Processing SoC Architec-   |     |

|---|------|---------------------------------------------------------------|-----|

|   |      | tures                                                         | 112 |

|   |      | 3.4.1 Introduction                                            | 112 |

|   |      | 3.4.2 Proposed Framework                                      | 112 |

|   |      | 3.4.3 Experimental Results                                    | 114 |

|   |      | 3.4.4 Conclusion                                              | 117 |

|   | Refe | erences                                                       | 119 |

| 4 | Con  | nputer-Aided Design Tools for Reconfigurable Platforms        | 125 |

|   |      | Introduction                                                  | 125 |

|   |      | Related Work                                                  |     |

|   | 4.3  | The Proposed Design Framework                                 | 130 |

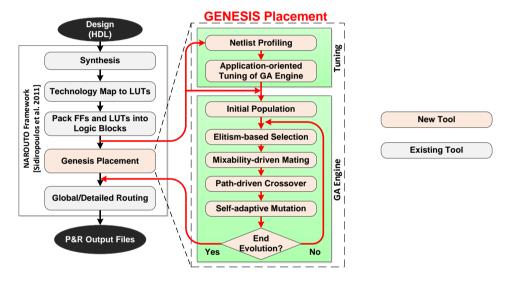

|   |      | 4.3.1 GENESIS Evolutionary Placement                          |     |

|   |      | 4.3.1.1 Selection                                             |     |

|   |      | 4.3.1.2 Mating                                                | 137 |

|   |      | 4.3.1.3 Crossover                                             | 138 |

|   |      | 4.3.1.4 Mutation                                              | 140 |

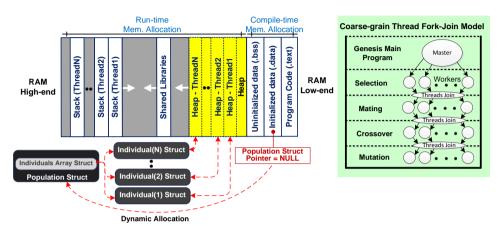

|   |      | 4.3.2 GENESIS Coarse-grain Parallelism Engine                 | 141 |

|   | 4.4  | Application-Aware Tuning of GENESIS Evolutionary Placement    |     |

|   |      | 143                                                           |     |

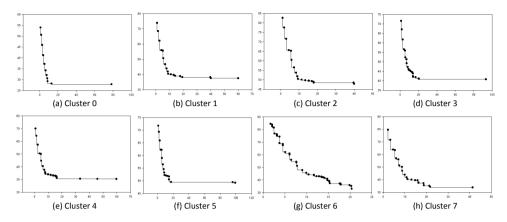

|   |      | 4.4.1 Application Level Clustering                            | 145 |

|   |      | 4.4.2 Cluster Level Exploration for Optimal Configuration Ex- |     |

|   |      | traction                                                      |     |

|   |      | Experimental Results                                          |     |

|   |      | Conclusion                                                    |     |

|   | Refe | erences                                                       | 161 |

| 5 | Arc  | hitectural Synthesis of Reconfigurable Many-Accelerator Sys-  |     |

|   | tem  |                                                               | 165 |

|   | 5.1  | Architectural template and programming interface for M.A.     |     |

|   |      | systems                                                       |     |

|   |      | 5.1.1 Introduction - Research motivation for M.A. systems     |     |

|   |      | 5.1.2 DMM-HLS for Many-Accelerator FPGAs                      |     |

|   |      | 5.1.3 Evaluation                                              |     |

|   |      | 5.1.4 Conclusions                                             |     |

|   | 5.2  | Scaling many-accelerator systems to workstations              |     |

|   |      | 5.2.1 Introduction                                            |     |

|   |      | 5.2.2 HLSMapReduceFlow Architecture                           |     |

|   |      | 5.2.2.1 Phoenix MapRecude Framework                           |     |

|   |      | 5.2.2.2 Dataflow FPGA-based Acceleration                      |     |

|   |      | 5.2.2.3 HLSMapReduceFlow Methodology for Vivado-HLS           |     |

|   |      | 5.2.2.4 Vivado-HLS Limitations for MapRecude                  |     |

|   |      | 5.2.3 Experimental Results                                    |     |

|   |      | 5.2.4 Conclusions                                             |     |

|   | Refe | erences                                                       | 195 |

0

xiv

**Curriculum Vitae**

6 Conclusions and Future Directions

199

6.1 Thesis Overview.

199

6.2 Future Directions.

202

References.

205

List of Publications

207

Contents

213

## List of Figures

| 1    | Thesis word cloud, after lexical analysis with <i>Detex v2.6 &amp; IBM Word Cloud build 32.</i>                                                                                         | vii |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1  | Worldwide semiconductor sales 1988-2014 (in billions dollars). Source: World Semiconductor Trade Statistics, [1].                                                                       | 2   |

| 1.2  | Scaling of static and dynamic power consumption of integrated circuits regarding to the technology node. Source: Mentor Graphics 2014.                                                  | 3   |

| 1.3  | Projections of the ITRS organization for the scaling of the maximum operating frequency at regular chronological studies.                                                               | 4   |

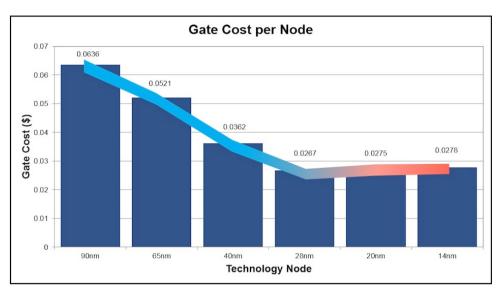

| 1.4  | Scaling manufacturing costs per gate for different technology nodes of integration. Source: IBS 2012                                                                                    | 5   |

| 1.5  | Comparison of different architectural designs approaches, with respect to their energy efficiency. Source: Bob Broderson, Berkeley                                                      |     |

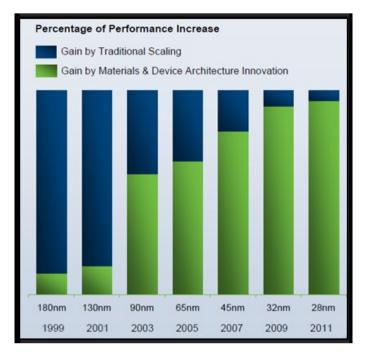

| 1.6  | Wireless group, ISSCC proceedings, Microsoft, 2011.  Performance growth rate of conventional technology scaling and architecture/materials innovation for each technology node. Source: | 6   |

| 1.7  | IBM Microelectronics, Intel IC Insights, 2012                                                                                                                                           | 8   |

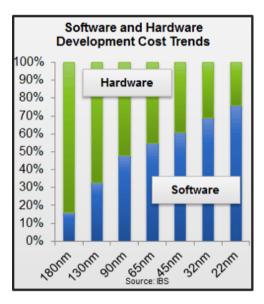

| 2.1  | Cost development trends for hardware and software deployment, in relation to technology scaling.                                                                                        | 16  |

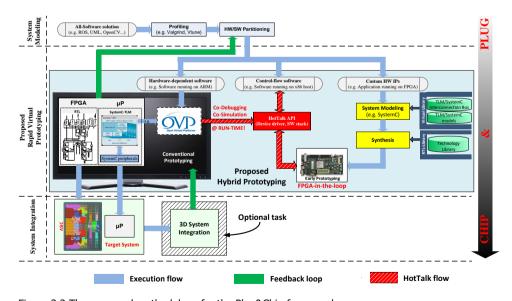

| 2.2  | The proposed methodology for the Plug&Chip framework.                                                                                                                                   | 22  |

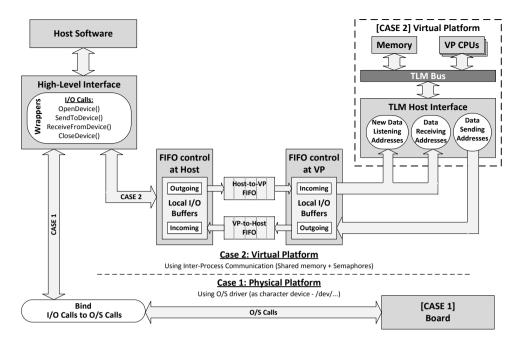

| 2.3  | Communication mechanism between Host and VP                                                                                                                                             | 26  |

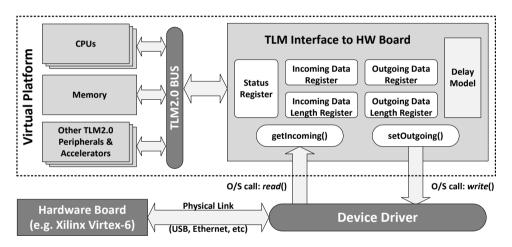

| 2.4  | Communication mechanism between VP and hardware board                                                                                                                                   | 27  |

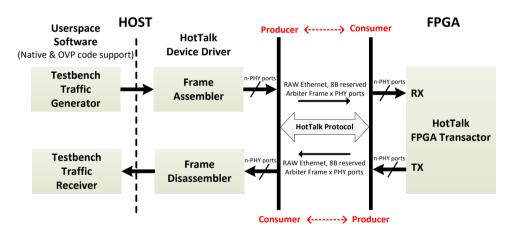

| 2.5  | The communication flow established in the transactor.                                                                                                                                   | 28  |

| 2.6  | Architecture of the employed FPGA transactor.                                                                                                                                           | 29  |

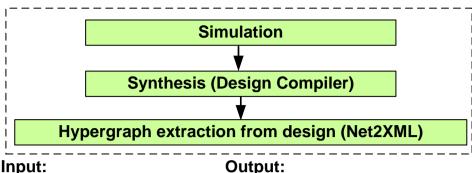

| 2.7  | Tasks for the pre-processing step.                                                                                                                                                      | 31  |

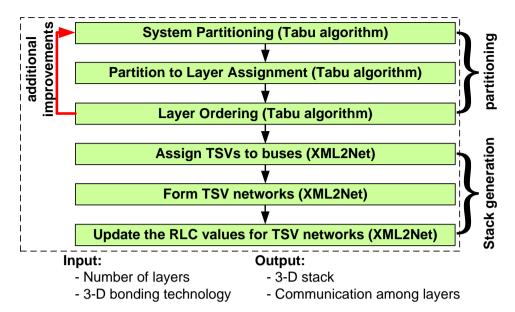

| 2.8  | Tasks for 3-D stack generation                                                                                                                                                          | 32  |

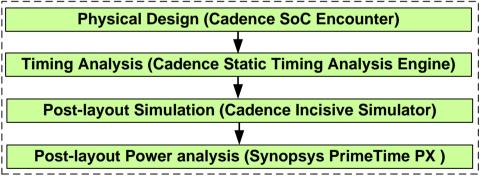

| 2.9  | Tasks for 3-D system prototyping.                                                                                                                                                       | 33  |

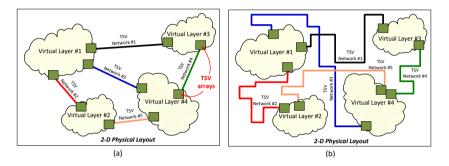

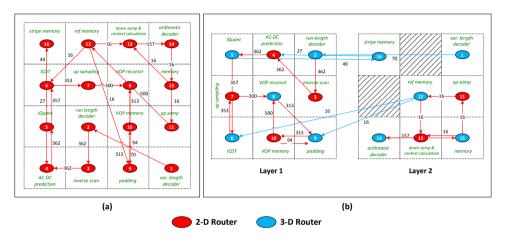

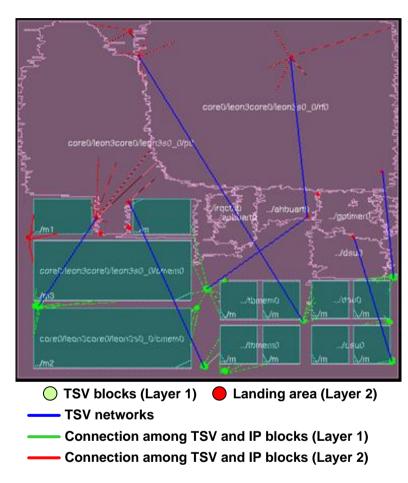

| 2.10 | design with virtual layers and TSV networks and (b) design after                                                                                                                        |     |

| 2 11 | successfully routing.                                                                                                                                                                   | 34  |

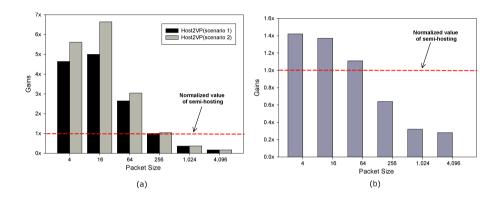

| 2.11 | Gain in term of wall-clock time for: (a) the proposed Host2VP library and (b) the proposed VP2HW library, as compared to semi-hosting approach [4].                                     | 35  |

| 2.12 | Evaluation of communication overhead between: (a) host PC and VP,                                                                                                                       | 55  |

|      | (b) VP and hardware assuming constant packet size of 4 bytes.                                                                                                                           | 37  |

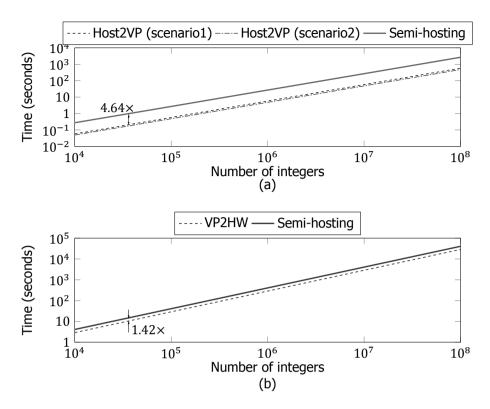

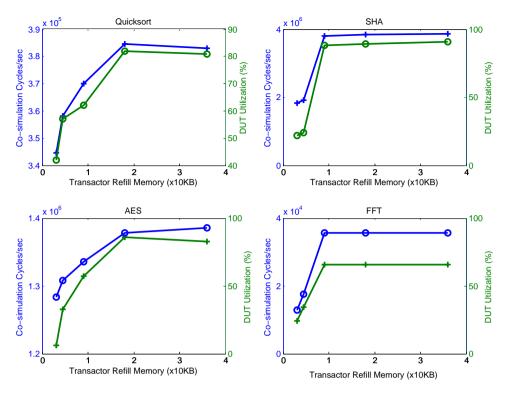

| 2.13 | Evaluation of the efficiency of introduced co-simulation approach for different benchmarks. | 38 |

|------|---------------------------------------------------------------------------------------------|----|

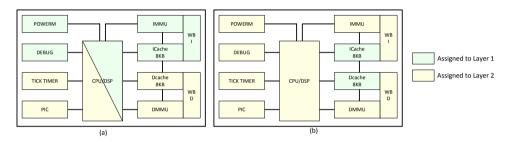

| 2.14 | Partitioning OpenRISC processors under different constraints: (i) min-                      | -  |

|      | cut partitioning and (b) technology-compatible partitioning.                                | 39 |

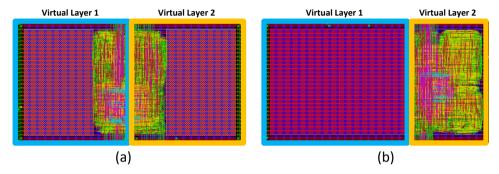

| 2.15 | Physical implementation of 3-D OpenRISC with the usage of Cadence                           | -  |

|      | SoC Encounter for the partitioning discussed in Figs. 2.14(a) and                           |    |

|      | 2.14(b), respectively                                                                       | 40 |

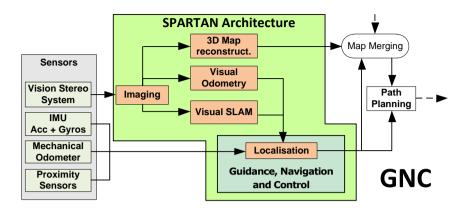

| 2.16 | Schematic overview of the SPARTAN system                                                    | 41 |

|      | Evaluation of SPARTAN system using a scenario-based trade-off anal-                         |    |

|      | ysis                                                                                        | 42 |

| 2.18 | Evaluation of SPARTAN system towards the efficiency of introduced                           |    |

|      | co-simulation approach                                                                      | 43 |

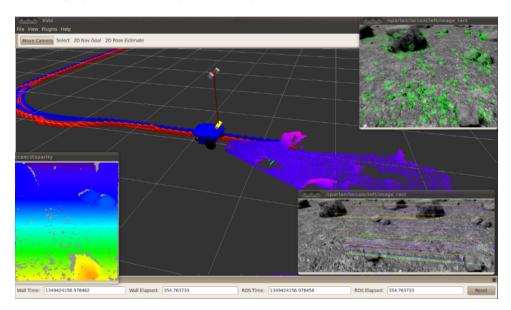

| 2.19 | Snapshot assessment of SPARTAN system on ROS/Linux environ-                                 |    |

|      | ment, using the framework Plug&Chip, on a PC-FPGA co-design plat-                           |    |

|      | form                                                                                        | 44 |

| 2.20 | snapshot assessment of a car engine control unit (ECU) on Linux                             |    |

|      | host, using the framework Plug&Chip for virtual prototyping of CV                           |    |

|      | algorithms, on a PC-FPGA co-design platform                                                 | 48 |

|      | argonamic, on a rearrast acaign placerim rearrast rearrast                                  |    |

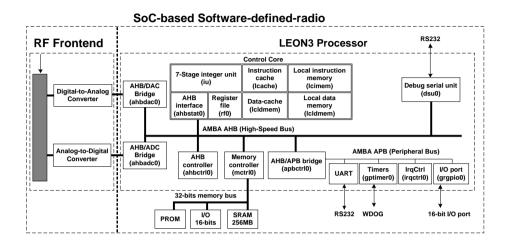

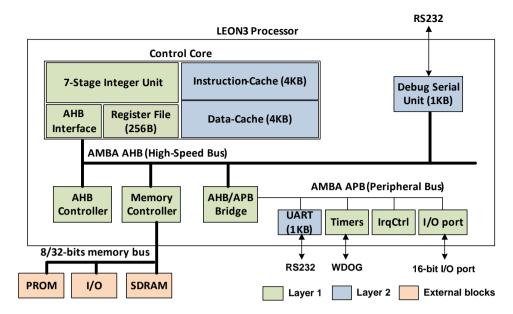

| 3.1  | The block diagram of employed SoC-based SDR                                                 | 53 |

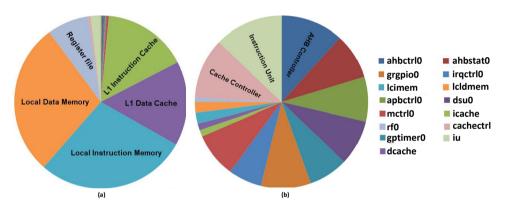

| 3.2  | (a) Power consumption and (b) Power density pies for LEON3 archi-                           |    |

|      | tecture                                                                                     | 54 |

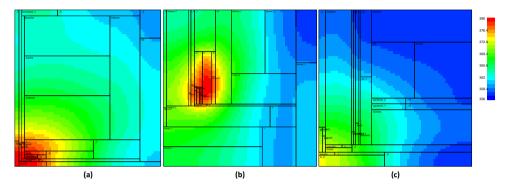

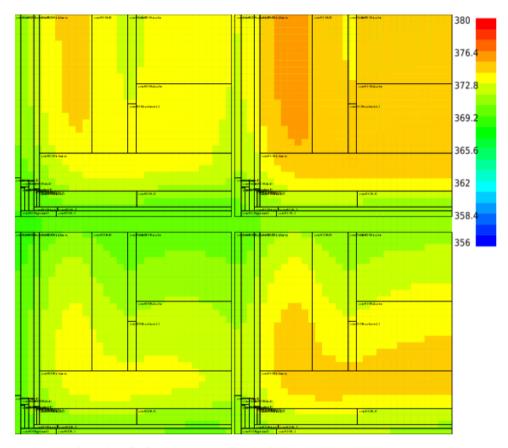

| 3.3  | Thermal profile for LEON3: (a) without considering replica blocks, (b)                      |    |

|      | with replica blocks (2×local data/instruction memories, 2×L1 data/in-                       |    |

|      | struction caches, 2×register file), and (c) with replica blocks (2×instructi                | on |

|      | unit, 2×cache controller, 2×AHB controller)                                                 | 55 |

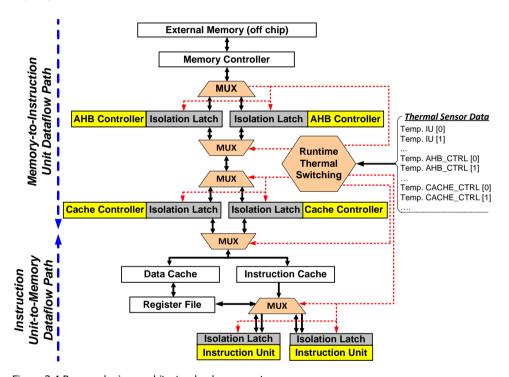

| 3.4  | Proposed micro-architectural enhancement                                                    | 57 |

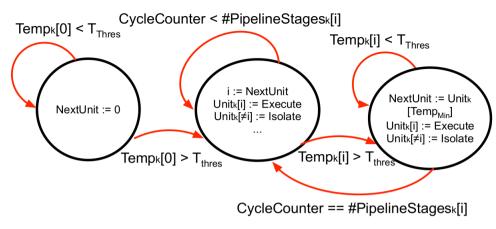

| 3.5  | Employed thermal-aware runtime controller per replicated block.                             | 59 |

| 3.6  | The proposed methodology for replication-aware thermal manage-                              |    |

|      | ment                                                                                        | 60 |

| 3.7  | Temperature variation for different instantiations of target architectural.                 | 66 |

| 3.8  | Results about power density versus maximum temperature.                                     | 67 |

| 3.9  | Results about area versus maximum temperature                                               | 69 |

|      | Evaluation in term of $A_f$ parameter for architectures with different                      |    |

|      | average temperatures                                                                        | 71 |

| 3.11 | Evaluation of different architectures under TDDB.                                           | 72 |

|      | Thermal profile for 2×2 CMP LEON3-based architecture.                                       | 73 |

|      | Normalized power density versus area overhead for multiprocessor                            |    |

| 0.10 | LEON3                                                                                       | 74 |

| 3.14 | Normalized maximum temperature versus area overhead for multi-                              |    |

|      | processor LEON3                                                                             | 75 |

| 3.15 | Example for an application's communication graph.                                           | 77 |

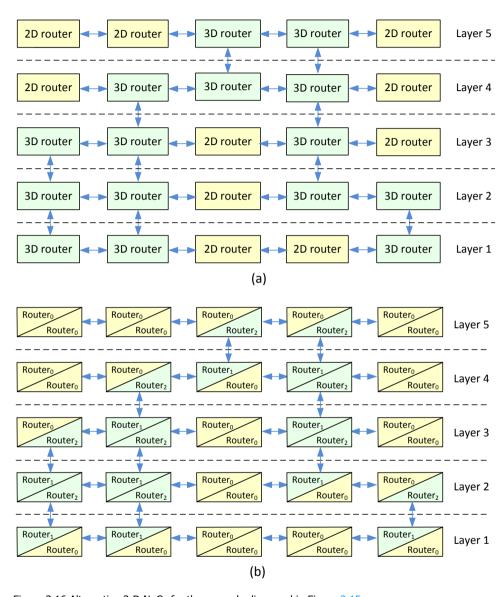

|      | Alternative 3-D NoCs for the example discussed in Figure 3.15.                              | 79 |

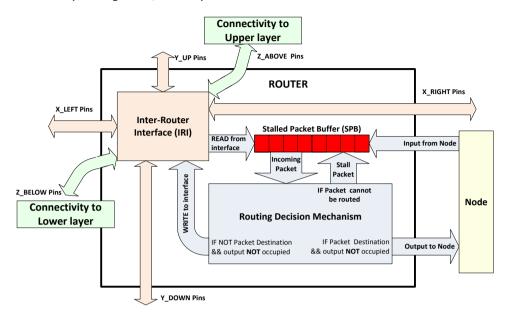

|      | Architectural template for a 3-D router.                                                    | 80 |

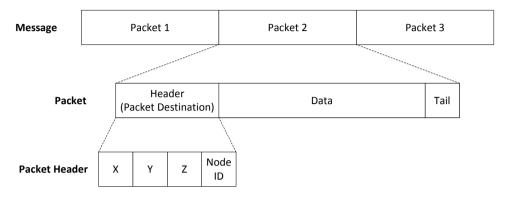

|      | Structure of packets for our proposed NoC architecture.                                     | 81 |

| -    | Charles of particle for our proposed free distinction of the first first                    | -  |

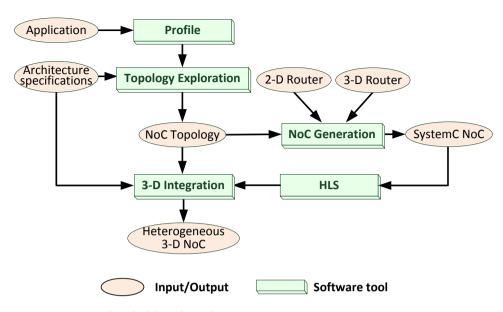

|       | Proposed methodology for evaluating 3-D NoCs.                                                                    |       |

|-------|------------------------------------------------------------------------------------------------------------------|-------|

|       | Tasks for the pre-processing step.                                                                               |       |

|       | Tasks for 3-D stack generation                                                                                   |       |

|       | Tasks for 3-D system prototyping.                                                                                | . 86  |

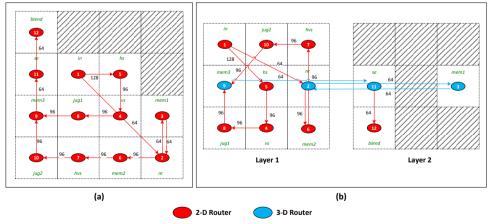

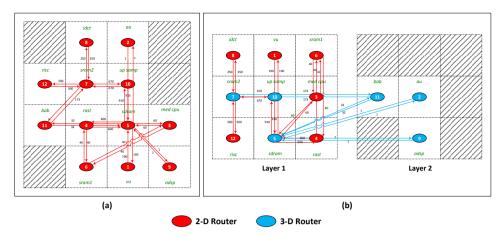

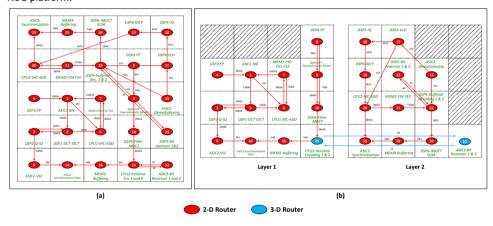

| 3.23  | Mapping of VOPD application onto: (a) 2-D NoC and (b) the proposed                                               |       |

|       | heterogeneous 3-D NoC platform.                                                                                  | . 88  |

| 3.24  | Mapping of MWD application onto: (a) 2-D NoC and (b) the proposed                                                |       |

|       | heterogeneous 3-D NoC platform.                                                                                  | . 88  |

| 3.25  | Mapping of MPEG-4 application onto: (a) 2-D NoC and (b) the pro-                                                 |       |

|       | posed heterogeneous 3-D NoC platform                                                                             | . 89  |

| 3.26  | Mapping of MMS application onto: (a) 2-D NoC and (b) the proposed                                                |       |

| 2 27  | heterogeneous 3-D NoC platform.                                                                                  |       |

|       | Evaluation of 2-D and 3-D router in term of equivalent gates.                                                    |       |

|       | Evaluation of 2-D and 3-D router in term of latency.                                                             |       |

|       | Evaluation of 2-D and 3-D router in term of energy dissipation.                                                  | . 92  |

| 3.30  | Physical layouts for the introduced heterogeneous 3-D NoC regarding                                              | 02    |

| 2 24  | the MPEG-4 application.                                                                                          | . 93  |

| 3.31  | Number of packet hops for different architectural solutions: (i) a                                               |       |

|       | homogeneous 2-D NoC, (ii) a homogeneous 3-D NoC and (iii) the                                                    | . 94  |

| 2 22  | proposed heterogeneous 3-D NoC.  Maximum operation frequency for different instantiations of NoC.                |       |

|       |                                                                                                                  |       |

|       | Power consumption for different instantiations of NoC.  Schematic view of SPARTAN mapping and localization mode. |       |

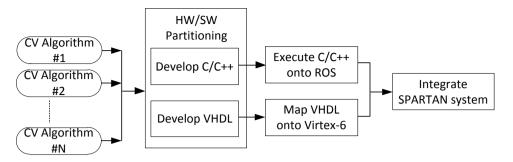

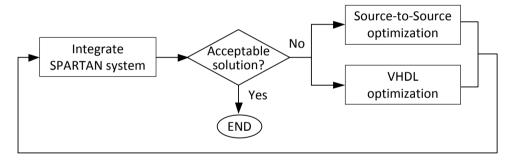

|       | Abstract view of the introduced HW/SW co-design methodology.                                                     |       |

|       | Tasks performed during the algorithmic analysis.                                                                 |       |

|       | Proposed methodology for performing platform independent opti-                                                   | . 100 |

| 3.37  | mizations and modifications.                                                                                     | 101   |

| 3 38  | Profiling tools.                                                                                                 |       |

|       | Proposed methodology for performing software-supported profiling.                                                |       |

|       | Proposed methodology for performing HW/SW co-design.                                                             |       |

|       | Proposed methodology for enhancing the performance of SPARTAN                                                    | . 103 |

| 31.11 | system with platform-dependent optimizations.                                                                    | 105   |

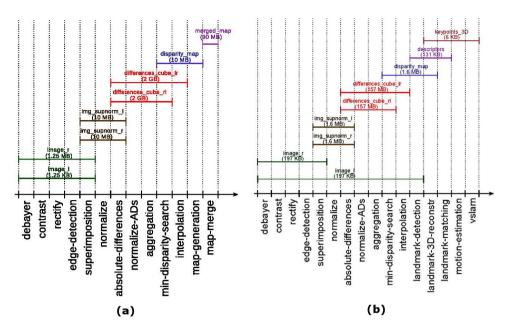

| 3.42  | Profiling results (a) for mapping mode and (b) for localization mode.                                            |       |

|       | Data life-time (a) for mapping mode and (b) localization mode.                                                   |       |

|       | Coarse-grain level HW/SW partitioning for mapping mode                                                           |       |

|       | Coarse-grain level HW/SW partitioning for localization mode.                                                     |       |

|       | Proposed framework for supporting rapid evaluation of 3-D SoCs.                                                  |       |

|       | Block diagram for the Leon3 processor.                                                                           |       |

|       | Example of designing a 3-D instantiation of LEON3 processor on                                                   |       |

|       | legacy 2-D Cadence SoC Encounter [24]                                                                            | . 116 |

|       | <u> </u>                                                                                                         |       |

| 4.1   | CPU speed versus FPGA logic capacity [2]                                                                         | . 126 |

| 4.2   | Proposed framework for parallel application placement.                                                           | . 130 |

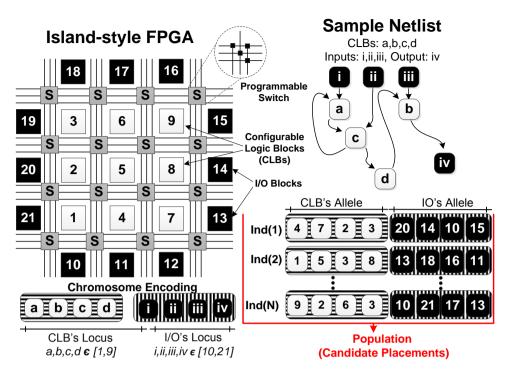

| 4.3   | The employed representation of FPGA with a chromosome structure                                                  |       |

|       | and an example of netlist encoding                                                                               | . 133 |

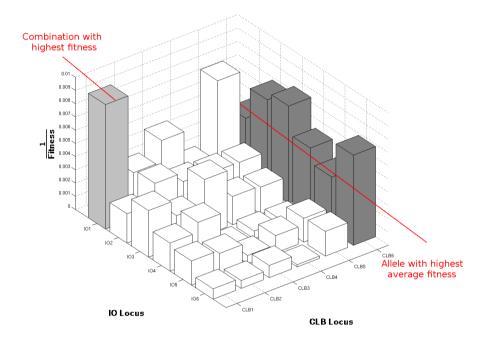

| 4.4  | The alu4 fitness landscape with six alleles per locus. Alleles ${\it CLB}_{1:6}$                                                            |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | in locus $CLB$ and $IO_{1:6}$ in locus $IO$ give 36 genotypes $CLB_jIO_k$ with                                                              |     |

| 4.5  | 7 7 7                                                                                                                                       | 134 |

| 4.5  | (a) Baseline FPGA architecture. (b) HDL-to-CLBs Synthesis. (c) Graph                                                                        | 127 |

| 16   | representation of a design circuit. (d) FPGA physical placement.                                                                            | 13/ |

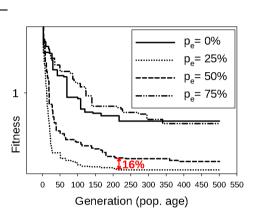

| 4.6  | GENESIS elitism rate impact on quality for MCNC circuit s38417 (6406                                                                        | 120 |

| 4.7  | CLBs, 29 Inputs, 106 Outputs), $n_p$ =100, $g_p$ =500, $mutation\_rate$ =25 Thread-oriented GA memory structure and the corresponding fork- | 130 |

| 7.7  | join model                                                                                                                                  | 142 |

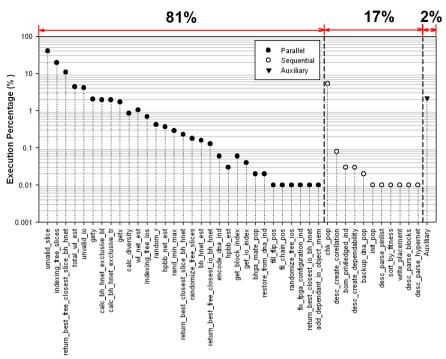

| 4.8  | Execution run-time breakdown analysis for functionalities of GENESIS                                                                        | 172 |

| 1.0  | •                                                                                                                                           | 144 |

| 4.9  | ·                                                                                                                                           | 147 |

|      | The Delay vs. Rutime Pareto front per cluster $F_i$ . Data normalized to                                                                    |     |

|      | the per cluster least efficient evaluated solution.                                                                                         | 151 |

| 4.11 | Evaluation for different combinations of <i>population size</i> and <i>popula-</i>                                                          |     |

|      | tion age regarding the bigkey benchmark                                                                                                     | 152 |

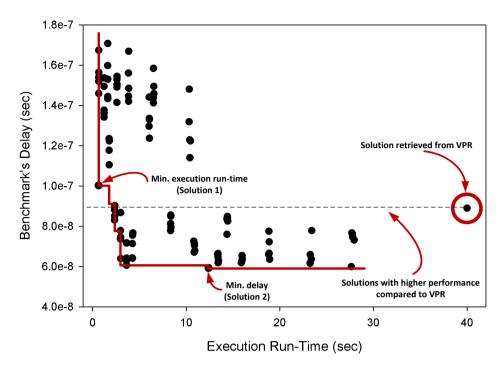

| 4.12 | Candidate solutions that are evaluated during placement.                                                                                    | 155 |

| 4.13 | Scaling of execution speedup for the GENESIS placer.                                                                                        | 156 |

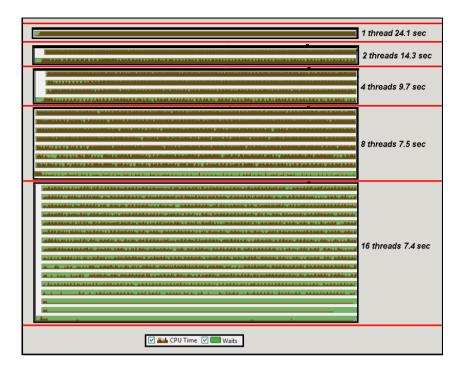

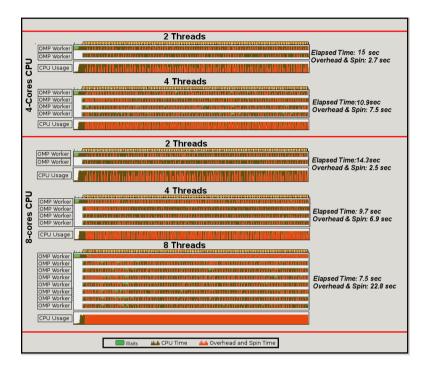

| 4.14 | GENESIS thread time breakdown analysis: CPU and Wait Time                                                                                   | 157 |

|      | GENESIS thread time breakdown analysis: Overhead and Spin Time.                                                                             | 158 |

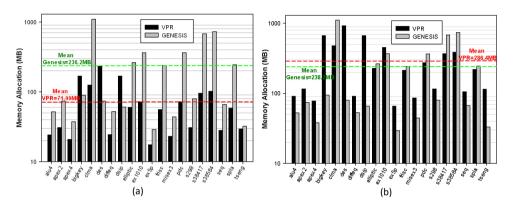

| 4.16 | Memory requirements for (a) minimum FPGA size and (b) double size                                                                           |     |

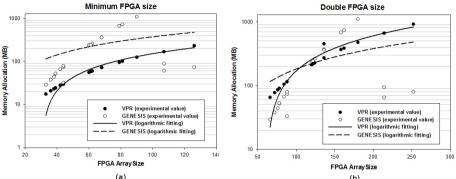

|      | for the FPGA array.                                                                                                                         | 159 |

| 4.17 | Memory footprint trend towards FPGA slices for (a) minimum FPGA                                                                             |     |

|      | size and (b) double size for the FPGA array                                                                                                 | 160 |

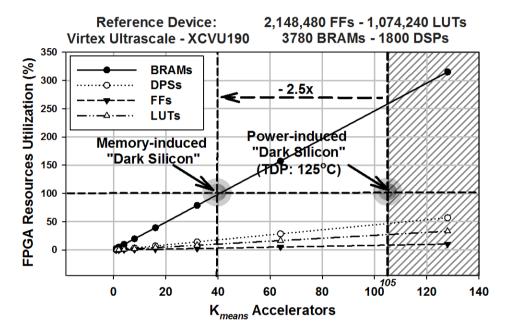

| 5.1  | Accelerators scalability analysis of $K_{means}$ clustering algorithm: $A_i$ -Accelerators= [1:                                             |     |

| 5.1  | 128], $N_p$ -Points=2 × 10 <sup>4</sup> , $P_k$ -Clusters=3                                                                                 | 167 |

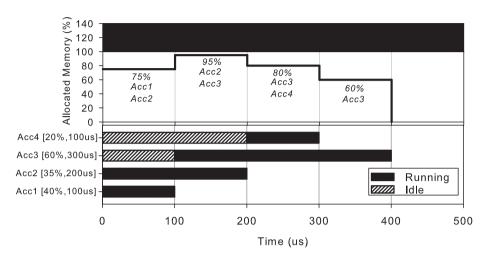

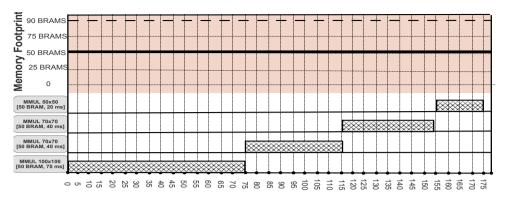

| 5.2  | Example scenario with four accelerators <i>Acc-i</i> [Static Memory Utiliza-                                                                | 10, |

| 3.2  | tion%, Latency]. All accelerators should start at time 0. The de-                                                                           |     |

|      | sign is un-synthesizable with static memory allocation. Lower part                                                                          |     |

|      | shows the final scheduling with DMM. Upper part shows the respec-                                                                           |     |

|      | tive memory footprint. Due to time-scale, we neglect showing in-                                                                            |     |

|      | stantaneous memory footprint transitions occurred whenever a new                                                                            |     |

|      | DMM allocation arrives                                                                                                                      | 169 |

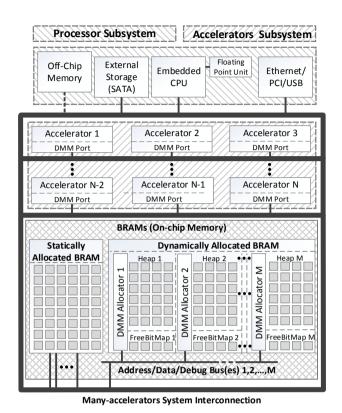

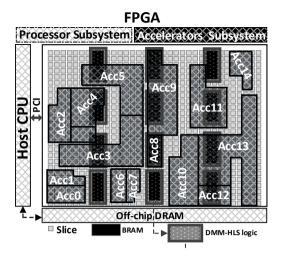

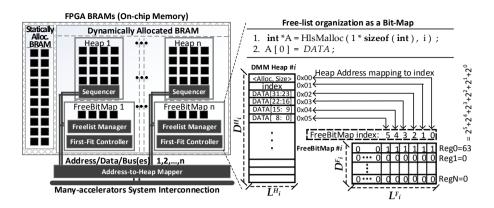

| 5.3  | Abstract proposed architectural template for memory efficient many-accelerator FPGA-                                                        |     |

|      | ,                                                                                                                                           | 170 |

| 5.4  | Proposed architectural template for memory efficient many-accelerator                                                                       |     |

|      | FPGA-based systems                                                                                                                          | 1/1 |

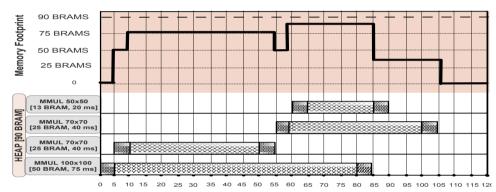

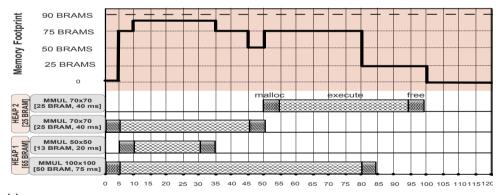

| 5.5  | Performance gains due to parallel and overlapped accelerators' ex-                                                                          |     |

|      | ecution enabled by DMM-HLS. Accelerator scheduling and memory footprint a) Conventional HLS with static allocation, b) DMM-HLS              |     |

|      | with 1 single heaps, c) DMM-HLS with 2-heaps. FPGA platform: 90                                                                             |     |

|      | BRAMs. Total MMULs' memory request: 113 BRAMs.                                                                                              | 172 |

| 5.6  | Architectural template of DMM-HLS memory controllers supporting                                                                             | 1/2 |

| 3.0  | DMM onto FPGAs                                                                                                                              | 173 |

|      |                                                                                                                                             |     |

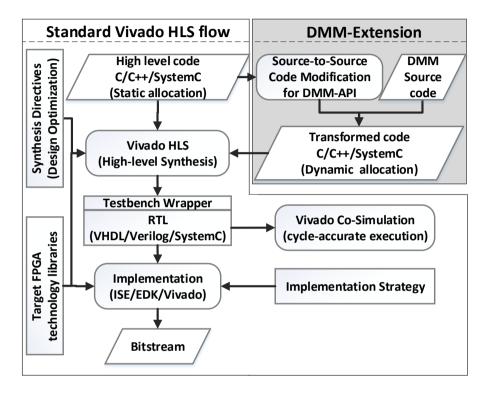

| 5.7          | Extension on Vivado HLS flow to support dynamic memory management for many-accelerators FPGA-based systems.                       | 174 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

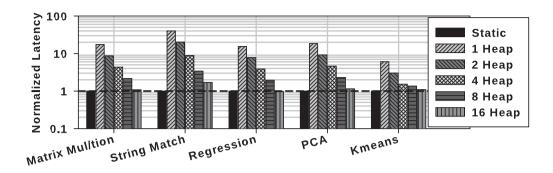

|              | Per-accelerator latency overhead for different number of heaps                                                                    |     |

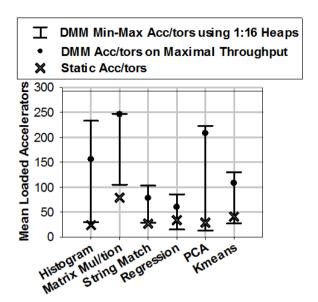

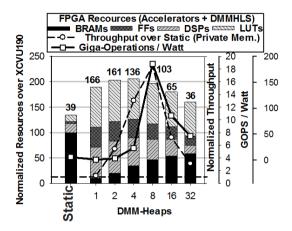

| 5.9          | Comparison on accelerators density between Static and DMM-HLS setups                                                              | 177 |

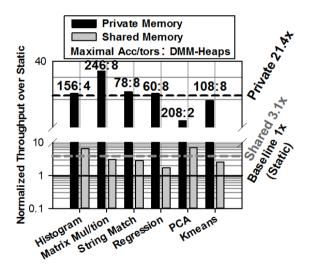

| 5.10         | Comparison on system's throughput between Static and DMM-HLS                                                                      |     |

| 5.11         | setups                                                                                                                            |     |

|              | trade-off, between Static and DMM-HLS setups.                                                                                     | 178 |

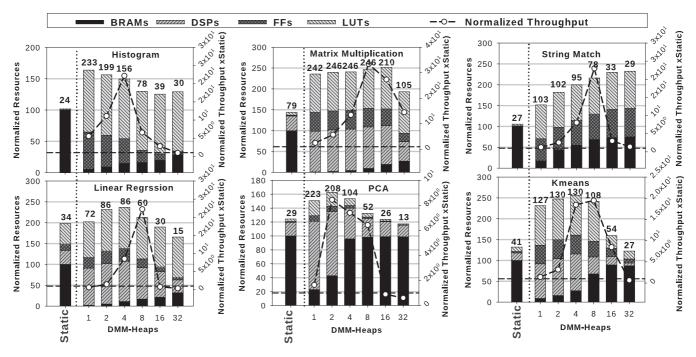

| 5.12         | Comparison on resources breakdown versus throughput and energy trade-offs between Static and DMM-HLS setups, for all employed ap- |     |

|              | plications                                                                                                                        | 180 |

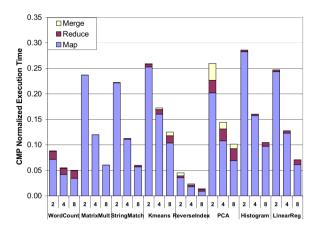

| 5.13         | Execution time breakdown for a CMP system on Phoenix MapRecude                                                                    |     |

| 5 1 <i>1</i> | framework[24]                                                                                                                     | 104 |

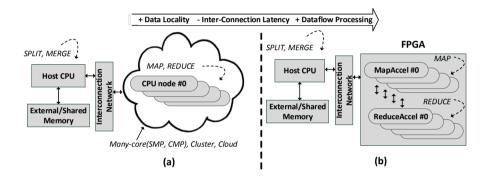

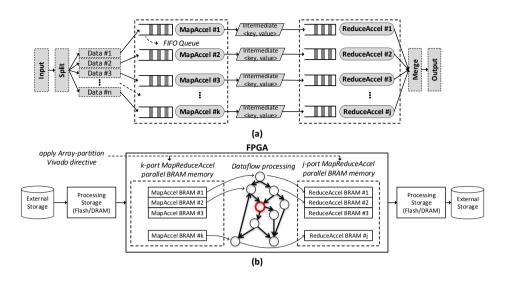

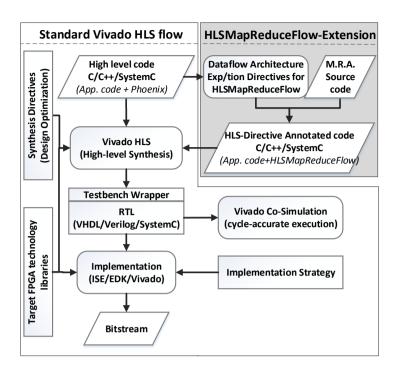

| 3.14         | proposed HLSMapReduceFlow.                                                                                                        | 124 |

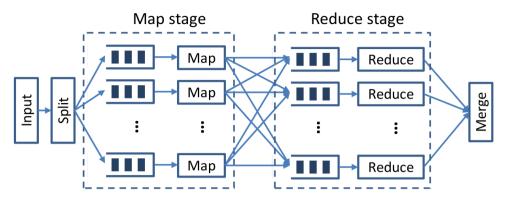

| 5 15         | The MapReduce programming framework                                                                                               |     |

|              | HLSMapReduceFlow dataflow architecture: Every dataflow computation node is working in its unique memory. The system memory        | 103 |

|              | is partitioned to <i>k-port</i> and <i>j-port</i> banks for the <i>k</i> -map and <i>j</i> -reduce                                | 107 |

| E 17         | tasks respectively.                                                                                                               | 10/ |

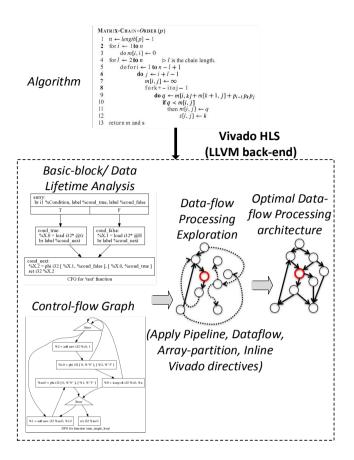

| 5.17         | Forcing dataflow exploration from control-flow algorithm description with Vivado HLS                                              | 188 |

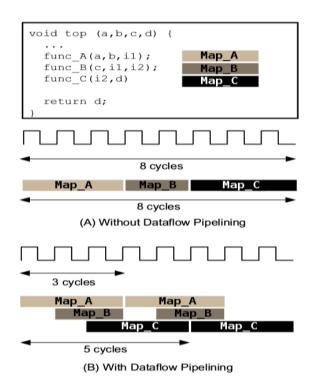

| 5.18         | (a) Sequential Functional Description (b) Parallel Process Architecture                                                           | 189 |

| 5.19         | Proposed extension on Vivado HLS flow to support MapReduce frame-                                                                 | 100 |

| E 20         | work for FPGA-based systems                                                                                                       | 190 |

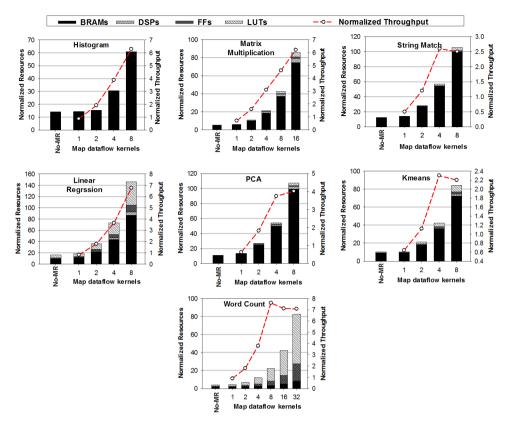

| 5.20         | work                                                                                                                              | 192 |

### List of Tables

| 2.1                               | Qualitative comparison among Host-to-VP communication mechanisms.                                                                                                                                           | 19         |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.2                               | Qualitative comparison among VP-to-Hardware communication mechanisms.                                                                                                                                       |            |

|                                   | Characteristics of the selected TSV technology [23]                                                                                                                                                         |            |

| 2.4                               | Metrics about the physical implementation of OpenRISC processor as a 3-D chip.                                                                                                                              | 40         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5   | Thermal characteristics of the employed processors                                                                                                                                                          | 92<br>94   |

|                                   | tions                                                                                                                                                                                                       | 118        |

| 4.1<br>4.2<br>4.3<br>4.4          | Overview of existing parallel placements.  Parameters of the proposed GA.  Feature characterization of the employed benchmark suite.  Evaluation of different (wirelength-driven and timing-driven) config- | 138<br>146 |

| 4.5                               | urations for the GA placer against the introduced GENESIS framework<br>Comparison in term of execution run-time, maximum operating fre-                                                                     | .148       |

|                                   | quency and power consumption                                                                                                                                                                                | 153        |

| 5.1                               | Exemplary scenario of the code patterns triggering code transformations, using DMM-HLS API.                                                                                                                 | 175        |

| <ul><li>5.2</li><li>5.3</li></ul> | Applications Characterization                                                                                                                                                                               | 175        |

| 5.4                               | Real-word representative comparison between HLSMapReduceFlow-                                                                                                                                               |            |

|                                   | accelerated FPGA and commodity workstation.                                                                                                                                                                 | 193        |

### Nomenclature

### **Roman Symbols**

| 3 <i>SLOG</i> | three (3) Step LOGarithmic search           |

|---------------|---------------------------------------------|

| ADPCM         | Adaptive Differential Pulse-Code Modulation |

| AHB           | Advanced High-performance Bus               |

| AMBA          | Advanced Micro-controller Bus Architecture  |

| APB           | Advanced Peripheral Bus                     |

| API           | Application Programming Interface           |

| ASIC          | Application Specific Integrated Circuit     |

| BLE           | Basic Logic Element                         |

| CAD           | Computer Aided Design                       |

| CLB           | Configurable Logic Block                    |

| CPS           | Cyber Physical Systems                      |

| CRC           | Cyclic Redundancy Check                     |

| CV            | Computer Vision                             |

| DMA           | Direct Memory Access                        |

| DMM           | Dynamic Memory Management                   |

| DSP           | Digital Signal Processor                    |

| DSU           | Debug Support Unit                          |

| DUT           | Design Under Test                           |

| DVFS          | Dynamic Voltage and Frequency Scaling       |

| ECO           | Engineering change orders                   |

| ECU           | Engine Control Unit                         |

| EDA           | Electronic Design Automation                |

| FSI           | Flectronic System Level                     |

xxiv Nomenclature

| ESoC        | Ecosystem-on-a-chip                                 |

|-------------|-----------------------------------------------------|

| FFT         | Fast Fourier Transform                              |

| FIFO        | First-In, First-Out                                 |

| FS          | Full Search                                         |

| FSB         | Front-Side Bus                                      |

| FSM         | Finite-State Machine                                |

| HDL         | Hardware Description Language                       |

| НРС         | High Performance Computing                          |

| HPWL        | Half-perimeter Wirelength                           |

| HS          | Hierarchical Search                                 |

| НТ          | HyperTransport                                      |

| I C         | Integrated Circuit                                  |

| IDW         | Inverse Distance Weighting                          |

| IP          | Intellectual Property                               |

| IPC         | Inter-Process Communication                         |

| ISA         | Instruction Set Architecture                        |

| ISS         | Instruction Set Simulator                           |

| ITRS        | International Technology Roadmap for Semiconductors |

| LAB         | Logic Array Block                                   |

| LUT         | Look-up Table                                       |

| MTTF        | Mean Time To Failure                                |

| MTU         | Maximum Transmission Unit                           |

| NASA        | National Aeronautics and Space Administration       |

| NIC         | Network Interface Controller                        |

| NUCA        | Non-Uniform Cache Architecture                      |

| PHODS       | Parallel Hierarchical One-Dimensional Search        |

| POSIX       | Portable Operating System Interface for Unix        |

| $O \circ R$ | Quality of Results                                  |

| QPI    | Intel QuickPath Interconnect          |

|--------|---------------------------------------|

| ROS    | Robotic Operating System              |

| RTL    | Register-Transfer Level               |

| RTS    | Run-Time Situation                    |

| SDR    | Software Defined Radio                |

| SiP    | System-in-package                     |

| SLAM   | Simultaneous Localization And Mapping |

| SNR    | Signal-to-Noise Ratio                 |

| SoC    | System-on-chip                        |

| SPEF   | Standard Parasitic Exchange Format    |

| SS     | Spiral Search                         |

| SURF   | Speeded Up Robust Features            |

| T - VP | ACK Timing-Driven Versatile Packing   |

| TDDB   | Time-Depended Dielectric Breakdown    |

| TDP    | Thermal Design Power                  |

| TSV    | Through Silicon Via                   |

| VCD    | Value Change Dump                     |

| VPR    | Versatile Placement and Routing       |

### Introduction

### 1.1. Thesis Research Background

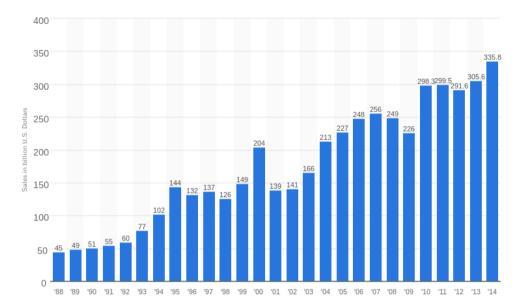

Integrated circuits (IC) are the cornerstone of developments in both the interscientific community and the daily life of modern man. The impact of these developments are so strong, that the technological transitions over time are taken for granted. Consumers have come to expect more and more sophisticated electronic products, while the business world expects increased productivity through improved technology information systems. At the same time, approaching the macro scale of this trend, it seems that the maturity of the semiconductor industry is the catalyst productivity and growth in almost all sectors of economic activity, which already marks a market of about 3 trillion dollars [1], as depicted in Figure 5.19.

According to predictions [2], this impressive market promises to connect 2.67 billion machines to the Internet till the end of 2017 (from 1.11 today), exclusively as far as the upcoming "smart cities" are concerned, and 25 billion machines totally as far as the society, culture and finance are concerned till the end of 2020 (today 4,8). It is clear that these loud numbers are fueled by the scalability assurance of semiconductor technology regarding the market needs.

The last 50 years of - nearly linear - increase of the computational power and the corresponding decrease of the power consumption, support this belief. Nevertheless this linearity has been supplied by the association of two technological disciplines: Moore's law [3] and Dennard's law [4]. The first one which is valid till today <sup>1</sup>, promises the doubling of the number of the elementary resources (for example transistors) which constitute a whole system in every 18 months. Practically, this law allows the increase of the computational power in each generation of technological completion. The second law, which expired in 2007, described the dimensions and the electrical characteristics of a transistor so that the sequential shrinkage of them to be possible, so as to improve at the same time the density

<sup>&</sup>lt;sup>1</sup>since the interpretation of Moore's law is not unique, there is evidence that this law will not be valid soon or has been already invalid [5, 6].

Figure 1.1 Worldwide semiconductor sales 1988-2014 (in billions dollars). Source: World Semiconductor Trade Statistics, [1].

of the silicon area, the processing frequency and the power performance. Practically, this law allowed the power consumption to be stable in each transition of new generation of completion during which the number of transistors was doubled. Also, due to the technology progress this law foresaw increase of the processing frequency till 40%. [7].

The combination of these two laws, allowed for almost four decades the increase of the supply voltage and the threshold voltage as much as the scale integration of the size of transistors. In that way the designers were allowed to decrease the supply power per transistor, so that the power density (power consumption per silicon area) remained almost stable, scaling from one technological node to another.

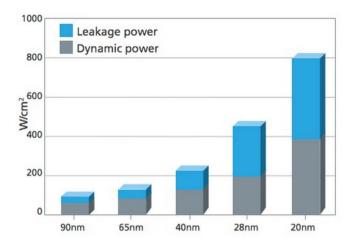

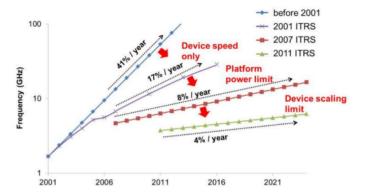

Nevertheless, on nodes of several nanometers (deep sub-micron technology nodes), the decrease of the threshold voltage leads to an exponential increase of the leakage power. Figure 5.17 illustrates the scaling of static and dynamic power consumption of integrated circuits, with respect to the technology node. As shown, given a set of typical integrated circuits designs, the dynamic energy consumption in the technological node of 20 nm has almost surpassed the corresponding static. In this way, the threshold voltage is no longer scalable and as a result the supply voltage cannot be scaled further without affecting the performance. This decrease in performance is illustrated in Figure 5.20. In particular, this figure shows the forecasts of ITRS organization for the scaling of the maximum operating frequency at regular chronological studies. As shown, the projections of each new study is pessimistic regarding the scaling of processing frequency, indicating an expected

Figure 1.2 Scaling of static and dynamic power consumption of integrated circuits regarding to the technology node. Source: Mentor Graphics 2014.

increase of 41%/year in 2001, which dropped to a 4% in 2011.

As a result, although more transistors can be manufactured per silicon area, the supply power per transistor doesn't scale in analogy and as a result the power density increases. This phenomenon becomes more intense in conjunction with the natural limits imposed by the package materials and the cooling technology for the maximum power and the maximum power density. This description highlights the introduction of the "Dark Silicon" era [7-10].

Another limitation of the modern semiconductor industry refers to the economic cost of manufacturing integrated circuits. Modern lithography design methods demanded continuous innovative solutions for each new technology node (high-k, Metal Gate, Strain, SiGe, Tri-gate, etc.), while is is expected that new nodes shall require respective research and implementing innovations, increasing manufacturing costs [11]. Apart from the research community, also a lot of companies of the semiconductor industry have recognized this problem, e.g. Nvidia Inc. [12]. Figure 3.7 shows the typical manufacturing cost per gate for recent technology nodes. As shown, in the past (90 nm, 65 nm, 45 nm, 28 nm), the cost per gate at each node increases. At the same time, the number of gates per wafer increases. This contrast was almost linearly bijective, thus the average cost per wafer remained stable. However the technology node of 20 nm appears to increase the cost over previous technology generations. It is expected that the manufacturing of integrated circuits in newer nodes is disadvantageous compared to existing ones, or even earlier. The three-dimensional integration technology (3-D) and heterogeneity have been identified as promising solutions to the problem of scaling manufacturing costs [13].

The research community has already proposed a remarkable set of alternative approaches for the problem above, such as the heterogeneous multi-processing architectures [14–19], the approximate computing [20–26] and the energy man-

Figure 1.3 Projections of the ITRS organization for the scaling of the maximum operating frequency at regular chronological studies.

agement for architectures of "Dark" and "Dim" Silicon [27–33]. Given the recent published results, it seems that the most effective approach is the creation of heterogeneous and specific purpose accelerators which increase the computational power per energy consumption and silicon area. In that direction, through this work, four basic constraints are identified as major limiters of building the aforementioned architectures: a) the programming problem, b) the problem of software/hardware partitioning, c) the problem of cost/time design and d) the problem of finding adequate CAD tools of optimal design. Identifying these constraints, this thesis proposes architecture templates and design frameworks for the "Dark Silicon" era.

### 1.2. Dissertation Overview

The above introductory field emerges the need for methods, tools and architectures which provide viability during the continuous scaling of technology and energy. The background design of computer systems in recent years has shown that scaling in energy and technology can be achieved with the customization of the architecture and the materials/manufacturing technology, respectively.

Figure 5.12 depicts different architectural designs approaches, with respect to their energy efficiency. It is obvious that the specialized architectures can lead to increased CPU power per energy unit (MOPS/mW) by a factor of  $100\times$ , compared to conventional general purpose processors. Also, it is stressed that FPGAs devices are a flexible platform of energy efficiency, according to their programming. However, the transition to specialized and/or reconfigurable architectures corresponds to increased difficulty in design and programming of appropriate software.

Figure 3.9 shows the performance growth rate introduced by conventional technology scaling and architectural/materials innovation for every technology node. As shown, the performance improvement of recent technology nodes is attributed, with a small percentage, to the conventional technology scaling. However, the highest profit is attributed to innovative techniques of architecture improvements

Figure 1.4 Scaling manufacturing costs per gate for different technology nodes of integration. Source: IBS 2012

#### and manufacturing materials.

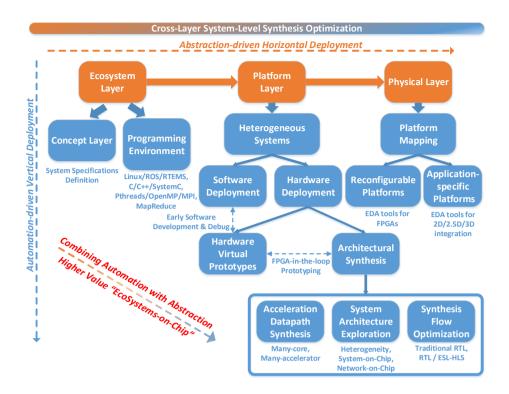

This thesis is positioned towards the direction of the two aforementioned motivations, a holistic methodology framework of which is presented in Fig 5.14. It aims to capture a new idea, evolved in the base of a new product/hardware/software service. The starting point of the developed methodological components is the conceptual level, meaning that stage that captures the desired characteristics of a new product or service of a computer system. Continues with the mapping of the desired specifications of a developed product as well as the functional constraints. An important stage in this level is the organization of the tasks. Lately a large number of specific managing works tools has been developed in the frames of a software/hardware work, which depending on the complexity, can manage different phases of the production procedure like the estimation and design, the programming, the cost control, the budget management, the allocation of resources, the communication of colleagues, the decision making, the quality management and the organization of management and technical paperwork ( $\pi.\chi$ . [34, 35]).

Having prescribe the required operating characteristics, the development team is asked to standardize the operating environment in which the under-development product will be operational. This level (Programming Environment) is the result of a new approach of the production process and it is responsible for the specification of all those environmental factors with which the developed product shall interact. The Concept Level with the Programming Environment constitute the Ecosystem Level which through early detection of the aforementioned characteristics of the final system, ensures adaptation of the design flow to the new trends of the market, where most growth is driven by the market itself and not necessarily from

Figure 1.5 Comparison of different architectural designs approaches, with respect to their energy efficiency. Source: Bob Broderson, Berkeley Wireless group, ISSCC proceedings, Microsoft, 2011.

#### technological developments [36].

The next level is established by the design of the reference platform (Platform Level), which forms the representations of operating characteristics to the actual system. This stage starts by partitioning hardware/software based on a analysis process (profiling) that constitute the inherent characteristics of the application and based on the retrieved results, classifies the total operating tasks for execution with either software or dedicated hardware accelerating modules. The hardware/software co-design procedure is enriched with the proposed rapid prototyping technique, i.e. a process that ensures faster product development as it allows the development of software throughout the development of the hardware, making use of virtual hardware modules that simulate the specialized hardware. Compared to existing prototyping solutions, the proposed methodology is superior with respect to speed, accuracy and debugged design completion, since it introduces FPGAs devices in the process of simulation. This action allows part of the hardware developed in tandem with the software, being directly tested on original hardware (FPGA) in the early design stages, where the final system is not complete.

The hardware development takes place at the stage of architectural design. This step is orthogonal independent to the virtual prototyping phase, since the subsystems that are gradually synthesized, they can be used in virtual prototyping replacing their virtual versions. Thereby, the process of simulation is accelerated and the overall systems is evaluated with greater accuracy. The stage of architectural synthesis is decomposed onto three distinct methodological analysis, the Acceleration Datapath Synthesis, the System Architecture Exploration and the Synthesis Flow Optimization. Each of these steps addresses different problems of modern design of integrated circuits for both reconfigurable (FPGAs) and application-specific (ASICs) platforms. Specifically, the Acceleration Datapath Synthesis includes the accelera-

Figure 1.6 Performance growth rate of conventional technology scaling and architecture/materials innovation for each technology node. Source: IBM Microelectronics, Intel IC Insights, 2012.

tion of computational intensive tasks of the system. We propose the use of multiple coarse-grained accelerators, as they offer higher productivity per power consumption ratio and therefore, they form an attractive solution to the "Dark Silicon" problem [37, 38]. System Architecture Exploration refers to the investigation of the appropriate interconnection scheme of the under-development integrated system. This thesis studies heterogeneous architectural templates based on System-on-Chip (SoC) and Network-on-Chip (NoC) topologies. The last stage of the architectural synthesis refers to the optimization of the synthesis flow. This procedure provides the introduction of new design techniques, utilizing abstraction design methods of high-level synthesis (HLS), which further accelerate the development flow. At the same time this step allows programming flexibility in the programming of heterogeneous many-accelerator systems. Moreover, at this stage it is proposed a fast and automated way of design space exploration of architectural solutions that combine HLS and virtual prototyping techniques in order to find a set of optimal solutions (Pareto optimal) under a multi-objective analysis environment.

The last step (Physical Layer) of the holistic proposed methodological framework refers to the physical mapping of the developed modules, through previous procedures, in real implementation platforms. The proposed procedures allow the placement of designs either to reconfigurable or application-specific platforms, depending on the desired characteristics which are reflected in the ecosystem layer, but

Figure 1.7 Dissertation overview.

also according to the constraints posed by the respective market. Specifically, the FPGA design flow is enriched through the proposed placement algorithms. These algorithms employ techniques of natural selection and evolutionary theory, providing optimal design solutions with reference to the maximum achieved operating frequency, wire-length, silicon area and power consumption. Such exploration is enabled through vertical and horizontal parallelization of the proposed algorithms and their multi-objective optimization mechanisms. At the same time, the mapping to application-specific platforms (ASICs) is enriched. By varying the microarchitecture, the proposed techniques achieve a reduction of emitted temperature and therefore they reduce the aging rate of the circuit, leading to increased reliability. Furthermore, we study the gains from the transition to the new promising three-dimensional integration technology (3-D), for which, to date, there is a lack of design tools, both academic and industrial. To this regard, it is suggested a novel design flow based on reliable conventional design tools (2-D) which manage to quantify the implementation gains from the transition to three-dimensional integration. The developed software tools are compatible with the file types of industrial standards, so they offer great flexibility in their adoption of alternative design flows and tools from different industrial vendors.

Overall, this thesis provides methodologies and tools at different design levels of integrated hardware/software systems bring-up. Through a structured design flow, it is attempted a coherent interaction of individual design flows, in order to establish a correlation of the characteristics sought by the market and those that can be offered by the technology. Basic characteristic of this effort is the clear conceptual separation of design levels, as well as the definition of specific and non-overlapping optimization mechanisms. The complete contribution to the proposed design flow targets design systems that can be deployed through a rapid, multi-objective optimized environment, incorporating largely systemic complexity. This degree of integration contributes to the emergence of a new generation of integrated systems which, in the context of this thesis, are assigned the term "Ecosystem-on-Chip" (ESoC).

### 1.2.1. Chapters Organization

The proposed framework and the corresponding design tools, which are developed in the research directions of this study, are organized according to the following structure:

- Chapter 1, i.e. the current chapter, presents the latest technology developments and trends of the dynamically evolving market of IT systems. Along-side, there are analyzed the limitations of existing design methods for systems that offer long term sustainability in the mentioned technological scaling and marketing trends. This chapter summarizes the key growth drivers of the thesis, through the presentation of a holistic methodological framework, which prioritises the individual contributions into discrete levels and describes the binding relationships among them.

- Chapter 2 presents the proposed methodology of rapid prototyping. It introduces the concept of virtual prototyping using the "FPGA-in-the-loop" technique, which speeds up the simulation process and enables the effective exploration of the solutions space during architecture optimization.

- Chapter 3 presents the cross-layer synthesis of heterogeneous architectures.

Referring to the holistic methodology of the thesis (Figure 5.14), the chapter contains the Acceleration Datapath Synthesis, the System Architecture Exploration and the Synthesis Flow Optimization.

- Chapter 4, presents the proposed design tools for reconfigurable platforms. It

introduces the characterization and classification technique, used during the

phase of the synthesis, according to application's intrinsic characteristics. Also

it is presented a multi-objective genetic algorithm for the placement problem, which utilizes the aforementioned characterization technique to guide

the placement to Pareto optimal points depending on the classification of the

application.

- Chapter 5, provides the architectural template and the programming environment for many-accelerator platforms. The proposed architecture promises

1. Introduction

1

high accelerator density with minimal energy footprint. It utilizing FPGAs as a medium of programming coarse-grained accelerators. The incorporation of high-level-synthesis techniques allows the easy programming and the system-level deployment of such mass-parallelism architectures.

• Chapter 6, concludes the findings of this study and highlights the future extensions arising from the use of the proposed methodologies.

#### References

- [1] Statista, Statista statistics portal, global semiconductor sales from october 2011 to february 2015 (in billion u.s. dollars), .

- [2] Gartner, Gartner inc. technology research, .

- [3] G. Moore, Cramming more components onto integrated circuits, Proceedings of the IEEE **86**, 82 (1998).

- [4] R. Dennard, F. Gaensslen, H.-N. YU, V. Rideout, E. BASSOUS, and A. R. LEBLANC, *Design of ion-implanted mosfet's with very small physical dimensions*, Proceedings of the IEEE **87**, 668 (1999).

- [5] CNET.com, End of moore's law: It's not just about physics, .

- [6] Recode.net, Moore's law hits 50, but it may not see 60, .

- [7] H. Esmaeilzadeh, E. Blem, R. S. Amant, K. Sankaralingam, and D. Burger, *Power challenges may end the multicore era*, Commun. ACM **56**, 93 (2013).

- [8] M. Shafique, S. Garg, J. Henkel, and D. Marculescu, The eda challenges in the dark silicon era: Temperature, reliability, and variability perspectives, in Proceedings of the 51st Annual Design Automation Conference, DAC '14 (ACM, New York, NY, USA, 2014) pp. 185:1–185:6.

- [9] C. Mack, Fifty years of moore's law, Semiconductor Manufacturing, IEEE Transactions on 24, 202 (2011).

- [10] M. Taylor, *Is dark silicon useful? harnessing the four horsemen of the coming dark silicon apocalypse,* in *Design Automation Conference (DAC), 2012 49th ACM/EDAC/IEEE* (2012) pp. 1131–1136.

- [11] A. Mallik, J. Ryckaert, A. Mercha, D. Verkest, K. Ronse, and A. Thean, *Maintaining moore's law: enabling cost-friendly dimensional scaling,* (2015) pp. 94221N–94221N–12.

- [12] J. Hruska, Nvidia deeply unhappy with tsmc, claims 20nm essentially worthless, .

- [13] M. D. I. Zvi Or-Bach, Is the cost reduction associated with ic scaling over? .

- [14] J. Cong, M. Ghodrat, M. Gill, B. Grigorian, and G. Reinman, *Architecture* support for accelerator-rich cmps, in *Design Automation Conference (DAC)*, 2012 49th ACM/EDAC/IEEE (2012) pp. 843–849.

- [15] J. Cong and B. Xiao, Optimization of interconnects between accelerators and shared memories in dark silicon, in Computer-Aided Design (ICCAD), 2013 IEEE/ACM International Conference on (2013) pp. 630–637.

- [16] N. Goulding-Hotta, J. Sampson, G. Venkatesh, S. Garcia, J. Auricchio, P. Huang, M. Arora, S. Nath, V. Bhatt, J. Babb, S. Swanson, and M. Taylor, *The greendroid mobile application processor: An architecture for silicon's dark future*, Micro, IEEE **31**, 86 (2011).

- [17] Y. Turakhia, B. Raghunathan, S. Garg, and D. Marculescu, *Hades: Architectural synthesis for heterogeneous dark silicon chip multi-processors*, in *Design Automation Conference (DAC)*, 2013 50th ACM / EDAC / IEEE (2013) pp. 1–7.

- [18] G. Venkatesh, J. Sampson, N. Goulding-Hotta, S. K. Venkata, M. B. Taylor, and S. Swanson, *Qscores: Trading dark silicon for scalable energy efficiency with quasi-specific cores*, in *Proceedings of the 44th Annual IEEE/ACM International Symposium on Microarchitecture*, MICRO-44 (ACM, New York, NY, USA, 2011) pp. 163–174.

- [19] M. J. Lyons, M. Hempstead, G.-Y. Wei, and D. Brooks, *The accelerator store: A shared memory framework for accelerator-based systems*, ACM Trans. Archit. Code Optim. **8**, 48:1 (2012).

- [20] M. R. Choudhury and K. Mohanram, Approximate logic circuits for low over-head, non-intrusive concurrent error detection, in Proceedings of the Conference on Design, Automation and Test in Europe, DATE '08 (ACM, New York, NY, USA, 2008) pp. 903–908.

- [21] V. Gupta, D. Mohapatra, S. P. Park, A. Raghunathan, and K. Roy, Impact: Imprecise adders for low-power approximate computing, in Proceedings of the 17th IEEE/ACM International Symposium on Low-power Electronics and Design, ISLPED '11 (IEEE Press, Piscataway, NJ, USA, 2011) pp. 409–414.

- [22] J. Han and M. Orshansky, *Approximate computing: An emerging paradigm for energy-efficient design,* in *Test Symposium (ETS), 2013 18th IEEE European* (2013) pp. 1–6.

- [23] P. Kulkarni, P. Gupta, and M. Ercegovac, *Trading accuracy for power with an underdesigned multiplier architecture*, in *VLSI Design (VLSI Design)*, *2011 24th International Conference on* (2011) pp. 346–351.

- [24] D. Mohapatra, V. Chippa, A. Raghunathan, and K. Roy, *Design of voltage-scalable meta-functions for approximate computing*, in *Design, Automation Test in Europe Conference Exhibition (DATE)*, 2011 (2011) pp. 1–6.

- [25] A. Verma, P. Brisk, and P. Ienne, *Variable latency speculative addition: A new paradigm for arithmetic circuit design,* in *Design, Automation and Test in Europe, 2008. DATE '08* (2008) pp. 1250–1255.

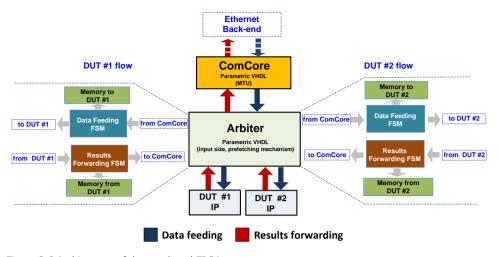

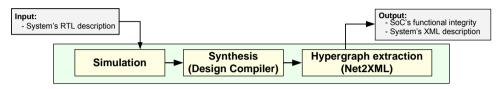

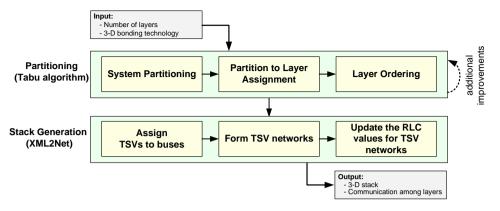

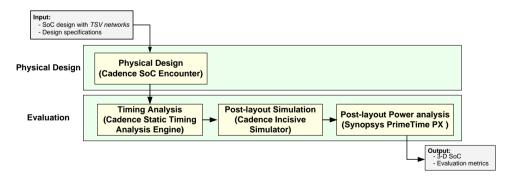

- [26] H. Esmaeilzadeh, A. Sampson, L. Ceze, and D. Burger, Architecture support for disciplined approximate programming, in ACM SIGPLAN Notices, Vol. 47 (ACM, 2012) pp. 301–312.