NATIONAL TECHNICAL UNIVERSITY OF ATHENS SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

Computer Science Division Computing Systems Laboratory

# LCN : Design and Implementation of a contention-aware Scheduler for Multiprocessing Systems

DIPLOMA THESIS

# **RAPTIS DIMOS - DIMITRIOS**

Supervisor : Nectarios Koziris Professor NTUA

Athens, February 2015

NATIONAL TECHNICAL UNIVERSITY OF ATHENS SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

Computer Science Division Computing Systems Laboratory

# LCN : Design and Implementation of a contention-aware Scheduler for Multiprocessing Systems

# DIPLOMA THESIS

# **RAPTIS DIMOS - DIMITRIOS**

Supervisor : Nectarios Koziris Professor NTUA

Approved by the examining committee on the 13th of February 2015.

Nectarios Koziris Professor NTUA Panayiotis Tsanakas Professor NTUA Georgios Goumas Lecturer NTUA

Athens, February 2015

**Raptis Dimos - Dimitrios** Electrical and Computer Engineer

Copyright © Raptis Dimos - Dimitrios, 2015. All rights reserved.

This work is copyright and may not be reproduced, stored nor distributed in whole or in part for commercial purposes. Permission is hereby granted to reproduce, store and distribute this work for non-propfit, educational and research purposes, provided that the source is acknowledged and the present copyright message is retained. Enquiries regarding use for profit should be directed to the author.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of the National Technical University of Athens.

## Abstract

The purpose of this diploma dissertation is the design and implementation of a scheduler that will be capable on one hand to detect the resource contention between different processes in a computing system, and on the other hand to schedule applications in order to alleviate this contention as much as possible, so as to improve the overall throughput of the computing system. The scheduler that has been implemented is compared to other state of the art contention-aware schedulers proposed by previous research, as well as with the scheduler used in modern Operating Systems, such as Linux.

Nowadays, the need for improvement in the software of modern Operating Systems is even more pressing than it was in the past, so that Operating Systems will become capable to leverage the continuous progress that is rapid in the field of hardware and computer architecture. During the last years, the use of Parallel Processing and Multithreaded Programming has become increasingly dominant. Parallel Processing allows scientists to distribute mathematical complex procedures to different resources of the system, in order to be able to complete calculations that would otherwise be lengthy and even impossible to execute. Respectively, Multithreaded Programming allows Software Engineers to create applications, that present significant scalability, but also satisfactory responsiveness.

There has also been an attempt, so that Operating Systems can follow this trend to be capable to manage system resources suitably, distributing them in different processes, without creating contention. In this way, they will be able to increase the overall performance of the computing system and in the meanwhile impose fairness among the different processes, so that they benefit in the same degree. In order to reach this target, the schedulers of the modern operating systems have to be improved, so as to manage to estimate the interference between different processes in the contention of the system resources.

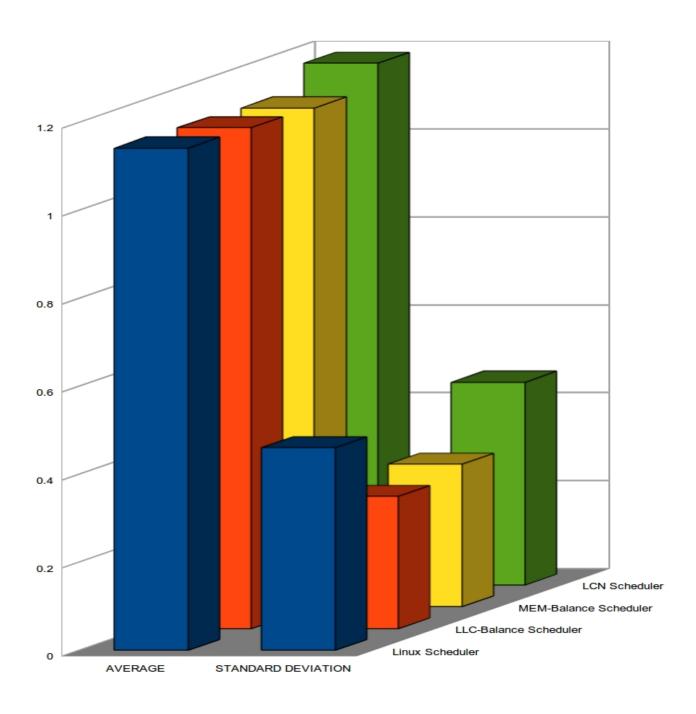

The comparison between this scheduler and the rest has been based on 2 criteria, the overall performance of the computing system and the fairness between different processes. We achieved to implement a scheduler, that presents significant improvement in overall performance and equal fairness, compared with the current scheduler of Linux. After comparing with the other schedulers that have been proposed by previous research, this one presents the optimum overall performance, but not the best fairness.

### Key words

Operating Systems, Contention, Aware, Scheduler, Multicore Systems, Resource Management, Parallel Processing, Computer Architecture

# Περίληψη

Σκοπός της παρούσας εργασίας είναι η σχεδίαση και υλοποίηση ενός χρονοδρομολογητή που να μπορεί αφενός να εντοπίζει τον ανταγωνισμό μεταξύ διαφορετικών διεργασιών στους πόρους των υπολογιστικών συστημάτων και αφετέρου να δρομολογεί εφαρμογές, ώστε να μειώνει κατά τον βέλτιστο βαθμό αυτόν τον ανταγωνισμό, προκειμένου να βελτιώσει την συνολική επίδοση του συστήματος. Ο χρονοδρομολόγητης που υλοποιήθηκε συγκρίνεται με άλλους χρονοδρομολογητές επίγνωσης ανταγωνισμού προτεινόμενους από την πιο πρόσφατη ερευνητική βιβλιογραφία, καθώς και με τον χρονοδρομολογητή που χρησιμοποιείται σε σύγχρονα Λειτουργικά Συστήματα, όπως το Linux.

Στη σημερινή εποχή, καθίσταται επιτακτική η ανάγκη βελτίωσης του λειτουργικού μέρους των σύγχρονων υπολογιστικών συστημάτων, προκειμένου να είναι ικανά να εκμεταλλευτούν την συνεχή πρόοδο που παρουσιάζεται στον τομέα του υλικού και της αρχιτεκτονικής των υπολογιστών. Τα τελευταία χρόνια, γίνεται όλο και πιο διαδεδομένη η έννοια του Παράλληλου και του Πολυνηματικού Προγραμματισμού. Ο Παράλληλος Προγραμματισμός επιτρέπει στους επιστήμονες να επιμερίζουν μαθηματικές πολύπλοκες διαδικασίες στους διαφορετικούς πόρους του συστήματους, προκειμένου να έχουν την δυνατότητα να ολοκληρώνουν υπολογισμούς που διαφορετικά θα ήταν ιδιαίτερα χρονοβόροι εώς και αδύνατοι. Αντίστοιχα, ο Πολυνηματικός Προγραμματισμός επιτρέπει στους μηχανικούς Λογισμικού να δημιουργούν εφαρμογές, οι οποίες παρουσιάζουν σημαντική κλιμακωσιμότητα, αλλά και ικανοποιητική αποκρισιμότητα.

Αντίστοιχα, γίνεται προσπάθεια τα υπολογιστικά συστήματα να ακολουθήσουν αυτή την τάση, προκειμένου να είναι ικανά να διαχειρίζονται τους πόρους του συστήματος κατάλληλα, κατανέμοντας τους στις διάφορες διεργασίες, χωρίς να δημιουργείται συμφόρηση. Με αυτό τον τρόπο, θα μπορούν να βελτιώσουν την συνολική απόδοση του υπολογιστικού συστήματος, αλλά και να επιβάλλουν δικαιοσύνη ανάμεσα στις διάφορες διεργασίες, προκειμένου να έχουν όλες τα ίδια οφέλη. Για να επιτευχθεί αυτός ο στόχος, οι χρονοδρομολογητές των σύγχρονων λειτουργικών συστημάτων πρέπει να βελτιωθούν, προκειμένου να είναι ικανοί να εκτιμήσουν την επίδραση μεταξύ διαφορετικών διεργασιών στην συμφόρηση των πόρων του συστήματος.

Η σύγκριση που έγινε μεταξύ του παρόντους χρονοδρομοολογητή και των υπολοίπων βασίστηκε σε 2 κριτήρια, την συνολική απόδοση του συστήματος και την δικαιοσύνη μεταξύ των διαφορετικών διεργασιών. Επιτύχαμε να σχεδιάσουμε έναν χρονοδρομολόγητη, ο οποίος παρουσιάζει σημαντική βελτίωση στην συνολική απόδοση του συστήματος και ισάξια δικαιοσύνη, συγκρινόμενος με τον τρέχοντα χρονοδρομολογητή του λειτουργικού συστήματος Linux. Σε σύγκριση με τους καλύτερους χρονοδρομολογητές που έχουν προταθεί από προηγούμενη έρευνα, ο προτεινόμενος παρουσιάζει την καλύτερη συνολική απόδοση συστήματος, αλλά όχι βελτιωμένη δικαιοσύνη.

### Λέξεις κλειδιά

Λειτουργικά Συστήματα, Ανταγωνισμός Πόρων, Χρονοδρομολογητής, Πολυπήρηνα Συστήματα, Παράλληλη Επεξεργασία, Αρχιτεκτονική Υπολογιστών

# Acknowledgements

The completion of this diploma thesis is without doubt the capping stone of a 5-year progress as an undergraduate student in National Technical University of Athens. During those 5 years, I was continuously evolving as an Engineer through facing challenging problems. The project of my thesis was the hardest of all those challenges and the one that urged me to revise my way of thinking.

This thesis was completed under the supervision of Professor Nectarios Koziris. I would like to thank him for introducing me to the field of Computing Systems through the various undergraduate courses and also for his supervision during the completion of this diploma thesis. I also want to thank Georgios I. Goumas for his valuable guidance towards a scientifically justified approach regarding the subject of this diploma thesis. Furthermore, I also want to thank Alexandros Haritatos for his substantial contribution to a deeper focus on more specialised sections of my thesis, as well as for his support in the resolution of problems that arised during its completion. Finally, I would like to thank my family and especially my parents, who continuously supported me not only during my diploma thesis but in the whole duration of my undergraduate studies.

> Raptis Dimos - Dimitrios, Athens, 13th of February 2015

# Contents

| Ab  | ostrac                  | t                                     |  |  |  |  |  |

|-----|-------------------------|---------------------------------------|--|--|--|--|--|

| П   | Περίληψη                |                                       |  |  |  |  |  |

| Ac  | Acknowledgements        |                                       |  |  |  |  |  |

| Ta  | Table of Contents    11 |                                       |  |  |  |  |  |

| Lis | List of Tables          |                                       |  |  |  |  |  |

| Lis | st of F                 | <b>`igures</b>                        |  |  |  |  |  |

| 1.  | Intro                   | oduction                              |  |  |  |  |  |

|     | 1.1                     | Thesis Motivation                     |  |  |  |  |  |

|     | 1.2                     | Thesis Structure                      |  |  |  |  |  |

| 2.  | Theo                    | pretical Background                   |  |  |  |  |  |

|     | 2.1                     | Hardware Technology Evolution         |  |  |  |  |  |

|     |                         | 2.1.1 Processing Power Progress       |  |  |  |  |  |

|     |                         | 2.1.2 Memory Speed Progress           |  |  |  |  |  |

|     | 2.2 Parallel Computing  |                                       |  |  |  |  |  |

|     |                         | 2.2.1 Taxonomy                        |  |  |  |  |  |

|     |                         | 2.2.2 MESI Protocol                   |  |  |  |  |  |

|     |                         | 2.2.3 Challenges in Multicore Systems |  |  |  |  |  |

|     | 2.3                     | Scheduling                            |  |  |  |  |  |

|     |                         | 2.3.1 Operating Systems Scheduling    |  |  |  |  |  |

|     |                         | 2.3.2 Major Scheduling disciplines    |  |  |  |  |  |

|     |                         | 2.3.3 Linux Scheduler - CFS           |  |  |  |  |  |

|     |                         | 2.3.4 Contention-Aware schedulers     |  |  |  |  |  |

|     | 2.4                     | Experimentation Environment           |  |  |  |  |  |

| 3.  | Class                   | sification Scheme                     |  |  |  |  |  |

|     | 3.1                     | Previous Research                     |  |  |  |  |  |

|     | 3.2                     | Application classes                   |  |  |  |  |  |

|     | 3.3                     | Decision Tree                         |  |  |  |  |  |

|     | 3.4                     | Evaluation and Validation    43       |  |  |  |  |  |

| 4.           | Pred | iction Model                         | 45 |  |  |

|--------------|------|--------------------------------------|----|--|--|

|              | 4.1  | Theoretical Foundation               | 45 |  |  |

|              | 4.2  | Linear Regression Model              | 46 |  |  |

|              | 4.3  | Evaluation and Validation            | 49 |  |  |

|              | 4.4  | Refinement                           | 55 |  |  |

| 5.           | Sche | duling                               | 59 |  |  |

|              | 5.1  | Algorithm                            | 59 |  |  |

|              | 5.2  | Comparison - Experimentation Results | 61 |  |  |

| 6.           | Cond | clusion                              | 69 |  |  |

|              | 6.1  | General Remarks                      | 69 |  |  |

|              | 6.2  | Future Work                          | 70 |  |  |

| Bibliography |      |                                      |    |  |  |

# **List of Tables**

| 2.1 | Sandy Bridge Architecture Details        | 33 |

|-----|------------------------------------------|----|

| 2.2 | Nehalem Architecture Details             | 33 |

| 2.3 | Intel Hardware Performance Counters used | 35 |

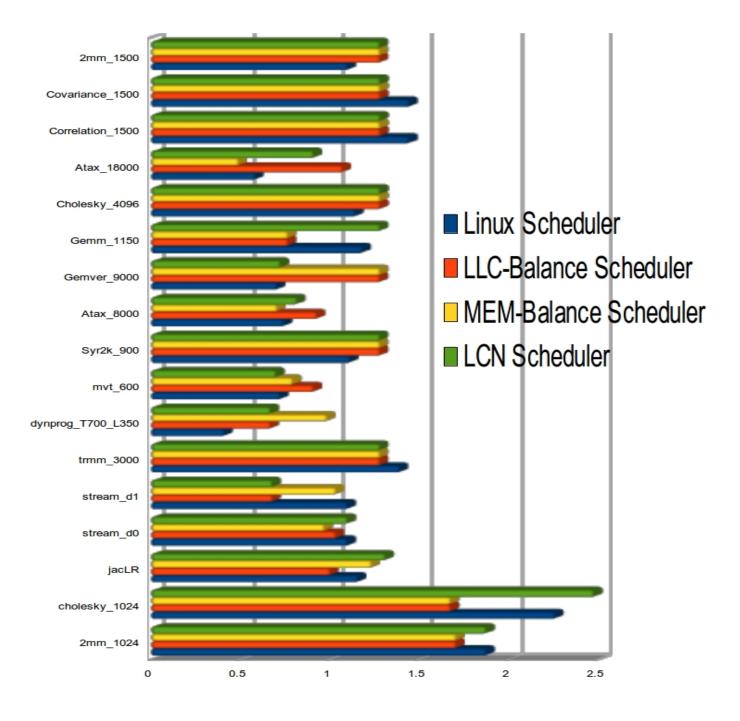

| 5.1 | Benchmarks Data Sets                     | 62 |

| 5.2 | Comparison between schedulers            | 64 |

# **List of Figures**

| 2.1 | Growth in processor performance since the mid-1980s. Copyright 2009<br>Elsevier. All Rights Reserved |

|-----|------------------------------------------------------------------------------------------------------|

| 2.2 | 6                                                                                                    |

| 2.2 | Graph of Clockspeed versus Power Consumption                                                         |

| 2.3 | Performance comparison between single-core and multicore systems 23                                  |

| 2.4 | Difference between processor performance progress and memory speed progress                          |

| 2.5 | Sandy Bridge architecture                                                                            |

| 3.1 | Class L applications                                                                                 |

| 3.2 | Class LC applications                                                                                |

| 3.3 | Class C applications                                                                                 |

| 3.4 | Class C+ applications 40                                                                             |

| 3.5 | Class N applications                                                                                 |

| 3.6 | Classification scheme                                                                                |

| 3.7 | Average slowdown between different classes    44                                                     |

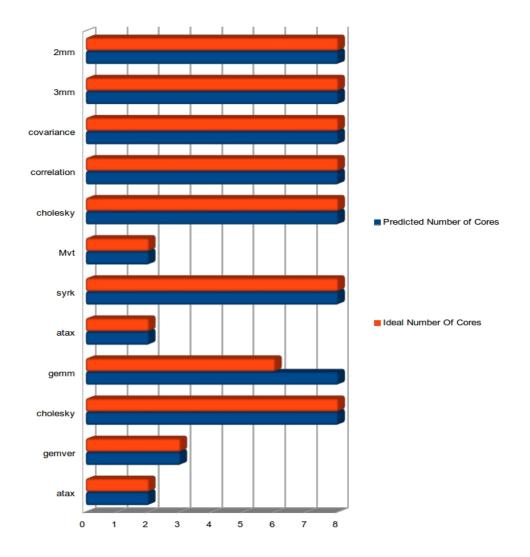

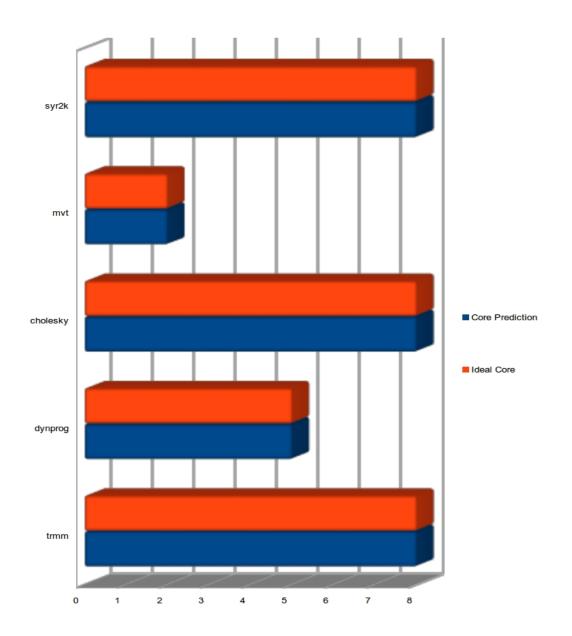

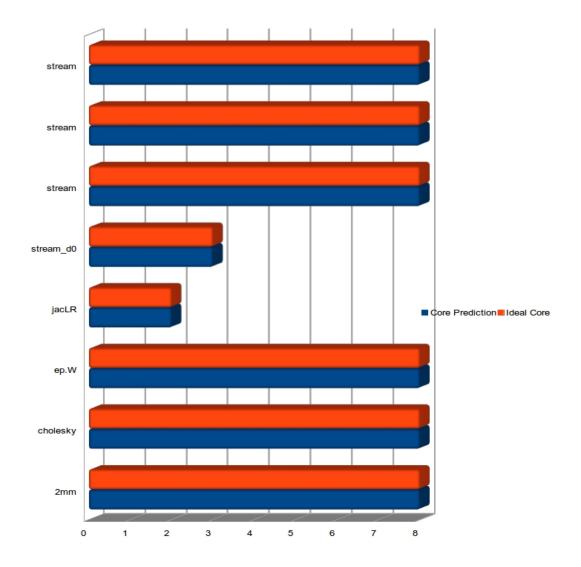

| 4.1 | Relative errors in predicted completion times for L,C,C+ applications 50                             |

| 4.2 | Deviation in predicted optimal number of cores for C applications 51                                 |

| 4.3 | Deviation in predicted optimal number of cores for LC applications 52                                |

| 4.4 | Deviation in predicted optimal number of cores for L and N applications . 53                         |

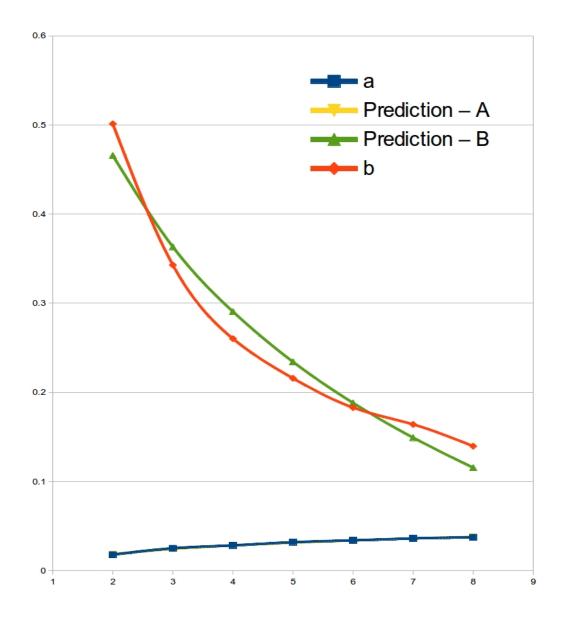

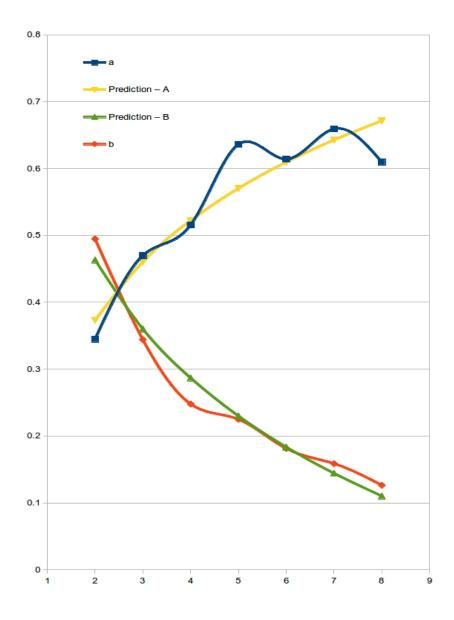

| 4.5 | Deviation for relationship $Completion(LC)_p = a * f_{LC} + b$ between initial                       |

|     | and refined-predicted model                                                                          |

| 4.6 | Deviation for relationship $Completion(C)_p = a * f_C + b$ between initial and                       |

|     | refined-predicted model 57                                                                           |

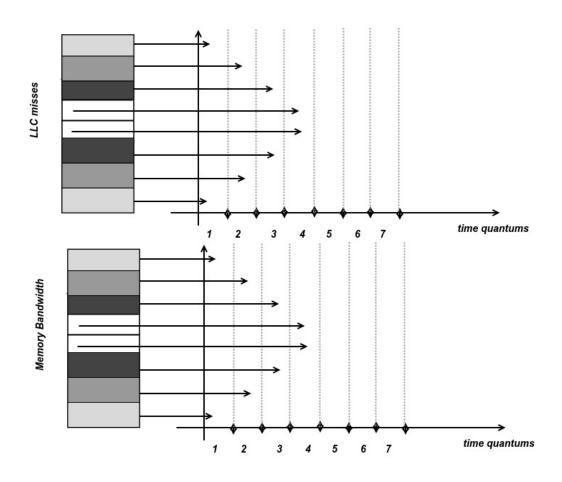

| 5.1 | LLC-MRB and LBB balancing schedulers                                                                 |

| 5.2 | Comparison of gains per application between 4 schedulers                                             |

| 5.3 | Comparison of average gain and standard deviation between 4 schedulers . 66                          |

## Chapter 1

## Introduction

When Linus Torvalds stated the following back in August 26 1991 :

"I'm doing a (free) operating system (just a hobby, won't be big and professional like gnu) for 386(486) AT clones."

he probably had no idea that 13 years later in 11th October of 2004, he would also state :

"I get the biggest enjoyment from the random and unexpected places. Linux on cellphones or refrigerators, just because it's so not what I envisioned it. Or on supercomputers."

Nowadays, Linux has extensively dominated the academic and industrial section, since its implementation alongside the continuous contributions by open-source developers has rendered this operating system superior to other mainstream operating systems. This is due to the fact that Linux components are constantly being improved and present higher performance compared to the corresponding components of other operating systems, like Windows. A main component that has a crucial impact on the performance of the applications and the responsiveness of the operating systems is the scheduler. As a result, this is one of the most focused components of Linux during the testing, maintenance and development by the open-source community. As Linus Torvalds has also stated :

"To kind of explain what Linux is, you have to explain what an operating system is. And the thing about an operating system is that you're never ever supposed to see it. Because nobody really uses an operating system; people use programs on their computer. And the only mission in life of an operating system is to help those programs run. So an operating system never does anything on its own; it's only waiting for the programs to ask for certain resources, or ask for a certain file on the disk, or ask to connect to the outside world. And then the operating system steps in and tries to make it easy for people to write programs."

Linux is widely used in enterprise data centers and in cloud computing environments, where extremely demanding mathematical and analytical calculations are executed. The improvement of the scheduler of Linux would be highly beneficial to those environments, where there would be a bigger throughput with the same hardware. However, even the daily users of Linux would also take advantage of those improvements, since their computer would be more responsive and efficient. So, how could the so-called Completely Fair Scheduler of Linux (CFS) [17] be significantly improved after so many years of continuous development ? The answer lies in the emerging trend of Parallel Processing during the last years.

### **1.1 Thesis Motivation**

The motivation behind this thesis emerged from observations regarding the efficiency of the CFS scheduler, where a random co-scheduling of threads from different applications resulted in higher throughput compared to co-scheduling of threads from the same application. This was due to the contention accumulated in specific resources of the computing system. The previous observations fostered the idea that the characterization of each application can lead us to conclusions regarding the part of the memory hierarchy, where the contention will be prevalent. And as a further step, this knowledge can help us investigate the way in which each application influences the co-scheduled applications and finally create a generic approach that will provide the scheduler with a new principle, that will improve the final efficiency of the scheduler.

The phenomenon of contention in different parts of the memory hierarchy described earlier stems from the exponential difference between the progress of computing power and the progress of memory speed [5]. This difference imposes significant delays during the execution of applications, while waiting for memory operations. Problems regarding memory bandwidth limitations are handled by methods, like improving data locality or hardware prefetching [6], but as long as the working set size of a job exceeds the size of the on-chip cache, the effectiveness of such approaches is quite limited. Another cause of performance degradation is the cache contention between different applications. Applications allocated to different cores of the same chip interfere with each other and the result of this interference on the overall performance depends on the data sharing patterns between the applications. Hardware or software-based methods have tried to analyse and leverage data-sharing patterns, such as Utility Cache Partitioning [4] or Page Colouring [3]. However, the applicability of those methods on modern operating systems are somewhat limited due to their requirement of additional hardware support or non-trivial changes to the virtual memory management system.

So, attempts are focused on implementing contention-aware schedulers that can detect and mitigate resource contention, since the current schedulers of modern operating systems are contention-unaware. Similar approaches handle applications either as single-threaded applications or as multi-threaded applications, where the allocation of resources is already predefined and the scheduler does not contribute to this step. This approach innovates, because it handles applications as multi-threaded applications without having any knowledge regarding required resources, since the definition of the optimum amount of resources that should be allocated for ideal scaling is predicted by a component of the scheduler. Most contention-aware schedulers consist of 2 parts : a classification scheme defining performance degradation for combinations of co-scheduled application and a scheduling policy using those estimations to schedule the corresponding workload. Our approach follows this philosophy, but it also contains a prediction model as intermediate step, where the optimum number of resources that should be allocated to each application to avoid resource contention is estimated.

The results of the scheduler are compared with those of other state-of-the-art contentionaware schedulers, like LLC-MRB [13, 2] and LBB schedulers [13, 14] proposed by previous research, and with the current scheduler of Linux (CFS), which is contention-unaware. The schedulers are compared using total throughput and fairness as main criteria, with our approach presenting the best overall throughput.

### **1.2** Thesis Structure

The thesis is structured in the following way :

**Chapter 2**: We provide some necessary historical background regarding the evolution of hardware and software, the bottlenecks imposed and the solutions proposed. We also make an introduction to some basic principles about Parallel Computing that are necessary to understand important notions in later chapters. Finally, an analysis of various techniques on scheduling policies is made with special focus on contention-aware schedulers

**Chapter 3**: The first component of the proposed scheduler is described, the classification scheme. First of all, there is a reference in previous research that inspired us to create this classification scheme .The decision tree that is used is described and its theoretical explanation is given. Some statistics are also given about the validity of the classification scheme.

**Chapter 4**: The second component of the proposed scheduler is described, the prediction model. A theoretical foundation is being built initially regarding the generic form of the prediction model. Then, the process that has been followed to establish the regression models and the final relationships are defined. Some statistics are given in the end to present the errors of the prediction model.

**Chapter 5**: The final component of the proposed scheduler is described, the scheduling algorithm. A theoretic introduction is given in the beginning to explain some basic principles of the scheduling policy. Then, the exact algorithm is defined. Finally, the statistic results of the experiments are analysed and a comparison between the different schedulers is being conducted.

*Chapter 6*: We make a conclusion regarding our suggested approach and declare some future work that can be done to further improve this approach.

### Chapter 2

# **Theoretical Background**

This chapter will focus on establishing some theoretical foundation that is necessary for the comprehension and analysis of the following parts. Everything started from the evolution of computing systems hardware. The computing power has been increasing tremendously during the last decades, so scientists and researchers have been continuously trying to improve the software of computers so that they can leverage the excessive amount of computing power. With the progress of the technology, the number of cores have started increasing significantly in every computing system. New software technologies have emerged that allow applications to take advantage of more than one cores of the system. Two basic methodologies that have revolutionised the field of Software are the areas of Parallel Programming and Multithreaded Programming. However, even if people could program all applications to execute in multithreaded way, those applications would be handled by the operating systems. So, if operating systems were not capable of scheduling all those parallel applications in a suitable way, the biggest part of the benefit of Parallel Processing would be lost. This was the point where the need for an evolution of the schedulers of operating systems became obvious. Initially, schedulers became capable of handling and scheduling multithreaded applications in a fair way, but they were not capable of detecting bottlenecks and helping applications reach their full performance potential. The basic reason behind this obstacle was the fact that the evolution of the memory speed of computing systems has been really slower than the progress of computing power. Another important reason was the fact that the increased number of cores has slightly spoiled the way the system was taking advantage of the cache memories, since now the different threads were interfering with each other affecting the locality gains. So, the schedulers of modern operating systems have to evolve accordingly in order to take those changes into account during the resource management of the computing system. In other words, schedulers should transform into contention-aware schedulers, thus being capable to detect the contention and decrease it as much as possible. During the last years, a lot of research has been conducted around contention-aware scheduling and this thesis attempts to contribute to this research with a real-life approach that could be easily applied in the current schedulers of modern operating systems.

### 2.1 Hardware Technology Evolution

In this section, the evolution of hardware technology will be briefly described and we will analyse the impact of this evolution to the adaptation of computing systems and their operating systems.

#### 2.1.1 Processing Power Progress

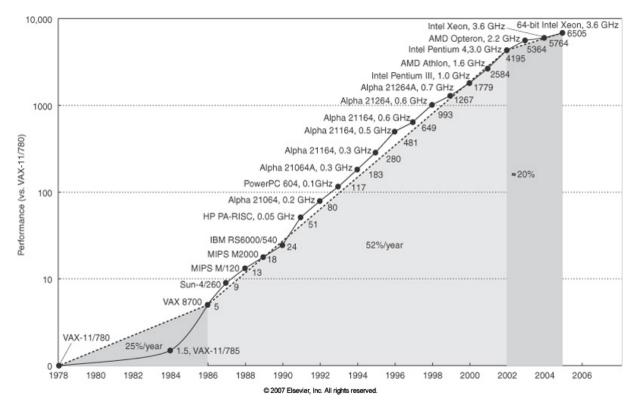

For the thirty-fifth anniversary issue of Electronics Magazine, which was published on April 19, 1965, Gordon E. Moore was asked to predict what was going to happen in the semiconductor components industry over the next ten years. His response was a brief article entitled, 'Cramming more components onto integrated circuits' [18], where he stated that circuit density-doubling would occur every 24 months. This was indeed the case, as we can see from the progress of computers performance in figure 2.1.

Figure 2.1: Growth in processor performance since the mid-1980s. Copyright 2009 Elsevier. All Rights Reserved.

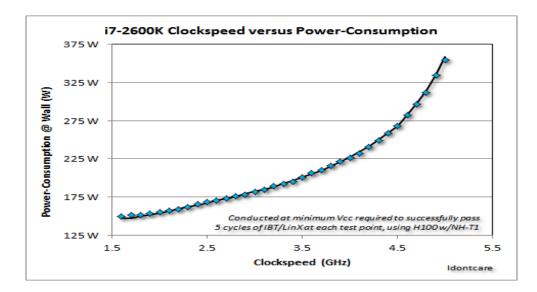

As we can see, prior to the mid-1980s processor performance growth averaged about 25% per year and this increased to about 52% until 2002. This increase of almost 25% has been achieved through Instruction Level Parallelism (ILP). However those gains were expunged and since 2002, it has slowed to about 20% per year. Also, the continuous increase of clock speed has led to a bottleneck regarding the produced power from computing systems. In the figure 2.2, we can see a graph containing the relationship between the clock speed of a intel i7-2600K processor and the produced power.

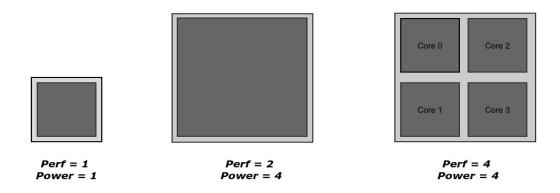

From the previous graph, it is evident that the benefits of the increase in clock speed could not be easily reaped, since there are limitation in the maximum power and heat that a computing system can produce. The previous phenomenon can be explained by Moore's law, since much of the increase of transistors was the reason why a great percentage of the power that was produced was returned to the system due to leakage currents and defects. With leakage power dominating, power consumption is roughly proportional to transistor count. According to Pollack's Law, processor performance grows proportionally to the square root of the area. Completing the necessary calculations as we can see in figure 2.3, this led to a shift to multiprocessing systems.

Figure 2.2: Graph of Clockspeed versus Power Consumption

Figure 2.3: Performance comparison between single-core and multicore systems

### 2.1.2 Memory Speed Progress

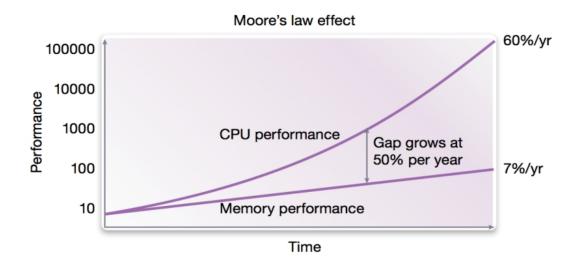

According to Moore's Law, there is also an observation that there is a difference between the progress in CPU performance and the progress in Memory performance and this difference is constantly growing by 50% every year. This can also be seen in figure 2.4. This difference imposes a really hard problem in the attempts to improve the infrastructure of computing systems. The processing power of computing systems evolves, but the memory speed increases slowly. This fact creates a severe bottleneck in the performance of computing systems, since applications waste a great part of their execution time by waiting for requests to memory.

As also stated in "Hitting the Memory Wall : Implications of the obvious" [5], this difference is already an issue, but it will be a much bigger one in in the future. In this paper, the author has attempted to exclude the implications of the cache memories in this consideration by assuming a perfect performance in the cache hierarchy. The author admits that its own prediction regarding the cessation of the rate of improvements in computer performance might not be so accurate, but she insists that we have to start thinking out of the box in order to find a solution to this complex problem. It is stated that the most convenient resolution to

Figure 2.4: Difference between processor performance progress and memory speed progress

the problem would be the discovery of a cool, dense memory technology whose speed scales with that of processors. However, since this type of technology is not easily conceived, we are currently trying to find workaround solutions to temporarily decrease the impact of this issue to computers performance.

### 2.2 Parallel Computing

The predominance of multicore systems, as explained before, has created a need for new software capable to leverage the benefits of those computing systems. The concepts of Parallel Programming and Multithreaded Programming emerged to satisfy this need. Multithreaded Programming allows software engineers to create applications separated in multiple threads, that can occupy the different cores of the computing system, thus allowing the application to be more responsive and complete faster. Most programming languages provide the necessary framework to create an application that can be created with multithreaded organisation, so that it can take advantage of multicore systems. However, in most cases the programmer has to be responsible for the switching between threads and their communication, so that there are no errors in applications. Parallel Programming is a model for creating parallel programs which can be compiled and executed in parallel. Depending on the used programming language, the programmer can either choose to let the operating system allocate resources to different instances or otherwise pre-define the way the resources will be allocated to each thread and the way multiple threads will communicate with each other. In the following parts, we will analyse the different forms of parallel programming and the implications of each one to the performance of the computing system.

#### 2.2.1 Taxonomy

The models of parallel programming can be classified by using 2 different criterias: the process interaction and the problem decomposition.

#### 2.2.1.1 Process Interaction

Process interaction involves the mechanisms by which the various instances of an application can communicate with each other. There are 3 basic forms of interaction : shared memory, message passing and implicit.

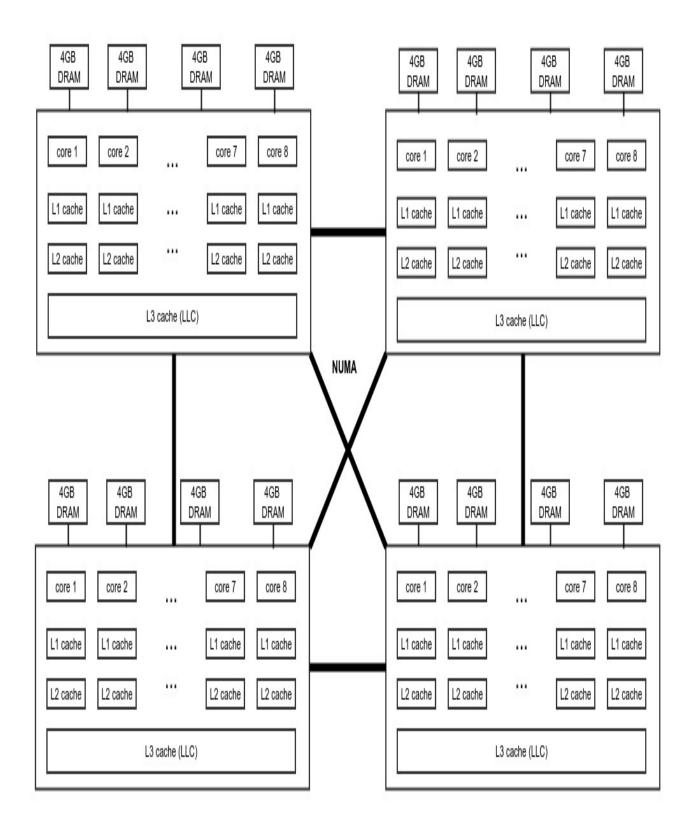

*Shared Memory* is a model of parallel programming used in architectures, where all the processors can access a globally shared memory. Shared Memory architectures can use either Uniform Memory Access (UMA), where all the processors share the physical memory uniformly, or Non-Uniform Memory Access (NUMA), where memory access depends on the distance between each processor and the physical memory. In this model, parallel tasks share a global address space which they read and write to asynchronously. This requires protection mechanisms, such as locks, semaphores and monitors to control concurrent access.

*Message Passing* is a concept from computer science that is used extensively in the design and implementation of modern software applications, where a process sends a message to another process and relies to the second one to select and invoke the actual code to run. In a message passing model, parallel tasks exchange data through passing message to one another. This communication can be either asynchronous or synchronous. The message passing model is used in architectures with distributed physical memory to each core.

*Implicit parallelism* is a model, where the programmer has no vision of the process interaction, since the compiler or interpreter automatically exploits the parallelism inherent to the computations expressed by some of each language's constructs. So, the programmer does not need to worry about task division or process communication, resulting in a significant improved programmer productivity. However, this model is applicable only with domain-specific languages where the concurrency with a problem can be more prescribed.

#### 2.2.1.2 **Problem Decomposition**

Problem Decomposition involves the structure around which the algorithm for the solution of a problem is constructed. This classification can also be referred as algorithmic skeletons. There are 3 basic forms of problem decomposition : task parallelism and data parallelism.

*Task Parallelism* focuses on matching each process with a specific task and distributing those processes across different parallel computing nodes. These processes will often be behaviourally distinct, which emphasizes the need for communication.

**Data Parallelism** on the other hand focuses on distributing the data across different parallel computing nodes. The operations that are performed in the given data set are usually structured in an array. A set of tasks will operate on this data, but independently on separate partitions. In a shared memory system, the data will be accessible to anybody, while in a distributed memory system it will be divided between processes.

Actually, most real programs fall somewhere between task parallelism and data parallelism as far as this classification is concerned. As it became obvious from the previous categorization, there were 2 basic architectures around the parallel programming models. The first architecture that came up was the Symmetric Multiprocessors (SMPs), where there were multiple CPUs with one core per CPU. All the caches were private to each CPU and the communication was conducted through the main memory. However, this architecture was not so efficient, because the phenomenon of false sharing was leading to costly memory

accesses. So, it has been increasingly replaced by Chip Multiprocessors (CMPs), where there are multiple CPU cores on one integrated circuit. Each core has its own private caches and the last-level caches are shared among the cores of a chip. In this architecture, false sharing impact is limited by the shared last-level caches.

#### 2.2.2 MESI Protocol

The predominance of CMPs was the main cause of a new issue called Memory Coherence. This issue affects the computing systems, where 2 or more processors share a common area of memory, as it is the case with the last-level caches of CMPs. More specifically, Cache Coherence is the consistency of shared resource data that ends up stored in multiple local caches. Coherence, for instance, defines the behavior of read and writes to the same shared last-level cache by different cores. The change of the architectures required a corresponding adaptation in the way the operating system would treat those shared resources. Among many protocols that were suggested as Cache Coherence protocols, the most widespread is the MESI protocol, which supports write-back cache. We will try to give a brief analysis of this protocol, since it is mainly involved in the prediction model of the suggested scheduler.

In this protocol, every cache line is marked with one of the 4 following states (using 2 bits) :

*Modified* : the cache line is present only in the current cache and it is dirty, which means it has been modified from the value in main memory. The cache is required to write the modified value back to the main memory at some time in the future, before permitting any other read of the (no longer valid) main memory state. This operation, called write-back, changes the line state to Exclusive.

*Exclusive* : the cache line is present only in the current cache, but it is clean, which means it matches main memory. It may be changed to the Shared state at any time, in response to a read request. Alternatively, it may be changed to the Modified state when writing to it.

*Shared* : this cache line may be stored in other caches of the machine and it is clean. The line may be discarded at any time.

Invalid : this cache line is invalid (unused).

A Read For Ownership (RFO) request is an operation in cache coherency protocols that combines a read and an invalidate broadcast. The operation is issued by the processor trying to write into a cache line that is either in the Shared state or in the Invalid state of the MESI protocol. The operation causes all other processors to set the state of this line to Invalid. A read for ownership transaction is a read operation with intent to write to that memory address. Therefore this operation is exclusive. It brings data to the cache and invalidates all other processor caches which hold this memory line.

#### 2.2.3 Challenges in Multicore Systems

As a conclusion, during the last decades there has been a turn to multicore systems, since it is claimed that they can provide higher degrees of performance. However, it is indisputable that those new hardware architectures have imposed new problems that have to be resolved if multicore systems are to reach their full potential. The main challenges that we have to face in multicore systems are 2. The first one is the memory bandwidth limitation in systems, in which the number of cores is significantly increased up to an extent, where important contention is observed in the shared memory bus during input or output of programs. The second challenge is the communication between different processes that run in cores of the same chip. In cases of strange data-sharing patterns, this can lead to continuous invalidation between different cores, which is stated as cache thrashing. In both cases, the contention in system resources is the crucial factor that has a major impact in the performance of the system. This can not be prevented in application-level. It can only be faced in a lower level, where we could manage the combination of applications, so that contention bottlenecks are avoided as much as possible. This is the reason why a great part of research has been devoted around contention-aware scheduling solutions, since they present really promising results regarding the overall performance of the computing system.

## 2.3 Scheduling

In computing, scheduling is the component of the operating system that allows threads, processes or data flows to have access to system resources, such as processing time and memory bandwidth. This is usually done to load balance and share system resources or achieve a target quality of service. The need for a scheduling algorithm arises from the requirement for most modern systems to perform multitasking (executing more than one process at a time) and multiplexing (transmit multiple data streams simultaneously across a single physical channel).

### 2.3.1 Operating Systems Scheduling

The basic characteristics for a scheduler are the following :

- Throughput, the total number of processes that complete their execution per time unit

- *Latency*, which is divided into

- *Turnaround time*, which is the total time between submissions of a process and its completion

- *Response time*, which is the time from submission of a process until the first time it is scheduled.

- *Fairness*, which is the attemt to give equal CPU time to each process or more generally appropriate times according to each process' priority and workload

- Waiting time, which is the time the process remains in the ready queue

However, these goals often conflict, thus a scheduler will implement a suitable compromise. For instance, the target of throughput can be controversial to that of low latency. So, focus is given to any of the characteristics mentioned before, depending upon the user's needs and objectives. As a result, the scheduler is a component of the operating system that selects the next jobs to be admitted into the system and the next process to execute.

Operating systems may feature up to 3 distinct types of scheduler :

• *Long-term scheduling* or admission scheduler decides which jobs are to be admitted to the ready queue (in the main memory). When an attempt is made to execute its admission

to the set of currently executing processes is either authorized or delayed by the longterm scheduler. So, this scheduler decides what processes are to run on a system and the degree of concurrency to be supported at any time, which means whether a high or low amount of processes are to be executed concurrently, and how the split between I/O bound and CPU bound processes is to be handled. The long term scheduler is responsible for controlling the degree of multiprogramming. It is mainly used in large-scale systems, such as batch processing systems, computer clusters, supercomputers and render farms.

- *Medium-term scheduling* temporarily removes processes from main memory and places them on secondary memory, like disk drive or vice versa. This process is referred to as 'swapping out' or 'swapping in' correspondingly. The medium-term scheduler may decide to swap out a process which is waiting response from the memory for a long time, a process that has low priority or a process that is page faulting frequently. The scheduler will swap the process back in, when the process has been unblocked and is no longer waiting for a resource. In systems that support mapping virtual address space to storage other than the swap file, the medium-term scheduler may actually perform the role of the long-term scheduler.

- Short-term scheduling, also known as the CPU scheduler, decides which of the ready, in memory processes are to be executed after a clock interrupt, an I/O interrupt, an operating system call or another form of signal. Thus, the short-term scheduler makes scheduling decisions much more frequently than the long-term or the medium-term schedulers. It will have to make a scheduling decision at least after every time quantum, which are really short periods. This scheduler can either be preemptive or non-preemptive. Preemptive schedulers are capable of forcibly removing processes from a CPU when the time quantum of their execution has finished. Non-preemptive schedulers, also known as 'cooperative' or 'voluntary', is unable to force processes off the CPU. A preemptive scheduler relies upon a programmable interval timer which invokes an interrupt handler that runs in kernel mode and implements the scheduling function. It can also be referred to as process scheduler.

### 2.3.2 Major Scheduling disciplines

Scheduling disciplines are generic algorithms used for distributing resources among parties which simultaneously and asynchronously require them. Scheduling disciplines can be used in routers as well as in operating systems, disk drives, printers etc. The main purpose of scheduling disciplines are to prevent resource starvation and to guarantee fairness amongst the parties utilising the resources. Scheduling deals with the problem of deciding which of the outstanding requests is to be allocated resources. Each discipline uses different criteria to explain its decisions. The main scheduling disciplines are the following :

• *First Come First Served* (FCFS) is the simplest scheduling algorithm. It simply queues processes in the order that they arrive in the ready queue. This kind of scheduling is non-preemptive, so the processes will start start and finish in the order that they arrive in scheduler queue. Since context switches occur only upon process termination and no reorganization of the queue is required, the scheduling overhead is minimal. The total throughput can be low, since some processes can hold the CPU even when they are blocked. Turnaround time, waiting time and response time can also be high for the

same reason. The systems faces trouble meeting process deadlines, since there is no prioritisation in processes. However, the lack of prioritization means that as long as every process eventually completes, there is no starvation.

- Shortest Job First (SJF) is a discipline, where processes with the least estimated processing time are the next to be scheduled. First of all, this requires advanced knowledge or estimations about the time required for a process to complete. This scheduling is preemptive. Thus, if a shorter process arives during another process' execution, the currently running process will be interrupted and the arrived process will be executed. This creates excess overhead through additional context switching. Waiting time and response time increase as the process's computational requirements increase. Overall waiting time is smaller than FIFO, since no process has to wait for the termination of the longest process. Besides the additional infrastructure needed for this scheduling discipline, the main problem is the possibility of starvation of long processes, if short processes arrive continuously in the queue.

- *Fixed priority preemptive scheduling*, where the operating system assigns a fixed priority rank to every process and the scheduler arranges the processes in the ready queue in order of their priority. Since this scheduling discipline is preemptive, lower-priority processes get interrupted by incoming higher-priority processes. The scheduling overhead is not minimal, nor it is significant. If the number of rankings is limited, it can be characterized as a collection of FIFO queues, one for each priority ranking. Processes in lower-priority queues are selected only when all of the higher-priority queues are empty. Deadlines can be met by giving processes with deadlines a higher priority. Starvation is possible, but it can be avoided, if aging is implemented so that processes do not stay in the same priority queue forever.

- *Round Robin scheduling* (RR) assigns a fixed time unit per process (defined as time quantum), and cycles through them. It involves extensive overhead, especially with a small time unit. It has a balanced throughput between FCFS and SJF. Short processes are completed faster than in FCFS and long processes are completed faster than in SJF. It has a good average response time and the waiting time is dependent on number of processes and not on average process duration. Deadlines are rarely met in RR Scheduling, because of high waiting times. Starvation can never occur, since no priority is given. There is also significant overhead in the context switch between processes when the time quantum finishes, especially if its duration is really short.

In the following sections, we will give a brief description of the CFS scheduler of Linux and other state-of-the-art contention-aware schedulers, since our proposed scheduler will be finally compared with these schedulers.

### 2.3.3 Linux Scheduler - CFS

The Completely Fair Scheduler (CFS) is a process scheduler which was merged into the 2.6.23 release of the Linux kernel and is the default scheduler. We could say that it is a combination of round robin and fixed priority preemptive scheduling. It handles CPU resource allocation for executing processes, and aims to maximize overall CPU utilization while also maximizing interactive performance. In contrast to the previous O(1) scheduler used in older Linux 2.6 kernels, the CFS scheduler implementation is not based on run queues. Instead, a red-black tree implements a "timeline" of future task execution. Additionally, the scheduler uses nanosecond granularity accounting, the atomic units by which an individual process' share of the CPU was allocated (thus making redundant the previous notion of timeslices). This precise knowledge also means that no specific heuristics are required to determine the interactivity of a process, for example. Like the old O(1) scheduler, CFS uses a concept called "sleeper fairness", which considers sleeping or waiting tasks equivalent to those on the runqueue. This means that interactive tasks which spend most of their time waiting for user input or other events get a comparable share of CPU time when they need it.

The data structure used for the scheduling algorithm is a red-black tree in which nodes are scheduler specific structures (called sched entity). A red black tree is a data structure which is a type of a self-balancing binary search tree. Balance is preserved by colouring the nodes with 2 colors (black and red) according to some properties, which define how unbalanced the tree can become in the worst case. Each time the tree is modified, the new tree is subsequently rearranged and repainted to restore coloring properties. The properties are designed in such a way that this rearranging and recoloring can be performed efficiently. The balancing of the tree is not perfect, but it guarantees searching in O(logn) time, where n is the total number of elements in the tree. The insertion and deletion operations are also performed in O(logn) time. Tracking the color of each node requires only 1 bit of information per node because there are only two colors. In CFS, the nodes of the red-black tree represent the processes. These nodes are indexed by processor execution time in nanoseconds. A maximum execution time is also calculated for each process. This time is based upon the idea that an "ideal processor" would equally share processing power amongst all processes. Thus, the maximum execution time is the time the process has been waiting to run, divided by the total number of processes, or in other words, the maximum execution time is the time the process would have expected to run on an "ideal processor".

When the scheduler is invoked to run a new process, the workflow of the scheduler is the following :

- 1. The left most node of the scheduling tree is retrieved by the scheduler (as it will have the lowest spent execution time) and scheduled for execution.

- 2. If the process simply completes execution, it is removed from the system and scheduling tree.

- 3. If the process reaches its maximum execution time or is otherwise stopped (voluntarily or via interrupt) it is reinserted into the scheduling tree based on its new spent execution time.

- 4. The new left-most node is selected from the tree, repeating the iteration.

If the process spends a lot of its time sleeping, then its spent time value is low and it automatically gets the priority boost when it finally needs it. Hence those kind of tasks do not get less processor time than the tasks that are constantly running.

#### 2.3.4 Contention-Aware schedulers

A crucial factor that is somewhat ignored in the implementation of the Completely Fair Scheduler is the fact that the different cores of a multicore system are directly dependent. CFS treats applications simply as single-threaded applications and cores as black boxes, where there is not interaction between different cores. However, this is not the truth. As it became evident in the previous analysis, there are multiple bottlenecks present in multicore systems. The impact of those bottlenecks is highly influenced by the profile of the applications and the way they interact with each other. For instance, if 2 applications that present similar data-use patterns are scheduled in cores of the same chip, then each one will invalidate the data of the other application due to Cache Coherence protocols, such as MESI protocol described before. Likewise, if 2 applications that use extensively the memory link are scheduled in cores of the same chip, then they will end up sharing the available memory bandwith and this will lead to serious performance degradation. However, if we crossed the pairs scheduling one application using the memory with one application using the last-level cache, then we would have managed to decrease significantly the competition between the 2 application and as well as ease the performance degradation. As a result, CFS scheduler would be drastically improved, if it was evolved into a contention-aware scheduler that would be able to detect those bottlenecks and handle them. An ideal contention-aware scheduler would have to be capable to characterize the applications in order to estimate the place of contention and then schedule the applications in suitable combinations, so that competition in system resources between application is minimized.

The research about contention-aware schedulers has progressed with big steps. A lot of contention-aware schedulers have been proposed both for UMA and NUMA systems with really promising results. For UMA systems, some of the best suggested contention-aware schedulers are :

- OBS-X scheduling policy based on OS Dynamic Observations [21]: this scheduling policy uses observations of each task's cache usage in order to distribute cache-heavy threads throughout the system, aiming to spread out cache load. When a new task is created, OBS-X looks for the LLC group with the smallest cache load, and places the new task in this group. this scheduling policy was only compared with the Linux default scheduler and it presented overall speedup increase up to 4.6%.

- Vector Balancing Scheduling policy [22]: this policy reduces contention by migrating tasks, led by the information of task activity vector, that represents the utilization of chip resources caused by tasks. The proposed scheduling policy avoids contention for resources by co-scheduling tasks with different characteristics. One weakness of this paper is that they used exclusively compute-intensive tasks and this limits the space where the Vector Balancing can be applied successfully.

- Distributed Intensity Online scheduler (DIO) [23]: this scheduler continuously monitors the miss rates of applications, since it is argued that this is the best contention predictor, then finds the best performance case and separates threads. It obtains the miss rates of applications dynamically online via performance counters. This makes DIO more attractive since the stack distance profiles, which require extra work to obtain online, are not required. It was compared to the default Linux scheduler and increased the

total performance by 13%. An adapted version of this scheduling policy has also been implemented for NUMA systems, called DINO. DINO tries to migrate threads in the same memory areas when possible. It uses the same heuristis with DIO and divides applications in categories depending on the number of LLC misses they have per 1.000 instructions.

- Symbiotic JobScheduling [19] : this scheduler combines an overhead-free sample phase which collects information about various possible schedules, and a symbiosis phase which uses that information to predict which schedule will provide the best performance. However, it required a sampling phase in which, the workload is not scheduled optimally.

- AMPS scheduler [24] : this scheduling is implemented both for SMPs and NUMAstyle performace assymetric architectures. AMPS contains the following components : assymetry-aware load-balancing, that balances threads to cores in proportion with their computing power and faster core-first scheduling, that controls thread migrations based on predictions of their overhead. However, AMPS uses thread-independent policies, which schedule threads independently regardless of application types and dependencies, which is a rather significant weakness.

- Framework for Adaptive Contention-Aware Thread Migrations (FACT) [20] : this approach monitors some performance indicators lively during the execution, predicts the bottlenecks and makes adaptations to the scheduling in order to avoid contention and improve overall performance. In the implementation of FACT, a variety of statistical models were used, such as linear regression models, fuzzy rule-based models, decision-tree models, K-nearest neighbor models. It proved to be slightly better than DI, but it relies on supervised learning and targeted the same problem from a whole different view.

As a conclusion, there are multiple contention-aware schedulers suggested from previous research. The majority of those schedulers have been compared to the default Linux scheduler, so as to ensure that the benefits from transition to contention-aware scheduling will be significant. However, there is not so much comparison between proposed contention-aware schedulers. Furthermore, all those schedulers are compared with the Linux default scheduler solely as far as overall performance is concerned, leaving outside the consideration the degree of fairness imposed by the scheduler. Since both throughput and fairness are significant properties of a scheduling policy, we will make comparisons using both criteria.

Our scheduler takes into consideration all kinds of applications, ranging from applications that are CPU-bound to applications that stress extensively the main memory. However, we have adjusted all applications so that they have integrated the input data set, in order to avoid I/O actions. This makes the workload not so realistic, but the I/O delays is an issue that can be resolved independently and is not included in systems resource contention. The miss rate was used as heuristic at OBS-X scheduler, Vector Balancing Scheduler, DIO and FACT. Moreover, the memory link usage was used as heuristic for detecting resources contention at Vector Balancing Scheduler, Symbiotic scheduling and FACT. It is consequently obvious

that those 2 measures are the most useful heuristics regarding system resources contention. For this reason, our scheduler will be compared with the default Linux scheduler and 2 contention-aware schedulers that are derived from the previously mentioned research. Those schedulers are the LLC-MRB and the LBB scheduler. The first one attempts to balance the last-level cache misses in the whole system, while the latter one tries to balance the memory link usage. This is achieved using a queue with all the applications sorted by their LLC misses (or memory bandwidth correspondingly) and the applications are paired suitably, so that applications that present high contention are co-scheduled with applications with low contention. The comparison between our scheduler and the rest will be in terms of fairness and total throughput.

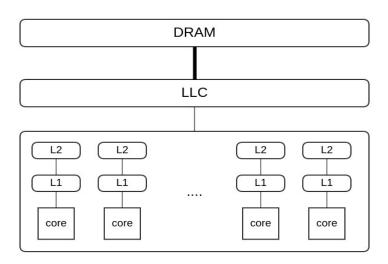

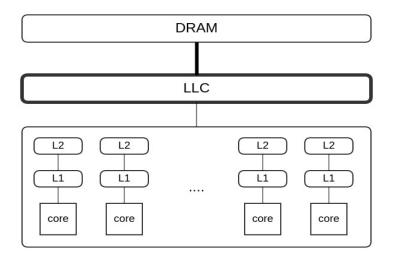

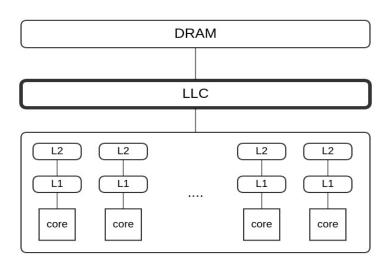

### **2.4 Experimentation Environment**

The comparison between the different schedulers is performed on an Intel Xeon R CPU E5-4620 Sandy Bridge architecture machine. The architectural details are presented in Table I. All the available hardware prefetchers are enabled whereas Hyperthreading and Turbo Boost are disabled. The platform's kernel was Debian Linux 6.0.6 with kernel 3.7.10.

| Cores  | 8                                                            |  |  |

|--------|--------------------------------------------------------------|--|--|

| L1     | Data Cache: private, 32KB, 8-way, 64 bytes block size        |  |  |

|        | Instruction Cache: private, 32KB, 8-way, 64 bytes block size |  |  |

| L2     | private, 256KB, 8-way, 64 bytes block size                   |  |  |

| L3     | shared, 16MB, 16-way, 64 bytes block size                    |  |  |

| Memory | 64GB, DDR3, 1333MHz                                          |  |  |

| OS     | Debian Linux 6.0.6 with kernel 3.7.10                        |  |  |

Table 2.1: Sandy Bridge Architecture Details

The prediction model was tested in the previous platform, but for more complete validation it was also tested in another machine with an AMD Opteron 248 Nehalem architecture. The architectural details of the second machine can be seen in the table 2.

| Cores  | 4                                |

|--------|----------------------------------|

| L1     | Data Cache: private, 32KB        |

|        | Instruction Cache: private, 32KB |

| L2     | private, 256KB                   |

| L3     | shared, 16MB                     |

| Memory | 32GB                             |

| OS     | Ubuntu 12.04.2 LTS               |

Table 2.2: Nehalem Architecture Details

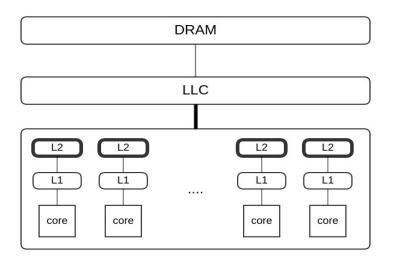

A diagram of the Sandy Bridge architecture that was mainly used for the design and verification of the prediction model, as well as for the implementation and testing of the scheduling algorithm can be seen in the Figure 2.5

Figure 2.5: Sandy Bridge architecture

The various counters that have been used for the investigation and verification of the classification scheme and the prediction model can be seen in table 2.3. This table contains the Intel hexadecimal codes for both architectures Nehalem and Sandy Bridge. We remind

that the Nehalem architecture was used only in the step of verification of the prediction model.

|                                                   | Sandy Bridge |       | Nehalem    |       |

|---------------------------------------------------|--------------|-------|------------|-------|

| Counter Name                                      | Event Num.   | Umask | Event Num. | Umask |

| L1 lines allocated in Modified                    | 0xD2         | 0x0F  | 0x51       | 0x02  |

| L1 lines evicted in Modified due to hitM or dirty | 0x51         | 0x08  | 0x51       | 0x08  |

| L1 lines evicted in Modified due to replacement   | 0x51         | 0x51  | 0x51       | 0x04  |

| L1 -> L2 writebacks                               | 0xfo         | 0x10  | 0x28       | 0x0F  |

| L2 cache lines allocated in Invalid               | 0xF1         | 0x01  | _          | _     |

| L2 cache lines allocated in Shared                | 0xF1         | 0x02  | 0xF1       | 0x02  |

| L2 cache lines allocated in Exclusive             | 0xF1         | 0x04  | 0xF1       | 0x04  |

| RFO requests that access L2 cache                 | 0xF0         | 0x02  | 0x24       | 0x0C  |

| Dirty L2 cache lines evicted                      | 0xf2         | 0x05  | 0xF2       | 0x02  |

| Clean L2 cache lines evicted by prefetcher        | 0xF2         | 0x0a  | 0xF2       | 0x04  |

| Snoop invaliations of Modified line               | 0x22         | 0x50  | _          | _     |

| L3 lines allocated in Exclusive                   | 0x0A         | 0x02  | 0x0A       | 0x02  |

| L3 lines allocated in Shared                      | 0x0A         | 0x04  | 0x0A       | 0x04  |

| LLC snoops invalidations due to memory requests   | 0x34         | 0x4F  | _          | _     |

| Micro-operations retired                          | 0xC2         | 0x01  | 0xC2       | 0x01  |

| Memory micro-operations retired                   | 0xD0         | 0x81  | 0xC2       | 0x81  |

Table 2.3: Intel Hardware Performance Counters used

The suggested scheduler is made of 3 components : the classification scheme, the prediction model and the scheduling algorithm. Each one of the following chapters analyses one component of the scheduler.

### **Chapter 3**

## **Classification Scheme**

In this chapter, we will cover the classification scheme used by our scheduler.

#### 3.1 Previous Research

All contention-aware schedulers presented in previous research rely on an application classification scheme that predicts application interference under a co-execution scenario. The accuracy of the classification scheme in the prediction of application co-execution penalties is one of the most critical factors for a co-scheduling framework. Cache utilization patterns, LLC miss rate, memory link bandwidth and sensitivity have been proposed towards this direction. However, as these schemes capture application activity in a limited part of the architecture, i.e. either memory link or last level cache (LLC), they fail to provide a more complete picture of the resources candidate to suffer from contention. This scheduler contains a classification scheme that attempts to take into consideration all possible places of contention in system's architecture. In this way, it can include a different heuristic for each part of the architecture and take into account all the different classes of applications. An attempt is made to cover the entire memory hierarchy from main memory down to the private caches and even the computing cores. This information is utilized to understand application behavior and predict interference problems.

The most dominant classification schemes of previous research are the color classes [16] and the animal classes [15]. The color classification categorizes applications into one of 4 colors, according to the observed performance degradation when running an program using only a 1MB L2 cache compared to the baseline configuration with 4MB. Any program with greater than 20% slowdown was classified as Red and greater than 5% slowdown (but less than 20%) as Yellow. Out of the remaining programs with less than or equal to 5% slowdown, the program is classified as Green if the total number of L2 accesses is greater than or equal to 14 misses per thousand cycles, otherwise the program is in the Black category. While Lin et al.'s color-based classification scheme may be useful for workload creation, it cannot be easily used for dynamic, on-the-fly classification of program behavior. In particular, computing the performance slowdown would require simultaneously running two copies of the program on two cores, each with their own dedicated L2 caches.

. The animal classification divides the applications into 4 classes : turtles, sheep, rabbits and devils. Turtles do not make rare use of the shared last-level cache, possibly due to small working data sets. Sheeps are applications that are not sensitive to the number of ways allocated to them, so they can exhibit high LLC usage even with a few ways allocated. Rabbits are very sensitive about the number of ways allocated to them. Devils access the last-level cache frequently, but still have very high miss rates. This classification aimed to better identify cache-sharing behaviors and more accurately predict when cache partitioning will be useful. For processors without some form of dynamic cache management/partitioning, one can provide feedback back to the operating system so that the process scheduler can attempt to avoid co-scheduling incompatible animal types, which means it could be used as classification scheme for our approach. However, the animalistic classification does not build a solid theoretical explanation between the various parts of the memory hierarchy and the different classes, as it is the case with our classification scheme

## **3.2** Application classes

Our classification scheme is inspired by previous research [1] and distinguishes between 5 application classes, where the names of the classes are indicative of the parts of the memory that are stressed :

- memory link intensive applications, that exhibit high memory bandwidth

- applications that have significant activity both on the memory link and the last-level shared cache

- cache intensive applications, that exhibit activity mainly in the last-level cache

- cache intensive applications, that exhibit activity in highest level private caches and when competing ending up using last-level cache but not to a extended degree

- applications that exhibit no significant activity on the shared resources of the system and are limited to private caches and cores

It is now visible that our classification scheme directly bonds the different parts of the memory hierarchy to the different application classes. Interactions between applications from various classes are adequately predictable to support an efficient scheduling mechanism. In the following paragraphs, each application class is described further.

**Class L**: Applications with very intense pressure on the memory link, consuming a high percentage of its bandwidth. This class typically includes applications that exhibit one or more of the following characteristics: they perform streaming memory accesses on data sets that largely exceed the size of the LLC, have either no reuse or large reuse distances, perform rather lightweight computations on the data fetched. To reach this high level of memory link bandwidth consumption, members of this class heavily involve the hardware prefetcher in their execution. Although they fetch data on the entire space of the LLC due their streaming nature, they do not actually reuse them either because their access pattern does not recur to the same data, or because they have been swept out of the cache.

*Class LC applications* : Applications with substantial pressure on the memory link and also high activity on the shared LLC. This is a wide class including applications with streaming access and heavy computations on the data fetched, or a combination of main memory access and LLC data reuse. The exact level of memory bandwidth consumption and data reuse on the LLC may significantly differentiate execution behavior within the class.

**Class** C: Applications with heavy activity on the shared LLC. This class includes applications with varying characteristics, such as those that operate on small data sets with

Figure 3.1: Class L applications

Figure 3.2: Class LC applications

heavy reuse, optimized code for the LLC (e.g. via cache blocking with a block size fitting the LLC), or latency-bound applications that make irregular data accesses and benefit a lot from LLC hits.

**Class** C+ : Applications with focused activity on the highest level private caches (L2 cache). In fact, it is a subcategory of class C applications. If executed without major contention in resources, those applications' activity is restricted in private cache. However, if executed with other applications exhibiting significant activity in L2 cache (e.g. with another C+ application), the overall contention will oblige the C+ application to increase the last-level cache usage.

**Class** N: Applications that restrict their activity either to the private part of the memory hierarchy or within the core. The members of this class create no contention to the shared

Figure 3.3: Class C applications

Figure 3.4: Class C+ applications

system resources. The class includes applications with heavy computations, very small working sets or optimized data reuse that can be serviced by the private caches.

Despite the fact that inside each class one may find applications with quite different execution patterns, the classes themselves can be used to capture the big picture of co-execution interference between applications. As it will also be used from the scheduling algorithm in the last step, we need to analyse the interference between each possible combination of applications. In the following we denote as x - y the co-execution of an application from class x with an application from class y. '\*' is used as a wildcard for any application class.

N - \* : This co-execution does not create any interference, since class N applications do not use any shared resource.

Figure 3.5: Class N applications

L - L: In this co-execution, applications compete for the memory link. The contention pattern in this case indicates that the shared resource which in this case is the memory link bandwidth is divided (not necessarily equally) between the competing applications.

L - C: In this co-execution, applications exhibit activity in different shared resources. However, it will lead to severe performance degradation for C applications with no impact in the performance of L applications. This is due to the fact that the constant delivery of new data from the main memory will invalidate the data of the C application, while L application will not have any problem with those invalidations as it does not use the cache memories.

L - LC : In this co-execution, there will be performance degradation for both applications. However, as described before, LC will face a bigger degradation than L application.

LC - LC : In this co-execution, there will be contention in shared resources, but the contention will be divided between 2 diffent resources (memory link and LLC). For this reason, the interference will be present on both sides but it will be kept in low levels.

LC - C : Similarly, there is some mediocre contention leading to performance degradation. The contention will be more severe for the C application than for the LC application.

C - C : This co-execution is the most difficult to predict, since the impact of the contention will depend upon data access patterns. As it will be described later, the MESI protocol was taken into consideration for this specific co-execution scenario.

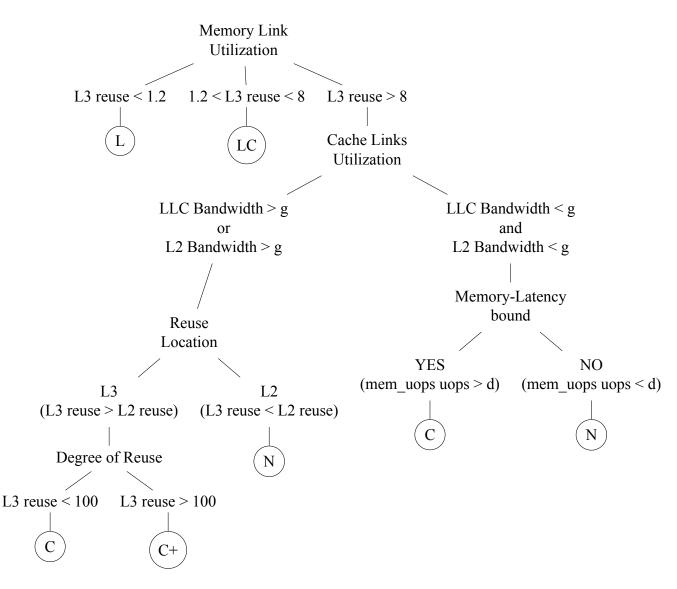

#### 3.3 Decision Tree

Having defined the application classes, we need a concrete method to perform the classification using runtime statistics. The core idea is to inspect the data path from main memory down to the core to locate links with high utilization. We have focused only on the stream flowing towards the core, as we have empirically found that this direction concentrates the largest portion of contention. A hierarchical approach is followed similarly to the application classes. First of all we examine if the current investigated application consumes a large portion of the system's memory link bandwidth. If this is true, this

application belongs to L class. When the memory link utilization is low, activity is restricted from the LLC and downwards. If we are able to measure significant data flow somewhere in the LLC  $\rightarrow$  Core part of the data path, then this is due to data reuse. By locating the reuse region –LLC or private caches– we can classify applications as C,C+ and N, respectively.

In case that low data flow is measured throughout the entire data path, we have identified three application patterns that may exhibit this picture: 1) applications that heavily reuse data on the L1 cache (high activity on the gray arrow of 2) applications that perform computations within the core with minimal data accesses, and 3) memory-latency bound applications that suffer from high LLC miss penalties (and also greatly benefit from LLC hits). We observed that inspecting the application's mem\_uops/all\_uops ratio and IPC suffices to differentiate between C and N classes.

Our classification method implements the decision tree shown in Figure 3.6. The L3 reuse has proved to be a better heuristic than memory bandwidth for distinguishing between LC and L classes, since it was combining both memory bandwidth and LLC bandwidth giving a more complete view. For the classification tree, we have used the following relationships and constants:

$$\begin{split} Memory \ bandwidth &= (per\_core\_bw * 64)/(10^6)(GB/sec) \\ LLC \ bandwidth &= (l2\_lines\_in * 64)/(10^6)(GB/sec) \\ L2 \ bandwidth &= (l1\_lines\_in * 64)/(10^6)(GB/sec) \\ L3 \ reuse &= LLC \ bandwidth/Memory \ bandwidth \\ L2 \ reuse &= L2 \ bandwidth/LLC \ bandwidth \\ g &= 0.35 * Maximum Memory Bandwidth \\ d &= 0.25 \end{split}$$

Figure 3.6: Classification scheme

In order to monitor the applications and acquire their profile, we retrieved hardware performance counters to collect performance data. More specifically, we used UNHLT\_CORE\_CYCLES, INSTR\_RETIRED, LLC\_MISSES, L1D.REPLACEMENT, L2\_LINES.IN, MEM\_UOP\_RETIRED.ALL and UOPS\_RETIRED.ALL. Furthermore, we use OFFCORE\_REQUESTS (0xB7, 0x01; 0xBB, 0x01) together with Intel's Performance Counter Monitor [9] utility to acquire information regarding bandwidth usage.

#### **3.4** Evaluation and Validation

The classification scheme is just a component of our scheduler and it is not really valuable to validate it separately, as we are specifically interested in the impact it will have in the overall efficiency of the scheduler. However, this classification scheme is theoretically ground. It has been created using the research done in [1] as a starting point. The initial classification scheme of [1] has been validated. The process that was followed is the following : a workload of applications belonging to all classes has been created.

The applications were initially executed solo and then all the possible combinations of applications were co-executed. The average slowdown of each possible combination of application classes was compared to the initial assumptions of the classification scheme. The slowdowns derived for each possible combination of different application classes from this research can be seen in Figure 3.7.

| L  | 1.93 | 1.73 | 2.35 | 1.05 |

|----|------|------|------|------|

| LC | 1.30 | 1.15 | 1.15 | 1.03 |

| с  | 1.22 | 1.11 | 1.23 | 1.02 |

| N  | 1.09 | 1.09 | 1.00 | 1.03 |

|    | L    | LC   | с    | N    |

Figure 3.7: Average slowdown between different classes

We can observe that, as expected, N applications neither impose nor suffer from interference. C applications, as predicted, experience dramatic slowdowns when co-executed with L applications and in general do not impose severe interference with a few remarkable exceptions. Interestingly, although the LC class may contain a wider variety of activity patterns, their interference behavior is more or less uniform: they suffer more by the co-execution with L applications, and then by the co-execution with applications of the same class. In general, they do not also heavily interfere with C applications. As a result, the assumptions that were initially made are verified.

## Chapter 4