# Εθνικό Μετσόβιο Πολυτεχνείο

Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών

# Efficient Estimation of Reliability Metrics for Circuits in Deca-Nanometer Nodes

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

Μιχαήλ Α. Νόλτσης

Επιβλέπων: Δημήτριος Σούντρης

Αναπληρωτής Καθηγητής Ε.Μ.Π.

## Εθνικό Μετσόβιο Πολυτεχνείο

Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών

# Efficient Estimation of Reliability Metrics for Circuits in Deca-Nanometer Nodes

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

Μιχαήλ Α. Νόλτσης

Επιβλέπων: Δημήτριος Σούντρης

Αναπληρωτής Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 31η Ιουλίου 2014.

Κιαμάλ Πεκμεστζή Δημήτριος Σούντρης Ιωάννης Ξανθάκης Καθηγητής Ε.Μ.Π. Αναπληρωτής Καθηγητής Ε.Μ.Π. Καθηγητής Ε.Μ.Π.

Αθήνα, Ιούλιος 2014

| Μιχαήλ Α. Νόλτση                                                       |                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Διπλωματούχος Ηλε                                                      | κτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.                                                                                                                                                                                                                                                                                                  |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                       |

|                                                                        | λ Α. Νόλτσης, 2014.<br>ός δικαιώματος. All rights reserved.                                                                                                                                                                                                                                                                                           |

| τμήματος αυτής, για ε<br>μη κερδοσκοπικό, εκπ<br>προέλευσης και να δια | γραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή<br>μπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό<br>αιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή<br>τηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για<br>τρέπει να απευθύνονται προς τον συγγραφέα. |

|                                                                        | μπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέο μηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου                                                                                                                                                                                                          |

## **Abstract**

In modern technologies of integrated circuits (IC) and with the downscaling of device dimensions, various degradation modes constitute major reliability concerns. Bias Temperature Instability (BTI) is a representative example, posing as a significant reliability threat in Field-Effect Transistor (FET) technologies and has been known for more than 30 years. At first, the model that tried to explain this phenomenon was based on the Reaction-Diffusion (RD) theory and was developed nearly 30 years ago. Recently, an atomistic model has been proposed, that enables the modeling of BTI in modern technologies.

By observing the amount of software designed to simulate the BTI degradation, tools can be found that are based on the atomistic theory but are computationally prohibitive when it comes to simulating complex circuits consisting of a large number of devices. Tools based on the RD model are unable to accurately capture the BTI-induced degradation, especially in devices with small dimensions. The current thesis is appropriately positioned since it discusses a novel simulation framework that is efficient yet highly accurate. A subset of an embedded Static Random Access Memory (SRAM) is used for verification purposes. The estimation of the functional yield of the circuit over three years of operation will be examined as well as other reliability metrics, such as defects per million (DPM), mean time to failure (MTTF) and failures in time (FIT rate). Finally, the interplay between these metrics is discussed and efficient computation methods are proposed for each one.

## **Key words**

Bias Temperature Instability (BTI), Gate Stack Defects, Reliability, Circuit Simulations, Static Random Access Memory (SRAM), Functional Yield, Mean Time to Failure (MTTF), Defects Per Million (DPM), Failures in Time rate (FIT rate).

# Περίληψη

Καθώς η τεχνολογία οδηγεί στην κατασκευή τρανζίστορ ολοένα και μικρότερων διαστάσεων, έχουν εμφανιστεί αρκετά φαινόμενα που επηρεάζουν την αξιοπιστία των ολοκληρωμένων κυκλωμάτων. Ένα από αυτά τα φαινόμενα ονομάζεται "Bias Temperature Instability", αποτελεί σημαντικό κίνδυνο για την αξιοπιστία των ολοκληρωμένων κυκλωμάτων και έχει παρατηρηθεί εδώ και πάνω από 30 χρόνια . Το πρώτο μοντέλο που προσπάθησε να εξηγήσει αυτό το φαινόμενο εμφανίστηκε πριν από 30 περίπου χρόνια, βασίστηκε στη διάχυση υδρογόνου και ως εκ τούτου ονομάστηκε "Reaction-Diffusion model". Πριν από μερικά χρόνια δημιουργήθηκε ένα νέο ατομιστικό μοντέλο το οποίο βασίζεται κυρίως στην εμφάνιση ελαττωμάτων στο διηλεκτρικό μεταξύ της πύλης και του καναλιού των FET τρανζιστορ.

Μελετώντας κανείς τη βιβλιογραφία που αφορά στο ατομιστικό αυτό μοντέλο, μπορεί να συναντήσει εργαλεία που προσομοιώνουν με ακρίβεια το μοντέλο αλλά δυστυχώς απαιτούν αρκετό χρόνο για να εκτελεστούν, κάτι το οποίο τα καθιστά απαγορευτικά για εκτενή χρήση. Παράλληλα, υπάρχουν εργαλεία βασισμένα στο μοντέλο της διάχυσης τα οποία βέβαια αδυνατούν να παράξουν σωστά και λεπτομερή αποτελέσματα, κυρίως σε τεχνολογίες μικρών διαστάσεων. Η παρούσα λοιπόν διπλωματική εργασία παρουσιάζει τα αποτελέσματα ενός νέου και καινοτόμου εργαλείου το οποίο βασίζεται στο ατομιστικό μοντέλο, ωστόσο προσομοιώνει αποδοτικά αλλά και με ακρίβεια το φαινόμενο της γήρανσης. Ένα αντιπροσωπευτικό μονοπάτι στατικής μνήμης (SRAM) θα χρησιμοποιηθεί ως παράδειγμα της λειτουργίας του μοντέλου ενώ παράλληλα θα υπολογισθούν, με βάση τα αποτελέσματα των προσομοιώσεων αυτών, μετρικές, σημαντικές για το χαρακτηρισμό της απόδοσης και αξιοπιστίας του κυκλώματος, ενώ παράλληλα θα μελετηθούν λεπτομερώς και οι σχέσεις που τις συνδέουν.

# Acknowledgements

First of all, I would like to thank assistant prof. Dimitrios Soudris for supervising this thesis. Having the chance to attend his lectures was of great importance to me, since he gave me the opportunity to attain a strong background in this specific field. Furthermore, his advice and guidance were really helpful for the completion of my undergraduate studies and the start of my professional career.

Moreover, this thesis would not be completed without the mentorship of Dimitrios Rodopoulos. Cooperating with him was one of my best academic experiences since our discussions always inspired and motivated me to work and overcome any difficulties. I am thankful for the time he devoted to my instruction and assistance.

Last but not least, I would like to express my gratitude to my family for their moral and financial support throughout these years.

Michail A. Noltsis, Athens, July 31, 2014

# **Contents**

| Li  | st of I | igures                                                                         | 13 |

|-----|---------|--------------------------------------------------------------------------------|----|

| Lis | st of T | Tables                                                                         | 13 |

| 1.  | Intro   | oduction                                                                       | 15 |

| 2.  | Prio    | r Art                                                                          |    |

|     | 2.1     | Introduction                                                                   | 17 |

|     | 2.2     | <b>,</b>                                                                       | 17 |

|     |         | 2.2.1 The Reaction-Diffusion Model                                             | 17 |

|     |         | 2.2.2 Insufficiencies of the RD Model                                          | 18 |

|     | 2.3     | Atomistic Theory                                                               | 19 |

|     |         | 2.3.1 The Two-State Atomistic Model                                            | 19 |

|     |         | 2.3.2 Advantages and boundaries of the atomistic model                         | 21 |

|     | 2.4     | Functional Yield and other Reliability Metrics                                 | 22 |

|     | 2.5     | Existing Aging Simulators                                                      | 23 |

|     | 2.6     | Conclusions                                                                    | 25 |

| 3.  | Yield   | d Inspection                                                                   | 26 |

|     | 3.1     | Introduction                                                                   | 26 |

|     | 3.2     | Existing Components                                                            | 26 |

|     | 3.3     | SPICE-free Signal Activity Propagation                                         | 28 |

|     | 3.4     | Combining Existing Tools to a Yield Analysis Tool                              | 34 |

|     | 3.5     | Yield vs. DPM vs FIT/MTTF                                                      | 36 |

|     | 3.6     |                                                                                | 38 |

| 4.  | Qua     | ntitative Results                                                              | 39 |

|     | 4.1     | Introduction                                                                   | 39 |

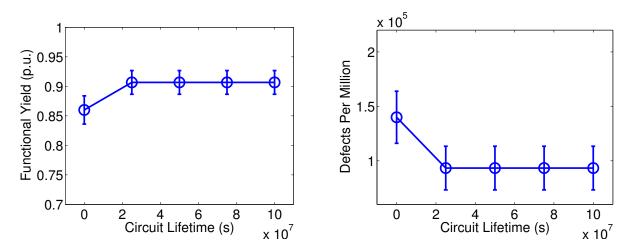

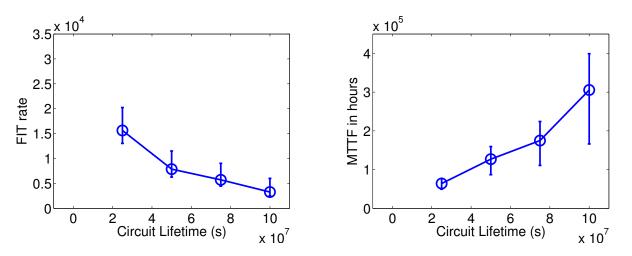

|     | 4.2     | Functional Yield, DPM, FIT rate and MTTF estimations                           | 39 |

|     |         | 4.2.1 Circuit Simulation under Fixed Supply Voltage                            | 39 |

|     |         | 4.2.2 Circuit Simulation under Dynamic Voltage Scaling                         | 42 |

|     | 4.3     | Comments                                                                       | 44 |

| 5.  | Con     | clusions                                                                       | 45 |

|     | 5.1     | Overall                                                                        | 45 |

|     | 5.2     | Future Work                                                                    | 46 |

|     |         | 5.2.1 Improving the Simulation Framework to Capture BTI on FinFET Technology . | 46 |

|     |         | 5.2.2 Enhancing the Simulation Framework to Account for both BTI and HCI       | 47 |

|     |         |                                                                                |    |

| Bi  | bliogr  | raphy                                                                          | 49 |

# **List of Figures**

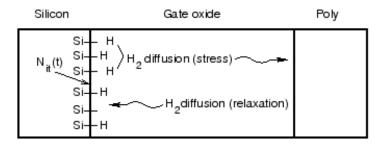

| 2.1<br>2.2 | Schematic description of the R-D model as shown in [1]                              | 18       |

|------------|-------------------------------------------------------------------------------------|----------|

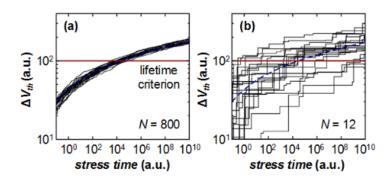

|            | presented in [2]                                                                    | 19       |

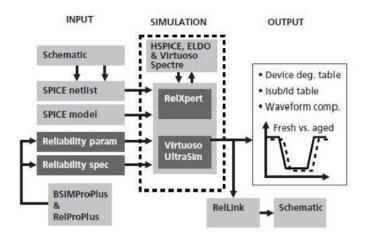

| 2.3        | Reliability simulation flowchart using UltraSim [3]                                 | 24       |

| 2.4        | Calculating the Aged Model parameters with UltraSim as shown in [3]                 | 24       |

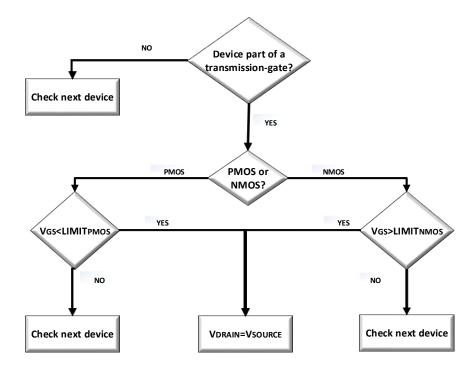

| 3.1        | Flowchart showing the algorithm of the extension of the propagate tool              | 29       |

| 3.2        | Operational path of an embedded SRAM design as presented in [4]                     | 30       |

| 3.3        | Logic diagram for propagate verification                                            | 31       |

| 3.4        | Histograms of mean error and st. deviation comparing the original and the extended  |          |

|            | version of the tool                                                                 | 32       |

| 3.5        | Histograms of mean error and st. deviation comparing the 0.95 hypothesis to the ex- |          |

|            | tended propagate algorithm                                                          | 33       |

| 3.6        | Difference in CPU time for SPICE simulation and for propagate                       | 34       |

| 3.7        | Flowchart for a single iteration of the proposed simulation framework               | 36       |

| 3.8        | Diagram showing the interdependability of Functional Yield, DPM, FIT rate and MTTF  | 37       |

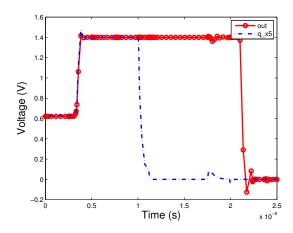

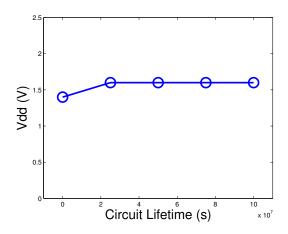

| 4.1        | Graph showing the $V_{dd}$ configuration for the case of fixed supply voltage       | 39       |

| 4.2        | Graph showing an instantiation of a functionally correct sample                     | 40       |

| 4.3        | Graphs showing examples of functional violations                                    | 40       |

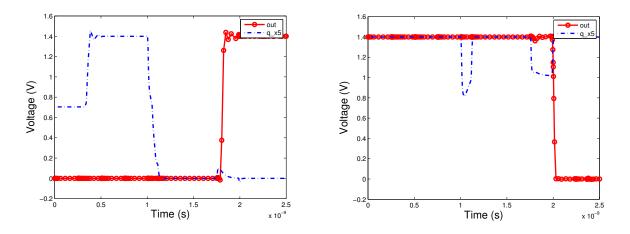

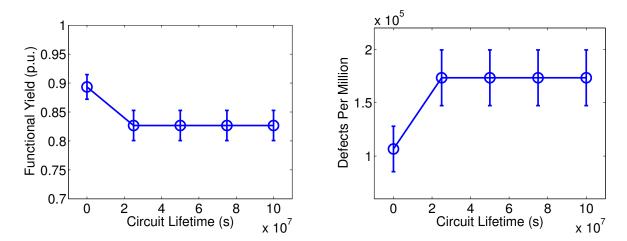

| 4.4        | Graphs showing the Functional Yield and DPM estimations                             | 41       |

| 4.5        | Graphs showing the FIT rate and MTTF estimations                                    | 42       |

| 4.6        | Graph showing the $V_{dd}$ configuration for the case of dvs                        | 42       |

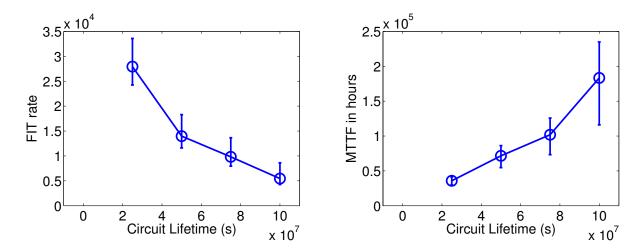

| 4.7        | Graphs showing the Functional Yield and DPM estimations for the dvs case            | 43       |

| 4.8        | Graphs showing the FIT rate and MTTF estimations for the dvs case                   | 43       |

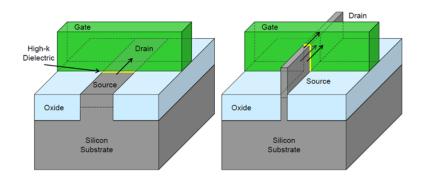

| 5.1        | A planar device vs a FinFET device as shown in [5]                                  | 47       |

| 5.2        | The physical mechanism of HCI as presented in [6]                                   | 48       |

| List       | of Tables                                                                           |          |

| 3.1<br>3.2 | The components of the simulation framework                                          | 28<br>35 |

# CHAPTER 1

## Introduction

The probability that an electronic circuit shall perform correct service along its operating time is defined as reliability of the respective electronic system [7]. Probability is introduced because predicting the failure mechanisms of any electronic circuit in a fully deterministic way is practically infeasible. Moreover, nowadays, the demand for ultra-large-scale integration in chips from the semiconductor industry led to a dramatic decrease in the size of the devices, amplifying a variety of reliability concerns in digital systems.

One key feature affecting reliability is the voltage and temperature stress. An effect that emerges from this voltage stress and deteriorates from the exposure of the device at elevated temperatures is called Bias Temperature Instability (BTI). The BTI effect is the aging phenomenon that results in an absolute increase of the threshold voltage of a transistor. It is this rise of  $V_{th}$  that further causes degradation of the drain current and transconductance of the channel in MOSFETs (Metal-Oxide semiconductor Field-Effect transistor). Therefore, these aging effects engender fluctuations in the delay and power of electronic circuits and may even cause system failures.

In order to capture this aging phenomenon, the community has developed a significant number of tools based on either the Reaction-Diffusion (RD) or the atomistic models. The simulation frameworks that follow the atomistic theory provide highly accurate results, however the computational time needed for long-lasting simulations is inhibitive. The tools based upon the RD theory are incapable of providing precise estimations when simulating small-dimensioned devices. Hence, the usage of tools that effectively model the aging effect but also provide elaborated results in short run-times is crucial and necessary. Thus, the purpose of this thesis is to discuss some preferable features of such tools and present a relevant instantiation.

Specifically, this thesis combines existing tools into an overall framework, which performs estimation of the time-dependent functional yield of a circuit, under BTI-induced degradation. The modules of the framework, which are already in place, are discussed and certain optimizations are proposed for some of them. Also, the mathematical formulation that connects the functional yield with some other important reliability metrics are presented.

In Chapter 2, the established BTI models are introduced. First, the Reaction-Diffusion model is presented along with its disadvantages and drawbacks. Next, follows the elaboration on the transition from the RD model to the atomistic theory. The concept of the defect is explained along with the definitions of capture and emission time constants. Afterwards, the functional yield along with other metrics used in reliability analysis such as defects per million (DPM), mean time to failure (MTTF) and

failures in time rate (FIT rate) are underlined. Lastly, some existing industry tools for BTI modeling are mentioned.

A simulation framework that accurately captures the mechanism of Bias Temperature Instability is discussed in Chapter 3. The components of this framework are demonstrated and the verification of one of them is presented step by step. The improved accuracy of this tool is emphasized in contrast to crude approximations given by other existing frameworks. Also, the synthetic design flow is demonstrated. Finally, the functional yield is converted through mathematical formulation to other reliability metrics.

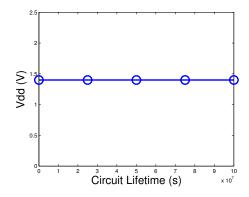

Moving to Chapter 4, the simulation results of the analyzed framework are presented in detail, with graphs that show the fluctuations of some reliability metrics of the target electronic circuit throughout its lifetime. It must be pointed out that a realistic circuit of a subset of an embedded Static Random Access Memory (SRAM) is used for verification purposes. The functional yield, MTTF, DPM and FIT rate of this circuit are estimated over three years of operation for 2 different cases of  $V_{dd}$  configuration. For the first case,  $V_{dd}$  is fixed to a constant value while for the second case, a dynamic voltage scaling is used for the simulations.

Finally, in the last Chapter, a number of conclusions that derive from this work are underlined. Also, some topics for future work are proposed that can expand the contributions of this thesis.

# CHAPTER 2

## **Prior Art**

#### 2.1 Introduction

This Chapter elaborates on the two existing models that try to explain the BTI phenomenon. Firstly, the Reaction-Diffusion model is reviewed along with its handicap to accurately describe the BTI degradation on downscaled devices. Other insufficiencies of this model are also noted that mostly regard the incapability of the model to explain the relaxation phase. Next, the atomistic theory is presented and an approach towards an atomistic model is reviewed, along with the advantages of this model over the Reaction-Diffusion approach. The main advantages of the model, namely the workload dependency and the capturing of the Random Telegraph Noise (RTN) as well, are noted.

BTI-induced degradation may lead to functional reliability violations, hence it constitutes a valid reliability concern for deca-nanometer circuits. Thus, the next part of the Chapter describes aspects of the reliability analysis and points out some key metrics used in this analysis. For this reason, the terms of functional yield, defects per million, mean time to failure and failures in time are discussed.

Finally, some simulation frameworks and commercial tools that were developed to model BTI degradation are reviewed. These tools are presented briefly while their disadvantages in following the aging effect in small-dimension devices are pointed out.

## 2.2 RD theory

#### 2.2.1 The Reaction-Diffusion Model

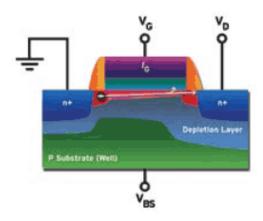

The Reaction-Diffusion model was created 30 years ago and was the first model that tried to explain and predict the BTI effect. It is based on the reaction-diffusion theory, namely on "the breaking and annealing of the Si-H bonds at the Si/oxide substrate and mainly focuses on pFETs" [8]. According to this approach, when the gate of a pFET is under bias stress, then the Si-H bonds are breaking and the H atoms are diffusing towards the gate stack, while holes are taking their place in those bonds. This procedure leads to the creation of interface traps and oxide charge that cause a shift to the pFET's threshold voltage as shown in Figure 2.1 [1]. A similar approach is expected for the nFETs, but with electrons being the trapped charge in this case. The model also argues that trap distances from the Si/oxide interface determine the portion of this threshold shift with "oxide charge located closer to the oxide substrate leading to a higher threshold voltage shift than charge near the gate-oxide interface" [9].

Figure 2.1: Schematic description of the R-D model as shown in [1]

In addition, the conventional RD theory predicts a recovery phase, during which, once the stress is removed from the pFET's gate, a subset of the Si-H bonds is annealed because hydrogen is expected to diffuse back, thus partially restoring the threshold shifts. In fact, according to the model, there are two degradation components: a permanent component, which remains after the bias stress is removed and a reversible component, that recovers with the absence of voltage stress to the gate of the device. In other words, the Reaction-Diffusion model claims partial recovery.

To be more specific, the number of interface traps  $N_{it}$  created by detached hydrogen atoms (from the Si-H interface) is defined by the Equation 2.1 [10]:

$$N_{it} = \sqrt{\frac{k_F N_o}{2k_R}} (D_H t)^{\frac{1}{4}}$$

(2.1)

where  $k_F$  is the dissociation rate constant that creates broken bonds,  $k_R$  is the rate of reverse annealing of Si-H bonds,  $N_o$  is the total number of Si-H bonds and  $D_H$  shows the hydrogen diffusion coefficient.

Also, according to the Reaction Diffusion model, the threshold voltage shift that occurs due to the increase in interface charge is given by [11]:

$$\Delta V_{th}(E_{ox}, t) = (1+m) \frac{q N_{it}(E_{ox}, t)}{C_{ox}}$$

(2.2)

$E_{ox} = \frac{V_{gs}}{C_{ox}}$ , q is the elementary charge and  $C_{ox}$  presents the gate capacitance and  $V_{gs}$  presents the gate voltage.

By combining the Equations 2.1 and 2.2, it can be implied that the change in  $V_{th}$  follows an 1/4 exponential dependence throughout the device lifetime. And it is true that in old technologies with large devices, such a shift in the threshold voltage could be experimentally verified [2]. However, in modern technologies and with the downscaling of device dimensions, a huge variation in  $\Delta V_{th}$  that did not follow the exponential rule mentioned earlier was observed, as shown in Figure 2.2. Moreover, when the research community turned its attention to the partial recovery phase predicted by the RD model and compared it with experimental data, it appeared that the data could not be explained by the RD theory and were opposed to what the theory suggested [12].

#### 2.2.2 Insufficiencies of the RD Model

One key feature of the RD theory is that a general and universal recovery is anticipated, meaning that "when  $\Delta V_{th}$  is normalized to its value at the end of the stress, it depends only on the ratio of the

**Figure 2.2:** Expected threshold voltage shift in devices of (a) older and (b) modern technologies as presented in [2]

stress and relaxation times  $t_s$  and  $t_r$ " [12]. Neither the forward and backward reaction rates nor the diffusion coefficient  $D_H$  have any impact on the recovery. Thus, the normalized RD recovery can be captured approximately by the Equation 2.3 [12]:

$$\frac{\Delta V_{th}(t_s, t_r)}{\Delta V_{th}(t_s, 0)} = \frac{1}{1 + (\frac{t_r}{t_s})^{\frac{1}{2}}}$$

(2.3)

Hence, according to the RD theory, a 50% recovery is expected when  $\frac{t_s}{t_r}=1$ , namely when the relaxation time equals the stress time. However, it can be seen from experimental data that "recovery in large devices is rather uniform and roughly follows  $\log(t_r)$  over the whole experimental time interval" [12]. Thus, this formula proves inconsistent with scientific measurements. Moreover, another problem emerges from the above mathematical formulation: while an insignificant part of the  $\Delta V_{th}$  is expected to have recovered when  $t_r \ll t_s$ , all experiments show that "recovery is already in full flight in measurements taken just some few microseconds after the stress is removed" [12], hence the relaxation phase and the  $\Delta V_{th}$  recovery are not consistent with Equation 2.3.

Summarizing the above claims, it can be concluded that the RD theory may prove rather unsuccessful in predicting BTI, especially in devices of modern technologies. Therefore, in order to precisely predict the BTI degradation another theory was created that captures the bulk of experimental data more accurately.

## 2.3 Atomistic Theory

#### 2.3.1 The Two-State Atomistic Model

The atomistic model has been recently proposed by the research community in order to capture BTI degradation in a more detailed manner. The defects created from the charge trapping mechanism occupy the central role of the atomistic theory. The essence of this defect-centric model is that, once the defect is created, its charge state can continuously change between two states depending on the temperature and gate stress. This stands in contrast to the RD theory and the term of trapped holes, which are not sensitive to bias changes. Hence, the atomistic theory confronts these defects as switching traps. According to the model, a defect has two states and can be charged or discharged, in other words occupied or unoccupied.

If a defect is unoccupied, it does not add to the  $\Delta V_{th}$  and has no impact in the aging of the device, but when a defect is occupied, it adds to the threshold shift. It has to be noted that while the RD theory supported the contribution of an oxide trap to the voltage threshold shift to depend on the defect's depth in the oxide, the atomistic model does not follow this assumption. Besides, the thickness of modern oxides cannot support any significant distribution of defects based on distance alone [9]. The atomistic approach supports that every defect is identified with its  $\Delta V_{th}$  impact on the device -when occupied- that comes from an exponential distribution with a mean value  $\eta$  [2]. All defects are also characterized with their capture and emission time constants  $\tau_c$  and  $\tau_e$  [2]. Each FET with gate length  $L_G$  and width  $W_G$  is populated with a specific number of defect precursors n taken from a Poisson distribution with mean  $N = L_G W_G N_{ot}$  [2]. This means that the number of defects of each transistor is strongly depending on its size with larger transistors being dwelled by a bigger number of defects than devices with smaller dimensions.

Whether a defect is captured or not, depends on the capture probability  $(P_c)$  of each gate stack defect. " $P_c$  is the probability of a gate stack defect being captured after a specific voltage stress signal  $(V_{gs})$  has been applied to the respective gate" [8]. Because of introducing probability to the scene, the atomistic model has a stochastic nature in dealing with the BTI and does not focus so much on the cite creation and the physical mechanisms responsible for BTI (and the creation of these defects). Nevertheless, this model accurately captures this aging phenomenon in large as well as in small devices were the number of defects decreases dramatically.

As a matter of fact, experiments show that recovery in small-area devices (e.g.  $W \times L = 100$  nm  $\times$  100 nm) proceeds in small steps, which are not consistent with a reaction-diffusion model. Rather, they are consistent with the emission of individual holes based on a first-order reaction-rate process. "The properties of these discrete steps are fully consistent with charge trapping observed in the context of Random Telegraph Noise" [12]. RTN is a type of electronic noise that occurs in semiconductors and consists of sudden capture and emission transitions of carriers on traps [13] at random and unpredictable times on a tiny fraction of time. This means that the atomistic model, with its inherent features of stochastic capture and emission of a defect, can accurately predict the impact of the BTI effect and also provide a solid modeling of the RTN.

As mentioned earlier,  $P_c$  is an important parameter of the atomistic model. Actually, the capture probability depends on the time constants of each defect and the characteristics of the  $V_{gs}$  signal or, to be more specific, its frequency f, its duty factor  $\alpha$  and its duration  $\Delta t$ . Time constants are generally voltage and temperature dependent. According to an atomistic approach designed for digital circuits [2], the voltage dependence of each time constant is simplified to the two dominant values: low (L) and high (H) gate bias. Hence, all defects are characterized by four time constants:  $\tau_{e,H}$ ,  $\tau_{e,L}$ ,  $\tau_{c,H}$ ,  $\tau_{c,L}$ . This approach [2] also assumes the latter to be uniformly distributed on the logarithmic scale between  $10^{-9}$  and  $10^{9}$ s while  $\tau_{c,H}$  and  $\tau_{e,H}$  are weakly correlated with  $\tau_{e,L}$ , with  $\langle \tau_{c,H} \rangle^{-1} \sim 0.01 \langle \tau_{e,L} \rangle$  and  $\langle \tau_{e,H} \rangle \sim 100 \langle \tau_{e,L} \rangle$ . Lastly,  $\tau_{c,L}$  is assumed to be large in comparison with the other 3 constants [2].

The capture and emission of charge is described by first-order kinetics and the probability of a defect capturing charge  $P_c$  is assumed to follow the differential Equation 2.4 [2]

$$\frac{dP_c}{dt} = \frac{1 - P_c}{\tau_c} - \frac{P_c}{\tau_e} \tag{2.4}$$

$<sup>^{1} &</sup>lt; \tau >$  presents the mean value of  $\tau$ .

The two terms of this Equation,  $\tau_c$  and  $\tau_e$  represent the capture and emission probabilities respectively. The  $P_c$ 's dependence on the capture and emission constants can be seen from 2.4. The solution of Equation 2.4 is 2.5 [2]:

$P_c = \frac{\tau}{\tau_c} + \left(P_{c0} - \frac{\tau}{\tau_c}\right) exp\left(-\frac{t}{\tau}\right)$  (2.5)

where  $\tau^{-1} = \tau_c^{-1} + \tau_e^{-1}$  and t stands for the time elapsed since the defect was occupied with the probability  $P_{c0}$ . The dependency on the initial value of  $P_{c0}$  should be expected since the capture probability was described by a first-order differential equation.

For every instance of a simulation at a time t,  $P_c$  is evaluated and the occupancy of a defect is resolved based on a comparison between the capture probability and a number r chosen randomly between 0 and 1. The defect is assumed occupied iff  $r < P_c$  and its impact to  $V_{th}$  is added to the device's  $V_{th}$ . A similar concept is followed for the calculation of the emission probability  $(P_e)$  for a gate stack defect.

#### 2.3.2 Advantages and boundaries of the atomistic model

While the RD model fails to capture the aging degradation at aggressively downscaled devices, the atomistic model succeeds in providing an approach that can accurately predict the threshold voltage shift due to BTI stress regardless of the size of the device. This atomistic approach introduces time dependent variability based on the stochastic properties of individual defects and their impact on a FET. "This framework is capable of following defects with widely distributed time scales, from fast and RTN-like to slow and quasi-permanent such as BTI, in a unified manner" [2]. Hence, the atomistic approach provides a first step towards RTN modeling as well.

Another important advantage of the atomistic model is the consideration of the workload of the device for the appropriate time inspection [14], an essential feature in reliability analysis of modern ICs. The atomistic model takes into account not only the time of the stress  $t_s$ , but also the type of the gate bias applied to the device. This distinct degradation of different input sequences and workload scenarios assists significantly on examining the BTI degradation of systems under realistic workloads, but also provides a strong contribution when considering mitigation techniques.

Simulation frameworks based on this model can also easily incorporate time-zero variability of threshold voltage, a factor that proves of great importance as the size of the dimensions is shrinking. Time-zero  $V_{th}$  variability is introduced because from a large set of devices, the assumption that all of them have an identical threshold voltage is unrealistic mainly due to production flaws. After all, even state-of-the-art manufacturing processes cannot produce chips with consistent characteristics, which means that two transistors, fabricated a few dozen nanometers apart on the same piece of silicon, can have different electrical properties [15]. Hence, this initial variability can be captured by the atomistic model by introducing a Gaussian distribution for the initial threshold voltage  $V_{th0}$  of each FET.

Nevertheless, the advantages of the atomistic model vanish when it comes to simulating devices over extensive time intervals and the superiority of the model becomes a bottleneck in case of the long-term aging simulations. Simulation frameworks following the atomistic model provide an accurate estimation of the BTI degradation but are computationally prohibitive when it comes to simulating large netlists. Other tools, that require lower memory usage and CPU time, provide only a crude approximation of the results.

To conclude, it seems that the atomistic model can capture more aspects of the BTI effect than the RD model, however the detailed nature of the model becomes a major disadvantage due to increased computational complexity.

#### 2.4 Functional Yield and other Reliability Metrics

It has been made clear by now that BTI-induced degradation constitutes a significant reliability threat in the hardware of digital systems. The aging effect can lead to delays or even functional violations. In the context of this thesis, a failure constitutes a functional violation. Specifically, "a failure is a nonperformance of the operating function" [16], that can be observed by the end-user.

A common metric used in many cases [17], [8] as quality assessment of digital circuits is the functional yield, which refers to the proportion of devices found to perform properly.

**Functional Yield.** Represents the ratio of the number of the circuits working correctly, to the total circuits examined [18].

Functional Yield =

$$\frac{\text{Number of circuits working properly}}{\text{Total circuits examined}}$$

(2.6)

Another metric used in some cases [19] to describe the functional behaviour of a set of ICs is defects per million (DPM). In the context of this thesis, a defect is simply a failed circuit sample.

**Defects Per Million.** (DPM) is the ratio of the number of "functionally incorrect" circuits, to the total circuits examined, normalized to one million.

Defects Per Million =

$$\frac{\text{Number of failed circuits}}{\text{Total circuits examined}} \times 10^6$$

(2.7)

The characterization of the reliability of a set of devices can also be given in terms of mean time to failure (MTTF) or failures in time rate (FIT rate). They represent the expected failure rate of semiconductors and other electronic devices during their lifetime operation and can be statistically projected from the results of accelerated test procedures [20], [21], [22].

**Mean Time To Failure.** Corresponds to the mean time of operation before a failure [23]. MTTF is calculated by the Equation 2.8 [22]:

$$MTTF = \frac{Device Hours}{Number of Failures}$$

(2.8)

**Failures In Time rate.** Represents the failure rate of a circuit during its lifetime, normalized to one billion device hours. 1 FIT stands for one failure observed during a billion device hours [20]. FIT rate and MTTF are connected via the mathematical formulation [23]:

$$FIT_{rate} = \frac{10^9}{MTTF} \tag{2.9}$$

A common practice of the test engineers is the acceleration of the test procedure that enables the simulation of long-lasting operating times. The test procedure can be accelerated by increasing the temperature of the test environment, because most failure mechanisms are temperature activated [21]. In this way, shorter tests can be conducted that simulate many years of device testing under normal temperature conditions. It is therefore important to be able to measure the effect of this testing acceleration. If a device is stressed at a high temperature  $T_2$ , for time  $t_2$ , the equivalent time  $t_1$  which would cause the device the same level of stress at a lower temperature  $T_1$  can be estimated by the *acceleration factor*, defined as [21]:

$$A = \frac{t_1}{t_2} \tag{2.10}$$

that is, the ratio of the time at the lower temperature, to that at a higher. The *acceleration factor* A can be estimated from the Equation 2.11 [21]:

Acceleration factor =

$$e^{\left[\frac{E_A}{k} \times \left(\frac{1}{T_1} - \frac{1}{T_2}\right)\right]}$$

(2.11)

where  $E_A$  is the activation energy of the failure mechanism and k is the Boltzmann constant=8.6 ×  $10^{-5}$  eV/K. The value of activation energy can be found from experiments and is usually nearly 1.0 eV [21].

According to relevant work [21], [22], when the failure rate  $f_2$  at temperature  $T_2$  is known, the failure rate at the temperature  $T_1$  can be found by:  $f_1 = A \times f_2$ . In this way, the failure rates under normal operating conditions can be estimated by testing circuit samples for shorter time windows and at higher temperatures.

### 2.5 Existing Aging Simulators

In order to understand the advantages of the simulation framework that will be discussed in the next Chapter, other simulation approaches that model the BTI degradation will be presented briefly, along with their distinguishing features. After all, the degradation of FET device characteristics because of aging, has become a critical reliability metric in downscaled technologies hence reliability analysis can be found on many simulating tools and approaches [3], [24], [25], [26]. The software support that models BTI is crucial in order to enable designers to detect reliability failures and estimate the reliability metrics of ICs.

Looking through a variety of simulation approaches, one can find the industry standard tool called Virtuoso UltraSim [3]. Virtuoso is a design suite developed by Cadence Design Systems and the Ultra-Sim package can simulate the effects of NBTI and HCI, independently or together. This tool performs short simulations in order to estimate the aging effect and perform a reliability analysis over a netlist. UltraSim has a built-in support for reliability simulations meaning that both simulations regarding the "fresh" and the "aged" netlist are performed independently and "Fresh and degraded waveforms are output to output waveform files during each simulation" [3]. In Virtuoso, the aged parameters of the devices' modelcards are calculated by interpolation or regression as can be seen in Figure 2.4.

A piece of software developed by Mentor Graphics that can be used for reliability analysis is ELDO [24]. ELDO is a SPICE-like simulator with addons that enable the aging analysis of a circuit. In the

Figure 2.3: Reliability simulation flowchart using UltraSim [3].

Figure 2.4: Calculating the Aged Model parameters with UltraSim as shown in [3].

ELDO environment, after the stress of each device is set for a transient time, the degradation of the devices for long time spans is calculated. The degradation results are then used to update the model parameters in the model card that can be user defined. The aging analysis in this tool can be achieved for a number of time intervals and at every time step, these model parameters can be updated. This estimation of the aging factor is based on extrapolation and specifically on either an exponential or linear calculation.

Other approaches that are also based on the RD model exist. However, some of them [26] fail to effectively capture the recovery phase leading to over-estimation of the BTI effect and pessimistic results concerning the yield inspection and other reliability metrics. In this work it is clearly mentioned that the model "does not include quantitative results considering an ac recovery" [26]. On the contrary, an RD-based model that can capture both stress and relaxation phases is [25]. The degradation in this model is calculated based on the operating conditions and the signal probability during the stress phase. In this approach, the threshold voltage shift is estimated from the Equation 2.2 but the  $N_{it}$  computations "are applicable only to deterministic waveforms" [25]. Considering the fact that predicting the exact nature of a random waveforms is impossible, this approach introduces a method that transforms an input signal of a random nature to an equivalent periodic deterministic waveform. In this work, the modified values of  $V_{th}$  of all the devices are computed and then a SPICE simulation is executed, to estimate the NBTI-induced delay.

From the above, it can be concluded that the majority of commercial tools and modeling approaches are based on the RD model and may fail to accurately capture the aging effect in downscaled devices of modern technologies. A second handicap that some of these simulators like UltraSim or ELDO have, is that they focus only on NBTI, while there is little consideration regarding the effects of the PBTI. So, a discussion of a simulation approach that is based on the atomistic theory rather than the RD theory seems a very timely and relevant contribution.

#### 2.6 Conclusions

The BTI-induced degradation, although observed in devices of older technologies with large dimensions, has proven to be a reliability threat of major importance in downscaled technologies. The first theory that tried to explicate and develop the physical mechanisms of this effect was the reaction-diffusion theory. This theory supported that the gradual breaking and annealing of Si-H bonds at the Si/oxide substrate was the cause of BTI. The breaking of the bonds led to carriers being trapped in the broken bonds and cause a threshold voltage shift. Whenever no stress was applied to the gate of the device, hydrogen diffused back and annealed some broken bonds and in this way, partially recovered the  $V_{th}$  shift.

However, the reaction-diffusion model was proven inadequate to capture this aging effect in modern, small-dimension devices. The stochastic properties of the BTI observed in experiments were explained by a new atomistic theory. This model treats defects as switching oxide traps that change their state between occupied and unoccupied by capturing and emitting charge in a stochastic way. Another strong feature of this model is its workload-dependency. Hence, a discussion over a simulation framework based on this model is an apt direction for this thesis.

Next, the definitions of time-dependent functional yield, defects per million, failures in time and mean time to failure were reviewed as they constitute common metrics used in reliability analysis. Finally some widely-used industry tools as well as some simulation approaches that aim at modeling the BTI degradation and can help in the reliability analysis were discussed. All of them follow the RD model hence they seem to be of inferior accuracy, in comparison to an atomistic model. Thus, a computationally feasible tool for atomistic reliability analysis constitutes the major motivation behind the current thesis.

# **CHAPTER 3**

# **Yield Inspection**

#### 3.1 Introduction

This Chapter presents an instantiation of a yield analysis methodology that targets the entire lifetime of realistic ICs. First, existing tools that are reused in the current instantiation are displayed and are briefly discussed. These tools have been in place as a result of previous work [27], however many of them have been extended and optimized in the context of this thesis. After the presentation of the existing components, we present the resulting instantiation and illustrate its functionality in a detailed way.

The importance of the propagate tool in this framework is underlined. This tool is responsible for estimating the duty factors of the internal nodes of the netlist and stands in contrast to other existing tools in frameworks for simulating BTI degradation. The verification of this component is also examined and the accuracy of the tool is compared to the hypothesis of a fixed duty factor for all nodes that can be seen in other works [28].

Lastly, after the definitions of functional yield, MTTF, FIT rate and DPM were reviewed in the previous Chapter, the mathematical formulation connecting these metrics is underlined.

## 3.2 Existing Components

In the previous Chapter, the insufficiencies of existing simulation tools based on the atomistic model were mentioned and the significance of a simulation framework that can accurately and effectively capture the principles of the atomistic theory was highlighted. A major handicap of these simulation approaches is the usage of a SPICE signal activity format that is very detailed but comes at a cost of inhibitive processing times. What previous approaches suffer from, is the absence of a signal waveform representation that would enable a precise yet efficient BTI simulation [8]. Recently, a novel waveform representation has been proposed, called Compact Digital Waveform (CDW). This signal representation "exploits optimally the accuracy versus complexity trade-off" and can enable BTI simulations at reduced CPU times [8].

• The tool that implements the idea of the CDW and has been adapted in the discussed framework is called wavapprox and a detailed description of its function can be found in previous work [27]. The key feature of this tool is "the grouping of consecutive signal regions that feature a similar f and  $\alpha$  figures and occupy a duration of  $\Delta T$ " [8]. So the percentage of the signal activity

belonging in this time interval (that is characterized by same values of f and  $\alpha$ ) is represented by a single point with coordinates  $(f, \alpha, \Delta T)$ . Thus, given the SPICE waveform, the initial signal is scanned and the CDW points are produced. Moreover, the compression of the initial signal waveform to a CDW representation is done via selected accuracy, achieved by the user-defined error margins  $\epsilon_f$ ,  $\epsilon_\alpha$ .

In the context of this thesis, an alteration of this tool has been performed, in order for it to account for dc signals. Specifically, the original version of the tool estimated the duty factor of an ac SPICE signal representation focusing on the alterations of the voltage value of the signal during its duration. The new version of this tool calculates also the duty factor of dc signals were no alteration of the voltage value is observed. The new algorithm compares the constant voltage value of a dc signal to a user-defined limit and iff the voltage value of this signal is higher than the limit, then the duty factor of the relative signal is set to 1. In this simulation framework the limit is set equal to  $\frac{V_{dd}}{2}$ .

• Another tool that is used in this simulation framework is pcestimate. This tool is responsible for calculating the capture probability of every single defect of all the devices of a netlist. Hence, at each point of the CDW representation of a signal, the following Equation is performed, that calculates the  $P_c$  of a defect [8]:

$$P_c = \left(P_{c0} + \frac{b}{a}\right)e^{an} - \frac{b}{a} \tag{3.1}$$

The parameters a and b are functions of  $\alpha$  and f, so it is clear that the inputs in this tool are the time constants, the initial capture probability and the  $\alpha$  and f that represent the gate workload and provide workload dependency in the simulation.

- The flatten tool is used in order to flatten the netlist. It should be noted that commercial tools allow an internal flattened representation. However, given that custom observability of the netlist is preferable during the development stage, we choose to flatten it with a dedicated tool.

- After the netlist is flattened, a tool named tzinit is used in order to capture  $V_{th0}$  variability. After all, in a population of realistic devices, not all of them have the same threshold voltage but the  $V_{th0}$  is distributed near a mean value [15]. Hence, this tool assumes a Gaussian distribution for the initial threshold voltage  $V_{th0}$  of each FET. "The parameters of this distribution are the mean  $V_{th0}$  and the variance  $\sigma^2$ " [2]. This  $V_{th0}$  variability is captured by using the **delvto** command [29], which is available in typical SPICE solvers.

- A tool that populates each device of a netlist with defects and creates initial conditions for the BTI defects is essential. The definit tool places a number of defects in all FETs of the netlist. The number of the defects of a device is taken randomly from a Poisson distribution according to the atomistic model with a mean of  $N = L_G W_G N_{ot}$  [2]. Hence, devices with larger dimensions carry a higher number of defects. Moreover, the impact of defects on the  $V_{th}$  (the  $\Delta V_{th}$  of every defect) is again taken randomly from an exponential distribution with a mean value of  $\eta = \frac{\eta_{p,n}wl}{L_G W_G}$  where w and l are scaling factors of the dimensions of the device and p,n concern the type of the device [2]. The definit tool also initializes the capture probability  $P_{c0}$  and prints the time

| <b>Existing Components</b> |                                                     |  |  |

|----------------------------|-----------------------------------------------------|--|--|

| flatten                    | flattens the netlist                                |  |  |

| tzinit                     | introduces time-zero variability                    |  |  |

| definit                    | populates with defects all devices                  |  |  |

| wavapprox                  | produces a CDW signal representation                |  |  |

| propagate                  | propagates the $\alpha$ to all nodes of the netlist |  |  |

| pcestimate                 | calculates the capture probability of a defect      |  |  |

| dvfs                       | introduces dvfs technique to the simulation         |  |  |

**Table 3.1:** The components of the simulation framework

constants of every defect.

Hence, the definit tool populates with defects all the devices of the netlist while the time constants are widely distributed along the logarithmic scale. This leads to a separation of the defects according to their time scales. This separation is necessary because in this simulation framework not all defects can be accurately simulated. Specifically, the  $P_c$  of the defects with time constants comparable to the bit stream's period  $1/f_{avg}$  cannot be estimated by the CDW simulation [8]. Thus, they constitute the first team of defects called "fast" defects. Simulating the BTI degradation imposed by the group of "fast" defects is out of the scope of this thesis because significant work on this matter already exists [14], [30], [31]. Defects with time constants much higher than the ones mentioned earlier are accurately modeled with the proposed flow and compose the second team of the defects, named "slow" defects [8].

- It must be noted that dynamic voltage scaling (dvfs) is a widely-used technique for mitigating the BTI-induced degradation on ICs. Therefore, a dvfs tool that changes the bias conditions of the netlist throughout the simulation is also necessary.

- BTI simulation is workload dependent, meaning that the signal activity -the workload- of every gate of a device has to be evaluated. In other words, propagating the CDW signal activity, or the duty factor more specifically, (as frequency and time duration remain constant throughout the circuit) from all primitive nodes to every gate node of the netlist is necessary. The propagate tool is used in this simulation framework for this work and the accuracy of this tool will be examined.

## 3.3 SPICE-free Signal Activity Propagation

As stated earlier, the propagate tool can calculate the duty factors of all the internal nodes of a netlist, given only the  $\alpha$  of the primitive nodes. It is important to note that the algorithm of this tool is based on estimating the duty factor on the device level while other tools calculate the signal probability at the gate level. According to the algorithm of this tool, the devices of the netlist are checked and depending on the signal activity of the gate node, the  $\alpha$  is propagated between the connections of source and drain. In case there is no signal activity in the gate node and the duty factor equals 0, then the device works as an open switch that does not propagate the signal between the connections of source

and drain. The respective algorithm has been presented thoroughly in previous work [27], hence only extensions and optimizations will be discussed in the current thesis.

For this simulation framework, an extension of this tool is suggested. The improved algorithm checks if all the devices are part of a transmission-gate, that has both source nodes of the complementary devices on the one side and the drain nodes of the two devices on the other. After scanning all the transistors of the netlist and a PMOS device is found to share the same drain and the same source with an NMOS, then these devices are considered to compose a transmission-gate. Hence, in this optimized version of the tool, devices that are found to compose a transmission-gate have a different signal activity propagation profile, as can be seen in Figure 3.1.

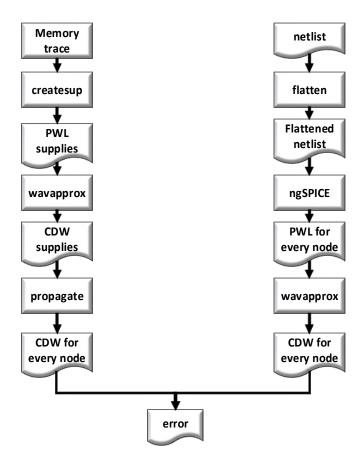

Figure 3.1: Flowchart showing the algorithm of the extension of the propagate tool

In order to achieve that, the algorithm checks the gate voltage of the devices that are part of a transmission-gate. In case the device is a PMOS, and the duty factor is below the limit of 0.95, the transistor is considered to propagate the voltage activity (meaning the duty factor  $\alpha$ ) from its source to its drain. If the value is greater than this limit, the NMOS device of the same transmission-gate is examined. In case the duty factor of the gate node of the NMOS is greater than the threshold of 0.05 then the drain of the transistor is set equal to the source's  $\alpha$ . In any other case, the transmission-gate is on the off-state. Then, there is no propagation of the signal from the one connection of the transmission-gate to the other. This simple extension of the original propagate algorithm is expected to capture the operation of a transmission-gate, thus provides more accurate results than the original version of the tool.

So as to verify the effectiveness of the extended version of the tool, the  $\alpha$  of every node of a memory netlist is estimated and is compared to the CDW representation derived from the transient waveform

of the same node. Hence, the absolute error between the duty factors estimated by the newer version of propagate and the duty factors calculated by a SPICE simulation can be defined as:

$$\epsilon_1 = |\alpha_{\text{propagate}} - \alpha_{SPICE}|$$

(3.2)

It has to be noticed that, in other BTI-related simulation frameworks, the duty factor of all internal nodes is considered fixed to a constant value [28], [32]. Specifically, we find that "a safe and tight upper bound for circuit delay degradation under worst-case signal probabilities is required for reliable operation. In most practical cases, it can be obtained by assuming WC- $K_{\rm aging}$  of 0.95 for the entire circuit" where  $K_{\rm aging}$  is "a scalar from the interval (0, 1), a function of stress probability" [28]. Taking into consideration that the atomistic model is workload dependent, it is expected that such a hypothesis may be oversimplified and could lead to pessimistic results when simulating large inventories consisting of numerous internal nodes. Hence, the efficacy of the propagate tool and its advantages over such plain estimations need to be tested. Therefore, the hypothesis of a fixed value at 0.95 is also explored while the absolute error in this occasion is defined as:

$$\epsilon_2 = |\alpha_{0.95} - \alpha_{SPICE}| \tag{3.3}$$

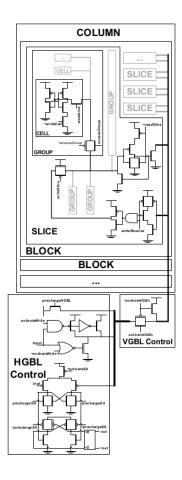

The netlist that will be used for this task, is a subset of an embedded Static Random Access Memory (SRAM) [4] that is shown in Figure 3.2.

Figure 3.2: Operational path of an embedded SRAM design as presented in [4]

First, from a createsup tool a memory trace is created that contains piece-wise linear waveforms of all primary nodes of the netlist. Every memory trace is set to contain the waveforms of the primary nodes for a series of 20 equiprobable operations: the writing of 0 in the memory bit, the writing of 1, the reading of the memory bit and the retaining operation that simply retains the stored bit. By default, the memory trace always starts with the writing of the 0 value in the SRAM cell. Then the rest operations of the memory cell, that will create a single memory trace, are selected randomly.

After the piece-wise linear waveforms (PWL) of the primary nodes of the netlist are created, the wavapprox tool is used in order to calculate the duty factors for each of these nodes according to their PWL waveform. A CDW representation of the primary nodes is then available with every waveform being represented by a single CDW point. In order to achieve that, the wavapprox tool is set to present the crudest approximation of every signal with  $\epsilon_f \to +\infty$  and  $\epsilon_\alpha = 1$ , thus the duty factor of every node is averaged out from the entire signal duration.

Figure 3.3: Logic diagram for propagate verification

Next, the duty factors of the primary nodes are propagated by using the propagate tool and the  $\alpha$  of every internal node is estimated. Thus, a file containing the CDW points of all nodes is created. By using the same memory trace and the initial PWL waveforms, a SPICE simulation is completed that calculates the transient waveform of all nodes of the netlist and creates a file for each node. It is generally assumed that a SPICE simulation provides a precise estimation of the signal waveform of all nodes.

After the calculation of the PWL waveforms of all nodes, the wavapprox tool is used and the CDW points of all nodes derive. Hence, the propagated duty factors estimated in the first case are compared against the duty factors calculated in the second case by the SPICE simulations and the absolute errors of all nodes of the netlist, defined in Equation 3.2, are estimated.

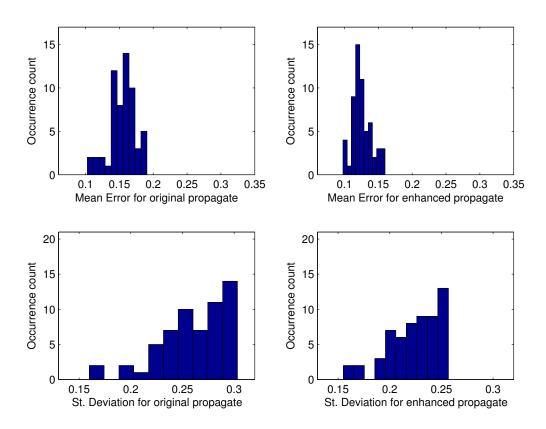

Following the verification flowchart presented in Figure 3.3 the histograms of the mean value and standard deviation of the absolute errors defined in the Equation 3.2 for 60 memory traces derive. First the accuracy of the extended and the original version of the propagate tool are compared and the histograms of the errors for the same 60 memory traces are shown in Figure 3.4.

**Figure 3.4:** Histograms of mean error and st. deviation comparing the original and the extended version of the tool

As it can be seen, the absolute error in the case of the extended version of the tool is less, both in terms of mean value and standard deviation. Therefore, the extended algorithm enhances the original propagate algorithm to provide more accurate estimations. This can be explained by the fact that transmission-gates are fundamental components of an SRAM path thus, by capturing the operation of transmission-gates the accuracy of this SPICE-free signal activity propagation tool is improved.

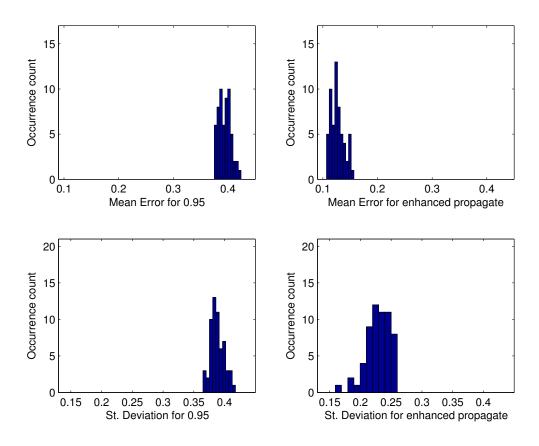

Next, another 60 memory traces are created and the duty factors of all internal nodes of the circuit are estimated by the enhanced tool. After the absolute errors are calculated, the efficiency of the tool is tested against the hypothesis of a fixed duty factor at 0.95. For the former case the absolute errors are estimated from the Equation 3.2 while for the latter, the absolute errors are calculated from 3.3. The histograms of the mean value and of the standard deviation of the absolute errors are shown in Figure 3.5.

**Figure 3.5:** Histograms of mean error and st. deviation comparing the 0.95 hypothesis to the extended propagate algorithm

From the graphs of Figure 3.5, it is clear that estimating duty factors by this propagation tool is a more accurate evaluation than the plain hypothesis of  $\alpha=0.95$  for all nodes. In fact, for realistic workload scenarios of the SRAM path, the mean absolute error is nearly tripled in the case of a fixed duty factor at 0.95. This indicates that a fixed duty factor to 0.95 for all nodes, in order to account for the worst-case scenario, is unrealistic and rather pessimistic. Thus, such a hypothesis can lead to overestimations of the BTI-induced degradation.

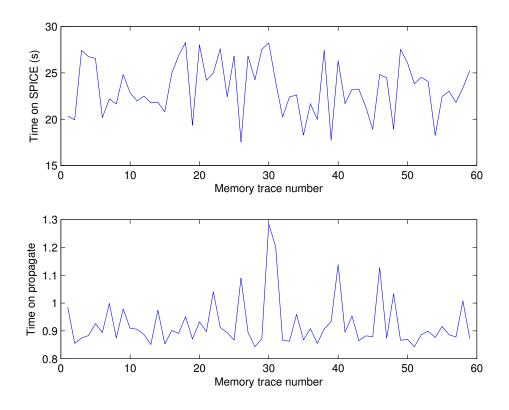

The efficiency of the propagate tool must also be noticed. Obviously, the hypothesis of a constant duty factor for all the nodes of a netlist does not require any computation time, but, as previously demonstrated, is inferior to the estimations of any systematic activity propagation scheme, either using SPICE or the proposed propagate tool. A complete SPICE simulation can provide more accurate results however, when large netlists are simulated and for long-lasting simulations, the use of SPICE is computationally prohibitive. Figure 3.6 shows the CPU time needed for the propagate estimation compared to the CPU time needed for the SPICE simulation. For the 60 memory traces tested, the mean time on the first case with the propagate tool is 0.9 s, while for the SPICE simulator, the mean CPU time equals 23.3 s. Hence, the huge gain in computation time is obvious when using the proposed propagate tool.

Figure 3.6: Difference in CPU time for SPICE simulation and for propagate

## 3.4 Combining Existing Tools to a Yield Analysis Tool

After presenting the existing tools and the proposed optimizations, we now combine them into a single framework for yield estimation. The yield of the same netlist (shown in Figure 3.2) used for the verification of the propagate tool will be estimated. This circuit contains 63 devices and it supports reading and writing of the cell. A sample of this design is defined as functionally correct if a zero value can be written and then read successfully. 150 Monte Carlo iterations will be simulated with an inspected lifetime of approximately 3 years, which will be split in time intervals. These time windows will be equal and will last  $2.5 \times 10^7$  seconds. The temperature will be constant at 50 ° C while it will be assumed that the test-case circuit operates at a frequency f = 0.88 GHz.

Firstly, the flattening tool is used in order to print all 63 devices from the subcircuits of the netlist. Then, with the flattened netlist available,  $\Delta V_{th0}$  variability is estimated via the tzinit tool. Hence, a time-zero component of  $\Delta V_{th0}$  is added to the threshold voltage of the devices that is constant through the device lifetime but varies across the set of the devices. The threshold shift is added to each device of the flattened netlist through the command [29]: **delvto**=  $\Delta V_{th}$ . The  $\Delta V_{th0}$  follows the Gaussian distribution which is different for the pFETs and the nFETs.

An initial file of voltage supplies for the SPICE simulation is created. Then, the definit tool is used, populating every device with defects. Always according to same atomistic approach [8], the time constants are distributed over a logarithmic scale, between a maximum and a minimum value. As mentioned earlier, defects with time constants comparable to the bit stream's period  $1/f_{avg}$  constitute the group of "fast" defects and are not taken into consideration in this thesis. Also, for the Monte-Carlo

| Variables for the Simulation Framework                    |                                                   |  |  |

|-----------------------------------------------------------|---------------------------------------------------|--|--|

| $V_{th0}$ variability follows a Gaussian distribution     | $\mu_0 = 0.397, \sigma_0 = 0.0397 \text{ nMOS}$   |  |  |

| $V_{th0} \sim Norm (\mu_0, \sigma_0)$                     | $\mu_0 = -0.339, \sigma_0 = 0.0339 \text{ pMOS}$  |  |  |

| Number of Defects is taken from a Poisson                 | $N_{ot} = 1e + 11 \text{ pMOS}$                   |  |  |

| distribution with mean $N=N_{ot}WL$                       | $N_{ot} = 6.7e + 10 \text{ nMOS}$                 |  |  |

| Time constants are chosen from a logarithmic distribution | $	au_{range} = 10^{24}, 	au_{min} = 10^{-12}$     |  |  |

| $V_{th,TD}$ follows an exponential distribution with      | $\eta_{p,n} = 5e - 3 \text{ V}$                   |  |  |

| mean $\eta = rac{\eta_{p,n}wl}{W_GL_G}$                  | $w \times l = 90 \text{ nm} \times 70 \text{ nm}$ |  |  |

**Table 3.2:** Variables for the Simulation Framework

iterations, the definit tool sets the  $P_{c0}$  to 0.

After a transient simulation of the netlist takes place, testing the delay (between the writing and reading of the SRAM cell), imposed by  $V_{th0}$  variability, the initial source supplies created by the  $\mathtt{dvfs}$  tool are propagated for a defined time-interval to all internal nodes of the circuit. Now that the duty factors, frequency and time duration (which equals the specific time interval) of all the gate nodes of the circuit are identified with a CDW representation of a waveform, the workload of every device is known and via the pcestimate tool the capture probability of every single defect of all devices can be estimated. The equation of  $P_c$  is a function of the workload of the device, the time constants and the previous value of  $P_c$ .

- A stride tool is created that compares the value of  $P_c$ , calculated by pcestimate, with a number r. This number is chosen randomly from the (0, 1) space. Iff  $r < P_c$  then the defect is considered occupied. For every defect a new value of r is drawn from the (0, 1) interval. All defects for every device are elaborated and if occupied their state is set to 1 and if unoccupied the state is 0.

- A tool named aging is also created that checks the state of all defects. Iff the state value equals 1, the  $\Delta V_{th}$  of the defect is added to the total threshold shift of the device through the **delvto** command [29]. After the aging tool is finished, the aged netlist is created with every device having a  $\Delta V_{th}$  depending on its occupied defects as claimed by the atomistic theory. This instance of the netlist is again simulated and the delay between the two functions of the circuit is measured.

The sources are propagated for the remaining time intervals until the end of the inspected lifetime. At each time step, following the process demonstrated earlier, the aged netlists are created and then simulated. If a zero value cannot be written and read successfully, the instance is considered as functionally erroneous.

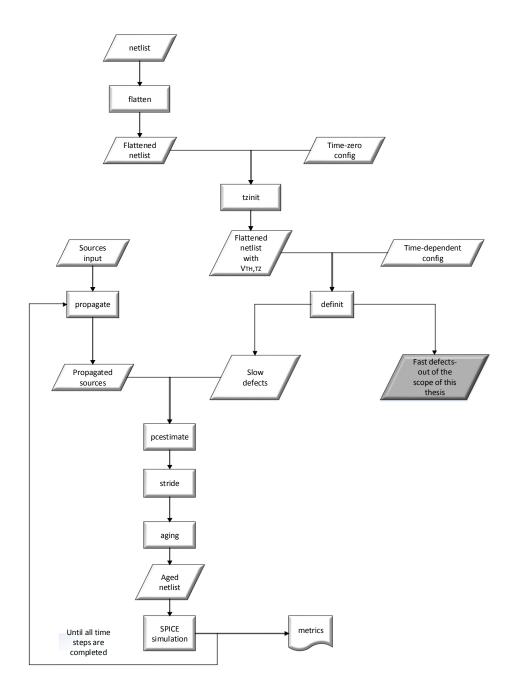

The procedure elaborated in this Section is placed in a loop, simulating a number of 150 samples that constitute a set of Monte Carlo iterations. At each time step, the functional yield of the circuit can be estimated by dividing the number of the circuits that did not fail at that specific time step, to the number of the samples tested. The flowchart for a single iteration of the proposed simulation framework is shown in Figure 3.7.

Figure 3.7: Flowchart for a single iteration of the proposed simulation framework

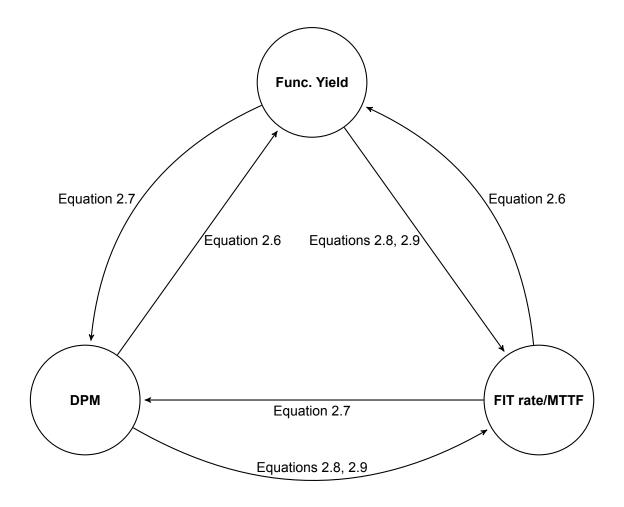

#### 3.5 Yield vs. DPM vs FIT/MTTF

The estimation of the functional yield is rather straightforward. When a failure appears during the simulations, then the respective sample is added to the functional violations. At the end, the functional yield of the circuit can be estimated by dividing the number of circuits that did not fail, to the set of the samples. The number of functionally acceptable circuits is simply the number of samples simulated minus the failed circuits. Hence, the functional yield is estimated by Equation 2.6. Also, considering the definition of defects per million, DPM is estimated by Equation 2.7.

Figure 3.8: Diagram showing the interdependability of Functional Yield, DPM, FIT rate and MTTF

In order to estimate the MTTF and FIT rate, some mathematical transformations need to follow. Firstly, the point of MTTF (in hours) is calculated by 2.8 of the previous Chapter. In this Equation, the Device Hours represent the equivalent device hours of the test procedure, which in the case of elevated test temperatures are estimated by [21]:

$$EDH = A \times CDH \tag{3.4}$$

A is the *acceleration factor* and is given by Equation 2.11 and CDH represents the cumulative device hours and can be calculated by [21]:

$$CDH = Number of Devices Tested \times Test time (in hours)$$

(3.5)

After the MTTF estimation, the point of FIT rate can be estimated from the Equation 2.9

It must be noted that the FIT rate and the MTTF estimations depend on the number of failures that occurred during the test procedure and on the cumulative device hours. As can be seen from Equation 3.5 longer time tests require fewer testing samples. On the contrary, if simulations for long time windows are infeasible or computationally prohibitive, then in order to calculate these metrics a large number of devices needs to be tested.

## 3.6 Conclusion

This Chapter discussed a simulation framework that is capable of capturing BTI degradation in large inventories and for long time spans. First, the existing tools that compose this framework were briefly reviewed. The tzinit that introduces  $V_{th0}$  variability in the simulation, the definit tool, that populates every device with defects, the wavapprox tool that compresses the signal representation and the propagate tool, that estimates the duty factor of all internal nodes of the netlist, are the most significant.

Then, a verification of the accuracy and the efficiency of the propagate tool were demonstrated. Specifically, the duty factors estimated by this tool were compared against the duty factors calculated by a SPICE simulation for a number of 60 iterations of a netlist. The netlist that was used, is a representative path of an embedded SRAM. Each iteration consisted of 20 operations of the netlist and the results showed that, indeed, the propagation algorithm constitutes an efficient and accurate tool for an overall estimation of the duty factors of all nodes of a circuit for long time spans, in which a SPICE simulation is computationally prohibitive.

Afterwards, the synthesizing of the simulation framework from its components was presented along with the constants that will be used for the simulations. These constants concern the mean and sigma values for Gaussian distributions, the defect densities for P-MOS and N-MOS transistors and constants that regard time scales. Finally, the inter-dependability between MTTF, FIT rate, DPM and functional yield was described and a unified formulation connected these reliability metrics.

# **CHAPTER 4**

# **Quantitative Results**

## 4.1 Introduction

This Chapter presents the quantitative results that regard the monitoring of the BTI-induced degradation over the circuit's lifetime. The time inspection will last approximately 3 years ( $10^8$  seconds) while the netlist simulated is a part of an embedded Static Random Access Memory (SRAM), as shown in Figure 3.2. The simulation framework was presented in the previous Chapter, along with the mathematical forms that connect the reliability metrics .