# National Technical University of Athens

# School of Electrical and Computer Engineering

DIVISION OF INFORMATICS AND COMPUTER TECHNOLOGY

# Development of a Layout-based Tool for the evaluation of an RTL Laser Fault Model

DIPLOMA THESIS

MARIOS TAMPAS

Supervisor: Kiamal Pekmestzi

Professor of NTUA

Athens, October 2014

The thesis took place at the LCIS laboratory of Grenoble INP

ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ

# Development of a Layout-based Tool for the evaluation of an RTL Laser Fault Model

# ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

του

Μάριου Τάμπα

Επιβλέπων : Κιαμάλ Πεκμεστζή

Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 30<sup>η</sup> Οκτωβρίου 2014.

| (Υπογραφή)       | (Υπογραφή)           | (Υπογραφή)               |  |

|------------------|----------------------|--------------------------|--|

|                  |                      |                          |  |

| Κιαμάλ Πεκμεστζή | Δημήτριος Σούντρης   | Πέτρος-Παύλος Σωτηριάδης |  |

| Καθηγητής Ε.Μ.Π. | Επ. Καθηγητής Ε.Μ.Π. | Επ. Καθηγητής Ε.Μ.Π.     |  |

Αθήνα, Οκτώβριος 2014

(Signature)

.....

# ΤΑΜΠΑΣ ΜΑΡΙΟΣ

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

The thesis took place at the LCIS laboratory (Laboratoire de Conception et d'Intégration des Systèmes)

Supervisors at the LCIS:

Athanasios Papadimitriou: athanasios.papadimitriou@lcis.grenoble-inp.fr

Vincent Beroulle: Vincent.beroulle@esisar.grenoble-inp.fr

David Hély: david.hely@lcis.grenoble-inp.fr

University Grenoble Alpes, LCIS 26000 Valence FRANCE

Copyright © Τάμπας Μάριος, Παπαδημητρίου Αθανάσιος, Hély David, Beroulle Vincent, 2014

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ' ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τους κατόχους των πνευματικών δικαιωμάτων.

# Abstract

Nowadays, digital integrated circuits (ICs) are found in all electronic devices and computer systems. Security and resilience of ICs is a modern subject that concerns scientists and hardware engineers. IC designers have recognized the importance of incorporating fault tolerance into microelectronic devices. In order to develop proper countermeasures for the security and the normal functionality of ICs, it is imperative to study the impact of attacks against circuits. Even further, study at the early stages of IC manufacture is mainly taken into consideration. There are different kinds of malicious attacks against ICs, cryptographic or not, such as hardware or physical attacks, as well as cryptanalytic attacks against the cryptographic algorithms. IC piracy using laser beam is the latest and most commonly applied by hardware hackers, who aim to extract information from secure ICs. Most of the times the aim of the hackers is to turn against chips that contain cryptographic algorithms, because those are the ones that hold the valuable data in encrypted form.

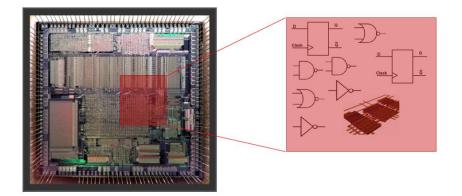

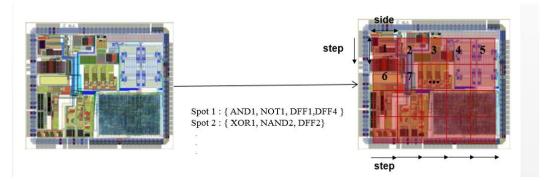

The object of the internship is divided in two parts. The first part includes the development of a layout extraction platform in order to model localized attacks on the layout of integrated circuits. Using OpenAccess<sup>TM</sup>, an EDA tool provided by Si2 (Silicon Integration Initiative) that allows the interface with IC designs, we were able to design the extraction tool, study the logic components that lie underneath specific areas of the layouts (potential laser spots) and check their significance on the functionality of the ICs. Next and principal task of the internship is the validation of an RTL laser fault methodology, already proposed in the article [1]. In this thesis, this methodology is explained in details. During the internship, long time and effort was dedicated for the validation of this methodology node of 45nm. Several localized attacks on the layout were studied thoroughly in order to examine if such kind of attacks could be predicted from the RTL, the early and abstract stage of IC manufacture which models digital systems. In this way, we get a concept of the most critical logic components to be hit during a realistic laser attack.

The internship took place in the Laboratory of Design and System Integration, LCIS (Laboratoire de Conception et d'Intégration des Systèmes), which is located in the city Valence of France. LCIS is one of the 21 research labs of the Grenoble Institute of Technology and its research activities are oriented towards the specification, modeling, design, communication, validation, diagnosis and security of integrated circuits, embedded and communication systems. This work is considered a part of the global project LIESSE (Laser-Induced fault Effects in Security-dedicated circuitS). Among others, the goal of this project is to study and model the effects of laser shots onto submicronic circuits and provide efficient tools to prevent such laser attacks.

#### Keywords

Hardware Security, Cryptography, AES, Fault Injection, OpenAccess, Integrated Circuits, Layout, Laser attacks, Fault Model, Validation

# Περίληψη

Στις μέρες μας, ψηφιακά μικροηλεκτρονικά κυκλώματα συναντώνται σε όλες τις ηλεκτρονικές συσκευές και σε συστήματα υπολογιστών. Η ασφάλεια και ανθεκτικότητα των ψηφιακών ολοκληρωμένων κυκλωμάτων (ΟΚ) συνιστά σύγχρονο θέμα που απασχολεί επιστήμονές και μηγανικούς hardware. Σχεδιαστές των ΟΚ έχουν αναγνωρίσει τη σημασία ενσωμάτωσης μηγανισμών ανογής σφαλμάτων στις μικροηλεκτρονικές διατάξεις. Προκειμένου να σχεδιαστούν κατάλληλα αντίμμετρα που θα συμβάλλουν στην ασφάλεια και ομαλή λειτουργία των ΟΚ, θεωρείται επιτακτική ανάγκη η μελέτη της επίδρασης κακόβουλων επιθέσεων εις βάρος τέτοιων κυκλωμάτων. Ακόμη περισσότερο, μελέτη στα πρώιμα στάδια κατασκευής ΟΚ πρέπει να ληφθεί υπ'όψιν. Υπάρχουν διάφοροι τύποι κακόβουλων επιθέσεων ενάντια OK, είτε κρυπτογραφικών είτε όχι, όπως physical επιθέσεις ή επιθέσεις υλικού, καθώς επίσης και κρυπτογραφικές (μαθηματικές) επιθέσεις εις βάρος των κρυπτογραφικών αλγορίθμων. Ειδικά, η «πειρατεία» των ΟΚ χρησιμοποιώντας λέιζερ ακτινοβολία συνιστά την πιο σύγχρονη και εφαρμόσιμη τεχνική επίθεσης, αποσκοπώντας στην υποκλοπή απόρρητης πληροφορίας από τα ασφαλή OK. Στις περισσότερες των περιπτώσεων ο στόχος των hardware hackers είναι να «σπάσουν» το κλειδί των κρυπτογραφικών υλοποιήσεων στα ΟΚ, καθώς τέτοιου είδους κυκλώματα προστατεύουν πολύτιμη πληροφορία σε κρυπτογραφημένη μορφή.

Το αντικείμενο που πραγματεύτηκε η Πρακτική, και κατ' επέκταση το κείμενο της Διπλωματικής αυτής, μπορεί να χωριστεί σε δύο σκέλη. Το πρώτο σκέλος περιελάμβανε την ανάπτυξη μιας Πλατφόρμας Εξόρυξης Στοιχείων του Layout OK με σκοπό τη μοντελοποίηση της τοπικής επίδρασης επιθέσεων στο Layout των OK. Χρησιμοποιώντας το OpenAccess<sup>TM</sup>, ένα EDA λογισμικό που παρέγεται από την Si2 (Silicon Integration Initiative) και επιτρέπει τη διεπαφή με την επιφάνεια ΟΚ, είχαμε τη δυνατότητα να σχεδιάσουμε την πλατφόρμα αυτή και να μελετήσουμε τα εξαρτήματα – συστατικά των Layout σε καθορισμένα σημεία (πιθανές περιοχές του Layout υπό λείζερ επίθεση), καθώς επίσης να μελετήσουμε τη συμβολή των στοιχείων αυτών στη λειτουργικότητα των ΟΚ. Επόμενο και κρίσιμο έργο της πρακτικής εργασίας ήταν η επικύρωση ενός RTL Λέιζερ Μοντέλου Σφαλμάτων. Το μοντέλο έχει ήδη δημοσιευθεί στο άρθρο [1]. Στα πλαίσια αυτής της Διπλωματικής, το μοντέλο περιγράφεται με λεπτομέρεια. Συνοπτικά, πραγματεύεται την μοντελοποίηση επιθέσεων λέιζερ στο RTL επίπεδο των ΟΚ. Στη διάρκεια της Πρακτικής, αρκετός χρόνος και ενασχόληση αφιερώθηκαν στην επικύρωση της μεθοδολογίας στα Layout, όχι μόνο κρυπτογραφικών AES υποκυκλωμάτων αλλά και κυκλωμάτων αναφοράς (benchmarks) με τεχνολογία υλοποίησης 45nm. Πολλαπλά σενάρια τοπικών επιθέσεων στο Layout (χρησιμοποιώντας προσέγγιση λέιζερ επίθεσης) μελετήθηκαν διεξοδικά προκειμένου να εξετάσουμε αν τέτοιες τοπικές επιθέσεις θα μπορούσαν να έχουν εκτιμηθεί και προβλεφθεί ήδη από το RTL, το πρώιμο και αφηρημένο στάδιο υλοποίησης ΟΚ που περιγράφει τα ψηφιακά συστήματα. Με αυτό τον τρόπο, μπορέσαμε να λάβουμε επίγνωση των πιο κρίσιμων στοιγείων στο Layout που κινδυνεύουν να γτυπηθούν από μια ρεαλιστική επίθεση με λέιζερ.

Η πρακτική έλαβε μέρος στο Εργαστήριο Σχεδιασμού και Υλοποίησης Συστημάτων (Laboratoire de Conception et d'Intégration des Systèmes LCIS), το οποίο βρίσκεται στην πόλη Valence της Γαλλίας. Το LCIS είναι ένα από τα 21 σύγχρονα τεχνολογικά ερευνητικά εργαστήρια του Πανεπιστημίου της Grenoble και οι ερευνητικές του δραστηριότητες προσανατολίζονται στη μοντελοποίηση, ανάπτυξη προδιαγραφών, σχεδιασμό, επικοινωνία, επικύρωση, διάγνωση και ασφάλεια OK, ενσωματωμένων συστημάτων και συστημάτων επικοινωνίας. Η πραγματοποιηθείσα εργασία θεωρείται μέρος του παγκόσμιου project LIESSE (Laser-Induced fault Effects in Security-dedicated circuitS). Μεταξύ άλλων, σκοπός του project αυτού είναι η μελέτη και μοντελοποίηση της επίδρασης επιθέσεων λέιζερ σε μικροηλεκτρονικά κυκλώματα, καθώς επίσης η ανάπτυξη αποτελεσματικών εργαλείων για την αντιμετώπιση τέτοιων επιθέσεων.

# Λέξεις – Κλειδιά

Ασφάλεια Υλικού, Κρυπτογραφία, AES, Εισαγωγή σφαλμάτων, OpenAccess, Ολοκληρωμένο Κύκλωμα, Layout, Επίθεση με λέιζερ, Επικύρωση μοντέλου σφαλμάτων

# Content

| 1. | Introduction1                                               |                                                 |     |  |  |  |

|----|-------------------------------------------------------------|-------------------------------------------------|-----|--|--|--|

|    | 1.1 Motivation                                              |                                                 |     |  |  |  |

|    | 1.2 Scope                                                   | of the internship                               | 2   |  |  |  |

|    | 1.2.1                                                       | Development of Layout Extraction Tool           | 2   |  |  |  |

|    | 1.2.2                                                       | Validation of Methodology                       | 2   |  |  |  |

|    | 1.3 Organ                                                   | ization                                         | 3   |  |  |  |

|    |                                                             |                                                 |     |  |  |  |

| 2. | Hardwar                                                     | e Security                                      | 5   |  |  |  |

|    | 2.1 Introduction                                            |                                                 |     |  |  |  |

|    | 2.2 Differ                                                  | ent Attacks on Cryptographic Hardware           | 6   |  |  |  |

|    | 2.2.1                                                       | Side-channel Attacks                            | 8   |  |  |  |

|    | 2.2.2                                                       | Microprobing                                    | 9   |  |  |  |

|    | 2.2.3                                                       | Reverse Engineering                             | 9   |  |  |  |

|    | 2.2.4                                                       | Fault Attack                                    | .10 |  |  |  |

|    | 2.3 Fault                                                   | Attack Techniques                               | 10  |  |  |  |

|    | 2.3.1                                                       | Voltage/Clock Fault Attack                      | .11 |  |  |  |

|    | 2.3.2                                                       | Temperature Fault Attack                        | 12  |  |  |  |

|    | 2.3.3                                                       | Electromagnetic Fault Attack                    | .12 |  |  |  |

|    | 2.3.4                                                       | Optical Fault Attack                            | 13  |  |  |  |

|    | 2.4 Fault Attacks on the Advanced Encryption Standard AES14 |                                                 |     |  |  |  |

|    | 2.4.1                                                       | The Advanced Encryption Standard (AES)          | 14  |  |  |  |

|    | 2.4.2                                                       | Different Methods of Fault Attacks on the AES   | 18  |  |  |  |

|    | 2.5 Fault                                                   | Injection for validating robustness of a design | 20  |  |  |  |

|    |                                                             |                                                 |     |  |  |  |

| 3. | Fault Mo                                                    | deling and Fault Injection Methodologies        | 23  |  |  |  |

|    | 3.1 Definition of Fault                                     |                                                 | .23 |  |  |  |

|    | 3.2 Different types of Faults                               |                                                 | 23  |  |  |  |

|    | 3.2.1                                                       | Permanent Faults                                | .24 |  |  |  |

|    | 3.2.2                                                       | Destructive Faults                              | 24  |  |  |  |

|    | 3.3 Definition of Fault Model24                             |                                                 |     |  |  |  |

|    | 3.4 Different Fault Models25                                |                                                 |     |  |  |  |

|    | 3.5 Fault Modeling at RTL and Gate Level                    |                                                 |     |  |  |  |

| 4. | State-of-the            | e-art Laser Fault Modeling at RTL              | 29 |

|----|-------------------------|------------------------------------------------|----|

|    | 4.1 General             | 29                                             |    |

|    | 4.2 Cone partitioning   |                                                |    |

|    | 4.2.1 I                 | Definition of Logic Cone                       |    |

|    | 4.2.2 F                 | Fault types                                    |    |

|    | 4.2.3 I                 | _ocality Approach                              | 31 |

|    | 4.2.4 A                 | Assumptions                                    | 31 |

|    | 4.3 Limitatio           | ons of the Method                              |    |

| 5. | Layout Ext              | raction Tool using OpenAccess <sup>TM</sup>    | 35 |

|    |                         | W                                              |    |

|    | 5.1.1 7                 | Franslation Flow – Layout Import               |    |

|    |                         | Design of Layout Extraction Tool – C++ Classes |    |

|    | 5.2 Spot Par            | titioning Attributes                           | 45 |

|    | 5.3 Glade <sup>TM</sup> | - Layout Viewer                                | 48 |

| 6. | Validation 2            | Methodology                                    | 51 |

|    | 6.1 Validatio           | on Flow                                        | 51 |

|    | 6.2 Gate Lev            | vel Cones and Intersection Sets                | 52 |

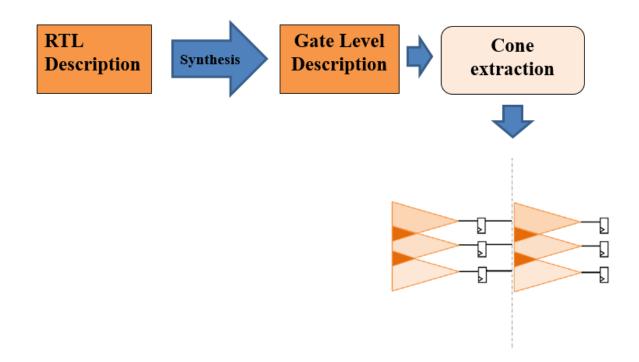

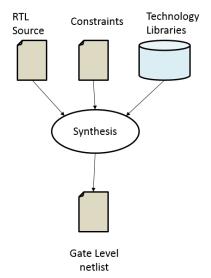

|    | 6.2.1                   | Synthesis – From RTL to Gate Level Description | 53 |

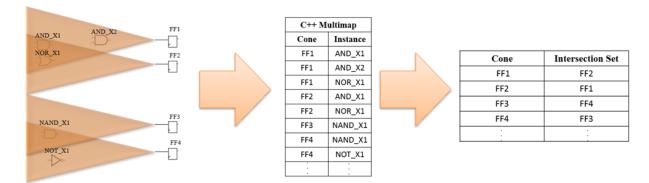

|    | 6.2.2                   | 2 Extraction of Gate Cones and Sets            | 54 |

|    | 6.3 Virtual S           | Spot Sets on the Layout                        | 55 |

| 7. | Validation              | Results                                        | 57 |

|    | 7.1 AES Mo              | orph                                           |    |

|    |                         | rity                                           |    |

|    |                         | Benchmark B17                                  |    |

|    | 7.4 ITC-99              | Benchmark B18                                  | 73 |

| 8. | Conclusion              |                                                | 77 |

# Acknowledgments

First, I would like to thank my professor from NTUA, Mr. Kiamal Pekmestzi, who supported my decision to do the internship in Valence. Moreover, I want to express my thanks to my supervisor in LCIS and PhD student of University of Grenoble, Mr. Athanasios Papadimitriou, for his advice, comments, practical indications and his patience during my internship in the Laboratory. In addition, I would like to express my gratitude towards the professors of University of Grenoble, Mr. David Hély and Mr. Vincent Beroulle for their guidance and their willingness to assist in my work and provide with corrections and advices during the whole period of my internship. Finally, I would like to thank my family for their unwavering support on me.

# **Chapter 1: Introduction**

# **1.1 Motivation**

Nowadays, security on digital integrated circuits (IC) is an extremely important subject, since ICs are involved in many critical aspects of our lives. Digital ICs can be found in many common electronic devices, such as cell phones, computer systems or smart-cards, credit cards, pay-per-view TV, etc. Security algorithms are implemented in order to ensure appropriate functionality of the circuits, however those algorithms often turn out to be inefficient. Hostile intrusions against secure ICs have been developed alongside the growth of silicon technology, enabling adversaries to unfold their malicious intentions. Especially, laser proves to be one of the most efficient and controllable means of attack. Scientists have concluded that innovative, proper kinds of countermeasures must be introduced, as current state-of-the-art countermeasure tools prove to be incapable of preventing several attacks.

Designing a secure integrated circuit requires implementing protection against malicious threats. The design and integration of efficient countermeasures depend on the methods available for an early validation in the design process. Study and analysis at an early level of abstraction, such as the Register Transfer Level (RTL), can provide the means to efficiently expose any vulnerabilities of security oriented circuit designs, and contribute to the implementation of both defensive and preventive mechanisms. At the same time, RTL analysis can lead to the enhancement of the design flow with the capability to avoid costly feedback runs [1].

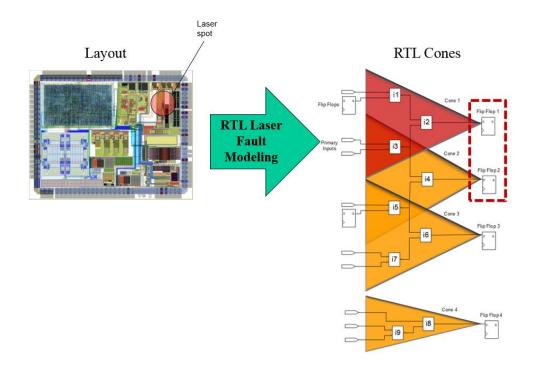

This work focuses on the development of a tool for the validation of a fault methodology applied at the RTL. The methodology is based on the partitioning of the elaborated RTL net-list (RTL logic circuit) and attempts to model the locality of laser attacks at RTL of digital ICs, either cryptographic or not. Several assumptions concerning the manifestation of faults are implied within the method. The main objective is to prove that the study of early stage of abstraction in circuit design flow, Register Transfer Level, can prove an effective source of information concerning the prediction of localized IC attacks. This information can ultimately contribute to the evaluation of new countermeasures against laser attacks.

# **1.2 Scope of the Internship**

#### **1.2.1 Development of Layout Extraction Tool**

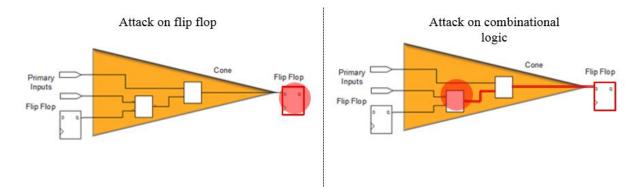

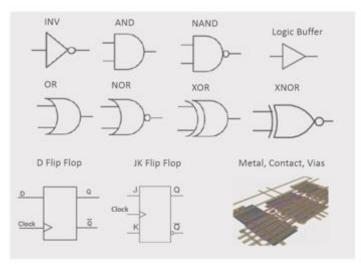

The scope of the internship and of this thesis, in extension, is twofold. The first part of the scope is the development of a layout extraction platform that is used in order to validate the RTL laser fault injection methodology, already published in the literature [1]. The platform is designed based on OpenAccess<sup>TM</sup>, a well-known C++ API, that targets to enable and facilitate the interface with IC design database. Using the layout extraction platform, we have the capability to inspect potential localized attacks on the layout and extract information from the layout. The nature of these components is either combinational logic (logic gates) or sequential logic (registers, flip flops). The ICs that we have chosen to validate include certain cryptographic implementations of the AES with different countermeasures, as well as certain benchmarks, the layout of which has been implemented with the Nangate Open-Cell process technology of 45nm.

#### 1.2.2 Validation of the Proposed Methodology

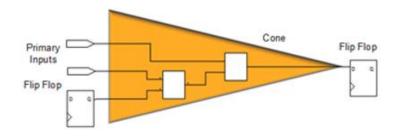

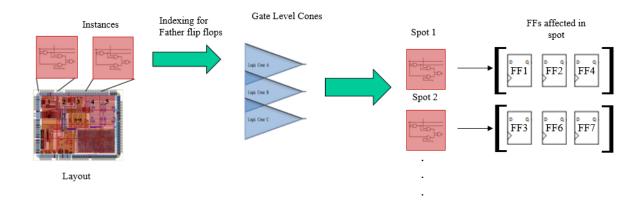

Concerning the second and most important part of the scope of internship, it is the part that deals with the validation of a fault methodology already proposed in the literature [1], concerning the modeling of laser attacks at the RTL of digital circuits. The methodology is based on Cone Partitioning, which constitutes the partitioning of the elaborated (non-optimized) net-list of an RTL description into logic cones. Briefly explained, a logic cone starts at a flip flop and ends to other flip flops or primary inputs. The last elements constitute the boundary of the expanding cone. Each cone corresponds to a single flip flop. In other words, the cone is the fan-in network of each single flip flop. For the validation, the cone of each flip flop in the RTL net-list is identified and extracted, with respect to the connectivity with its fan-in network.

Moreover, a single cone at the RT level may contain numerous elements of combinational logic. There is this scenario where many logic elements appear in more than one RTL cones, making these cones intersect with each other. By thoroughly examining, for each element of a single cone, where else it belongs to, the methodology extracts the set of RTL cones that intersect with this particular cone. In this thesis, the groups of RTL cones that intersect are referred as "RTL Intersection Sets". Each RTL Intersection Set corresponds to a single RTL cone.

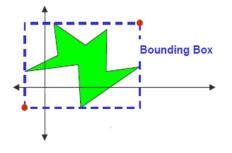

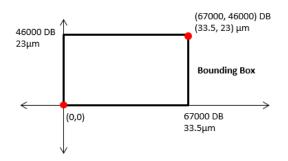

Validation flow proceeds with the extraction of multiple localized spots (bounding boxes) on the layout and their detailed examination with respect to the logic components found underneath. These spots are considered as areas on the layout affected by a potential localized attack (laser beam), an attack that injects faults to the affected components included in the area. Such attack affects either sequential logic, i.e. registers (group of flip flops) or combinational logic, i.e. gates, or both. According to the proposed methodology of [1], for a certain localized spot, faults can be modeled by their injection in flip flops. In case the spot covers combinational logic, then the faults are not stored in the combinational elements, but they are modeled at the flip flops that include the affected combinational elements in their

fan-in network. The fan-in network of each flip flop on the layout is technically another cone partitioning technique, this time not at RTL, but at the Gate Level of the design. Gate cone partitioning endorses the same functional formality as the RTL Cone technique, but this time with respect to the connectivity nets on the Gate Level net-list. Gate Level description (net-list) is the result of synthesis on the RTL net-list and it practically represents the functional relations among physical elements encountered on the layout. Ultimately, the set of flip flops affected directly or indirectly by the localized spot is extracted and stored for further analysis. The same procedure takes place for all localized spots under examination. The sets of flip flops extracted from the layout are referred as "Virtual Spot Sets", in this thesis.

Finally, the validation of the methodology is carried out by checking if the Virtual Spot Sets, extracted from several localized spots, match exactly or constitute subsets of the RTL Intersection Sets. In other words, for each Virtual Spot Set of flip flops we check if it can be found in, at least one, RTL Intersection Set. That is the main reference point for associating the early stage of RTL design with the final stage of layout implementation. When a Virtual Spot Set is contained in one or more RTL Intersection Sets, the proposed fault model succeeds and we have an estimated prediction of the consequences of a potential laser attack, already at an early phase of design. It is a valuable information that can ultimately lead to the evaluation of existing and the design of new countermeasures against laser attacks.

### **1.3 Organization**

This thesis is structured as follows. Chapter 2 gives general introductory information on hardware security, mentioning the need for cryptographic algorithms and the aspects of life where we meet secure integrated circuits. Furthermore, there is an extensive reference on attacks against secure systems, the nature of existing attacks a hacker can unleash and the impact on the semiconductor. In this thesis, what we mainly focus on is the laser attack, which is part of fault injection attacks. After presenting briefly the Advanced Encryption Standard, which is implemented in many secure systems, some examples are stated in order to show in more depth the procedure of injecting hardware faults that results in the exposure of secret key. Finally, it is stated that, nowadays fault attacks can be used as a validating and testing methodology for the resilience of hardware systems.

Chapter 3 focuses on Fault Modeling, presenting different types of faults and fault models that are used to describe the impact of IC attacks. Terminologies such as fault and fault model are explained, as well as previous fault injection techniques, in order for the reader to get an overview of the different methods used to introduce faults on integrated circuits.

Chapter 4 details on the fault methodology which our work is based on. Cone partitioning at the RTL is explained thoroughly, terms like logic cone, faults the method represents and the assumptions on which the methodology is based, are presented. Finally, some limitations on the method are stated.

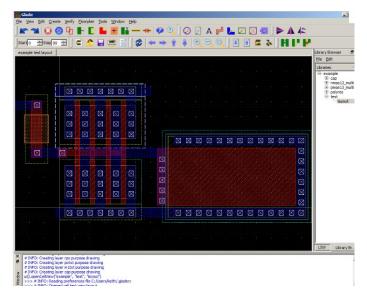

Chapter 5 presents the development of the Layout Extraction tool, which was used for the validation of the RTL fault method. The tool was designed using the OpenAccess<sup>TM</sup> C++ API. Particular coding functions and techniques for implementing the spot partitioning are explained. Finally, there is

a reference on  $Glade^{TM}$ , a layout viewer that facilitates the analysis and offers a visual perspective on the designs under test.

Chapter 6 describes the validation algorithm and the technical processes that took place for its completion. Extraction of RTL and Gate Level Intersection Sets, as well as extraction of Virtual Spot Sets is explained in detail, according always to the theory and assumptions of the RTL fault methodology.

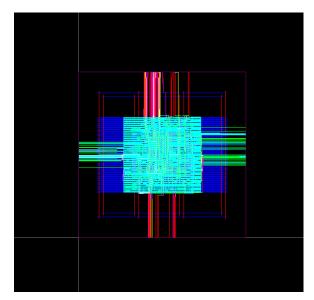

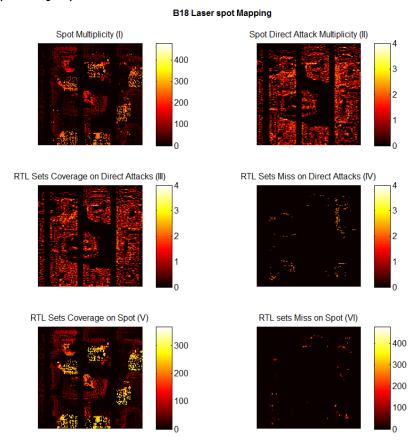

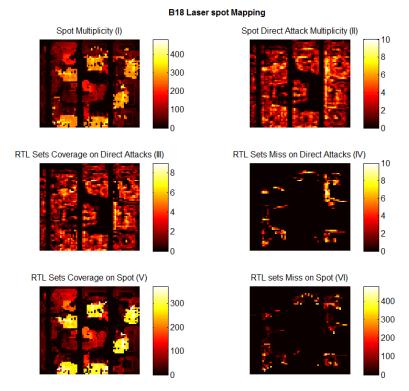

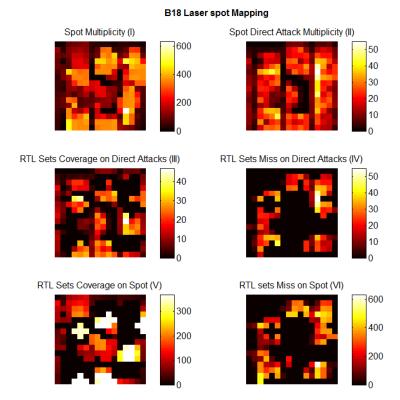

Chapter 7 presents the results produced by the analysis, which was applied on four different designs. Tables and layout mappings offer a reflection of the analysis outcome and validation percentages are explained revealing method's efficiency.

Chapter 8 contains the conclusion of the thesis, the most notable points in the internship and a glimpse on future work concerning the specific subject.

# **Chapter 2: Hardware Security**

# **2.1 Introduction**

Nowadays, hardware security is a major subject concerning many scientists and engineers. Even more, methods that break down hardware security is a topic susceptible of research. Early evaluation on the design process of ICs may prove decisive for the installation of proper countermeasures that improve the resilience of digital systems. That is the main point that concerns the work, in the context of the internship. Earlier manufacturing stages on IC design flow, such as RT level can provide the means for implementing accurate safety measures. Nevertheless, the term "hardware security" is mostly associated with cryptographic mechanisms. Usually, secure systems are the center of attention for hardware hackers, as valuable information is secretly banked in these systems. Security on hardware annotates the incorporation of cryptographic algorithms on digital systems. Thus, cryptography is the main scientific domain behind system security.

Cryptography is the study and the practice of methods for secret communication and writing of messages. Its aim is hiding their meaning to everybody except an intended recipient, who will be the only one who can uncover the secret and read the message. Cryptography, in general, may be used to provide any of following properties:

- Confidentiality: To prevent the unauthorized disclosure of data, only an authorized receiver should be able to extract the message contents from its encrypted form.

- Integrity: The receiver should be able to determine whether he receives the original message or an altered version.

- Authenticity: The receiver should be able to check from the message the sender's identity and the message origin or the path it followed.

- Non-repudiation: The sender should not be able to deny sending the message.

Modern cryptography is based on mathematics, computer science, and electrical engineering. Cryptographic algorithms, known as ciphers, use secret keys for encrypting the given data, known as plaintext, thus generating a cipher-text, and for decrypting the cipher-text to reconstruct the original plaintext. The keys that are used for the encryption and decryption steps can be either identical (or nearly related), leading to what are known as symmetric key ciphers, or they can be completely different, leading to what are known as asymmetric key (or public key) ciphers. Symmetric key ciphers have simpler, and therefore faster, encryption and decryption processes, compared to asymmetric key ciphers. Symmetric ciphers have the main weakness that the secret key is shared, which may lead to its discovery by malicious hackers, and therefore, must be changed in frequent periods.

Consequently, cryptography is an indispensable tool for protecting information in electronic circuits and computer systems. Today's cryptosystems contain secret keys for cryptographic algorithms

used to protect confidential information or to provide authentication mechanisms. These keys are the target of malicious hacking activity.

The need for secure chips, nowadays, is more necessary than ever. Cryptographic algorithms are being implemented in an increasing number of, not only consumer products, but also services. As an example, some categories using cryptographic ICs are mentioned:

- Car industry: anti-theft protection, spare parts identification

- Service providers: access cards, payment token, RFID tags, electronic keys, software license dongles

- Mobile phone manufacturers: batteries and accessories control

- Manufacturers of entertainment systems: copy protection, consumables and accessories control

- Manufacturers of devices and equipment: protection against cloning and reverse engineering, IP protection (hardware, software, protection of algorithms)

- Banking industry: secure payment cards, secure processing

- Military applications: data protection, encrypted communication

For this reason, they are always the subject of much research aimed at improving their security and resistance to any unauthorized interference. The current work aims towards this direction, meaning to provide with the proper feedback for the design of countermeasures that resist attacks on ICs, mostly on the cryptographic ones. The particular attack our work has focused on is the laser beam, which constitutes a state-of-the-art technique for IC fault manifestation. But, in general malicious attackers eventually use different kinds of techniques in order to accomplish their purpose and snoop secret information. Detection of the secret key may require the parallel usage of multiple different attacks, concerning the most commonly used cryptographic algorithms.

## 2.2 Different Attacks on ICs

In this sub-chapter, different attacks against digital systems are described thoroughly in order to give the reader a notion for the outbreak of malicious attacks. Attacks on digital (cryptographic) systems can be divided into cryptanalytic or mathematical attacks and hardware attacks. It is common for an IC hacker to make use of more than one type of attack so as to accomplish his purpose.

#### > Cryptanalytic or Mathematical Attacks

These attacks search for vulnerabilities in a cryptographic schema or algorithm in order to deduct the keys by mathematical methods. When an opponent is not able to find any weakness in a cryptosystem that could help him perform a cryptanalytic attack, he may use an exhaustive searching of the key. An exhaustive search, or as it called brute-force attack, for finding the key is a cryptanalytic attack that can, theoretically, be used for finding a key that maps a plaintext to its corresponding cipher-text. It requires checking all possible keys until the correct one is found. In practice, it requires checking, on average, half of the entire search space for the key. For this kind of attack, an automated software can be used in order to generate a large number of consecutive guesses as to the value of the desired data.

The key length of reliable cryptographic algorithms increases continuously beyond the computer's capability of calculating and finding the keys. So, a brute-force search for the keys is not able to give any answer in a reasonable amount of time, except if it has been applied as a complement of another attack that can reveal a significant part of a key.

The example of a real cryptographic algorithm is quoted. The Data Encryption Standard, called DES, was, historically, approved by former US National Bureau of Standards as an official Federal Information Processing Standard (FIPS) for the United States in 1976. DES is a block cipher that encrypts messages with a 56-bit key and it was considered as a secure encryption method at that time. But, as a result of the growth of computation capabilities, it was announced by the US National Institute of Standards and Technology (NIST) that they wished to choose a successor to DES. They mentioned that the new standard will be known as Advanced Encryption Standard or AES. The new encryption algorithm was chosen with 3 key sizes of 128, 192 and 256-bit, all greater than the 56-bit key of the outdated DES.

The previous fact, revealing the historical transition from DES to AES, states the growth of minimal key size from 56 bits to 128 bits, underlining the extremely important attribute of key size against brute-force attacks for information security. This example is much more obvious when we consider that each additional bit doubles the required computations in an exhaustive search (e.g. 2<sup>128</sup> computations for 128 bits). Nowadays, cryptanalytic attacks, although being very cheap, are not applicable as long time and effort is required for leaking out the secret information. Thus, attackers have turned to other efficient attacking techniques that need extra hardware material. Many times, a combination of cryptanalytic and hardware attacks is used.

### > Hardware Attacks

This large family of attacks targets mostly secure hardware, and by hardware it is meant the physical implementation of crypto-algorithms on integrated circuits. Hardware attacks are divided into invasive and non-invasive. Invasive attacks are those which leave behind such a footprint. They are a penetrative to the material and leave tamper evidence or even destroy the physical circuit. Non-invasive are able to hide their presence so as to have no effect on the system other than the introduced faults. Some common techniques, used against hardware security, are explained as follows:

- Side-channel attacks: technique that allows the attacker to monitor the analog characteristics of power supply and interface connections and any electromagnetic radiation.

- Micro-probing: technique used to access the chip surface in physical way, so one can observe, manipulate and interfere with the device.

- Reverse engineering: technique used to understand the inner structure of the device and learn or emulate its functionality. This method requires the use of the same technology available to semiconductor manufacturers and gives similar capabilities to the attacker.

- Fault Attacks: usage of abnormal environmental conditions to generate faults in the system that provide additional access.

#### 2.2.1 Side-channel attacks

Secret information, such as the key of the encryption algorithm, can leak out through sidechannels. A side-channel attack is a non-invasive attack, performed based on information gained from the physical implementation of a crypto-system. This new class of physical attacks against cryptographic circuits is drawing much attention from attackers' part.

Side-channel attacks do not process or open the package of target systems. The attacker only observes side-channel information from system modules. This category include timing attacks using operation times, as applied in [2]. Clock side-channel attacks are based on the fact that the individual computation steps that are required during the encryption are highly dependent on the bits of the secret key and, thus, the time needed for these steps is directly correlated to the bits of the secret key. Moreover, power analysis attacks using power consumption, as stated in [3] is another example of side-channel attack. The authors in [3] apply Differential Power Analysis (DPA), a technique to automatically locate correlated regions with respect to power consumption levels, so attacker needs little to no information about details on the target system, as long as they hold the information of power flow. In addition, electromagnetic radiation consists a passive side-channel attack and turns out to be a particularly serious issue for devices that pass keys or secret intermediates across a data bus. This example of attack is described in [4]. As it is stated, even a simple AM radio can detect strong signals from many cryptographic devices, allowing experiments to be conducted for further investigation.

Side-channel attacks have proven to be effective and incur a relatively low cost. Furthermore, once a side-channel attack technique has been developed and become public, high technical skills or expensive equipment are not required to apply it in practice. Side-channel attacks have become a major industrial concern in the last years and resulted in an intensive research effort to develop suitable countermeasures that can defeat the attacks, or at least make them more difficult and time consuming to perform. Many different types of countermeasures against this type of attack have been developed, including: restructuring of the cryptographic algorithm, shielding of the device, randomizing the computation, using power independent implementation, and others.

#### 2.2.2 Micro-probing

Micro-probing consists an invasive attack. Its major component is a special optical microscope. On an arm of the microscope, the attacker installs a probe, which is a metal shaft that holds a long tungsten-hair, which has been sharpened and allows the attacker to establish electrical contact with onchip bus lines. The probe is connected via an amplifier to a digital signal processor card that records or overrides processor signals and also provides the power, clock, reset, and I/O signals needed to operate the processor via pins.

In [6], the authors show that by locally observing the value of a few RAM or address bus bits (or possibly a single one) during the execution of a cryptographic algorithm, typically by the mean of a probing needle, an attacker could easily recover information on the secret key being used. The attacks presented in the article apply to public-key cryptosystems such as RSA, as well as to secret-key encryption schemes including DES and RC5.

Technological progress concerning countermeasures against micro-probing, is increasing the costs to the attackers. For modern deep submicron semiconductor chips, attacker must use very sophisticated and expensive probing technologies in order to remove layer after layer and reach the target point on the surface of the IC. Especially, in case there exist voltage, light or top metal sensors that prevent an opened chip from functioning, attackers are forced to turn to other attacking methods.

#### 2.2.3 Reverse engineering

Reverse engineering is an invasive and destructive form of analyzing a crypto-IC. The attacker grinds away layer after layer of the IC and takes pictures with an electron microscope. With this technique, it is possible to reveal the complete hardware and software parts. The major problem for the attacker is to bring everything into the right order to find out how everything works. The IC manufacturers try to hide secret keys and operations by mixing up memory positions, using bus scrambling. Moreover, they implement sensors to detect and prevent such attacks. This kind of attack is not very common because it requires a large investment in effort and special equipment that is generally only available to large chip manufacturers. Furthermore, the payoff from this attack is low since other attack security techniques, like sensors, are often employed.

An example of reverse engineering attack is stated in [7], where the authors describe a mostly automated process that can be used to cheaply determine the functionality of previously unknown cipher on the NXP Mifare Classic RFID tag, the world's most widely used cryptographic RFID tag. This is done by using a combination of image analysis of circuits and protocol analysis and can be feasible also for larger chips. It is stated that reverse engineering silicon is a cheap and effective way of overpassing IC security, even when very little is known about a cipher or about any software implementation.

#### 2.2.4 Fault Attacks

Fault Attacks is the category that gathers most of the attackers' efforts, thus this type is what mainly concerns our work. It constitutes the intentional introduction of faults in hardware systems. These attacks are considered as semi-invasive attacks, with intermediate cost of implementation and very effective results. It is mostly preferable by the attackers, while it provides some serious advantages over the previous attack techniques. A variety of fault attacks exist, where some hardware fault (an unexpected condition or defect) results in a processing mistake that is advantageous for the attacker. Methods of introducing faults include: supplying noise power or clock signals, voltage glitching, excessive temperature, radiation or high energy beams such as UV, laser, etc.

This category, although being the most important kind of hardware attacks, was intentionally left last to analyze as it deals with the fault model discussed in the thesis. Our work is associated with the study of laser fault attacks: How they are injected and how faulty outputs are used to endanger the secrecy of cryptographic devices. For this reason, we focus on the fault injection technique even more, and explain how it can be used for testing the resilience of digital systems.

## **2.3 Fault Attack Techniques**

Nowadays, most of the research dedicated on IC hack prevention, focuses on fault attacks, which is considered a modern and effective manner of intruding into secure systems. These kind of malicious assaults consist in introducing faults and forcing a cryptographic device to execute erroneous operations, hoping that the result of that wrong functionality will leak out information about the secret parameters involved. Fault attacks have proven to be practical and pose a risk against the secure operation of crypto devices. Contrary to side-channel attacks, where the side channels (power consumption, electromagnetic radiation, etc.) of an integrated circuit are observed in order to reveal information, fault attacks try to have an active impact on the IC's operation by skipping or corrupting security operations, corrupting registers and in general perturbating the IC's core operations. Being the most technologically advanced (state-of-the-art) and effective method, allowing high controllability, to break hardware security, it is reasonable for our research to focus on and study thoroughly this category, and more specifically, the laser attacks. However, for information fullness towards the readers, we describe briefly certain types of Fault attacks. The most common methods of fault injection into digital ICs or embedded devices are mentioned as follows:

- Voltage/Clock fault injection, by introducing dips or spikes in the VCC/Clock line of the target

- Temperature fault injection, by heating/cooling the IC outside of its thermal tolerance range

- Electromagnetic fault injection, by using a magnetic field close to the IC.

- Optical fault injection, by targeting certain areas of the IC with a laser

#### 2.3.1 Voltage/Clock Fault Attack

Voltage and Clock fault injection techniques turn out to be a common and quite successful series of attacks against ICs. They are also the most applicable ones, by using particular voltage and clock glitch sensors, respectively. Voltage glitch sensors may not allow the voltage in the supply line to exceed a certain range and, in the same way, clock sensors control the level of voltage in the clock input. Both these fault injection techniques require preparation for the target, leaving evidence of intrusion, in the form of isolating the power/clock lines (invasive attack). An example of voltage glitching is demonstrated as follows:

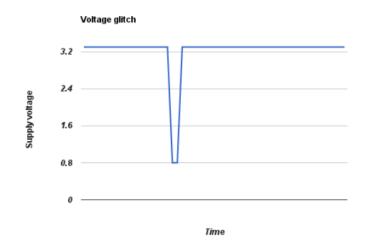

The normal operation of an IC is at its nominal voltage (say 3.3V). If one interferes by dropping the voltage down to 1V, he provokes a fault injection (Fig. 2.1). At that moment, the input voltage to certain gates within the chip will be too low due to the lack of supply voltage. Thus, these gates will receive an input voltage which is below the threshold that indicates whether the signal is a zero or a one, no matter what value it was supposed to be. By increasing the voltage again to the nominal voltage of 3.3V, we get a functioning chip that just failed to execute one of its operations. For instance, it failed to execute a conditional jump and fell through to the code that was expected to have executed.

Fig 2.1: Example of voltage glitching. The supply voltage is set to 0.8V during a short moment of time.

In this case, the trick is to discover some proper parameters for the glitch: voltage drop level, length of the glitch and the timing. Typically, if voltage drop and length of glitch are too small, the chip will function properly. If they are too large, then the chip will just either mute or reset, or even maybe get physically damaged. Of course, it is mandatory that the attack timing is accurate, otherwise the attacker will never see the effects he wants to get.

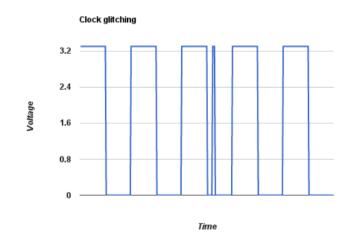

Clock <u>glitching</u> is similar to  $V_{CC}$  glitching in the sense that it affects another critical parameter of the chip that can be controlled by the attacker. In this case, the attacker is injecting spurious clock cycles that are way shorter than the original clock cycle (Fig. 2.2). Since the internal logic of the chip operates based on its clock, a short clock cycle will trigger a new operation before the results of the previous one were completely computed or propagated through the device. For instance, proper function includes

multiplication of two values, and then addition of a third value to them. Normally, multiplying values takes longer than adding them up. Thus, the clock frequency for a chip that only performs these two operations would be long enough for the multiplication to occur and its result to be ready at the input of the next stage, since that is the critical operation. In case addition precedes the result of the multiplication, then the data will turn to be invalid. Thus, there will be failure at computing the correct result. Clock glitching exploits exactly that situation. Again, finding the right parameters in this case is the key to success.

Fig 2.2: Example of clock glitching. A very short spurious clock cycle is inserted at the beginning of a normal cycle.

## 2.3.2 Temperature Fault Attack

Cryptographic circuits operating outside of the specified range of temperature will start to malfunction. That situation is exploited by attacker in order to perform temperature fault injection. This type of fault injection is a hard technique to be achieved and controlled because of the exact timing needed between the target operations and the temperature variations that are to take place. Usually, a combination of voltage and temperature fault attack takes place. The authors in [8] demonstrate a way to break even state-of-the-art ciphers, by lowering  $V_{DD}$  to the point when individual logic gates are not able to switch, while increasing ambient temperature. They state that low-cost voltage and temperature manipulations can be used for high-precision fault injection required to break state-of-the-art ciphers.

#### 2.3.3 Electromagnetic Fault Attack

A new type of fault attacks is introduced, which uses an electromagnetic field to induce faults in the target device. The Electro Magnetic field Fault Injection (EMFI) perturbation is effective and non-invasive. This attack can bypass the countermeasures, such as light or motion sensors and, by its nature, it is harder to detect during run-time, leaving little or no evidence of intrusion. Article [9] considers the use of magnetic pulses to inject transient faults into the calculations of a RISC micro-controller running

the AES algorithm. This technique enables to fault every byte of the AES state on a non-protected software implementation of an AES, running on an 8-bit micro-controller.

#### **2.3.4 Optical Fault Attack**

Optical fault attack, or most commonly referred as laser fault attack, uses a light beam to inject faults into semiconductor devices. The light beam basically consists of a number of photons carrying a certain amount of energy. Roughly, when these photons reach a semiconductor (typically the silicon in electronic devices), their energy is absorbed by the semiconductor. Given enough energy, electrons that would otherwise be within the semiconductor will start to move, creating current. So, this means that some of the transistors in the chip will actually change their state, when such change should not happen.

The big difference between this fault attack technique and the previous mentioned ones is that, in this case the attacker actually has spatial selectivity (or resolution). In a laser attack the opponent usually controls the beam's diameter, wavelength, the amount of emitted energy, and the exposure's duration. Attacker can choose which parts of the chip to attack by pointing the laser beam on them. Of course, this is very powerful but at the same time it increases the complexity to the attack, because he needs to find the sensitivity spots of the chip. As before, there are a number of parameters one needs to take into account in order to successfully inject faults. Some of them are beam exposure timing and length, wavelength of the injected light and amount of energy injected.

Moreover, this attack is semi-invasive, meaning that attacker needs to open up the chip package so that the light radiation can reach the level of the die. Otherwise, the light will be blocked by the package or, in case of a smart-card, the plastic around the die. Thus, this attack provides additional power at the cost of additional complexity, as usual. In terms of hardware level protections, this is also the most difficult attack to prevent. Typically light sensors are scattered around the chip, but manufacturers cannot place sensors everywhere because of high cost, so there is always open spots. In this work, we have focused on laser attacks in order to validate a fault injection model that describes fault locality at the RT Level. In conclusion, the reasons for specifically deepening into the effects of laser attack underlie to its attributes over the rest of the attacks, which are summarized as follows:

- Complete controllability over the fault location. That means that the attacker can turn against selected components on the chip, thus affecting specific bits.

- Precise controllability on the timing of attack (the desired exact time can be met).

- Advanced controllability over the range and spreading of attack, meaning that attacker is able to roughly select the number of bits affected. Therefore, attacker can target to single faulty bit, or few faulty bits (e. g., a byte or word), or even a random number of faulty bits (bounded by the length of the affected variable).

- Variable power level of the laser leads to different kinds of impacts on fault location. By operating the laser at a low level of power, attacker can induce transient faults, i.e. faults that cease to exist after a short period. In case of high power level, the impact might be destructive, thus irreversible.

Concerning IC protection, countermeasures against fault attacks require a combination of hardware and software prevention and detection mechanisms. Typically, what is needed are sensors at the hardware level and double-checking and redundancy at the software side. Due to the difficulty of completely preventing this kind of attacks, fault attacks are nowadays one of the main threats to secure hardware. In addition this difficulty, combined with the physical nature of the attacks, indicates that simulating or emulating on testing devices these attacks is typically not enough to assure appropriate protection levels, making fault attacks a notable testing key for secure hardware [10]. The next chapter presents various efforts of studying and testing the AES algorithm against fault attacks.

# 2.4 Fault Attacks on the Advanced Encryption Standard AES

## 2.4.1 The Advanced Encryption Standard (AES)

In this sub-chapter, we present some fault attacks applied on the Advanced Encryption Standard. This algorithm was studied during the internship and testing efforts are dedicated on some implementations of AES with different countermeasures. AES is a symmetric method and is based on Rijndael cipher. It can grant a high level security using a reasonable calculation time. AES was quickly adopted for many systems and products after NIST validation in 2001. Many types of attacks have been studied by researchers with the intention of improving AES incorporations by suitable countermeasures.

AES is an algorithm that performs message encryption processing by data blocks of 128 bits at input and output using a key size of 128, 192 or 256 bits respectively in 10, 12 or 14 rounds (after a short initial round) according to the size of the key. Encryption includes two separated processes:

- Key Scheduling to derive the round keys from the secret key

- Data encryption

Decryption also is divided into two separated processes:

- Key Scheduling to derive the secret key from round keys

- Data Decryption

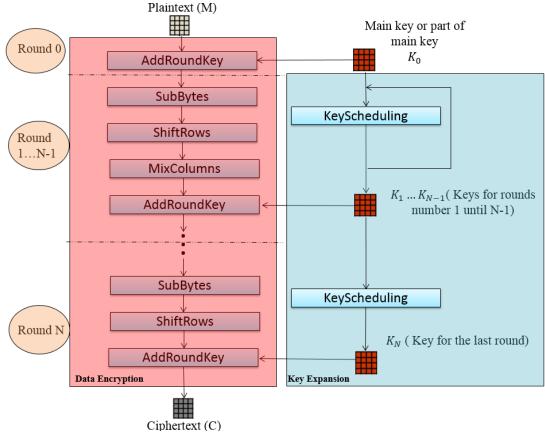

For the initial round in AES-128 bits, the algorithm uses the secret key as the round key. But for each following round, the corresponding round key is calculated from the previous one. Figure 2.3 shows

the different operations of the AES algorithm. We use AES to refer to AES-128 and we use the "K" prefix plus the number of a round to refer to a round key (e.g.  $K_1$  for the round key of the 1rst round)

Figure 2.3: AES general outline

To encrypt a plaintext, namely M, according to the implementation of AES, usually at the beginning of algorithm execution, all the round keys are computed from the main key and are stored in the memory. Then, the encryption process begins and takes separated blocks of 16 bytes (128 bits) from M as input and put each block in a matrix of 4x4 bytes. Each round of the algorithm, except the initial and the last ones, includes 4 steps:

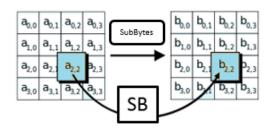

1) At the beginning, it exchanges the value of each matrix element, i.e. one byte value, by the corresponding value in a fixed substitution table (SubBytes or SB).

Fig 2.4: In the SubBytes step, each byte is replaced with its entry in a fixed 8-bit lookup table, SB;  $b_{ij} = SB(a_{ij})$ .

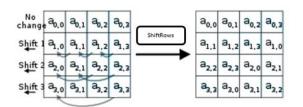

2) Then, it executes a rotational operation on the matrix rows (ShiftRows or SR). It cyclically shifts the bytes in each row by a certain offset. The offset is decided according to the row index (first:0, second:1, third:2,..). That means the first row is left unchanged.

Fig. 2.5: In the ShiftRows step, bytes in each row of the state are shifted cyclically to the left, according to row index

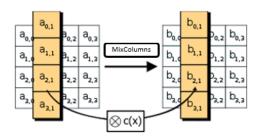

3) In the third step, the algorithm applies a linear transformation to each element and combines it with other values of the same column with a different coefficient of 1, 2 or 3 for each element (MixColumns or MC) under the specific rules of  $GF(2^8)$ . This step guarantees the distribution of the information of each byte on 4 bytes and increases security of encrypted messages.

Fig. 2.6: In the MixColumns step, each column is multiplied with a fixed matrix

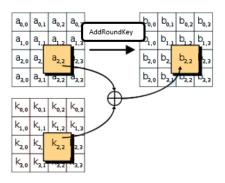

4) Finally, in the last step of each round, a bitwise XOR operation is performed between the value of each element and the corresponding byte on the round key (AddRoundKey or ARK).

Fig. 2.7: In the AddRoundKey step, each byte is combined with a byte of the round-dependent key using the XOR operation

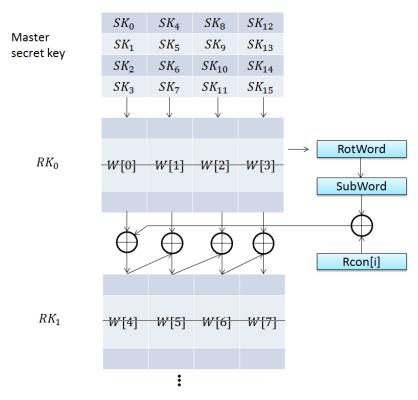

Concerning the procedure of round key computation, the 128-bit AES algorithm takes the main key and performs a key expansion routine to generate 10 round keys. Each expanded round key consists of a linear array of 4-byte words, denoted as W[i]. There are three transformation functions in the key expansion process as follows:

- RotWord is a function that takes a word  $[a_0, a_1, a_2, a_3]$  as an input, performs a cyclic permutation and returns the word  $[a_1, a_2, a_3, a_0]$ .

- SubWord is a function that takes a word composed of 4 bytes and applies Sbox to each byte.

- Rcon[i] is a round constant word given by  $[x^{i-1}, \{00\}, \{00\}]$ , with  $x^{i-1}$  representing powers of x (x is denoted as  $\{02\}$  in the field GF(2<sup>8</sup>). Note that i starts at 1.

The following figure shows the AES key expansion process.  $RK_0$  is the initial round key identical to the main secret key. The rest of round keys are generated by the key expansion process.

Fig 2.8: AES key expansion process

Currently, AES encryption is widely used for governmental, military and commercial purposes. Therefore, it has opened a new and large domain of research on the security of cryptographic circuits.

## 2.4.2 Different Methods of Fault Attacks on the AES

Different types of fault attacks on AES have been studied in general by researchers. These specific fault attacks can be categorized in certain categories, according to their methodology or mathematical implementation. Also, some evidence, describing the outcome of these attacks is stated.

### Differential Fault Analysis (DFA)

This attack depends on introducing faults into key-dependent cryptographic operations through physical intrusion. It is based on gaining some insights into the secret data handled by the circuit and then finding the secret key by comparing faulty cipher-texts with the corresponding (correct) ciphertexts.

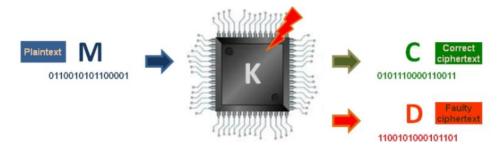

Fig. 2.9: An overview on Differential Fault Analysis [12]

The authors of [12] presented a theoretical DFA attack on AES. This attack required the injection of a single-byte fault into the temporary cipher-text between the MixColumns output of the antepenultimate round and the MixColumns input of the penultimate round to be successful.

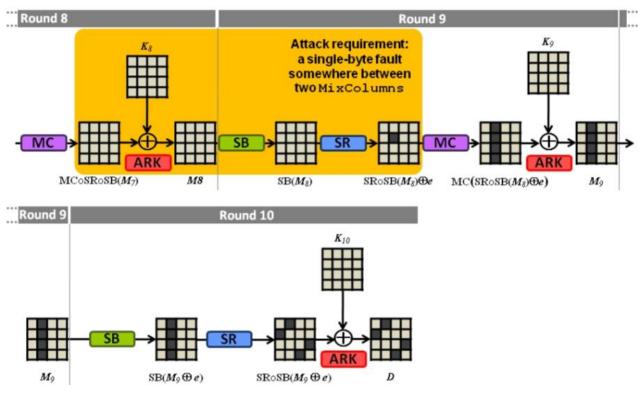

Fig. 2.10: Propagation of a single-byte fault at MixColumns input of the round 9 [12]

Figure 2.10 shows a tuning window that extends between MixColumns exit of round 8 and MixColumns entry of round 9 for a single-byte fault injection as the attack's requirement. The same Figure also presents the fault propagation and diffusion into four bytes. The attack scheme allows to infer some information on the four corresponding bytes of  $K_{10}$  by processing the correct and faulty cipher-texts and checking over the list of all the related possible single-byte faults. By repeating this process twice (i.e. by iterating the attack for a different plaintext) the exact value of the four bytes of  $K_{10}$  is found with a success rate of about 98%. The procedure is repeated to target  $K_{10}$ 's remaining bytes. Finally,  $K = K_0$  is inferred by reversing the key expansion operations.

#### Round Reduction (RR)

Many cryptographic algorithms, such as AES, are based on repetition of identical sequences of transformations, called rounds. A significant part of theses algorithms' strength against cryptanalysis is based on their repeated rounds. Any decrease on the number of rounds reduces their security. The Round Reduction belongs to the family of attacks by algorithm modification. For instance, suppose an attack by the opponent that makes a jump after the execution of few instructions from the first round at the beginning of algorithm to its end. So, the remaining encryption processes are skipped and the final cipher-text is the product of few algorithm processes that may reveal easily the key.

Principle of Round Reduction is based on decreasing the number of rounds in an algorithm in order to facilitate subsequent cryptanalysis. This method was first presented in the article [13]. It

illustrates that a transient glitch on the VCC may change the round counter value of a repetitive cipher. The opponent may break the algorithm execution at end of the first round. In this case, the cryptanalysis will be very fast and easy. Its complexity no more corresponds to the cryptanalysis of correct execution of entire 10 rounds for the reported algorithm. Application of laser attack aiming on such technique is also feasible [13].

#### Safe-Error Analysis (SEA)

This analysis method searches for existence of any behavioral difference of a cryptographic circuit instead of faulty cipher-texts. A fault attack, may release an alarm or stop the operations. These signs of a behavioral difference in comparison with a normal execution may lead to find secrets from the circuits. The first SEA is presented in [14]. It consists in the injection of a fault by laser on a temporary register value and then observing the consequences on the output. One year later after the publication of [14], the authors in the article [15] reported a safe-error based attack by inducing a temporary random computational fault in addition to a temporary memory fault. Some other publications, such as in [16], tend to distinguish the two attacks, by considering the first method as a Memory or M Safe-Error that targets memory or register contents and the second one as a Computational or C Safe-Error Analysis focusing on the operations. However, in general the target of attacks against AES algorithms, such as DFA and RR, is mostly the temporary cipher-text, the round keys, the SubBytes table or the round counter.

# 2.5 Fault Injection for validating robustness of a design

Except for breaking system's security, fault attacks are recognized by scientists as a particularly attractive and valuable method for testing the robustness of hardware designs. Fault attacks that are used for validating purposes are usually referred as fault injection techniques. Fault injection can provide a method of assessing the dependability of a design under test. This is done by intentionally inserting faults into the system and monitoring system's reaction with respect to these faults. Fault injection allows validating robustness or dependability of a target system by providing:

- An understanding of the effects of real faults and, thus, of the related behavior of the target system in terms of functionality and performance.

- An evaluation of the efficacy of the fault tolerance techniques that are included into the target system and, therefore, a feedback for their enhancement and correction.

- Estimation on the failure coverage and latency (for example, timing, voltage level) of fault tolerant mechanisms.

- A forecasting method of the erroneous function of the target system, in terms with encompassing a measurement of the efficiency provided by the fault tolerance mechanisms.

- Exploration of the effects of different workloads (different input environments) in regards with the effectiveness of fault tolerant techniques.

- Identification of the weak spots in the design, as an example, parts of the system that because of a single fault could lead to severe consequences.

- Study of the system's behavior in the presence of faults, for example, propagation of fault effects between system components or the degree of fault isolation and determination of the coverage of a given set of tests.

With that said, engineers and designers use fault injection techniques to test the hardware systems. The next chapter offers an insight in several fault injection methodologies based on existing literature, as well as in the application of fault models that are used in combination with fault injection techniques. The objective is to deepen more into testing fault techniques concerning early levels in the design flow, such as RT and Gate Level and, finally focus on the main subject of the internship and, in extension, of the thesis. It is reminded that the early levels of abstraction may provide an effective source of information to lead towards the development of new countermeasures against malicious attacks on ICs.

# **Chapter 3: Fault Modeling and Fault Injection Methodologies**

As mentioned before, the implementation of fault tolerance on digital systems dictates the testing of systems reliability. This is done by introducing faults into the system and inspecting system's response. The fault injection methodology under validation [1], proposes is a generalized RTL fault methodology, based on some other categories of fault types. That is why this chapter is focusing even more to fault modeling and fault injection techniques.

# **3.1 Definition of Fault**

The definition is provided in accordance with the faults occurred on secure digital systems. A fault in a cryptographic system refers to an accidental or an intentional condition that causes the encryption or decryption process to deviate from its correct execution or result. In this case, the cryptographic system may act abnormally or the result of encryption or decryption may be incorrect, thus considered as faulty. A faulty execution or result is considered reproducible, if it occurs consistently under the same circumstances.

# **3.2 Different types of Faults**

The present work concentrates on the hardware faults. Faults on the electronic circuits can be classified into three general categories, according to their persistence [17]:

- Provisional or transient faults: These faults are temporary or short-term. As the fault introduction is interrupted, the provisional faults disappear. So, after some time has elapsed, the chip recovers its normal execution without circuit reset. For instance, by heating a circuit (Temperature fault attack) faults are created that result to extended propagation times. The circuit resumes its correct functioning after temperature decreases.

- Permanent faults: The permanent faults are persistent but reversible. As the corrupted area is

modified or changed by another part of the circuit or as the circuit is reset, these faults disappear.

Thus, they are not destructive and don't damage the circuit. For instance, a fault injected on a

SRAM cell persists until memory rewrite or circuit reset.

- Destructive faults: The interferences may create a perpetual defect on hardware. Once infected, such destructions affect the chip's behavior permanently. For example, a laser emission with a high energy level on a memory cell may permanently destroy some memory cells. In this case, the memory cells can no longer be rewritten or recovered by circuit reset.

#### **3.2.1 Permanent faults**

Effects of permanent faults are reversible. After a system reset or when the fault's stimulus is interrupted, the circuit will recover at its original behavior. There are two kinds of transient faults, and are explained below [11]:

- Single-event upsets (SEUs): It is interesting to note that this kind of attack was first noticed as an effect of cosmic rays during a space mission. Research then began on mechanisms of such faults into the circuits. SEUs consist in a cell's logical state flipping to a complementary state without any damage to the circuit. If the fault is produced in a system that recovers its original values after a reset, its effect is temporarily. SEUs can be created using focused laser beams.

- Multiple-event upsets (MEUs): They consist of several SEUs occurring simultaneously. So, MEUs can be considered as a generalization of SEUs. With the augmentation of integration density, the risk of generating such faults is increased.

## **3.2.2 Destructive faults**

Destructive faults are due to an effect on the circuit that remains permanent and creates expanding faulty behavior or value. Due to their permanence on the circuit material, these types concern the highest level of abstraction in the design, indicating the semiconductor components. Different types of faults are included in this class, such as [11]:

- Single-event snap back faults (SESs): These kinds of faults are created by the self-sustained current by the parasitic bipolar transistor in channel n of MOS transistors. It seems that they do not occur in low supply voltage devices.

- Single-event latch-up faults (SELs): A latch-up consists in the activation of a parasitic thyristor structure formed in CMOS circuits. The transient current induced by a laser beam, for instance, may activate the parasitic thyristor resulting in a high current flow.

# **3.3 Definition of Fault Model**

A fault model is an engineering model of something that could go wrong in the construction or operation of hardware. From the model, the designer can predict the consequences of a particular fault. In electronics, a fault model constitutes a description of how elements in a defective circuit behave. Usually, it is attached with several assumptions on fault manifestation and spreading. The goal of fault modeling is to model a high percentage of the physical defects that can occur in the device at the highest possible level of abstraction. In digital systems, high levels are described by the Gate and RTL net-lists.

## **3.4 Different Fault Models**

The injected faults on the circuit can be described with different fault models, concerning bit level. The following fault models can be applied in an RTL fault injection analysis, during simulation. For the sake of describing some of these models accurately, we consider  $T_1 = \{b_1, b_2, b_3, ..., b_n\}$  as the initial values of an arbitrary set of targeted bits. Let  $T_2 = \{b_1', b_2', b_3', ..., b_n'\}$  be values of  $T_1$  after a fault attack. Now, we review the effect of some existing fault models on the targeted set [11]:

• **Bit-flip** or **Bit inversion**: When the values of targeted bits are changed to their opposite values, we consider the fault type as bit-flip or bit inversion, if and only if:

$$\forall i: 0 \le i \le n, \qquad b_i' = 1 - b_i$$

• **Stuck-At**: In this fault model, the targeted bits are set permanently to their previous value. Therefore, even if new values must be affected to the targeted bits, the memory write operation cannot change them. This effect is usually considered as a destructive fault due to a wire, gate or memory cell damage, but it might be a permanent fault that disappears after a circuit reset. The fault model is considered as stuck-at 0, if and only if:

$\forall i: 0 \le i \le n, \qquad b'_i = b_i = 0$

The fault model is considered as stuck-at 1, if and only if:

$$\forall i: 0 \le i \le n, \qquad b'_i = b_i = 1$$

In this category of faults, the values of targeted bits are usually unknown to the opponent before and after the attack. A stuck-at fault has a noticeable effect only when it must be rewritten to its opposite value. At this point, it may create a change in the system behavior or results.

• **Random**: When the value of at least one of targeted bits is changed, but the value changes are random. In other words, the fault model is random, if and only if:

$$\forall i: 0 \le i \le n, \qquad b'_i \in \{0,1\}$$

• Set or Reset: In this fault model, the targeted bits are set or reset to whatever is their previous value. The fault model is considered as set, if and only if:

$$\forall i: 0 \le i \le n, \qquad b'_i = 1$$

Otherwise the fault is considered as reset, if and only if:

$$\forall i: 0 \le i \le n, \qquad b'_i = 0$$

Between these fault models, the random faults are usually considered to be the most realistic. Such simple fault models, describing the perturbation of bits in hardware are usually implied in more complicated fault models, such as those studying fault manifestation in early levels of design flow (Gate and RT level)

## **3.5 Fault Modeling at RTL and Gate Level**

Fault models constitute a representation of fault impact on a small part of the electronic device. Based on such models, scientists develop large-scale fault injection methodologies to test the robustness of IC designs. The need for early evaluation of the IC design flow with respect to fault-based attacks has led to the development of fault injection models at a high level of abstraction, indicating RTL and Gate Level. Logic synthesis transforms the RTL description into an optimized technology-specific hardware description in the form of Gate Level net-list, without altering design's original functionality. This sub-chapter makes a brief reference on previous work concerning fault models that are applied on earlier stages of manufacture, such as RTL and Gate Level. The fault injection models that are mentioned here, make use of statistical and probabilistic methods, as well as simulation techniques. The current thesis is attempting to validate a fault injection methodology that takes place at the RTL [1].

Gate Level is widely accepted as a good compromise between abstraction level and the ability to represent most of the defects in designs under test. By representing the device under test (DUT) as a gate-level model, fault injection models have the ability to increase testing efficiency in the design flow. As stated in the article [18], testing has been historically performed using gate-level fault models. Much research has focused on gate level modeling of attacks. In [27], the author mentions several Gate-level fault models and explain how error properties induced by a fault attack in a logic circuit can be modeled in terms of those models. It is a fact that faults in Gate-level can be further modeled, according to the way they occur. For instance, single (or multiple) stuck-at faults make the assumption that one line in a gate is (or multiple lines in many gates are) fault model that assumes a single physical line in the circuit is broken and the resulting open node is not tied to either  $V_{DD}$  or GND. Finally, fault models related with the delay of signal propagation and the short-circuiting between two or more lines on the circuit are presented.

In [19], the authors focus on the evaluation of circuit reliability under probabilistic methods that can capture both soft errors, such as radiation-related errors, and spatially-uniform manufacturing defects. This task can be used by synthesis procedures to select more reliable circuits and to estimate yield for electronic nanotechnologies where high defect density is expected. In their work, they propose a matrix-based formalism to compute the error probability of the whole testing circuit based on probabilities of specific gate errors. This formalism is related to that of quantum circuits, but also it is revealed that the numerical computation of error probabilities can apply on larger circuits.

In other articles sampling techniques are used as fault injection modeling. Sampling techniques, where a randomly selected subset of faults is simulated to estimate the fault coverage, can reduce the performance penalty of gate-level fault simulation. The author in [20] introduced the sampling technique to gate-level fault simulation to decide whether or not the fault coverage of a given test exceeds a given bound. This technique was elaborated by the author in [21] to provide upper and lower bounds for the coverage. He also proposed a method that uses a fault sample of a fixed size. The estimation of fault coverage by simulating only a fraction of gate-level faults requires only a fraction of time and resources required for the complete gate-level fault simulation. Similar approaches based on statistical sampling technique reduces the size of the fault-list used for simulation, it requires a complete gate-level fault-list, meaning all the combinations of faults occurred on gates and, therefore, cannot be used prior to logic synthesis. Post-synthesis findings of test generation and fault simulation efforts are too late in the design cycle to be utilized for architectural changes to improve system resilience. It is, therefore, desirable to develop the fault injection models at a higher level of abstraction than the Gate level.

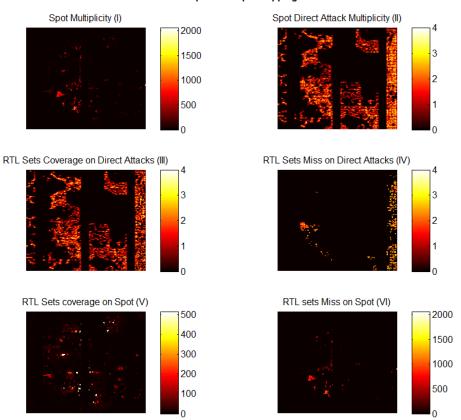

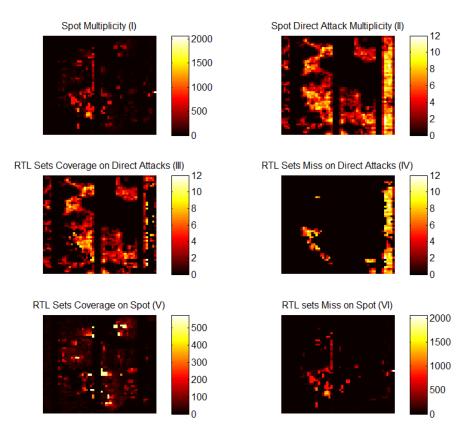

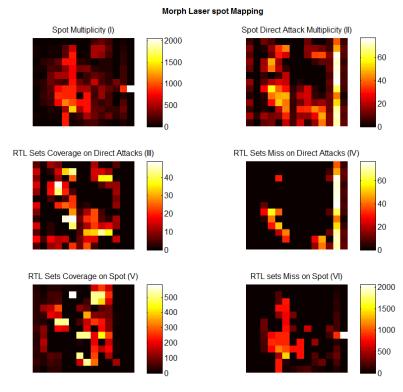

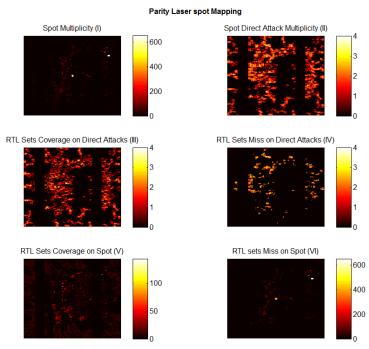

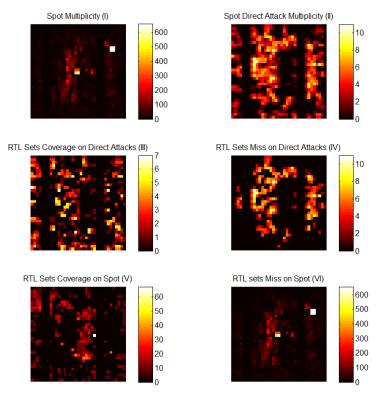

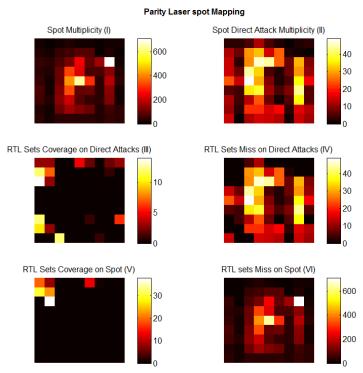

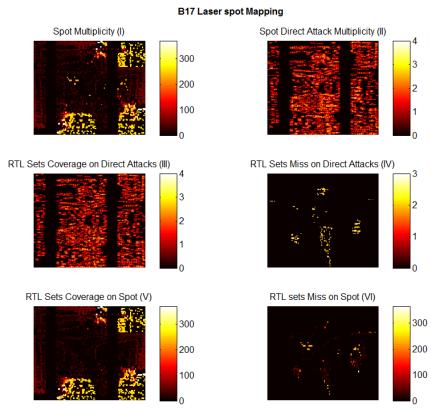

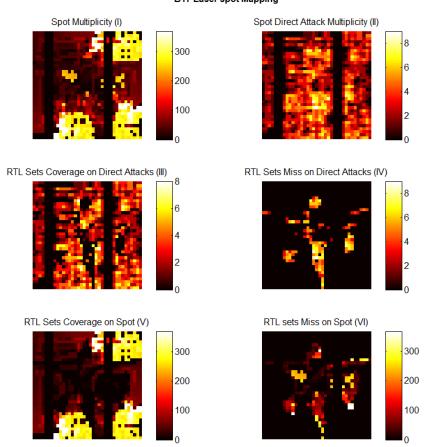

Mao and Gulati [24] proposed an RTL fault model and a fault injection methodology using simulation. The fault model used is the single stuck-at fault for each bit of all variables in the RTL netlist. The RTL fault simulator they developed, supports RTL testability analysis on circuit designs. They were able to generate quantitative RTL fault coverage and provide information for design modifications, leading to the testability at the RT level. Their approach also required to run fault simulation twice (first in an optimistic and then in a pessimistic mode) and to use the average of the results to reduce the difference between the RTL and the gate-level fault coverages. Their work showed that RTL fault coverage results in the improvement of fault coverage at the Gate Level. Nevertheless, the RT level description is at a higher level of abstraction and may not cover all the gate level faults.