# FPGA VIRTUALISATION ON HETEROGENEOUS COMPUTING SYSTEMS

## MODEL, TOOLS, AND SYSTEMS

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF SCIENCE AND ENGINEERING

2020

Khoa Dang Pham

School of Computer Science

## Contents

| Al | Abstract<br>Declaration |         |                                                            |    |

|----|-------------------------|---------|------------------------------------------------------------|----|

| D  |                         |         |                                                            |    |

| C  | opyri                   | ght     |                                                            | 14 |

| A  | cknov                   | vledgen | ients                                                      | 15 |

| 1  | Intr                    | oductio | n                                                          | 16 |

|    | 1.1                     | Motiva  | ation and Aims                                             | 20 |

|    | 1.2                     | Contri  | butions                                                    | 21 |

|    |                         | 1.2.1   | FPGA Virtualisation Model for Heterogeneous Computing Sys- |    |

|    |                         |         | tems                                                       | 21 |

|    |                         | 1.2.2   | Bitstream Abstraction                                      | 23 |

|    |                         | 1.2.3   | Decoupled Compilation Flow for FPGA Virtualisation         | 24 |

|    |                         | 1.2.4   | System Prototypes                                          | 26 |

|    | 1.3                     | Thesis  | Structure                                                  | 27 |

|    |                         | 1.3.1   | Chapter 2 – Background and Related Works                   | 27 |

|    |                         | 1.3.2   | Chapter 3 – Bitstream Manipulation Tool and API            | 27 |

|    |                         | 1.3.3   | Chapter 4 – Decoupled Compilation Flow for FPGA Virtuali-  |    |

|    |                         |         | sation                                                     | 29 |

|    |                         | 1.3.4   | Chapter 5 – Run-time Management                            | 29 |

|    |                         | 1.3.5   | Chapter 6 – System Evaluation                              | 29 |

|    |                         | 1.3.6   | Chapter 7 – Conclusion                                     | 29 |

|    | 1.4                     | Public  | ations                                                     | 30 |

|    | 1.5                     | Open    | Source Releases                                            | 32 |

| 2 | Bac  | Background and Related Works  |                                                              |    |  |

|---|------|-------------------------------|--------------------------------------------------------------|----|--|

|   | 2.1  | Overv                         | iew                                                          | 3  |  |

|   | 2.2  | Partial                       | Reconfiguration (PR)                                         | 3  |  |

|   |      | 2.2.1                         | FPGA Vendors' PR Design Flows                                | 3  |  |

|   |      | 2.2.2                         | Academic PR Development Tools                                | 3  |  |

|   |      | 2.2.3                         | Discussion                                                   | 3' |  |

|   | 2.3  | Bitstre                       | eam Manipulation                                             | 3  |  |

|   | 2.4  | Comp                          | ilation Flows for HLS Applications                           | 3  |  |

|   | 2.5  | Shell-                        | based Systems                                                | 4  |  |

|   | 2.6  | Chapte                        | er Summary                                                   | 4  |  |

| 3 | Bits | tream N                       | Manipulation Tool and API                                    | 4  |  |

|   | 3.1  | Bitstre                       | eam Investigation and BitMan Implementation                  | 4′ |  |

|   |      | 3.1.1                         | Bitstream Format                                             | 4′ |  |

|   |      | 3.1.2                         | Module Placement and Relocation                              | 5  |  |

|   |      | 3.1.3                         | Bitstream Manipulation Tool                                  | 5  |  |

|   | 3.2  | 2 Applications and Evaluation |                                                              |    |  |

|   |      | 3.2.1                         | Run-time Adaptation                                          | 6  |  |

|   |      | 3.2.2                         | Hardware Mapping and Linking for the Overlay Architecture .  | 62 |  |

|   |      | 3.2.3                         | Bitstream generation for Enabling On-chip Self-compilation . | 6  |  |

|   | 3.3  | Chapte                        | er Summary                                                   | 6  |  |

| 4 | Dec  | oupled                        | Compilation Flow                                             | 6  |  |

|   | 4.1  | Design                        | n Methodology                                                | 60 |  |

|   |      | 4.1.1                         | Overview                                                     | 6  |  |

|   |      | 4.1.2                         | Academic Tools for Routing Constraints Generation and Bit-   |    |  |

|   |      |                               | stream Manipulation                                          | 6  |  |

|   | 4.2  | Shell I                       | Design                                                       | 6  |  |

|   |      | 4.2.1                         | Implementation of the Shell                                  | 70 |  |

|   |      | 4.2.2                         | Bus Virtualisation                                           | 7. |  |

|   |      | 4.2.3                         | I/O FPGA Virtualisation                                      | 74 |  |

|   | 4.3  | Modu                          | le Compilation                                               | 7  |  |

|   |      | 4.3.1                         | Overview of Module (Role) Design                             | 73 |  |

|   |      | 4.3.2                         | Module Synthesis                                             | 7  |  |

|   |      | 4.3.3                         | Module Implementation                                        | 8  |  |

|   |      | 4.3.4                         | Hardware Module Library                                      | 8. |  |

|   | 4.4         | Chapte                       | er Summary                                               | 87  |  |

|---|-------------|------------------------------|----------------------------------------------------------|-----|--|

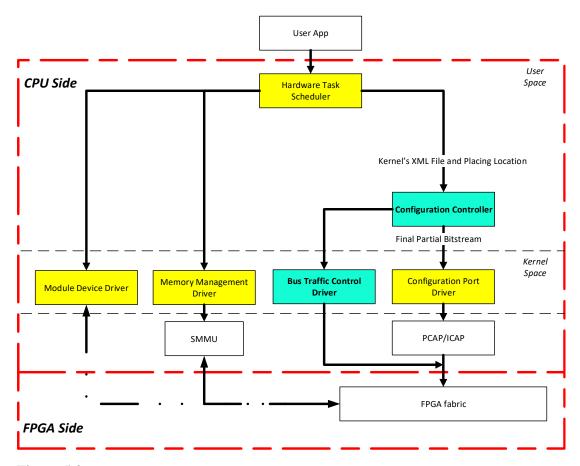

| 5 | Run         | -time N                      | Ianagement                                               | 90  |  |

|   | 5.1         | Workf                        | low Overview                                             | 90  |  |

|   | 5.2         | 5.2 Configuration Controller |                                                          |     |  |

|   |             | 5.2.1                        | Overview                                                 | 91  |  |

|   |             | 5.2.2                        | Hardware Module Placement Process                        | 92  |  |

|   |             | 5.2.3                        | Configuration Overhead                                   | 93  |  |

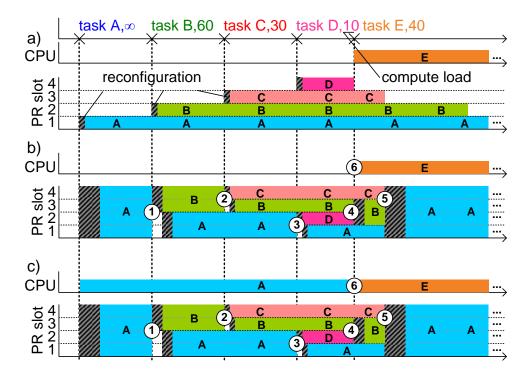

|   | 5.3         | Hardw                        | vare Task Scheduler                                      | 94  |  |

|   |             | 5.3.1                        | Overview                                                 | 94  |  |

|   |             | 5.3.2                        | Scheduling Overhead                                      | 95  |  |

|   | 5.4         | Modu                         | le Device Driver                                         | 95  |  |

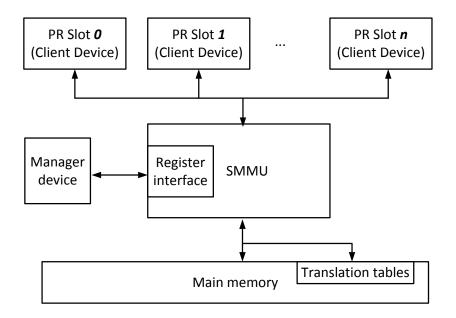

|   | 5.5         | Memo                         | ry Isolation/Management                                  | 96  |  |

|   |             | 5.5.1                        | Overview                                                 | 96  |  |

|   |             | 5.5.2                        | Memory Management Framework for FPGA:                    | 97  |  |

|   |             | 5.5.3                        | Memory Management Overhead                               | 98  |  |

|   | 5.6         | Chapte                       | er Summary                                               | 99  |  |

| 6 | Svst        | em Eva                       | luation                                                  | 100 |  |

|   | <b>6</b> .1 |                              | n Productivity and Deployment Flexibility                | 101 |  |

|   |             | 6.1.1                        | Analysis of Design Productivity                          | 101 |  |

|   |             | 6.1.2                        | Analysis of Configuration Overhead                       | 103 |  |

|   |             | 6.1.3                        | Analysis of Deployment Flexibility and System Completion |     |  |

|   |             |                              | Time                                                     | 103 |  |

|   |             | 6.1.4                        | Summary                                                  | 105 |  |

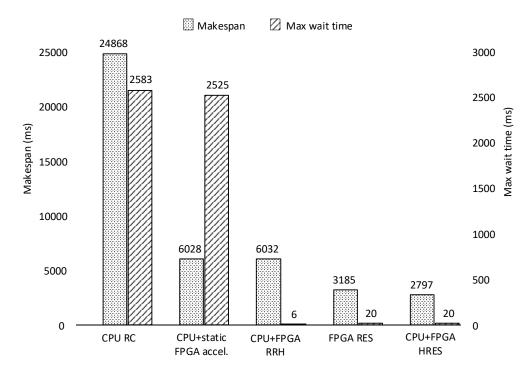

|   | 6.2         | Resou                        | rce Utilisation and System Performance                   | 105 |  |

|   |             | 6.2.1                        | Analysis of Resource Utilisation and Performance         | 107 |  |

|   |             | 6.2.2                        | Summary                                                  | 107 |  |

|   | 6.3         | Cost o                       | f Multi-tenancy Support                                  | 107 |  |

|   |             | 6.3.1                        | Analysis of Resource and Performance Overhead            | 108 |  |

|   |             | 6.3.2                        | Summary                                                  | 109 |  |

|   | 6.4         | Resilie                      | ence and Maintenance of Multi-node Systems               | 110 |  |

|   |             | 6.4.1                        | Mitigation Scenarios for Fault Tolerance/Resilience      | 111 |  |

|   |             | 6.4.2                        | Analysis of System Maintenance                           | 113 |  |

|   |             | 6.4.3                        | Summary                                                  | 113 |  |

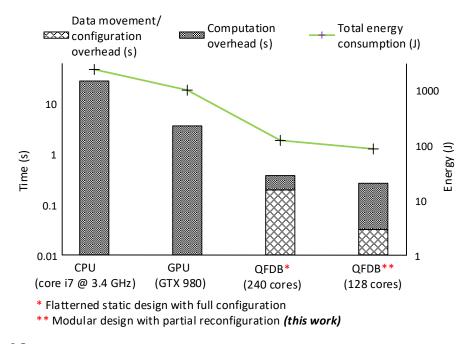

|   | 6.5         | Scalab                       | ility and Energy Efficiency                              | 114 |  |

|    |        | 6.5.1   | Analysis of Scalability and Energy Efficiency           | 117 |

|----|--------|---------|---------------------------------------------------------|-----|

|    |        | 6.5.2   | Summary                                                 | 119 |

|    | 6.6    | Chapte  | er Summary                                              | 119 |

| 7  | Con    | clusion |                                                         | 120 |

|    | 7.1    | Summ    | ary of Contributions                                    | 120 |

|    |        | 7.1.1   | A Model of FPGA Virtualisation on Heterogeneous Comput- |     |

|    |        |         | ing Platforms                                           | 120 |

|    |        | 7.1.2   | A Tool and API for Bitstream Abstraction                | 120 |

|    |        | 7.1.3   | Design Methodology and System Implementation            | 121 |

|    |        | 7.1.4   | System Prototype and Evaluation                         | 121 |

|    | 7.2    | Future  | Works                                                   | 121 |

|    |        | 7.2.1   | Security for Multi-tenancy FPGA-virtualised Systems     | 121 |

|    |        | 7.2.2   | High-speed Configuration Infrastructure                 | 122 |

|    |        | 7.2.3   | Vendor-independent FPGA Platforms for Education and Re- |     |

|    |        |         | search Purposes                                         | 122 |

| Bi | bliogı | aphy    |                                                         | 124 |

| A  | IPR    | DF      |                                                         | 136 |

|    | A.1    | Introdu | uction                                                  | 136 |

|    | A.2    | Relate  | d Work                                                  | 140 |

|    |        | A.2.1   | Isolation Design Flows                                  | 140 |

|    |        | A.2.2   | Partial Reconfiguration Tools                           | 140 |

|    |        | A.2.3   | Designing for Reliability                               | 140 |

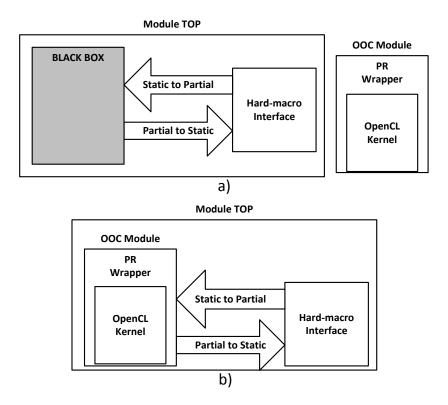

|    | A.3    | The IP  | PRDF Flow                                               | 141 |

|    |        | A.3.1   | Overview                                                | 141 |

|    |        | A.3.2   | Static Design                                           | 142 |

|    |        | A.3.3   | Module Design                                           | 144 |

|    | A.4    | Case S  | Study I: Triple Modular Redundancy                      | 144 |

|    |        | A.4.1   | System Implementation                                   | 146 |

|    |        | A.4.2   | Error Detection and Recovering Schemes                  | 147 |

|    |        | A.4.3   | Result                                                  | 149 |

|    | A.5    | Case S  | Study II: Single-chip Cryptographic Design              | 151 |

|    |        | A.5.1   | System Implementation                                   | 152 |

|    |        | A.5.2   | Result                                                  | 152 |

| A.6 Conclusion |  |

|----------------|--|

|----------------|--|

## **List of Tables**

| 1.1 | Comparison between a software OS and the proposed model of FPGA virtu-       |     |

|-----|------------------------------------------------------------------------------|-----|

|     | alisation.                                                                   | 23  |

| 2.1 | HLS Development Frameworks.                                                  | 41  |

| 2.2 | Comparision of shells                                                        | 45  |

| 3.1 | Resource information in the Xilinx Virtex-6, and 7-Series families           | 51  |

| 3.2 | Resource information in the UltraScale and UltraScale+ families              | 51  |

| 3.3 | BitMan functions                                                             | 58  |

| 3.4 | Performances of BitMan (B) and Maverick (M)'s bitstream generation           | 58  |

| 3.5 | BitMan performance on overlay architecture's support                         | 62  |

| 3.6 | Overheads of bitstream generation for a partial region                       | 63  |

| 4.1 | Resource overheads for bus virtualisation at the logical and physical levels | 74  |

| 4.2 | Available resources for 1 slot of on the ZCU102 platform and the UltraZed &  |     |

|     | Ultra96 platforms.                                                           | 80  |

| 4.3 | The overheads of two implementation options on the ZCU102 and Ultra-         |     |

|     | Zed/Ultra96 platforms.                                                       | 81  |

| 4.4 | The compilation flow's bitstream XML keyword description                     | 84  |

| 4.5 | Module compilation overhead: the Xilinx PR flow vs. the decoupled compi-     |     |

|     | lation flow.                                                                 | 88  |

| 5.1 | The overhead of using the SMMU.                                              | 98  |

| 6.1 | Matrix Multiplication (MM) and Discrete Cosine Transform (DCT) show cases.   | 102 |

| 6.2 | Shell update latency breakdown                                               | 112 |

| 6.3 | Throughput of ICAP-based controller in intra- and inter-chip configuration   | 117 |

| A.1 | Isolation Design Flows' features and supports.                               | 138 |

| A.2 | Available primitives on various resource slots and required elements for dif-              |     |

|-----|--------------------------------------------------------------------------------------------|-----|

|     | ferent modules                                                                             | 146 |

| A.3 | Available resources in <i>ISO_K0</i> and <i>ISO_K1</i> partial regions and size of partial |     |

|     | bitstream to reconfigure each region.                                                      | 154 |

# **List of Figures**

| The U.S. FPGA Market by applications                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The organisation of a heterogeneous CPU+FPGA computing system 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Analogies between the software operating system concepts and the proposed    |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| FPGA virtualisation model for heterogeneous computing systems.               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| The proposed abstractions and their functional roles in the FPGA develop-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| ment/deployment process. Note that the work of scheduler and driver/kernel   |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| library is done by A. Vaishnav, while the remaining parts are core contribu- |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| tions of this PhD thesis.                                                    | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Decoupled compilation flow for FPGA virtualisation.                          | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Contributions of this PhD thesis                                             | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| A typical FPGA vendor's PR design flow.                                      | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Overview of the GoAhead PR toolflow                                          | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

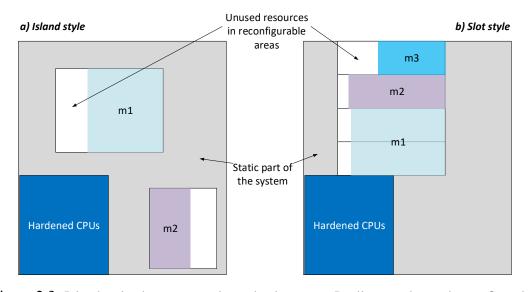

| Island style placement vs slot style placement.                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

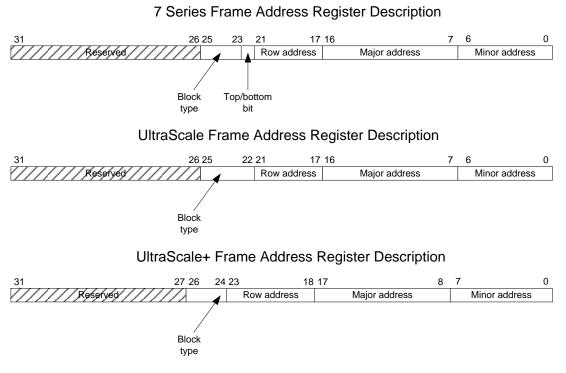

| 7-Series, UltraScale and UltraScale+'s Frame Address Register Descriptions.  | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

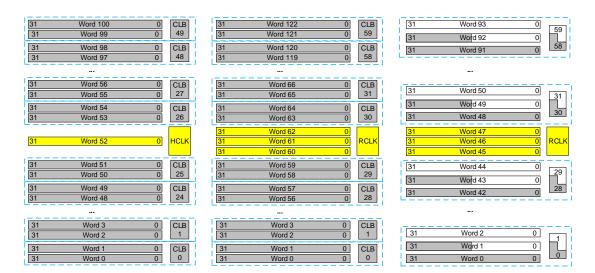

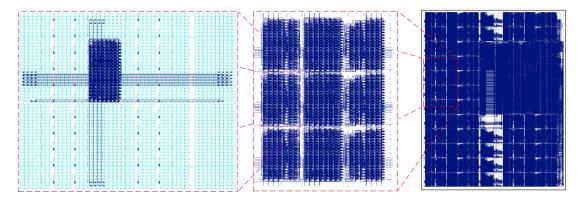

| Frame configurations for a CLB column in the 7-Series (left), UltraScale     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| (middle), and UltraScale+ (right) devices                                    | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

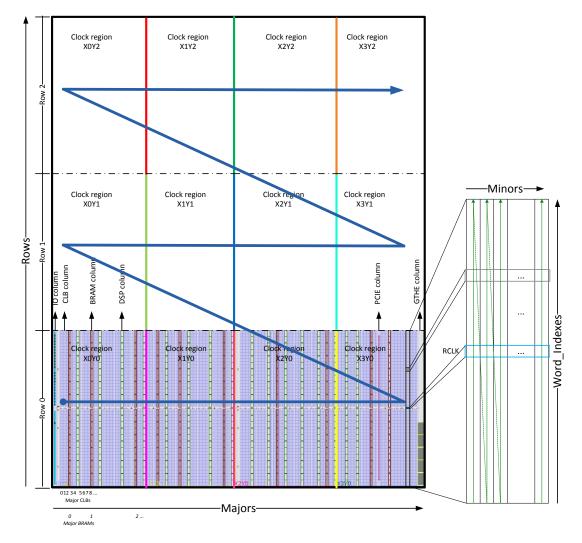

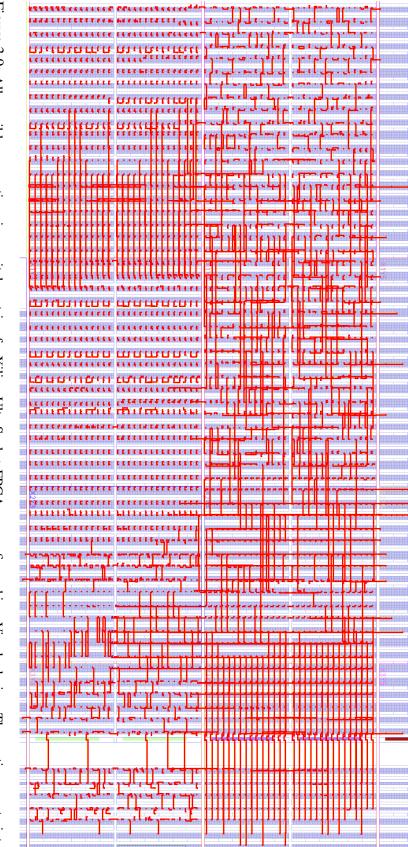

| Overview of Kintex UltraScale XCKU025's device layout                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

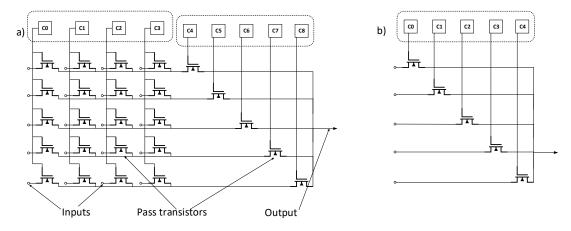

| Switch matrix multiplexer implementation.                                    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

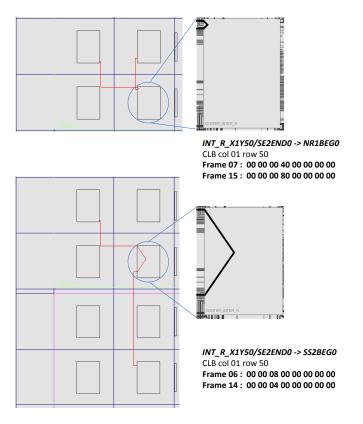

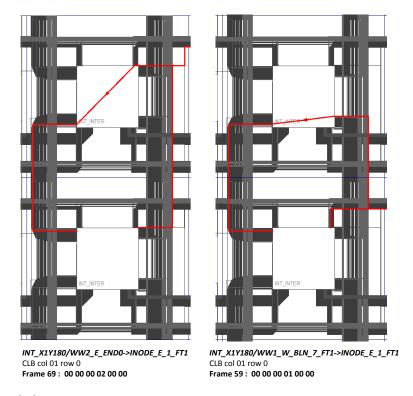

| Example of bitstream encodings for routing in the 7-Series family            | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Example of bitstream encodings for routing in the UltraScale+ family         | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

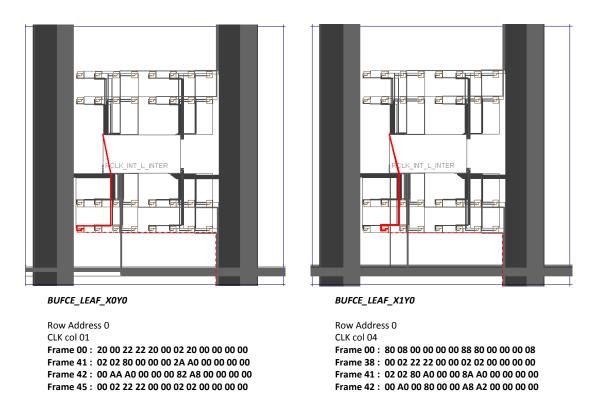

| Clock resource encodings of 7-Series FPGAs in bitstream.                     | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Clock resource encodings of UltraScale+ FPGAs in bitstream.                  | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Possible connections in a switch matrix of a Xilinx UltraScale+ FPGA         | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| The BitMan process.                                                          | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

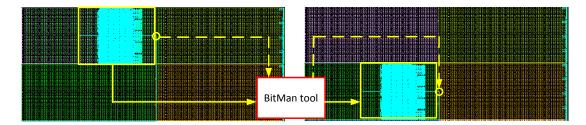

| An example of module relocation.                                             | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

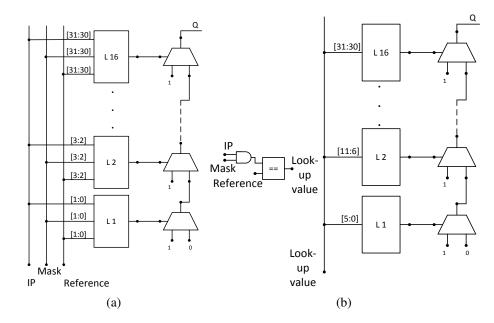

| Conventional CAM (a) vs LUT-modifiable CAM (b)                               | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                              | The organisation of a heterogeneous CPU+FPGA computing system Analogies between the software operating system concepts and the proposed FPGA virtualisation model for heterogeneous computing systems The proposed abstractions and their functional roles in the FPGA development/deployment process. Note that the work of scheduler and driver/kernel library is done by A. Vaishnav, while the remaining parts are core contributions of this PhD thesis |  |

| 3.13       | Performances of ROB and BitMan.                                            | 62         |  |

|------------|----------------------------------------------------------------------------|------------|--|

| 3.14       | The EFCAD flow                                                             |            |  |

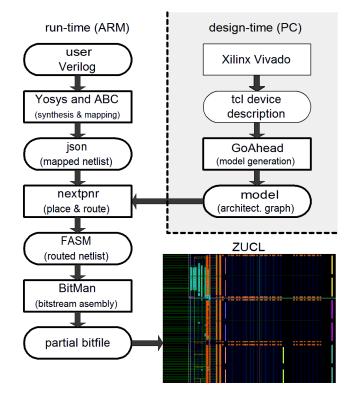

| 4.1        | The decoupled compilation flow.                                            | 68         |  |

| 4.2        | The overall organisation of an FPGA-virtualised system                     | 70         |  |

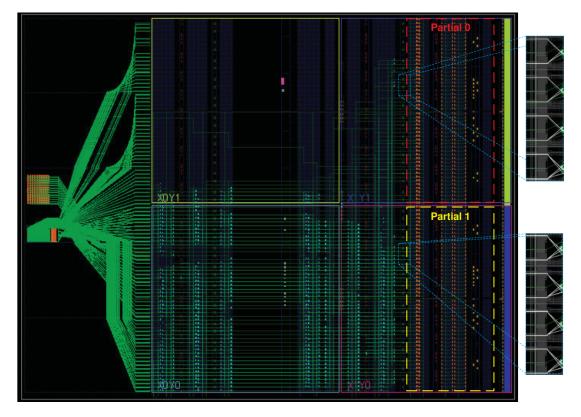

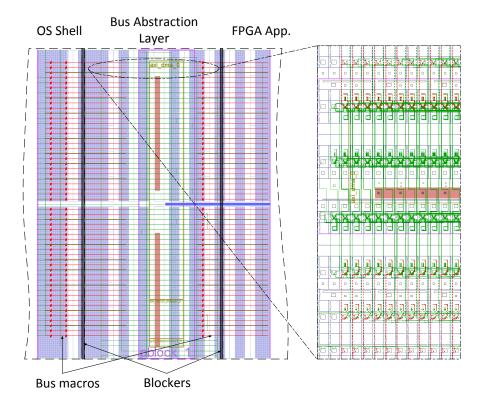

| 4.3        | The physical implementation on the Zybo platform                           | 71         |  |

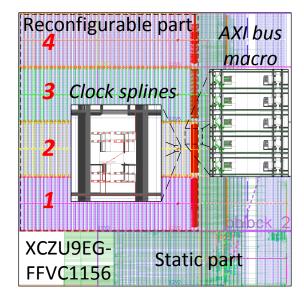

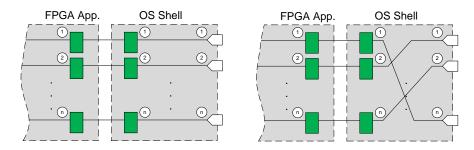

| 4.4        | The implemented static system on the ZCU102 platform                       | 72         |  |

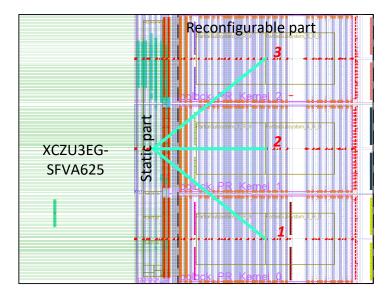

| 4.5        | The physical implementation on the UltraZed and Ultra96 platforms          | 72         |  |

| 4.6        | An example for bus virtualisation                                          | 73         |  |

| 4.7        | Implementation of a bus abstraction layer on UltraZed/Ultra96 platforms    | 75         |  |

| 4.8        | I/O FPGA virtual pins                                                      | 75         |  |

| 4.9        | I/O Virtualisation                                                         | 76         |  |

| 4.10       | The module compilation process.                                            | 78         |  |

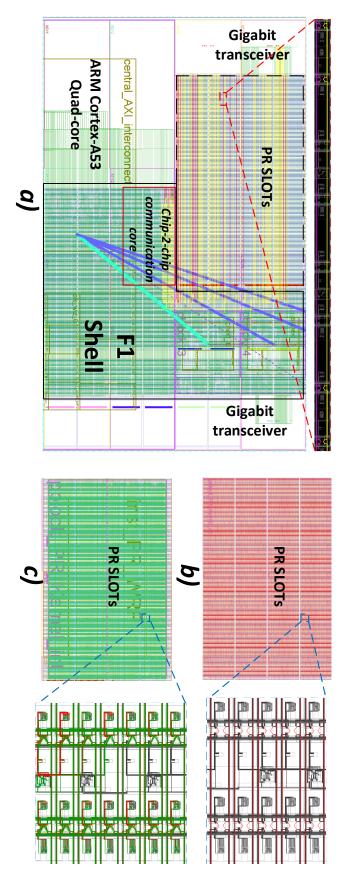

| 4.11       | Options of module compilation                                              | 81         |  |

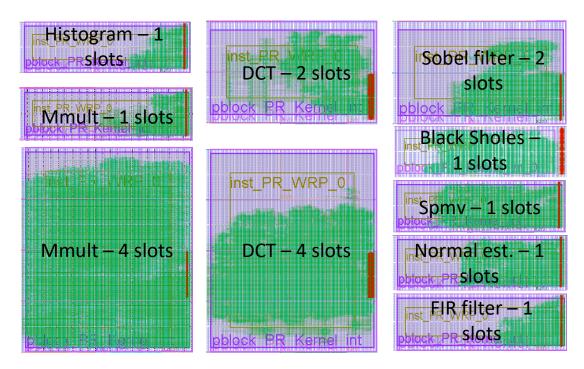

| 4.12       | Physical implementation designs on the Zybo platform                       | 83         |  |

| 4.13       | Physical implementation designs on the ZCU102 platform                     | 84         |  |

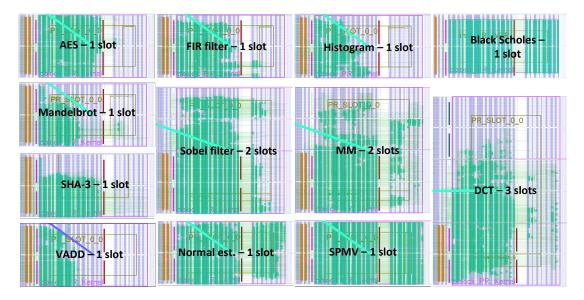

| 4.14       | Physical implementation designs on the UltraZed and Ultra96 platforms      | 85         |  |

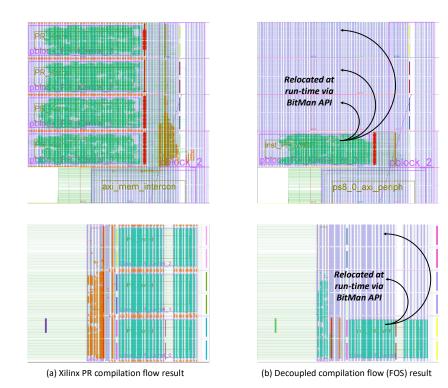

| 4.15       | Implemented results from the Xilinx PR flow and the decoupled compilation  |            |  |

|            | flow                                                                       | 86         |  |

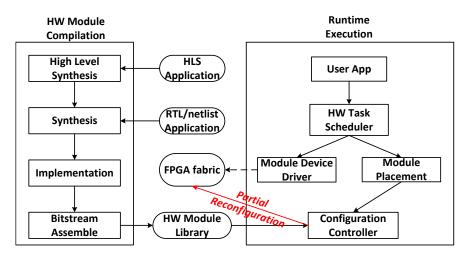

| 5.1        | Hardware (HW) module compilation steps and the run-time execution envi-    |            |  |

|            | ronment for hardware modules                                               | 91         |  |

| 5.2        | Run-time execution and management                                          | 92         |  |

| 5.3        | The configuration controller's hardware module placement process           | 94         |  |

| 5.4        | Resource allocation for tasks from different scheduling policies           | 95         |  |

| 5.5        | The implementation of the ARM SMMU in the memory system                    | 96         |  |

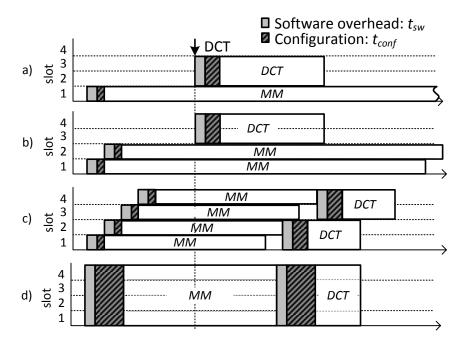

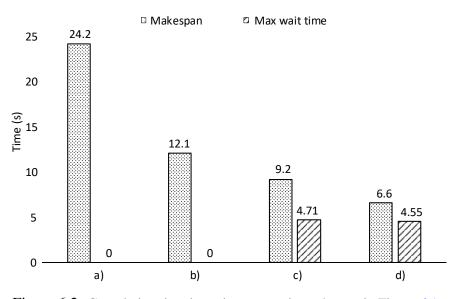

| 6.1        | Various instantiation and execution schemes for Matrix Multiplication (MM) |            |  |

|            | and Discrete Cosine Transform (DCT) kernels.                               | 104        |  |

| 6.2        | Completion time in various execution schemes in Figure 6.1                 | 104        |  |

| 6.3        | Comparison of different scheduling policies on CPU+FPGA platforms          | 106        |  |

| 6.4        |                                                                            |            |  |

| 0          | Cost of security and virtualisation.                                       | 109        |  |

| 6.5        | Cost of security and virtualisation                                        | 109<br>111 |  |

|            |                                                                            |            |  |

| 6.5        | The cluster setup for the case study of live migration                     | 111        |  |

| 6.5<br>6.6 | The cluster setup for the case study of live migration                     | 111        |  |

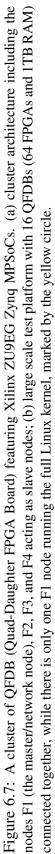

| 6.8  | The ECOSCALE platform with 16 QFDBs (64 FPGAs and 1TB RAM) is                |     |  |

|------|------------------------------------------------------------------------------|-----|--|

|      | used in this case study.                                                     | 116 |  |

| 6.9  | Execution latency and energy consumption of Michelsen on different deploy-   |     |  |

|      | ing platforms.                                                               | 118 |  |

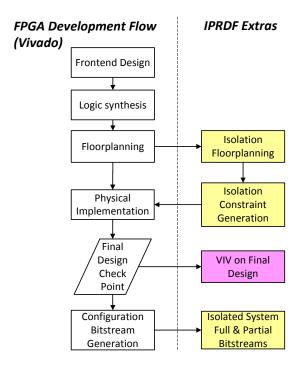

| A.1  | Isolated Partial Reconfiguration Design Flow (IPRDF)                         | 141 |  |

| A.2  | An example of a 16-bit bus for system communication                          | 142 |  |

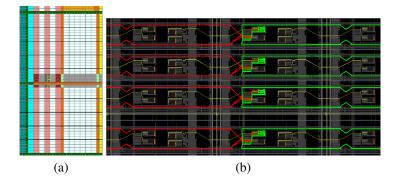

| A.3  | 3 Module placement, communication tunnels and blockers for the selected par- |     |  |

|      | tial module                                                                  | 143 |  |

| A.4  | Partial slots with various FPGA primitive slots                              | 144 |  |

| A.5  | Block diagram of the TMR system.                                             | 145 |  |

| A.6  | Two different error detection and recovering schemes                         | 148 |  |

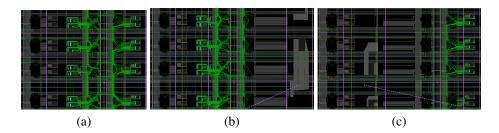

| A.7  | Implemented options of a Video Overlay Generator module                      | 150 |  |

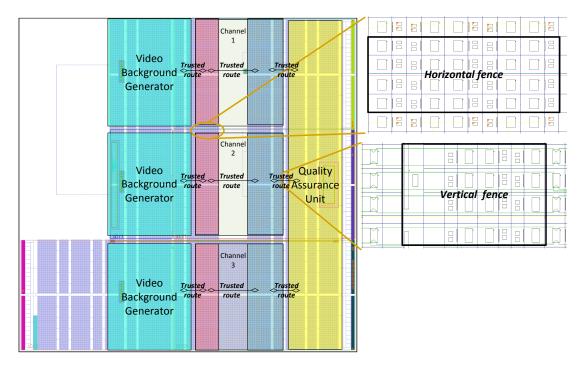

| A.8  | System layout of the TMR design implemented on a <i>XC7Z020</i> FPGA         | 151 |  |

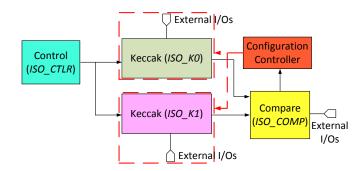

| A.9  | The single-chip cryptographic (SCC) system's block diagram.                  | 151 |  |

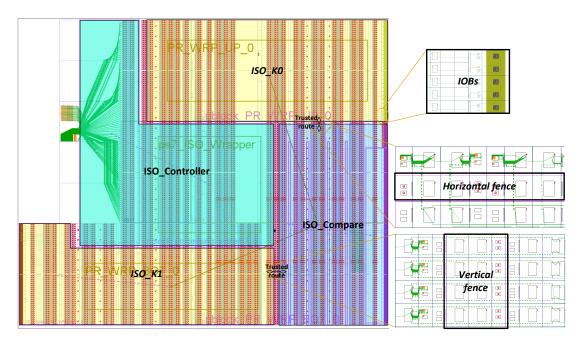

| A.10 | System layout of the SCC design implemented on the <i>XC7Z020</i> FPGA       | 153 |  |

## Abstract

Field Programmable Gate Arrays (FPGAs) can be utilised to speed up applications by two orders of magnitude as compared to running on conventional CPUs. However, designing FPGA accelerators still remains challenging for most users. Furthermore, despite the trend of integrating FPGA resources into high-performance and cloud computing systems, FPGA management is still immature commonly following a run-tocompletion execution model and with providing no abstraction layers to underlying hardware. Thus, FPGA virtualisation is highly desired to provide an abstraction level for FPGA development and deployment in complex heterogeneous CPU+FPGA computing systems which provide us an opportunity to adapt the workload on either software (running on CPUs) or hardware (running on FPGAs). This PhD thesis aims at promoting FPGA virtualisation for such heterogeneous computing systems ranging from embedded, to edge, to high-performance and cloud nodes. Consequently, this thesis proposes a fully FPGA-virtualised computing model to tackle these obstacles on complex heterogeneous CPU+FPGA systems. Moreover, partial reconfiguration is one of the key techniques to implement the proposed model, yet has still significant limitations which prevented us to implement such model on real hardware. These limitations motivated this PhD project and resulted in the development and implementation of several solutions to overcome these limitations, and hence, advance the partial reconfiguration technique towards the propsed fully FPGA-virtualised computing model. Combining this new capability of partial reconfiguration with other academic design tools, a novel design methodology has been developed to realise the proposed model on real hardware. Finally, resulting systems of the proposed design methodology on various heterogeneous computing platforms have shown significant improvements in compute performance thanks to the here implemented FPGA-virtualised techniques.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

## Acknowledgements

First and foremost, I would like to express my deep gratitude to my supervisor, Dr. Dirk Koch, for his patient guidance, enthusiastic support, and strong encouragement. His vision, experience and expertise helped to clarify my doubts and overcome the hurdles. I also thank Dr. James Garside, my co-supervisor, for his valuable feedback and advice.

I appreciate my friends Anuj Vaishnav, Edson Horta, Malte Vesper, Jose Raul Garcia, Kristiyan Manev and Athanasios Stratikopoulos for their help, support, encouragement, deep insights, thorough discussions, and fruitful collaborations during my research of this PhD project. People from APT group are also thankful for the positive and professional research environment.

I also thank to K. Georgopoulos, A. Ioannou, I. Mavroidis, and P. Malakonakis from the ECOSCALE project for the friendly support and effective collaborations.

Finally, I would like to thank my parents, my loving family, and my dear Vietnamese friends in Manchester whose support and understanding helped me to achieve this milestone.

This work is supported by the European Commission under the H2020 Programme and the ECOSCALE project (grant agreement 671632).

## Chapter 1

## Introduction

People who are really serious about software should make their own hardware.

Alan Kay

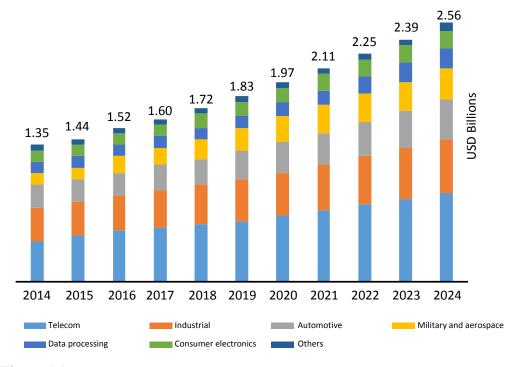

Field Programmable Gate Array (FPGA) devices can be used not only to substantially accelerate applications, but they are also able to achieve these performance advantages with fairly low power overhead [CSPJ03]. Therefore, more and more software applications such as deep learning [AOC<sup>+</sup>17], computer vision [JCP<sup>+</sup>10], telecommunication [BCB18], and networking [LMW<sup>+</sup>07] are being implemented as FPGA-based accelerators to exploit high performance and energy efficiency. Moreover, with the capability of reconfiguration and short time-to-market, the demand for FPGAs has increased in many industrial domains, as summarised in Figure 1.1.

However, FPGA accelerators are difficult to develop for most of software developers as they have to deal with new programming languages/paradigms, and/or coding styles, as well as several low-level system development including IP cores, system integration, bootloaders, and drivers which can be error-prone and time-consuming. In addition, despite the availability of large capacity devices and demand for more complex applications, FPGA management is still rudimentary without real abstraction layers to underlying resources. This renders FPGA acceleration similar to the traditional bare-metal embedded application use case. In those systems, applications are able to access the underlying hardware freely but are not able to switch to another application arbitrarily or to start new processes at run-time.

There are two major types of FPGA systems: 1) heterogeneous (SoC-based) computing systems, such as Intel Xeon-Arria hybrid chips [Huf], Xilinx Adaptive Compute Acceleration Platform [Xil19a], and Xilinx Zynq UltraScale+ MPSoC devices [Xil17b], in which CPUs and FPGAs are tightly coupled on the same die; and 2) PCIe-based systems, which are targeting high performance computing (HPC) and data centre markets. Hence, it is worth to highlight the differences of architecture and organisation between the SoC-based and PCIe-based systems.

Figure 1.1: The U.S. FPGA Market by applications, 2014 – 2024 (USD Billion) [Gra18]

A heterogeneous computing system can utilise the built-in system bus interface (such as ARM AMBA [ARMa]) to communicate with main memory and the host CPU. Therefore, no reconfigurable logic resources have to be used to implement a PCIe core and DDR controllers, which can contribute as much as 70% of the resource utilisation of the PCIe-based static system, as reported in [VKP17]. Furthermore, the bus interconnect that is required to connect the different modules with memory and resources needed to cross clock domains between kernel and DDR memory is hardened on heterogeneous devices. The hardened bus interconnect allows for higher bus clock frequencies than in PCIe-based systems. An SoC-based system allows accelerators working directly on the main memory used by the CPU, saving the transfers to and from dedicated FPGA memory required by PCIe-based counterparts. Therefore, an SoC-based system is often able to deliver higher clock frequency, more efficient memory access, and lower energy requirements, while a PCIe-based system provides space for larger kernels and allows choosing the host CPU alongside more various host memory configurations.

Since this PhD project aims at deploying reconfigurable resources in high performance computing systems as well as data centres [MPL<sup>+</sup>16, SVC<sup>+</sup>16], there is a need to adapt swiftly to changing workloads and to a different number of tasks to execute [MPL<sup>+</sup>16]. This swift adaptability does not fit the traditional methods of operating FPGAs. Moreover, to achieve high utilisation, individual systems often have a number of active tasks, each operating without any impact or knowledge of each other. For such systems, it would be highly desirable to have a middleware that can automatically adapt for any workload scenario that may arise at run-time

in the best possible way.

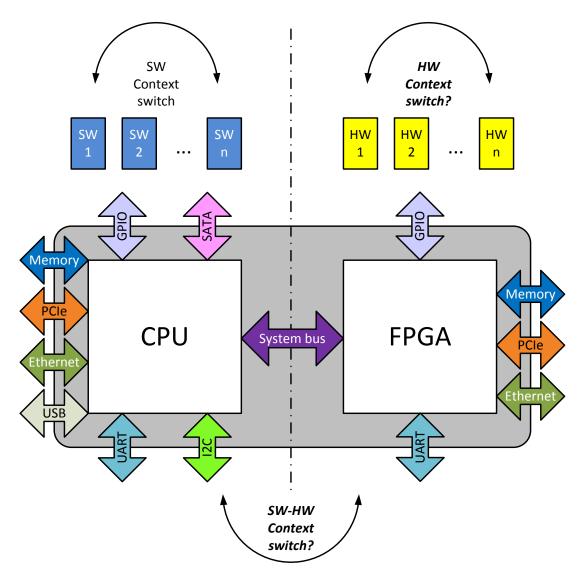

With the rise of heterogeneous computing systems, we have now an unprecedented opportunity to adapt the workload on either software (running on CPUs) or hardware (running on FPGAs), as shown in Figure 1.2. Therefore, FPGA virtualisation is required to provide an abstraction level for both FPGA development and deployment in an analogue fashion as known from traditional software operating systems (OSs).

Overall objectives of such FPGA virtualisation can be summarised in [VPK18a, VPK18b] as following:

- **Multi-tenancy**: The ability to serve multiple different users simultaneously by sharing the same FPGA fabric.

- **Resource Management**: Providing an abstraction/driver layer to the FPGA fabric and means of scheduling tasks to the CPU and the FPGA as well as monitoring the CPU+FPGA resource usage.

- Flexibility: Ability to support a wide range of acceleration workload, i.e. from custom accelerators handcrafted in RTL to accelerators designed in a High-Level Language (HLL) or a Domain Specific Language (DSL).

- **Isolation**: Providing the illusion of being a sole user of the FPGA resources for better security, fewer dependencies and correctness of the task execution.

- Scalability: A system/application that can scale to multiple different FPGAs or can support multiple different users at relatively low overhead.

- **Performance**: The impact of virtualisation should be minimal on the performance achievable and therefore, should maximise FPGA resources usable by the user application.

- Security: Ensuring that information of other tenants is not leaked and for safekeeping the infrastructure from malicious users. This also contributes to overall robustness of a system.

- Resilience: Ability to keep the system/service running despite failures.

- **Maintenance**: Ability to update hardware/software in a node without affecting the executing applications.

- **Design Productivity**: Improving the time-to-market and reducing the complexity of deploying a design to an FPGA from its software description.

Figure 1.2: The organisation of a heterogeneous CPU+FPGA computing system. Depending on the application, peripherals and memory may be connected to either the CPU, the FPGA fabric, or arbitrary to both. This implies some challenges, in particular if both parts the CPU and the FPGA need access to the peripherals or a shared memory. Moreover, although context switching on the CPU side (SW context switching) is a mature topic in computer science, performing context switching on the FPGA side (HW context switching) or between both sides (HW-SW context switching) is another challenge and open question.

The FPGA ecosystem is steadily improving and IP integration has become much easier thanks to a widespread adoption of the ARM Advanced Micro-controller Bus Architecture (AMBA) specification [ARMa]. Similarly, application development is now well-supported through standardised High-level synthesis (HLS) approaches, such as OpenCL [KHR]. More-over, partial reconfiguration (PR) [Koc12], a noticeable feature allowing FPGAs to change a portion of reconfigurable hardware circuitry while the rest of the FPGA is still functioning, can be utilised to decouple accelerator design from the underlying platform and to switch between various hardware applications arbitrarily. A PR system includes a *static part* which does not change the functionality during system operation, and the *reconfigurable part* with one or more *PR regions*. Therefore, combining these technologies would allow software developers building their accelerators once but instantiating them multiple times in the provided regions on the platform in a hot plug-and-play manner. Such kind of feature is essential towards building FPGA-virtualised systems. Despite this progress, there are still few examples of methodologies, toolflows, and systems available that fulfil the aforementioned objectives of FPGA virtualisation.

### **1.1** Motivation and Aims

The main motivation of this research is to advance the existing knowledge of FPGA virtualisation ranging from embedded/edge to high-performance/cloud computing systems. Thus, key research questions tackled in this thesis include:

- Models and Methodologies: How to efficiently virtualise and abstract resources in heterogeneous computing systems? What should the model of an FPGA-virtualised heterogeneous computing system be? How to speed up the design, implementation, and deployment of hardware applications?

- **Systems**: How to launch and manage multiple hardware tasks transparently? How to dynamically orchestrate software and hardware context switching in heterogeneous computing systems for better performance and better utilisation of resources? And how to protect data and execution of a specific user from another on a multi-tenanted platform?

- **Tools and Flows**: How to physically implement FPGA-virtualised heterogeneous computing systems at a high level of abstraction with the latest FPGA technology?

Therefore, this PhD project is going to 1) investigate state-of-the-art FPGA virtualisation techniques; 2) propose a novel approach/model to virtualise FPGA resources in heterogeneous computing systems; 3) explore novel design methodology, tools, and frameworks to implement the proposed approach; 4) propose a compilation path for productive application development;

5) provide an abstraction layer between accelerators and the underlying platform as a readyto-use hardware operating system (OS) infrastructure; 6) enable run-time support for running, sharing and swapping multiple accelerators; and 7) investigate mechanisms to make the system safer, more secure, and more resilient.

### **1.2** Contributions

To tackle the aforementioned research questions, this PhD thesis proposes a 1) novel model of FPGA virtualisation including three level of resource abstractions (i.e. infrastructure abstraction, development abstraction, and deployment abstraction) as well as 2) introducing a tool for bitstream abstraction supporting modern Xilinx FPGAs, 3) a novel design methodology targeting heterogeneous computing systems, and 4) FPGA-virtualised system prototypes, as discussed in the following paragraphs.

### 1.2.1 FPGA Virtualisation Model for Heterogeneous Computing Systems

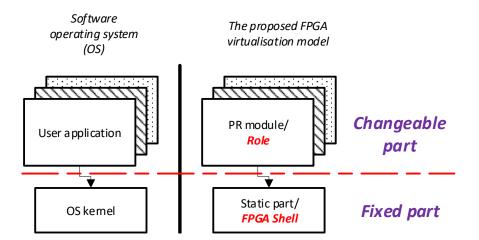

Based on the deep understanding and thorough analysis of state-of-the-art trends and techniques on FPGA virtualisation [VPK18a] as well as due to the increasing popularity of heterogeneous computing systems (see Figure 1.2), this thesis proposes that FPGA resources in heterogeneous systems should be abstracted, managed, and virtualised in an analogous way as the way that is known from software operating systems (OSs). With this model, we can contrast and compare OS services known from software system with services needed for FPGA management. The equivalent concept of the software OS kernel is named the *FPGA shell*, or shell for short and it provides all essential infrastructure, whereas the user applications (often called *roles*) do perform the actual work. A brief comparison between a software OS and the proposed model of FPGA virtualisation is shown in Table 1.1. Ultimately, the proposed model is a great fit to partial reconfiguration (PR) of FPGAs, in which a *shell* is located in the fixed part of a PR system, while *roles* are assigned to reconfigurable parts, called *slots* (i.e. PR regions), and deployed at run-time in a hot plug-and-play manner, as illustrated in Figure 1.3.

To implement the proposed model for achieving the aforementioned objectives of FPGA virtualisation, this thesis proposes the following abstractions:

- **Infrastructure abstraction:** the underlying heterogeneous resources including their various layouts and available primitives should be designed, abstracted and managed as shells to provide common essential services, such as system bus communication, I/O access, and memory access to the deploying roles.

- Development abstraction: the requirements for this level of abstraction are:

Figure 1.3: Analogies between the software operating system concepts and the proposed FPGA virtualisation model for heterogeneous computing systems.

1) In this project, shell and roles are able to be designed independently, and hence, to be updated individually as long as the pre-defined system communication and the preallocated resources of a slot remain the same (i.e. decoupling the development of shell and roles). 2) A role should be compiled once and reused as many times as possible regardless of its physical mapping to the shell.

Requirement 1 of decoupled compilation may lead to *internal resource fragmentation* [Koc12] as a role can occupy more or less resources than what are available in a slot. We have further targeted this issue by utilising design space exploration (DSE) techniques [MMRL17], providing the flexibility of 2D module-stitching at run-time [PHK<sup>+</sup>18] (for roles occupying much less resources than what a slot can provide), or merging multiple adjacent slots to host a big role [PVVK18] (for roles occupying more resources than what a slot can provide), as explained further in Chapter 4. Moreover, Requirement 2 is not supported by state-of-the-art vendor PR flows because a role needs to be compiled many times to *all possible mappings* to the shell, as discussed in Section 2.2.

• Deployment abstraction: at this level of abstraction, there are four requirements:

1) Roles can be deployed on top of the underlying shell in a hot plug-and-play manner. 2) A user may run multiple roles, or multiple users may run one or multiple roles on the same shell to utilise the underlying resource, to reduce each user's waiting time and to enhance the overall system throughput. Moreover, 3) temporal and spatial resource sharing between roles via hardware/hardware-software context switching, and cooperative scheduling must be performed transparently from the user's point of view. Finally, 4) role deployment must not imply any security threat to the whole system, including the underlying hardware and other users [MLG<sup>+</sup>20].

|                     | Software OS                 | Proposed model                        |

|---------------------|-----------------------------|---------------------------------------|

| Organisation        | * Fixed part: OS kernel     | * Fixed part: FPGA shell (i.e.        |

|                     |                             | static infrastructure)                |

|                     | * Changeable part: user ap- | * Changeable part: <i>roles</i> (i.e. |

|                     | plications                  | acceleration modules)                 |

| Objects of hardware | CPU, memory, and I/Os       | Physical FPGA primitives              |

| abstractions        |                             | (may include memory and               |

|                     |                             | FPGA I/Os)                            |

| Resource sharing/-  | Time domain                 | Space and time domains                |

| management          |                             |                                       |

Table 1.1: Comparison between a software OS and the proposed model of FPGA virtualisation.

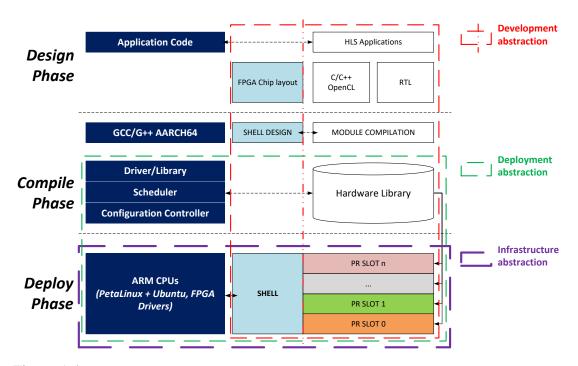

The positions and functional roles of these proposed abstractions in real-world are illustrated in Figure 1.4. The *infrastructure abstraction* is provided by shells according to the physical FPGA layouts as well as the essential infrastructure, as introduced in [PCC<sup>+</sup>14, KBT08], while the author of this thesis has implemented shells for heterogeneous platforms ranging from Xilinx Zynq-7000 to Xilinx Zynq UltraScale+ devices. Moreover, the *development abstraction* and the *deployment abstraction* are original contributions of this PhD project as they are direct results from an enhanced partial reconfiguration approach (via bitstream abstraction), as discussed in Section 1.2.2 and Chapter 3, and a novel compilation flow, as discussed in Section 1.2.3 and Chapter 4. Ultimately, operational system prototypes for CPU+FPGA heterogeneous computing systems including the proposed abstractions are presented and evaluated against the objectives of FPGA virtualisation, as described in Section 1.2.4 and Chapter 6.

#### **1.2.2** Bitstream Abstraction

In the proposed model for FPGA virtualisation, partial reconfiguration [Koc12] is playing a key role to improve design productivity, to perform hardware context switching, to enhance the resilience as well as the maintainability of the system. However, despite of current progresses, state-of-the-art approaches of partial reconfiguration have significant limitations which lessen its potential contribution to FPGA virtualisation dramatically, as pointed out in a recent survey [VF18]. Hence, this thesis has explored an alternative approach to leverage the principle of partial reconfiguration (PR) for FPGA virtualisation. PR is innovated with design productivity, system efficiency, and physically isolated modularity [PHK<sup>+</sup>18] in mind.

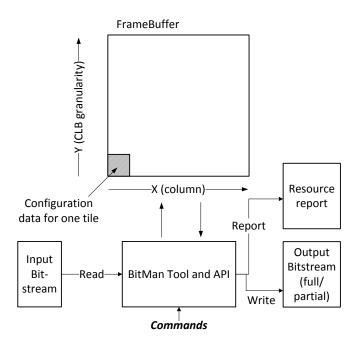

At the heart of the problem, the ability to adapt FPGA designs at bitstream level for latest architectures is the crucial missing key for any PR flow towards FPGA virtualisation (see Section 2.2). This thesis, therefore, has provided a generic tool and API called BitMan [PHK17]

Figure 1.4: The proposed abstractions and their functional roles in the FPGA development/deployment process. Note that the work of scheduler and driver/kernel library is done by A. Vaishnav, while the remaining parts are core contributions of this PhD thesis.

for this FPGA bitstream adaptation purpose. At the time of this PhD thesis written, BitMan is the only tool which can support all recent Xilinx FPGAs such as Spartan-6, Virtex-6, 7-Series, UltraScale and UltraScale+ devices, as discussed detail in Chapter 3.

BitMan, thus, complements the PR flow in [Koc12] and contributes two pivotal attributes: 1) to enable the *decoupled compilation flow* for development abstraction; and 2) to dynamically switch PR modules (i.e. roles) at run-time via the *Configuration Controller* (See Figure 1.6) for deployment abstraction to implement the proposed model of FPGA virtualisation in heterogeneous computing systems.

#### **1.2.3 Decoupled Compilation Flow for FPGA Virtualisation**

Although many progresses have been made to improve the design productivity and the ease of FPGA application deployment [Ama] such as High-Level Synthesis [CLN+11, CCA+13], IP integration [Xild, Xilc], and partial reconfiguration [VF18], there are very few notable solutions that allow direct application development such that software engineers can develop accelerators for hugely dynamic FPGA-based systems. Designing such a partially reconfigurable system still requires very specific knowledge in the FPGA domain and expertise in the vendors' partial reconfiguration toolchains, which is a challenge even for many experienced FPGA developers. Furthermore, user applications (roles) must be designed and implemented with the surrounding infrastructure (shell) as a monolithic system. This approach commonly causes unnecessarily lengthy design phase and even worse, a single change in either the application or the surrounding infrastructure will likely request the whole system to be rebuilt. Therefore, it is impossible to maintain or upgrade either shell or role independently. This limitation still remains in most of the state-of-the-art partial reconfiguration design flows [Xil18c, Alt17], as discussed in Chapter 2.

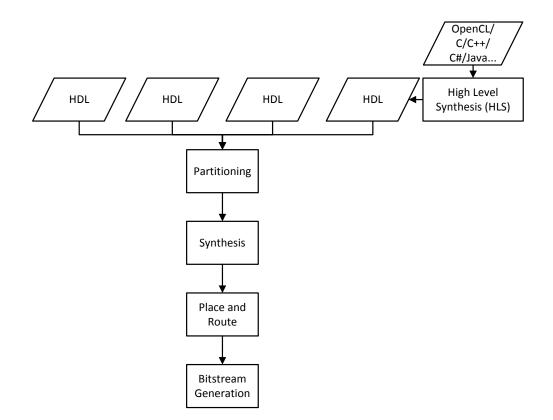

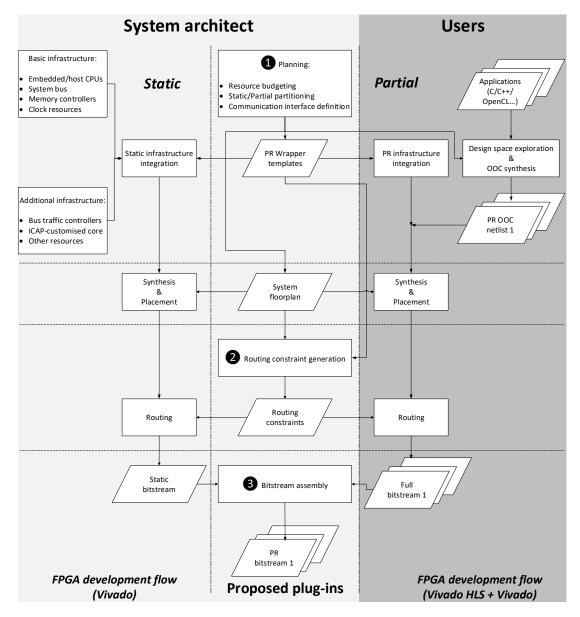

Thus we have introduced a novel design methodology to design FPGA shells and to compile hardware modules (roles) from user applications. A resulting shell provides the infrastructure abstraction on the targeting platform featuring multiple adjacent partial reconfiguration (PR) regions, called *slots*, having an identical resource layout. Module compilation for application development takes HLS/RTL/netlist descriptions to produce *relocatable accelerator partial bitstreams* in a fully software-centric design process [PVVK18], which essentially presents the development abstraction. Note that the BitMan tool, which were mentioned in Section 1.2.2, is an essential part of this compilation flow, as explained in Chapter 4. This module compilation also delivers prerequisites for the deployment abstraction by allowing users building their hardware modules once but instantiating them multiple times in the provided regions in a hot plug-and-play manner as well as implementing different implemented module variants that can share the reconfigurable resources at run-time. The development and deployment scenarios are similar to compiling a software binary from its source code and then running it on top of a software OS. The proposed compilation is summarised and compared to the conventional software counterpart in Figure 1.5.

To demonstrate this automatically implemented process, we have compiled applications written in RTL, OpenCL [GAPK16], and in C language as partially reconfigurable modules without manual intervention, as shown in Chapter 4. Although the Xilinx Vitis development flow [Xil20], released when this thesis was already submitted, can offer similar automatic compilation experience for heterogeneous computing systems, this decoupled compilation flow offers more attributes than the Vitis flow. For instance, this module compilation can be done independently from shell development process as long as they keep in pre-defined resource footprints for roles and the interface between shell and roles. In one showcase, we deliberately designed a shell and several roles in different Xilinx Vivado versions, and then launched roles on top of shell at run-time (see Section 6.1). Moreover, Vitis has not yet reached the level of flexibility introduced by this proposed compilation flow for compiling *relocatable PR modules*, as discussed further in Section 2.4. Note that the work in this thesis has been carried out, demonstrated, and published in [PVVK18, PPV<sup>+</sup>19, VPMK19] before the introduction of the Xilinx Vitis flow.

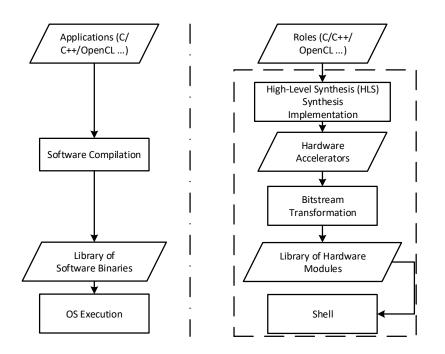

Figure 1.5: Left: conventional software compilation. Right: the proposed module compilation flow [PVVK18].

#### **1.2.4** System Prototypes

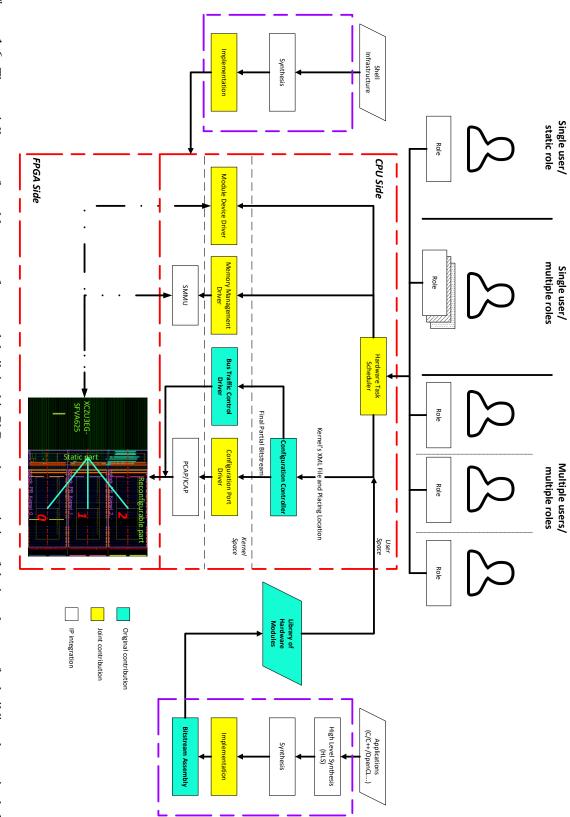

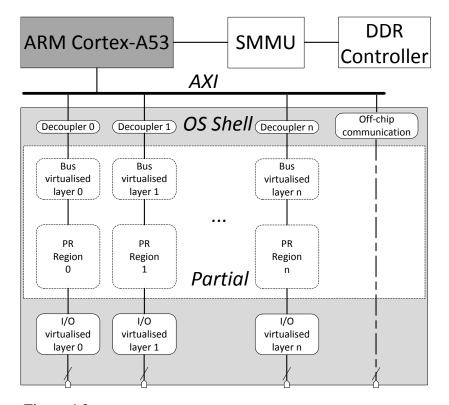

Four system prototypes [HSPK17, PHK<sup>+</sup>18, PVVK18, PPV<sup>+</sup>19] using different FPGA families, including Xilinx Zynq-7000 [Xil18e] and Zynq UltraScale+ [Xil17b] heterogeneous devices, have been built on top of the proposed methodology, tools, and framework. The systems are composed of three essential parts contributing to their distinct features: shell, the module compilation, and the run-time management. These systems, as shown in Figure 1.6, realised the proposed model of FPGA virtualisation by providing the following features:

- *Decoupled Implementation*: static systems (*shells*) and reconfigurable modules (*roles*) are implemented independently; supports most application design techniques such as HLS (OpenCL, C/C++), RTL (Verilog/VHDL), and netlist.

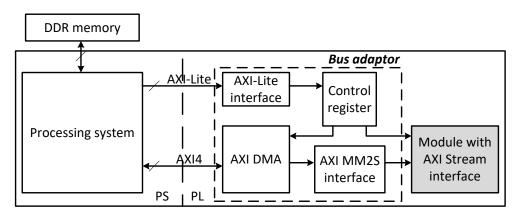

- *Bus Virtualisation*: supporting different AXI interfaces (Master/Slave/Stream as well as 32/64/128-bit data width) transparently.

- *I/O FPGA Virtualisation*: allowing the same reconfigurable module bitstream to be used multiple times in systems with different I/O layouts.

- *Run-time Flexibility*: supporting different partial configuration styles: 1) island-style (where a module is placed exclusively in a reconfigurable region); 2) slot-style (where

multiple modules can be daisy-chained within one shared region); and 3) 2-dimensional module placement as modules may occupy multiple adjacent regions.

- *Cooperative Scheduling*: allowing hardware context switching to adjust resource allocation dynamically and transparently through a user-friendly API. The research and implementation of run-time heterogeneous scheduling algorithms has been conducted by A. Vaishnav and interacts with the low-level FPGA API developed in this thesis project.

- *Memory Isolation*: through memory management enabling isolation of simultaneously running hardware tasks in multi-tenanted environments. The work of Linux kernel driver for this memory management is contributed by K. Paraskevas, while the author of this thesis is in charge of system integration and user interface.

- *Physical Module Isolation*: fulfilling the requirements for single chip cryptography (SCC) [NIS01] as well as building robust triple modular redundancy (TMR) systems. The here presented design methodology has been extended to guarantee module isolation requirements [PHK<sup>+</sup>18].

### **1.3 Thesis Structure**

This thesis is organised in seven chapters. In addition, an appendix provides another showcase in applying the proposed design methodology to build SCC and robust TMR systems. Brief descriptions of the content of the remaining six chapters are described in the following paragraphs.

#### **1.3.1** Chapter 2 – Background and Related Works

Since the primary idea of this PhD project is to leverage partial reconfiguration for FPGA virtualisation, this chapter discusses state-of-the-art partial reconfiguration toolflows and obstacles have been examined. Additionally, related works of bitstream manipulation and HLS framework for designing partially reconfigurable systems are being reviewed. Finally, shell-based systems are classified and examined to highlight the contributions of this PhD thesis amongst recent works.

#### **1.3.2** Chapter 3 – Bitstream Manipulation Tool and API

As the ability to adapt FPGA designs at binary (bitstream) level for modern FPGAs is highly desired for the proposed FPGA-virtualised model yet missing in state-of-the-art design methodology and deploying systems, this chapter describes our effort to fulfil this requirement. A tool

well as the reconfigurable roles and run-time services for configuring and running roles on the system. Figure 1.6: The partially reconfigurable system framework built in this PhD project consisting of design elements for building the static shell as

28

and API, called BitMan, has been developed and utilised to provide the development and deployment abstractions.

### **1.3.3** Chapter 4 – Decoupled Compilation Flow for FPGA Virtualisation

With the availability of academic design tools such as GoAhead/TedTCL and BitMan, a novel design methodology is introduced in this chapter to incorporate these academic tools and the Xilinx Vivado toolflow into a single decoupled compilation flow to design systems for the proposed FPGA-virtualised heterogeneous computing model. This design methodology essentially provides the development abstraction which decouples the development of the static shell and the reconfigurable roles. Moreover, static shells developed by this design methodology crucially provide the infrastructure abstraction to the underlying FPGA platforms. A number of FPGA-virtualised systems have been implemented and evaluated on top of various development platforms featuring different FPGA devices as well as families by utilising the proposed methodology.

#### **1.3.4** Chapter 5 – Run-time Management

The run-time management which ultimately provides the deployment abstraction is described in this chapter. Components of the run-time management including the configuration controller, the hardware task scheduler, the module device driver, and the memory isolation framework are presented.

#### **1.3.5** Chapter 6 – System Evaluation

Five case studies of the resulting systems are presented and evaluated against the aforementioned objectives of FPGA virtualisation in order to demonstrate the versatility of the here introduced FPGA virtualusation techniques in this Chapter.

#### **1.3.6** Chapter 7 – Conclusion

Finally, this chapter summarises this thesis and discusses future work, which has been enabled by the research carried out through this project.

### **1.4 Publications**

The research conducted throughout this project has been produced through the 16 research articles listed below.

- 1. K. D. Pham, E. Horta, and D. Koch, *BITMAN: a Tool and API for FPGA Bitstream Manipulations*, in *Design Automation and Test in Europe (DATE)*, 2017.

- E. Horta, X. Shen, K. D. Pham, and D. Koch, Accelerating Linux Bash Commands on FPGAs Using Partial Reconfiguration, in FPGAs for Software Programmers (FSP), 2017.

- 3. M. Vesper, D. Koch, and K. D. Pham, *PCIeHLS: an OpenCL HLS framework*, in *FPGAs for Software Programmers (FSP)*, 2017.

- 4. A. Vaishnav, K. D. Pham, D. Koch, and J. Garside, *Resource Elastic Virtualization for FPGAs using OpenCL*, in *Field-Programmable Logic and Applications (FPL)*, 2018.

- A. Vaishnav, K. D. Pham, and D. Koch, A Survey on FPGA Virtualization, in Field-Programmable Logic and Applications (FPL), 2018.

- K. D. Pham, A. Vaishnav, M. Vesper, and D. Koch, ZUCL: A ZYNQ UltraScale+ Framework for OpenCL HLS Applications, in FPGAs for Software Programmers (FSP), 2018.

- K. D. Pham, E. Horta, D. Koch, A. Vaishnav, and T. Kuhn, *IPRDF: an Isolated Partial Reconfiguration Design Flow for Xilinx FPGAs*, in *Multicore/Many-core Systems-on-Chip (MCSoC)*, 2018.

- 8. A. Vaishnav, K. D. Pham, and D. Koch, *Live Migration for OpenCL FPGA Accelerators*, in *Field-Programmable Technology (FPT)*, 2018.

- K. D. Pham, M. Vesper, D. Koch, and E. Hung, EFCAD an Embedded FPGA CAD Tool Flow for Enabling On-Chip Self-Compilation, in Field-Programmable Custom Computing Machines (FCCM), 2019.

- A. Vaishnav, K. D. Pham, and D. Koch, *Heterogeneous Resource-Elastic Schedul*ing for CPU+FPGA Architectures, in Highly-Efficient Accelerators and Reconfigurable Technologies (HEART), 2019.

- 11. A. Vaishnav, K. D. Pham, Kristiyan Manev, and D. Koch, *The FOS (FPGA Operating System) Demo*, in *Field Programmable Logic and Applications (FPL)*, 2019.

- K. D. Pham, Kyriakos Paraskevas, Anuj Vaishnav, Andrew Attwood, Malte Vesper, and D. Koch, ZUCL 2.0: Virtualised Memory and Communication for ZYNQ UltraScale+ FPGAs, in FPGAs for Software Programmers (FSP), 2019.

- K. Georgopoulos, K. Bakanov, I. Mavroidis, I. Papaefstathiou, A. Ioan-nou, P. Malakonakis, K. Pham, D. Koch, and L. Lavagno, A Novel Framework for Utilising Multi-FPGAs in HPC Systems, in Heterogeneous Computing Architectures: Challenges and Vision, Taylor and Franchis Group, 2019.

- A. Vaishnav, K. D. Pham, J. Powell, and D. Koch, FOS: A Modular FPGA Operating System for Dynamic Workloads, in arXiv, 2020.

- 15. K. Matas, T. La, N. Grunchevski, **K. D. Pham**, and D. Koch, *Invited Tutorial: FPGA Hardware Security for Datacenters and Beyond*, in *Field-Programmable Gate Arrays* (*FPGA*), 2020.

- K. Matas, T. La, K. D. Pham, and D. Koch, *Power-hammering through Glitch Amplification Attacks and Mitigation*, in *Field-Programmable Custom Computing Machines* (FCCM), 2020.

Papers are currently under review process:

- A. Vaishnav, K. D. Pham, J. Powell and D. Koch, FOS: A Modular FPGA Operating System for Dynamic Workloads, in ACM Transaction Reconfigurable Technology (TRETS).

- T. M. La, K. Matas, N. Grunchevskip, K. D. Pham, and D. Koch, FPGADefender: Malicious Self-Oscillator Scanning for Xilinx UltraScale+ FPGAs, in ACM Transaction Reconfigurable Technology (TRETS).

#### CHAPTER 1. INTRODUCTION

### **1.5 Open Source Releases**

This PhD thesis has also contributed the following open-source projects:

- BitMan: a Tool and API for FPGA Bitstream Manipulations.

Available at https://github.com/khoapham/bitman.git

- ZUCL: A ZYNQ UltraScale+ Framework for OpenCL HLS Applications.

Available at https://github.com/zuclfpl/zucl\_fsp.git

- 3. EFCAD an Embedded FPGA CAD Tool Flow for Enabling On-Chip Self-Compilation. Available at https://github.com/khoapham/efcad.git

- 4. FOS FPGA Operating System Demo

Available at https://github.com/khoapham/fos.git

### Chapter 2

## **Background and Related Works**

This too shall pass.

Rumi

### 2.1 Overview

To provide layers of abstraction and virtualisation for FPGA development and deployment, this PhD project is going to leverage partial reconfiguration (PR) of FPGAs. Therefore, basic concepts of PR and a brief overview of state-of-the-art PR flows, including industrial and academic flows, are provided in Section 2.2. Moreover, remaining problems of current PR approaches are further discussed to emphasise the need of conducting the work on bitstream abstraction/manipulation. Next, Section 2.3 provides background and related works for bitstream manipulation. Further, state-of-the-art compilation flows High-level Synthesis (HLS) applications are reviewed in Section 2.4. Finally, shell-based systems are analysed to identify our work amongst state-of-the-art ones in Section 2.5.

### 2.2 Partial Reconfiguration (PR)

Partial reconfiguration is a distinguished feature of FPGA technology in which a portion of the FPGA fabric can be reconfigured to change the functional behaviour and/or structure of the system whereas the remaining of the fabric can keep functioning. Hence, PR has been being an active research topic in the FPGA community. Ultimately, this PhD project is going to exploit partial reconfiguration to construct a novel compilation flow, which is used to implement such FPGA-virtualised systems as described in Chapter 1. Hence, this section is going to briefly review the topic focusing on design methodologies and toolchains as well as highlighting current

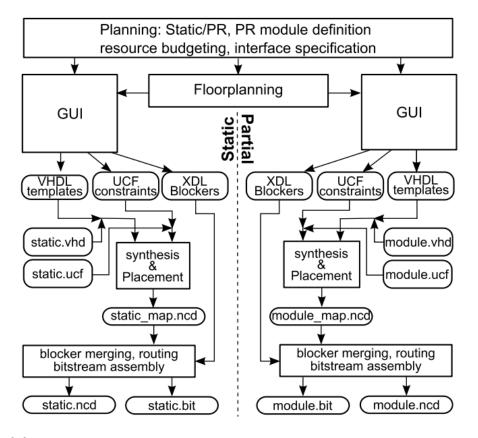

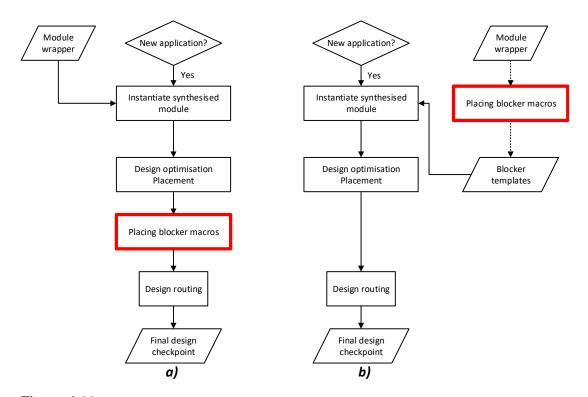

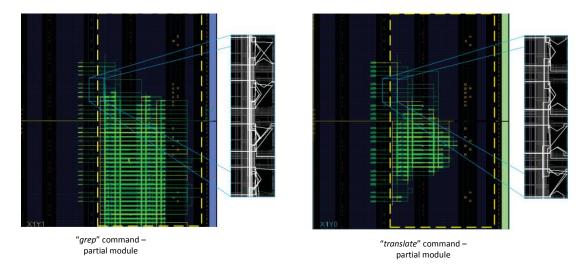

Figure 2.1: A typical FPGA vendor's PR design flow.

limitations which are preventing us to have a system which could fulfil the objectives of FPGA virtualisation.

#### 2.2.1 FPGA Vendors' PR Design Flows

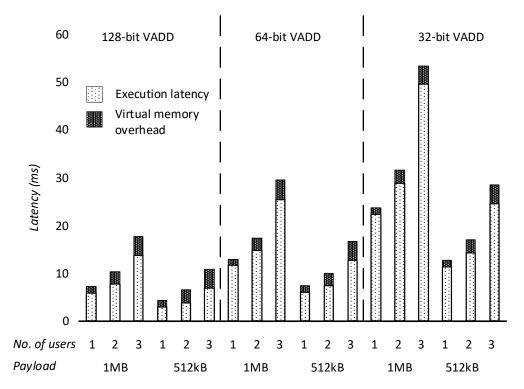

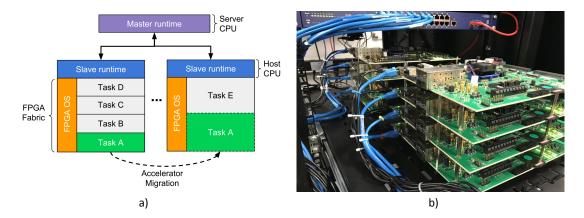

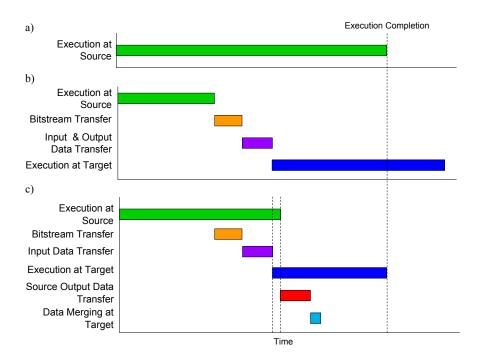

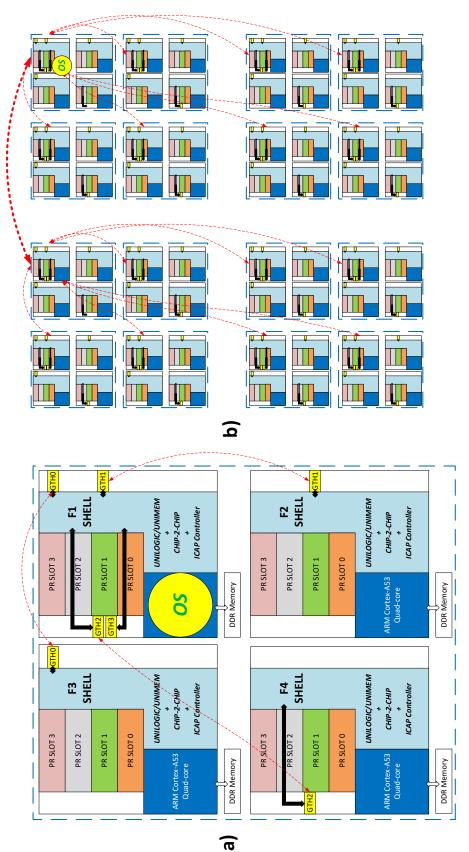

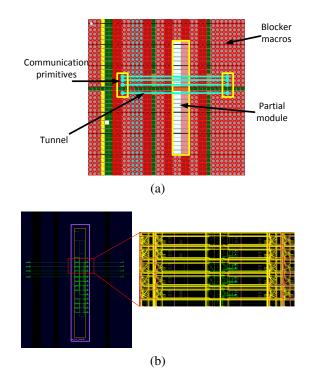

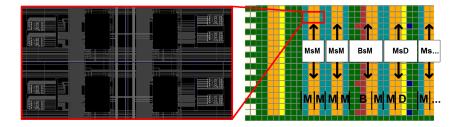

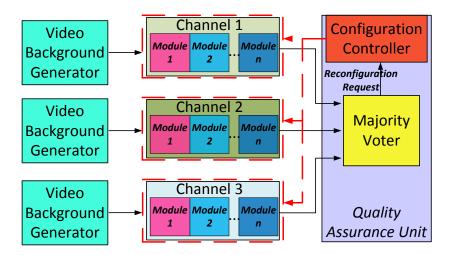

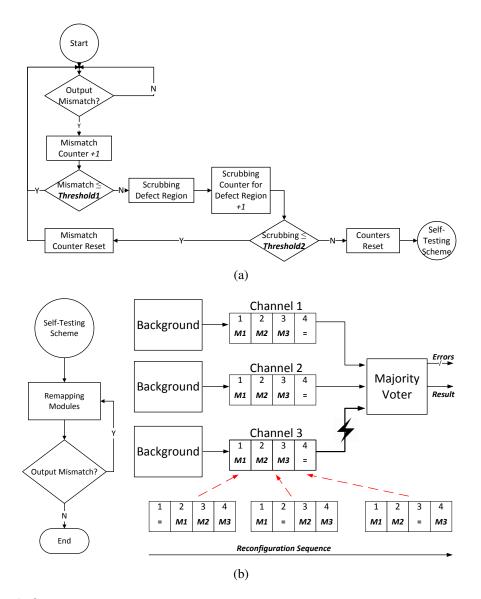

Xilinx Vivado PR Flow: Vivado PR flow [Xil18c] is an integral part of the Vivado Design Suite to implement partially reconfigurable designs for the latest 7-Series, UltraScale, and UltraScale+ FPGAs. A PR design consists of the *static part* which does not change its functionality during system operation and the *reconfigurable part* including one or more *reconfigurable regions*. In 7-Series and older Xilinx FPGAs, reconfiguration regions may contain only LUTs, BRAMs, and DSP slices but cannot contain clocks and clock modifying logic, I/O and I/O related components, serial transceivers and related components, and individual architecture feature components. However, these restrictions have been lessened for UltraScale/UltraScale+ devices so that only components needed for the actual partial reconfiguration process must remain in the static part of the design [Xil18c]. The static part commonly contains a processor (running the run-time management), a configuration interface as well as memory and network interface modules (i.e. the essential infrastructure to keep the whole system functioning). Reconfigurable regions *instantiate* the reconfigurable modules to perform the real computing work and can be reconfigured to change the behaviour at run-time. In the Xilinx PR flow, a PR design is implemented by using TCL commands.