# Automated Design of Approximate Accelerators

Jorge Castro-Godínez

## Automated Design of Approximate Accelerators

by Jorge Castro-Godínez This work has been supported financially by the Instituto Tecnológico de Costa Rica through the "Costa Rican Higher Education Improvement Project" (Proyecto Costa Rica BIRF 8794-CR), and the DAAD-STIBET-Abschlussstipendium.

Cover designed by the author. The base image corresponds to the *cameraman*, a standard test image in image processing (http://www.imageprocessingplace.com/root files V3/image databases.htm).

This document is licensed under the Creative Commons Attribution-Share Alike 4.0 International License (CC BY-SA 4.0):

https://creativecommons.org/licenses/by-sa/4.0/deed.en

### **Automated Design of Approximate Accelerators**

zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

M.Sc.

Jorge Castro-Godínez aus San Isidro de El General, Costa Rica

Tag der mündlichen Prüfung: 19.11.2020

Erster Gutachter: Prof. Dr.-Ing. Jörg Henkel

Karlsruher Institut für Technologie

Zweiter Gutachter: Prof. Dr. rer. nat. Wolfgang Karl

Karlsruher Institut für Technologie

Dritter Gutachter: Prof. Dr.-Ing. Muhammad Shafique

New York University Abu Dhabi

Jorge Castro-Godínez Steinstr. 18 77815, Bühl

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit — einschließlich Tabellen, Karten und Abbildungen — die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

\_\_\_\_\_\_ Jorge Castro-Godínez

People think that computer science is the art of geniuses but the actual reality is the opposite, just many people doing things that build on eachother, like a wall of mini stones.

Donald Knuth

### Contents

| A  | cknov | wledgem    | ents    |               |       |      |    |      |    |    |     | •  |   |  |  | • | • | • | • |   | • | • | . x          | vii  |

|----|-------|------------|---------|---------------|-------|------|----|------|----|----|-----|----|---|--|--|---|---|---|---|---|---|---|--------------|------|

| Li | st of | Publicat   | ions    |               |       |      |    |      |    |    |     | •  | • |  |  | • | • |   |   |   |   |   |              | xix  |

| A  | bstra | ct         |         |               |       |      |    |      |    |    |     | •  | • |  |  | • | • |   |   |   |   |   | . <b>x</b> : | xiii |

| Zı | usam  | menfass    | ung .   |               |       |      |    |      |    | •  |     | •  | • |  |  |   |   |   |   | • |   |   | .xx          | vii  |

| 1  | Intr  | oduction   | ı       |               |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 1    |

|    | 1.1   | Approx     | imate   | Comp          | outii | ng   |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 1    |

|    | 1.2   | Disserta   | ation ( | Contri        | buti  | on   |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 3    |

| 2  | Bac   | kground    | and F   | <b>Relate</b> | d W   | ork  |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 7    |

|    | 2.1   | Approx     |         |               |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 7    |

|    | 2.2   | Approx     |         |               |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 10   |

|    |       |            | Repres  |               |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 10   |

|    |       |            | Metric  |               |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 11   |

|    |       |            | Accura  |               |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 12   |

|    | 2.3   | Approx     |         | •             |       |      | -  |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 14   |

| 3  | Ger   | nerating . | Appro   | ximat         | e A   | rith | me | etic | Ci | rc | uit | ts |   |  |  |   |   |   |   |   |   |   |              | 17   |

|    | 3.1   | A Tool     |         |               |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 18   |

|    |       |            | Descri  |               | _     |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 19   |

|    |       | 3.1.2      |         | •             |       |      |    |      |    |    |     |    |   |  |  |   |   |   |   |   |   |   |              | 20   |

|    | 3.2   | A Framework for Approximate Logic Synthesis       |

|----|-------|---------------------------------------------------|

|    |       | 3.2.2 Evaluation                                  |

|    | 3.3   | Summary                                           |

|    |       |                                                   |

| 4  |       | deling Error Propagation                          |

|    | 4.1   | Motivation                                        |

|    | 4.2   | Error Estimation for Approximate Desings          |

|    | 4.3   | Models for Error Propagation                      |

|    | 4.4   | Estimation of Error Propagation                   |

|    | 4.5   | CEDA Tool                                         |

|    | 4.6   | Evaluation                                        |

|    | 4.7   | Summary                                           |

| 5  | Des   | igning Approximate Accelerators                   |

|    | 5.1   | Motivation                                        |

|    | 5.2   | Generation of Approximate Accelerators            |

|    | 5.3   | Models for Resource Estimation                    |

|    | 5.5   | 5.3.1 Evaluation                                  |

|    | 5.4   | Design-Space Exploration with Analytical Models   |

|    | 3.4   |                                                   |

|    |       |                                                   |

|    | 5.5   |                                                   |

|    |       | 5.5.1 Evaluation                                  |

|    | 5.6   | Summary                                           |

| 6  | Bala  | nncing Error Correction                           |

|    | 6.1   | Motivation                                        |

|    | 6.2   | Accuracy Control                                  |

|    |       | 6.2.1 Correction at the Accelerator Level         |

|    |       | 6.2.2 Correction at the Approximate Circuit Level |

|    | 6.3   | Early Error Correction                            |

|    | 6.4   | ECAx Methodology                                  |

|    | 6.5   | Evaluation                                        |

|    | 6.6   | Summary                                           |

| 7  | Con   | clusion                                           |

| ′  | 7.1   | Dissertation Summary                              |

|    | 7.1   | Future Work                                       |

|    | 1.4   | ruture vvoik                                      |

| Bi | bliog | raphy 99                                          |

| Li | st of | Figures                                           |

| $\sim$ |    |     |          |     |

|--------|----|-----|----------|-----|

| C      | or | 1†6 | $^{2}$ n | ıts |

| List of Tables | <br> | <br> | 117 |

|----------------|------|------|-----|

| List of Tables | <br> | <br> | 11  |

I've never been a good estimator of how long things are going to take.

Donald Knuth

### **Acknowledgements**

First of all, I express my sincere thanks to Prof. Dr.-Ing. Jörg Henkel for letting me, an unknown guy from Costa Rica with very little research experience, to carry out my doctoral studies at the Chair for Embedded Systems (CES), Karlsruhe Institute of Technology (KIT). Prof. Henkel provided me the freedom to explore and propose my own ideas, and he set the bar very high to help me discover my potential as a researcher. For this, I will ever be deeply thankful.

I deeply thank Prof. Dr.-Ing. Muhammad Shafique for his constant motivation, questions, discussions, and feedback that helped me to shape my ideas and write my papers in such a way that they were accepted. I express my gratitude to Prof. Dr. rer. nat. Wolfgang Karl for accepting the invitation to be one of my reviewers.

I thank Prof. Dr.-Ing. Rüdiger Dillmann and Prof. Dr.-Ing. Gregor Snelting for accepting the invitation to be examiners for my oral defense; and Prof. Dr. Mehdi B. Tahoori and Prof. Dr.-Ing. Michael Beigl for being part of the defense as members of the doctoral committee.

I would like to thank my colleagues at CES, both present and past, for their friend-ship, support, and counsels; they were always really appreciated. I particularly thank my colleagues with whom I have the chance to share the office (in alphabetical order): Tanfer Alan, Dr.-Ing. Santiago Pagani, and Dr.-Ing. Farzad Samie. The interesting discussions, funny anecdotes, and experiences shared have made my time at CES more pleasant. I also thank Dr.-Ing Lars Bauer for being always reachable to answer questions and for the funny moments.

A special thank goes to all the students that worked with me during this time, in many cases coming from Costa Rica for short research stays. I am particularly indebted to my student co-authors for the wonderful work done and the friendship developed (in alphabetical order): Humberto Barrantes-García, Sven Esser, Deykel Hernández-Araya, Luis G. León-Vega, and Julián Mateus-Vargas.

The possibility of doing this doctorate was originated by the *Instituto Tecnológico de Costa Rica*, through the "Costa Rican Higher Education Improvement Project" (Proyecto Costa Rica BIRF 8794-CR). I am profoundly thankful for the given opportunity and the trust placed in me. In general, I am thankful for the public education system in Costa Rica. Education is one of the greatest social mobility vectors, which has allowed me, the son of a widow and domestic worker, to get to this point. I thank the scholarship committee for help and support with paperwork and questions. In the last year, I received the support of the DAAD-STIBET-Abschlussstipendium, for which a deeply thank the support of Oliver Kaas from the International Scholars & Welcome Office (IScO) at KIT.

My deepest gratitude goes to my family, especially to my kids, that have had an always busy dad for the last years, and to my wife, for her constant support, love, and care. She has been always there to celebrate our achievements and to help me stand during my difficult times. To my extended family, thanks for their never-ending good wishes.

Karlsruhe, 19.11.2020

Jorge Castro-Godínez

#### Terry Pratchett

### **List of Publications**

The following publications provided a major contribution to this dissertation:

- [Cas+20c] J. Castro-Godínez, J. Mateus-Vargas, M. Shafique, and J. Henkel. "AxHLS: Design Space Exploration and High-Level Synthesis of Approximate Accelerators using Approximate Functional Units and Analytical Models". In: 2020 IEEE/ACM 39th International Conference on Computer-Aided Design (ICCAD). 2020. DOI: 10.1145/3400302.3415732

- [Cas+21] J. Castro-Godínez, H. Barrantes-García, M. Shafique, and J. Henkel. "AxLS: A Framework for Approximate Logic Synthesis based on Netlist Transformations". In: IEEE Transactions on Circuits and Systems II: Express Briefs (2021)

- [Her+20] D. Hernández-Araya, J. Castro-Godínez, M. Shafique, and J. Henkel.

"AUGER: A Tool for Generating Approximate Arithmetic Circuits".

In: 2020 IEEE 11th Latin American Symposium on Circuits & Systems (LASCAS). 2020, pp. 1–4. DOI: 10.1109/LASCAS45839.2020.9069045

- [CSH19] J. Castro-Godínez, M. Shafique, and J. Henkel. "ECAx: Balancing Error Correction Costs in Approximate Accelerators". In: ACM Trans. Embed. Comput. Syst. 18.5s (2019). DOI: 10.1145/3358179

- [Cas+18] J. Castro-Godínez, S. Esser, M. Shafique, S. Pagani, and J. Henkel. "Compiler-Driven Error Analysis for Designing Approximate Accelerators". In: 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE). 2018, pp. 1027–1032. DOI: 10.23919/DATE.2018.8342163

The following publications provided a minor contribution to this dissertation:

- [CSH20b] J. Castro-Godínez, M. Shafique, and J. Henkel. "Towards Quality-Driven Approximate Software Generation for Accurate Hardware: Work-in-Progress". In: 2020 International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES). 2020, pp. 12–14. DOI: 10.1109/CASES51649.2020.9243814

- [Cas+20b] J. Castro-Godínez, D. Hernández-Araya, M. Shafique, and J. Henkel. "Approximate Acceleration for CNN-based Applications on IoT Edge Devices". In: 2020 IEEE 11th Latin American Symposium on Circuits & Systems (LASCAS). 2020, pp. 1–4. DOI: 10.1109/LASCAS45839.2020. 9069040

#### Other co-authored publications:

- [Kha+20] N. Khan, J. Castro-Godínez, S. Xue, J. Henkel, and J. Becker. "Automatic Floorplanning and Standalone Generation of Bitstream-Level IP Cores". In: IEEE Transactions on Very Large Scale Integration (VLSI) Systems (2020). DOI: 10.1109/TVLSI.2020.3023548

- [LCH20] L. G. León-Vega, J. Castro-Godínez, and J. Henkel. "Measuring Traffic Dynamics at the Edge". In: International Work Conference on Bioinspired Intelligence (IWOBI) (2020)

- [CCC14] L. Cabrera-Quirós, R. Campos-Gómez, and J. Castro-Godínez. "Critical steps in camera pose estimation: an evaluation using LTI-LIB2 library". In: *Revista Tecnología en Marcha* (2014), pp. 60–69. DOI: 10.18845/tm. v0i0.1656

#### Workshops and Summer Schools:

- [Cas+20a] J. Castro-Godínez, H. Barrantes-García, M. Shafique, and J. Henkel. "AxLS: An Open-Source Framework for Netlist Transformation Approximate Logic Synthesis". In: 3rd Workshop on Open-Source EDA Technology (WOSET), co-located with ICCAD '20. 2020

- [CSH20a] J. Castro-Godínez, M. Shafique, and J. Henkel. "Towards Designing and Implementing Approximate Accelerators". In: 16th International Summer School on Advanced Computer Architecture and Compilation for High-performance Embedded Systems (ACACES). 2020

- [Cas19] J. Castro-Godínez. "Approximate Software for Accurate Hardware". In: NiPS Summer School, OPRECOMP Summer of Code Initiative. 2019

- [CH18] J. Castro-Godínez and J. Henkel. "Error Propagation Estimation on Approximate Designs with Compiler-Driven Support". In: 3rd. Workshop on Approximate Computing (AxC '18), co-located with the IEEE European Test Symposium 2018. 2018

What is not started today is never finished tomorrow.

Johann Wolfgang von Goethe

### **Abstract**

In the last decade, the need for computing efficiency has motivated the coming forth of new devices, architectures, and design techniques. *Approximate Computing* has emerged as a modern energy-efficient design paradigm for applications that present inherent tolerance to errors. By reducing the accuracy of the results in current applications, such as image processing, computer vision, and machine learning, to an acceptable amount, savings in the circuit area, delay, and power consumption can be achieved.

With the emergence of the approximate computing paradigm, many approximate functional units have been reported in the literature, particularly approximate adders and multipliers. For a plethora of such approximate circuits, and considering their usage as building blocks for the design of approximate accelerators for errortolerant applications, a challenge arises: selecting those approximate circuits for a given application that minimize the required resources while satisfying a defined accuracy.

This dissertation proposes automated methods for designing and implementing approximate accelerators built with approximate arithmetic circuits. To achieve it, this dissertation addresses the following challenges and provides the subsequent novel contributions:

Many approximate adders and multipliers have been reported in the literature, either by proposing approximate designs from accurate implementations, such as the ripple-carry adder, or by generating them through Approximate Logic Synthesis (ALS) methods. A representative set of these approximate components is required to build approximate accelerators. In that sense, this dissertation presents two approaches to generate such approximate arithmetic circuits. First, AUGER is introduced, a tool capable of generating Register-Transfer Level (RTL) descriptions for a broad set of approximate adders and multipliers for different data bit-width and accuracy configuration. A Design Space Exploration (DSE) of approximate components can be performed with AUGER to find those Pareto-optimal for a given bit-width, approximation range, and circuit metric. Then, AxLS is presented, a framework for ALS that allows the implementation of state-of-the-art methods, and the proposition of novel ones, to perform structural netlist transformations and to generate approximate arithmetic circuits from accurate ones. Moreover, both tools provide an error characterization, in the form of error distribution, and circuit characteristics (area, delay, and power) for each approximate circuit they generate. This information is essential for the scope of this dissertation.

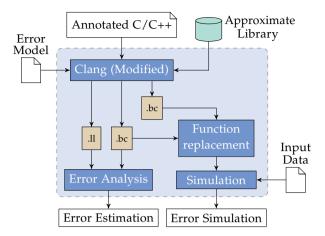

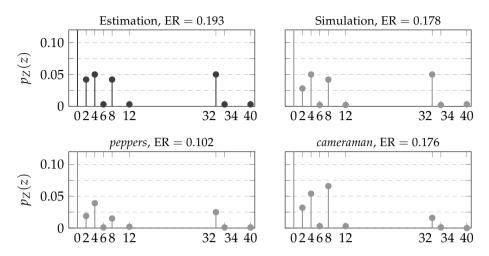

- Despite the tolerance to errors, approximate accelerators must be designed to satisfy accuracy constraints. Hence, for the design of such accelerators using approximate arithmetic circuits, it is imperative to assess how the errors introduced by approximate circuits propagate through other computations, either accurate or inaccurate, and finally accumulate at the output. This dissertation proposes analytical models to describe the error propagation through exact and approximate calculations. With them, an automated, compiler-based methodology is proposed to estimate the error propagation on approximate accelerators designs. This methodology is integrated into a tool, CEDA, to perform fast, simulation-free accuracy estimations of approximate accelerator models described using C code.

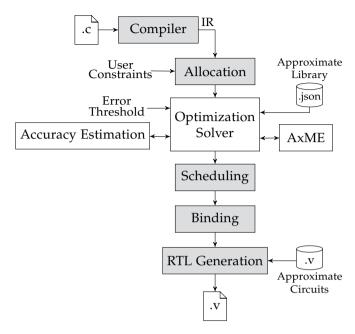

- In the design of approximate accelerators, repetitive gate-level simulations and circuit synthesis consume a significant time to explore many, or even all, possible combinations for a given set of approximate arithmetic circuits. On the other hand, current trends for designing accelerators are based on High-Level Synthesis (HLS) tools. This dissertation presents analytical models for estimating the required computational resources when using approximate adders and multipliers in approximate accelerators' designs. Furthermore, together with the proposed analytical models for accuracy estimation, these models are integrated into a DSE methodology for error-tolerant applications, DSEwam, to identify Pareto-optimal, or near Pareto-optimal, solutions for approximate accelerators. DSEwam is integrated into an HLS tool to automatically generate RTL descriptions of approximate accelerators from C language descriptions, for a given error threshold and minimization goal.

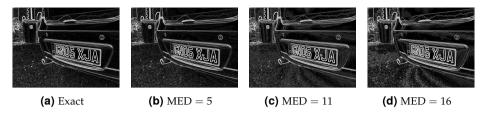

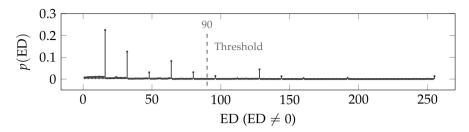

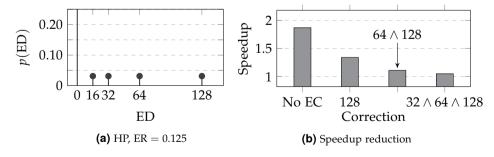

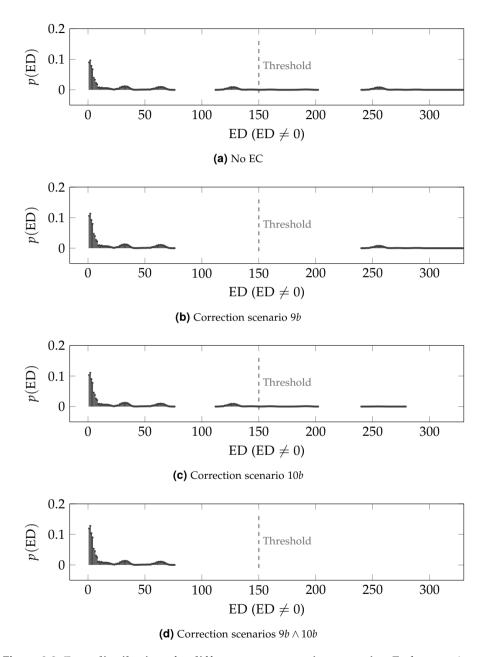

• The use of approximate accelerators must ensure that errors generated due to approximations remain within a defined maximum value for a given accuracy metric. However, the errors produced by approximate accelerators depend on the input data, which can be different regarding the data used for the design. This dissertation presents ECAx, an automated methodology to explore and apply fine-grained, low-overhead error correction in approximate accelerators, to reduce the cost of error correction at the software level, as reported in the literature. This is performed by selectively correcting the most significant errors produced by approximate components in terms of their magnitude without losing approximations' gains. The experimental evaluation shows speedup improvements for the application in exchange for a small area and power increment in the approximate accelerator design.

Johann Wolfgang von Goethe

### Zusammenfassung

In den letzten zehn Jahren hat das Bedürfnis nach Recheneffizienz die Entwicklung neuer Geräte, Architekturen und Entwurfstechniken motiviert. *Approximate Computing* hat sich als modernes, energieeffizientes Entwurfsparadigma für Anwendungen herausgestellt, die eine inhärente Fehlertoleranz aufweisen. Wenn die Genauigkeit der Ergebnisse in aktuellen Anwendungen wie Bildverarbeitung, Computer Vision und maschinellem Lernen auf ein akzeptables Maß reduziert wird, können Einsparungen im Schaltungsbereich, bei der Schaltkreisverzögerung und beim Stromverbrauch erzielt werden.

Mit dem Aufkommen dieses Approximate Computing Paradigmas wurden in der Literatur viele approximierte Funktionseinheiten angegeben, insbesondere approximierte Addierer und Multiplizierer. Für eine Vielzahl solcher approximierter Schaltkreise und unter Berücksichtigung ihrer Verwendung als Bausteine für den Entwurf von approximierten Beschleunigern für fehlertolerante Anwendungen, ergibt sich eine Herausforderung: die Auswahl dieser approximierten Schaltkreise für eine bestimmte Anwendung, die die erforderlichen Ressourcen minimieren und gleichzeitig eine definierte Genauigkeit erfüllen.

Diese Dissertation schlägt automatisierte Methoden zum Entwerfen und Implementieren von approximierten Beschleunigern vor, die aus approximierten arithmetischen Schaltungen aufgebaut sind. Um dies zu erreichen, befasst sich diese Dissertation mit folgenden Herausforderungen und liefert die nachfolgenden neuartigen Beiträge:

- In der Literatur wurden viele approximierte Addierer und Multiplizierer vorgestellt, indem entweder approximierte Entwürfe aus genauen Implementierungen wie dem Ripple-Carry-Addierer vorgeschlagen oder durch Approximate Logic Synthesis (ALS) Methoden generiert wurden. Ein repräsentativer Satz dieser approximierten Komponenten ist erforderlich, um approximierte Beschleuniger zu bauen. In diesem Sinne präsentiert diese Dissertation zwei Ansätze, um solche approximierte arithmetische Schaltungen zu erstellen. Zunächst wird AUGER vorgestellt, ein Tool, mit dem Register-Transfer Level (RTL) Beschreibungen für einen breiten Satz von approximierten Addierern und Multiplizierer für unterschiedliche Datenbitbreiten- und Genauigkeitskonfigurationen generiert werden können. Mit AUGER kann eine Design Space Exploration (DSE) von approximierten Komponenten durchgeführt werden, um diejenigen zu finden, die für eine gegebene Bitbreite, einen gegebenen Approximationsbereich und eine gegebene Schaltungsmetrik Pareto-optimal sind. Anschließend wird AxLS vorgestellt, ein Framework für ALS, das die Implementierung modernster Methoden und den Vorschlag neuartiger Methoden ermöglicht, um strukturelle Netzlistentransformationen durchzuführen und approximierte arithmetische Schaltungen aus genauen Schaltungen zu generieren. Darüber hinaus bieten beide Werkzeuge eine Fehlercharakterisierung in Form einer Fehlerverteilung und Schaltungseigenschaften (Fläche, Schaltkreisverzögerung und Leistung) für jede von ihnen erzeugte approximierte Schaltung. Diese Informationen sind für das Untersuchungsziel dieser Dissertation von wesentlicher Bedeutung.

- Trotz der Fehlertoleranz müssen approximierte Beschleuniger so ausgelegt sein, dass sie Genauigkeitsvorgaben erfüllen. Für den Entwurf solcher Beschleuniger unter Verwendung von approximierten arithmetischen Schaltungen ist es daher unerlässlich zu bewerten, wie sich die durch approximierte Schaltungen verursachten Fehler durch andere Berechnungen ausbreiten, entweder genau oder ungenau, und sich schließlich am Ausgang ansammeln. Diese Dissertation schlägt analytische Modelle vor, um die Fehlerpropagation durch genaue und approximierte Berechnungen zu beschreiben. Mit ihnen wird eine automatisierte, compilerbasierte Methodik vorgeschlagen, um die Fehlerpropagation auf approximierten Beschleunigerdesigns abzuschätzen. Diese Methode ist in ein Tool, CEDA, integriert, um schnelle, simulationsfreie Genauigkeitsschätzungen von approximierten Beschleunigermodellen durchzuführen, die unter Verwendung von C-Code beschrieben wurden.

- Beim Entwurf von approximierten Beschleunigern benötigen sich wiederholende Simulationen auf Gate-Level und die Schaltungssynthese viel Zeit, um viele oder sogar alle möglichen Kombinationen für einen gegebenen Satz von approximierten arithmetischen Schaltungen zu untersuchen. Anderer-

seits basieren aktuelle Trends beim Entwerfen von Beschleunigern auf High-Level Synthesis (HLS) Werkzeugen. In dieser Dissertation werden analytische Modelle zur Schätzung der erforderlichen Rechenressourcen vorgestellt, wenn approximierte Addierer und Multiplizierer in Konstruktionen von approximierten Beschleunigern verwendet werden. Darüber hinaus werden diese Modelle zusammen mit den vorgeschlagenen analytischen Modellen zur Genauigkeitsschätzung in eine DSE-Methodik für fehlertolerante Anwendungen, DSEwam, integriert, um Pareto-optimale oder nahezu Pareto-optimale Lösungen für approximierte Beschleuniger zu identifizieren. DSEwam ist in ein HLS-Tool integriert, um automatisch RTL-Beschreibungen von approximierten Beschleunigern aus C-Sprachbeschreibungen für eine bestimmte Fehlerschwelle und ein bestimmtes Minimierungsziel zu generieren.

• Die Verwendung von approximierten Beschleunigern muss sicherstellen, dass Fehler, die aufgrund von approximierten Berechnungen erzeugt werden, innerhalb eines definierten Maximalwerts für eine gegebene Genauigkeitsmetrik bleiben. Die Fehler, die durch approximierte Beschleuniger erzeugt werden, hängen jedoch von den Eingabedaten ab, die hinsichtlich der für das Design verwendeten Daten unterschiedlich sein können. In dieser Dissertation wird ECAx vorgestellt, eine automatisierte Methode zur Untersuchung und Anwendung feinkörniger Fehlerkorrekturen mit geringem Overhead in approximierten Beschleunigern, um die Kosten für die Fehlerkorrektur auf Softwareebene (wie es in der Literatur gemacht wird) zu senken. Dies erfolgt durch selektive Korrektur der signifikantesten Fehler (in Bezug auf ihre Größenordnung), die von approximierten Komponenten erzeugt werden, ohne die Vorteile der Approximationen zu verlieren. Die experimentelle Auswertung zeigt Beschleunigungsverbesserungen für die Anwendung im Austausch für einen leicht gestiegenen Flächen- und Leistungsverbrauch im approximierten Beschleunigerdesign.

Carveth Read

1

### Introduction

The discontinuation of Dennard scaling and the fading of Moore's law have motivated the coming forth of new devices, architectures, and design techniques for computing [TW17]. Nowadays, power and energy efficiency have become significant design concerns for modern computing systems. On the other hand, current applications and workloads, such as image processing, computer vision, graphics, machine learning, data mining, and financial and physical simulations, are part of a set of applications classified as Recognition, Mining, and Synthesis [Che+08], which have been reported as error-tolerant. This means that even in the presence of deliberately introduced errors, these applications produce acceptable results as a golden result does not exists, the application deals with noisy input data, or even it presents iterative refinement [Ven+15].

### 1.1 Approximate Computing

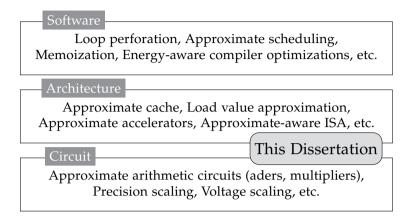

In recent years, *Approximate Computing* has emerged as a novel energy- and latency-efficient design paradigm relevant to applications with inherent resilience to errors [HO13; XMK16]. By accepting *good enough* results caused by imprecise calculations, for instance, in image and video processing where the human perception plays a major role, the computational *quality* (accuracy of results) is traded-off to reduce the required computational *effort* (execution time, area, power, or energy). As depicted in Figure 1.1, this tolerance to inexactness has been exploited at different abstraction layers [Sta+20]. For instance, non-critical computations are skipped at the software level, architectural changes are introduced in arithmetic blocks at the architecture level, or operation voltage is lowered at the circuit level [XMK16]. Many more

**Figure 1.1: Approximate computing at different abstraction layers.** Different approximate computing techniques have been proposed and applied at different abstraction layers (based on [LLS20]).

approximate computing techniques have been reported in the literature than those in Figure 1.1. Still, these show the need to exploit this design paradigm to improve computation efficiency at all layers where computation occurs.

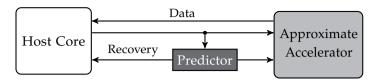

Recent work has proposed to exploit inherent resilience to errors in applications by using approximate accelerators [XMK16]. In general, hardware accelerators have reported significant benefits for reducing energy consumption, and they have been used to overcome the utilization wall challenge [Con+14]. In a nutshell, an accelerator is used to offload a highly-frequent and compute-intensive section of an application to dedicated hardware, while a host processor executes the rest of the application. Accelerators can be in the form of a GPU, a DSP, or a specialized FPGA design. From the approximate computing perspective, approximate accelerators exploit error resilience as frequently-executed, but error-tolerant sections of an application are performed by dedicated approximate hardware designs [Sha+16; Esm+12].

One approach proposed is to implement these accelerators as neural networks and take advantage of the approximate nature of the results produced by this computational model [Esm+12; Mor+15]. Another approach proposes the usage of approximate arithmetic circuits to replace exact calculations in hardware accelerator designs [Maz+16; Sha+16]. Nevertheless, many approximate adders [Mah+10; Gup+13; Sha+15] and multipliers [Mah+10; BMH14; HBR15; Zen+17] have been reported in the literature. For an ongoing number of such approximate arithmetic circuits, and considering their usage in building approximate designs, such as approximate accelerators, a question arises: given a design for an error-tolerant ap-

plication and a set of approximate components, which approximate arithmetic circuits should be used to minimize the computational effort, for instance, the required area, delay, power, or energy, while satisfying a defined accuracy? Traditional approaches required exhaustive synthesis and simulation of by-hand designed approximate accelerators, which might be infeasible due to the large design space even considering a reduced set of approximate arithmetic circuits. For instance, to satisfy accuracy constraints in these accelerators, required to guarantee *good enough* results despite the on-purpose errors, it is imperative to assess how the errors introduced by approximate circuits propagate through other exact and approximate computations, and finally accumulate at the output. This is, in particular, crucial to enable the high-level synthesis of approximate accelerators.

Bridging the gap between many approximate arithmetic circuits and the automated design and implementation of approximate accelerators is crucial to further enable cross-layer approximate computing [Sha+16].

#### 1.2 Dissertation Contribution

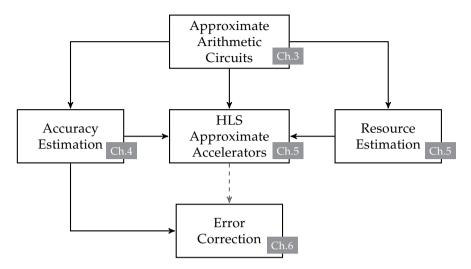

This dissertation proposes the automated design of approximate accelerators using approximate arithmetic circuits. As depicted in Figure 1.1, this dissertation can be placed between the circuit and architecture layers, but from the computer-aided design perspective. The contributions of this dissertation, and their relationship, are depicted in Figure 1.2.

### **Approximate Arithmetic Circuits**

In the literature, many approximate adders and multipliers have been reported. To automate the design of approximate accelerators, a representative set of these approximate components is required. In Chapter 3, this dissertation presents two approaches to generate such approximate arithmetic circuits. First, AUGER is introduced, a tool capable of generating Register-Transfer Level (RTL) descriptions for a broad set of approximate adders and multipliers for different data bit-width and accuracy configuration. A Design Space Exploration (DSE) of approximate components can be performed with AUGER to find those Pareto-optimal for a given bit-width, approximation range, and circuit metric. Then, AxLS is presented, a framework for Approximate Logic Synthesis that allows the implementation of state-of-the-art methods, and the proposition of novel ones, to perform structural netlist transformations and to generate approximate arithmetic circuits from accurate ones. Moreover, both tools provide an error characterization, in the form

**Figure 1.2: Contributions of this dissertation.** The chapter number is indicated where each contribution is presented in this dissertation.

of error distribution, and circuit characteristics (area, delay, and power) for each approximate circuit they generate. This information is required to define analytical models for accuracy and resource estimation presented within this dissertation, as those models are based on the information of the approximate arithmetic circuits.

### **Accuracy Estimation**

For the automated design of approximate accelerators built with approximate arithmetic circuits, it is essential to count with models to estimate the accuracy of approximate accelerator designs. Despite the tolerance to errors, approximate accelerators must limit the output error to satisfy accuracy constraints. In Chapter 4, this dissertation proposes analytical models to describe the error propagation through exact and approximate computations, considering approximate additions and multiplications as source of errors. These models are defined with the individual error characteristics of approximate arithmetic circuits, as provided by the contribution in Chapter 3. With these analytical models, an automated, compiler-based methodology is proposed to estimate the error propagation of approximate accelerators models described at the software level.

#### **Resource Estimation**

In the design of approximate accelerators, repetitive gate-level simulations and circuit synthesis consume a significant time to explore many, or even all, possible combinations for a given set of approximate arithmetic circuits. To speed up the exploration of many approximate accelerator designs, this dissertation presents resource estimation models in Chapter 5. As the accuracy models, these models are derived using the information of approximate circuits, adders and multipliers, provided by the contribution in Chapter 3.

### **High-Level Synthesis of Approximate Accelerators**

With the generation of approximate arithmetic circuits and analytical models to estimate accuracy and resources in approximate accelerator designs, in Chapter 5, this dissertation presents a high-level synthesis approach to automatically generate RTL descriptions of approximate accelerators from C language descriptions. This is performed for a given error threshold and minimization goal, and using approximate adders and multipliers. To achieve it, a DSE methodology is proposed that takes advantage of the analytical models for accuracy and resource presented in this dissertation, to find Pareto-optimal, or near Pareto-optimal, solutions for approximate accelerators.

#### **Error Correction**

The use of approximate accelerators must ensure that errors generated due to approximations remain within a defined maximum value for a given accuracy metric. In Chapter 6, this dissertation presents an automated methodology to explore and apply fine-grained, low-overhead error correction in approximate accelerators. These accelerators can be automatically generated, as proposed in this dissertation or designed by hand. The main idea behind this error correction methodology is to reduce the cost of error correction at the software level, as currently reported in the literature. This is performed by selectively correcting the most significant errors produced by approximate circuits, in terms of their magnitude, without losing the gains of approximations. For this contribution, the analytical models for accuracy estimation presented in Chapter 4 are crucial to enable a fast exploration of error correction's effect in the output accuracy of approximate accelerator designs.

Man muss viel gelernt haben, um über das, was man nicht weiß, fragen zu können.

Jean-Jacques Rousseau

2

# **Background and Related Work**

This chapter presents common principles, notions, and definitions used throughout this dissertation.

## 2.1 Approximate Arithmetic Circuits

As discussed in Chapter 1, with the coming forth of *Approximate Computing* (AxC) as an energy- and accuracy-aware design paradigm, many approximate arithmetic circuits have been proposed, mainly approximate adders [VBI08; Mah+10; KK12; Sha+15] and multipliers [BMH14; HBR15]. A quick search in the Scopus database<sup>1</sup> shows more than 1400 publications related to AxC in the last decade, and about 37% of those works correspond to approximate adders or multipliers. The main idea behind this approximate circuits is to perform the mathematical operations faster or with less area, power, or energy than the accurate circuits while introducing errors in the results.

In the literature, several methods have been proposed to generate approximate circuits from accurate descriptions, for instance, by transforming gate-level representations of the circuit [Ven+12; HMV16; Zer+16; SAP18; Cas+20a] or exploiting delay in non-critical circuit paths [AH18]. However, the dominant trend has been to propose approximate designs directly from accurate counterparts [Jia+17a].

<sup>&</sup>lt;sup>1</sup> The search was performed on September 22th, 2020.

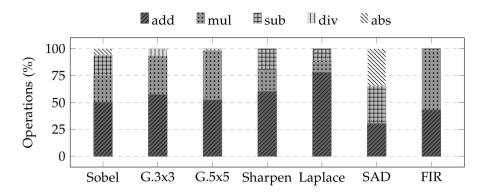

**Figure 2.1: Operations profile for a set of error-tolerant applications.** For most of these applications, additions and multiplications are the dominant operations.

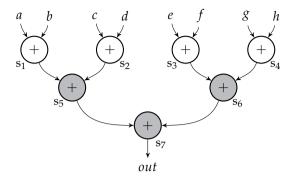

Other approximate arithmetic circuits have been proposed, for example, approximate dividers [HBR16]. However, this dissertation focuses on approximate adders and multipliers to built approximate accelerators, as they are the most common operations in a wide range of applications [VBI08]. For instance, consider the following error-tolerant applications: Sobel filter,  $3 \times 3$  and  $5 \times 5$  Gaussian filter (G.3  $\times$  3 and G.5  $\times$  5), Sharpen filter, Laplace filter, sum of absolute differences (SAD), and a 5-tap FIR filter. Figure 2.1 presents a profile of the required mathematical operations for these applications. As it can be noticed, in most of these applications, excluding SAD, 75% or more of the operations correspond to additions and multiplications, and, for instance, none have division as a significant operation.

As many approximate arithmetic circuits have been proposed, and are still being proposed in the community, this chapter does not cover them extensively. Although the main idea is to reduce the complexity of the arithmetic circuits, some of the key concepts behind these approximate units are here mentioned. Extensive evaluations of approximate arithmetic circuits have already been reported in the literature [JHL; Jia+16; Jia+17b; Jia+19].

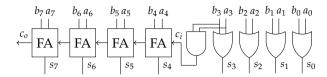

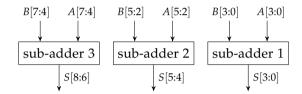

**Approximate Adders:** In the literature, two main approaches have been proposed regarding approximate adders. The first considers the substitution of 1-bit full adder (FA) for simplified versions [Mah+10; Gup+13; Yan+13; Dut+16; AKL16], aiming to reduce the power consumption of the addition. This type is known as low-power (LP) approximate adder. For instance, Figure 2.2 depicts an 8-bit approximate adder built from a Ripple-Carry Adder (RCA). This adder, named Lower-part-OR adder (LOA), replaces the 1-bit additions of least significant bits

**Figure 2.2:** An 8-bit LOA approximate adder. This approximate adder, called Lowerpart-OR adder (LOA), approximates the addition by using an OR gate to add the LSB [Mah+10].

**Figure 2.3:** An 8-bit GeAr approximate adder. An 8-bit approximate adder, Generic Accuracy Configurable adder (GeAr), uses multiple overlapping sub-adders to perform the addition [Sha+15].

(LSB) performed by a FA with a single OR gate. By doing so, for instance, the required area is reduced as fewer logic gates are needed. Also, the circuit delay is reduced, as the carry propagation chain is cut. For this LOA example, area and power delay are reduced by about 35%, respectively, compared to an 8-bit RCA.<sup>2</sup>

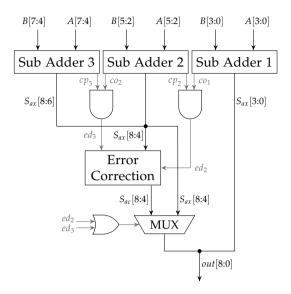

The second type of approximate adder is known as high-performance (HP) approximate adder. For this approximate adders, the addition is computed by breaking the carry propagation chain of the exact addition and using multiple (sometimes overlapping) sub-adders to generate the addition result, aiming to reduce the latency of the computation. Figure 2.3 depicts an example of an HP approximate adder. This adder, called Generic Accuracy Configurable adder (GeAr), performs an *N*-bit addition using multiple sub-adders of smaller size. In this example, an 8-bit addition is done by three 4-bit adders. The most significant *R*-bits of the sub-adders are considered as resultant bits, and they are used in the actual result. The remaining *P*-bits, known as previous bits, are used to estimate the carry propagation to the upper bits. As shown in Figure 2.3, only the sub-adder 1 contributes with all its partial result to the final result, while sub-adder 2 and 3 provide 2 and 3 bits to the result. This 8-bit GeAr example reduces the delay in 40% with respect to an 8-bit RCA.<sup>3</sup>

9

<sup>&</sup>lt;sup>2</sup> Considering a synthesis performed with Synopsys Design Compiler and the NanGate 15 nm technology library.

<sup>&</sup>lt;sup>3</sup> Same synthesis tool and technology library as before.

Most of the reported HP approximate adders in the literature, such as ACA-I [VBI08], ACA-II [KK12], ETAII [ZGY09], and GDA [Ye+13], can be implemented as a configuration of GeAr [Sha+15]. This helps to reduce the representation of various HP approximate adders to a single proposed design.

**Approximate Multipliers:** For approximate multipliers, the technique applied to reduce their complexity depends on the topology of the accurate multiplier used as a base. For instance, carry-in predictions can be made to reduce latency in a Wallace Tree Multiplier [BMH14], dynamic and fast bit selection can be applied to reduce the size of the multiplier [HBR15], or rounding of operands performed to the nearest exponent of two [Zen+17]. Also, partial product perforations have been applied to accurate multipliers [Zer+16], approximate multipliers have been built from smaller approximate 2x2 multipliers [Reh+16], approximate 4-2 compressors have been proposed to design approximate Dadda multipliers [Mom+15]. Even the LOA LP approximate adder has been used to present approximate versions of array-based multipliers [Mah+10].

## 2.2 Approximation Error

As part of the design of approximate accelerators, the error generated due to approximate arithmetic circuits needs to be represented and measured. This is particularly useful, as the use of approximations in error-tolerant applications is limited to allow the application to produce results with the sufficient accuracy required.

## 2.2.1 Representation

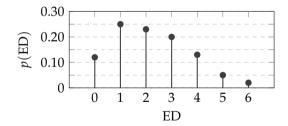

In this dissertation, a Probability Mass Function (PMF) is the main form used to represent the error distribution of approximate circuits and accelerators. A PMF denotes the probability **P** of a discrete random variable X to be equal to a determined value x. This is expressed as  $p_X(x) = \mathbf{P}(X = x)$ . For the case of approximate circuits and accelerators, a PMF allows the representation of each Error Distance, ED, and its probability of ocurrance, p. The ED is defined as:

$$ED = |O_i^{ac} - O_i^{ax}| \tag{2.1}$$

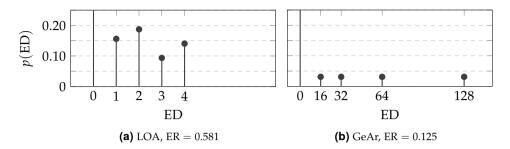

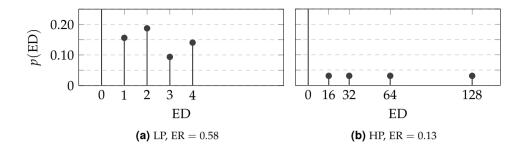

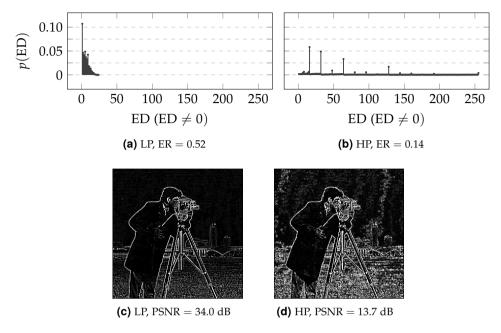

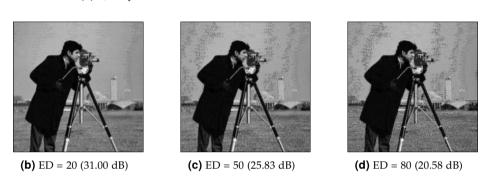

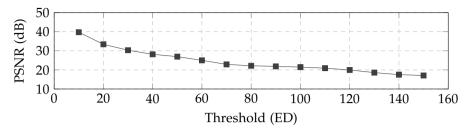

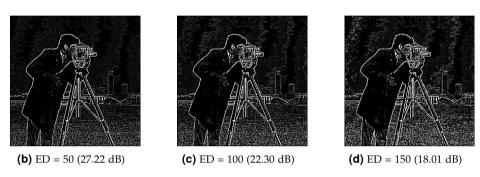

**Figure 2.4:** Error distribution for two 8-bit approximate adders. Errors in LP approximate adders appear with low ED but higher frequency in comparison to HP approximate adders, where adders have a higher ED but with lower frequency. These two 8-bit approximate adders correspond to LOA [Mah+10] and GeAr [Sha+15], previously described.

which is the arithmetic distance between the result generated by an accurate ( $O^{ac}$ ) and an approximate ( $O^{ax}$ ) circuit (or accelerator) for identical input data (i) [LHL13].

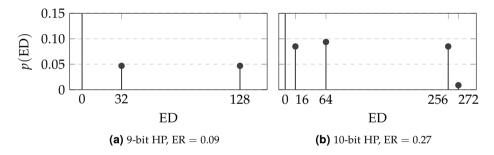

Figure 2.4 presents two PMFs representing the error distribution of two approximate adders. As can be noticed, errors in LP approximate adders, like the LOA, appear with low ED values and a higher probability of occurrence than the errors for an HP approximate adder, like the GeAr, for which errors have a higher ED but with lower probability. Interestingly, the errors for an HP approximate adder correspond to power values of 2, or combinations of them, due to errors are produced by carry-in mispredictions, as the original adder carry chain is broken.

The error distribution of any approximate arithmetic circuit can be estimated through circuit simulations and using representative input data. However, for some of these circuits, their error distribution can be generated through analytical methods [Maz+17b; Maz+17a; Wu+19; Han+20], eliminating the need of time-consuming simulations.

For the case of approximate accelerators, this dissertation proposes a methodology to estimate their error distribution (Chapter 4). Using only the error distributions of individual approximate arithmetic circuits used in an approximate accelerator design, analytical rules are presented to model the interaction of errors generated with other accurate and approximate computations and obtain an output error distribution.

#### 2.2.2 Metrics

An error metric measures how much the results an approximate circuit or accelerator deviates from the accurate ones. Different error metrics have been reported

and used in the AxC literature [LHL13; Mra+17; Vas19], which can be derived from the error distribution represented as a PMF. While each of them presents challenges and advantages, three error metrics are widely used for the scope of this dissertation.

The first is Error Rate (ER), which denotes the total probability of error for an approximate circuit or accelerator. As depicted in Figure 2.4, the values in the x-axis, the ED, represent the error values produced by each approximate adder. The probability of having no errors, i.e.,  $p_X(0)$ , is 1 - ER. For both PMFs in Figure 2.4, the probability of no having errors is depicted out of the axis. Also, in Figure 2.4, for the LP approximate adder case, it can be observed that it presents a higher ER, 0.581, compared to the HP approximate adder, 0.125.

A second error metric is Worst-Case Error (WCE). WCE represents the maximum error generated by an approximate circuit or accelerator, despite its probability of occurrence, and it is defined as:

$$WCE = \max_{\forall i} |O_i^{ac} - O_i^{ax}| \tag{2.2}$$

From the PMFs in Figure 2.4, WCE = 4 and WCE = 128 for the LP and HP approximate adders, respectively. A third error metric used widely in this dissertation is Mean-Error Distance (MED). MED is the weighted average of all ED [LHL13]:

$$MED = \sum_{i=0}^{n} ED_i \cdot p(ED_i)$$

(2.3)

which can be calculated from the information in the PMF. For the approximate adders in Figure 2.4, the LP and HP approximate adders have 1.37 and 7.50 for this MED metric, respectively.

## 2.2.3 Accuracy and Quality

Accuracy and quality are two important terms that have been used indistinctly equal in AxC contributions reported in the literature. For this dissertation, the accuracy of an approximate circuit or accelerator is measured with error metrics, as the accuracy is considered not application-dependent. On the other hand, quality is an application-dependent evaluation of an approximate accelerator's results, and for it, specific quality metrics are required. In this dissertation, the automated design of approximate accelerators is performed for given accuracy constraints.

Still, quality evaluations take place to assess the degradation of the results at the application level.

In this dissertation, three quality metrics are used. Mean Squared Error (MSE) is one of them. MSE is a way to assess the fidelity of a signal, and it is defined as [WB09]:

$$MSE(ac, ax) = \frac{1}{N} \sum_{i=0}^{N} (O_i^{ac} - O_i^{ax})^2$$

(2.4)

where **ac** and **ax** are sets containing all accurate and approximate results, respectively, for the same input data set. With MSE, a degree of similarity or error/distortion between two signals can be assessed.

In the context of image processing, the Peak-Signal-to-Noise Ratio (PSNR) is widely used, which is a converted version of the MSE. PSNR is defined as [WB09]:

$$PSNR = 10 \log_{10} \frac{L^2}{MSE}$$

(2.5)

where L is the dynamic range of the value a pixel can take, in the context of image processing. For the case of a grayscale image and using 8-bits for representation, that means L = 255.

Also related to image processing, in this dissertation, the Structural Similarity (SSIM) index is used as an image fidelity metric [Wan+04]. The SSIM aims to represent better the way the human visual system evaluates the quality in an image, and it is defined as:

SSIM =

$$l(\mathbf{ac}, \mathbf{ax}) \cdot c(\mathbf{ac}, \mathbf{ac}) \cdot s(\mathbf{ac}, \mathbf{ax})$$

=  $\left(\frac{2\mu_{ac}\mu_{ax} + C_1}{\mu_{ac}^2 + \mu_{ax}^2 + C_1}\right) \cdot \left(\frac{2\sigma_{ac}\sigma_{ax} + C_2}{\sigma_{ac}^2 + \sigma_{ax}^2 + C_2}\right) \cdot \left(\frac{\sigma_{ac,ax} + C_3}{\sigma_{ac} + \sigma_{ax} + C_3}\right)$  (2.6)

where  $l(\mathbf{ac}, \mathbf{ax})$  is the similarity of local patch luminances (brightness values),  $c(\mathbf{ac}, \mathbf{ac})$  is the similarity of local path contrast, and  $s(\mathbf{ac}, \mathbf{ax})$  is the similarity of local patch structures [WB09]. These local similarities are expressed in terms of statistics that are computed to obtain a local SSIM evaluation.

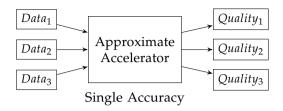

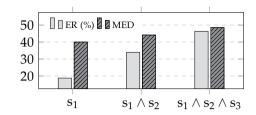

One challenge faced by AxC is that the errors produced by an approximate accelerator not only depend on the approximations applied but also in the data that is processed [Mah+16]. For instance, an approximate accelerator designed to meet a

**Figure 2.5:** Quality as a function of input data. In approximate computing, the quality depends on the data processed and the quality metric used.

**Table 2.1:** Quality results for a single accuracy Sobel approximate accelerator and different data set. Even though the quality evaluated with PSNR metric is similar for these four test images, the quality estimated with SSIM produce different results.

| Data set  | MED   | PSNR (dB) | SSIM |

|-----------|-------|-----------|------|

| sails     | 14.23 | 22.92     | 0.86 |

| plate     | 15.05 | 22.46     | 0.65 |

| cameraman | 16.92 | 21.53     | 0.61 |

| lena      | 16.30 | 22.00     | 0.59 |

specific, single accuracy can produce results with different quality of results for different data processed, as motivated in Figure 2.5.

Consider a SOBEL filter designed to meet a MED = 15 as an accuracy constraint. Four different test images are used as test data with this accelerator. As shown in Table 2.1, just for one of the test images, *sails*, the accuracy threshold is met. On the other hand, for all test images, the quality is similar when evaluated with the PSNR metric, approximately 22 dB. However, when the SSIM index is used for assessing the quality of the results, very different results are obtained, ranging from 0.86 to 0.59 for the *sails* and *lena* test images, respectively. These results confirm that accuracy and quality in AxC are two related but different aspects.

## 2.3 Approximate Accelerators

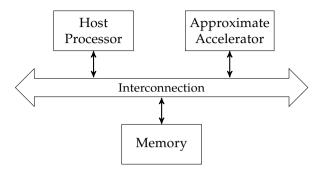

By definition, hardware acceleration is the use of specialized hardware to perform tasks more efficiently compared to a general processor [Con+14]. In that sense, an accelerator is used to offload a highly-frequent and compute-intensive section of an application to dedicated hardware, while the rest of the application is executed

**Figure 2.6: Simplified diagram of a system architecture.** This diagram considers that a host processor connects to one (or more) approximate accelerator.

by a host processor, aiming to reduce the execution time of the application and increasing the throughput, and in many cases, reducing the energy consumption. Accelerators can be in the form of a GPU, a DSP, or a specialized design on an FPGA.

From the point of view of AxC, approximate accelerators exploit error resilience as frequently-executed, but error-tolerant sections of an application are executed by dedicated approximate hardware designs [Sha+16; Esm+12]. By doing so, additional benefits can be achieved, such as application speedup improvement or energy reduction. Figure 2.6 shows a simplified diagram of a system architecture depicting a host processor and an approximate accelerator interconnected through a standard on-chip interface alongside a memory system. In this sense, the approximate accelerator is designed to execute error-resilient parts of the host processor's applications. Such an approximate accelerator is built to achieve a defined accuracy during design time. Although just one approximate accelerator is shown, many could be designed and deployed in a system. It is even foreseen the development of multi-accelerator platforms, where a diverse set of accelerators with different accuracy is available to a group of processors, providing high flexibility and adaptivity and allowing applications to meet their accuracy and quality constraints while minimizing the required resources [Sha+16].

Existing work has proposed the design of approximate accelerators using neural networks [Esm+12] or approximate functional units, particularly approximate adders and multipliers [Sha+16; Maz+16]. This dissertation focuses on the automated design of approximate accelerators using approximate arithmetic circuits.

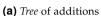

As many approximate adders have been proposed considering an RCA as a base, a skeptical observation could point to better use parallel-prefix adders that present smaller delays compared to RCA, if the goal is to reduce the delay of an accelerator

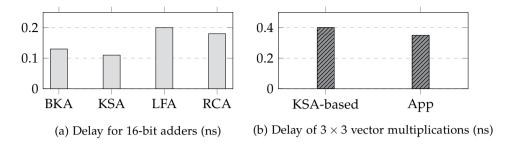

**Figure 2.7: Comparison of parallel-prefix and approximate adders.** Delay comparison of parallel-prefix adders and RCA-based approximate adders, individually and in approximate accelerator designs.

by using approximations. As can shown in Figure 2.7, parallel-prefix adders such as Brent-Kung Adder (BKA) and Kogge-Stone Adder (KSA) present delays 38% and 63% smaller than an RCA, respectively. Just for the case of Ladner-Fischer Adder (LFA), the RCA presents a delay smaller, about 10%.<sup>4</sup>

However, combinations of state-of-the-art LP and HP approximate adders can produce smaller delays than using these parallel-prefix adders when building approximate accelerators. As depicted in Figure 2.7, using LP and HP approximate adders, such as LOA and GeAr, a delay nearly 15% smaller is obtained by an approximate version (App) of a  $3 \times 3$  vector multiplication compared to an accelerator built using KSA (KSA-based). On the other hand, the approximate version for this evaluation consumes about 35% less power.

$<sup>^4</sup>$  Evaluation performed using  $10^6$  uniform distributed input test vectors and Synopsys Design Compiler with the TSMC 65nm technology library.

Result of a 2x2-bit approximate multiplier to keep the result to 3 bits [KGE11].

3

# **Generating Approximate Arithmetic Circuits**

The goal of this dissertation is the automated design of approximate accelerators, particularly using approximate arithmetic circuits as building blocks. To achieve it, first, it is necessary to have these approximate arithmetic circuits to then proceed with the design of accelerators.

This chapter presents two contributions for the generation of approximate arithmetic circuits. First, AUGER, a tool to generate and characterize approximate arithmetic circuits reported in the literature, is presented. This tool provides register-transfer level (RTL) implementations and functional models, at the software level, of approximate adders and multipliers. This is performed for different proposed designs of approximate adders and multipliers, and different approximation levels. It also provides a characterization of the circuits generated in terms of area, delay, and power, for a given technology library.

Second, AxLS, a framework for approximate logic synthesis (ALS) techniques based on netlist transformations, is presented. AxLS is a novel, open-source framework with which existing ALS methodologies can be implemented, and new techniques can be proposed. With AxLS, automated methods can be developed to automatically

The content of this chapter is based on the work originally published in [Her+20]:

D. Hernández-Araya, J. Castro-Godínez, M. Shafique, and J. Henkel: "AUGER: A Tool for Generating Approximate Arithmetic Circuits". In: 2020 IEEE 11th Latin American Symposium on Circuits & Systems (LASCAS),

and [Cas+20a]:

J. Castro-Godínez, H. Barrantes-García, M. Shafique, and J. Henkel: "AxLS: An Open-Source Framework for Netlist Transformation Approximate Logic Synthesis", In: 3rd Workshop on Open-Source EDA Technology (WOSET), 2020.

generate approximate versions of accurate arithmetic circuits described at RTL. Additionally, AxLS performs a characterization of the circuit resources and error distribution of the circuits generated.

Both contributions have been made open-source, allowing their utilization by the research community and their extension to newer approximate arithmetic circuits and newer ALS techniques based on netlist transformations.

# 3.1 A Tool for Generating Approximate Arithmetic Circuits

As discussed in Section 2.1, an increasing number of approximate arithmetic circuits has been reported in the literature, mainly approximate adders and multipliers. Selecting those that properly fit an application, reducing resources, and achieving a specific accuracy constraint is cumbersome. Comparisons of state-of-the-art approximate adders and multipliers have been reported [JHL; Jia+16; Jia+17b], but if such approximate circuits are expected to be used in approximate designs, they must be first implemented. Additionally, the characterization of such approximate arithmetic circuits, in terms of the resources required and error generated, can speed up the design space exploration of approximate accelerators. This is because the impact in savings and accuracy degradation can be faster estimated than performing iterative circuit synthesis and simulations [Cas+18; Cas+20c], as it is presented in Chapters 4 and 5 of this dissertation.

This section presents AUGER, an Approximate Units GenERator. AUGER<sup>1</sup> is a tool to generate approximate adders and multipliers that have been proposed and reported in academia. AUGER generates the register-transfer level (RTL) descriptions of the circuits. It provides a software model for the arithmetic circuit generated, which can be used to assess its impact on the application accuracy or quality of results at the software level. AUGER uses industrial circuit simulation and synthesis tools to provide a characterization of the components generated in terms of area, power, delay, and error distribution. This information is useful for comparison among other similar approximate circuits, as presented in this section.

<sup>&</sup>lt;sup>1</sup> AUGER is an open-source contribution and it is available at https://git.scc.kit.edu/CES/AUGER.

#### 3.1.1 Description

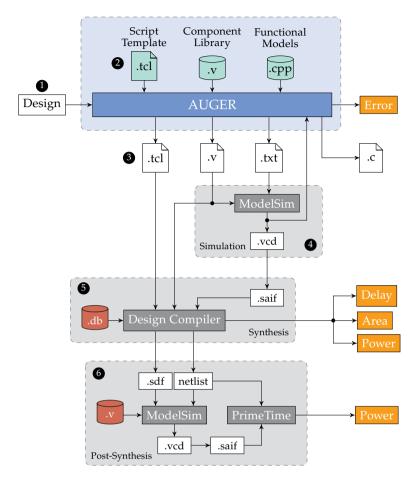

Figure 3.1 depicts AUGER and its interaction with commercial tools to synthesize and simulate circuits to characterize each circuit generated. AUGER receives the design for one of the supported approximate arithmetic circuits to be generated (see 1 in Figure 3.1). This implies the type of component, defined by its name, and parameters, such as bit-width and approximation level, according to the approximate circuit design. For instance, for approximate adders, this can include the number of approximate less significant bits (LSB) or bit-width of the sub-adders. Due to approximate arithmetic circuits can be built with different configurations, they can present different accuracy results and savings.

Using the design characteristics, AUGER employs a set of predefined templates (see 2) to generate: the corresponding RTL description in Verilog HDL (.v), a software model of the component in C language (.c), a set of 10<sup>6</sup> random uniformly distributed input vectors (.txt), generated accordingly to the input bit-width, and a set of scripts to perform synthesis and simulations (.tcl) for the generated approximate circuit (see 3). A simple formal verification of the design is performed using the results of the RTL simulation (see 4) and the internal execution of the generated software model. This allows guaranteeing that the design generated corresponds to the given parameters, but also, the software model can be used to carry out accelerator design explorations using high-level models.

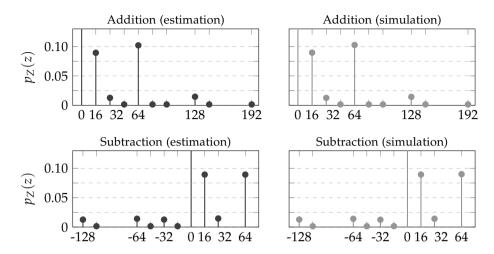

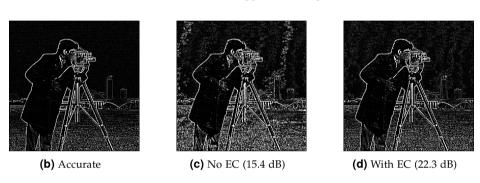

For the scope of AUGER, ModelSim is used for circuit simulations, both at presynthesis and post-synthesis level. The results of the verification are used to form an error distribution of the approximate arithmetic circuit generated, esentially for those approximate circuits that no analytical model has been proposed to obtain their error distribution [Maz+17b; Maz+17a; Wu+19]. Figure 3.2 shows two probability mass function (PMF) to represent the error distribution (see Section 2.2) for two different 8-bit approximate adders generated by AUGER. As described in Section 2.2, from this distribution, different error metrics, for instance, error rate (ER), mean error distance (MED), and worst-case error (WCE), can be obtained, which are useful to assess and compared the accuracy of the generated approximate circuit. This error distribution can be later used for error propagation estimation when using the generated approximate circuit in the design of approximate accelerators [Cas+18].

The approximate arithmetic circuit design is then synthesized for minimum delay using Synopsys Design Compiler and for a given technology library (see **5**). Area and delay characteristics, as well as preliminary power estimations, are obtained from the synthesis reports. A post-synthesis characterization is performed with

**Figure 3.1:** Main components in the AUGER tool. The AUGER tool generates an RTL for the bit-width and approximate configuration provided. AUGER relies on standard commercial tools for circuit simulation and synthesis to provide a characterization of the approximate arithmetic circuits.

Synopsys PrimeTime and a gate-level netlist simulation to obtain better power consumption estimations for the approximate circuit (see 6).

#### 3.1.2 Evaluation

In this section, three scenarios of analysis for different approximate arithmetic circuits generated with AUGER are presented, particularly for approximate adders and multipliers, as they are the primary operations present in error-tolerant appli-

**Figure 3.2:** Error distribution for two 8-bit approximate adders generated with AUGER. The error characterization is obtained with AUGER, either with simulations or analytical methods.

cations, as discussed in Section 2.1. Results have been generated using the TSMC 65 nm technology library.

#### LP approximate adder

A first comparison scenario can be performed for low-power (LP) approximate adders. In such adders, exact 1-bit full adders are replaced for inexact counterparts, and they are used to calculate the LSB of the addition. AUGER can be used to compare new proposed adders against existing ones. For this, consider that an approximate full adder has been proposed, such that s and  $c_{out}$  bits are calculated as:

$$s = (a \oplus b) \lor c_{in}$$

and  $c_{out} = a \land b$

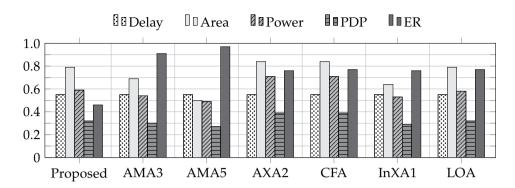

Seven 10-bit low-power approximate adders from the state-of-the-art, including one using the proposed approximate full adder, are compared. These adders include the Lower-part-OR Adder (LOA) [Mah+10], two variants of the Approximate Mirror Adder (AMA) [Gup+13], one from the Approximate XOR/XNOR-based Adders (AXA) [Yan+13], the Carry-Free Adder (CFA) [Dut+16], and one variant of the Inexact Adder by Cell Replacement (InXA) [AKL16]. For each adder, the 5 LSB bits have been approximated. Figure 3.3 presents normalized values, with respect to an accurate 10-bit ripple-carry adder (RCA), for the delay, area, power, and power-delay-product (PDP). The lower these normalized values are, the more savings are achieved. The error rate (ER) is here used to assess the accuracy of the approximate adder. In this case, a lower ER means a smaller probability of the adder to generate erroneous results.

**Figure 3.3: Comparison of LP approximate adders.** The proposed replacement for a 1-bit full addition is compared against other reported LP approximate adders. Each one corresponds to a 10-bit approximate adder with the 5 LSBs approximated.

As can be noticed from Figure 3.3, the proposed approximate adder presents good savings in terms of PDP and, in comparison to its peers, slightly surpassed by the AMA3 and InAX1. However, the proposed approximate adder has the smallest ER compared to all approximate adders presented, being more accurate in this sense.

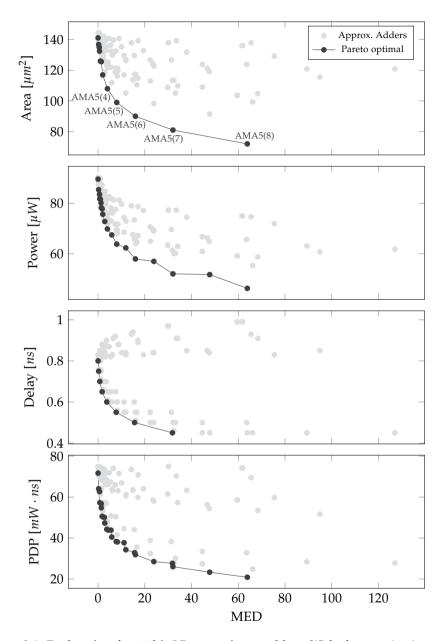

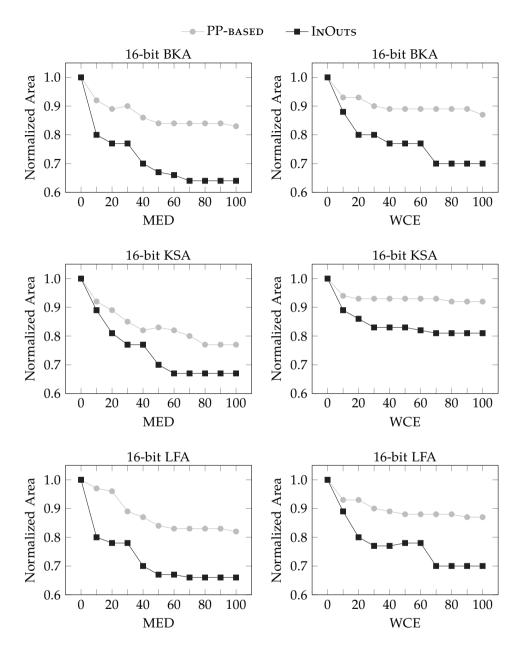

Besides this comparison of potential new LP approximate adder designs, with AUGER, it is possible to perform exhaustive explorations to find those Paretooptimal configurations from a set of reported approximate adders. In Figures 3.4 and 3.5, different configurations have been explored for 17 different LP approximate adders reported in the literature. The exploration has been made for 16 and 32 bitwidth and considering up to half of the output bits to be approximate. This means 137 and 273 different approximate adders explored for each case. Figures 3.4 and 3.5 show a set of dominant configurations for each circuit metric and considering MED as error metric. Consider the particular case of area exploration for 16bit LP adders in Figure 3.4. As depicted in the graph, different configurations of the AMA5 [Gup+13] LP approximate adder are Pareto optimal for moderate large MED tolerable. This also confirms what is presented in Figure 3.3, where the AMA5 configuration is the one with a lower area concerning the other LP approximate adders compared. Similar to for area, for the other metrics, the Paretooptimal configurations can be extracted and selected, if desired, for the design of approximate accelerators.

#### **HP** approximate adders

High-performance (HP) approximate adders correspond to those in which the addition is performed by a set of sub-adders, as described in Section 2.1. In many

**Figure 3.4:** Exploration for 16-bit LP approximate adders. With characterization performed by AUGER, it is possible to find those Pareto-optimal LP approximate adders and their aproximate configuration, in this case for 16-bit adders and MED as error metric.

**Figure 3.5:** Exploration for 32-bit LP approximate adders. With characterization performed by AUGER, it is possible to find those Pareto-optimal LP approximate adders and their aproximate configuration, in this case for 32-bit adders and MED as error metric.

**Figure 3.6:** Exploration of 8-bit GeAr approximate adders. Comparison of all possible and valid 8-bit combinations for GeAr approximate adders. A set of these configurations are Pareto-optimal solutions with respect to the rest.

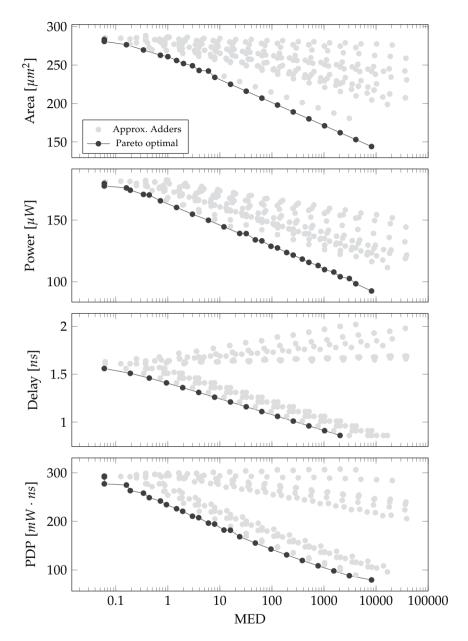

cases, for a given bit-width, several possible configurations of overlapping sub-adders can be generated. For instance, for a 16-bit GeAr adder [Sha+15], there are 22 different valid configurations. In fact, the GeAr adder can assume other HP approximate adders in its configuration, such as ACA II [KK12] and GDA [Ye+13]. When using GeAr, and for an *N*-bit addition, the most significant *R*-bits of the sub-adders are considered as resultant bits, and they are integrated as part of the final result, while the remaining *P*-bits, defined as previous bits, are used to estimate the carry propagation to upper bits.

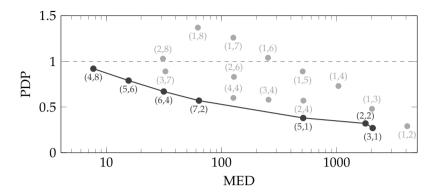

Figure 3.6 presents a comparison in terms of PDP and MED for 20 of the valid 16-bit GeAr adder configurations. The GeAr configurations are denoted as (R,P) in Figure 3.6. As it can be noticed, and considering PDP as an energy estimation, there is a set of optimal configurations placed along the Pareto front. For instance, the (6,4) configuration present smaller PDP with respect to (2,8) and (3,7), for similar MED values. Although the delay is significantly reduced for some non-optimal designs, power consumption exceeds due to the additional hardware used in the several sub-adders required. This means that that GeAr designs consume more energy (normalized PDP > 1) compared to a 16-bit RCA. From this type of comparison that can be performed with characterized approximate arithmetic circuits generated by AUGER, it is possible to select better those that minimize the required resources while meeting a defined accuracy threshold.

**Figure 3.7: Comparison of two types of approximate multipliers.** Comparison of two different 16-bit approximate multiplier approaches.

#### Approximate multipliers

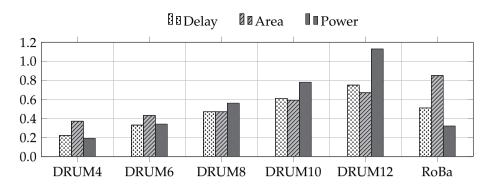

To compare approximate multipliers generated with AUGER, consider two very distinct designs from the state-of-the-art, particularly one that presents different levels of approximations per input bit-width [HBR15], and another that presents a single configuration per input bit-width [Zen+17]. Figure 3.7 presents characterization values for some of these approximate multipliers normalized with respect to an exact array multiplier. Although the RoBa multiplier presents a single configuration for each bit-width, it is capable of obtaining good total power consumption improvement, about 70%. DRUM configurations can achieve even better power improvement, such as DRUM4, but introducing a MED about two orders of magnitude higher with respect to the RoBa.

It is also noticeable that DRUM configurations can overpass an accurate multiplier power consumption while still reducing its delay, but keeping the errors smaller than for other DRUM variants. If the delay is the design constraint, this could be the right candidate as delay improvement is obtained while not introducing significant errors.

## 3.2 A Framework for Approximate Logic Synthesis

Many efforts have been made to design approximate arithmetic circuits from their accurate implementations to reduce their size, delay, and power consumption [XMK16]. For instance, one effort focuses on reducing the circuit's supply voltage to lower the power required, allowing timing errors [Mia+12], and relaxing the synthesis of specific non-critical delay paths [AH18]. Other significant effort aims

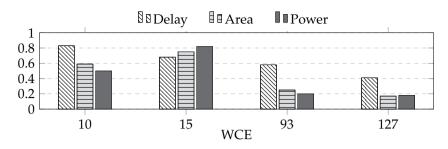

**Figure 3.8:** Characterization of four 8-bit approximate adders generated from an exact adder. Normalized values for delay, area, and power are depicted for different accuracy threshold. The adders were generated using the circuit carving technique [SAP18].

to perform functional approximations in which the functionality of an application, at register-transfer level (RTL) circuit or gate-level netlist, is simplified to trade-off accuracy for performance.

Regarding this second effort, different Approximate Logic Synthesis (ALS) methods have been proposed to generate approximate circuits from accurate implementations automatically. In the literature, three main approaches to exploit functional simplification have been reported [Sca+20]: structural netlist transformation [Sch+17; SAP18], Boolean rewriting [WQ16; HTR18], and approximate high-level synthesis [LJG17; Cas+20c].

For netlist transformations, various techniques have been reported, mostly based on the node pruning of a Direct Acyclic Graph (DAG) representations of the circuit netlist. For instance, nodes are pruned iteratively according to the significance they present to the final output and the toggle activity they have [Sch+17]. Another technique performs exhaustive exploration of all possible subsets of nodes that can be removed without surpassing a given error threshold [SAP18]. Figure 3.8 depicts the circuit properties for 8-bit approximate adders generated for a given worst-case error (WCE) (see Equation (2.2)) under this technique. As depicted, the goal is to reduce the resulting circuit's complexity, reflected in a reduction in its circuit metrics, while having a target accuracy for a specific error metric as a design constraint.

For the case of Boolean rewriting techniques, open-source contributions have been made [HTR18; MHR19]. However, to explore and implement current ALS techniques based on netlist transformation, develop methods for error modeling to avoid exhaustive simulations, and propose new netlist transformation approaches, an open-source framework that enables it is still missing.

This section presents AxLS<sup>2</sup>, a novel, open-source framework for ALS techniques based on structural netlist transformations. With AxLS, existing ALS methodologies can be implemented and new ones proposed. This section describes this novel framework and provides an experimental evaluation for arithmetic circuits.

#### 3.2.1 Description

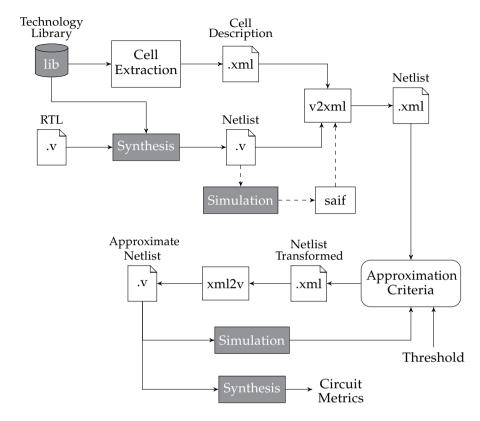

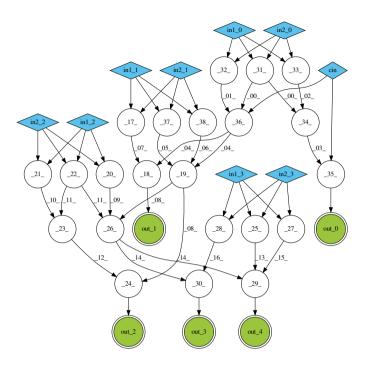

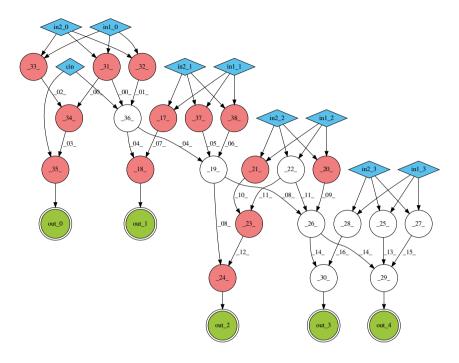

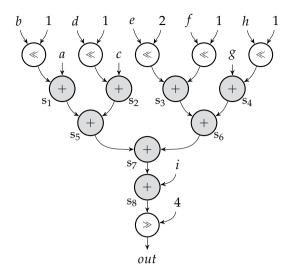

AxLS is a framework for ALS techniques based on the concept of structural netlist transformations. Figure 3.9 depicts the main components of this framework. As shown, AxLS takes as an input the Verilog RTL description of the circuit to be approximated. A netlist is generated for a specific standard cell technology library using a synthesis tool. From the same technology library, particularly from the Verilog simulation models, a description of the basic gates is extracted into an XML file. Then, using this cell description, a representation of the netlist is generated with a custom netlist to XML function (v2xml). XML files are easy to retrieve, manipulate, and save; for that reason, it was chosen for the netlist's internal representation. Figure 3.10 presents a code snippet of a toy netlist representation with XML, using the NanGate 15nm technology library. Figure 3.11 shows a DAG representation for this netlist example, generated from the XML representation. Each node corresponds to a gate in the netlist, while primary inputs and outputs are indicated.

As depicted, a post-synthesis simulation can be performed to obtain gate-level switching activity values (saif file). This information can be included in the XML netlist representation as part of each node's properties, and it can be further used to guide the netlist transformation criteria [Lin+11]. Other characteristics, such as significance or weight, and fan-out can be calculated from the netlist and added to each node [Bro+15].

With an XML representation of the netlist, approximation criteria can be applied to transform the netlist. As previously mentioned, gates can be pruned one by one considering their switching activity and impact on the output error [Sch+17]. Genetic algorithms can also be used to mutate the netlist into approximate versions by interchanging gates with wire connections [MVS19], or output pruning can be applied by removing all logic gates that affect a specific circuit output bit. AxLS provides the capability to implement such types of techniques to modify and transform the netlist.

$<sup>\</sup>overline{{}^2}$  AxLS is an open-source contribution and it is available at https://github.com/ECASLab/AxLS.

**Figure 3.9: Overview of the AxLS framework.** An XML representation of the synthesized netlist is created to manipulate it according to approximation criteria that can be defined within AxLS. AxLS uses external tools for synthesis and simulation of the accurate and approximate versions of the netlist.

Regardless of the netlist transformation technique followed, an accuracy threshold is required for a defined error metric. This accuracy target is used to assess if the approximations applied creates an approximate netlist that still produces acceptable results. According to the approximation criteria implemented within AxLS, a Verilog file with the approximate netlist can be generated from the transformed XML description, using a custom XML to netlist function (xml2v). This Verilog file generation is performed every time the accuracy of an approximate version is evaluated. The generated netlist is always based on the gates available in the cell library used for the synthesis.

Although recent techniques have been proposed to reduce the simulation dependency [Sca+19; Ech+20], by default, AxLS relies on gate-level simulations for accuracy assessment. The approximate netlist can be simulated to produce their

```

<?xml version="1.0" encoding="UTF-8"?>

<root>

<node name="INV_X2" var="u19">

<input name="A1" wire="n14" />

<output name="ZN" wire="n16" />

</node>

<node name="OAI21_X1" var="u23">

<input name="A1" wire="n14" />

<input name="A2" wire="n20" />

<output name="ZN" wire="n21" />

</node>

<node name="NAND2_X2" var="u33">

<input name="A1" wire="n16" />

<input name="A2" wire="n14" />

<output name="ZN" wire="S[1]" />

</node>

[ ... ]

<circuitinputs>

<input var="in[0]"/>

<input var="in[1]"/>

</circuitinputs>

<circuitoutputs>

<output var="S[0]"/>

<output var="S[1]"/>

</circuitoutputs>

</root>

```

**Figure 3.10:** Example of XML code for netlist description. Primary inputs and outputs, gates and their connections are easily represented with XML code.

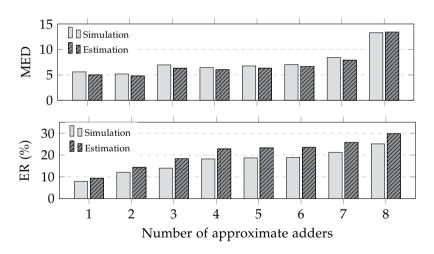

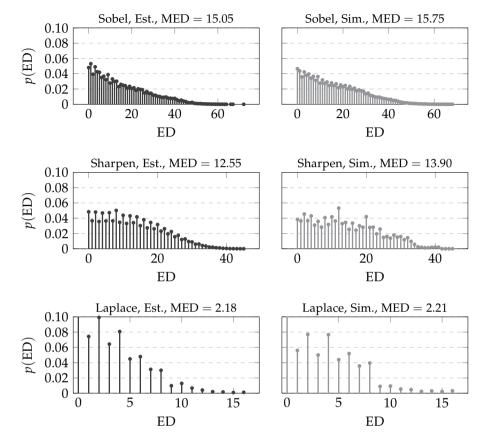

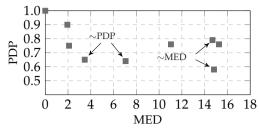

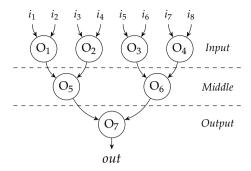

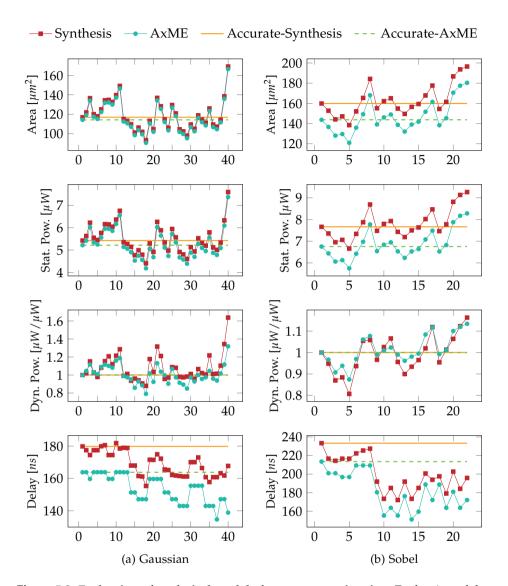

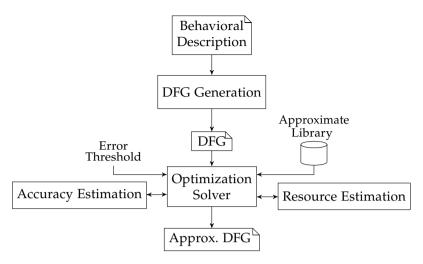

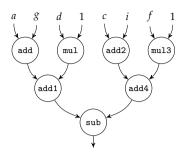

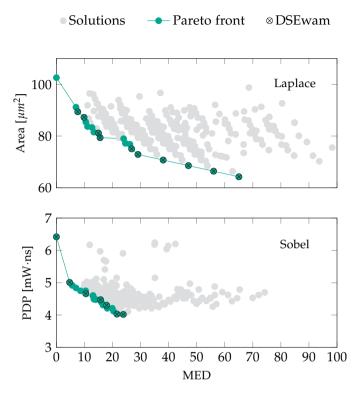

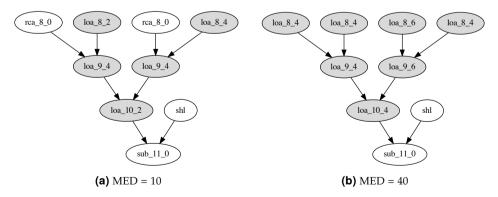

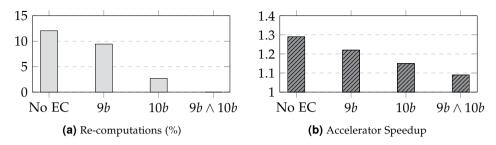

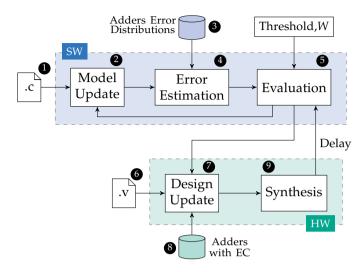

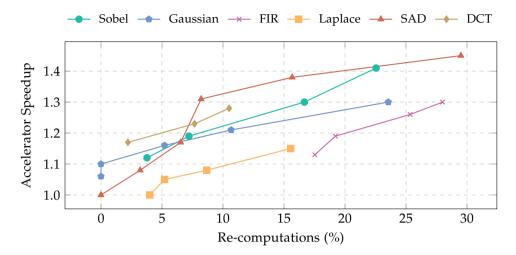

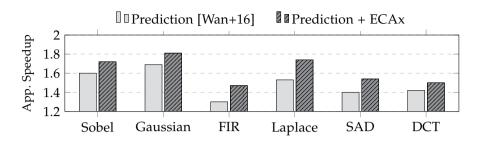

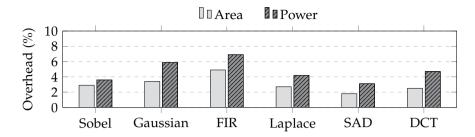

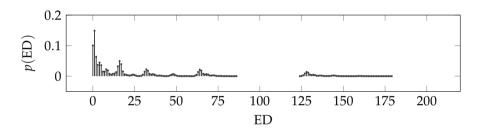

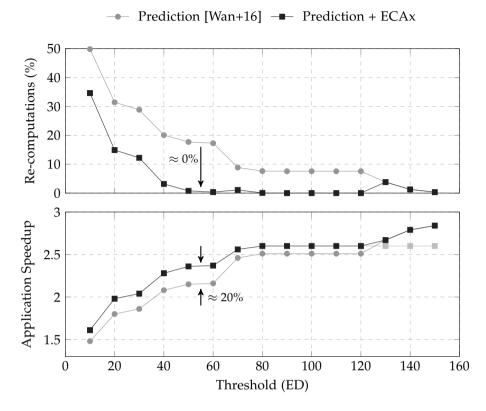

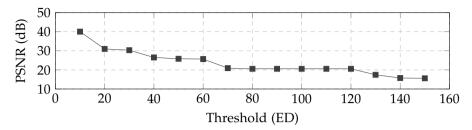

**Figure 3.11: DAG representation of an XML netlist example.** AxLS provides custom functionality to perform graphical representations of the netlists during the transformation process.