The HKU Scholars Hub The University of Hong Kong 香港大學學術庫

| Title       | A practical regularization technique for modified nodal analysi in large-scale time-domain circuit simulation    |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| Author(s)   | Chen, Q; Weng, SH; Cheng, CK                                                                                     |  |  |  |

| Citation    | IEEE Transactions on Computer-Aided Design of Integrated<br>Circuits and Systems, 2012, v. 31 n. 7, p. 1031-1040 |  |  |  |

| Issued Date | 2012                                                                                                             |  |  |  |

| URL         | http://hdl.handle.net/10722/174230                                                                               |  |  |  |

| Rights      | IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. Copyright © IEEE                  |  |  |  |

# A Practical Regularization Technique for Modified Nodal Analysis in Large-Scale Time-Domain Circuit Simulation

Quan Chen, Member, IEEE, Shih-Hung Weng, Student Member, IEEE, and Chung-Kuan Cheng, Fellow, IEEE

Abstract-Fast full-chip time-domain simulation calls for advanced numerical integration techniques with capability to handle the systems with (tens of) millions of variables resulting from the modified nodal analysis (MNA). General MNA formulation, however, leads to a differential algebraic equation (DAE) system with singular coefficient matrix, for which most of explicit methods, which usually offer better scalability than implicit methods, are not readily available. In this paper, we develop a practical two-stage strategy to remove the singularity in MNA equations of large-scale circuit networks. A topological index reduction is first applied to reduce the DAE index of the MNA equation to one. The index-1 system is then fed into a systematic process to eliminate excess variables in one run, which leads to a nonsingular system. The whole regularization process is devised with emphasis on exact equivalence, low complexity, and sparsity preservation, and is thus well suited to handle extremely large circuits.

Index Terms—Explicit method, graph theory, index reduction, modified nodal analysis (MNA), singular matrix.

## I. INTRODUCTION

THE EVER-INCREASING integration density of modern integrated circuit (IC) designs has made the runtime of SPICE-like simulation [1] a bottleneck in the IC design flow. A circuitry modeled by modified nodal analysis (MNA) with millions of variables usually takes days, even weeks, to complete a time-domain simulation. The major reason is that mainstream circuit simulators adopt implicit numerical integration methods, e.g., backward Euler, for the sake of stability. The scalability, however, is to some extent sacrificed since solving large systems of differential equations is costly and difficult for parallelization.

The explicit methods (e.g., forward Euler), on the other hand, eliminate the need of actually solving a large linear system, and thus provide a much better scalability. Despite the well-known stability problem, the explicit methods have recently become a revived research area owing to the potential

Manuscript received June 14, 2011; revised October 12, 2011 and December 4, 2011; accepted January 9, 2012. Date of current version June 20, 2012. This work was supported by the National Science Foundation, under the Project CCF-1017864. This paper was recommended by Associate Editor A. Demir.

Q. Chen is with the Department of Electrical and Electronic Engineering, University of Hong Kong, Pokfulam, Hong Kong (e-mail: q1chen@ucsd.edu).

S.-H. Weng and C.-K. Cheng are with the Department of Computer Science and Engineering, University of California, San Diego/La Jolla, CA 92093 USA (e-mail: s2weng@ucsd.edu; ckcheng@ucsd.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCAD.2012.2184761

to respond to the demand of simulating million-scale problems. Previous efforts include adaptive time step for better stability [2], telescopic projective integration [3], and recent work on matrix exponential method, which allows the usage of even larger time step than implicit methods [4], [5].

One hurdle of explicit methods, on top of the stability issue (and kind of "overlooked" in the past), is the singular matrix problem associated with the MNA formulation. Recall that in MNA a circuit network is described by a system of differential algebraic equations (DAEs)

$$\mathbf{C}\dot{\mathbf{x}}(t) = -\mathbf{G}\mathbf{x}(t) + \mathbf{B}\mathbf{u}(t) \tag{1}$$

where matrix **C** collects the effects of capacitances and inductances, matrix **G** collects the effects of resistance and the incidence matrix for current variable vector, vector  $\mathbf{x}(t)$  consists of all node voltages and some branch currents, and vector  $\mathbf{u}(t)$  denotes the independent sources.

Before most explicit methods can actually get started, (1) should preferably be convertible to a system of ordinary differential equations (ODEs) (for which these methods were developed in the first place)

$$\dot{\mathbf{x}}(t) = -\mathbf{C}^{-1}\mathbf{G}\mathbf{x}(t) + \mathbf{C}^{-1}\mathbf{B}\mathbf{u}(t)$$

(2)

which naturally requires the coefficient matrix C to be nonsingular. Implicit methods, on the other hand, relax the restriction on matrix invertibility. In backward Euler, for instance, only the matrix C/h + G needs to be nonsingular, where *h* is the time step size.

The most common causes of singular C in MNA formulation are the empty rows corresponding to the nodes in the absence of capacitances, and the currents of independent and controlled voltage sources of which no time differential terms are present in (1). On top of this "explicit" singularity, it is often the case that some "hidden" dependence among MNA variables exists in a given circuit, rendering the C matrix singular or ill-conditioned even none of its rows are empty [6].

In this paper, we develop an effective method to regularize the DAE (1), i.e., to derive an equivalent equation with a nonsingular C. In control theory, this amounts to converting the descriptor representation [7] of a circuit to an explicit state-space representation. To handle the large sparse matrices from real IC designs, our technique consists of two stages. By analyzing the topology with graph theory, an index reduction technique is first applied to reduce the DAE index of the MNA equation; then a systematic elimination is employed to remove the dependence among variables in one run ending up with a nonsingular system.

Our motivation is to offer a practical and cost-effective regularization solution for the majority of the real-world problems, without appealing to complete but complicated mathematics. In other words, we recognize the fact that most problems we have to deal with do not require so much generality, and instead can be resolved by less rigorous approaches in a more efficient manner. The rationale behind our method is to avoid (to most extent) certain matrix operations, such as (iterative) LU decompositions and matrix-matrix multiplications, which tend to damage the sparsity of MNA matrices. This is crucial for any practical techniques in large-scale circuit simulation considering the giant problem sizes. We achieve this goal by preprocessing the DAE index and the floating capacitors before systematic elimination, and using topology analysis to guide the preprocessing so that it affects only a small portion of the matrices. The proposed method also sheds some lights on relevant problems in other areas such as model order reduction [8].

## **II. SYSTEMATIC ELIMINATION**

One widely used regularization method in previous work (e.g. [9]) is to reorder all nonzero entries of **C** to the upper left corner and partition (1) into two sets of equations

$$\begin{bmatrix} \mathbf{C}_{11} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} \end{bmatrix} \begin{bmatrix} \dot{\mathbf{x}}_1 \\ \dot{\mathbf{x}}_2 \end{bmatrix} = -\begin{bmatrix} \mathbf{G}_{11} & \mathbf{G}_{12} \\ \mathbf{G}_{21} & \mathbf{G}_{22} \end{bmatrix} \begin{bmatrix} \mathbf{x}_1 \\ \mathbf{x}_2 \end{bmatrix} + \begin{bmatrix} \mathbf{B}_1 \\ \mathbf{B}_2 \end{bmatrix} \mathbf{u}.$$

(3)

Provided the submatrix  $G_{22}$  is invertible, (3) can be converted to an equation of  $\mathbf{x}_1$  by the substitution of  $\mathbf{x}_2$ . Once  $C_{11}$  is also nonsingular, the whole system becomes regular. In spite of the simplicity, the applicability of this approach is rather limited. It relies upon the invertibility of both  $C_{11}$  and  $G_{22}$ , which is generally not guaranteed in MNA formulation.

Chua and Lin in their classic book [6] provided a generic approach to obtain the state-space model for a circuit network with an arbitrarily high DAE index. The triplet [C, G, B] is reduced to the row echelon form recursively, and during each reduction some excess variables are eliminated. A method based on similar idea but specific to MNA formulation was developed by Natarajan [10], in which the nonzero entries are concentrated on the entire upper part of C (instead of only the top left corner) by the row echelon reduction

$$\begin{bmatrix} \mathbf{C}_{11} \ \mathbf{C}_{12} \\ 0 \ 0 \end{bmatrix} \begin{bmatrix} \dot{\mathbf{x}}_1 \\ \dot{\mathbf{x}}_2 \end{bmatrix} = -\begin{bmatrix} \mathbf{G}_{11} \ \mathbf{G}_{12} \\ \mathbf{G}_{21} \ \mathbf{G}_{22} \end{bmatrix} \begin{bmatrix} \mathbf{x}_1 \\ \mathbf{x}_2 \end{bmatrix} + \begin{bmatrix} \mathbf{B}_{01} \\ \mathbf{B}_{02} \end{bmatrix} \mathbf{u}.$$

(4)

After (4) is obtained, another row echelon transform is applied to the submatrix of  $[G_{21} G_{22}]$  from the bottom row, which is essentially a UL decomposition [11]. The columns of **G** and **C** are rearranged to ensure  $G_{22}$  is lower triangular. Finally, block Gaussian elimination (GE) is used to obtain a reduced system of equations

$$\mathbf{C}_r \dot{\mathbf{x}}_1 = -\mathbf{G}_r \mathbf{x}_1 + \mathbf{B}_{0r} \mathbf{u} + \mathbf{B}_{1r} \dot{\mathbf{u}}$$

(5)

where

$$\mathbf{C}_r = \mathbf{C}_{11} - \mathbf{C}_{12}\mathbf{G}_{22}^{-1}\mathbf{G}_{21} \quad \mathbf{G}_r = \mathbf{G}_{11} - \mathbf{G}_{12}\mathbf{G}_{22}^{-1}\mathbf{G}_{21} \quad (6a)$$

$$\mathbf{B}_{0r} = \mathbf{B}_{01} - \mathbf{G}_{12}\mathbf{G}_{22}^{-1}\mathbf{B}_{02} \quad \mathbf{B}_{1r} = -\mathbf{C}_{12}\mathbf{G}_{22}^{-1}\mathbf{B}_{02}$$

(6b)

$$\mathbf{x}_2 = -\mathbf{G}_{22}^{-1} \left( \mathbf{G}_{21} \mathbf{x}_1 - \mathbf{B}_{02} \mathbf{u} \right).$$

(6c)

Note that the derivative term of source **R** in (5) arises from the cross-coupling term  $C_{12}\dot{x}_2$ . The substitution of the latter differentiates the lower set of equations in (4), leading to the differentiation of the source term. Provided  $C_r$  is invertible, a variable transform of  $\mathbf{x}_r = \mathbf{x}_1 - C_r^{-1}\mathbf{B}_{1r}\mathbf{u}$  is applied to absorb the derivative of **u**, yielding a regular ODE as in (2)

$$\mathbf{C}_r \dot{\mathbf{x}}_r = -\mathbf{G}_r \mathbf{x}_r + \mathbf{B}_r \mathbf{u} \tag{7}$$

with  $\mathbf{B}_r = \mathbf{B}_{0r} - \mathbf{G}_r \mathbf{C}_r^{-1} \mathbf{B}_{1r}$ .

The systematic elimination described in (4)–(7) is a component of our regularization framework. The direct application of this processs, however, has two bottlenecks: 1) reducing **C** to the row echelon form is costly (LU decomposition with row pivoting), and will introduce fill-ins into **G** during concurrent elementary operations (matrix-matrix multiplications); and 2) the matrix  $\mathbf{C}_r$  can remain singular after the first round of regularization, and if so, the process has to be repeated to eliminate more variables from  $\mathbf{x}_1$  until a nonsingular  $\mathbf{C}_r$  is achieved. This situation arises when the system of DAE has an index higher than one, i.e., the output equation contains derivatives of the source terms, which can appear in the systematic elimination only after the second cycle [10]. Such iterative check and elimination of singularity is unfavorable for computational efficiency and sparsity preservation.

Note that the DAE index of a circuit can be arbitrarily high depending on its topology, but is usually no higher than 2 in practice. Index-3 (or higher) circuits are generally not suitable for computer simulation [6]. In this paper, we restrict our focus to index-2 circuits that represent the majority of the designs of practical interest. These index-2 systems in most cases result from the presence of CV-loops and LI-cutsets in the topology [12]. Hence, the key to address the second bottleneck lies in reducing an index-2 circuit to its index-1 equivalent *prior to* the elimination process of (4) by breaking all CV-loops and LI-cutsets in the topology. The index-1 system is then fed into (4) which is guaranteed to stop after the first iteration.

## **III. TOPOLOGICAL INDEX REDUCTION**

Generic index reduction of DAEs can be realized by the spectral projector technique [13]. Provided that the MNA matrices are known, the spectral projector can be constructed analytically through a lengthy matrix computation [14]. However, this construction process does not preserve sparsity, i.e., the projected matrices tend to be dense. Alternatively, an element-based topological index reduction method is proposed in [15] and [16] based on the concept of minimal extension. The virtue is that no algebraic (matrix) transformation is required; only the netlist needs to be augmented. Nevertheless, CHEN et al.: PRACTICAL REGULARIZATION TECHNIQUE FOR MODIFIED NODAL ANALYSIS

$$\begin{bmatrix} C_{kk} & C_{kl} & 0\\ C_{lk} & C_{ll} & 0\\ \hline 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} \dot{v}_k\\ \dot{v}_l\\ \dot{i}_v \end{bmatrix} = -\begin{bmatrix} G_{kk} & G_{kl} & 1\\ G_{lk} & G_{ll} & -1\\ \hline -1 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_k\\ v_l\\ \dot{i}_v \end{bmatrix} + \begin{bmatrix} 0\\ 0\\ 1 \end{bmatrix} [Vs]$$

(8a)

$$\begin{bmatrix} C_{kk} & C_{kl} & 0\\ C_{kk} + C_{lk} & C_{kl} + C_{ll} & 0\\ \hline 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} \dot{v}_k\\ \dot{v}_l\\ \dot{i}_v \end{bmatrix} = -\begin{bmatrix} G_{kk} & G_{kl} & 1\\ G_{kk} + G_{lk} & G_{kl} + G_{ll} & 0\\ \hline -1 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_k\\ v_l\\ \dot{i}_v \end{bmatrix} + \begin{bmatrix} 0\\ 0\\ 1 \end{bmatrix} [Vs]$$

(8b)

$$\begin{bmatrix} C_{kk} & C_{kl} & 0\\ C_{kk} + C_{lk} & C_{kl} + C_{ll} & 0\\ \hline 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} \dot{v}_k\\ \dot{v}_l\\ \dot{i}_v \end{bmatrix} = -\begin{bmatrix} G_{kk} & G_{kl} & 1\\ 0 & G_{kk} + G_{lk} + G_{kl} + G_{ll} & 0\\ \hline -1 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_k\\ v_l\\ \dot{i}_v \end{bmatrix} + \begin{bmatrix} 0\\ G_{kk} + G_{lk}\\ 1 \end{bmatrix} [Vs]$$

(8c)

$$\begin{bmatrix} C_{kk} & C_{kl} & 0\\ C_{kk} + C_{lk} & C_{kl} + C_{ll} & 0\\ \hline -1 & 1 & 0 \end{bmatrix} \begin{bmatrix} \dot{v}_k\\ \dot{v}_l\\ \dot{i}_v \end{bmatrix} = -\begin{bmatrix} G_{kk} & G_{kl} & |1\\ 0 & G_{kk} + G_{lk} + G_{kl} + G_{ll} & 0\\ \hline 0 & 0 & |0 \end{bmatrix} \begin{bmatrix} v_k\\ v_l\\ \dot{i}_v \end{bmatrix} + \begin{bmatrix} 0\\ G_{kk} + G_{lk}\\ \hline 0 \end{bmatrix} \begin{bmatrix} Vs] + \begin{bmatrix} 0\\ 0\\ 1 \end{bmatrix} \begin{bmatrix} \dot{V}s]$$

(8d)

$$\begin{bmatrix} C_{kk} & C_{kl} & | & 0 \\ 0 & C_{kk} + C_{lk} + C_{kl} + C_{ll} & 0 \\ \hline -1 & 1 & | & 0 \end{bmatrix} \begin{bmatrix} \dot{v}_k \\ \dot{v}_l \\ \dot{v}_l \end{bmatrix} = -\begin{bmatrix} G_{kk} & G_{kl} & | & 1 \\ 0 & G_{kk} + G_{lk} + G_{ll} & 0 \\ \hline 0 & 0 & | & 0 \end{bmatrix} \begin{bmatrix} v_k \\ v_l \\ \dot{v}_l \end{bmatrix} + \begin{bmatrix} 0 \\ G_{kk} + G_{lk} \\ \hline 0 \end{bmatrix} \begin{bmatrix} v_s \\ + C_{kk} + C_{lk} \\ \hline 1 \end{bmatrix} \begin{bmatrix} \dot{v}_s \\ \dot{v}_s \end{bmatrix}$$

(8e)

$[C_{kk} + C_{lk} + C_{kl} + C_{ll}][\dot{v}_l] = -[G_{kk} + G_{lk} + G_{kl} + G_{ll}][v_l] + [G_{kk} + G_{lk}][V_s] + [C_{kk} + C_{lk}][\dot{V}_s]$ (8f)

this method adds two unknowns into the system for every capacitor to be replaced. For networks with a large number of capacitor loops, e.g., with many capacitors mounted in parallel, this will increase the problem size considerably [17].

The index reduction method we develop here combines topology analysis and algebraic transformation in such a way that the algebraic transformation (mostly elementary row operations) is only applied to a small portion of the original system selected by the topology analysis. Modifications are made on the matrix equation instead of the netlist for better adaptability. One key observation is that a loop with capacitors only does not lead to an index-2 system in MNA; only when voltage source(s) come into the loop will the circuit become index-2 [18]. This is different from *L1*-cutsets where inductors alone can form a cutset leading to an index-2 system (because inductor currents are state variables in MNA).

## A. Elimination of Voltage Sources

The first step of our topological index reduction is to eliminate all voltage sources. One (nondatum) node voltage and the branch current are eliminated for each (independent and controlled) voltage source regardless of whether it is part of a *CV*-loop. The intention of this elimination to break all *potential CV*-loops *in one shot*, which takes advantage of the (usually) small number of voltage sources in a given circuit. The MNA stamp of an independent voltage source is shown in (8a) and the corresponding elimination procedure is described in (8b)–(8f) (suppose  $v_k$  and  $i_v$  are eliminated). In (8b), the KCL of node *k* is applied to eliminate  $i_v$  at node *l*. In (8c),  $v_k$  is eliminated using the branch constitutive equation (BCE) of the independent voltage source. We enforce the implicit constraint in (8d) by differentiating the BCE, after which the derivative

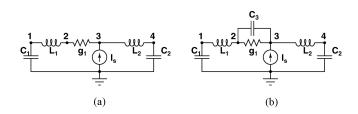

Fig. 1. LI-cutset examples. (a) Simple example of LI-cutset. (b) All terminals of inductors are connected to capacitors.

of *Vs* appears in the RHS. With the implicit constraint,  $\dot{v}_k$  is eliminated in (8e). After deleting the rows and columns of  $v_k$  and  $i_v$ , we obtain the reduced equation (8f). The eliminations of the two types of controlled voltage sources, VCVS and CCVS, are described in the Appendix.

Note that when a voltage source is connected to a large number of elements at the same node, the elimination of this "supernode" has a chance to generate some rows/columns with a large number of nonzeros, with the total amount of nonzeros staying roughly the same or even becoming smaller. The dense rows/columns may affect the performance of sparse solvers in finding a good reordering for the sparse matrix. Hence, it is advisable to monitor the sparsity change in rows/columns involved in the elimination process during the implementation, and issue a warning if highly dense rows/columns are generated.

## B. Breaking of LI-Cutsets

The second step is to break all LI-cutsets. The procedure is similar to the elimination of voltage sources, except that one inductor (not current source) per LI-cutset must be selected for elimination. A proper selection of the target inductors

$$\begin{bmatrix} C_{1} & & & & \\ 0 & & & \\ C_{2} & & & \\ \hline & \\ \hline & & \\ \hline & & \\ \hline & \\ \hline & \\ \hline & & \\ \hline &$$

relies on deriving a reduced graph from the original network with only inductive branches and current sources. Then the inductors belonging to the tree branches of the reduced graph are selected [16]. For each selected inductor, the selection of nodes for elimination depends on the capacitors attached to the terminals of the inductor. Generally, at least one terminal of the inductor has no attached capacitors, and this node will be the one to eliminate. An example of *L1*-cutset is shown in Fig. 1(a) and the corresponding procedure to eliminate  $i_{L1}$ and  $v_2$  (the node without capacitors) is shown in (9). A mutual inductance *K* between  $L_1$  and  $L_2$  is also included. The altered entries at each step are highlighted in bold.

In (9b),  $i_{L_1}$  is eliminated from **G** by the current law of the *L1*-cutset (10a). The differential current  $\dot{i}_{L_1}$  is eliminated from **C** in (9c) using the differential current law (10b) of the *L1*-cutset

$$i_{L_1} - i_{L_2} + Is = 0 \tag{10a}$$

$$\dot{i}_{L_1} - \dot{i}_{L_2} + \dot{I}s = 0.$$

(10b)

In (9d), the dependence of  $v_2$  in the second and third rows of **G** is eliminated by the BCE of  $L_1$  (the fifth row). By removing the rows and columns corresponding to  $v_2$  and  $i_{L_1}$ we get (9e). Notice that the second column of **C** is empty, which indicates the KCL at node 3 is an algebraic constraint despite the nonempty row in **C**. In this case, one could either eliminate  $g_1(L_1 + K)$  by the fourth row of **C** to illuminate the algebraic nature of the KCL, or simply eliminate  $v_3$ by algebraic substitution. Equation (9f) is resulted from the elimination of  $v_3$ .

One exception arises when all terminals of the selected inductor are connected to capacitors. An example of this exception is shown in Fig. 1(b), where a parallel capacitor  $C_3$  is added. In such a case, the **C** matrix in (9c) becomes

$$\begin{bmatrix} C_1 & & & \\ & \mathbf{C}_3 & -\mathbf{C}_3 & \\ & -\mathbf{C}_3 & \mathbf{C}_3 & \\ & & C_2 & \\ \hline & & & 0 & L_1 + K \\ & & & 0 & L_2 + K \end{bmatrix}.$$

(11)

Due to the dependence of  $\dot{v}_2$  in **C**, we can no longer use the BCE of  $L_1$  to eliminate  $v_2$  from the unknown list as done in (9d). However, one can prove the following lemma related to the concept of floating capacitors, which is defined as a

| Algorithm 1: Breaking procedure of L1-cutset                                                                       |

|--------------------------------------------------------------------------------------------------------------------|

| <b>Input</b> : matrices C, G, $B_0$ , $B_1$                                                                        |

| Identify all L1-cutsets via topology analysis;                                                                     |

| Select one inductor $L_e$ from each cutset for elimination;                                                        |

| Eliminate $i_{L_e}$ and $\dot{i}_{L_e}$ using the algebraic and differential                                       |

| KCL of the cutset;                                                                                                 |

| <b>if</b> one terminal $n_e$ of $L_e$ has no capacitor <b>then</b><br>Eliminate $v_{n_e}$ using the BCE of $L_e$ ; |

| else                                                                                                               |

| Invoke floating capacitor routine to eliminate one                                                                 |

| redundant node voltage;                                                                                            |

| end                                                                                                                |

| Remove corresponding rows and columns from the MNA                                                                 |

| equations.                                                                                                         |

group of connected capacitors that have no path of capacitors to the ground node.

*Lemma 1:* If any inductor in a *L1*-cutset has all its terminals attached to capacitors, there is at least one terminal that all the attached capacitors are (part of) a set of floating capacitors.

*Proof:* A *LI*-cutset refers to a set of inductor and current source branches on which the algebraic sum of currents is zero all the time. If any inductor in an *LI*-cutset is connected to nonfloating capacitors at all its terminals, one (neither inductor nor current source) current bypass will form and the *LI*-cutset will be broken. In other words, at least one set of terminal capacitors of the inductor must all locate within the generalized node (a subcircuit) isolated by the inductors and current sources, and hence must be floating.

To deal with this exception, a special treatment for floating capacitors will be invoked to eliminate one node voltage, which will be detailed in the next section. The whole procedure of LI-cutset elimination is summarized in Algorithm 1.

## **IV. TREATMENT FOR FLOATING CAPACITORS**

An index-1 system results, after eliminating all voltage sources and the selected inductors from the topology

$$\hat{\mathbf{C}}\dot{\hat{\mathbf{x}}} = -\hat{\mathbf{G}}\hat{\mathbf{x}} + \hat{\mathbf{B}}_{0r}\mathbf{u} + \hat{\mathbf{B}}_{1r}\dot{\mathbf{u}}.$$

(12)

The matrix  $\hat{\mathbf{C}}$  may still be singular, due to the hidden (algebraic) singularity in  $\hat{\mathbf{C}}$  caused by floating capacitors, i.e., in each group of floating capacitors one node voltage is dependent on the others. To reveal such singularity, an LU decomposition is needed to reduce  $\hat{\mathbf{C}}$  to the row echelon form as in (4). Nevertheless, if this singularity can be detected and eliminated in advance via topology analysis, the LU decomposition can actually be replaced by a simple permutation of all nonzero rows to the upper part of  $\hat{\mathbf{C}}$ , which is much more desirable in terms of speed and sparsity.

To this end, we represent each group of floating capacitors by a connected component in a derived graph comprising only capacitive nodes and branches. The MNA stamp of a 3node floating capacitors group is given in (13a). The algebraic constraint of the floating capacitors implies the relevant rows

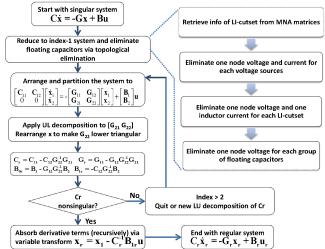

Fig. 2. Flow of the regularization process.

in  $\hat{\mathbf{C}}$  add up to zero as shown in (13b). Provided the row summation in  $\hat{\mathbf{G}}$  leads to at least one nonzero pivot entry for voltage (assuming  $\sum \hat{G}_{*k}$  for  $\hat{v}_k$ ),  $\hat{v}_k$  (and  $\dot{\hat{v}}_k$ ) can then be eliminated by the algebraic (and differential) KCL at node k. The nonzero pivoting appears when the subgraph of connected component has at least one outgoing branch of resistor

$$\begin{bmatrix} \hat{C}_{kk} & \hat{C}_{kl} & \hat{C}_{km} \\ \hat{C}_{lk} & \hat{C}_{ll} & \hat{C}_{lm} \\ \hat{C}_{mk} & \hat{C}_{ml} & \hat{C}_{mm} \end{bmatrix} \begin{bmatrix} \dot{\hat{v}}_{k} \\ \dot{\hat{v}}_{l} \\ \dot{\hat{v}}_{m} \end{bmatrix} = -\begin{bmatrix} \hat{G}_{kk} & \hat{G}_{kl} & \hat{G}_{km} \\ \hat{G}_{lk} & \hat{G}_{lm} & \hat{G}_{lm} \\ \hat{G}_{mk} & \hat{G}_{ml} & \hat{G}_{lm} \end{bmatrix} \begin{bmatrix} \hat{v}_{k} \\ \hat{v}_{l} \\ \dot{\hat{v}}_{m} \end{bmatrix} + \begin{bmatrix} \hat{I}_{s_{k}} \\ \hat{I}_{s_{l}} \\ \hat{I}_{s_{m}} \end{bmatrix}$$

(13a)

$$\begin{bmatrix} 0 & 0 & 0 \\ \hat{C}_{lk} & \hat{C}_{ll} & \hat{C}_{lm} \\ \hat{C}_{mk} & \hat{C}_{ml} & \hat{C}_{mm} \end{bmatrix} \begin{bmatrix} \dot{\hat{v}}_{k} \\ \dot{\hat{v}}_{l} \\ \dot{\hat{v}}_{m} \end{bmatrix} = -\begin{bmatrix} \sum \hat{G}_{sk} & \sum \hat{G}_{sl} & \sum \hat{G}_{sm} \\ \hat{G}_{lk} & \hat{G}_{ll} & \hat{G}_{lm} \\ \hat{G}_{mk} & \hat{G}_{ml} & \hat{G}_{mm} \end{bmatrix} \\ \begin{bmatrix} \hat{v}_{k} \\ \hat{v}_{l} \\ \hat{v}_{m} \end{bmatrix} + \begin{bmatrix} \sum \hat{I}_{s_{s}} \\ \hat{I}_{s_{l}} \\ \hat{I}_{s_{m}} \end{bmatrix} .$$

(13b)

If all row pivotings in **G** for voltages are zero after the summation, i.e., the resistor group also forms a connected component isolated by current variable branches (inductors or voltage sources), a general treatment based on transforming node voltages to branch voltages can be exploited [19]. The rationale is to transform the node voltages  $[v_1, v_2, ..., v_n]^T$  in each set of floating capacitors, to the "branch" voltage with reference to  $v_n$ , namely,  $[v_1 - v_n, v_2 - v_n, ..., v_n]^T$ . The new "reference voltage"  $v_n$  is then eliminated to reduce the number of unknowns by one.

Taking (11) as an example, the node-branch transform procedure is shown in (14). Suppose  $v_3$  is selected as the new reference node, then in the remaining nodes, there must be one node ( $v_2$  in this case) having at least one outgoing current variable branch ( $i_{L_1}$ ). The BCE of this current branch is used to eliminate the dependence of  $v_2$  (except the  $v_2$  row itself), then the node-branch voltage transformation is carried out to transform  $v_2$  to  $v_2 - v_3$ . The *partial* elimination of  $v_2$  in (14a) is to ensure the nonzero pivot element of  $v_3$ in **G** after the node-branch transformation [see (14c)]. The empty column in **C** at the same step results from the algebraic

$$\begin{bmatrix} C_{1} & & & \\ -C_{3} & -C_{3} & & \\ -C_{3} & C_{3} & & \\ -C_{3} & C_{3} & & \\ -C_{3} & C_{3} & & \\ 0 & L_{1} + K \\ 0 & L_{2} + K \end{bmatrix} \begin{bmatrix} \dot{v}_{1} \\ \dot{v}_{2} \\ \dot{v}_{3} \\ \dot{v}_{4} \\ \dot{l}_{L_{1}} \\ \dot{l}_{L_{2}} \end{bmatrix} = -\begin{bmatrix} & & & & & \\ g_{1} - g_{1} & g_{1} & & \\ -1 & 1 & & \\ -1 & 1 & \\ \end{bmatrix} \begin{bmatrix} v_{1} \\ v_{2} \\ v_{3} \\ \dot{v}_{4} \\ \dot{l}_{L_{1}} \\ \dot{l}_{L_{2}} \end{bmatrix} + \begin{bmatrix} 1 \\ -1 \\ 1 \\ -1 \\ \hline \end{bmatrix} \begin{bmatrix} Is \end{bmatrix} + \begin{bmatrix} 1 \\ L_{1} \\ K \end{bmatrix} \begin{bmatrix} is \end{bmatrix} (14a)$$

$$\begin{bmatrix} C_{1} \\ -C_{3} & C_{3} \\ -C_{3} & C_{3} \\ C_{2} \end{bmatrix} 0 g_{1}(L_{1} + K) \\ \hline L_{1} + K \\ L_{2} + K \end{bmatrix} \begin{bmatrix} \dot{v}_{1} \\ \dot{v}_{3} \\ \dot{v}_{4} \\ \dot{i}_{L_{1}} \\ \dot{i}_{L_{2}} \end{bmatrix} = -\begin{bmatrix} g_{1} & 0 & 1 \\ -g_{1} & 0 & g_{1} & 0 & 1 \\ -g_{1} & 0 & g_{1} & 0 & 1 \\ -1 & 1 & 1 \\ \hline \end{bmatrix} \begin{bmatrix} v_{2} \\ v_{3} \\ v_{4} \\ \dot{i}_{L_{2}} \end{bmatrix} + \begin{bmatrix} -1 \\ -1 \\ -1 \\ -1 \\ \hline \end{bmatrix} \begin{bmatrix} Is \end{bmatrix} + \begin{bmatrix} L_{1}g_{1} \\ L_{1}g_{1} \\ K \end{bmatrix} \begin{bmatrix} is \end{bmatrix} (14b)$$

$$\begin{bmatrix} C_{1} \\ C_{3} & 0 \\ -C_{3} & 0 \\ C_{2} & 0 & L_{1} + K \\ 0 & L_{2} + K \end{bmatrix} \begin{bmatrix} \dot{v}_{1} \\ \dot{v}_{2} \\ \dot{v}_{3} \\ \dot{v}_{4} \\ \dot{i}_{L_{1}} \end{bmatrix} = -\begin{bmatrix} g_{1} & 0 & 0 & 1 \\ 0 & -1 \\ -1 & 1 & 1 \\ -1 & 1 \end{bmatrix} \begin{bmatrix} v_{2} - v_{3} \\ v_{3} \\ v_{4} \\ \dot{i}_{L_{2}} \end{bmatrix} + \begin{bmatrix} -1 \\ -1 \\ -1 \\ -1 \\ -1 \end{bmatrix} \begin{bmatrix} Is \end{bmatrix} + \begin{bmatrix} L_{1}g_{1} \\ L_{1}g_{1} \\ K \end{bmatrix} \begin{bmatrix} is \end{bmatrix} (14b)$$

$$\begin{bmatrix} C_{1} \\ C_{3} & 0 \\ -C_{3} & 0 \\ C_{2} & 0 \\ -C_{3} & 0 \\ C_{2} & 0 \\ 0 & L_{1} + K \\ 0 & L_{2} + K \end{bmatrix} \begin{bmatrix} \dot{v}_{1} \\ \dot{v}_{2} & \dot{v}_{3} \\ \dot{v}_{4} \\ \dot{i}_{L_{1}} \end{bmatrix} = -\begin{bmatrix} g_{1} & 0 \\ 0 & 0 \\ -1 \\ -1 & 1 \\ -1 \\ 1 \end{bmatrix} \begin{bmatrix} v_{1} \\ 0 \\ 0 \\ -1 \\ -1 \\ 1 \end{bmatrix} \begin{bmatrix} v_{1} \\ v_{2} - v_{3} \\ v_{4} \\ \dot{i}_{L_{1}} \end{bmatrix} + \begin{bmatrix} 1 \\ -1 \\ -1 \\ 0 \\ 1 \\ \frac{1}{g_{1}} \end{bmatrix} \begin{bmatrix} Is \end{bmatrix} + \begin{bmatrix} L_{1}g_{1} \\ L_{1}g_{1} \\ L_{1}g_{1} \end{bmatrix} \begin{bmatrix} is \end{bmatrix} \begin{bmatrix} is \\ -1 \\ -1 \\ 0 \\ -1 \\ \frac{1}{g_{1}} \end{bmatrix} \begin{bmatrix} is \\ -1 \\ 0 \\ \frac{1}{g_{1}} \end{bmatrix} \begin{bmatrix} v_{1} \\ v_{2} - v_{3} \\ \frac{v_{4} \\ v_{4} \\ \frac{v_{4}} \\ \frac{v_{4$$

constraint of floating capacitors. Then the excess voltage  $v_3$  is eliminated, resulting in (14d). Equation (14e) is obtained after relevant variables are removed. Note that, different from [19], our node-branch voltage transformation does not require the generation of normal tree, which can be prohibitive for large-scale circuit networks. The elimination procedure for floating capacitors is summarized in Algorithm 2. The complete flow of the regularization is demonstrated in Fig. 2.

## V. APPLICABILITY, COMPLEXITY, AND IMPLEMENTATION

#### A. Applicability

The proposed method is not a universal way out of the singular problem associated with MNA formulation in circuit simulation. By breaking *CV*-loops and *LI*-cutsets, one can cure most of the index-2 circuits, but not all of them. In active circuits with controlled sources, *CV*-loops and *LI*-cutsets may not be the only causes of index-2 systems; the complex actions of controlled sources and negative elements can also give rise to intricate dependence that leads to higher DAE indices.

Some such examples can be found in [6, p. 335]. In these cases the regularized matrix  $C_r$  will be singular after the first cycle, where a simple check of condition number can reveal the problem. Then another cycle of systematic elimination, if affordable, can be carried out to eliminate more variables. Designers can also return to check whether the circuit has been designed as desired. To the authors' knowledge, no practical approach has been reported in literatures to regularize index-2 circuits with millions of variables, and with the high DAE index arising from controlled sources.

On the other hand, the proposed method is effective for the circuits where *CV*-loops and *L1*-cutsets are the only causes of index-2 DAEs, e.g., RLCM networks. Notice that in [20] Tischendorf remarks that the networks containing voltage controlled current sources, which is a vital component in common linearized models of nonlinear devices, also belong to this category provided a mild constraint is satisfied. This implies that our regularization approach is also applicable to nonlinear circuit simulation with common device models. Note that the current regularization technique is applicable

## Algorithm 2: Elimination procedure of floating capacitors

| Algorithm 2. Eminiation procedure of noating capacitors         |

|-----------------------------------------------------------------|

| <b>Input</b> : matrices C, G, $B_0$ , $B_1$                     |

| Identify all floating capacitors via topology analysis;         |

| For each group of floating capacitors, add up all rows in       |

| G corresponding to the nodes;                                   |

| <b>if</b> At least one node voltage (e.g., $v_1$ ) with nonzero |

| pivoting in <b>G</b> after the summation <b>then</b>            |

| Eliminate $v_1$ from C and G;                                   |

| else                                                            |

| Eliminate $v_1$ using the BCE of the current branch             |

| (except the $v_1$ row itself);                                  |

| Apply node-branch transformation, leading to empty              |

|                                                                 |

row in **C** and nonempty row in **G**; Eliminate  $v_n$  from **G**;

#### end

Remove corresponding rows and columns from the MNA equations.

TABLE I SPECIFICATIONS OF TEST CASES

| Design | Function    | Туре | Nodes | Nodes w/o Cap | Index |

|--------|-------------|------|-------|---------------|-------|

| D1     | Trans. line | L    | 5.6K  | 431           | 2     |

| D2     | Power grid  | L    | 1.6M  | 0.6M          | 2     |

| D3     | Power amp.  | NL   | 342   | 105           | 2     |

| D4     | ALU         | NL   | 10K   | 373           | 1     |

for standard MNA formulation only. Extension to charge/flux MNA will be a topic of future work.

## B. Complexity and Implementation Issues

The computational cost of the regularization can be divided into two parts: the cost of topology analysis and the cost of algebraic transformation. The complexity of the two main graph theory algorithms, finding minimal spanning tree and searching for connected components, are  $O(N_g)$  and  $O(N_g log(N_g))$ , respectively [21], where  $N_g$  refers to the number of "nodes" in the corresponding graphs. Since these algorithms work on reduced graphs,  $N_g$  is usually much smaller than the number of MNA variables, e.g., a subcircuit consisting of only capacitors or resistors, regardless of its real size, will be seen as one node in the graph to find L1-cutsets. Therefore, the CPU time devoted to the topology analysis part is insignificant. The algebraic transformation includes the rowwise eliminations and the LU decomposition of  $[G_{21} G_{22}]$  in the systematic elimination stage, of which costs are generally topology-dependent. The expense in row-wise eliminations rests with the number of voltage sources, LI-cutsets and floating capacitors in a topology. In our experiments, the number of these "trouble makers" is usually less than 0.1% for million-scale designs. The cost of factorizing  $[G_{21} G_{22}]$ depends on the number of nodes in absence of capacitances. A circuit having many nodes without capacitances (which is uncommon) will require a longer processing time. Note that the reduction of  $[G_{21} G_{22}]$  to the row echelon form does not affect the sparsity of **C**.

For linear networks, the regularization procedure is implemented as a one-time preprocessing step. Owing to its reduc-

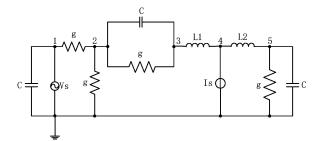

Fig. 3. Schematic of a simple circuit example.

tion nature, the expense of regularization can be amortized by the saving of solving a smaller system in each time step during the subsequent transient simulation. This is in contrast to the expansion nature of [15] wherein the later time integration is carried out with an augmented system.

For nonlinear circuits, the regularization may have to be repeated whenever the (linearized) MNA matrices are modified by the nonlinear device evaluation. A positive side is that the device evaluation does not alter the topology after linearization, which is fixed in the first place when the device models are chosen. Hence, the topology analysis can remain as a one-time preprocessing. The row-wise GE can also be made symbolic as in (8f) to enable a fast computation. What has to be repeated then boils down to the processing of (4)–(7), essentially several sparse block GEs. Again, this part of cost should not be "sneered at" purely as an extra cost; it is actually proportional to the saving one can benefit later from solving a smaller system in downstream simulations.

To ensure a right implementation, a proper design of error checking and exception handling is necessary. For instance, "nonzero pivoting" assertions (or "zero pivoting" if no fill-ins should be generated) can be used to guarantee the validity of every row-wise elimination. Condition number checking can be applied before matrix inverse or linear solve. This way, one can guarantee the correctness in the regularization process (no erroneous systems will be generated), even though it may not stop in one cycle. Again, instead of a universal algorithm that covers all possible situations, the aim of this paper is to provide a framework of regularization with sufficient flexibility that allows users to design their own codes with different coverage according to their needs, which span from analysis of specific types of circuits (power-ground networks, and so on) to general-purpose circuit simulation.

## VI. EXPERIMENTAL RESULTS

We prototype the regularization technique in MATLAB and integrate the codes into a SPICE-like circuit simulator SMORES developed in MIT [22]. Experiments are carried out on a server with Intel Xeon 3.0 GHz CPU and 16 GB memory.

## A. Simple Example

Fig. 3 shows a simple index-2 circuit. The MNA formulation is given in (15a) (for simplicity we assume uniform values of g = 1, C = 1, and L = 1.5). The **C** matrix is singular because of: 1) the fourth and the last zero rows; and 2) the linear dependence between the second and third rows.

TABLE II TOPOLOGY ANALYSIS RESULTS AND PERFORMANCE OF REGULARIZATION (TIME UNIT: SECOND)

| Case | Vs | LI  | FC | $cond(\mathbf{C}_r)$ | nnz(C + G) | $nnz(\mathbf{C}_r + \mathbf{G}_r)$ | t <sub>TP</sub> | t <sub>GE</sub> | $t_{\rm SE}$ | t <sub>All</sub> |

|------|----|-----|----|----------------------|------------|------------------------------------|-----------------|-----------------|--------------|------------------|

| D1   | 18 | 3   | 1  | $1.1 \times 10^{7}$  | 0.9M       | 0.9M                               | 0.3             | 0.5             | 5.1          | 5.9              |

| D2   | 0  | 181 | 0  | $1.4 \times 10^{6}$  | 5.4M       | 4.8M                               | 46.8            | 144.4           | 8.9          | 191.2            |

| D3   | 2  | 0   | 0  | $2.4 \times 10^{3}$  | 2.2K       | 2.1K                               | 0.02            | 0.02            | 0.01         | 0.05             |

| D4   | 11 | 0   | 0  | $4.4 \times 10^{5}$  | 44K        | 43K                                | 0.24            | 0.91            | 0.02         | 1.2              |

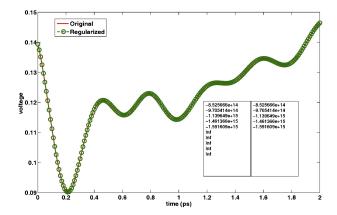

Fig. 4. Accuracy of regularization process.

The topological index reduction eliminates  $v_1$  and  $i_V$  to break the *CV*-loop, and  $v_4$  and  $i_{L1}$  to break the *LI*-cutset, resulting in an index-1 DAE (15b). The final equation after the floating capacitor removal, systematic elimination and variable transformation is given in (15c). Note that the variables are different from those in (15b) due to the variable transformation.

## B. Practical Examples

The regularization technique is also tested with a set of large designs. Table I details the functionality, type (linear and nonlinear), size (up to 1.6M nodes), DAE index of MNA system and the number of nodes without capacitances of the benchmark circuits.

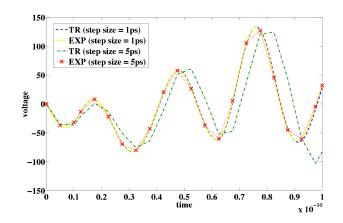

Fig. 5. Transient simulation results of EXP and TR methods with different step sizes.

First, the transient response (by trapezoidal method) of D1 before and after the regularization are compared in Fig. 4. Since no approximation is introduced, the regularization maintains the accuracy quite well (the relative mismatch between the two curves is  $4.3 \times 10^{-11}$ ). The five largest (in magnitude) generalized eigenvalues of the matrix pencils (-G, C) and ( $-G_r, C_r$ ) are also shown in Fig. 4. The five INF eigenvalues are removed by the regularization and the remaining normal eigenvalues are preserved, which guarantees the exact equivalence between the original and regularized systems.

Table II lists the primary data of interest for regularization. With the tested cases, several observations can be made: 1) the number of "troublemaker" elements to be eliminated before

$$\begin{bmatrix} z & z & z & z & 0 \\ z & z & z & z & 0 \\ z & z & z & z & 0 \\ z & z & z & z & 0 \\ \hline z & z & z & z & 0 \\ \hline z & z & z & z & 0 \\ \hline 1 & -1 & -K & K & 0 \end{bmatrix} \begin{bmatrix} v_j \\ v_k \\ v_l \\ v_m \\ \hline i_v \end{bmatrix} + \begin{bmatrix} z \\ z \\ z \\ \hline 0 \end{bmatrix} [u] + \begin{bmatrix} z \\ z \\ z \\ \hline 0 \end{bmatrix} [\dot{u}]$$

(16a)

$$\begin{aligned} z & z & z & z & 0 \\ \mathbf{z}_{1} & \mathbf{z}_{1} & \mathbf{z}_{1} & 0 \\ z & z & z & z & 0 \\ \frac{z}{0} & 0 & 0 & 0 & 0 \end{aligned} \end{bmatrix} \begin{bmatrix} \dot{v}_{j} \\ \dot{v}_{k} \\ \dot{v}_{l} \\ \frac{\dot{v}_{m}}{i_{v}} \end{bmatrix} = -\begin{bmatrix} z & z & z & z & -1 \\ \mathbf{z}_{1} & \mathbf{z}_{1} & \mathbf{z}_{1} & \mathbf{z}_{1} \\ z \\ z & z & z & z & 0 \\ \frac{z}{1} & -1 & -K & K & 0 \end{bmatrix} \begin{bmatrix} v_{j} \\ v_{k} \\ v_{l} \\ \frac{v_{m}}{i_{v}} \end{bmatrix} + \begin{bmatrix} z \\ \mathbf{z}_{1} \\ z \\ 0 \end{bmatrix} \begin{bmatrix} u \end{bmatrix} + \begin{bmatrix} z \\ \mathbf{z}_{1} \\ z \\ \frac{z}{0} \end{bmatrix} \begin{bmatrix} \dot{u} \end{bmatrix}$$

(16b)

$$\begin{bmatrix} z & z & z & z & 0 \\ z_1 & z_1 & z_1 & 0 \\ z & z & z & z & 0 \\ \hline v_{i} \\ v_{i} \\ \hline v_{i}$$

$$\begin{bmatrix} z & z & z & z & 0 \\ \mathbf{0} & \mathbf{z_3} & \mathbf{z_3} & \mathbf{z_3} & 0 \\ \mathbf{0} & \mathbf{z_3} & \mathbf{z_3} & \mathbf{z_3} & 0 \\ \mathbf{1} - \mathbf{1} - K & K & 0 \end{bmatrix} \begin{bmatrix} \dot{v}_j \\ \dot{v}_k \\ \dot{v}_l \\ \dot{v}_m \\ \dot{i}_v \end{bmatrix} = -\begin{bmatrix} z & z & z & z & -1 \\ 0 & z_2 & z_2 & z_2 & 0 \\ 0 & z_2 & z_2 & z_2 & 0 \\ 0 & 0 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} v_j \\ v_k \\ v_l \\ \dot{v}_m \\ \dot{i}_v \end{bmatrix} + \begin{bmatrix} z \\ z_1 \\ z \\ 0 \end{bmatrix} \begin{bmatrix} u \end{bmatrix} + \begin{bmatrix} z \\ z_1 \\ z \\ 0 \end{bmatrix} \begin{bmatrix} \dot{u} \end{bmatrix}$$

(16d)

$$\begin{bmatrix} z_3 & z_3 & z_3 \\ z_3 & z_3 & z_3 \\ z_3 & z_3 & z_3 \end{bmatrix} \begin{bmatrix} \dot{v}_k \\ \dot{v}_l \\ \dot{v}_m \end{bmatrix} = -\begin{bmatrix} z_2 & z_2 & z_2 \\ z_2 & z_2 & z_2 \\ z_2 & z_2 & z_2 \end{bmatrix} \begin{bmatrix} v_k \\ v_l \\ v_m \end{bmatrix} + \begin{bmatrix} z_1 \\ z \\ z \end{bmatrix} [u] + \begin{bmatrix} z_1 \\ z \\ z \end{bmatrix} [\dot{u}]$$

(16e)

$$\begin{bmatrix} z & z & 0 & 0 \\ z & z & 0 & z \end{bmatrix} \begin{bmatrix} v_j \\ \dot{v}_k \\ \dot{v}_l \\ \dot{v}_m \\ \dot{i}_v \\ z & z & z \end{bmatrix} = - \begin{bmatrix} z & z & z & z & -1 & 0 \\ z & z & z & z & z & 1 & 0 \\ z & z & z & z & z & 0 & -1 \\ z & z & z & z & 0 & -1 \\ \hline 1 & -1 & 0 & 0 & 0 & -K \\ 0 & 0 & z & z & 0 & z \end{bmatrix} \begin{bmatrix} v_j \\ v_k \\ v_l \\ v_m \\ \dot{i}_v \\ \dot{i}_c \end{bmatrix} + \begin{bmatrix} z \\ z \\ z \\ 0 \\ z \end{bmatrix} \begin{bmatrix} u \end{bmatrix} + \begin{bmatrix} z \\ z \\ z \\ 0 \\ 0 \end{bmatrix} \begin{bmatrix} \dot{u} \end{bmatrix}$$

(17a)

$$\begin{bmatrix} z_{3} & z_{1} & z_{3} \\ z_{3} & z_{2} & z_{3} \\ z_{3} & z_{2} & z_{3} \\ \hline z_{3} & z_{2} & z_{3} \\ \hline z_{2} & z_{2} & z_{2} \\ \hline z_{2} & z_{2} & z_{2} \\ \hline 0 & z_{2} & z_{2} \\ \hline 0 & z_{2} & z_{2} \\ \hline z_{2} & z_{2} & z_{2} \\ \hline$$

systematic elimination is only a negligible percentage (<0.5%) of the total number of variables; 2) the regularized matrix  $C_r$  is invertible with a reasonable condition number; 3) the matrix sparsity is not much affected by the regularization (the numbers of nonzeros stay roughly the same); and 4) in terms of CPU time, the cost of topology analysis ( $t_{TP}$ ) depends on the sizes of MNA matrices. The expense in row-wise GE ( $t_{GE}$ ) rests with the number of topological elements to be eliminated. The time spent on systematic elimination ( $t_{SE}$ ) depends on the number of nodes in absence of capacitances. Overall, these results confirm the proposed regularization process can address the singular **C** problem for large-scale designs within a reasonable time (e.g., 191.2 s for the 1.6M case).

$\begin{array}{ccc}z & z \\ z & z \\ z & z \\ \hline 0 & 0 \\ 0 & 0 \end{array}$

## C. Application in Explicit Method

To show the application of the proposed regularization technique, we apply a recently developed explicit method, matrix exponential method (EXP) [5], to simulate the 1.6M case (D2). The EXP method requires the matrix-vector product of  $\mathbf{C}^{-1}(\mathbf{G}\mathbf{v})$ , which is not possible without the application of

TABLE III CPU TIMES OF TR AND EXP METHODS FOR D3 (TIME SPAN = 100 PS, UNIT: SECOND)

| Step Size | TR     | EXP    |

|-----------|--------|--------|

| 1 ps      | 2907.1 | 1190.2 |

| 5 ps      | 853.2  | 233.8  |

regularization. The transient responses calculated by the EXP method and the implicit trapezoidal method (TR) are compared in Fig. 5. It shows that the EXP method can use large step sizes while maintaining a good accuracy. The performance data of the two methods in Table III show that the explicit EXP method is  $12 \times$  faster than the implicit TR method [note that EXP(5 ps) has a comparable accuracy with TR(1 ps)].

## VII. CONCLUSION

We proposed a two-stage regularization technique to address the singular matrix problem commonly encountered in explicit numerical integration methods. Combining topological index reduction and systematic elimination, our method is able to regularize large-scale circuit networks with a reasonable efficiency, and maintain the sparsity of the resultant matrices. Numerical experiments have confirmed the accuracy and performance of the proposed technique with examples featuring up to 1.6 million nodes.

## ACKNOWLEDGMENT

The reviewers' comments that led to significant improvement for the paper are highly appreciated.

#### APPENDIX

The MNA stamp of a VCVS, with the BCE of  $v_j - v_k = K(v_l - v_m)$ , is shown in (16a). Entries *z* can have arbitrary values and the subscript indicates the step where the entry is updated. Suppose  $v_j$  and  $i_v$  are selected for elimination. In (16b), the dependence of  $i_v$  is first removed from row *k* in **G** using the row of  $v_j$ . We eliminate  $v_j$  and  $\dot{v}_j$  in (16c) and (16d), respectively, using the algebraic and differential BCE. After removing relevant rows and columns, we obtain (16e).

The MNA stamp of a CCVS with the BCE of  $v_j - v_k = Ki_c$ is shown in (17a). Two current variables are introduced and only the current of (controlled) voltage source  $i_v$  is eliminated. The elimination procedure is similar to that of VCVS. The reduced stamp is shown in (17b).

#### REFERENCES

- L. Nagel, SPICE2: A Computer Program to Simulate Semiconductor Circuits. Berkeley, CA: Univ. California, May 1975.

- [2] A. Devgan and R. A. Rohrer, "Event driven adaptively controlled explicit simulation of integrated circuits," in *Proc. ICCAD*, 1993, pp. 136–140.

- [3] W. Dong and P. Li, "Parallelizable stable explicit numerical integration for efficient circuit simulation," in *Proc. DAC*, 2009, pp. 382–385.

- [4] S. H. Weng, P. Du, and C. K. Cheng, "A fast and stable explicit integration method by matrix exponential operator for large scale circuit simulation," in *Proc. ISCAS*, 2011, pp. 321–327.

[5] S. H. Weng, Q. Chen, and C. K. Cheng, "Time-domain analysis of large-

- [5] S. H. Weng, Q. Chen, and C. K. Cheng, "Time-domain analysis of largescale circuits by matrix exponential method with adaptive control," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, to be published.

- [6] L. O. Chua and P. M. Lin, Computer-Aided Analysis of Electronic Circuits. Englewood Cliffs, NJ: Prentice-Hall, 1975.

- [7] A. Varga, "A descriptor systems toolbox for MATLAB," in *Proc. CACSD Symp.*, 2000, pp. 150–155.

- [8] P. Miettinen, M. Honkala, J. Roos, and M. Valtonen, "Improving modelorder reduction methods by singularity exclusion," in *Proc. SCEE Book Abstracts*, 2010, pp. 137–138.

- [9] Q. Su, V. Balakrishnan, and C.-K. Koh, "Efficient approximate balanced truncation of general large-scale RLC systems via Krylov methods," in *Proc. ASP-DAC*, 2002, pp. 311–316.

- [10] S. Natarajan, "A systematic method for obtaining state equations using MNA," *IEE Proc. G Circuits Devices Syst.*, vol. 138, no. 3, pp. 341–346, Jun. 1991.

- [11] G. W. Stewart, *Matrix Algorithms: Basic Decompositions*. Philadelphia, PA: SIAM, 1998, p. 185.

- [12] D. E. Schwarz and C. Tischendorf, "Structural analysis for electric circuits and consequences for MNA," *Int. J. Circuits Theor. Appl.*, vol. 28, no. 2, pp. 131–162, Mar. 2000.

- [13] Z. Zhang and N. Wong, "An efficient projector-based passivity test for descriptor systems," *IEEE Trans. Comput.-Aided Des.*, vol. 29, no. 8, pp. 1203–1214, Aug. 2010.

- [14] T. Reis and T. Stykel, "PABTEC: Passivity-preserving balanced truncation for electrical circuits," *IEEE Trans. Comput.-Aided Des.*, vol. 29, no. 9, pp. 1354–1367, Sep. 2010.

- [15] S. Bächle and F. Ebert, "Element-based topological index reduction for differential-algebraic equations in circuit simulation," Inst. Math., TU Berlin, Berlin, Germany, Tech. Rep. 05-246, 2005.

- [16] S. Bächle and F. Ebert, "Graph theoretical algorithms for index reduction in circuit simulation," Inst. Math., TU Berlin, Berlin, Germany, Tech. Rep. 05-245, 2005.

- [17] S. Bächle and F. Ebert, "Index reduction by element-replacement for electrical circuits," SCEE, vol. 11, pp. 191–197, 2007.

- [18] M. Güther and U. Feldmann, "The DAE-index in electric circuit simulation," *Math. Comput. Simul.*, vol. 39, nos. 5–6, pp. 573–582, Nov. 1995.

- [19] L. Mandache, D. Topan, and I. G. Sirbu, "Improved modified nodal analysis of nonlinear analog circuits in the time domain," in *Proc. World Congr. Eng.*, 2010, pp. 905–908.

- [20] C. Tischendorf, "Topological index calculation of DAEs in circuit simulation," Surv. Math. Ind., vol. 8, nos. 3–4, pp. 187–199, 1999.

- [21] D. Joyner, M. V. Nguyen, and N. Cohen. (2012). Graph-Theory-Algorithms-Book [Online]. Available: http://code.google.com/p/ graph-theory-algorithms-book

- [22] B. N. Bond. (2010). SMORES: A MATLAB Tool for Simulation and Model Order Reduction of Electrical Systems [Online]. Available: http: //bnbond.com/software/smores

**Quan Chen** (S'09–M'11) received the B.S. degree in electrical engineering from Sun Yat-Sen University, Guangzhou, China, in 2005, and the M.Phil. and Ph.D. degrees in electronic engineering from the University of Hong Kong, Pokfulam, Hong Kong, in 2007 and 2010, respectively.

From 2010 to 2011, he was a Post-Doctoral Fellow with the Department of Computer Science and Engineering, University of California, San Diego. He is currently a Post-Doctoral Fellow with the Department of Electrical and Electronic Engineering,

University of Hong Kong. His current research interests include multiphysics and multiscale simulation, parallel computation in computer-aided design, and applied electromagnetics.

Shih-Hung Weng (S'10) received the B.S. and M.S. degrees from National Tsing Hua University, Hsinchu, Taiwan, in 2006 and 2008, respectively, both in computer science. He is currently pursuing the Ph.D. degree with the Department of Computer Science and Engineering, University of California, San Diego/La Jolla, under the supervision of Dr. C.-K. Cheng.

His current research interests include parallel circuit simulation, clock-gating optimization, and power-grid noise analysis in very large scale

integration systems.

**Chung-Kuan Cheng** (S'82–M'84–SM'95–F'00) received the B.S. and M.S. degrees in electrical engineering from National Taiwan University, Taipei, Taiwan, and the Ph.D. degree in electrical engineering and computer sciences from the University of California, Berkeley, in 1984.

From 1984 to 1986, he was a Senior CAD Engineer with Advanced Micro Devices, Inc., Sunnyvale, CA. In 1986, he joined the University of California, San Diego/La Jolla, where he is currently a Professor with the Department of Computer Science

and Engineering and an Adjunct Professor with the Department of Electrical and Computer Engineering. He was a Chief Scientist with Mentor Graphics, Wilsonville, OR, in 1999. His current research interests include medical modeling and analysis, network optimization, and design automation on microelectronic circuits.

Dr. Cheng was an Associate Editor of the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN from 1994 to 2003. He was a recipient of the Best Paper Awards, IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN in 1997and 2002, the NCR Excellence in Teaching Award, School of Engineering, UCSD, in 1991, the IBM Faculty Awards in 2004, 2006, and 2007. He was an Honorary Guest Professor of Tsinghua University from 2002 to 2008 and a Visiting Professor of National Taiwan University in 2011.