The HKU Scholars Hub The University of Hong Kong 香港大學學術庫

| Title       | Analysis and design of a high-voltage-gain hybrid switched-<br>capacitor buck converter     |

|-------------|---------------------------------------------------------------------------------------------|

| Author(s)   | Xiong, S; Tan, SC; Wong, SC                                                                 |

| Citation    | leee Transactions On Circuits And Systems I: Regular Papers, 2012, v. 59 n. 5, p. 1132-1141 |

| Issued Date | 2012                                                                                        |

| URL         | http://hdl.handle.net/10722/155756                                                          |

| Rights      | Creative Commons: Attribution 3.0 Hong Kong License                                         |

# Analysis and Design of a High-Voltage-Gain Hybrid Switched-Capacitor Buck Converter

Song Xiong, Siew-Chong Tan, Senior Member, IEEE, and Siu-Chung Wong, Senior Member, IEEE

Abstract—This paper presents an analysis on the effect of having different number of capacitors n in the first-stage switched-capacitor circuit of an improved hybrid switched-capacitor buck converter for high-voltage-gain conversion. Various aspects of the topology, operation, and efficiency are investigated. It is shown both analytically and experimentally that a higher n in the step-down capacitor stage does not necessarily lead to an overall improved power efficiency. A design and optimization method is thus proposed for the improved SC-buck converter.

*Index Terms*—High voltage gain converter, hybrid switch-capacitor buck converter.

## I. INTRODUCTION

**H** IGH-VOLTAGE-GAIN dc-dc converters are commonly used for electronic applications. To save energy, the supply voltage of modern electronics is decreased to an ultra-low voltage level of less than 1 V. Meanwhile, the intermediate dc supply voltage, especially that of renewable power sources [1], is at a relatively high level of above 12 V [2]–[6]. This prompts the power electronics community to investigate high-voltage-gain dc-dc converters which have a low-voltage output and a high bandwidth regulation.

At present, the electronic industry is still using simple and easy-to-control converters based on conventional buck converter topologies, for achieving such kind of voltage step-down conversions [2]–[5]. However, to achieve high-voltage-gain conversions, the buck converter has to be operated with a very small duty ratio ( $D = (V_{out})/(V_{in})$  being very small), which not only complicates its implementation due to the limits of the duty ratio and the switching frequency [6], but also deteriorates its dynamic performance and reduces its efficiency due to the very-short on time and very-long freewheeling time within the switching cycle [7]. For this kind of conversion, converters with transformers would be a better choice. However, this increases size and cost, which makes them less acceptable for applications that do not need isolation [6].

Digital Object Identifier 10.1109/TCSI.2012.2191313

Switched-capacitor (SC) dc-dc converters, which consist exclusively of power switches and capacitors, can efficiently perform high-voltage-gain conversion [6]–[8]. As there is no magnetic component in the topologies, they are suitable for integrated circuit (IC) implementation in microelectronic form. Besides, they also have advantages of small size, light weight, high efficiency and high power density [9]–[17]. These advantages make them useful in modern electronic products such as portable digital assistant, MP3 players, digital cameras, FLASH, and LED lighting applications [18], [19]. However, SC dc-dc converter cannot get a high efficiency if they are used for the purpose of voltage regulation, which limits their applications [9]–[20].

The limitations of the conventional converters have spurred the interests in developing a new kind of high-voltage-gain hybrid SC dc-dc converters [6]-[8], [21]-[25], of which the converter is made up of a first-stage SC converter, followed by a second-stage buck converter. For this two-stage SC-buck converter, the first-stage SC converter steps down the input voltage to a low level while the second-stage buck converter mainly performs the voltage regulation. An overall high efficiency is achievable with such two-stage hybrid SC-buck converter because the first-stage SC converter is used only for voltage transformation and not voltage regulation. As mentioned, for performing only voltage transformation, a very high efficiency SC converter is achievable. Industrial SC converter products of higher than 98% efficiency (e.g., LTC1044, MAX1044, SI7660, GS7660, etc.) is available. Once the input voltage is converted to a low unregulated voltage by the high efficiency SC converter, the second-stage buck converter will perform a small voltage transformation and the voltage regulation operation at a high efficiency. This is also possible because the input voltage to the buck converter is already at a low level making its duty ratio relatively normal. Recall that the reason why a single buck converter when used for high-voltage-gain conversion is lossy is because the buck converter has to do both the voltage conversion and regulation and that its duty ratio being the function of the input voltage and the output voltage, is very small.

Interestingly, while the concept of such converters have been widely reported [6], [7], [21]–[23], the effect of having different number of capacitors n in the first-stage switched-capacitor circuit has not being studied. In this paper, using an improved hybrid SC-buck converter as an illustrative example, we introduce a systematic way of modifying n for high-voltage-gain conversion that will result in an optimal way of designing and configuring such a hybrid SC-buck converter. Various aspects of the topology, operation, and efficiency will be discussed.

Manuscript received September 02, 2011; revised November 24, 2011; accepted February 15, 2012. Date of publication April 09, 2012; date of current version May 09, 2012. This work was supported by the Hong Kong Polytechnic University under Grant 4-ZZ7X. This paper was recommended by Associate Editor T.-J. Liang.

A version of this paper was presented at the 2011 IEEE Symposium on Circuits and Systems, (ISCAS), Rio de Janeiro, Brazil.

S. Xiong and S. C. Wong are with Department of Electronic and Information Engineering, The Hong Kong Polytechnic University, Kowloon, Hong Kong (E-mails: 09902718r@connect.polyu.hk, siewchong@ieee.org, and enscwong@polyu.edu.hk).

S. C. Tan is with Department of Electrical and Electronic Engineering, University of Hong Kong, Hong Kong (E-mails: siewchong@ieee.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

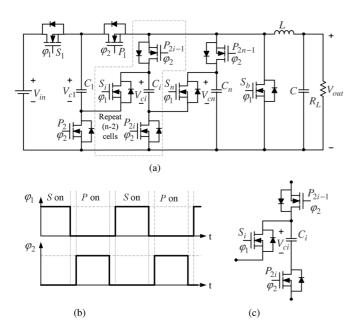

Fig. 1. Overview of the modified SC-buck converter. (a) Topology. (b) Timing diagram. (c) Single cell.

This paper is organized as follows. Section II shows the modified topology of the SC-buck converter and its working principle. Section III gives an analysis on the efficiency of the converter using an energy-flow approach. Section IV describes the control mechanism of the SC-buck converter. Section V shows the experimental results of the modified circuit. Section VI gives a guideline on the design of the SC-buck converter. Section VII gives the conclusions to this paper.

## II. HYBRID SWITCHED-CAPACITOR BUCK CONVERTER

A modified version of the hybrid SC-buck converter that was originally reported in [24] is illustrated in this paper. Using the proposed hybrid SC-buck converter with n flying capacitors (hereon known only as SC-buck converter), the effect of having a different step-down conversion ratio in the first-stage SC converter on the SC-buck converter is theoretically investigated in this section and experimentally verified in Section V. Some insights to the design of the converter can be obtained from this analysis.

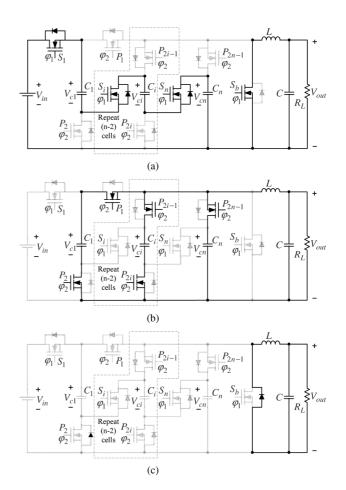

Fig. 1 shows the SC-buck converter and its timing diagram. Fig. 2 shows its three operating states.

In State 1, all S switches are "ON" and all P switches are "OFF."  $V_{in}$  charges the flying capacitors  $C_1, C_2, \ldots, C_n$ , which are connected in series as illustrated in Fig. 2(a). Concurrently, the buck stage of the converter is in freewheeling mode, of which the current in L freewheels through  $S_b$ .

In State 2, all S switches are "OFF" and all P switches are "ON." All the flying capacitors are connected in parallel and discharge to the buck stage of the converter as shown in Fig. 2(b).

In State 3, all switches are "OFF" as indicated in Fig. 2(c). Flying capacitors are neither charging nor discharging. The current in L freewheels through the body diode of  $S_b$ .

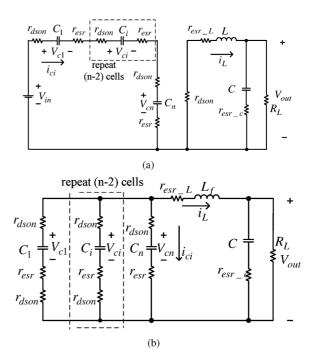

The equivalent circuits of State 1 and State 2 shown in Fig. 3 can be illustrated as given in Fig. 3(a) and (b), respectively, where  $r_{\rm dson}$  is the turn-on resistance of the switch,  $r_{\rm esr}$  is the

Fig. 2. Operating states of the modified SC-buck converter. (a) State 1. (b) State 2. (c) State 3.

Fig. 3. Equivalent circuit of the converter. (a) State 1: Charging equivalent circuit. (b) State 2: Discharging equivalent circuit.

resistance of each flying capacitor,  $r_{esr_C}$  is the resistance of the output capacitor C, and  $r_{esr_L}$  is the resistance of L.

92 buck 91 2-stage 3-stage 90 4-stage 89 88 87 Efficiency (%) 86 85 84 83 82 81 80 79 78 'n 3 4 5 6 8 9 10 11 12 13 14 15 Output power (W)

Fig. 4. Comparison of experimentally measured efficiencies among SC-buck converters with n = 2, 3, 4 and a buck converter (i.e., n = 1).

TABLE I

Parameters of SC-Buck Converter

| V <sub>in</sub> & V <sub>out</sub> | $f_S$        | MOSFET    |

|------------------------------------|--------------|-----------|

| 12 V & 1 V                         | 200 kHz      | Si7356ADP |

| $C_1, C_2 \cdots C_n$              | L            | C         |

| 94 μF                              | $13 \ \mu H$ | 410 µF    |

A prototype based on the SC-buck topology (n = 2, 3, 4)given in Fig. 1(a) and parameters given Table I is constructed. The number n can be modified by connecting or bypassing the single-cell structure depicted in Fig. 1(c). Experiment is performed to compare the performance of this converter against a conventional buck converter. Both the buck converters have the same C and  $f_S$ . Operating at the same 12 V input and 1 V output condition, it can be seen from Fig. 4 that the SC-buck converters gives a better efficiency than the conventional buck converter, except when it is at very light-load condition, similar to what has been reported in [7] and [22]. From Fig. 4, it is observed that a higher n of SC-buck converter always give a better efficiency at heavy load. However, depending on the loading condition, there is an optimal n that allows the SC-buck converter to achieve the best possible efficiency. In the next section, the efficiency of the SC-buck converter will be studied.

### **III. EFFICIENCY ANALYSIS**

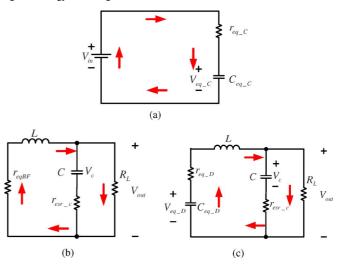

From Fig. 2, the energy-flow mechanism of the SC-buck converter can be seen as having two parts as depicted in Fig. 5. First, in State 1, energy is transferred from the power source  $V_{in}$  to the flying capacitors through the SC-stage with a "charging efficiency" of  $\eta_C$ . In this state, energy is temporarily stored in the flying capacitors. Then, in State 2, the energy stored in the capacitors will be transferred to the load through the buck-stage with a "discharging efficiency" of  $\eta_D$ . Averaged over a switching period, the energy in the flying capacitors is kept constant during steady state. The overall efficiency of SC-buck converter is the product of the charging efficiency and the discharging efficiency, i.e.,  $\eta_{overall} = \eta_C \cdot \eta_D$ .

The circuit in Fig. 3(a) can be further simplified into equivalent circuits representing the charging, discharging and free-

|        | charging     |           | discharging |      |

|--------|--------------|-----------|-------------|------|

| Power  | SC-stage     | Flying    | buck-stage  | Load |

| source | $\eta_{C}$ ' | capacitor | $\eta_D$ '  | LUau |

Fig. 5. Energy-flow diagram of a SC-buck converter.

Fig. 6. Simplified equivalent circuits of the charging, discharging and freewheeling operations of the SC-buck converter. (a) Charging operation. (b) Freewheeling operation. (c) Discharging operation.

wheeling operations as given in Fig. 6(a)–(c), respectively. For Fig. 6(a),  $C_{eq\_C} = C_1/n = C_{sum}/n^2$  and  $r_{eq\_C} = n \cdot (r_{dson} + r_{esr})$ . For Fig. 6(b),  $r_{eqBF} = r_{dson} + r_{esr\_L}$ . For Fig. 6(c),  $C_{eq\_D} = n \cdot C_1 = C_{sum}/n$  and  $r_{eq\_C} = (r_{dson} + r_{esr})/n$ . Here,  $C_{sum} = C_1 + \cdots + C_n$ .

## A. Charging Efficiency $\eta_C$

The charging efficiency  $\eta_C$  given in the energy-flow diagram in Fig. 5 can be obtained by analyzing the RC circuit given in Fig. 6(a). In this state, the energy stored in the flying capacitors will be transferred to the buck stage in the following state. The energy change would have an influence on the charging efficiency. The key point of calculating charging efficiency is to obtain the initial voltage of the flying capacitors. The method of deriving the charging efficiency of an equivalent RC circuit of an SC converter is given in [8]. Here, we apply the method to this converter.

First, the voltage across  $C_{eq_{C}}$  is

$$V_{\text{eq}\_C}(t) = V_{\text{in}} \left[ 1 - (1 - b)e^{-\frac{t}{\tau}} \right],$$

(1)

where  $b = V_{eq\_C(i)}/V_{in}$ ,  $\tau = r_{eq\_C}C_{eq\_C}$ , and that  $V_{eq\_C(i)}$  is the initial voltage of the equivalent flying capacitor. The total energy stored in  $C_{eq\_C}$  in each switching period is

$$\Delta E_C(t) = \frac{1}{2} C_{\text{eq\_C}} \left( V_{\text{eq\_C}}^2(t) - V_{\text{eq\_C}(i)}^2 \right).$$

(2)

This stored energy will be discharged into the buck stage. We denote  $\Delta E_T$  as the energy consumed by the buck stage in one period. Therefore,  $\Delta E_C(T_{\rm on}) = \Delta E_T$ .

Assume the input power of the buck stage of the SC-buck converter is  $P_{\rm bin}$ . In one switching period, the input energy is

$$\Delta E_T = P_{\rm bin} T = P_{\rm bin} / f_S. \tag{3}$$

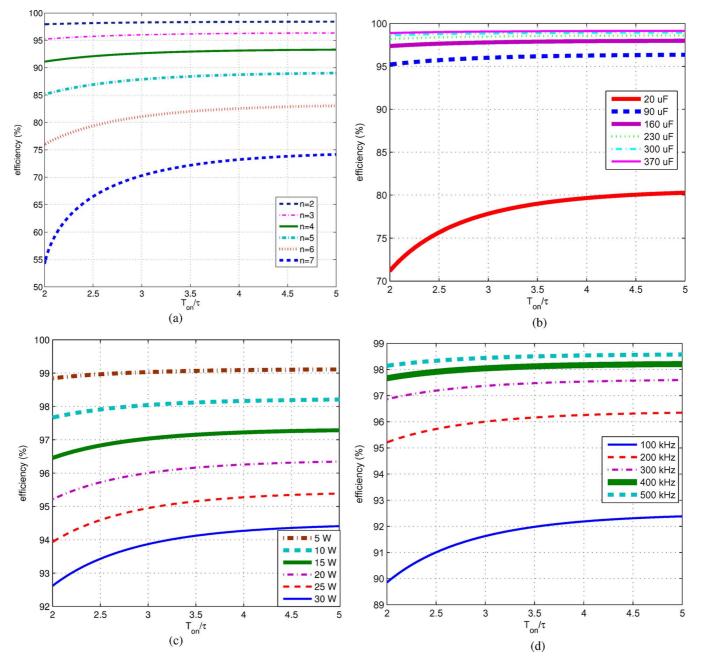

Fig. 7. Properties of SC-stage charging efficiency. (a) Plot of calculated charging efficiency for different  $n_{\cdot}$  (b) Plot of calculated charging efficiency for different  $C_{sum}$ . (c) Plot of calculated charging efficiency for different  $P_{bin}$ . (d) Plot of calculated charging efficiency for different switching frequency  $f_s$ .

At steady state, for each period, the energy stored in  $C_{\rm eq\_C}$  is equal to this input energy, i.e.,  $\Delta E_C(T_{\rm on}) = \Delta E_T$ , giving

$$V_{\rm eq\_C}^2(T_{\rm on}) - V_{\rm eq\_C}^2(i) = \frac{2P_{\rm bin}}{f_S C_{\rm eq\_C}}.$$

(4)

By substituting (1) into (4) and solving the equation, the initial voltage can be derived as

$$b = \frac{1}{1 + e^{-\frac{T_{\text{on}}}{\tau}}} \times \left[ e^{-\frac{T_{\text{on}}}{\tau}} + \sqrt{1 - \frac{2P_{\text{bin}}\left(1 + e^{-\frac{T_{\text{on}}}{\tau}}\right)}{f_S C_{\text{eq\_C}} V_{\text{in}}^2 \left(1 - e^{-\frac{T_{\text{on}}}{\tau}}\right)}} \right].$$

(5)

By substituting  $V_{\text{eq}\_C(i)} = b \cdot V_{\text{in}}$  into the charging efficiency equation in [8] where  $\eta_C = (V_{\text{eq}\_C}(t) + V_{\text{eq}\_C(i)})/(2V_{\text{in}})$ , we get

$$\eta_C = \frac{(1+b) - (1-b)e^{-\frac{T_{\rm on}}{\tau}}}{2}.$$

(6)

Fig. 7(a) gives the charging efficiency plot obtained from (6) for different n of which the total capacitance is kept constant with  $C_{\text{sum}} = 90 \ \mu\text{F}$  at  $P_{\text{bin}} = 20 \ \text{W}$  and  $f_S = 200 \ \text{kHz}$ . Fig. 7(b) illustrates the charging efficiency for different values of  $C_{\text{sum}}$  at  $f_s = 200 \ \text{kHz}$ ,  $P_{\text{bin}} = 20 \ \text{W}$ , n = 3,  $V_{\text{in}} = 12 \ \text{V}$ , and  $V_o = 1 \ \text{V}$ . Fig. 7(c) shows the charging efficiency for different  $P_{\text{bin}}$  at  $f_s = 200 \ \text{kHz}$ ,  $C_{\text{sum}} = 90 \ \mu\text{F}$ , n = 3,  $V_{\text{in}} = 12 \ \text{V}$ , and  $V_o = 1 \ \text{V}$ . Fig. 7(d) shows the charging efficiency for different  $P_{\text{bin}}$  at  $f_s = 200 \ \text{kHz}$ ,  $C_{\text{sum}} = 90 \ \mu\text{F}$ , n = 3,  $V_{\text{in}} = 12 \ \text{V}$ , and  $V_o = 1 \ \text{V}$ . Fig. 7(d) shows the charging efficiency for different

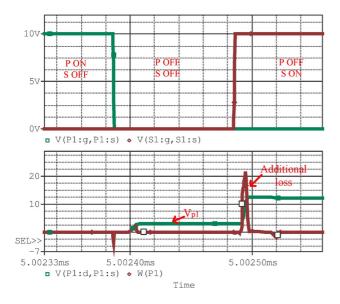

Fig. 8. Waveforms of P switches during the transition from State 3 to State 1.

switching frequency  $f_s$  with  $C_{sum} = 90 \ \mu\text{F}$ ,  $P_{bin} = 20 \ \text{W}$ , n = 3,  $V_{in} = 12 \ \text{V}$  and  $V_o = 1 \ \text{V}$ .

From the calculated results, the following conclusions can be deduced:

- 1) When the value of capacitor  $C_{sum}$  is fixed, having more flying capacitors gives a lower charging efficiency.

- 2) With a longer charging time  $T_{\rm on}$  in (6), the charging efficiency  $\eta_C$  is higher.

- 3) A bigger  $C_{sum}$  value leads to a higher charging efficiency. However, the rate of increase in charging efficiency decreases with an increasing  $C_{sum}$ .

- 4) A heavier load gives a lower charging efficiency.

- 5) A faster switching frequency leads to a higher charging efficiency.

## B. Discharging Efficiency $\eta_D$

The discharging efficiency of the SC-buck converter is mainly influenced the buck stage of the converter, of which it is being used to process and deliver energy from the flying capacitors to the output. Our study shows that the buck-stage efficiency of the SC-buck converter is dominantly the efficiency of a conventional buck converter plus an additional parasitic capacitor charging loss that is not present in the buck converter. The power loss of buck converter is well documented in many papers. It includes the conduction loss, switching loss, and the ESR loss. In the SC-buck converter, the power loss includes the following losses.

1) Conduction Loss:

i. Conduction loss on each branch's switches:

$$\begin{cases} P_{c\_sw\_up} = R_{dson} D\left(I_o^2 + \frac{\Delta I_L^2}{12}\right) & (upper switch) \\ P_{c\_sw\_dn} = R_{dson} D\left(I_o^2 + \frac{\Delta I_L^2}{12}\right) & (lower switch), \end{cases}$$

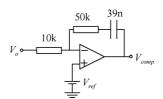

Fig. 9. Compensation circuit of the controller in the experimental prototype.

where  $I_o$  is the output current and  $\Delta I_L$  is the inductor current ripple.

ii. Conduction loss on the buck-stage switch:

$$P_{\text{c\_sw\_Sb}} = R_{\text{dson}} \left( 1 - D - \frac{2T_{\text{dt}}}{T} \right) \left( I_o^2 + \frac{\Delta I_L^2}{12} \right).$$

(8)

iii. Conduction loss on the body diode of buck-stage switch:

$$P_{\rm c\_diode\_Sb} = 2f_S V_{\rm fd} I_o T_{\rm dt}, \tag{9}$$

where  $V_{\rm fd}$  is the forward diode voltage of  $S_b$  and  $T_{\rm dt}$  is the dead time. Thus, the total conduction loss is

$$P_c = nP_{c\_sw\_up} + (n-1)P_{c\_sw\_up} + P_{c\_sw\_Sb} + P_{c\_diode\_Sb}.$$

(10)

- 2) Switching Loss:

- i. Switching loss on switches of each branch, which includes the switching loss on the upper switches:

$$\begin{cases} P_{\text{sw\_on\_up}} = f_S V_{\text{C\_on}} I_{\text{d\_on}} \frac{t_{ri} + t_{fu}}{2} \\ P_{\text{sw\_off\_up}} = f_S V_{\text{C\_off}} I_{\text{d\_off}} \frac{t_{ru} + t_{fi}}{2}, \end{cases}$$

(11)

and the switching loss on the lower switches:

$$\begin{cases} P_{\text{sw\_on\_dn}} = f_S V_{\text{C\_on}} I_{\text{d\_on}} \frac{t_{ri} + t_{fu}}{2} \\ P_{\text{sw\_onf\_dn}} = f_S V_{\text{fd}} I_{\text{d\_onf}} \frac{t_{ru} + t_{fi}}{2}, \end{cases}$$

(12)

where  $I_{d_on}$  and  $I_{d_off}$  are respectively the branch current of the capacitor when P is turned on and off.

ii. Switching loss of the body diode of buck-stage switch:

$$P_{\rm sw\_diode\_Sb} = f_S C_{\rm oss} V_{\rm inb\_on}^2, \tag{13}$$

where  $V_{\text{inb}on}$  is the voltage of flying capacitor when P is turned on. Thus, the total switching loss is

$$P_{sw} = n(P_{sw\_on\_up} + P_{sw\_off\_up}) + (n+1)$$

$$\times (P_{sw\_on\_dn} + P_{sw\_off\_dn}) + P_{sw\_diode\_Sb}.$$

(14)

3) ESR Loss:

(7)

i. Loss on the ESR of inductor:

$$P_{\text{esr}\_L} = r_{\text{esr}\_L} \left( I_o^2 + \frac{\Delta I_L^2}{12} \right). \tag{15}$$

ii. Loss on the ESR of a flying capacitor:

$$P_{\text{esr\_C}} = r_{\text{esr\_C}} D \left( I_o^2 + \frac{\Delta I_L^2}{12} \right).$$

(16)

Thus, the total ESR loss is

$$P_{\rm esr} = P_{\rm esr\_L} + nP_{\rm esr\_C}.$$

(17)

4) Parasitic Capacitor Charging Loss: When the SC-buck converter switches from State 3 to State 1, the voltage across all the P switches will change. This causes the parasitic capacitor of the P switches to charge up to a certain voltage level, generating an additional charging loss. Fig. 8 shows the simulation voltage and current waveforms of the SC-buck converter during the transition from State 3 to State 1, which introduces the additional power loss.

The equation describing the parasitic capacitor charging loss of each P switch is given as

$$\begin{cases} P_{ad\_up} = f_s C_{oss} V_{sw\_up}^2 \\ P_{ad\_dn} = f_s C_{oss} V_{sw\_dn}^2, \end{cases}$$

(18)

where  $V_{sw\_up}$  and  $V_{sw\_dn}$  are respectively the voltages of the upper and lower switches of each branch. For *n* number of *P* switches, the parasitic capacitor charging loss is

$$P_{\mathrm{ad}} = P_{\mathrm{ad\_up\_1}} + \dots + P_{\mathrm{ad\_up\_n}} + P_{\mathrm{ad\_dn\_1}} + \dots + P_{\mathrm{ad\_dn\_(n-1)}}.$$

(19)

Finally, the overall power loss of the buck-stage is

$$P_{\rm dis\_loss} = P_c + P_{\rm sw} + P_{\rm esr} + P_{\rm ad}.$$

(20)

Then, the discharging efficiency of the SC-buck converter is

$$\eta_D = \frac{P_o}{P_o + P_{\text{dis\_loss}}} \times 100\%.$$

(21)

### IV. CONTROL MECHANISM OF THE SC-BUCK CONVERTER

As the buck stage of the SC-buck converter is switching between the freewheeling and the discharging operation [see Fig. 6(b) and (c)], it behaves similarly to a simple duty-cycle controlled buck converter. Hence, only an ordinary voltage-mode controller will be needed for the control of the buck stage of the SC-buck converter. With this controller, the compensator can be designed using the pole placement approach. For this work, the adopted controller has a compensation network with the transfer function  $G_c(s) = 5 + (1)/(0.00039s)$ . Fig. 9 shows the implementation circuit of the compensation network used in the experimental prototype.

#### V. EXPERIMENTAL RESULTS

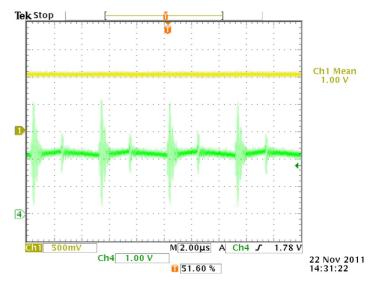

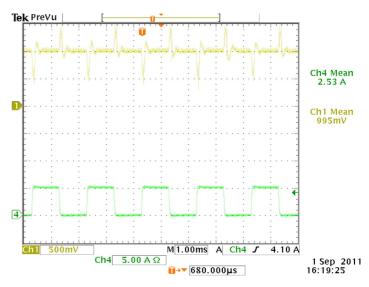

In order to verify the calculation method and the properties of the topology, a prototype has been built. The parameters are shown in Table I. Fig. 10 shows the output voltage waveform of a SC-buck converter with 5 flying capacitors (n = 5) under a constant load of 15 A. In comparison to the flying capacitor

Fig. 10. Output voltage waveform of a SC-buck converter with 5 flying capacitors (n = 5) (Ch1: buck output voltage; Ch4: SC flying capacitor voltage).

Fig. 11. Output voltage waveform of the proposed converter with closed-loop control with an active load switching between 0 A and 5 A (Ch1: Output voltage; Ch4: Output current).

voltage of the first-stage SC converter, the final output voltage waveform of the SC-buck converter contains a much smaller voltage ripple.

Fig. 11 depicts the closed-loop output voltage waveforms of the SC-buck converter operating with an active load switching between 0 A and 5 A, showing that ordinary voltage-mode control can be applied to the SC-buck converter with good result.

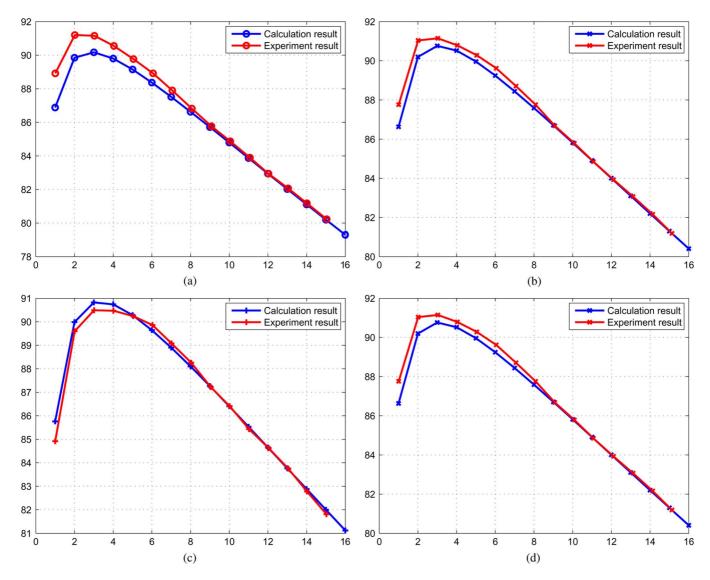

Fig. 12 gives a comparison of the calculated efficiencies and the experimental efficiencies at various output power levels and value of n. The efficiency curves fit well at higher power levels. The small discrepancy at lower power levels may be due to the relative higher measurement error at the lower power levels.

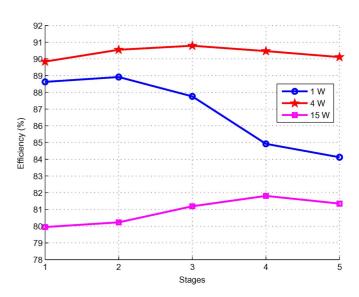

Fig. 13 gives the experimental efficiency curves at various output power levels using a different n. The results show that

Fig. 12. Plots of the experimentally measured efficiencies and calculated efficiencies for the SC-buck converter with (a) n = 2, (b) n = 3, (c) n = 4, and (d) n = 5.

there is a best n to achieve a highest efficiency at different loading conditions.

#### VI. CIRCUIT DESIGN AND OPTIMIZATION

Four parameters are needed to start a design: input voltage  $(V_{\rm in})$ , output voltage  $(V_o)$ , maximum output current  $(I_{o\_Max})$  and the switching frequency  $(f_s)$ . With these parameters, the component design of the converter circuit can be carried out based on the number of capacitor n chosen, as given in the following subsection.

## A. Components Selection

i. *Inductor:* Assuming that the switch of the buck is ideal, then

$$L = V_o \cdot \left(1 - \frac{V_o}{V_{\rm in}}\right) \cdot \frac{1}{f_s} \frac{1}{\Delta I_L}.$$

(22)

where  $\Delta I_L = p \cdot I_{o_{\text{Max}}}$ , and p is typically chosen as 0.3.

Fig. 13. Experimental result of the SC-buck converter for 1 W, 4 W, and 15 W loading with different n.

|               | $S_{off}P_{on}$ | $S_{off}P_{off}$ | $S_{on}P_{off}$                        | $S_{off}P_{off}$                       |

|---------------|-----------------|------------------|----------------------------------------|----------------------------------------|

| $V(P_1)$      | 0               | $V_{c1}$         | $V_{ m in}$                            | $V_{ m in}$                            |

| $V(P_3)$      | 0               | $V_{c2}$         | $V_{ m in} - V_{c1}$                   | $V_{\rm in} - V_{c1}$                  |

|               | 0               |                  |                                        |                                        |

| $V(P_{2n-1})$ | 0               | $V_{cn}$         | $V_{\rm in} - V_{c1} - \dots - V_{cn}$ | $V_{\rm in} - V_{c1} - \dots - V_{cn}$ |

| $V(P_2)$      | 0               | $V_D$            | $V_{c2} + \dots + V_{cn}$              | $V_{c2} + \dots + V_{cn}$              |

| $V(P_4)$      | 0               | $V_D$            | $V_{c3} + \dots + V_{cn}$              | $V_{c3} + \dots + V_{cn}$              |

|               | 0               | $V_D$            |                                        |                                        |

| $V(P_{2n})$   | 0               | $V_D$            | $V_{cn}$                               | $V_{cn}$                               |

TABLE II Voltages of Parallel Switches at Different States

ii. *Output capacitor:* The output capacitor dictates the ripple of output voltage. The output voltage ripple is

$$\Delta V_o = \Delta I_L \cdot (\text{ESR} + \Delta T/C_o). \tag{23}$$

Rearranging (23), we have

$$C_o = \frac{\Delta T}{\frac{\Delta V_o}{\Delta I_L} - \text{ESR}},$$

(24)

where  $\Delta T = \max\{(V_o)/(V_{in}) \cdot (1)/(f_s), (1 - (V_o)/(V_{in})) \cdot (1)/(f_s)\}$ , and ESR is the equivalent series resistance of output capacitor. Using (24), the value of the output capacitor is determined. Typically, the output voltage ripple is mainly contributed by the ESR of output capacitor.

iii. *Flying capacitor:* A proper value of the flying capacitor will improve the charging efficiency. Equation (5) gives the initial voltage b, which indicates the minimum voltage of the flying capacitors. Furthermore, it also dictates the charging efficiency. To obtain a high charging efficiency, b should be higher than 0.95. Although (5) can give an exact value of the flying capacitor, it is difficult to solve. A simplified version of this equation is desired. Assume the discharging efficiency is 100%. Then,

$$P_{o\_Max} = \frac{1}{2} f_s \cdot C_{sum} \cdot \left(\frac{V_{in}}{n} - \Delta V_f\right) \cdot \Delta V_f, \qquad (25)$$

where  $\Delta V_f$  is the voltage drop of flying capacitors. In (25),  $\Delta V_f$  is relatively low compared with  $(V_{in})/(n)$ . So, (25) can be simplified as

$$P_{o\_Max} = \frac{1}{2} f_s \cdot C_{sum} \cdot \frac{V_{in}}{n} \cdot \Delta V_f.$$

(26)

By rearranging (26) and setting  $\Delta V_f = (1-b) \cdot (V_{in}/(n))$ , the flying capacitor can be simplified as

$$C_{\text{sum}} = \frac{2 \cdot n^2 \cdot V_o \cdot I_{o\_\text{Max}}}{(1-b) \cdot f_s \cdot V_{\text{in}}^2}.$$

(27)

iv. Switch: Essentially, the maximum voltage and current ratings of the switches can be determined using a scaling function of n multiplied by  $V_{in}$  or  $I_o$ , as shown in Table IV. Most of the scaling functions are simple factors of n. However, the charging currents passing through the switches  $(S_1 \ldots S_n)$  are controlled by the circuit. The maximum current passing through these switches is

$$I_{\rm max} = \frac{\Delta V_f}{R_{\rm dson}}.$$

(28)

TABLE III Comparison of Different Stages SC-Buck Converter Components Used

| Stages            | Buck | 2-stage | 3-stage | <br><i>n</i> -stage |

|-------------------|------|---------|---------|---------------------|

| Switches          | 2    | 6       | 6       | <br>3n              |

| Flying capacitors | none | 2       | 3       | <br>n               |

| Inductor          | 1    | 1       | 1       | <br>1               |

| Output Capacitor  | 1    | 1       | 1       | <br>1               |

The parameter  $R_{\rm dson}$  not only affects the maximum charging current, but also dictates the time constant  $\tau$ , which affects the charging time. In order to have a high charging efficiency, the charging time should be at least three times higher than the time constant  $\tau$ . So,

$$R_{\rm dson} = \frac{n}{3} \cdot \frac{1}{C_{\rm sum}} \cdot \left(1 - \frac{n \cdot V_o}{V_{\rm in}}\right) \cdot \frac{1}{f_s}.$$

(29)

Substitute (29) into (28), the maximum current passing through the switches  $(S_1 \dots S_n)$  is given as

$$I_{\max} = \frac{3f_s C_{\text{sum}} \Delta V_f}{n \cdot \left(1 - \frac{n \cdot V_o}{V_{\text{in}}}\right)}.$$

(30)

#### B. Design and Optimization of the SC-Buck Converter

In the previous subsection, methods of selecting the components are introduced. Here, the design and optimization procedure will be given as follows.

- 1) Preset the four design specifications of input voltage  $(V_{in})$ , output voltage  $(V_o)$ , maximum output current  $(I_{o\_Max})$  and the switching frequency  $(f_s)$ .

- 2) The maximum number of stages  $n_{\text{max}} = \text{floor}(V_{\text{in}}/V_{\text{out}})$  is calculated.

- 3) For n = 2 to  $n_{\text{max}}$ , components are selected as illustrated in Section VI-A. A best efficiency of this n at a particular loading condition can be found as illustrated in Section III.

- Based on the results of different n's, an optimal n can be obtained.

#### VII. CONCLUSION

This paper presents an analysis on the effect of having different number of flying capacitors n in the first-stage SC circuit of an improved SC-buck converter for high-voltage-gain conversion. The analysis shows that a higher n in the SC stage with the same overall capacitance leads to a lower charging efficiency. On the other hand, the buck-stage efficiency is dependent on the operating conditions and design parameters. A higher n leads to a higher discharging efficiency. Since the overall efficiency is the multiplication of the charging efficiency and the discharging efficiency, there will be an optimal n in terms of efficiency for each switched-capacitor buck converter at a particular load. The experimental results confirms the analytical findings. As such, a design and optimization procedure is developed for the hybrid switched-capacitor buck converter for choosing the optimal n. It is also shown that the converter can easily be controlled using ordinary voltage-mode control for buck converter.

|                         | Stages            | 2-stage                                                                                                                                   | 3-stage                                                                                                                                                  |  | <i>n</i> -stage                                                                                                                                          |

|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Inductor          | $V_o \cdot (1 - \frac{2 \cdot V_o}{V_{in}}) \cdot \frac{1}{f_s} \cdot \frac{1}{\Delta I_L}$                                               | $V_o \cdot (1 - \frac{3 \cdot V_o}{V_{in}}) \cdot \frac{1}{f_s} \cdot \frac{1}{\Delta I_L}$                                                              |  | $V_o \cdot (1 - \frac{n \cdot V_o}{V_{in}}) \cdot \frac{1}{f_s} \cdot \frac{1}{\Delta I_L}$                                                              |

|                         | Output Capacitor  | $\frac{\max\{\frac{V_o}{V_{\rm in}}\cdot\frac{1}{f_s},(1-\frac{V_o}{V_{\rm in}})\cdot\frac{1}{f_s}\}}{\frac{\Delta V_o}{\Delta I_L}-ESR}$ | $\frac{\max\{\frac{V_o}{V_{\text{in}}} \cdot \frac{1}{f_s}, (1 - \frac{V_o}{V_{\text{in}}}) \cdot \frac{1}{f_s}\}}{\frac{\Delta V_o}{\Delta I_L} - ESR}$ |  | $\frac{\max\{\frac{V_o}{V_{\text{in}}} \cdot \frac{1}{f_s}, (1 - \frac{V_o}{V_{\text{in}}}) \cdot \frac{1}{f_s}\}}{\frac{\Delta V_o}{\Delta I_L} - ESR}$ |

|                         | Flying Capacitors | $rac{4 \cdot V_o \cdot I_o Max}{(1-b) \cdot f_s \cdot V_{ m in}^2}$                                                                      | $\frac{6 \cdot V_o \cdot I_{o-Max}}{(1-b) \cdot f_s \cdot V_{\rm in}^2}$                                                                                 |  | $\frac{2 \cdot n \cdot V_o \cdot I_{o-Max}}{(1-b) \cdot f_s \cdot V_{in}^2}$                                                                             |

| Switch $S_1$ :          | $V_{\max}$        | $rac{rac{1}{2}\cdot V_{	ext{in}}}{3f_sC_{sum}\Delta V_f}$                                                                               | $\frac{2}{3} \cdot V_{in}$                                                                                                                               |  | $\frac{n-1}{n} \cdot V_{\text{in}}$                                                                                                                      |

|                         | $I_{\max}$        | $2 \cdot \left(1 - \frac{2 \cdot V_o}{V_{\text{in}}}\right)$                                                                              | $\frac{f_s C_{sum} \Delta V_f}{(1 - \frac{3 \cdot V_o}{V_{in}})}$                                                                                        |  | $\frac{3f_s C_{sum} \Delta V_f}{n \cdot (1 - \frac{n \cdot V_o}{V_{in}})}$                                                                               |

| Switch $S_i$ ,          | $V_{\max}$        | $\frac{1}{2} \cdot V_{\text{in}}$                                                                                                         |                                                                                                                                                          |  | $rac{1}{2} \cdot V_{\mathrm{in}}$                                                                                                                       |

| $(i=2\cdots n).$        | $I_{\max}$        | $\frac{\frac{1}{2} \cdot V_{\text{in}}}{\frac{3f_s C_{sum} \Delta V_f}{2 \cdot (1 - \frac{2 \cdot V_o}{V_{\text{in}}})}}$                 | $\frac{\frac{1}{3} \cdot V_{\text{in}}}{\frac{f_s C_{sum} \Delta V_f}{(1 - \frac{3 \cdot V_o}{V_{\text{in}}})}}$                                         |  | $rac{3f_sC_{sum}\Delta V_f}{n\cdot(1-rac{n\cdot V_o}{V_{ m in}})}$                                                                                     |

| Switch $S_b$ :          | $V_{\max}$        | $\frac{1}{2} \cdot V_{ m in}$                                                                                                             | $\frac{1}{3} \cdot V_{in}$                                                                                                                               |  | $rac{1}{n} \cdot V_{ m in}$                                                                                                                             |

|                         | $i_{\max}$        | <sup>2</sup> I <sub>o</sub>                                                                                                               |                                                                                                                                                          |  | $I_o$                                                                                                                                                    |

| Switch $P_1$ :          | $V_{\max}$        | $V_{\rm in}$                                                                                                                              | $V_{\rm in}$                                                                                                                                             |  | $V_{\rm in}$                                                                                                                                             |

|                         | $I_{\max}$        | $\frac{1}{2} \cdot I_o$                                                                                                                   | $\frac{1}{3} \cdot I_o$                                                                                                                                  |  | $\frac{1}{n} \cdot I_o$                                                                                                                                  |

| Switch $P_{2i-1}$ ,     | $V_{\max}$        | $\frac{n-i+1}{2} \cdot V_{\text{in}}$                                                                                                     | $\frac{n-i+1}{3} \cdot V_{in}$                                                                                                                           |  | $\frac{n-i+1}{n} \cdot V_{\text{in}}$                                                                                                                    |

| $(i=2\cdots n).$        | $I_{\max}$        | $\frac{1}{2} \cdot I_o$                                                                                                                   | $\frac{1}{3} \cdot I_o$                                                                                                                                  |  | $\frac{n}{\frac{1}{n}} \cdot I_o$                                                                                                                        |

| Switch P <sub>2</sub> : | $V_{\max}$        | $\frac{1}{2} \cdot V_{\text{in}}$                                                                                                         | $\frac{2}{3} \cdot V_{in}$                                                                                                                               |  | $\frac{n-1}{n} \cdot V_{in}$                                                                                                                             |

|                         | $I_{\max}$        | $\frac{1}{2} \cdot I_{\alpha}$                                                                                                            | $\frac{1}{3} \cdot I_o$                                                                                                                                  |  | $\frac{1}{n}$                                                                                                                                            |

| Switch $P_{2i}$ ,       | $V_{\max}$        | $\frac{n-i}{2} \cdot V_{\text{in}}$                                                                                                       | $\frac{n-i}{3} \cdot V_{\in}$                                                                                                                            |  | $\frac{n-i}{n} \cdot V_{\text{in}}$                                                                                                                      |

| $(i=2\cdots n-1).$      | $I_{\max}$        | $\frac{\frac{n-i}{2} \cdot V_{\text{in}}}{\frac{1}{2} \cdot I_o}$                                                                         | $\frac{1}{3} \cdot I_o$                                                                                                                                  |  | $rac{n-i}{n}\cdot V_{\mathrm{in}} = rac{1}{n}\cdot I_o$                                                                                                |

TABLE IV Components' Parameters

#### REFERENCES

[1] [Online]. Available: http://www.itrs.net/Links/2005ITRS/ Home2005.htm

- [2] J. Wei, P. Xu, H. P. Wu, F. C. Lee, K. Yao, and M. Ye, "Comparison of three topology candidates for 12 V VRM," in *IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2001, pp. 245–251.

- [3] P. Xu, J. Wei, and F. C. Lee, "Multiphase coupled-buck converter—A novel high efficient 12 V voltage regulator module," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 74–82, Jan. 2003.

- [4] J. Agrawal, D. Kastha, and B. Culpepper, "An improved control scheme for multiphase buck converter circuits used in voltage regulator modules," in *Proc. IEEE Conf. Power Electron. Drives Syst.* (*PEDS*), Apr. 2006, pp. 418–423.

- [5] J. J. Sun, Y. Qiu, M. Xu, and F. C. Lee, "High-frequency dynamic current sharing analyses for multiphase buck VRs," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2424–2431, Nov. 2007.

- [6] R. Guo, Z. Liang, and A. Huang, "A multi-modes charge-pump based high efficiency wide input range DC-DC converter," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Sep. 2010, pp. 2706–2712.

- [7] M. Xu, J. Sun, and F. C. Lee, "Voltage divider and its application in the two-stage power architecture," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2006, vol. 2, pp. 499–505.

[8] C. K. Cheung, S. C. Tan, Y. M. Lai, and C. K. Tse, "A new visit to

- [8] C. K. Cheung, S. C. Tan, Y. M. Lai, and C. K. Tse, "A new visit to an old problem in switched-capacitor converters," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2010, pp. 3192–3195.

- [9] S. V. Cheong, H. S. H. Chung, and A. Ioinovici, "Inductorless DC-DC converter with high power density," *IEEE Trans. Ind. Electron.*, vol. 41, no. 2, pp. 208–215, Apr. 1994.

- [10] G. Zhu and A. Ioinovici, "Implementing IC based designs for 3.3 V supplies," *IEEE Circuits Devices Mag.*, vol. 11, no. 5, pp. 27–29, Sep. 1995.

- [11] C. K. Tse, S. C. Wong, and M. H. L. Chow, "On lossless switchedcapacitor power converters," *IEEE Trans. Power Electron.*, vol. 10, no. 3, pp. 286–291, May 1995.

- [12] G. Zhu and A. Ioinovici, "DC-to-DC converter with no magnetic elements and enhanced regulation," *IEEE Trans. Aerosp. Electron. Sys.*, vol. 33, no. 2, pp. 499–506, Apr. 1997.

- [13] D. Maksimovic and S. Dhar, "Switched-capacitor DC-DC converters for low-power on-chip applications," in *IEEE Power Electron. Specialists Conf. (PESC)*, Jul. 1999, vol. 1, pp. 54–59.

- [14] G. Zhu, H. Wei, I. Batarseh, and A. Ioinovici, "A new switched-capacitor DC-DC converter with improved line and load regulation," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 1999, pp. 234–237.

- [15] W. Chen, W. H. Ki, P. K. T. Mok, and M. Chan, "Switched-capacitor power converters with integrated low dropout regulator," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2001, pp. 293–296.

- [16] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Transformerless DC-DC converters with a very high DC line-to-load voltage ratio," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2003, vol. 3, pp. 435–438.

- [17] J. Han, A. V. Jouanne, and G. C. Temes, "A new approach to reducing output ripple in switched-capacitor-based step-down DC-DC converter," *IEEE Trans. Power Electron.*, vol. 21, no. 6, pp. 1548–1555, Nov. 2006.

- [18] J. Liu, Z. Chen, and Z. Du, "Switched capacitor DC-DC converters enable electronic products to become more compact," in *Proc. Int. Conf. Softw. Eng. (ICSE)*, Nov. 1996, pp. 234–237.

- [19] J. Liu, Z. Chen, and Z. Du, "A new design of power supplies for pocket computer systems," *IEEE Trans. Ind. Electron.*, vol. 45, no. 2, pp. 228–235, Apr. 1998.

[20] Y. H. Chang, "Variable-conversion-ratio switched-capacitor-voltage-

- [20] Y. H. Chang, "Variable-conversion-ratio switched-capacitor-voltagemultiplier/divider DC-DC converter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, pp. 1944–1957, Aug. 2011.

- [21] R. D. Middlebrook, "Transformerless DC-to-DC converters with large conversion ratios," *IEEE Trans. Power Elect.*, vol. 3, no. 4, pp. 484–488, Oct. 1988.

- [22] J. Sun, M. Xu, Y. Ying, and F. C. Lee, "High power density high efficiency system two-stage power architecture for laptop computers," in *IEEE Power Electron. Specialists Conf. Rec. (PESC)*, Jun. 2006, pp. 4008–4015.

- [23] R. C. N. Pilawa-Podgurski, D. M. Giuliano, and D. J. Perreault, "Merged two-stage power converter architecture with soft charging switched-capacitor energy transfer," in *IEEE Power Electron. Specialists Conf. Rec. (PESC)*, Jun. 2008, pp. 4008–4015.

- [24] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Switched-capacitor/switched-inductor structures for getting transformerless hybrid DC-DC PWM converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 2, pp. 687–696, Mar. 2008.

- [25] S. Xiong, S. C. Tan, and S. C. Wong, "Analysis of a high-voltage-gain hybrid switched-capacitor buck converter," in *Proc., IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2011, pp. 1616–1619.

**Song Xiong** was born in Jiangxi Province, China, in 1985. He received the B.Eng. and M.Eng. degrees in electrical and electronic engineering from Huazhong University of Science and Technology, Wuhan, China, in 2007 and 2009, respectively. He is currently working toward his Ph.D. degree in the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hong Kong

From January 2009 to January 2010, he worked as a Research Assistant in the Department of Electronic

and Information Engineering, Hong Kong Polytechnic University. His current research interests include high-voltage-gain dc-dc converters and switched-capacitor converters.

Siew-Chong Tan (S'00–M'06–SM'11) received the B.Eng. (Hons.) and M.Eng. degrees in electrical and computer engineering from the National University of Singapore, Singapore, in 2000 and 2002, respectively, and the Ph.D. degree in electronic and information engineering from the Hong Kong Polytechnic University, Hong Kong, in 2005.

From October 2005 to May 2012, he worked as Research Associate, Postdoctoral Fellow, Lecturer, and Assistant Professor in Department of Electronic and Information Engineering, Hong Kong

Polytechnic University, Hong Kong. From January to October 2011, he was Senior Scientist in Agency for Science, Technology and Research (A\*Star), Singapore. He is currently an Associate Professor in Department of Electrical and Electronic Engineering, University of Hong Kong, Hong Kong. Dr. Tan was a Visiting Scholar at Grainger Center for Electric Machinery and Electromechanics, University of Illinois at Urbana-Champaign, Champaign, from September to October 2009, and an Invited Academic Visitor of Huazhong University of Science and Technology, Wuhan, China, in December 2011. He is the coauthor of the book *Sliding Mode Control of Switching Power Converters: Techniques and Implementation* (Boca Raton: CRC, 2011). His research interests are focused in the areas of power electronics, control theories, smart grids, and clean energy technologies.

Dr. Tan serves extensively as a reviewer for various IEEE/IET transactions and journals on power, electronics, circuits, and control engineering.

**Siu-Chung Wong** (M'01–SM'09) received the B.Sc. degree in physics from the University of Hong Kong, Hong Kong, in 1986, the M.Phil. degree in electronics from the Chinese University of Hong Kong in 1989, and the Ph.D. degree from the University of Southampton, U.K., in 1997.

Dr. Wong joined Hong Kong Polytechnic in 1988 as an Assistant Lecturer. He is currently an Associate Professor in the Department of Electronic and Information Engineering at Hong Kong Polytechnic University, Hong Kong. In 2012, he was appointed as

Chutian Scholars Chair Professor at Wuhan University of Science and Technology, Wuhan, by the Hubei Provincial Department of Education, China. He was a visiting scholar at the Center for Power Electronics Systems, Virginia Tech, on November 2008 and Aero-Power Sci-tech Center, Nanjing University of Aeronautics & Astronautics, Nanjing, China on January 2009. His research interests include modeling of power converters, nonlinear analysis of power electronics, LED lighting systems, wind energy systems, and Internet traffic analysis.

Dr. Wong serves actively as a reviewer for several IEEE/IET/International journals on power electronics, circuits and systems, and Internet communications. He is an editor of *Energy and Power Engineering* (EPE) journal since 2010. He is a member of the Electrical College, The Institution of Engineers, Australia.