Failure Mode Modular De-Composition

R.P. Clark

A thesis submitted in partial fulfilment of the requirements for the University of Brighton for the degree of Doctor of Philosophy.

September 2013

# Colophon

In short "Thanks every body"!

It has been a great privilege to spend several years visiting the Mathematics and Engineering departments of the University of Brighton, pushing me forward in clarity of self-expression, precision through mathematics, critical assessment and carefully crafted English: its members will always remain dear to me. My first debt of gratitude must go to my supervisors, Dr. A. Fish, Dr. C Garret and Professor J. Howse. They patiently provided the guidance, encouragement and advice necessary for me to proceed through the research, consolidation and write-up phases of the PhD program, to prepare and present three papers to conferences [19, 20, 21] and to complete and submit this thesis.

I owe a debt of thanks to Dr J. flower, my MSc project supervisor, who explained that the chapter in my project documentation postulating a modular form of FMEA—which had potential for making the process more efficient—was a concept worthy of being developed for a PhD and assisting me to present the chapter as a conference paper [22]. Further I thank her for encouraging me to apply for the PhD. I also wish to thank Alan Jones of Brighton College of Technology for taking a chance on someone with no 'A' levels and letting him start an HND in software Engineering in 1986. That more than anything changed my life and gave me fantastic opportunities.

I am deeply thankful to the directors of Energy Technology Control Ltd not only for funding this course, but providing training and work experience in the field of safety critical engineering and giving me Friday afternoons to pursue my studies. At Energy Technology Control, the following people gave encouragement, and validated the concepts for the 'modular FMEA' that I was developing, Martin Thirsk, Colin Talmay, Darren Legge and Hazel Anderson. These Engineers, whose whole careers have been focused on the safety critical electronic/computing area, gave valuable time to look at and comment on my FMMD proposals. Their comments gave me confidence that the methodology I was developing had potential practical applications and benefits. The environment and context of the work at Energy Technology Control Ltd was very useful for clarifying concepts relating to FMEA and safety; at least once a week there is a new practical case study arising and being discussed, be it, say, the observability of the effect of failures in an traditional amplifier configuration, or how a particular sensor could fail. The field of industrial burner control, is highly regulated and is rich with practical examples of safety measures built into hybrid digital/electronic systems. This has given me many opportunities to apply the new methodology against 'real world' problems. These real world failure scenarios and their proposed solutions, were often detailed in requirements and design documentation, submitted in support of safety accreditation. I was glad to be tasked to produce many of these documents. Again I thank Energy Technology Control Ltd, for giving me these parallel tasks, which aided my studies.

I wish to thank my parents, Jennifer and Richard Clark. I hope that this work makes you proud.

Typeset in LATEXFebruary 6, 2014.

# Declaration

I declare that the research contained in this thesis, unless otherwise formally indicated within the text, is the original work of the author. The thesis has not been previously submitted to this or any other university for a degree, and does not incorporate any material already submitted for a degree.

Signed

Dated

### Abstract

#### Failure Mode Modular De-Composition

The certification process of safety critical products for European and other international standards typically demand environmental stress, endurance and electro magnetic compatibility testing. Theoretical, or 'static testing' also a requirement. Failure Mode Effects Analysis (FMEA) is a tool used for static testing. FMEA is a bottom-up technique that aims to assess the effects of all component failure modes in a system. Its use is traditionally limited to hardware systems. With the growing complexity of modern electronics traditional FMEA is suffering from state explosion and re-use of analysis problems. Also with the now ubiquitous use of microcontrollers in smart instruments and control systems, software is increasingly being seen as a 'missing factor' for FMEA.

This thesis presents a new modular variant of FMEA, Failure Mode Modular Decomposition (FMMD). FMMD has been designed to integrate mechanical/electronic and software failure models, by treating them all as components in terms of their failure modes. For instance, software functions, electronic and mechanical components can all be assigned sets of failure modes. FMMD builds failure mode models from the bottom-up by incrementally analysing functional groupings of components, using the results of analysis to create higher level derived components, which in turn can be used to build functional groupings. In this way a hierarchical failure mode model is built. Software functions are treated as components by FMMD and can thus be incorporated seamlessly into the failure mode hierarchical model. A selection of examples, electronic circuits and hardware/software hybrids are analysed using this new methodology. The results of these analyses are then discussed from the perspective of safety critical application. Performance in terms of test efficiency is greatly improved by FMMD and the examples analysed and theoretical models are used to demonstrate this.

This thesis presents a methodology that mitigates the state explosion problems of FMEA; provides integrated hardware and software failure mode models; facilitates multiple failure mode analysis; encourages re-use of analysis work and can be used to produce traditional format FMEA reports.

# Contents

| 1        | Intr | roducti | on                                                                     | 1        |

|----------|------|---------|------------------------------------------------------------------------|----------|

|          | 1.1  | Motiv   | ation                                                                  | 2        |

|          |      |         | MSc Project: Euler/Spider diagram Editor.                              | 2        |

|          |      |         | European Safety Requirements increase in scope and complexity          | 2        |

|          |      | 1.1.1   | Modularising/De-Composing FMEA: Initial concepts.                      | 3        |

|          |      | 1.1.2   | Initial direction: Application of Spider diagrams to FMEA              | 3        |

|          | 1.2  | Objec   | tives of the thesis                                                    | 4        |

|          |      |         | Overview of the thesis                                                 | 4        |

| <b>2</b> | Fail | lure M  | ode Effect Analysis                                                    | <b>5</b> |

|          | 2.1  | FMEA    | Basic concept.                                                         | 5        |

|          | 2.2  | FMEA    | Process                                                                | 6        |

|          | 2.3  | Deteri  | nining the failure modes of base components                            | 7        |

|          | 2.4  | Deteri  | nining the failure modes of Components.                                | 8        |

|          |      | 2.4.1   | Failure mode determination for generic resistor                        | 9        |

|          |      |         | Resistor failure modes according to FMD-91                             | 9        |

|          |      |         | Resistor failure modes according to EN298                              | 9        |

|          |      |         | 2.4.1.1 Resistor Failure Modes                                         | 10       |

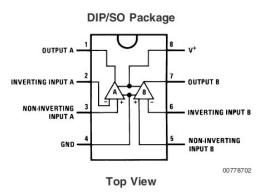

|          |      | 2.4.2   | Failure modes determination for a generic operational amplifier        | 10       |

|          |      |         | Failure Modes of an Op-Amp according to FMD-91.                        | 10       |

|          |      |         | Op-Amp failure cause: Poor Die attach.                                 | 10       |

|          |      |         | No Operation - over stress.                                            | 11       |

|          |      |         | Shorted inputs: $V_+$ to $V$                                           | 11       |

|          |      |         | Open input: $V_+$                                                      | 11       |

|          |      |         | Collecting Op-Amp failure modes from FMD-91.                           | 11       |

|          |      |         | Failure Modes of an Op-Amp according to EN298                          | 11       |

|          |      |         | 2.4.2.1 Failure modes of an Op-Amp                                     | 12       |

|          |      | 2.4.3   | Comparing the component failure mode sources: EN298 vs FMD-91 $\ldots$ | 12       |

|          | 2.5  | FMEA    | worked example: milli-volt reader                                      | 13       |

|          |      | 2.5.1   | FMEA Example: Milli-volt reader                                        | 13       |

| 2.6  | Theor  | etical Concepts in FMEA                                                                  | 14         |

|------|--------|------------------------------------------------------------------------------------------|------------|

|      |        | Failure modes of a component and mutual exclusivity                                      | 14         |

|      |        | The signal path.                                                                         | 14         |

|      |        | Failure Modes and the signal path                                                        | 15         |

|      |        | Single component failure mode to system failure relation.                                | 15         |

|      |        | Use of Markov chains to model failure modes                                              | 15         |

|      |        | Subjective and Objective thinking in relation to FMEA.                                   | 15         |

|      |        | Multiple Simultaneous Failure Modes.                                                     | 16         |

|      |        | Failure modes and their observability criterion: detectable and undetectable             | 16         |

|      |        | Impracticality of Field Data for Modern Systems.                                         | 16         |

|      |        | Forward and Backward Searches.                                                           | 17         |

|      | 2.6.1  | Reasoning distance.                                                                      | 17         |

|      | 2.6.2  | FMEA and the State Explosion Problem                                                     | 17         |

|      |        | Problem of which components to check for a given base component failure mode.            | 17         |

|      |        | Exhaustive Single Failure FMEA                                                           | 18         |

|      |        | Exhaustive FMEA and double failure scenarios.                                            | 18         |

|      |        | Reliance on experts for meaningful FMEA Analysis.                                        | 18         |

|      | 2.6.3  | Component Tolerance                                                                      | 18         |

| 2.7  | FMEA   | in current usage: Four variants                                                          | 18         |

|      |        | Four main Variants of FMEA                                                               | 18         |

| 2.8  | FMEC   | CA - Failure Modes Effects and Criticality Analysis                                      | 19         |

|      |        | FMECA - Statistical variables.                                                           | 19         |

| 2.9  | FMEI   | DA - Failure Modes Effects and Diagnostic Analysis                                       | 20         |

|      |        | SIL and Software.                                                                        | 20         |

|      | 2.9.1  | FMEDA - Failure Modes Effects and Diagnostic Analysis                                    | 21         |

|      | 2.9.2  | Automotive Safety Integrity Levels                                                       | 21         |

| 2.10 | FMEA   | used for Safety Critical Approvals                                                       | 22         |

|      | 2.10.1 | DESIGN FMEA: Safety Critical Approvals FMEA                                              | 22         |

| 2.11 | Conclu | 1sion                                                                                    | 22         |

|      |        | Which, or how many components should be checked for each failure mode entry? .           | 22         |

|      |        | FMEA gives us objective system level failures/symptoms.                                  | 23         |

|      |        | Re-use potential of an FMEA report                                                       | 23         |

| FМ   | EA Cr  | iticism                                                                                  | <b>25</b>  |

| 3.1  |        | ical Origins of FMEA and the base component failure mode to system level failure/symptom | <u>4</u> 0 |

| 0.1  |        | gm                                                                                       | 26         |

|      | 3.1.1  | FMEA: base component failure mode to system level failure modelling                      | 26<br>26   |

|      | 3.1.2  | FMEA does not encourage Traceable Reasoning       ••••••••••••••••••••••••••••••••••••   |            |

|      | 0.1.2  | Re-use of FMEA analysis.                                                                 |            |

|      |        |                                                                                          | 40         |

3

|          |               | 3.1.3    | FMEA does not support modularity                                             | 26        |

|----------|---------------|----------|------------------------------------------------------------------------------|-----------|

|          |               | 3.1.4    | FMEA one to many mapping for component failure to system level failure modes | 27        |

|          | 3.2           | Compar   | rison Complexity                                                             | 27        |

|          |               |          | The ideal of exhaustive FMEA (XFMEA)                                         | 27        |

|          | 3.3           | Softwar  | e and FMEA                                                                   | 27        |

|          |               |          | Current work on Software FMEA.                                               | 28        |

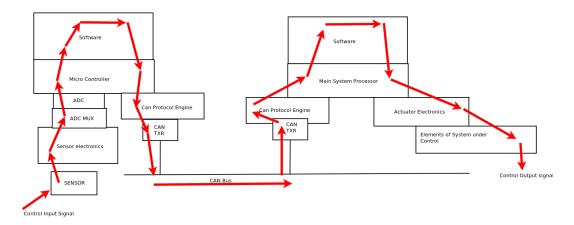

|          |               | 3.3.1    | The rise of the smart instrument                                             | 28        |

|          |               | 3.3.2    | Distributed real time systems                                                | 29        |

|          | 3.4           | FMEA     | —- general criticism — conclusion                                            | 29        |

|          |               | 3.4.1    | FMEA Criticism: Conclusions.                                                 | 30        |

|          |               | 3.4.2    | FMEA - Better Methodology - Wish List                                        | 30        |

| 4        | Fail          | ure Mo   | de Modular Decomposition                                                     | <b>31</b> |

|          | 4.1           | Introdu  | ction                                                                        | 31        |

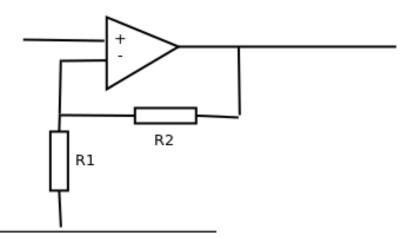

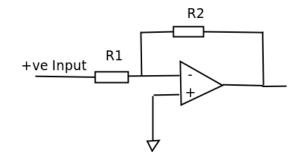

|          | 4.2           | Worked   | Example: Non-Inverting Amplifier                                             | 32        |

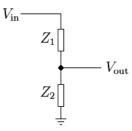

|          |               |          | Analysing the failure modes of the Potential Divider.                        | 32        |

|          |               |          | Failure Mode Analysis of a generic op-amp.                                   | 33        |

|          | 4.3           | Defining | g terms                                                                      | 35        |

|          |               |          | A discussion on the terms Parts, Components and Base Components              | 35        |

|          |               | 4.3.1    | Definition of terms: sound system example                                    | 36        |

|          |               |          | Functional Groupings and Components.                                         | 36        |

|          |               | 4        | 4.3.1.1 Functional grouping to derived component process outline             | 37        |

|          |               |          | Functional grouping determination                                            | 37        |

|          |               |          | Failure modes used for base components                                       | 37        |

|          | 4.4           | Failure  | Modes in depth                                                               | 38        |

|          | 4.5           | Fault M  | Iode Analysis, top down or bottom up?                                        | 38        |

|          |               | 4.5.1    | From functional group to newly derived component                             | 39        |

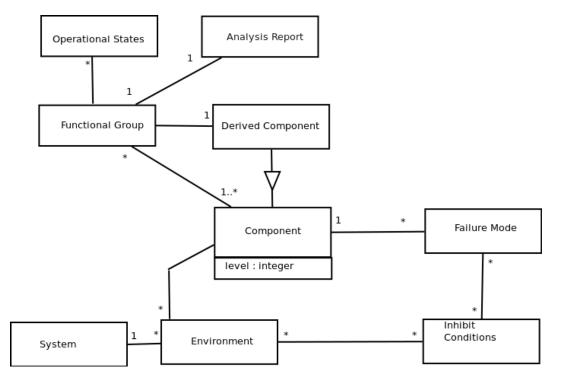

|          |               | 4.5.2    | How the UML Meta Model maps to an FMMD Hierarchy                             | 39        |

|          |               |          | Traceability and quality of FMMD analysis.                                   | 40        |

|          |               |          | Keeping track of the derived components position in the hierarchy.           | 41        |

|          | 4.6           | Conclus  | sion                                                                         | 41        |

|          |               |          | Failure model Completeness.                                                  | 41        |

|          |               |          | Mutual exclusivity of derived component failure modes.                       | 41        |

|          |               |          | Objective and contextual/subjective failure symptoms                         | 41        |

|          |               |          | State explosion problem of FMEA mitigated by FMMD                            | 41        |

|          |               |          | Uses of the FMMD failure mode model                                          | 42        |

| <b>5</b> | $\mathbf{FM}$ | MD Ex    | amples                                                                       | 43        |

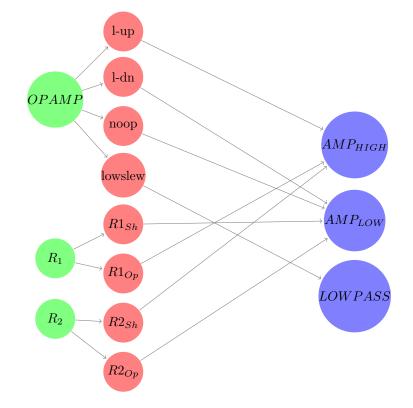

|          | 5.1           | Exampl   | le Analysis: Inverting OPAMP                                                 | 44        |

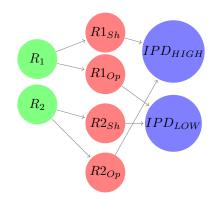

|          |               | 5.1.1    | First Approach: Inverting OPAMP using a Potential Divider derived component  | 45        |

|     | 5.1.2   | Second Approach: Inverting OpAmp analysing with three components in one larger func-        |    |

|-----|---------|---------------------------------------------------------------------------------------------|----|

|     |         | tional grouping                                                                             | 48 |

|     | 5.1.3   | Comparison between the two approaches                                                       | 48 |

|     | 5.1.4   | Conclusion                                                                                  | 48 |

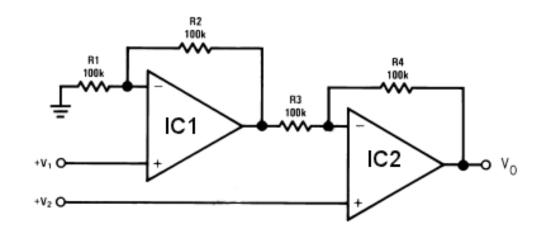

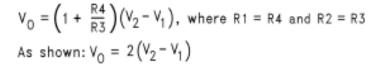

| 5.2 | Differe | encing Amplifier using two op-amps                                                          | 49 |

|     | 5.2.1   | The second stage of the amplifier                                                           | 49 |

|     | 5.2.2   | Final stage of the $DiffAmp$ Analysis                                                       | 51 |

|     | 5.2.3   | Conclusion                                                                                  | 51 |

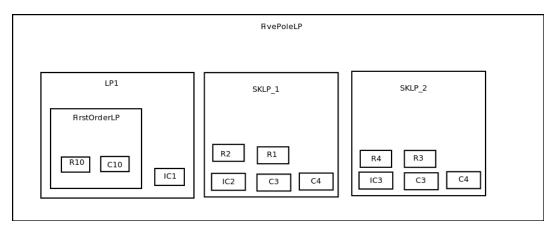

| 5.3 | Five F  | Pole Low Pass Filter, using two Sallen Key stages.                                          | 54 |

|     | 5.3.1   | First Order Low Pass Filter                                                                 | 54 |

|     | 5.3.2   | Addition of Buffer Amplifier: First stage                                                   | 55 |

|     | 5.3.3   | Second order Sallen Key Low Pass Filter                                                     | 56 |

|     | 5.3.4   | A failure mode model of the five pole Sallen Key filter                                     | 57 |

|     | 5.3.5   | Conclusion                                                                                  | 59 |

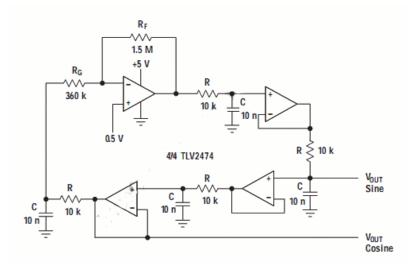

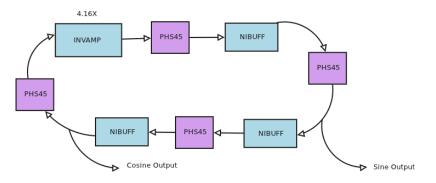

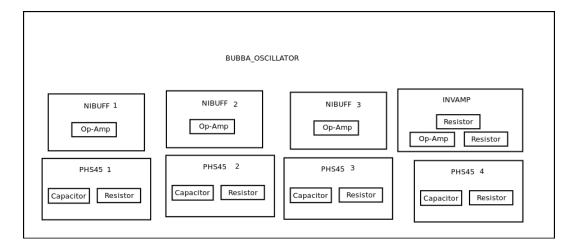

| 5.4 | Quad    | Op-Amp Oscillator                                                                           | 60 |

|     | 5.4.1   | Inverting Amplifier: INVAMP                                                                 | 61 |

|     | 5.4.2   | Phase shifter: PHS45                                                                        | 61 |

|     | 5.4.3   | Non Inverting Buffer: NIBUFF                                                                | 61 |

|     | 5.4.4   | Bringing the functional groupings Together: FMMD model of the 'Bubba' Oscillator. $\ . \ .$ | 61 |

|     | 5.4.5   | FMMD Analysis using initially identified functional groupings                               | 61 |

|     | 5.4.6   | FMMD Analysis of Bubba Oscillator using a finer grained modular approach (i.e. more         |    |

|     |         | $hierarchical \ stages) \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                             | 63 |

|     |         | Outline of finer grained FMMD analysis of the Bubba oscillator.                             | 63 |

|     |         | Analysis details of the finer grained FMMD analysis of the Bubba oscillator                 | 63 |

|     | 5.4.7   | Comparing both approaches                                                                   | 64 |

|     | 5.4.8   | Conclusion                                                                                  | 64 |

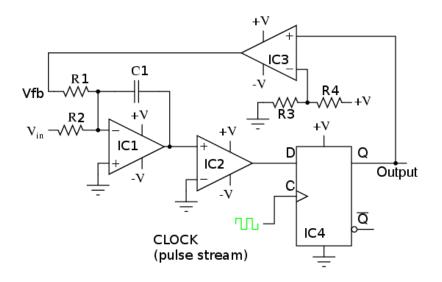

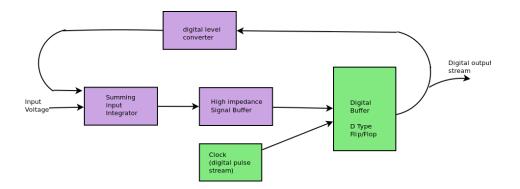

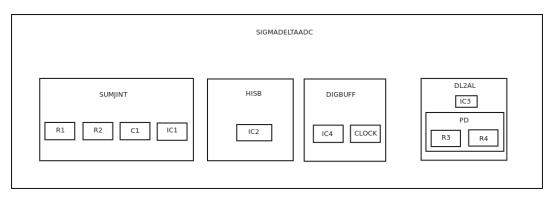

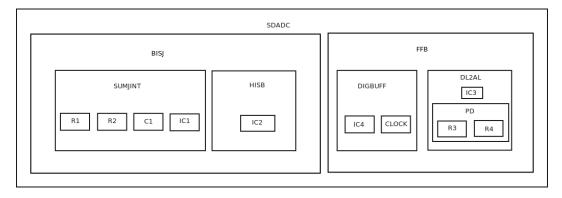

| 5.5 | Sigma   | a Delta Analogue to Digital Converter ( $\Sigma \Delta ADC$ ).                              | 65 |

|     |         | How the circuit works                                                                       | 65 |

|     | 5.5.1   | FMMD analysis of $\Sigma \Delta ADC$                                                        | 66 |

|     | 5.5.2   | Identifying initial functional groupings                                                    | 66 |

|     |         | 5.5.2.1 Summing Junction Integrator (SUMJINT)                                               | 66 |

|     |         | 5.5.2.2 High Impedance Signal Buffer (HISB)                                                 | 66 |

|     |         | 5.5.2.3 Digital level to analogue level conversion $(DL2AL)$                                | 67 |

|     |         | Potential divider formed by R3,R4                                                           | 67 |

|     |         | 5.5.2.4 $DIGBUF$ — digital clocked memory (flip-flop)                                       | 67 |

|     | 5.5.3   | First functional groupings analysed                                                         | 67 |

|     |         | 5.5.3.1 Buffered Integrating Summing Junction (BISJ): functional grouping of $HISB$         |    |

|     |         | and $SUMJINT$                                                                               | 68 |

|     |         | 5.5.3.2 Flip Flop Buffer (FFB): functional grouping of $DL2AL$ and $DIGBUF$                 | 68 |

|   |     | 5.5.4  | Final, top level functional grouping for sigma delta Converter         | 68 |

|---|-----|--------|------------------------------------------------------------------------|----|

|   |     | 5.5.5  | Conclusion                                                             | 69 |

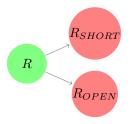

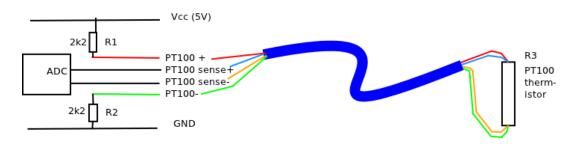

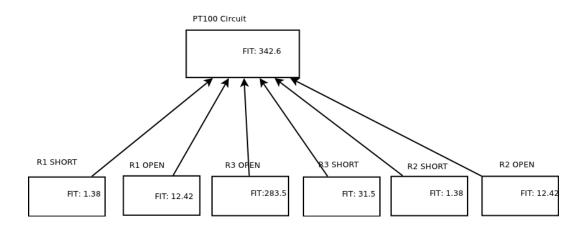

|   | 5.6 | Pt100  | Analysis: FMMD and Double Failure Mode Analysis                        | 70 |

|   |     | 5.6.1  | General Description of Pt100 four wire circuit                         | 70 |

|   |     |        | Accuracy despite variable resistance in cables                         | 70 |

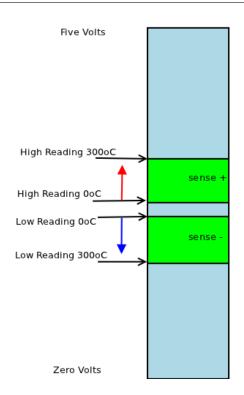

|   |     |        | Calculating Temperature from the sense line voltages                   | 70 |

|   |     | 5.6.2  | Safety case for 4 wire circuit: Detailed calculations                  | 71 |

|   |     |        | Single Fault FMEA Analysis of $Pt100$ Four wire circuit                | 71 |

|   |     |        | Consideration of Resistor Tolerance.                                   | 72 |

|   |     |        | Range and $Pt100$ Calculations                                         | 72 |

|   |     |        | Single Fault FMEA Analysis of $Pt100$ Four wire circuit                | 73 |

|   |     |        | Proof of Out of Range Values for Failures                              | 73 |

|   |     |        | TC 2 : Voltages $R_1$ OPEN                                             | 74 |

|   |     |        | TC 3 : Voltages $R_2$ SHORT                                            | 74 |

|   |     |        | TC 4 : Voltages $R_2$ OPEN                                             | 74 |

|   |     |        | TC 5 : Voltages $R_3$ SHORT                                            | 74 |

|   |     |        | TC 6 : Voltages $R_3$ OPEN                                             | 74 |

|   |     | 5.6.3  | Summary of Analysis                                                    | 74 |

|   |     | 5.6.4  | Derived Component $Pt100$ analysed for single failure modes            | 75 |

|   | 5.7 | Pt100  | ) Double Simultaneous Fault Analysis                                   | 75 |

|   |     |        | TC 7 : Voltages $R_1$ OPEN $R_2$ OPEN                                  | 75 |

|   |     |        | TC 8 : Voltages $R_1$ OPEN $R_2$ SHORT $\ldots$                        | 76 |

|   |     |        | TC 9 : Voltages $R_1$ OPEN $R_3$ OPEN                                  | 76 |

|   |     |        | TC 10 : Voltages $R_1$ OPEN $R_3$ SHORT                                | 76 |

|   |     |        | TC 11 : Voltages $R_1$ SHORT $R_2$ OPEN                                | 76 |

|   |     |        | TC 12 : Voltages $R_1$ SHORT $R_2$ SHORT                               | 76 |

|   |     |        | TC 13 : Voltages $R_1$ SHORT $R_3$ OPEN                                | 76 |

|   |     |        | TC 14 : Voltages $R_1$ SHORT $R_3$ SHORT                               | 76 |

|   |     |        | TC 15 : Voltages $R_2$ OPEN $R_3$ OPEN                                 | 76 |

|   |     |        | TC 16 : Voltages $R_2$ OPEN $R_3$ SHORT                                | 76 |

|   |     |        | TC 17 : Voltages $R_2$ SHORT $R_3$ OPEN                                | 76 |

|   |     |        | TC 18 : Voltages $R_2$ SHORT $R_3$ SHORT.                              | 76 |

|   |     |        | Symptom Extraction, forming a derived component.                       | 76 |

| 6 | App | olying | FMMD to Software and Hybrid Systems                                    | 77 |

|   | 6.1 | Softwa | are and Hardware Failure Mode Concepts                                 | 77 |

|   |     | 6.1.1  | Software, a natural hierarchy                                          | 78 |

|   |     | 6.1.2  | Contract programming description                                       | 78 |

|   |     |        | Mapping contract 'pre-condition' violations to component failure modes | 78 |

|   |               |         | Ν            | Iapping contract 'post-condition' violations to symptoms.         .                                              | 78  |

|---|---------------|---------|--------------|------------------------------------------------------------------------------------------------------------------|-----|

|   |               |         | Ν            | fapping contract 'invariant' violations to symptoms and failure modes                                            | 79  |

|   |               | 6.1.3   | Combine      | ed Hardware/Software FMMD                                                                                        | 79  |

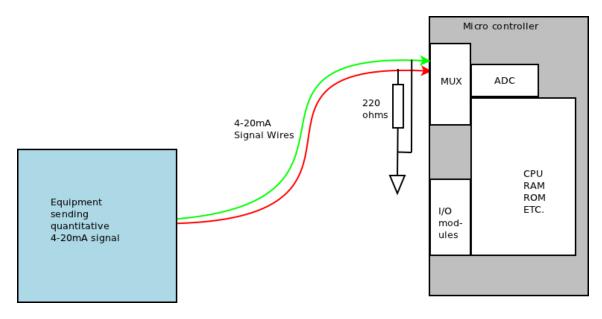

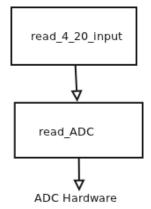

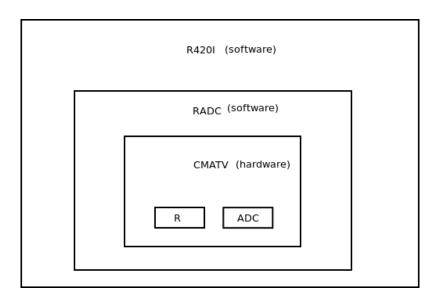

|   | 6.2           | Simple  | Software     | e Example: Reading a $4 \rightarrow 20mA$ input into software $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 80  |

|   |               | 6.2.1   | FMMD         | Process                                                                                                          | 83  |

|   |               |         | Η            | lardware only Functional Grouping - Convert mA to Voltage - CMATV                                                | 83  |

|   |               |         | $\mathbf{S}$ | oftware and hardware hybrid functional grouping — RADC                                                           | 84  |

|   |               |         | F            | unctional Group - Software - voltage to per mil - VTPM                                                           | 85  |

|   |               | 6.2.2   | Conclus      | ion: $4 \rightarrow 20 mA$ Reader Software/Hardware FMMD Model                                                   | 85  |

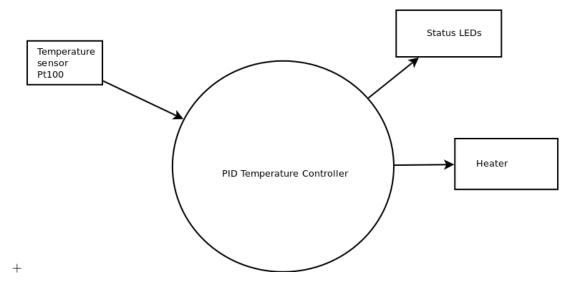

|   | 6.3           | Closed  | Loop Co      | ontrol Hardware/Software Hybrid Example                                                                          | 87  |

|   |               | 6.3.1   | Design S     | Stage: Implementation on a micro-controller.                                                                     | 87  |

|   |               |         | Γ            | Data flow model to programmatic call tree                                                                        | 89  |

|   |               |         | S            | oftware Algorithm.                                                                                               | 90  |

|   |               | 6.3.2   | FMMD         | Analysis of PID temperature Controller                                                                           | 91  |

|   |               | 6.3.3   | Tempera      | ature Controller Hardware Elements FMMD                                                                          | 91  |

|   |               |         | Ā            | DCMUX and Read_ADC.                                                                                              | 91  |

|   |               |         | Γ            | 'IMER                                                                                                            | 91  |

|   |               |         |              |                                                                                                                  | 91  |

|   |               |         |              |                                                                                                                  | 91  |

|   |               |         |              |                                                                                                                  | 91  |

|   |               |         |              |                                                                                                                  | 92  |

|   |               | 6.3.4   |              |                                                                                                                  | 92  |

|   |               |         | 6.3.4.1      | Afferent flow FMMD analysis, Pt100, temperature, set point error, PID output                                     |     |

|   |               |         |              | demand                                                                                                           | 92  |

|   |               |         | 6.3.4.2      |                                                                                                                  | 95  |

|   |               |         | 6.3.4.3      |                                                                                                                  | 95  |

|   |               |         | 6.3.4.4      |                                                                                                                  | 96  |

|   |               | 6.3.5   |              |                                                                                                                  | 97  |

|   |               |         |              |                                                                                                                  |     |

| 7 | $\mathbf{FM}$ | MD M    | etrics C     | ritiques Exceptions and Evaluation                                                                               | 99  |

|   | 7.1           | Definir | ng the co    | ncept of 'comparison complexity' in FMEA                                                                         | 99  |

|   |               | 7.1.1   | Formal of    | definitions of entities used in FMEA                                                                             | .00 |

|   |               | 7.1.2   | A genera     | al formula for counting Comparison Complexity in an FMMD hierarchy 1                                             | .00 |

|   |               | 7.1.3   | Complex      | xity Comparison Examples                                                                                         | .01 |

|   |               |         | C            | Complexity Comparison for a hypothetical 81 component system                                                     | .01 |

|   |               | 7.1.4   | Compar       | ing FMMD and XFMEA Comparison Complexity                                                                         | .03 |

|   |               | 7.1.5   | Compar       | ing XFMEA and FMMD: an Example                                                                                   | .04 |

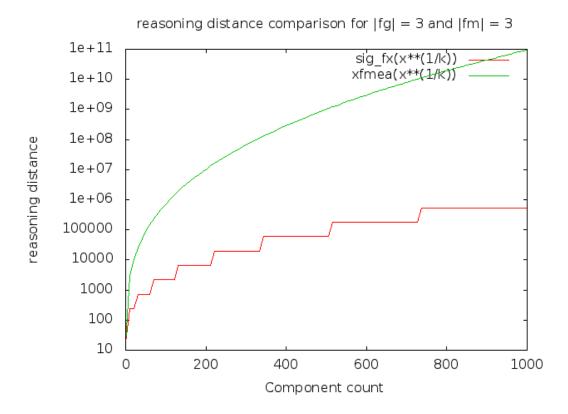

|   |               |         | 7.1.5.1      | Plotting XFMEA and FMMD reasoning distance                                                                       | .05 |

|   | 7.2           | Comple  | exity Co     | mparison applied to FMMD electronic circuits analysed in chapter 5. $\ldots$ 1                                   | .05 |

|   |               |         |              |                                                                                                                  |     |

|   |     | 7.2.1   | Comparison Complexity for the Bubba Oscillator Example                                                                                                                      |

|---|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 7.2.2   | Sigma Delta Example: Comparison Complexity Results                                                                                                                          |

|   | 7.3 | Unita   | ry State Component Failure Mode Sets                                                                                                                                        |

|   |     |         | Design Decision/Constraint                                                                                                                                                  |

|   |     | 7.3.1   | Example of unitary state component failure modes                                                                                                                            |

|   |     |         | Design Rule: Unitary State                                                                                                                                                  |

|   | 7.4 | Handl   | ing Simultaneous Component Faults                                                                                                                                           |

|   | 7.5 | Cardin  | nality Constrained Power-set                                                                                                                                                |

|   |     |         | Calculating the number of elements in a Cardinality Constrained power-set $\ . \ . \ . \ 111$                                                                               |

|   |     | 7.5.1   | Actual Number of combinations to check with Unitary State Fault mode sets $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                          |

|   |     |         | 7.5.1.1 Example: Two Component functional grouping Cardinality Constraint of 2 112                                                                                          |

|   |     |         | 7.5.1.2 Establishing Formulae for unitary state failure mode cardinality calculation 112                                                                                    |

|   |     | 7.5.2   | Example: Pt100 Verifying complete coverage for a cardinality constrained power-set of $2$ . 113                                                                             |

|   | 7.6 | Comp    | onent Failure Modes and Statistical Sample Space                                                                                                                            |

|   | 7.7 | Comp    | onents with Independent failure modes                                                                                                                                       |

|   |     |         | De-composition of complex component                                                                                                                                         |

|   |     |         | Combinations become new failure modes                                                                                                                                       |

|   | 7.8 | Critiq  | ues                                                                                                                                                                         |

|   |     | 7.8.1   | Problems in choosing membership of functional groupings                                                                                                                     |

|   |     |         | 7.8.1.1 Side Effects: A Problem for FMMD analysis                                                                                                                           |

|   |     |         | 7.8.1.2 Example de-coupling capacitors in logic circuits                                                                                                                    |

| 8 | Cor | nclusio | n 119                                                                                                                                                                       |

|   | 8.1 | Furthe  | er Work                                                                                                                                                                     |

|   |     | 8.1.1   | How traditional FMEA reports can be derived from an FMMD model                                                                                                              |

|   |     | 8.1.2   | Statistics: From base component failure modes to System level events/failures 120                                                                                           |

|   |     | 8.1.3   | Composition of functional groupings                                                                                                                                         |

|   |     | 8.1.4   | Deriving FTA diagrams from FMMD models                                                                                                                                      |

|   |     |         | Environment, operational states and inhibit gates: additions to the UML model. $% \mathcal{A} = \mathcal{A}$ . 121                                                          |

|   |     |         | Environmental Modelling                                                                                                                                                     |

|   |     |         | Operational states                                                                                                                                                          |

|   |     |         | Inhibit Conditions                                                                                                                                                          |

|   |     |         | UML Diagram Additional Objects                                                                                                                                              |

|   |     | 8.1.5   | Retrospective failure mode analysis and FMMD                                                                                                                                |

|   |     |         | Retrospective failure mode analysis and software                                                                                                                            |

|   |     |         | Effect of newly discovered failure modes in components. $\dots \dots \dots$ |

|   |     | 8.1.6   | Creation of a software FMMD tool                                                                                                                                            |

|   | 8.2 | Objec   | tive and Subjective Reasoning stages                                                                                                                                        |

|   |     |                   | Objective and Subjective Reasoning in FMEA: Three Mile Island nuclear accident                                                                                                    |

|---|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     |                   | example                                                                                                                                                                           |

|   |     |                   | Further Work. Objective and Subjective Reasoning in FMEA                                                                                                                          |

| Α | Det | ailed I           | FMMD analyses 127                                                                                                                                                                 |

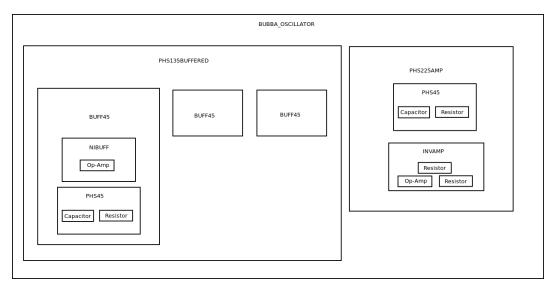

|   | A.1 | Bubba             | a Oscillator FMMD analyses                                                                                                                                                        |

|   |     | A.1.1             | PHS45 Detailed Analysis                                                                                                                                                           |

|   |     | A.1.2             | Bubba Oscillator: One Large Functional Group: Detailed Analysis                                                                                                                   |

|   |     | A.1.3             | BUFF45: Detailed Analysis                                                                                                                                                         |

|   |     | A.1.4             | PHS135BUFFERED: Failure Mode Effects Analysis                                                                                                                                     |

|   |     | A.1.5             | PHS225AMP: Failure Mode Effects Analysis                                                                                                                                          |

|   |     | A.1.6             | BUBBAOSC: Failure Mode Effects Analysis                                                                                                                                           |

|   | A.2 | Sigma             | Delta Detailed FMMD Analyses                                                                                                                                                      |

|   |     | A.2.1             | FMMD Analysis of Summing Junction Integrator: SUMJINT                                                                                                                             |

|   |     | A.2.2             | FMMD Analysis of High Impedance Signal Buffer : HISB                                                                                                                              |

|   |     | A.2.3             | FMMD Analysis of Digital level to analogue level converter : DL2AL                                                                                                                |

|   |     | A.2.4             | FMMD Analysis of Digital Buffer : DIGBUF                                                                                                                                          |

|   |     | A.2.5             | FMMD Analysis of buffered integrating summing junction : BISJ                                                                                                                     |

|   |     | A.2.6             | FMMD Analysis of flip flop buffered : FFB                                                                                                                                         |

|   |     | A.2.7             | FMMD Analysis of $\Sigma \Delta ADC$ : SDADC                                                                                                                                      |

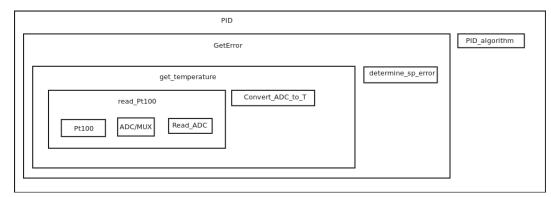

|   | A.3 | Standa            | alone temperature controller                                                                                                                                                      |

|   |     | A.3.1             | Read_Pt100: Failure Mode Effects Analysis                                                                                                                                         |

|   |     | A.3.2             | Get_Temperature: Failure Mode Effects Analysis                                                                                                                                    |

|   |     | A.3.3             | GetError: Failure Mode Effects Analysis                                                                                                                                           |

|   |     | A.3.4             | PID: Failure Mode Effects Analysis                                                                                                                                                |

|   |     | A.3.5             | HeaterOutput: Failure Mode Effects Analysis                                                                                                                                       |

|   |     | A.3.6             | LEDOutput: Failure Mode Effects Analysis                                                                                                                                          |

|   |     | A.3.7             | Standalone temperature controller: Failure Mode Effects Analysis                                                                                                                  |

|   |     | A.3.8             | Statistics and FMMD: Pt100 example for single and double failures                                                                                                                 |

|   |     |                   | Pt100: Single Failures and statistical data                                                                                                                                       |

|   |     |                   | Resistor FIT Calculations                                                                                                                                                         |

|   |     |                   | Pt100 Example: Double Failures and statistical data                                                                                                                               |

|   |     |                   | MTTF statistics and FMMD hierarchies                                                                                                                                              |

|   |     | A.3.9             | Gnuplot script for hypothetical XFMEA FMMD reasoning distance comparison 150                                                                                                      |

| в | Alg | $\mathbf{orithm}$ | ic Description of FMMD 153                                                                                                                                                        |

|   | B.1 | Overv             | iew of the FMMD analysis process                                                                                                                                                  |

|   |     |                   | FMEA applied to the functional grouping: choosing test cases. $\dots \dots \dots$ |

|   |     |                   | Environmental Conditions or Operational States                                                                                                                                    |

|   |     |                   | Symptom Identification                                                                                                                                                            |

|          |         | Collection of Symptoms                                            | 154 |

|----------|---------|-------------------------------------------------------------------|-----|

| B.2 I    | Expan   | ding on a single stage of the FMMD process                        | 154 |

| Η        | B.2.1   | Single stage of FMMD described as a 'symptom abstraction process' | 154 |

| B.3 A    | Algorit | thmic Description of Symptom Abstraction                          | 155 |

| Η        | B.3.1   | Determine Failure Modes to Examine                                | 155 |

| Η        | B.3.2   | Determine Test Cases                                              | 155 |

| Η        | B.3.3   | Analyse Test Cases                                                | 158 |

| Η        | B.3.4   | Find Common Symptoms                                              | 159 |

| Η        | B.3.5   | Create Derived Component                                          | 159 |

|          |         | Enumerating abstraction levels                                    | 159 |

| Η        | B.3.6   | Hierarchical Simplification                                       | 160 |

| Ι        | B.3.7   | Traceable Fault Modes                                             | 160 |

| Glossary | y       |                                                                   | 164 |

# List of Figures

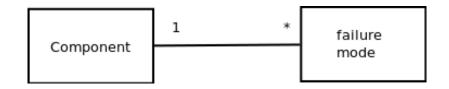

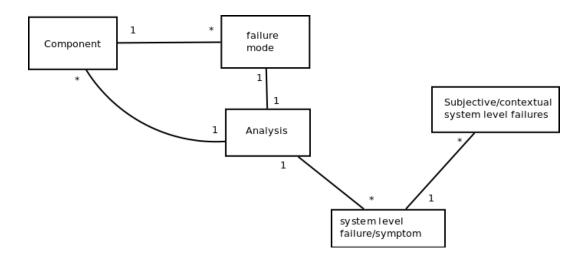

| 2.1 | Base Component to Failure Modes relationship UML diagram                                                    | 6  |

|-----|-------------------------------------------------------------------------------------------------------------|----|

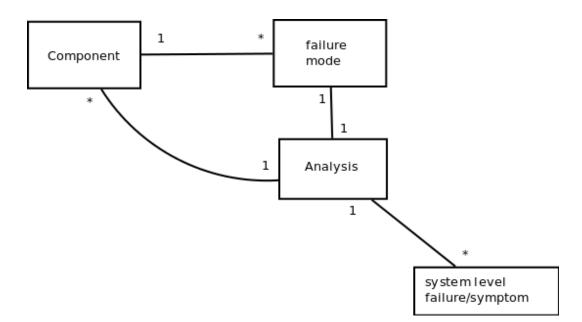

| 2.2 | FMEA analyis entry data relationships                                                                       | 7  |

| 2.3 | Pinout for an LM358 dual Op-Amp                                                                             | 11 |

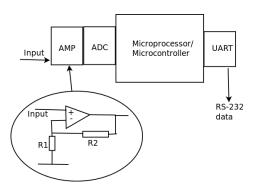

| 2.4 | System diagram of a milli-volt reader, showing an expanded circuit diagram for the component                |    |

|     | of interest                                                                                                 | 13 |

| 2.5 | FMEA UML data representation with subjective system level failure modes                                     | 23 |

| 3.1 | Distributed Control System FMEA signal path for a single input.                                             | 29 |

| 4.1 | Standard non inverting amplifier configuration                                                              | 32 |

| 4.2 | DAG representing a resistor and its failure modes.                                                          | 32 |

| 4.3 | Failure mode graph of the Potential Divider                                                                 | 33 |

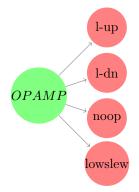

| 4.4 | DAG representing failure modes of an Op-amp                                                                 | 34 |

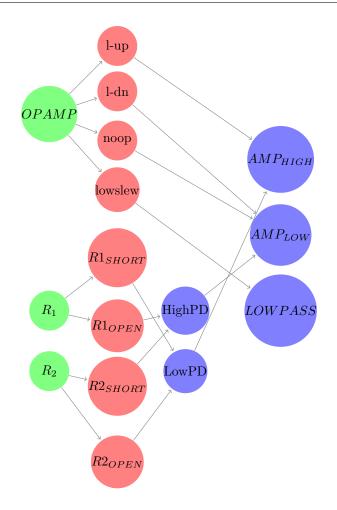

| 4.5 | Full DAG representing failure modes and base components of the Non Inverting Op-amp Circuit                 | 35 |

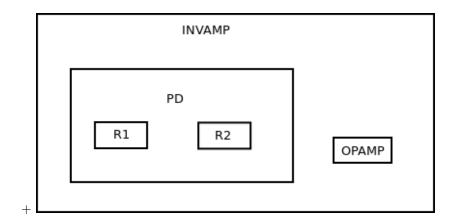

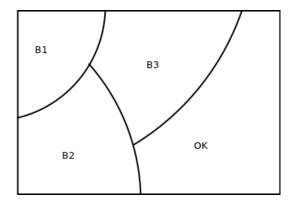

| 4.6 | FMMD analysis of the INVAMP represented as an Euler diagram, showing how the components                     |    |

|     | have been collected into functional groupings and then used as derived components to build the              |    |

|     | analysis hierarchy.                                                                                         | 36 |

| 4.7 | UML diagram of a component and its associated failure modes                                                 | 38 |

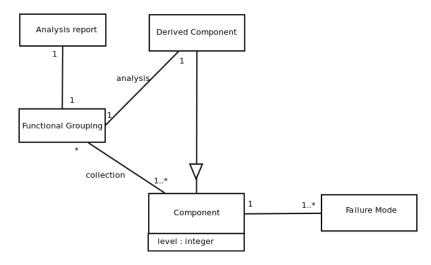

| 4.8 | Basic UML Meta model for FMMD hierarchy                                                                     | 39 |

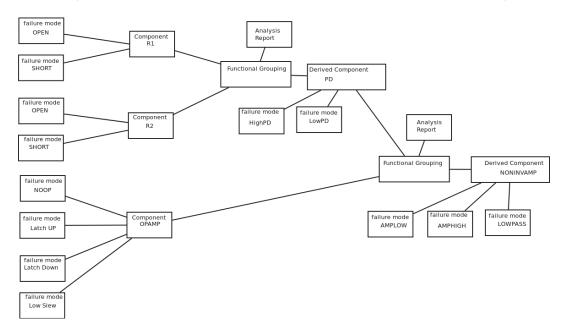

| 4.9 | Instance diagram for the NONINVAMP example                                                                  | 40 |

| 5.1 | Inverting Amplifier Configuration                                                                           | 44 |

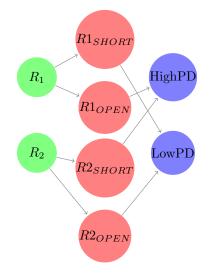

| 5.2 | Failure symptoms of the 'Inverted Potential Divider' $IPD$                                                  | 45 |

| 5.3 | Full DAG representing failure modes and symptoms of the Inverting Op-amp Circuit                            | 46 |

| 5.4 | Full DAG representing failure modes and symptoms of the Inverting Op-amp Circuit analysed in                |    |

|     | one stage                                                                                                   | 47 |

| 5.5 | Differencing Amplifier using two op-amps                                                                    | 49 |

| 5.6 | Directed Acyclic Graph of the two op-amp differencing amplifier failure modes $\ldots \ldots \ldots \ldots$ | 53 |

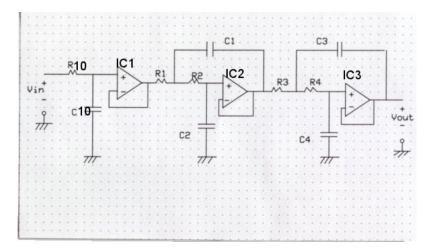

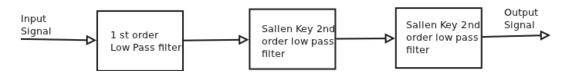

| 5.7 | Five Pole Low Pass Filter, using two Sallen Key stages and three op-amps. An example of FMMD                |    |

|     | applied to a multi-stage but linear signal path topology                                                    | 54 |

| 5.8 | Signal Flow through the five pole low pass filter                                                           | 54 |

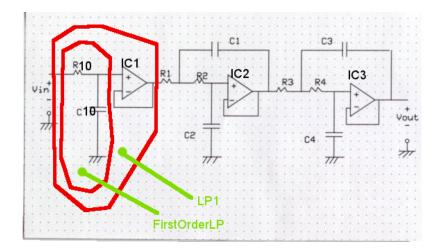

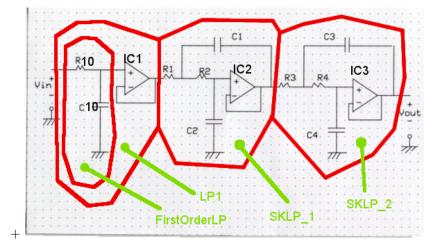

| 5.9  | Five Pole Sallen Key Filter: Circuit showing the first two functional groupings modelled as an                                                                                       |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Euler diagram super-imposed onto the electrical schematic.                                                                                                                           | 56 |

| 5.10 | Functional Groupings in Five Pole Low Pass Filter. Shown as an Euler diagram super-imposed                                                                                           |    |

|      | onto the electrical schematic.                                                                                                                                                       | 57 |

| 5.11 | Euler diagram showing functional grouping/derived component relationships for the analysis of                                                                                        |    |

|      | the Five Pole Sallen Key filter. This is an abstract version of figure 5.10 $\ldots$                                                                                                 | 57 |

| 5.12 | Circuit diagram for the Quad Op-Amp 'Bubba' Oscillator                                                                                                                               | 60 |

| 5.13 | Circuit 3: Electrical signal path block diagram of the 'Bubba' oscillator, showing the circular                                                                                      |    |

|      | circuit topology                                                                                                                                                                     | 60 |

| 5.14 | Euler diagram showing the hierarchy of the initial FMMD analysis performed on the Bubba                                                                                              |    |

|      | Oscillator circuit.                                                                                                                                                                  | 62 |

| 5.15 | Euler diagram showing functional groupings for the Bubba oscillator using a more decomposed approach.                                                                                | 63 |

| 5.16 | Sigma Delta Analogue to Digital Converter                                                                                                                                            | 65 |

| 5.17 | Electrical signal path Block diagram: $\Sigma \Delta ADC$                                                                                                                            | 65 |

| 5.18 | Euler diagram showing the initial derived components used to model the $\Sigma \Delta ADC$                                                                                           | 68 |

| 5.19 | Euler diagram showing the final derived components used to model the $\Sigma \Delta ADC$                                                                                             | 69 |

|      | Pt100 four wire circuit                                                                                                                                                              | 70 |

|      | Pt100 expected voltage ranges for a temperature range of $0^{\circ}$ to $300^{\circ}$                                                                                                | 71 |

|      | Voltage Divider                                                                                                                                                                      | 71 |

| 6.1  | Context Diagram for $4 \rightarrow 20mA$ loop                                                                                                                                        | 79 |

| 6.2  | Software Function: read_4_20_input()                                                                                                                                                 | 81 |

| 6.3  | Software Function: read_ADC()                                                                                                                                                        | 82 |

| 6.4  | Call tree for software example                                                                                                                                                       | 83 |

| 6.5  | Electronics and Software shown in an integrated failure mode model—an Euler diagram showing relationship between derived components determined from electronics and software—the two |    |

|      | outermost contours are software functions, and the inner two are electronic derived components.                                                                                      | 87 |

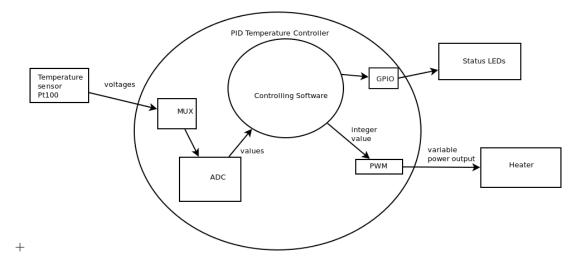

| 6.6  | Yourdon Context Diagram for a standalone micro-processor implemented PID Temperature Con-                                                                                            |    |

|      | troller                                                                                                                                                                              | 88 |

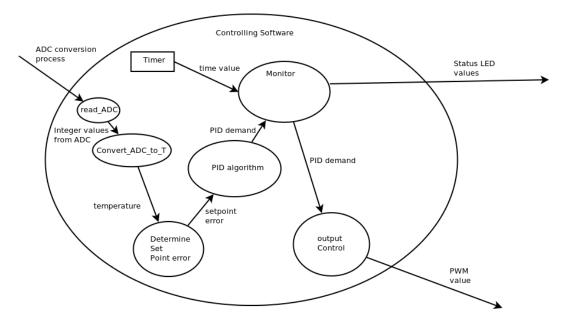

| 6.7  | Yourdon data flow diagram for PID Temperature Controller identifying initial processing nodes.                                                                                       | 88 |

| 6.8  | Final Yourdon data flow diagram which has defined the software functions for the PID tempera-                                                                                        |    |

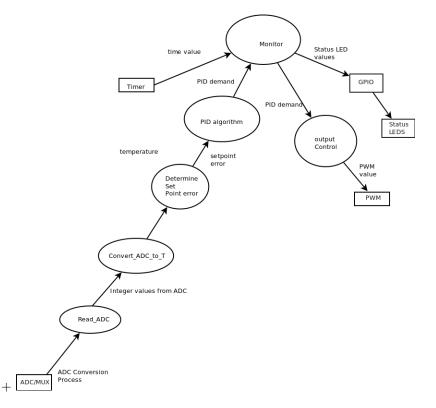

|      | ture controller                                                                                                                                                                      | 89 |

| 6.9  | Software: Yourdon data flow diagram converted to programatic call tree                                                                                                               | 90 |

| 6.10 | Euler diagram representing the hierarchy of FMMD analysis applied to the afferent branch of                                                                                          |    |

|      | call tree for the PID temperature controller example                                                                                                                                 | 94 |

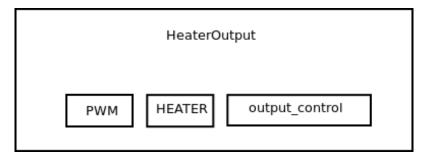

| 6.11 | Euler diagram showing HeaterOutput with its two hardware components, PWM and HEATER,                                                                                                 |    |

|      | and its software component <b>output_control()</b>                                                                                                                                   | 95 |

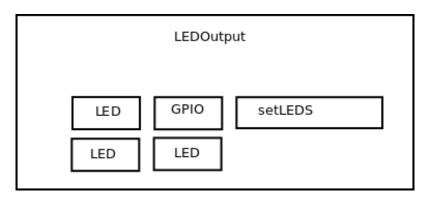

| 6.12 | Euler diagram showing LEDOutput with its three LEDs and GPIO hardware elements, and its                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | software component set<br>LEDS                                                                                                                                                                |

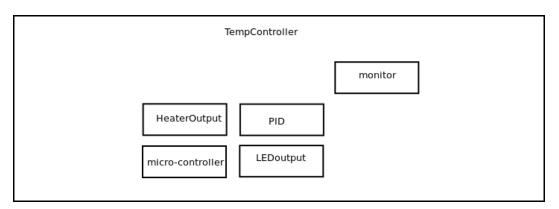

| 6.13 | $Euler\ diagram\ of\ the\ temperature\ controller\ final\ analysis\ stage,\ showing\ the\ hybrid\ software/hardware$                                                                          |

|      | derived components and the function at the head of the call tree <b>monitor()</b>                                                                                                             |

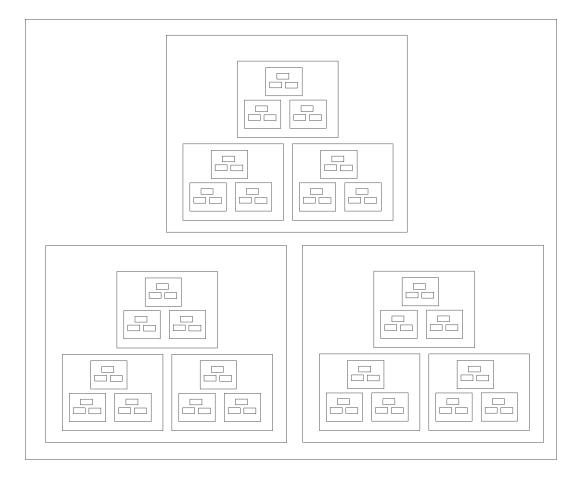

| 7.1  | Euler diagram of a hypothetical FMMD Hierarchy with 81 base components with the number of                                                                                                     |

|      | components in each $FG$ fixed to three $( FG  = 3) \dots $                              |

| 7.2  | XFMEA and FMMD reasoning distance comparison graph                                                                                                                                            |

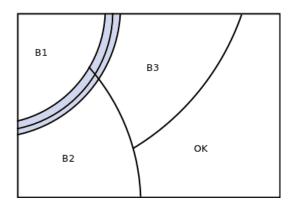

| 7.3  | Component with three failure modes as partitioned sets $\ldots \ldots \ldots$ |

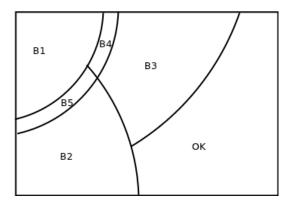

| 7.4  | Component with three failure modes where $B_1$ is independent                                                                                                                                 |

| 7.5  | Component with two new failure modes                                                                                                                                                          |

| 8.1  | FMMD UML diagram extended for potential compatibility with FTA: incorporating Environ-                                                                                                        |

|      | mental, Operational State and Inhibit gates                                                                                                                                                   |

| A.1  | Probablistic Fault Tree : Pt100 Single Faults                                                                                                                                                 |

# List of Tables

| 2.1  | LM358: EN298 Open and shorted pin failure symptom determination technique                                    |     |  |

|------|--------------------------------------------------------------------------------------------------------------|-----|--|

| 2.2  | Table adapted from EN61508-1:2001 [7.6.2.9 p33], showing statistical tolerance of 'dangerous fail-           |     |  |

|      | ures' to comply with a given SIL level                                                                       | 20  |  |

| 4.1  | Potential Divider: FMEA for single failures                                                                  | 33  |  |

| 4.2  | Non Inverting Amplifier: Failure Mode Effects Analysis: Single Faults                                        | 34  |  |

| 5.1  | Inverted Potential divider: Single failure analysis                                                          | 45  |  |

| 5.2  | Inverting Amplifier: Single failure analysis using the $IPD$ derived component $\ldots \ldots \ldots \ldots$ | 46  |  |

| 5.3  | Inverting Amplifier: Single failure analysis: 3 components                                                   | 48  |  |

| 5.4  | Second Amplifier $SEC\_AMP$ : Failure Mode Effects Analysis: Single Faults                                   | 50  |  |

| 5.5  | Difference Amplifier $DiffAMP$ : Failure Mode Effects Analysis: Single Faults $\ldots \ldots \ldots$         | 51  |  |

| 5.6  | FirstOrderLP: Failure Mode Effects Analysis: Single Faults                                                   | 55  |  |

| 5.7  | First Stage LP1: Failure Mode Effects Analysis: Single Faults                                                | 55  |  |

| 5.8  | Sallen Key Low Pass Filter SKLP: Failure Mode Effects Analysis: Single Faults                                | 56  |  |

| 5.9  | Five Pole Low Pass Filter: Failure Mode Effects $Analysis(FivePoleLP)$ : Single Faults                       | 58  |  |

| 5.10 | Pt100 FMEA Single Faults                                                                                     | 72  |  |

| 5.11 | Pt100 Maximum and Minimum Values                                                                             | 73  |  |

| 5.12 | Pt100 FMEA Double Faults                                                                                     | 75  |  |

| 6.1  | functional grouping $G_1$ : Failure Mode Effects Analysis                                                    | 84  |  |

| 6.2  | functional grouping $G_2$ : Failure Mode Effects Analysis                                                    | 85  |  |

| 6.3  | $G_3$ : Read_4_20(): Failure Mode Effects Analysis                                                           | 86  |  |

| 7.1  | Comparison Complexity figures for the first three examples in Chapter 5                                      | 106 |  |

| 7.2  | Complexity Comparison figures for the Bubba Oscillator FMMD example (see section 5.4). $\ldots$ 1            | 108 |  |

| 7.3  | Complexity Comparison figures for the $\Sigma \Delta ADC$ FMMD example (see section 5.5)                     | 109 |  |

| A.1  | PhaseShift: Failure Mode Effects Analysis: Single Faults                                                     | 127 |  |

| A.2  | Bubba Oscillator: Failure Mode Effects Analysis: One Large Functional Group                                  | 128 |  |

| A.3  | BUFF45: Failure Mode Effects Analysis                                                                        | 129 |  |

| A.4  | PHS135BUFFERED: Failure Mode Effects Analysis                                                                | 130 |  |

| A.5 PHS225AMP: Failure Mode Effects Analysis                                                            | 1 |

|---------------------------------------------------------------------------------------------------------|---|

| A.6 BUBBAOSC: Failure Mode Effects Analysis                                                             | 2 |

| A.7 Summing Junction Integrator $(SUMJINT)$ : Failure Mode Effects Analysis                             | 3 |

| A.8 High Impedance Signal Buffer : Failure Mode Effects Analysis                                        | 4 |

| A.9 $PD, IC3$ Digital level to analogue level converter: Failure Mode Effects Analysis                  | 5 |

| A.10 $IC4, CLOCK$ Digital Buffer: Failure Mode Effects Analysis                                         | 6 |

| A.11 $HISB, SUMJINT$ buffered integrating summing junction ( $BISJ$ ): Failure Mode Effects Analysis 13 | 7 |

| A.12 $DIGBUF$ , $DL2AL$ flip flop buffered ( $FFB$ ): Failure Mode Effects Analysis                     | 8 |

| A.13 $FFB$ , $BISJ \Sigma \Delta ADC(SDADC)$ : Failure Mode Effects Analysis                            | 9 |

| A.14 Read_Pt100: Failure Mode Effects Analysis                                                          | 0 |

| A.15 Get_Temperature: Failure Mode Effects Analysis                                                     | 1 |

| A.16 GetError: Failure Mode Effects Analysis                                                            | 2 |

| A.17 PID: Failure Mode Effects Analysis                                                                 | 3 |

| A.18 HeaterOutput: Failure Mode Effects Analysis                                                        | 4 |

| A.19 LEDOutput: Failure Mode Effects Analysis                                                           | 5 |

| A.20 Standalone temperature controller: Failure Mode Effects Analysis                                   | 6 |

| A.21 Fixed film resistor Failure In Time (FIT) assessment                                               | 7 |

| A.22 Bead type Thermistor Failure in time assessment                                                    | 8 |

| A.23 Pt100 FMEA Single Fault Statistics                                                                 | 8 |

|                                                                                                         |   |

# List of Algorithms

| 1 | Derive new 'Component' $DC$ from a given functional grouping $FG: D(FG) \ldots \ldots \ldots$ | 155 |

|---|-----------------------------------------------------------------------------------------------|-----|

| 2 | Determine Test Cases: dtc: (F) $\ldots$                                                       | 157 |

| 3 | Analyse Test Cases: atc(TC)                                                                   | 158 |

## Chapter 1

## Introduction

Increasingly society relies on automation in everyday life. Many automated systems have the potential to cause harm or even death should they fail. Safety assessment and certification is now required for almost all potentially dangerous equipment. As part of the assessment/certification process, typically a battery of tests is applied, examining features such as resistance to extremes of environment, Electro Magnetic Compatibility (EMC), endurance regimes and static testing. Static testing is at the theoretical, or design level, and involves looking at failure scenarios and trying to predict how systems would react. This thesis deals with one area of static testing, that of Failure Mode Effects Analysis (FMEA) [16], a commonly used technique that is a legal requirement for a wide range of equipment certification.

The ability to assess the safety of machinery has been a concern since the dawn of the industrial age [31, 52]. The philosophy behind safety measures has progressed over time and by World War Two concepts such as 'no single component failure should cause a dangerous system failure' [12] emerged [55][Ch.13]. Concepts such as these allow objective criteria of safety assessment. The 'no single failure' concept can be extended to double or even multiple failures being unacceptable as the cause of dangerous states. The concept of a double failure causing a dangerous condition being forbidden can be found in the legally binding European standard EN298<sup>1</sup> which came into force in 2006 [14]. More sophisticated statistically based standards, i.e EN61508 [95] and variants thereof, are based on statistical thresholds for the frequency of dangerous failures. For instance, acceptable maximum numbers of dangerous failures per billion hours of operation could be stated. Orders of failure rates can then be broadly categorised into Safety Integrity Levels (SIL) [89]. So for a maximum of 10 potentially dangerous failures per billion hours of operation a SIL level of 3, and so on in powers of ten. If SIL ratings can be determined, they can be matched against given risks. The more dangerous the consequences of failure the higher the SIL rating. A band-saw with one operative may require a SIL rating of 1, but systems such as nuclear power-stations or air-liners, with far greater consequences on dangerous failure, may require a SIL ratings of 4.

All of these risk assessment techniques are based on variations of Failure Mode Effect Analysis (FMEA), which has its roots in the 1940's mass production industry and was designed to save large companies money by

$<sup>^{1}</sup>$ EN298:2003 became a legal requirement for all new forced draft industrial burner controllers in 2006 within the European Union.

prioritising the most financially draining problems in a product. The FMEA of the 1940's has been refined and extended into four main variants. This thesis describes the refinements and additions made to FMEA to tailor them for military or statistically biased use. It then reveals common flaws which make them unsuitable for the higher safety requirements of the 21st century. Problems with state explosion in failure mode reasoning and the current difficulties of integrating software and hardware failure mode models [42] are the most obvious of these. These four current methodologies are described in chapter 2 and critically assessed in chapter 3. In chapter 4, a new methodology is proposed which addresses the state explosion problem and using contract programmed software, allows the modelling of integrated software/electrical systems. This is followed by two chapters showing examples of the new modular FMEA analysis technique (Failure Mode Modular De-Composition, FMMD) firstly looking at a variety of common electronic circuits and then at electronic/software hybrid systems.

### 1.1 Motivation

The motivation for this study came from two sources, one academic (the author's Software Engineering MSc project) and the other practical (the author is a practising embedded software engineer working with FMEA on safety critical burner systems).

MSc Project: Euler/Spider diagram Editor. The author had recently completed an MSc and the project was to create an Euler/Spider Diagram [47] editor in Java. This editor allowed the user to draw Euler/Spider diagrams, and could then represent these as abstract—i.e. mathematical—definitions. The primary motive for writing the Spider diagram editor was to provide an alternative to formal languages for software specification. An added attraction for using spider diagrams was that they could be used in proving logic and theorems [33, 32] in an intuitive way. Because of the author's daily work exposure to FMEA, it was natural to think of ways to apply formal languages and spider diagrams to failure mode analysis.