The HKU Scholars Hub The University of Hong Kong 香港大學學術庫

| Title       | Impacts of Ti content and annealing temperature on electrical properties of Si MOS capacitors with HfTiON gate dielectric |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Author(s)   | Ji, F; Xu, JP; Li, CX; Lai, PT; Chan, CL                                                                                  |  |  |  |

| Citation    | 2009 leee International Conference On Electron Devices And<br>Solid-State Circuits, Edssc 2009, 2009, p. 221-224          |  |  |  |

| Issued Date | 2009                                                                                                                      |  |  |  |

| URL         | http://hdl.handle.net/10722/126194                                                                                        |  |  |  |

| Rights      | Creative Commons: Attribution 3.0 Hong Kong License                                                                       |  |  |  |

# Impacts of Ti Content and Annealing Temperature on Electrical Properties of Si MOS Capacitors with HfTiON Gate Dielectric

F. Ji, J. P. Xu<sup>\*</sup>, C. X. Li, P. T. Lai<sup>\*</sup>, C. L. Chan

Abstract - HfTiON gate dielectric is fabricated by reactive co-sputtering method followed by annealing in  $N_2$  ambient. The effects of Ti content and annealing temperature on the performances of HfTiON gate-dielectric Si MOS devices are investigated. Experimental results indicate that gate capacitance is increased with increasing Ti content. However, when the Ti/Hf ratio exceeds ~1.75, increase of the gate capacitance becomes small. Surface roughness of the samples annealed at different temperatures is analyzed by AFM, and results show that high annealing temperature (e.g. 700 °C for 30 s) can produce smooth surface, thus resulting in low gate leakage current. Keywords: MOS capacitor, high-k dielectric, HfTiON

## I. INTRODUCTION

High-k gate dielectrics, such as HfO<sub>2</sub> [1, 2], ZrO<sub>2</sub> [3, 4], and LaO [5, 6], have been widely investigated as the potential replacement of SiO<sub>2</sub> for the forthcoming CMOS technology. Among various high-k candidates, HfO<sub>2</sub> receive more and more attention due to acceptable thermodynamic stability on Si surface [7] and relatively large bandgap (5.68 eV). However, its low crystallization temperature (~520°C [8]) restricts the post-deposition annealing which is important for avoiding high gate leakage current. It has been reported that the crystallization temperature can be increased through incorporating N into high-k films [9]. In addition, the reported relative permittivity of HfO2 and HfON is below 24, which limits further scaling of equivalent oxide thickness (EOT). Incorporation of Ti, whose oxide has a high k of  $50 \sim 80$  due to strong contribution from soft phonons [10, 11], is a possible approach to further increase the permittivity of hafnium-based oxides. However, as Ti content increases, the interface quality gradually deteriorates, resulting in an increase of gate leakage current due to the reaction between Ti and Si substrate [12]. In this work, influences of Ti content in

F. Ji is with Wuhan Institute of Technology & with Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China

J. P. Xu is with Department of Electronic Science & Technology, Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China \*E-mail: jpxu@mail.hust.edu.cn

C. X. Li, P. T. Lai and C. L. Chan are with Department of Electrical & Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong

\*E-mail: <u>laip@eee.hku.hk</u>

HfTiON film and post-deposition annealing (PDA) temperature on the electrical properties of MOS capacitor with HfTiON as gate dielectric are investigated, and suitable Ti content and annealing temperature are obtained by considering the interface quality and gate leakage properties.

## **II. EXEREMENTS**

MOS capacitors were fabricated on (100)-oriented n-type Si wafers. After the wafers were cleaned, they were dipped in diluted hydrofluoric for 60 s to remove natural oxide. Then, the Si wafers were immediately transferred to the vacuum chamber of a sputtering system. The HfTiN films with approximately same thickness were first deposited at room temperature hv co-sputtering of Hf target at a RF power of 25 W and Ti target at different DC powers of 16.5 W, 26.4 W, 33 W and 39.6 W (corresponding monitoring DC power is 13W, 22W, 28.5 W and 35.5 W respectively) in an Ar/N<sub>2</sub> = 24/6 ambient (denoted as P1, P2, P3 and P4 samples respectively). The ratio of Ti/Hf was calculated according to the deposition rates of TiN and HfN films, and listed in Table I. The PDA was performed in N<sub>2</sub> (500 ml/min) at 700 °C for 60 s to oxidize the HfTiN films by consuming the residual oxygen in the N2 ambient and annealing system. Then, Al was thermally evaporated and patterned using lithography technology as the gate electrode. Also, Al was evaporated as the back electrode of the MOS capacitors to decrease contact resistance. Finally, a forming-gas annealing was carried out at 400  $^{\circ}$ C for 25 min in N<sub>2</sub>/H<sub>2</sub> = 95/5. After analyzing the accumulation capacitances and leakage current of the samples, Ti target power of 33 W was determined to be suitable since both reasonable k value and acceptable gate leakage current can be obtained. Furthermore, influences of annealing temperature on the electrical properties of the sample prepared using Ti target DC power of 33 W were investigated, and a suitable annealing temperature of 700°C for 30 s was found.

TABLE I PREPARATION CONDITIONS FOR SAMPLES WITH DIFFERENT TI CONTENTS

| Sample    | P1   | P2   | P3   | P4   |

|-----------|------|------|------|------|

| Ti-target | 16.5 | 26.4 | 33   | 39.6 |

| power / W |      |      |      |      |

| Ti/Hf     | 0.43 | 0.85 | 1.75 | 2.83 |

High-frequency accumulation capacitance (HF, 1 MHz) and gate leakage current were measured at room temperature, and under light-tight and electrically shielded conditions. High-resolution transmission electron microscopy (TEM) was used to observe the cross section of the HfTiON/Si system, thus getting the physical thickness of the film and calculating equivalent oxide thickness (EOT). Surface roughness was evaluated using atomic force microscope (AFM).

# **III. RESULTS AND DISCUSSION**

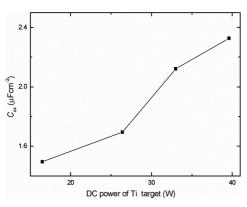

The HF accumulation capacitance  $C_{ox}$  of the samples is shown in Fig. 1. As can be seen, as Ti target power increases,  $C_{ox}$  is increased, which should be ascribed to the increase of k value due to Ti incorporation. Also, it can be noted that the  $C_{ox}$  difference between the P3 and P4 samples is smaller than that between P2 and P3, indicating a gradual saturation trend of k-value increase with Ti content, because the dielectric is closer to Ti-based oxide (TiO<sub>2</sub>: k = ~50) for high Ti content. A small difference of  $C_{ox}$  between the P1 and P2 samples is also observed because the dielectric with low Ti content behaves more like Hf-based oxide (k = 18 ~ 20) [12].

Fig.1 Dependence of Cox on Ti content

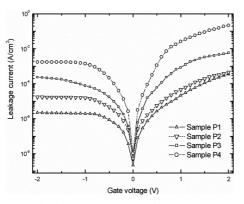

Gate leakage current density of the samples is shown in Fig. 2. Obviously, the higher the Ti content, the larger is the gate leakage current. This is because with more Ti incorporation, more reaction between Ti and Si could happen during PDA, resulting in rougher interface [12].

Fig. 2 Gate leakage current density versus gate voltage for MOS capacitors with different Ti contents

From Fig. 2, it can be seen that gate leakage current density of the P3 sample at  $V_g = 1$  V is  $\leq 10^{-3}$  Acm<sup>2</sup>.

Based on the above discussion, a Ti/Hf ratio of 1.75 (Ti-target DC power of 33 W) could be considered as a suitable option.

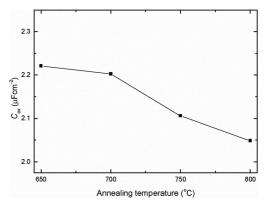

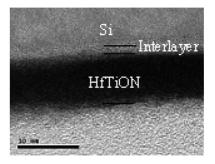

Furthermore, the electrical properties of the P3 sample are investigated by annealing it at different temperatures of 650 °C, 700 °C, 750 °C, and 800 °C respectively (denoted as T1, T2, T3 and T4 samples respectively). The extracted  $C_{ox}$ 's are shown in Fig 3. It is found that the higher the annealing temperature, the smaller the  $C_{ox}$  is. This is probably resulted from the growth of a HfTiSiON interlayer with smaller k value than HfTiON due to interdiffusions between the layers [12] during PDA, as shown by the TEM image of the T2 sample in Fig.4, with a ~1.2-nm interlayer.

Fig. 3  $C_{ox}$  of the samples as a function of PDA temperature

Fig.4 TEM image of the T2 sample annealed at 700  $^{\circ}$ C for 30 s

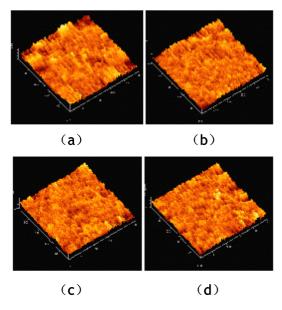

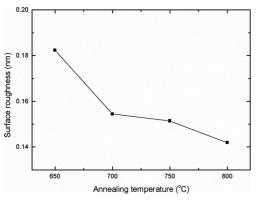

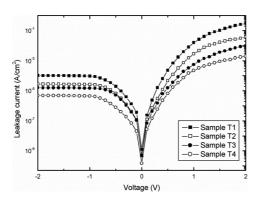

On the other hand, the gate leakage current is impacted by the roughness of the dielectric/gate interface [13] and denseness of the films. The surface roughness of the HfTiON films with different PDA temperatures is evaluated by means of AFM, as shown in Fig. 5, and extracted surface roughness is shown in Fig. 6. It can be seen that the surface roughness is decreased as PDA temperature increases, because higher PDA temperature could result in denser HfTiON film. Also, reduction of the roughness is large from 650 °C to 700 °C, and becomes small from 700 °C to 800 °C, implying that 700 °C should be high enough for densifying the film. The gate leakage current density of MOS capacitors with different PDA temperatures is shown in Fig. 7. Low gate leakage current is observed for the samples with high PDA temperatures, in good correlations with their small

Fig.5 AFM images  $(0.5 \times 0.5 \ \mu m^2)$  of the samples prepared using Ti target power of 33 W with different PDA temperatures of 650 °C (a), 700 °C (b), 750 °C (c), and 800 °C (d) respectively.

Fig.6 Surface roughness of the samples with different PDA temperatures

Fig. 7 Gate leakage current density of MOS capacitors with different PDA temperatures

surface roughness, high denseness of the HfTiON film and small interlayer thickness. Therefore, by considering both  $C_{ox}$  value and gate leakage current, the suitable annealing condition is 700  $^{0}$ C for 30 s.

## **IV. CONCLUSION**

HfTiON films with different Ti contents and PDA have been prepared by reactive temperatures co-sputtering of Hf and Ti targets. Experimental results show that high Ti content contributes to large gate capacitance due to increased k value of the HfTiON film, but however, the interface properties become poor with increase of Ti content. As a trade-off between k value and interface-state density, a Ti/Hf ratio of 1.75 is suitable in our study. On the other hand, the effects of the PDA temperature on the interlayer growth, surface roughness and thus gate leakage properties have been investigated. It is found that as the annealing temperature increases, k value is reduced due to thicker interlayer, and gate leakage current is decreased due to enhanced denseness of the film with smaller surface roughness. In order to obtain large gate capacitance and simultaneously maintain low gate leakage, the suitable PDA condition is 700°C for 30 s in N<sub>2</sub> ambient for Si MOS devices with HfTiON as gate dielectric.

#### ACKNOWLEDGES

This work is financially supported by Foundation of Hubei Provincial Department of Education (Grant no. Q20095001), the National Natural Science Foundation of China (Grant no. 60776016), and the University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong.

#### REFERENCES

- S. Pidin, Y. Morisaki, Y. Sugita, T. Aoyama, K. Irino, T. Nakamura, and T. Sugii, "Low standby power CMOS with HfO<sub>2</sub> gate oxide for 100-nm generation," *in VLSI symp. Tech. Dig.*, p. 28-29, 2002.

- [2] X. F. Yu, J. D. Huang, M. B. Yu, and C. X. Zhu, "Effect of gate dopant diffusion on leakage current in n+ ploy-Si/HfO<sub>2</sub> and examination of leakage paths by conducting atomic force microscopy," *IEEE Electron Device letters*, vol. 28, no. 5, p. 373-375, 2007.

- [3] Barshilia, C. Harish, B. Deepthi, and K. S. Rajam, "Stabilization of tetragonal and cubic phases of ZrO<sub>2</sub> in pulsed sputter deposited ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub>/Y2O<sub>3</sub> nanolayered thin films," *J. Appl. Phys.*, vol.104, p.113532-113532-12, 2008

- [4] Yao-Zhi Hu, and Sing-Pin, "Characterization of high-k dielectric ZrO<sub>2</sub> films annealed by thermal processing," *January of Vacuum Science & Technology B: Microelectronics and Nanometer Structures*, vol. 19 (5), p. 1706-1714, Sep 2001.

- [5] Suzuki Masamichi, Yamaguchi Takeshi, Fukushima Noburu, and Koyama. Masato, and "LaAlO<sub>3</sub> gate dielectric with ultrathin equivalent oxide thickness and ultrlow leakage current directly deposited on Si substrate," *J. Appl. Phys.*, vol. 103 (3), p. 034118-034122, Feb 2008.

- [6] Hongwei Chen, Chuanren Yang, Bo Wang, Hong Ji, and Jihua Zhang, "Structural, dielectric, and insulating properties of barium strontium titanate thin films grown on various oriented LaAlO<sub>3</sub> substrates," *J. Appl. Phys.*, vol. 105 (3), p. 034112-034116, Feb 2009.

- [7] K. J. Hubbard, and D. G. Schlom, "Thermodynamic stability of binary oxides in contact with silicon," J. Mater. Res., vol. 11 (11), p. 2757-2776, Nov. 1996.

- [8] R. Jiang, E. Q. Xie, and Z. F. Wang, "Interfacial chemical structure of HfO<sub>2</sub>/Si film fabricated by sputtering," *Appl. Phys. Lett.*, vol. 89, p. 142907, 2006.

- [9] C. H. Choi, T. S. Jeon, R. Clark, "Electrical properties and thermal stability of CVD HfO<sub>x</sub>N<sub>y</sub> gate dielectric with poly-Si gate electrode," *IEEE Electron Device Letters*, vol. 24 (4), p. 215-217, Apr. 2003.

- [10] C. Lee, P. Ghosez, X. Gonze, "Lattice dynamics and

dielectric properties of incipient ferroelectric TiO<sub>2</sub> rutile," *Phys Rev. B*, vol. 65, p. 13379, 1994.

- [11] F. Chen, X. Bin, C. Hella, X. Shi, W. L. Gladfelter, S. A. Campbell, "A study of mixtures of HfO<sub>2</sub> and TiO<sub>2</sub> as high-k gate dielectrics," *Microelectron Engineer.*, vol. 72, p. 263-266, April 2004.

- [12] M. Li, Z. Zhang, S. A. Campbell, W. L. Gladfelter, M. P. Agustin, D. O. Klenov, and S. Stemmer "Electrical and material characterizations of high-permittivity Hf<sub>x</sub>Ti<sub>1-x</sub>O<sub>2</sub> gate insulators," *Journal of Applied Physics*, vol. 98, p.054506, 2005.

- [13] Lingfeng Mao, Changhua Tan, and Mingzhen Xu, "Numerical analysis for root-mean-square roughness of SiO<sub>2</sub>/Si interface on direct tunneling current in ultrathin MOSFETs," *Solid-state Electron.*, vol. 45, p. 531-534, 2001.