The HKU Scholars Hub The University of Hong Kong 香港大學學術庫

| Title       | Improved performance for OTFT with HfTiO2 as gate dielectric by N2O annealing                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)   | Tang, WM; Cheng, KH; Leung, CH; Lai, PT; Xu, J; Che, CM                                                                                                                       |

| Citation    | The 2007 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Tainan, Taiwan, 20-22 December 2007. In Conference Proceedings, 2007, p. 189-192 |

| Issued Date | 2007                                                                                                                                                                          |

| URL         | http://hdl.handle.net/10722/97159                                                                                                                                             |

| Rights      |                                                                                                                                                                               |

# Improved Performance for OTFT with HfTiO<sub>2</sub> as gate dielectric by N<sub>2</sub>O annealing

# W.M. Tang, K.H. Cheng, C.H. Leung, P.T. Lai, J.P. Xu and C.M. Che

Abstract - OTFTs with  $HfTiO_2$  as gate dielectric have been successfully fabricated. The devices show small threshold voltage and subthreshold slope, and thus are suitable for low-voltage and low-power applications. This work also finds that OTFT with gate dielectric annealed in N<sub>2</sub>O has larger dielectric constant, smaller threshold voltage, smaller subthreshold slope and larger on/off ratio than the N<sub>2</sub>-annealed sample. This demonstrates that the N<sub>2</sub>O annealing is an important surface treatment for preparing a highquality insulator/organic interface.

## **I. INTRODUCTION**

Organic thin-film transistors (OTFTs) have attracted a great deal of interest in recent vears in the field of microelectronics and optoelectronics. They can be used to make sensors [1], flat-panel displays, low-end smart cards and electronic identification tags [2]. OTFTs based on polymers have several advantages and become a promising alternative to silicon-based transistors for many applications. They are particularly suitable for large-area and flexible electronics applications because organic semiconductors are strong, soluble and flexible. They can be deposited by spray coating and screen-printing, which are simple to process and can cover a large area. In addition, these processes can be done at low-temperature to minimize the production cost. Several organic semiconductors have been used to make OTFTs, such as pentacene, rubrene, pervlene, poly(3-hex-

W. M. Tang, K.H. Cheng, C. H. Leung P.T. Lai are with Department of Electrical and Electronic Engineering, the University of Hong Kong. J.P. Xu is with Department of Electronic Science & Technology, Huazhong University of Science and Technology, Wuhan. C.M. Che is with the Department of Chemistry, the University of Hong Kong E-mail: laip@eee.hku.hk ylthiophene) regioregular (P3HT) and dihexylquin-quethiophene (DH-5T). Among these organic materials, pentacene is commonly chosen as the active layer for making OTFT. It is because pentacene has a strong tendency to form molecular crystals and well-ordered film by evaporation which is an important factor for obtaining high carrier mobility [3, 4]. Moreover, pentacene is a p-type semiconductor, which is stable in air and less sensitive to moisture.

Silicon dioxide  $(SiO_2)$  and oxynitride have been traditionally used as the gate insulator They can be easily fabricated by in OTFT. conventional thermal oxidation and patterned by However, these kinds of photolithography. insulators are not very suitable for making highperformance OTFTs for high-speed and lowpower display driving circuits. The required insulator must be very thin in order to get high gate capacitance but scaling down the thickness of silicon dioxide creates a lot of problems such as high leakage current, intermixing of materials at the interfaces and direct tunneling in the thin film. In order to solve these problems, insulator with high dielectric constant (k) should be used. High-k materials can allow thicker physical thickness to suppress gate leakage current while maintaining a high gate capacitance to reduce the operating voltage of OTFT. Several high-k dielectrics have been employed to fabricate OTFT, for example  $HfO_2$  [5],  $Al_2O_3$  [6],  $TiO_2$  [7],  $Ta_2O_5$  [8] and  $BaTiO_3$  [9]. In this study, high-k dielectric material hafnium titanium oxide  $(HfTiO_2)$  is used as the gate insulator. The purpose of adding Ti into HfO<sub>2</sub> is to get higher dielectric constant while maintaining good thermal stability with Si [10]. As the interface between the organic layer and the gate insulator can greatly influence the performance of OTFT,

the high-k dielectric is annealed in nitrous oxide  $(N_2O)$  in order to improve its surface quality. The electrical characteristics of the devices are measured, and then used to calculate the carrier mobility, threshold voltage, sub-threshold slope and on-off ratio of the devices.

### **II. EXPERIMENTS**

N-type <100> Si wafers (resistivity of 0.2 - 0.5  $\Omega$ cm) were used in this study. The wafers were cleaned using the conventional RCA method followed by a 60-sec dip in 5% hydrofluoric acid to remove the native oxide. The wafers were then loaded into a Denton vacuum LLC Discovery 635 sputterer, which was then pumped down to  $2 \times 10^{-6}$  Torr. HfTiO<sub>2</sub> was then deposited at room temperature by cosputtering of hafnium metal (99.99 % purity) with a RF power of 25 W and titanium metal (99.995 % purity) with a DC current of 0.1 A in a mixed  $Ar/O_2$  ambient (Ar to  $O_2$  ratio = 8:1). One sample then underwent an annealing in a furnace at 700 °C in N<sub>2</sub>O for 10 min. For the purpose of comparison, a control sample with N2-annealed HfTiO<sub>2</sub> as gate dielectric was also fabricated. In order to use the substrate as the gate of the device, the back oxide was removed by using 20 % HF. A layer of 30-nm pentacene was then deposited onto the insulator by vacuum evaporation at  $10^{-6}$ Torr. The pentacene was purchased from Aldrich and used without further purification. The source and drain gold pads were then deposited on top of the organic layer by evaporation through a stainless steel mask with a channel length L of 30 µm and a channel width W of 200 µm. The structure of the high-k OTFT fabricated is shown in Fig. 1. In order to deduce the dielectric constant, capacitor structures were also fabricated

| Au |           | Au |

|----|-----------|----|

|    | Pentacene |    |

|    | HfTiO     |    |

|    | n-Si      |    |

Fig. 1 Structure of high-k OTFT

by evaporation of Al onto the dielectric films. The area of capacitors was  $7.85 \times 10^{-5}$  cm<sup>2</sup>. The capacitance-voltage (C-V) characteristics were measured by a HP4284A LCR meter and a HP4140B pA meter at 100 kHz. The current-voltage (I-V) characteristics were measured by a HP4156B semiconductor parameter analyzer. All measurements were conducted in a dark environment at room temperature. The final thickness of the oxide layers t<sub>ox</sub> was measured by an ellipsometer.

#### **III. RESULTS AND DISCUSSION**

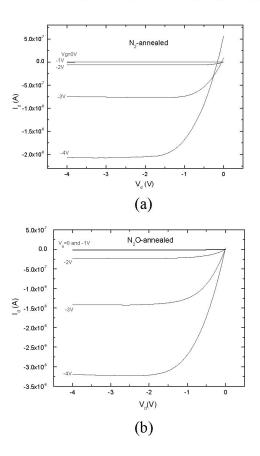

Fig. 2(a) and (b) show the drain current  $I_d$  versus drain voltage  $V_d$  characteristics of the OTFTs with insulator annealed in  $N_2$  and  $N_2O$  respectively. The operating principle of OTFT is similar to that of traditional MOSFET. OTFT with a p-type organic semiconductor (e.g. pentacene) as an active layer is called p-type OTFT. When a negative gate voltage  $V_g$  is appl-

Fig. 2  $I_d vs V_d$  characteristics for the OTFT with gate dielectric annealed in (a)  $N_2$  (b)  $N_2O$

applied to the p-type OTFT, positive charges or holes will accumulate at the insulator/organic interface. A conductive channel will be formed and the transistor is in the on state when the applied negative gate voltage is large enough to accumulate sufficient amount of holes in the channel. The voltage required to turn on an OTFT is called the threshold voltage V<sub>t</sub>. Current will flow through the channel from source to drain when a negative drain voltage is applied to the device. The drain current I<sub>d</sub> in the linear and saturation regions can be given by equations (1) and (2) respectively

$$I_{d} = \frac{W}{L} \mu C_{o} (V_{g} - V_{t} - \frac{V_{d}}{2}) V_{d}$$

(1)

$$I_{d} = \frac{W}{2L} \mu C_{o} (V_{g} - V_{t})^{2}$$

(2)

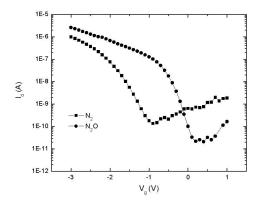

where  $C_o$  is the capacitance per unit area of the insulator, and  $\mu$  is the carrier mobility. Presented in Fig. 3 is the logarithmic plot of  $I_d$  versus  $V_g$  for the  $N_2$  and  $N_2$ O-annealed samples. The subthreshold slope (S) is a very important parameter for OTFTs used as switches because it shows the voltage needed to separate the on and off modes of the switch. The S parameter is defined as  $\frac{\partial V_g}{\partial \log_{10}(I_d)}$  which can be calculated

by taking the reciprocal of the steepest slope of the plot.

Fig. 3  $I_d$  vs  $V_g$  characteristics for the  $N_2$ -annealed and  $N_2O$ -annealed samples

The important parameters of the samples are summarized in Table 1. The N<sub>2</sub>O-annealed sample has higher dielectric constant and hence smaller threshold voltage than the N2-annealed sample. It is because during the N<sub>2</sub>O annealing, atomic N is decomposed from this nitridation gas and then diffuses into the oxide film. These N atoms can hinder the diffusion of O into the oxide, thus suppressing the formation of a low-k SiO<sub>2</sub> interlayer between the high-k dielectric and the substrate. The incorporation of nitrogen in the insulator can also passivate the insulator surface by forming strong triple bonds with the dangling bonds of silicon. These strong  $Si \equiv N$  bonds can improve the interfacial diffusion barrier, decrease the interfacial strain and remove fixed oxide charges. N<sub>2</sub>O nitridation can also reduce the traps and defects inside the oxide layer. Hence, the N<sub>2</sub>O-annealed samples show significant reduction in gate leakage current and great improvement in on/off or Ig/Id ratio. The subthreshold slope is also improved by the N<sub>2</sub>O annealing.

|                                 | Annealing gas  |                  |

|---------------------------------|----------------|------------------|

|                                 | N <sub>2</sub> | N <sub>2</sub> O |

| $C_o (\mu F/cm^2)$              | 0.531          | 0.599            |

| t <sub>ox</sub> (nm)            | 18.9           | 18.1             |

| k                               | 11.3           | 12.2             |

| $\mu$ (cm <sup>2</sup> /Vs)     | 0.24           | 0.22             |

| $V_t(V)$                        | -1.73          | -1.28            |

| S (V/decade)                    | 0.27           | 0.25             |

| on/off ratio (10 <sup>4</sup> ) | 7.1            | 17.5             |

| I <sub>d</sub> (μA)             | 2.33           | 4.58             |

| $(at V_g = V_d = -4V)$          |                |                  |

| I <sub>g</sub> (μA)             | 1.24           | 0.32             |

| $(at V_g = -4V, V_d = 0V)$      |                |                  |

| $I_g/I_d$                       | 53%            | 7%               |

Table 1 Device parameters of OTFTs with  $HfTiO_2$  as gate dielectric annealed in  $N_2$  and  $N_2O$  gas ambients

## **IV. CONCLUSION**

Organic thin-film transistor with high-k material  $HfTiO_2$  as gate insulator has been fabricated and studied. This study has

demonstrated the use of HfTiO<sub>2</sub> as gate dielectric can obtain low operating voltage and high switching speed. In addition, the gate leakage current and on/off ratio are greatly improved by the N<sub>2</sub>O annealing. The excellent electrical characteristics of the N<sub>2</sub>O-annealed sample are attributed to nitrogen incorporation in the gate insulator during nitridation, which can passivate the insulator surface to produce a better insulator/organic interface. In conclusion, N<sub>2</sub>Oannealed HfTiO<sub>2</sub> is a promising gate insulator for fabricating high-performance OTFTs.

## ACKNOWLEDGE

We would like to acknowledge the RGC of HKSAR, China (Project No. HKU 7133/07E), and the University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong..

# REFERENCES

[1] T. Zhu, J. T. Mason, R. Dieckermanm, G. G. Malliaras, "Humidity sensors based on pentacene thin-film transistor," Applied Phys. Lett., vol. 81, pp. 4643-4645, 2002.

[2] C. D. Dimitrakopoulos and D. J. Mascaro, "Organic thin-film transistor: A review of recent advances," IBM J. Res. Dev., vol. 45, pp. 11-37, 2001.

[3] Y.-Y. Lin, D. J. Gundlach, S. F. Nelson, and T. N. Jackson, "Stacked Pentacene Layer Organic Thin-film Transistors with Improved Characteristics," IEEE Electron Device Letters, vol. 18, No. 12, pp. 606-608, 1997.

[4] Y. Y. Lin, David J. Gundlach, Shlby F. Nelson, and Thomas N. Jackson, "Pentacene-Based Organic Thin-film Transistors," IEEE transactions on electron devices, vol. 44, no. 8, pp. 1325-1331, 1997.

[5] J. Tardy, M. Erouel, A. L. Deman, A. Gagnaire, V. Teodorescu, M. G. Blanchin, B.

Canut, A. Barau, and M. Vaharescu, "Organic thin film transistors with  $HfO_2$  high-k gate dielectric grown by anodic oxidation or deposited by sol-gel," Microelectronics reliability, vol. 47, pp. 372-377, 2007.

[6] J. B. Koo, J. W. Lim, S. H. Kim, S. J. Yun, H. K. Chan, S. C. Lim, J. H. Lee, "Pentacene thin-film transistors and inverters with plasmaenhanced atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> gate dielectric," Thin solid films, vol. 515, pp. 3132-3137, 2007.

[7] G. Wang, D. Moses, A. J. Heeger, H.-M. Zhang, M. Narasimhan, R. E. Demaray, "Poly(3-hexylthiophene) field-effect transistors with high dielectric constant gate insulator," J. Appl. Phys., vol. 95, pp. 316-322, 2004.

[8] C. Bartic, H. Jansen, A. Campitelli, S. Borghs, "Ta<sub>2</sub>O<sub>5</sub> as gate dielectric material for low-voltage organic thin-film transistors," Organic electronics, vol. 3, pp. 65-72, 2002.

[9] N. Hiroshiba, R. Kumashiro, K. Tanigaki, T. Takenobu, Y. Iwasa, K. Kotani, I. Kawayama, and M. Tonouchi, "Rubrene single crystal fieldeffect transistor with epitaxial BaTiO<sub>3</sub> high-k gate insulator," Applied Phys. Lett., vol. 89, pp. 152110-1-3, 2006.

[10] R. K. Nahar, Vikram Singh, Aparna Sharma, "Study of electrical and microstructure properties of high dielectric hafnium oxide thin film for MOS devices," J Mater Sci: Mater Electron 18, pp. 615-619, 2007.