| Title       | Electrical properties of HfTiON gate-dielectric metal-oxide-<br>semiconductor capacitors with different Si-surface nitridations |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| Author(s)   | Ji, F; Xu, JP; Lai, PT; Li, CX; Guan, JG                                                                                        |

| Citation    | Applied Physics Letters, 2007, v. 91 n. 5                                                                                       |

| Issued Date | 2007                                                                                                                            |

| URL         | http://hdl.handle.net/10722/57493                                                                                               |

| Rights      | Applied Physics Letters. Copyright © American Institute of Physics.                                                             |

## Electrical properties of HfTiON gate-dielectric metal-oxide-semiconductor capacitors with different Si-surface nitridations

F. Ji and J. P. Xu<sup>a)</sup> Department of Electronic Science & Technology, Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China

P. T. Lai<sup>b)</sup> and C. X. Li

Department of Electrical & Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong

J. G. Guan

State Key Laboratory of Advanced Technology for Materials Synthesis and Processing, Wuhan University of Technology, Wuhan 430070, People's Republic of China

(Received 4 April 2007; accepted 7 July 2007; published online 30 July 2007)

Electrical properties of HfTiON gate-dielectric metal-oxide-semiconductor (MOS) capacitors with different Si-surface nitridations in N<sub>2</sub>O, NO, and NH<sub>3</sub> prior to high-*k* film deposition are investigated and compared. It is found that the NO-nitrided sample exhibits low interface-state density and gate leakage current, and high reliability. This is attributed to formation of a SiON interlayer with suitable proportions of N and O. The MOS capacitor with Hf<sub>0.4</sub>Ti<sub>0.6</sub>O<sub>x</sub>N<sub>y</sub>/SiON gate dielectric stack (capacitance equivalent thickness of 1.52 nm and *k* value of 18.9) prepared by NO surface nitridation has an interface-state density of  $1.22 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> and gate leakage current density of  $6 \times 10^{-4}$  A cm<sup>-2</sup> ( $V_g$ =1 V). Moreover, only a small degradation of electrical properties after a stressing at 10 MV/cm for 3000 s is observed for the NO-nitrided sample. © 2007 American Institute of Physics. [DOI: 10.1063/1.2767177]

Development of high-k gate dielectric for future complimentary metal-oxide-semiconductor (CMOS) devices is indispensable for achieving both low leakage current and small equivalent oxide thickness.<sup>1</sup> Among various kinds of high-k materials, HfO<sub>2</sub> (Ref. 2) receives more and more attention for the forthcoming CMOS technology due to its good compatibility with Si, such as suitable band gap offset with Si and higher carrier mobility for Hf silicates compared with other high-k materials.<sup>3</sup> Addition of Ti in Hf oxide can form Hf/Ti-based oxide or oxynitride with higher k value because Ti oxide has higher k value than Hf oxide.<sup>4</sup> Therefore, it is expected that HfTiON used as the gate dielectric of a MOS device should increase its k value. In order to avoid the formation of a low-k interlayer between the high-k gate dielectric and Si substrate during deposition and postdeposition annealing, it is important to form an interlayer with suitable contents of N and O. In this work, nitridations of Si surface in N<sub>2</sub>O, NO, and NH<sub>3</sub> ambients prior to HfTiON deposition are investigated and compared. It is found that the NOnitrided Hf<sub>0.4</sub>Ti<sub>0.6</sub>O<sub>x</sub>N<sub>y</sub> gate-dielectric MOS capacitor exhibits excellent electrical properties and reliability, and gives a capacitance equivalent thickness (CET) of 1.52 nm and a k value of 18.9.

MOS capacitors with HfTiON as high-k gate dielectric were fabricated on (100)-oriented *n*-type Si wafers with a resistivity of 0.07  $\Omega$  cm. After RCA cleaning, the wafers were put in diluted HF for 1 min to remove the native SiO<sub>2</sub>. Surface pretreatment was performed at 700 °C for 1 min in N<sub>2</sub>O, NO, and NH<sub>3</sub> ambients (500 ml/min) (denoted as N<sub>2</sub>O, NO, and NH<sub>3</sub> samples, respectively). Then, the wafers were immediately transferred to the vacuum chamber of vacuum discovery deposition system made by Denton Corporation. A HfTiN film was deposited at room temperature by cosputtering of a Hf target at 25 W rf power and a Ti target at 33 W dc power in an  $Ar/N_2=24/6$  ambient, with 60 mTorr igniting pressure and 6.6 mTorr sputtering pressure. Next, the samples were transferred in air to a postdeposition annealing (PDA) system. The PDA was performed in N<sub>2</sub> (500 ml/min) at 700 °C for 30 s to transform HfTiN into HfTiON by consuming the residual oxygen in the  $N_2$ ambient<sup>5</sup> and PDA system. Control sample with surface pretreatment in N<sub>2</sub> was also fabricated with the same sputtering and PDA conditions. Al was thermally evaporated and patterned using lithography technology as the gate electrode with an area of  $7.85 \times 10^{-5}$  cm<sup>2</sup>. Also, Al was evaporated as the back electrode of the MOS devices to decrease contact resistance. Finally, all samples were annealed at 400 °C in forming gas  $(N_2/H_2=95/5)$  for 25 min.

High-frequency (1 MHz) *C-V* curves were measured at room temperature using HP4284A precision *LCR* meter. Flatband voltage ( $V_{\rm fb}$ ) and oxide-charge density ( $Q_{\rm ox}$ ) were extracted from the high-frequency *C-V* curves. The interfacestate density ( $D_{\rm it}$ ) at midgap was also extracted from the high-frequency *C-V* curve using the Terman method.<sup>6</sup> Highfield stress (10 MV/cm for 3000 s), with the capacitors biased in accumulation by HP4156A precision semiconductor parameter analyzer, was used to examine device reliability in terms of flatband-voltage shift ( $\Delta V_{\rm fb}$ ) and gate-leakage increase. All measurements were carried out under a light-tight and electrically shielded condition.

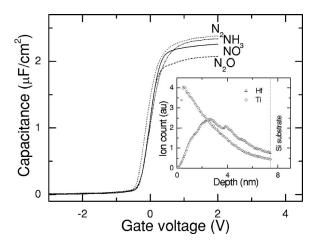

The *C*-*V* curves of the samples with different surface nitridations are measured, as shown in Fig. 1. The NO and  $N_2O$  samples exhibit smaller accumulation capacitance than

91. 052902-1

<sup>&</sup>lt;sup>a)</sup>Authors to whom correspondence should be addressed; electronic mail: jpxu@mail.hust.edu.cn

<sup>&</sup>lt;sup>b)</sup>Electronic mail: laip@eee.hku.hk

<sup>© 2007</sup> American Institute of Physics

FIG. 1. High-frequency *C*-*V* curves of MOS capacitors with different Sisurface nitridations. The insert shows the SIMS depth profiles of Ti and Hf in the NO sample.

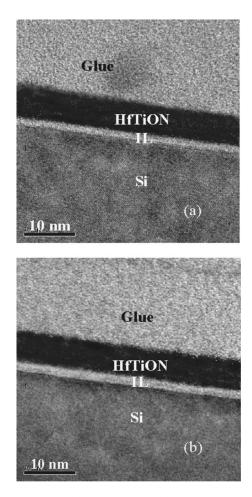

the control and NH<sub>3</sub> samples, with accumulation capacitance of the NO sample being slightly larger than that of the N<sub>2</sub>O sample. This is because the oxidation and nitridation roles of NO are, respectively, weaker and stronger than those of N<sub>2</sub>O, resulting in thinner interlayer and more nitrogen incorporation in the NO sample than in the N<sub>2</sub>O sample, as can be seen from the Transmission Electron Microscopy (TEM) images in Fig. 2. The higher nitrogen content is favorable for preventing the growth of low-*k* oxide during the subsequent PDA.<sup>7,8</sup> On the other hand, since the NH<sub>3</sub> sample has the

FIG. 2. TEM image of (a) NO sample and (b)  $N_2O$  sample, with an interlayer thickness of 13 and 1.5 nm, respectively.

TABLE I. Electrical properties of MOS capacitors with different Si-surface pretreatments.

| Sample                                         | NO    | N <sub>2</sub> O | $N_2$ | NH <sub>3</sub> |

|------------------------------------------------|-------|------------------|-------|-----------------|

| $D_{\rm it} (10^{11} {\rm ~cm^{-2}  eV^{-1}})$ | 1.22  | 4.1              | 8.0   | 6.4             |

| $V_{\rm fb}~({ m V})$                          | -0.09 | -0.10            | -0.19 | -0.08           |

| $Q_{\rm ox}~(10^{11}~{\rm cm}^{-2})$           | 4.7   | 5.7              | 18.7  | 3.4             |

| CET (nm)                                       | 1.52  | 1.66             | 1.45  | 1.48            |

strongest nitridation effect and the control sample has no intended growth of interlayer, they have larger accumulation capacitance and thus smaller CET.

Electrical parameters of the samples are extracted from the HF C-V curves and listed in Table I. The equivalent  $(Q_{\alpha x})$ including fixed-oxide charge, border-trap charge, mobile-ion, and interface-state charges, is calculated according to  $Q_{\rm ox} = -C_{\rm ox}(V_{\rm fb} - \varphi_{\rm ms})/q$ , where  $\varphi_{\rm ms}$  is the work-function difference between aluminum and Si substrate. The NO sample shows the lowest interface-state density. This should be attributed to the fact that with its weaker oxidation role, the NO surface nitridation can more easily form a stoichiometric SiON interlayer by providing suitable proportions of N and O compared to the N<sub>2</sub>O surface nitridation. As shown by the secondary-ion mass spectroscopy (SIMS) profile in the insert of Fig. 1, there is a Hf-rich region with less Ti near the interface, thus suppressing the possible effects of Ti on the interlayer due to possible reaction between Ti and Si.<sup>9</sup> As a result, better interfacial properties are obtained. An average Hf/Ti ratio of about 0.4/0.6 is obtained from the inset, which is basically consistent with that obtained from the deposition rates of Hf and Ti, and such high Ti content contributes to the larger equivalent k value of the HfTiON/SiON/Si system, e.g., k=18.9 for the NO sample. However, the NO and N<sub>2</sub>O samples have slightly larger CET  $(CET = k_0 k_{SiO_2} / C)$ , where  $k_0$  and  $k_{SiO_2}$  are permittivity of vacuum and dielectric constant of  $SiO_2$ , respectively; C is accumulation capacitance per unit area, as shown in Fig. 1) than the control and NH<sub>3</sub> samples due to the oxidation role of NO and  $N_2O$ . It is worth pointing out that the smallest values of  $Q_{\rm ox}$  and  $V_{\rm fb}$  for the NH<sub>3</sub> sample probably arise from a compensation effect between the negative charges of hydrogen-related electron traps and the positive fixed charges associated with N incorporation.<sup>10</sup>

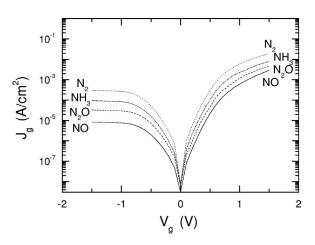

FIG. 3. Gate leakage current density of MOS capacitors with different Si-

ayer thickness of 13 and 1.5 nm, respectively. Downloaded 27 Apr 2009 to 147.8.17.95. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

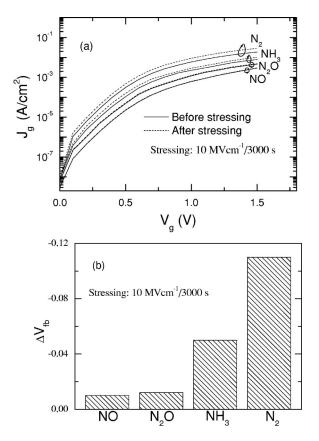

FIG. 4. (a) Increase of gate leakage and (b) shift of flatband voltage of MOS capacitors after a high-field stressing at 10 MV/cm for 3000 s, with the samples biased in accumulation.

The gate leakage currents of different samples are shown in Fig. 3. The NO and control samples have the smallest and largest leakage currents  $(7 \times 10^{-6} \text{ and } 2.7 \times 10^{-4} \text{ A cm}^{-2} \text{ for} V_g = -1 \text{ V}; 6 \times 10^{-4} \text{ and } 5.9 \times 10^{-3} \text{ A cm}^{-2} \text{ for } V_g = 1 \text{ V})$  respectively. Obviously, this is associated with the low/high oxide-charge and interface-state densities of the former and latter samples, respectively. The large  $D_{it}$  of the control sample is due to the formation of an unpassivated HfTiON/Si interface without a SiON interlayer. For the NH<sub>3</sub> sample, large gate leakage current results from the high interface-state density and a large amount of hydrogenrelated electron traps induced by the NH<sub>3</sub> nitridation.<sup>11</sup>

A high-field stress at 10 MV/cm [= $(V_g - V_{fb})$ /CET] for 3000 s is used to examine the reliability of the samples. Increase of leakage current and flatband voltage ( $\Delta V_{fb}$ ) are

measured after the stress, and are shown in Fig. 4. The NO and control samples have the smallest and largest increase of leakage current and  $\Delta V_{\rm fb}$ , indicating that the NO sample has the best reliability due to the largest incorporation of nitrogen in the interlayer of NO sample, i.e., near/at the SiON/Si interface.

Si-surface nitridations in N<sub>2</sub>O, NO, and NH<sub>3</sub> prior to high-*k* film deposition are employed to improve the electrical properties of MOS capacitors with HfTiON high-*k* gate dielectric. The experimental results show that the NO-nitrided sample exhibits excellent interface properties, low gate leakage current, and high device reliability. The involved mechanism lies in the formation of a stoichiometric SiON interlayer. An interface-state density of  $1.22 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>, a gate leakage current density of  $6 \times 10^{-4}$  A cm<sup>-2</sup> for  $V_g$ =1 V, a CET of 1.52 nm, and a *k* value of 18.9 are obtained for the MOS capacitor with Hf<sub>0.4</sub>Ti<sub>0.6</sub>O<sub>x</sub>N<sub>y</sub>/SiON gate dielectric stack prepared by the Si-surface nitridation in NO. Therefore, the surface nitridation in NO is a promising technique for preparing small-sized MOS field-effect transistors with excellent electrical performance and high reliability.

The authors would like to thank Supratic Chakraborty for his kind help on SIMS analysis. This work is financially supported by the National Natural Science Foundation of China (Grant No. 60376019) and Open Foundation of State Key Laboratory of Advanced Technology for Materials Synthesis and Processing (Project No. WUT2006M02).

- <sup>1</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

- <sup>2</sup>B. H. Lee, L. Kang, W. J. Qi, R. Nieh, Y. Jeon, K. Onishi, and J. C. Lee, Tech. Dig. - Int. Electron Devices Meet. **1999**, 133.

- <sup>3</sup>X. F. Yu, M. B. Yu, and C. X. Zhu, IEEE Electron Device Lett. **27**, 498 (2006).

- <sup>4</sup>J. Mcpherson, J. Kim, A. Shanware, H. Mogual, and J. Rodriguez, Tech. Dig. - Int. Electron Devices Meet. **2002**, 633.

- <sup>5</sup>K. Muraoka, 13th IEEE International Conference on Advanced Thermal Processing of Semiconductors, 2005, p. 37.

- <sup>6</sup>L. M. Terman, Solid-State Electron. 5, 285 (1962).

- <sup>7</sup>T. Hori, H. Iwasaki, and K. Tsuji, IEEE Trans. Electron Devices **36**, 340 (1989).

- <sup>8</sup>R. P. Vasquez and A. Madhukar, Appl. Phys. Lett. 47, 998 (1985).

- <sup>9</sup>S. A. Campbell, H. S. Kim, D. Gilmer, B. He, T. Ma, and W. L. Gladfelter, IBM J. Res. Dev. **43**, 383 (1999).

- <sup>10</sup>T. Hori, H. Iwasaki, Y. Naito, and H. Esaki, IEEE Trans. Electron Devices ED-34, 2238 (1987).

- <sup>11</sup>S. T. Chang, N. M. Johnson, and S. A. Lyon, Appl. Phys. Lett. **44**, 316 (1984).