| Title       | An economical fabrication technique for SIMOX using plasma immersion ion implantation                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)   | Min, J; Chu, PK; Cheng, YC; Liu, JB; Iyer, SSK; Cheung, NW                                                                                                          |

| Citation    | Proceedings of the 4th International Conference on Solid-State<br>and Integrated-Circuit Technology, ICSICT '95, Beijing, China,<br>October 24-28, 1995, p. 253-256 |

| Issued Date | 1995                                                                                                                                                                |

| URL         | http://hdl.handle.net/10722/54229                                                                                                                                   |

| Rights      | Creative Commons: Attribution 3.0 Hong Kong License                                                                                                                 |

# AN ECONOMICAL FABRICATION TECHNIQUE FOR SIMOX USING PLASMA IMMERSION ION IMPLANTATION

J. MIN, P. K. CHU, Y. C. CHENG Department of Physics & Materials Science, City University of Hong Kong, Hong Kong

J. B. LIU, S. S. K. IYER, N. W. CHEUNG

Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720, USA

## ABSTRACT

Buried oxide layers in Si were fabricated using non-mass analyzed plasma immersion ion implantation (PIII). The implantation was carried out by applying a large negative bias to a Si wafer immersed in an oxygen plasma and a dose of  $3 \times 10^{17}$  cm<sup>-2</sup> of oxygen was implanted in about three minutes. Cross section transmission electron microscopy (XTEM) and Rutherford backscattering spectrometry (RBS) were used to characterize the wafers. Our results indicate that a continuous buried oxide layer with a single crystal silicon overlayer was synthesized.

# INTRODUCTION

The advantages of using devices fabricated on silicon on insulator (SOI) wafers are well documented [1]. The low power requirements and device scaling to sub 0.25  $\mu$ m minimum dimensions required for future integrated circuit devices appear to necessitate the use of SOI wafers in order to attain the required level of performance in speed, device isolation and short channel effects [2].

Separation by implantation of oxygen (SIMOX) is one of the most widely used SOI materials for IC fabrication today. In this process, oxygen is implanted into a silicon wafer to the required depth and the wafer is then annealed at a temperature of 1300°C or higher for about 6 hours. If the oxygen dose is high enough, the nucleated oxide precipitates ripen and form a buried oxide layer of the desired thickness under the Si surface layer with atomically sharp and smooth surfaces [1]. The silicon surface can be prevented from amorphization by holding the wafer temperature above 600°C during implantation. One of the principal reasons for the high cost of the SIMOX wafers is the long time required during the implantation step which limits the throughput.

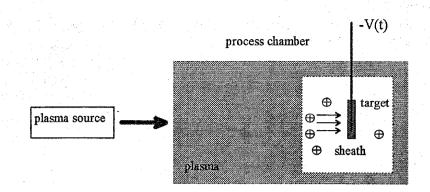

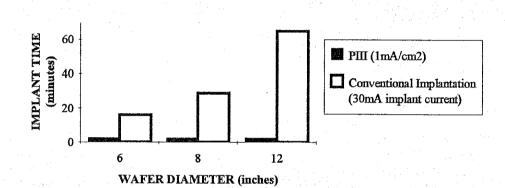

In this paper, we describe an alternative method for SIMOX fabrication using plasma immersion ion implantation (PIII). In PIII, implantation is performed by immersing the whole wafer in an oxygen plasma while applying a negative bias on the wafer [3] (Figure 1). The applied bias determines the depth to which the oxygen ions are implanted. The inherent advantage of this process is that the rate of implantation is limited only by the heat dissipation capability of the wafer holder and the current limitation of the power supply, but does not depend on the scanning speed, as in a conventional implanter. Therefore, in the PIII process, the implantation time is independent of the wafer area (Figure 2). This is important considering the increasing size of wafers used in the IC industry.

(0 - 7803 - 3062 - 5)

Figure 1: Schematic diagram of plasma immersion ion implantation (PIII)

Figure 2: Comparison of the implantation time for a  $1 \times 10^{18}$  cm<sup>-2</sup> O<sup>+</sup> implant by PIII with a current density of 1mA cm<sup>-2</sup> with that required by a high-current conventional implant with an ion current of 30 mA.

## **EXPERIMENTAL**

254

The oxygen implantation was performed using a prototype PIII reactor developed in the Plasma Assisted Materials Processing Laboratory at U.C. Berkeley [3]. The ECR source for the oxygen plasma was excited with 2.45 GHz microwaves with input power of 200-300 W. The implantation was carried out at a substrate bias of -50 kV. The wafer temperature during the implantation was above  $600^{\circ}$ C as measured with a pyrometer. The nominal implantation time was 3 minutes for an oxygen dose of 3 x  $10^{17}$  cm<sup>-2</sup>. The implanted oxygen profile was characterized by RBS.

The implanted wafer was annealed at 1270°C for 2 hours in a nitrogen ambient. Before annealing, the wafer was capped with silicon nitride to prevent surface oxidation during the high temperature step. The annealed sample was analyzed by XTEM to reveal the buried oxide.

### **RESULTS AND DISCUSSION**

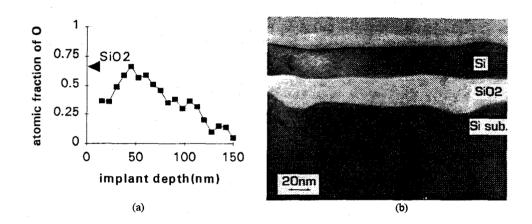

The as-implanted oxygen profile was studied by RBS (Figure 3a). Comparing the depth of the oxygen peak with theoretical projected range values calculated by the Monte Carlo simulator TRIM (version 90.05), it is clear that  $O_2^+$  was the dominant species implanted. The peak concentration of oxygen corresponds to an atomic fraction value of 0.67.

Due to the high concentration of oxygen at the peak, oxide nucleation was initiated during the subsequent thermal treatment. By annealing the sample at 1250°C for two hours, the oxide precipitates ripened and formed a continuous buried oxide (Figure 3b). The high resolution XTEM micrograph depicts a single-crystal silicon surface-layer, verifying that holding the wafer temperature above 600°C during implantation was effective in preserving the crystallinity of the top Si layer.

Figure 3: (a) Oxygen depth profile determined by RBS in a silicon wafer implanted with 3 x  $10^{17}$  cm<sup>-2</sup> oxygen at 50kV. (b) XTEM micrograph of the sample after annealing at 1270°C for 2 hours depicting a continuous buried oxide layer.

Our results demonstrate that PIII is potentially a viable technique for the commercial production of thin SIMOX wafers. The implantation time for a 300-mm silicon wafer is less than 3 minutes, as compared to over an hour required by a conventional ion implanter with a current of 30mA. The implantation time could be further reduced by improving the heat sink and temperature control of the wafer and by better controlling the ion species in the plasma to get negligible  $O^+$  ions.

PIII is an alternative high-throughput method for making SOI. The implantation time, which is independent of the wafer area, is an order of magnitude lower than that required by conventional beamline ion implantation. Owing to the increased throughput and the lower cost of the implanter, the PIII process is a potential candidate for the economical production of SOI substrates.

#### ACKNOWLEDGMENT

Our thanks to Dr. Kin Man Yu for making the RBS measurements on our implanted samples. This work is sponsored in part by the Joint Services Electronics Program, Contract Number F49620-94-C-0038 and National Science Foundation, Grant Number ECS-9202993.

## REFERENCES

- [1] J.-P. Colinge, <u>Silicon-on-Insulator Technology: Materials to VLSI</u>, (Khuwer Academic Publisher, Boston, 1991).

- [2] T. Tsuchiya, T. Ohno and Y. Kado, in <u>Silicon-On-Insulator Technology and Devices</u>, edited by Sorin Cristoloveanu (The Electrochemical Society Inc., Pennington, New Jersey, 1994) pp 401-412.

- [3] N. W. Cheung, Nuclear Instruments and Methods in Physics Research B, 51, 811 (1991).