# Portland State University PDXScholar

Dissertations and Theses

Dissertations and Theses

1-1-2010

# Library Characterization and Static Timing Analysis of Single-Track Circuits in GasP

Swetha Mettala Gilla Portland State University

# Let us know how access to this document benefits you.

Follow this and additional works at: http://pdxscholar.library.pdx.edu/open access etds

#### Recommended Citation

Mettala Gilla, Swetha, "Library Characterization and Static Timing Analysis of Single-Track Circuits in GasP" (2010). Dissertations and Theses. Paper 273.

10.15760/etd.273

This Thesis is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact pdxscholar@pdx.edu.

# Library Characterization and Static Timing Analysis of Single-Track Circuits in GasP

by

Swetha Mettala Gilla

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science in Electrical and Computer Engineering

> Thesis Committee: Xiaoyu Song, Chair Douglas V. Hall Christof Teuscher Marly Roncken

Portland State University ©2010

#### Abstract

Library characterization and 'Static Timing Analysis' (STA) are widely used in the design of modern CMOS integrated circuits to confirm that critical timing constraints are met. While many commercial tools are available to do timing validation using library characterization and static timing analysis, their operation depends on calculations relative to a global synchronous clock. This thesis applies timing validation to circuits from which the global synchronous clock is absent, making application of commercial tools difficult. Previous work at the University of Southern California (USC) showed how to overcome the incompatibility of commercial STA tools for asynchronous circuits. This thesis shows how to overcome the incompatibility of library characterization for asynchronous circuits, and ties the results to the STA solution of USC.

The particular family of circuits considered in this thesis is called GasP. GasP circuits are light in area and power, and have demonstrated operation at about twice the throughput one would expect from conventional clocked circuits. This makes GasP an ideal candidate for modern network-on-chip and system-on-chip architectures. In part, GasP circuits achieve their performance advantages by using a 'single-track' signaling protocol. Two GasP modules communicate with each other over a single wire. One module drives the wire up and a second module at the other end of the wire drives the wire down. This conflicts with the common assumption that wires are driven only from one end. As a result, special circuitry is needed to characterize a GasP library module. This thesis shows how to break a GasP module and its timing constraints into manageable pieces and how to simulate and collect the data relevant for characterization and static timing analysis. When combined with software tools for identifying the critical timing constraints, these thesis results will provide confidence in the correct operation of GasP.

### Acknowledgements

This work was partly sponsored under DARPA grant number HR0011-10-1-0069 for "Fleet Studies". In addition to DARPA, I would like to thank all the people who have helped and inspired me during my thesis work.

I especially want to thank my advisor, Drs. Marly Roncken, for her guidance during my research and study at Portland State University (PSU). Her perpetual energy and enthusiasm in research were a great motivation to me. She was always accessible and willing to help me with my research. She is the greatest personality I ever met in my 24 years life time. I admire her personality after Swami Vivekananda.

I was delighted to interact with Dr. Ivan Sutherland. It was a great opportunity to participate in his seminars on GasP circuits, and an even greater opportunity to get the chance to work with him on a timing flow for these circuits. His insight in asynchronous circuit design is amazing. He explains anything that looks like "eschew obfuscation" into something as obvious as "keep it simple".<sup>0.1</sup> To me, he defines what a world-class researcher and teacher are about.

The GasP seminar class and my research with Marly and Ivan at the Asynchronous Research Center (ARC) were both a turning point in my life and a wonderful experience. The chance to publish and present my research work at the ASYNC 2010 conference

<sup>&</sup>lt;sup>0.1</sup>The text "eschew obfuscation" is on one of his sweatshirts.

in Grenoble, France, broadened my view of the world, and enabled me to meet other researchers and students working in the domain of asynchronous circuits.

I am much obliged to Professor Xiaoyu Song, for agreeing to be my thesis advisor. One simply could not wish for a more friendly and understanding advisor. I feel blessed by his encouragement to pursue this thesis topic, and to help me plan it. Professor Douglas V. Hall, and Professor Christof Teuscher deserve special thanks as my thesis committee members. I sincerely appreciate their participation and technical feedback.

I want to thank Prasad Joshi, Mallika Prakash, and Professor Peter Beerel from the University of Southern California (USC), for making their static timing analysis flow available, and for sending me their publications and any scripts they could officially provide. The USC flow became the basis for my thesis. I am particularly grateful to Prasad for being so patient in replying to my string of emails with questions, even during the busy time before his wedding.

I would also like to thank my first manager at PSU, Lisa Weldon, for her support in providing me with a student job during my initial struggling days at PSU when finances were tight. My one year stint at HAL India opened my mind and motivated me to attend graduate school. I would like to thank the friends from my college years in India, in particular my badminton friends "6STARS", and my close friend in Portland: Laddu.

My deepest gratitude goes to my family for their unflagging love and support. Without them, this thesis would simply not exist. I am indebted to my mother, Indira Bai, for her care and love. She is simply perfect. I have no suitable words to describe her everlasting love to me. I remember her support when I encountered difficulties, and I am daily reminded of her delicious dishes now that I do my own cooking. I thank my father, Gopal Reddy, for believing in me and for supporting my study and career decisions.

# Contents

| Al | ostrac           | et                                                     | j  |  |

|----|------------------|--------------------------------------------------------|----|--|

| Ac | Acknowledgements |                                                        |    |  |

| Li | st of l          | Figures                                                | xi |  |

| 1  | INT              | RODUCTION                                              | 1  |  |

|    | 1.1              | GasP Circuits                                          | 2  |  |

|    | 1.2              | Timing Validation Flow                                 | 4  |  |

|    | 1.3              | Reading Guide                                          | 6  |  |

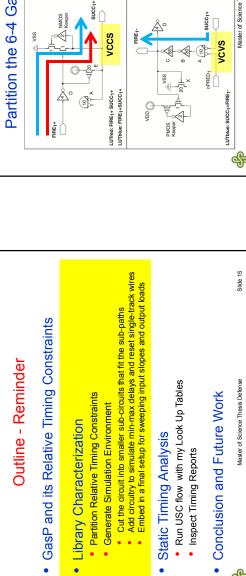

| 2  | 6-4              | GASP AND ITS RELATIVE TIMING CONSTRAINTS               | 10 |  |

| 3  | LIB              | RARY CHARACTERIZATION PART-A: LOOK UP TABLES (LUTs)    | 14 |  |

|    | 3.1              | Introduction                                           | 14 |  |

|    | 3.2              | Step 1: Use Electric to Access the GasP Design         | 18 |  |

|    | 3.3              | Step 2: Create a Simulation Environment for the Design | 20 |  |

|    | 3.4              | Step 3: Generate Input Files for SPICE                 | 21 |  |

|   |     | 3.4.1   | Generate a    | SPICE Netlist                                            | 21 |

|---|-----|---------|---------------|----------------------------------------------------------|----|

|   |     | 3.4.2   | Generate S    | SPICE Simulation Files: HEADER and TRAILER               | 21 |

|   | 3.5 | Step 4: | Modify the    | e SPICE Input Files                                      | 23 |

|   |     | 3.5.1   | Create Swe    | eep Parameters in the SPICE Netlist                      | 23 |

|   |     | 3.5.2   | Add Swee      | p and Measurement Statements to the TRAILER File         | 25 |

|   | 3.6 | Step 5: | Generate a    | SPICE Output File with Look Up Tables                    | 26 |

|   | 3.7 | Validat | ion           |                                                          | 30 |

|   | 3.8 | Conclu  | sion and Fu   | ture Work for Chapter 3                                  | 33 |

|   |     |         |               |                                                          |    |

| 4 | LIB | RARY    | CHARACT       | ERIZATION PART-B: FROM GASP TO LUTs                      | 34 |

|   | 4.1 | Introdu | iction        |                                                          | 34 |

|   | 4.2 | Quick   | Reminder: V   | What's a Look Up Table and How's It Used?                | 37 |

|   | 4.3 | STEP    | 1: Partitioni | ng Complex Paths into Simple Paths                       | 37 |

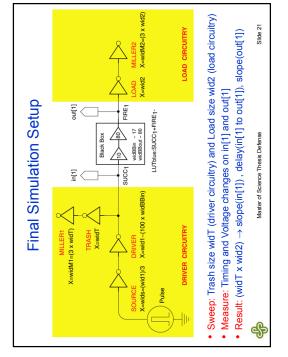

|   | 4.4 | STEP    | 2: Defining   | an Accurate Simulation Set-Up for Simple Paths           | 47 |

|   |     | 4.4.1   | Circuit Par   | titioning for RT1 to RT4                                 | 47 |

|   |     | 4.4.2   | Circuit Enl   | hancements for Min-Max and Repetitive Simulations        | 55 |

|   |     |         | 4.4.2.1       | Simulating Minimum Gate Delays                           | 56 |

|   |     |         | 4.4.2.2       | Autonomously Re-Initializing Un-Driven Wires             | 59 |

|   |     |         | 4.4.2.3       | Summary of Circuit Enhancements                          | 64 |

|   |     | 4.4.3   | Back to PA    | ART-A to Generate Look Up Tables                         | 65 |

|   |     |         | 4.4.3.1       | Setup for Figure 4.8 and LUTblue: $PRED_i - FIRE_i - $ . | 66 |

|   |      |         | 4.4.3.2     | Setup for Figure 4.9 and LUTblue: $SUCC_i + FIRE_i -$ .          | 68   |

|---|------|---------|-------------|------------------------------------------------------------------|------|

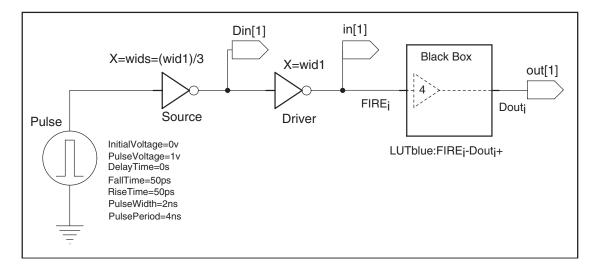

|   |      |         | 4.4.3.3     | Setup for Figure 4.7(b) and LUTblue:FIRE $_i$ -Dout $_i$ +       | 69   |

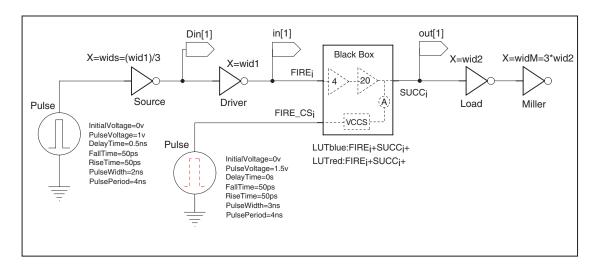

|   |      |         | 4.4.3.4     | Setup for Figure 4.10, LUTred/blue:FIRE $_i$ +SUCC $_i$ +        | 71   |

|   |      |         | 4.4.3.5     | Setup for Figure 4.11, LUTblue/green: $FIRE_i + PRED_i - PRED_i$ | - 76 |

|   | 4.5  | Genera  | al Simulati | on Setup Covering All Possible Sweep Cases                       | 81   |

|   |      | 4.5.1   | Covering    | All Possible External Input Drives                               | 81   |

|   |      | 4.5.2   | Covering    | Zero Exernal Output Loads                                        | 83   |

|   | 4.6  | Conclu  | ision and F | Future Work for Chapter 4                                        | 85   |

| _ | OTTA |         | MINICI AN   |                                                                  | 00   |

| 5 | SIA  | HC H    | MING AN     | ALYSIS OF 6-4 GASP USING LOOK UP TABLES                          | 88   |

|   | 5.1  | Introdu | action      |                                                                  | 89   |

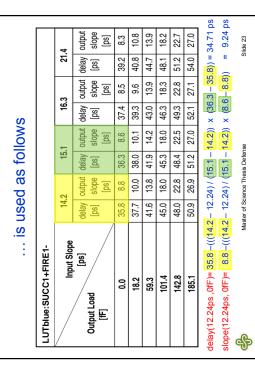

|   | 5.2  | STEP    | 1: From SI  | PICED to PrimeTime Look Up Tables                                | 91   |

|   |      | 5.2.1   | From Inp    | ut Driver Size to Input Transition Slope                         | 93   |

|   |      | 5.2.2   | From Ou     | tput Load Size to Output Load Capacitance                        | 94   |

|   |      | 5.2.3   | A Quick     | Sanity Check of the PrimeTime Look Up Tables                     | 103  |

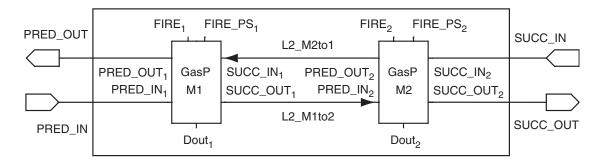

|   | 5.3  | STEP    | 2: From 6-  | 4 GasP Module to PrimeTime Black Box                             | 105  |

|   | 5.4  | STEP    | 3: Create a | Library File with SPICED Look Up Tables                          | 106  |

|   |      | 5.4.1   | STEP 3.1    | : Rename Look Up Tables to Match Black Box Names                 | 107  |

|   |      | 5.4.2   | STEP 3.2    | 2: Create a Library File with SPICED Look Up Tables.             | 110  |

|   | 5.5  | STEP    | 4: Create ( | Commands for Relative Timing Validation                          | 112  |

|   | 5.6  | STEP :  | 5: Run and  | I Inspect Timing Reports                                         | 113  |

|    | 5.7   | Conclusion and Future Work for Chapter 5     | 116 |

|----|-------|----------------------------------------------|-----|

| 6  | SUM   | IMARY AND DISCUSSION OF TIMING RESULTS       | 118 |

| 7  | CON   | MPARISON TO RELATED WORK                     | 123 |

| 8  | CON   | NCLUSION AND FUTURE WORK                     | 126 |

| Re | feren | ces                                          | 127 |

| Ap | pend  | ices                                         |     |

| A  | SPIC  | CE FILES FOR SPICE SWEEPS                    | 132 |

|    | A.1   | SPICE Netlist Generated by Electric          | 132 |

|    | A.2   | SPICE Simulation Set-Up File: HEADER         | 136 |

|    | A.3   | SPICE Simulation Set-Up File: TRAILER        | 136 |

|    | A.4   | Modified SPICE Netlist, Ready for Sweep      | 137 |

|    | A.5   | Modified SPICE TRAILER File, Ready for Sweep | 140 |

|    | A.6   | SPICE Output File                            | 141 |

| В  | SPIC  | CE FILES FOR SWEEPS IN THE DESIGN SPACE      | 142 |

|    | B.1   | SPICE Netlist for Reference Design           | 142 |

|    | B.2   | SPICE TRAILER File for Reference Design      | 151 |

|    | B.3   | SPICE Output File for Reference Design       | 153 |

| C | SPIC                             | CE FILES FOR FIGURE 4.8 AND LUTblue:PRED <sub>i</sub> -FIRE <sub>i</sub> -   | 154                                           |

|---|----------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|

|   | C.1                              | SPICE Netlist                                                                | 154                                           |

|   | C.2                              | SPICE Simulation Setup File: HEADER                                          | 160                                           |

|   | C.3                              | SPICE Simulation Setup File: TRAILER                                         | 161                                           |

|   | C.4                              | SPICE Output File                                                            | 163                                           |

| D | SPIC                             | CE FILES FOR FIGURE 4.9 AND LUTblue: $SUCC_i + FIRE_i -$                     | 165                                           |

|   | D.1                              | SPICE Netlist                                                                | 165                                           |

|   | D.2                              | SPICE Simulation Setup File: HEADER                                          | 171                                           |

|   | D.3                              | SPICE Simulation Setup File: TRAILER                                         | 172                                           |

|   | D.4                              | SPICE Output File                                                            | 174                                           |

|   |                                  |                                                                              |                                               |

| E | SPIC                             | CE FILES FOR FIGURE 4.7(b) AND LUTblue:FIRE $_i$ -Dout $_i$ +                | 176                                           |

| E | <b>SPI</b> (                     | CE FILES FOR FIGURE 4.7(b) AND LUTblue:FIRE $_i$ -Dout $_i$ +  SPICE Netlist |                                               |

| E |                                  |                                                                              | 176                                           |

| Ε | E.1                              | SPICE Netlist                                                                | 176<br>180                                    |

| E | E.1<br>E.2                       | SPICE Netlist                                                                | 176<br>180<br>181                             |

| E | E.1<br>E.2<br>E.3<br>E.4         | SPICE Netlist                                                                | 176<br>180<br>181                             |

|   | E.1<br>E.2<br>E.3<br>E.4         | SPICE Netlist                                                                | 176<br>180<br>181<br>182<br><b>183</b>        |

|   | E.1<br>E.2<br>E.3<br>E.4         | SPICE Netlist                                                                | 1766 1800 1811 1822 1833                      |

|   | E.1<br>E.2<br>E.3<br>E.4<br>SPIC | SPICE Netlist                                                                | 176<br>180<br>181<br>182<br><b>183</b><br>183 |

| G  | SPIC | CE FILES FOR FIGURE 4.11 AND LUTblue/green:FIRE <sub>i</sub> +PRED <sub>i</sub> - | 194 |

|----|------|-----------------------------------------------------------------------------------|-----|

|    | G.1  | SPICE Netlist                                                                     | 194 |

|    | G.2  | SPICE Simulation Setup File: HEADER                                               | 199 |

|    | G.3  | SPICE Simulation Setup File: TRAILER                                              | 200 |

|    | G.4  | SPICE Output File                                                                 | 202 |

| Н  | SPIC | CE FILES FOR FIGURE 4.22 WITH ZERO EXTERNAL LOADS                                 | 204 |

|    | H.1  | SPICE Netlist                                                                     | 204 |

|    | H.2  | SPICE Simulation Setup File: HEADER                                               | 214 |

|    | H.3  | SPICE Simulation Setup File: TRAILER                                              | 215 |

|    | H.4  | SPICE Output File                                                                 | 217 |

| Ι  | TRA  | ANSLATING LOAD SIZE INTO LOAD CAPACITANCE                                         | 219 |

|    | I.1  | SPICE Netlist                                                                     | 219 |

|    | I.2  | SPICE Simulation File: HEADER                                                     | 223 |

|    | I.3  | SPICE Simulation File: TRAILER                                                    | 224 |

|    | I.4  | SPICE Output File                                                                 | 226 |

| J  | PRI  | METIME NETLIST FOR THE TWO-STAGE GASP FIFO                                        | 228 |

| K  | PRI  | METIME LIBRARY WITH SPICED LOOK UP TABLES                                         | 229 |

| T. | PRI  | METIME COMMANDS FOR VALIDATING RT1 TO RT4                                         | 234 |

| M PRIMETIME TIMING REPORTS |                                                             |     |  |  |  |

|----------------------------|-------------------------------------------------------------|-----|--|--|--|

|                            | M.1 Timing Report for RT1 or RT(L2) $^{\rm TrfF-RstB}$      | 237 |  |  |  |

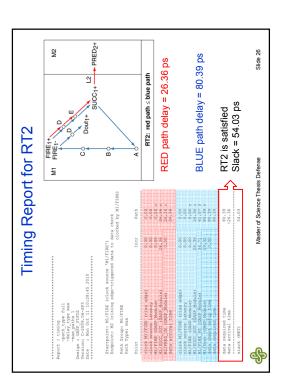

|                            | M.2 Timing Report for RT2 or RT(L2) $^{\mathrm{TrfF-RstF}}$ | 238 |  |  |  |

|                            | M.3 Timing Report for RT3 or RT(L2) $^{\rm TrfB-RstF}$      | 239 |  |  |  |

|                            | M.4 Timing Report for RT4 or RT(L2) $^{\rm TrfB-RstB}$      | 240 |  |  |  |

| N                          | BONUS MATERIAL: DISTANCE CONSTRAINT GRAPH                   | 241 |  |  |  |

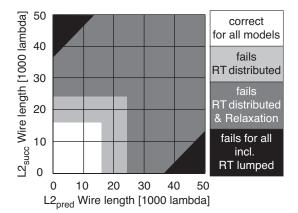

| o                          | BONUS MATERIAL: SHORT-TO-MEDIUM-TO-LONG WIRE STUDY          | 253 |  |  |  |

| P                          | BONUS MATERIAL: THESIS POWERPOINT PRESENTATION              | 265 |  |  |  |

# **List of Figures**

| 1.1 | High-level view of a linear pipeline in GasP with a bundled datapath     | 4  |

|-----|--------------------------------------------------------------------------|----|

| 1.2 | Timing validation flow for GasP circuits                                 | 5  |

| 2.1 | Two-stage FIFO with two 6-4 GasP modules                                 | 11 |

| 2.2 | Relative timing constraints on single-track wire L2 of Figure 2.1        | 13 |

| 3.1 | Half-way GasP circuit                                                    | 19 |

| 3.2 | Simulation environment for the Half-way GasP circuit in Figure 3.1       | 19 |

| 3.3 | Initial SPICE netlist with wrong null values for sweep size parameters . | 22 |

| 3.4 | SPICE netlist with corrected sweep size parameters                       | 24 |

| 3.5 | SPICE simulation file fragment with sweep and measurement statements     | 27 |

| 3.6 | SPICE output file fragment with look up table data                       | 29 |

| 3.7 | Design sweep of the Half-way GasP circuit in Figure 3.1                  | 31 |

| 3.8 | Comparison of Design sweep versus SPICE sweep results                    | 32 |

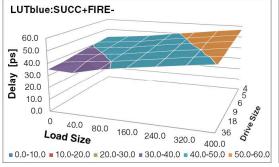

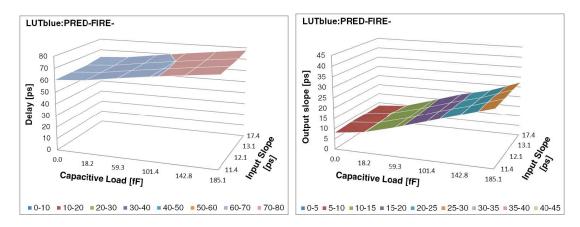

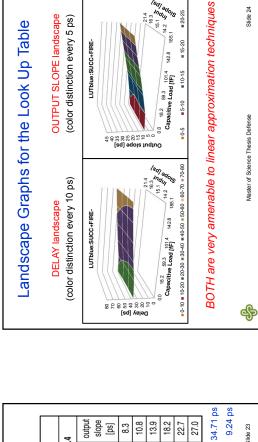

| 4.1 | Wide-range look up table with delay and output slopes                    | 38 |

| 4.2 | Wide-range landscape graphs with delay and output slope information .    | 38 |

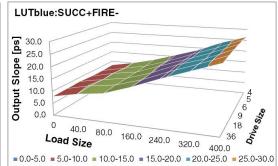

| 4.3 | Partitioning of the complex paths in relative timing constraint RT1      | 42 |

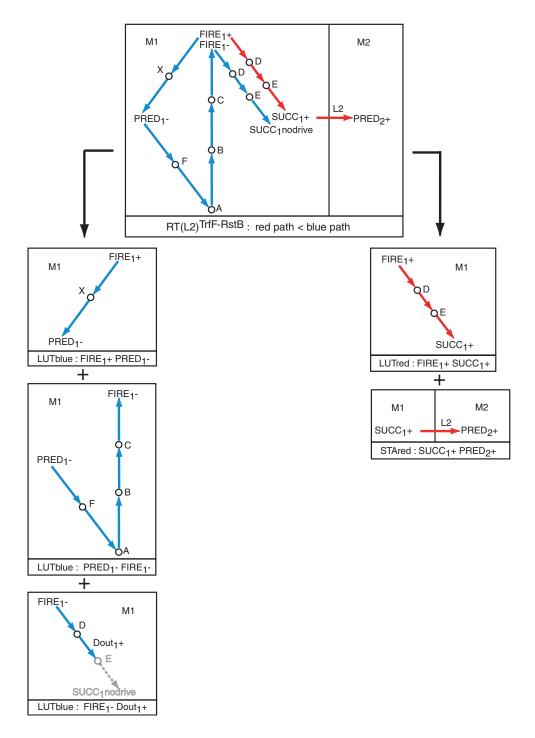

| 4.4  | Partitioning of the complex paths in relative timing constraint RT2             | 43 |

|------|---------------------------------------------------------------------------------|----|

| 4.5  | Partitioning of the complex paths in relative timing constraint RT3             | 44 |

| 4.6  | Partitioning of the complex paths in relative timing constraint RT4             | 45 |

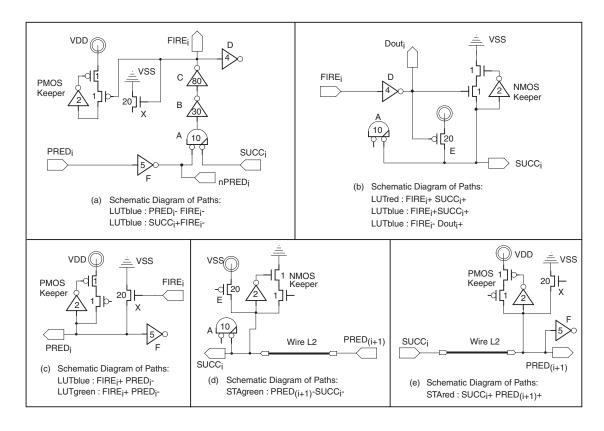

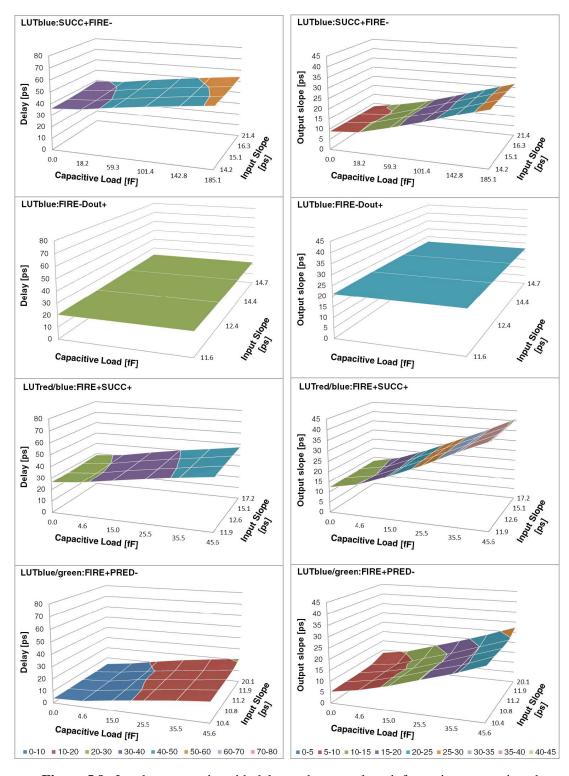

| 4.7  | 6-4 GasP circuit partitioning for RT1 to RT4                                    | 51 |

| 4.8  | Circuit enhancement for LUTblue: $PRED_i - FIRE_i$ for minimum delay            | 57 |

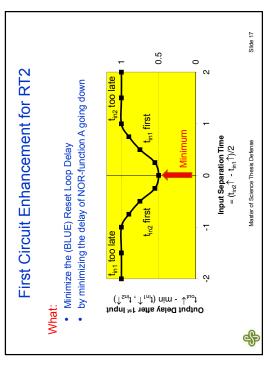

| 4.9  | Circuit enhancement for LUTblue: $SUCC_i + FIRE_i$ for minimum delay            | 58 |

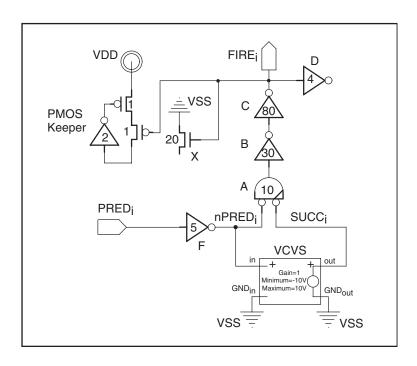

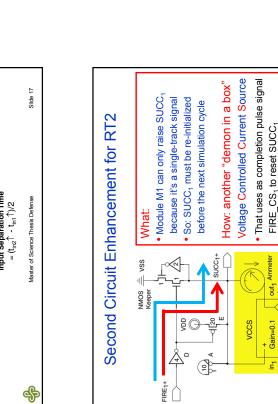

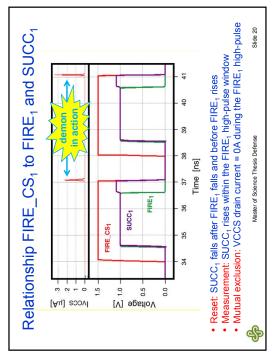

| 4.10 | Circuit enhancement LUTred/blue: $FIRE_i + SUCC_i + to$ self-reset output       | 61 |

| 4.11 | Circuit enhancement LUTblue/green: $FIRE_i + PRED_i$ — to self-reset output     | 63 |

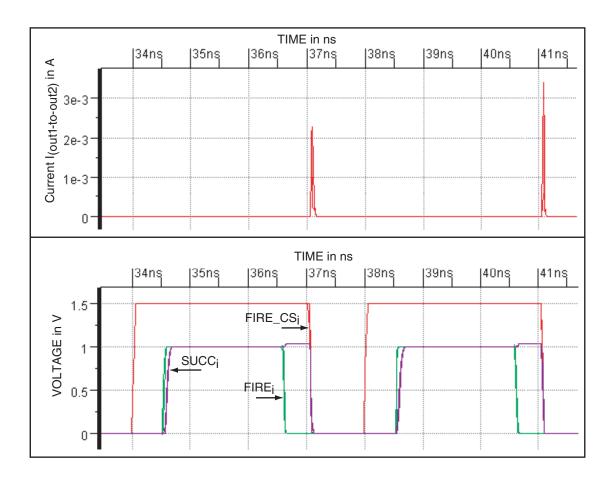

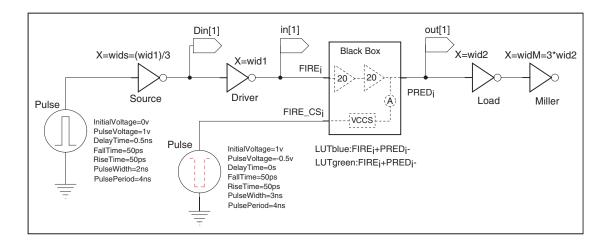

| 4.12 | Simulation setup for Figure 4.8 and LUTblue: $PRED_i - FIRE_i - \dots$ .        | 67 |

| 4.13 | Simulation setup for Figure 4.9 and LUTblue: SUCC $_i$ +FIRE $_i$               | 69 |

| 4.14 | Simulation setup for Figure 4.7(b) and LUTblue: $FIRE_i - Dout_i + \dots$       | 70 |

| 4.15 | Simulation setup for Figure 4.10 and LUTred/blue:FIRE $_i+SUCC_i+$              | 72 |

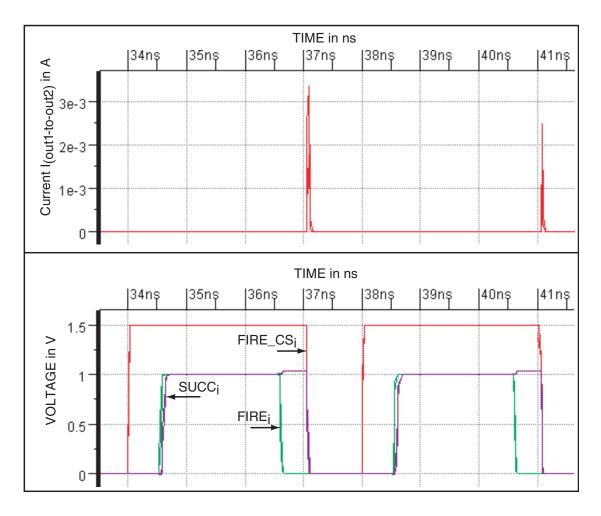

| 4.16 | VCCS validation-1 for Figure 4.15 and LUTred/blue:FIRE $_i$ +SUCC $_i$ + .      | 74 |

| 4.17 | VCCS validation-2 for Figure 4.15 and LUTred/blue:FIRE $_i$ +SUCC $_i$ + .      | 75 |

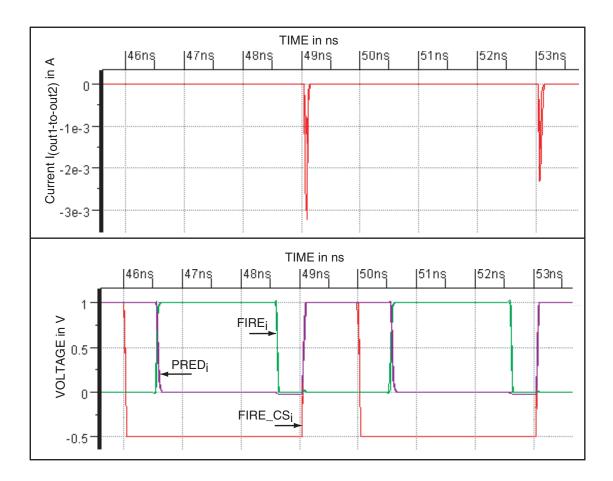

| 4.18 | Simulation setup for Figure 4.11 and LUTblue/green: $FIRE_i + PRED_i -$ .       | 77 |

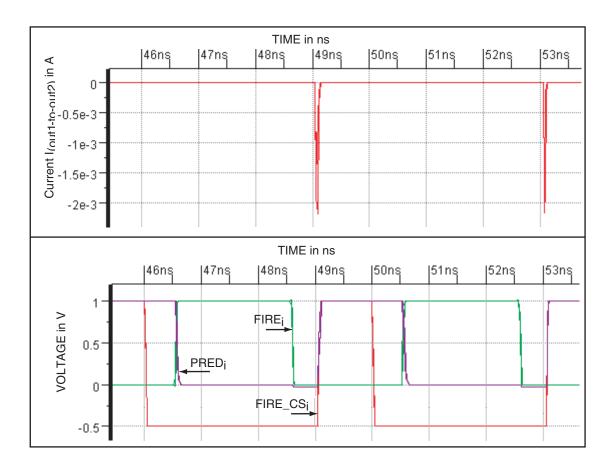

| 4.19 | VCCS validation-1 for Figure 4.18 and LUTblue/green: $FIRE_i + PRED_i - PRED_i$ | 79 |

| 4.20 | VCCS validation-2 for Figure 4.18 and LUTblue/green: $FIRE_i + PRED_i - PRED_i$ | 80 |

| 4.21 | General simulation setup for look up table sweeps                               | 82 |

| 4.22 | Simulation setup for zero external ouput load                                   | 84 |

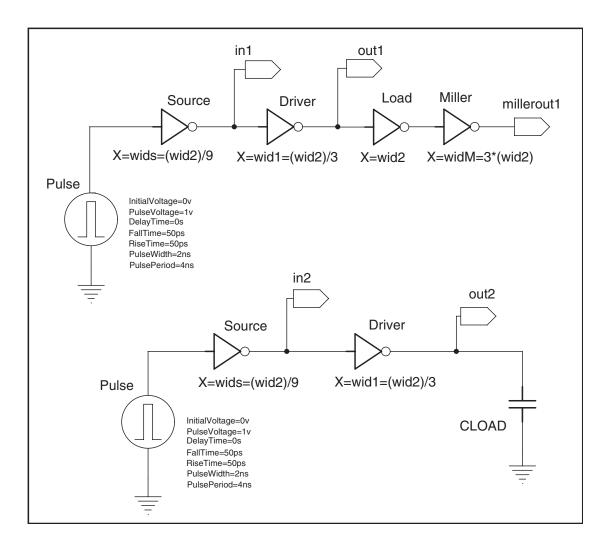

| 5.1  | Simulation setup for translating load size into load capacitance                | 95 |

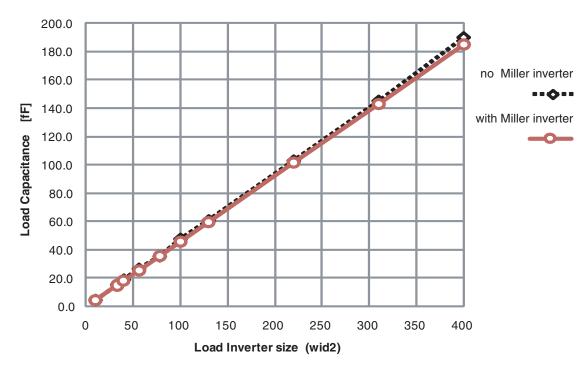

| 5.2  | Graph showing the translation of load size into load capacitance          | 97  |

|------|---------------------------------------------------------------------------|-----|

| 5.3  | SPICE to PrimeTime look up table for LUTblue: $PRED_i - FIRE_i - \dots$ . | 98  |

| 5.4  | SPICE to PrimeTime look up table for LUTblue:SUCC $_i+$ FIRE $_i-$        | 99  |

| 5.5  | SPICE to PrimeTime look up table for LUTblue:FIRE $_i$ -Dout $_i$ +       | 100 |

| 5.6  | SPICE to PrimeTime look up table for LUTred/blue:FIRE $_i$ +SUCC $_i$ + . | 101 |

| 5.7  | SPICE to PrimeTime look up table for LUTblue/green:FIRE $_i$ +PRED $_i$ - | 102 |

| 5.8  | Landscape graphs with delay and output slope information                  | 103 |

| 5.9  | Landscape graphs with delay and output slope information — continued      | 104 |

| 5.10 | Split pin architecture of a basic 6-4 GasP module with its black box icon | 105 |

| 5.11 | Split pin architecture of the two-stage GasP FIFO                         | 106 |

| 5.12 | PrimeTime version of the relative timing constraints from Figure $2.2$    | 108 |

| 5.13 | Renaming of SPICE look up table names into PrimeTime names                | 110 |

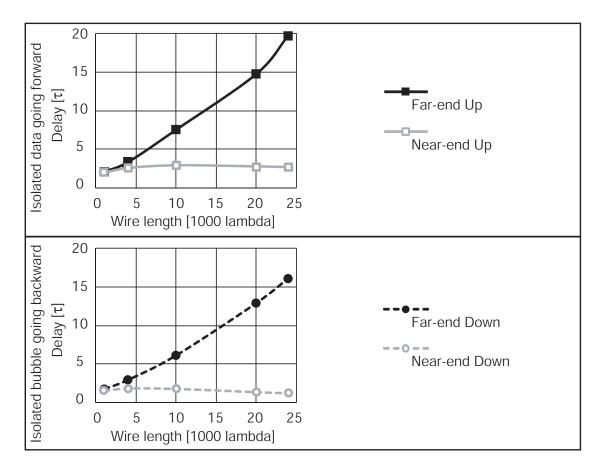

| 6.1  | Rising and falling delays at the near and far end of single-track wire L2 | 120 |

|      |                                                                           |     |

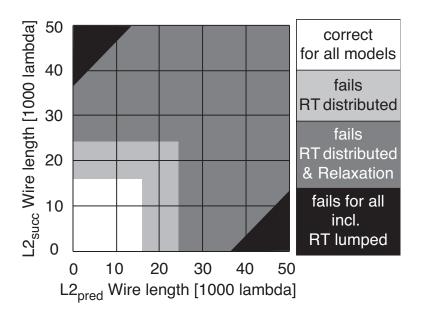

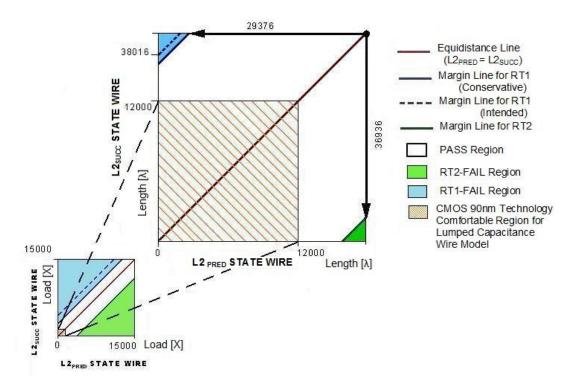

| 6.2  | Distance Constraint Graph for 6-4 GasP in 90nm CMOS                       | 122 |

# Chapter 1

#### INTRODUCTION

Concurrency and energy efficiency have taken their place as first class criteria in the design of modern circuits and systems along with, and at times even at the cost of, speed in terms of throughput and latency. The design of modern concurrent systems centers around a communication infrastructure that connects a number of functional blocks. Examples are IBM Research's Cell systems [8], Intel's research milestones for many-core and teraflop systems [9, 10], and Sun's (now: Oracle's) UltraSPARC T1 microprocessor, codenamed 'Niagara' [11]. Each block tends to have its own clock or timing regime, fit to best match its operations. From a timing point of view, the blocks operate asynchronously. Even if blocks use the same clock frequency, their operations are likely to be skewed or out of phase with respect to each other.

The Asynchronous Research Center (ARC) at Portland State University is building a concurrent system architecture called 'Fleet' [31, 13] centered around an asynchronous communication network, built using GasP modules. Fleet anticipates the use of a variety of computation blocks of low to modest complexity, called 'ships', such as low-power adders and multipliers, high-speed adders and multipliers, dividers, various shift and sort functions, I/O functions, and memory blocks. The ships can be synchronous

or asynchronous, including GasP. They can be integrated in a single chip, or spread over different chips or FPGAs. This makes it possible to import asynchronous ships designed by companies like Achronix Semiconductor Corporation [5] for asynchronous FPGA's, Fulcrum Microsystems [7] for high-density ethernet switches, and Tiempo [14] for ultra-low-power functions. Alternatively, Fleet can take ships built using different asynchronous design styles from other academic and research institutes. For an overview of asynchronous design styles and a list of institutes that study and develop asynchronous circuits, see the yearly international symposium on asynchronous circuits and systems, which is approaching its 17-th anniversary [12].

#### 1.1 GasP Circuits

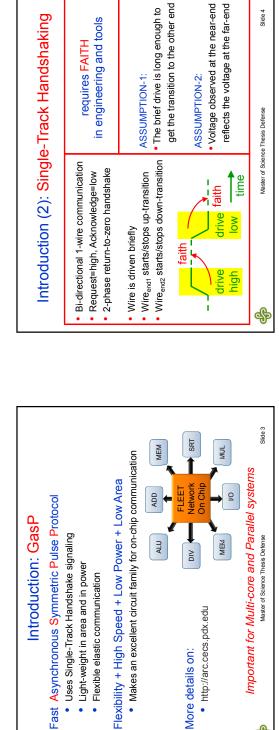

The target circuits for this thesis are GasP circuits. These circuits use handshake signaling over a single-track wire and single-rail data encoding. This results in (N+1) wires to communicate N data bits. The combination of single-track handshaking and single-rail data results in light-weight circuits — light in area and light in power. GasP circuits also happen to be about twice as fast as one would expect of a globally clocked circuit implemented in the same technology. Add the flexibility and elasticity of asynchronous design to high speed, low power, and low area, and you get an excellent circuit family for on-chip communication — which is why Fleet uses a GasP network on chip.

In addition to the data wires, GasP circuits use a single wire for timing. The single-track handshake is a bi-directional communication on that wire. A logical high voltage level on the wire indicates a request, and a logical low voltage level on the wire indicates an acknowledge signal. The wire has two drivers — one at each end, one for the request and one for the acknowledge. This leads naturally to a two-phase return-to-zero handshake.

The wire is shared, so each end drives only briefly. The brief drive avoids a drive fight between the two ends. In addition, each driver responds only to changes at its own end. It's this local response that enables the communication to complete in two phases. To make this work, we need some *faith*: faith in our own engineering and in the design tools that we use. The faith in a single-track handshake depends on two assumptions:

**Assumption 1:** The brief drive is long enough to traverse the wire.

**Assumption 2:** The voltage level at the near end of the wire reflects the far-end level.

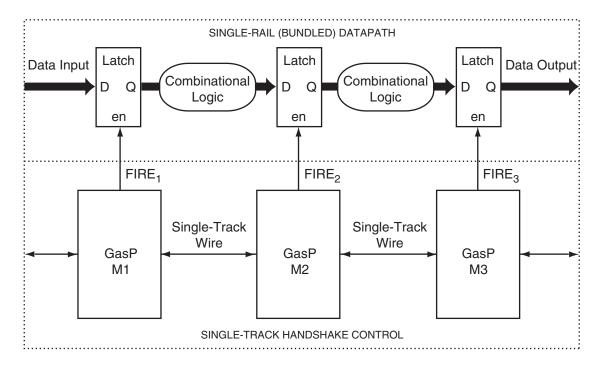

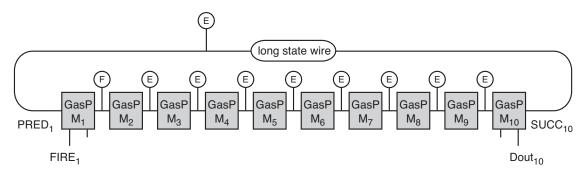

Data in GasP are exchanged using a bundled-data, also known as single-rail, protocol. Data bits are represented using one wire per bit, just like in conventional synchronous circuits. The single-track request signal indicates that the sender module has new data for the receiver module, i.e. it acts as a 'data valid' signal for the data transfer. The single-track acknowledge signal indicates that the receiver module has finished consuming the data, i.e. it acts as a 'completion' signal for the data transfer. Figure 1.1 gives a high-level overview of a linear pipeline in GasP. The GasP modules are connected with single-track wires. Each GasP module Mi generates a local pulse signal FIRE; that acts as a local clock or enable signal for the group of latches above it, making the group temporarily transparent. To make this work, we need — again — some faith. The faith in a bundled datapath operation can be expressed in terms of conventional setup and hold times between the data inputs and outputs and the clock enable signals at both ends of the datapath. The data bundling constraints in GasP and their static timing analysis have been solved successfully by Prasad Joshi in his Master of Science thesis [2].

In the rest of my thesis, I will assume that timing constraints related to datapaths are no longer an issue, and I will henceforth ignore the datapath portion of a GasP design.

**Figure 1.1** High-level view of a linear pipeline in GasP with a bundled datapath. The GasP control modules are connected with bi-directional single-track wires. Their implementations are omitted here, but follow in Chapter 2, Figure 2.1, page 11. Each GasP module Mi generates a local pulse signal FIRE<sub>i</sub> that acts as a local clock or enable signal for the group of latches above it, making the group temporarily transparent.

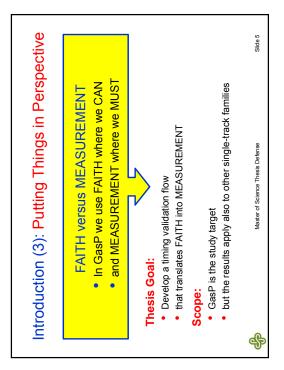

The message to take away is that GasP designs are light-weight because GasP designers use faith where they can and build in measurement where they must. This take-away also explains where my thesis comes in: I developed a timing validation flow that translates *faith* into *measurement*. As a result, a GasP designer can rely on faith to make her design light-weight, and use my validation flow to check how well that faith holds up.

# 1.2 Timing Validation Flow

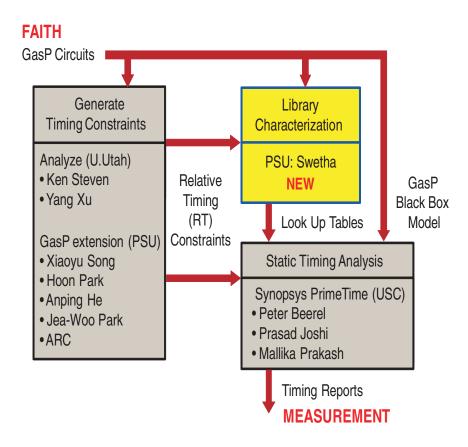

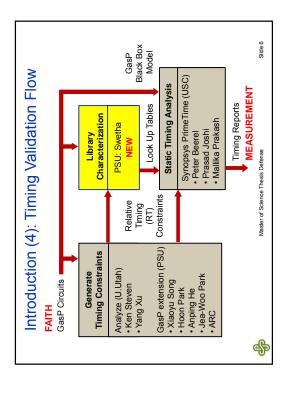

Figure 1.2 gives an overview of the timing validation flow I offer. The complete flow consists of three consecutive parts: (1) generation of the critical timing constraints, and (2) library characterization, and (3) static timing analysis (STA).

**Figure 1.2** Timing validation flow for GasP circuits. The complete flow consists of three parts: (1) generation of the critical timing constraints, (2) library characterization, and (3) static timing analysis (STA). Together the three parts take a GasP circuit, built using faith, and translate it into timing reports that measure how well the faith holds up.

Ideally, the first step takes a GasP circuit and generates its critical timing constraints. There is a tool for this step, developed at the University of Utah by Professor Ken Stevens and his students [26, 37]. The tool is called 'Analyze'. It is being extended for GasP circuits here at Portland State University by Professor Xiaoyu Song and his students, in collaboration with the Asynchronous Research Center. The tool uses formal verification techniques. The timing constraints are called 'Relative Timing Constraints'. In my thesis, I assume that the first part is done, i.e. I start with a GasP circuit and a given set of relative timing constraints.

The second step in the flow, and the first step addressed in my thesis is called 'Library Characterization'. This is the key part of my thesis, and it's new work. In this step, I take a GasP circuit and its relative timing constraints. I partition these into manageable pieces that I simulate for various operating conditions. And I generate a collection of so-called 'Look Up Tables' (LUTs) that store the timing information of the paths under those conditions.

I feed these look up tables and a so-called 'Black Box' model of the GasP circuit into static timing analysis. The black box shows only the circuit input and output pins, and hides the combinational loops and single-track details of GasP. This third step is not new. The black box model and the analysis commands for the relative timing constraints were developed at the University of Southern California by Professor Peter Beerel and his students. The tool itself is a commercial tool by Synopsys called 'PrimeTime' [35]. All I had to do was to get it running at Portland State University and to import my timing constraints and look up tables.

The result of static timing analysis is a collection of timing reports, one for each relative timing constraint, showing how much slack there is to make or break the constraint. So, in total, these three flow parts take a GasP circuit, built using faith, and translate it into timing reports that measure how well the faith holds up. *In summary: the timing validation flow outlined in Figure 1.2 translates faith into measurement.*<sup>1.1</sup>

#### 1.3 Reading Guide

I have now told you why I built a timing validation flow for GasP, and which parts I borrowed and which parts are new. The rest of my thesis is organized as follows:

<sup>&</sup>lt;sup>1.1</sup>Of course, the real measurement is the silicon, but that is a very expensive and time-consuming measurement. The measurement I am talking about is a simulated measurement.

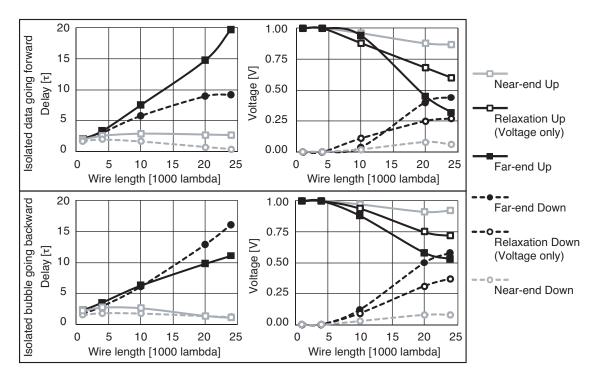

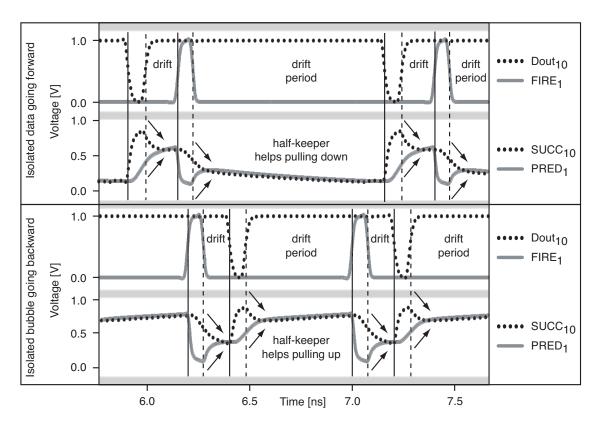

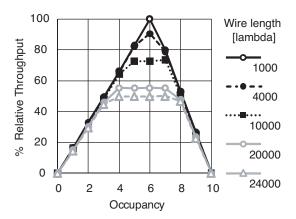

- Chapter 2 gives the design details on GasP, and identifies the four key relative timing constraints for single-track communication. In this thesis, I work with TSMC 90nm CMOS implementations of 6-4 GasP, but that's just a choice. This choice has zero impact on the generality and applicability of my flow to other CMOS implementations or other members of the GasP family, such as 4-2 GasP or 3-7 GasP. More GasP details can be found in Appendix O or [30, 29, 18, 13].

- Chapter 3–4 are about library characterization, and cover he biggest part of my thesis. Here, I show how timing constraints are translated into look up tables. This requires three steps. In the first step, I partition the timing constraints into manageable pieces. In the second step, I build a simulation environment for each partitioned timing constraint, using the schematic design environment provided by Electric [24] and the transistor-level simulation environment provided by SPICE [34]. In the third step, I run the SPICE simulator to generate the look up tables. Chapter 3 explains the basic simulation environment in Electric and the SPICE commands for the third step. Chapter 4 takes a 6-4 GasP module and the four key relative timing constraints identified in Chapter 2, and goes into the details of each step.

- Chapter 5 shows how static timing analysis uses the timing information in the look up tables to validate the four relative timing constraints. Here, I explain the STA part of the flow and show how to import the look up tables generated in Chapter 4.

- Chapter 6 analyzes the timing results produced by the STA part of the flow. Because the proof of the pudding is in the eating, I did not just propose and develop a timing validation flow, but I also used it. I used it to validate the four timing constraints that are key to single-track handshake communication in 6-4 GasP.

Moreover, I show that the results in the timing reports are compatible with the results of my ASYNC 2010 publication in [18] and Appendix O.

- Chapter 7 compares my approach to the approach taken by USC. I deliberately postpone this comparison to the end of my thesis, because this enables me to give a more in-depth explanation than would be possible with an up-front comparison where the reader has not yet had a chance to read any of my work.

- Chapter 8 concludes this thesis and indicates what next steps are needed. As far as future work goes, what this flow needs most is a wire delay model. The wire delay model should distinguish the effective capacitance seen at the near end of the wire from the capacitance and delay seen at the far end. It may be that an Elmore delay model suffices [23, 36]. Last but not least: this flow needs automation so it can become an integral part of the GasP design environment.

Chapters 2–7 are also available as internal reports [16, 17, 19] from the Asynchronous Research Center at Portland State University, where I worked as a Research Assistant. The reports are co-authored by Marly Roncken and Ivan Sutherland. For that reason, Chapters 2–7 use as author identity 'we' instead of 'I'. The author identity changes to 'I' again when I conclude this thesis in Chapter 8.

After working with flows that require various tools and translations from file formats in one tool to file formats in another tool, I have come to realize that documentation often lacks the clarity and teaching capability that it should provide. I have therefore set an extra goal for my thesis. Not only do I want to show that I generated a timing validation flow for single-track circuits in GasP, but I also want to explain this flow in a way that is useful for professors as well as for their students. I have set up this thesis so

that others can easily use the flow, execute it, and validate its results. The many files in Appendices A–M in this thesis are there to support this extra goal.

In addition to Appendices A–M with files, I have added three more Appendices N–P with extra bonus material to complete the picture and provide a quick tour of this thesis:

- Appendix N contains the ARC report on the Distance Constraint Graph. I defined

this graph notion when studying 6-4 GasP with short wires. It has turned out to be

a useful abstraction for thinking about wire lengths and module distances versus

critical timing paths (or relative timing constraints as we call them at the ARC).

- Appendix O contains the paper that I presented and published at ASYNC 2010. It contains the short-to-medium-to-long wire studies for 6-4 GasP. The above ARC report and the ASYNC 2010 paper shaped the topic of this thesis. Both are cited repeatedly in this thesis to motivate their inclusion. IEEE and my co-authors graciously allowed me to include them as appendix to this thesis.

- Appendix P contains the handout of the powerpoint presentation that I presented during my thesis defense, on 29 October 2010. Reading the powerpoint slides, which I printed as a 4-slides-per-page handout may be the quickest way to get a tour of this thesis. I hope you will enjoy the tour!

# Chapter 2

#### 6-4 GASP AND ITS RELATIVE TIMING CONSTRAINTS

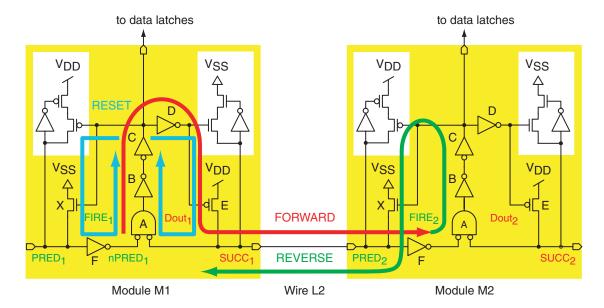

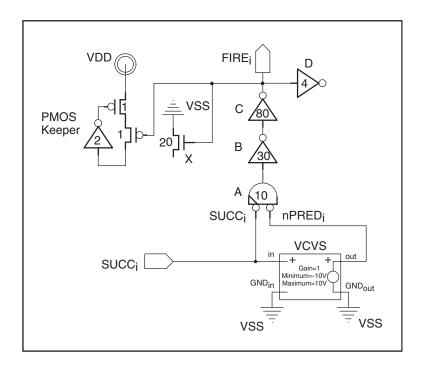

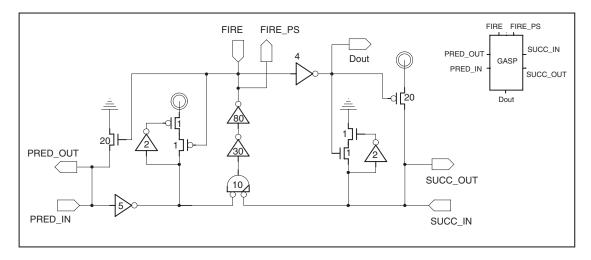

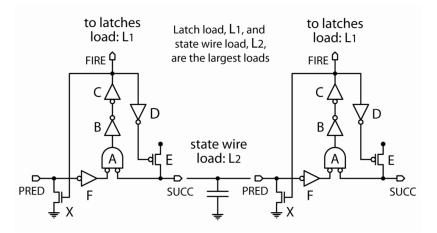

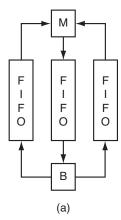

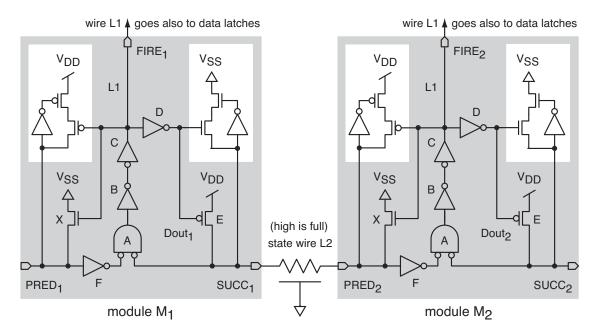

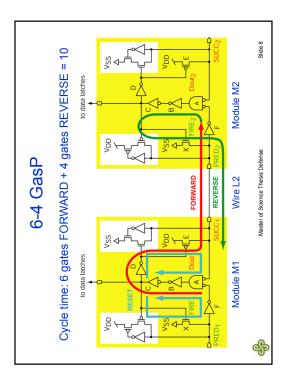

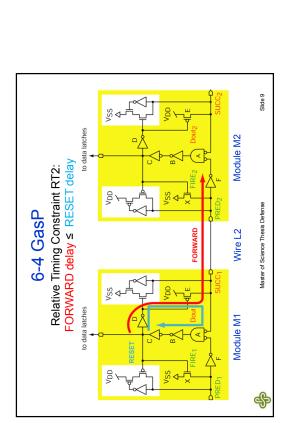

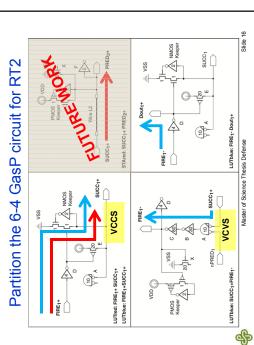

Chapter 2 introduces the basics of GasP circuits. We use a 6-4 GasP FIFO module as reference design. Figure 2.1 shows a two-stage FIFO with two 6-4 GasP FIFO modules, M1 and M2. Modules M1 and M2 are connected by a bi-directional wire L2 in the middle. Module M1 drives wire L2 high via P-transistor E and module M2 drives wire L2 low via N-transistor X. Wire L2 is called a 'single-track wire', but in GasP we also call it a 'state wire' because it holds state. It is high when it has valid data in which case we call its state 'Full' and it is low when it has a bubble, in which case we call its state 'Empty'. GasP module M1 fires when its PRED<sub>1</sub> signal is high, meaning full, and its SUCC<sub>1</sub> signal is low, meaning empty.

When M1 fires, it forwards the full state on its left to state wire L2 and module M2 on its right, using the six gates on the red arrow in Figure 2.1: A, B, C, D, E and F. When M2 fires it drains state wire L2, using the 4 gates on the green arrow: A, B, C and X. The name for 6-4 GasP comes from the six gates in the path going forward from one module to the next, and the four gates in the reverse path.

In addition, a 6-4 GasP module has two self-resetting loops of five gates each, as indicated by the blue arrows in Figure 2.1. We distinguish the successor loop through

**Figure 2.1** Two-stage FIFO with two 6-4 GasP modules, M1 and M2, connected by a single-track wire L2 which is bi-directional. In GasP, we often refer to single-track wire L2 as 'state wire'. The bundled data paths are not shown here, nor are the state wires connected to the left of M1 and the right of M2. For a high-level view with datapaths, see Figure 1.1 on page 4.

the path with gates A, B, C, D, and E from the predecessor loop through the path with gates A, B, C, X, and F. When state wire L2 is not driven its state is held by the half-keepers at the two ends of the wire, shown in the white insets of Figure 2.1. Note that the NMOS half-keeper is connected to the SUCC<sub>1</sub> signal at the successor side and to the successor loop. Similarly, the PMOS half-keeper is connected to the PRED<sub>1</sub> signal at the predecessor side and to the predecessor loop. Further details on 6-4 GasP can be found in Appendix O and in [30, 29, 18, 13].

The two self-resetting loops turn off the drive signal to the state wire and we must avoid letting them turn the drive off prematurely. Correct operation of 6-4 GasP requires that state wire L2 is (1) driven long enough in the forward direction to raise both wire ends, SUCC<sub>1</sub> and PRED<sub>2</sub>, and (2) driven long enough in the reverse direction to lower both wire ends.

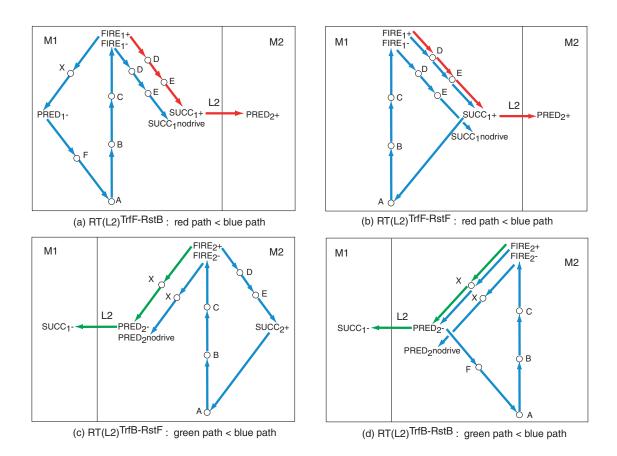

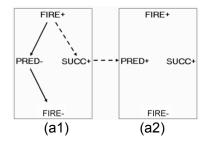

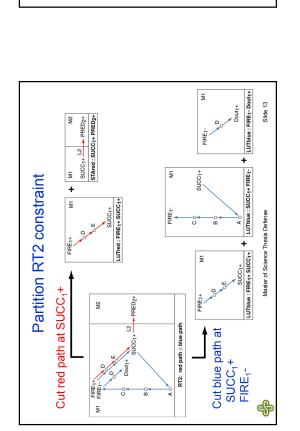

To validate that both (1) and (2) hold, we compare the forward and the reverse drive delays for L2 to the self-resetting loop delays and require the former to beat the latter. Thus, state wire L2 in Figure 2.1 produces the following four relative timing constraints:

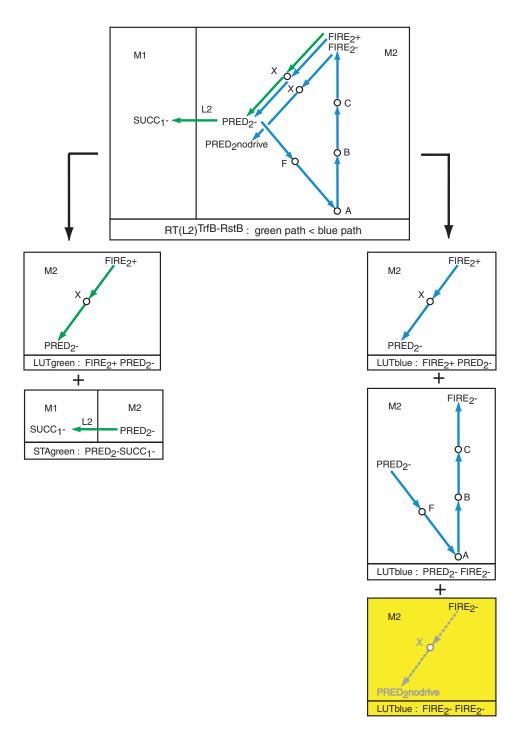

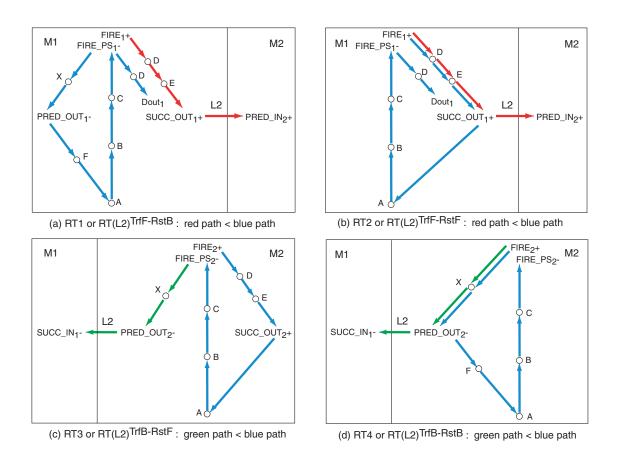

- RT1 or RT(L2)<sup>TrfF-RstB</sup>: The forward transfer delay to drive both ends of L2 high through DE in module M1 is shorter than the delay of the backward self-resetting loop through XFABCDE in M1 that stops the drive. Figure 2.2(a) illustrates this graphically: the red path must be shorter than the blue path.

- RT2 or RT(L2)<sup>TrfF-RstF</sup>: The forward transfer delay to drive both ends of L2 high through DE in module M1 is shorter than the delay of the forward self-resetting loop through DEABCDE in M1 that stops the drive. Figure 2.2(b) illustrates this graphically: the red path must be shorter than the blue path.

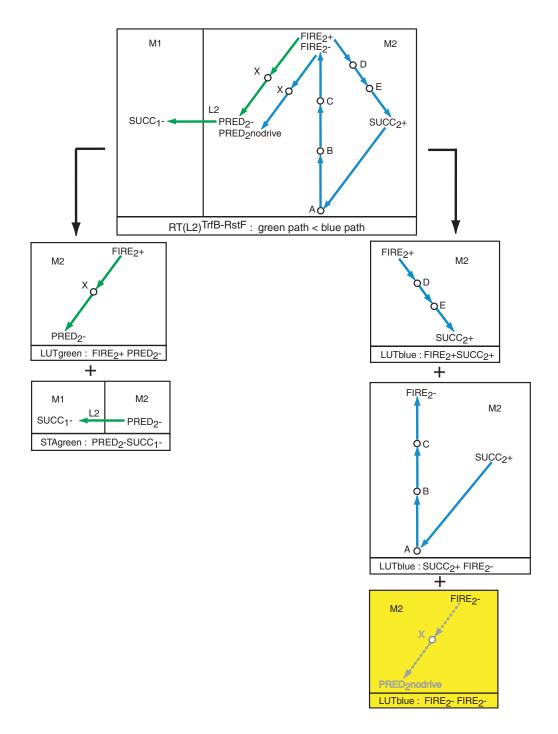

- RT3 or RT(L2)<sup>TrfB-RstF</sup>: The reverse transfer delay to drive both ends of L2 low through X in module M2 is shorter than the delay of the forward self-resetting loop through DEABCX in M2 that stops the drive. Figure 2.2(c) illustrates this graphically: the green path must be shorter than the blue path.

- RT4 or RT(L2)<sup>TrfB-RstB</sup>: The backward transfer delay to drive both L2 ends low through X in module M2 is shorter than the delay of the backward self-resetting loop through XFABCX in M2 that stops the drive. Figure 2.2(d) illustrates this graphically: the green path must be shorter than the blue path.

From these relative timing constraints, and their graphical representations in Figure 2.2, it follows that the red, green and blue paths in Figures 2.1–2.2 are the circuit paths whose delays we must calculate. Note that the blue paths contain (combinational) loops. This classifies them as complex paths, and as such as paths too difficult to handle by commercial library characterization and static timing analysis tools. In Chapters 4 and 5 we explain how this can be solved.

**Figure 2.2** Graphical representation of the four relative timing constraints on state wire L2 in Figure 2.1. Graph (a) is a graphical representation of relative timing constraint RT1 or RT(L2)<sup>TrfF-RstB</sup>. It requires that the delay for the red-arrow path must be less than the delay for the blue-arrow path. The red-arrow path in graph (a) corresponds to the forward red arrow in Figure 2.1, followed from FIRE<sub>1</sub> to PRED<sub>2</sub>. The blue-arrow path in (a) correspond to the backward blue reset arrow in Figure 2.1, followed from FIRE<sub>1</sub> to FIRE<sub>1</sub> and on to the point where M1 stops its forward drive to L2. We use circles for gates and arcs for signal transitions. A '+' symbol indicates a rising transition, and a '-' symbol indicates a falling transition. Likewise, graph (b) is a graphical representation of RT2 or RT(L2)<sup>TrfF-RstF</sup>, graph (c) of RT3 or RT(L2)<sup>TrfB-RstF</sup>, and (d) of RT4 or RT(L2)<sup>TrfB-RstB</sup>. The green-arrow paths in graph (c) and graph (d) correspond to the reverse green arrow in Figure 2.1, followed from FIRE<sub>2</sub> to SUCC<sub>1</sub>. The delay for the green-arrow path in graph (c) must be less than the delay for the blue-arrow path in graph (c), and likewise for graph (d).

# Chapter 3

# LIBRARY CHARACTERIZATION PART-A: LOOK UP TABLES (LUTs)

Chapter 3 is also available as internal report ARC2010-smg01 [16]. It describes the results of our investigations into creating look up tables that accurately characterize the timing information of a 6-4 GasP module. These tables allow us to bypass tool issues related to loops and other design elements used in asynchronous circuits that standard tools for synchronous circuit designs are not accustomed to. In addition to avoiding tool issues, the use of look up tables can also speed up the static timing analysis (STA) of a large GasP design. We present our results in two parts. PART-A, described here, takes a simple circuit without loops, and shows the basic flow aspects from the schematics entry level of the design in Electric to the SPICE simulation set-up and the SPICE output files with the look up tables. PART-B, described in Chapter 4 shows how to partition complex circuits with loops and multiple inputs and outputs into designs simple enough for the characterization flow in PART-A.

#### 3.1 Introduction

A look up table is basically an array with a search key and a corresponding result. look up tables are often used to reduce the run time of a computation. In the old days people used printed look up tables like logarithmic or trigonometry tables to speed up hand

calculations. Look up tables are used in one of three ways: (1) Exact match or (2) Interpolation, or (3) Extrapolation. When the search key exists, i.e. when it exactly matches a look up table entry, we can simply read out the corresponding result value. When the search key does not match any of the look up table entries, we estimate the result value for a search key that is inside respectively outside the entry range, by using interpolation respectively extrapolation techniques on the result values of the look up table entries that are closest in value to the search key. For our usage, linear interpolation and extrapolation techniques suffice.

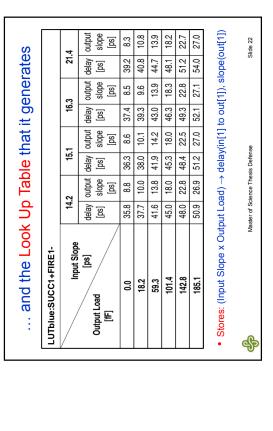

We use look up tables (LUTs) for static timing analysis (STA) of GasP circuits. The look up tables that we generate store the path delays for a GasP circuit, under various operating conditions. Our look up tables use a two-dimensional search key (wid1  $\times$  wid2) and store three types of delay:

- 1.  $(wid1 \times wid2) \rightarrow slope (in[1])$

- 2.  $(wid1 \times wid2) \rightarrow delay (in[1] to out[1])$

- 3.  $(wid1 \times wid2) \rightarrow slope (out[1])$

#### where:

- wid1 is the size of the external gate driving path input in[1].

- wid2 is the size of the external gate driven by path output out[1].

- slope(in[1]) is the input transition slope, a.k.a. input slew time, as denoted by the time difference (tin2-tin1) from time tin1 when a rising input transition on in[1] passes the 20% supply voltage point to time tin2 when it passes the 80% voltage point and vice versa for a falling input transition.

- delay(in[1] to out[1]) is the input-to-output transition delay time (tout-tin) from time tin when the input transition on in[1] passes the 50% supply voltage point to time tout when the output transition on out[1] passes the 50% supply point.

slope(out[1]) is the output transition slope, a.k.a. output slew, as for instance denoted by the time difference (tout<sub>2</sub> - tout<sub>1</sub>) from time tout<sub>1</sub> when a falling output transition on out[1] passes the 80% supply voltage point to time tout<sub>2</sub> when it passes the 20% point — and vice versa for a rising output transition.

For those of you who are familiar with standard static timing analysis (STA) tools like PrimeTime of Synopsys: note that the search keys in our look up tables are different. We use sizing information instead of input slopes and output loads. By doing this we can use the theory of Logical Effort [32] in both the design and the characterization of our circuits. We feel that this makes the characterization process less artificial and more realistic. To accommodate standard STA tools, we measure the input slopes for a given drive size and we have methods to translate a driven output size into an output load which we'll explain in Chapter 5. In the present Chapter 3, we show how to generate such look up tables for simple paths in a GasP circuit, i.e. paths with one input and one output, and without feedback. Complex paths are the topic of Chapter 4.

There are basically two ways to sweep the search key values for (wid1 × wid2) and generate the resulting delay and slope information for a simple path in a GasP circuit. One approach is to design all sweeps in parallel at the schematic entry level and create one composite SPICE run. This works provided the size of the simulation result file is small enough to be read back into Electric's schematic entry and layout environment [24] for validation and debug. We had some trouble with this in our long wire studies for [18]. We will investigate another approach where we design exactly one parameterized sweep schematics in Electric, which we will simulate multiple times, each time with a new set of parameter values, using the .DATA sweep command in SPICE [34].

Our look up table generation procedure distinguishes the following five steps:

- **Step 1:** Use schematics and layout tool Electric to access the GasP design.

- **Step 2:** In Electric, create a realistic simulation environment for the GasP design.

- **Step 3:** From Electric, generate input files for SPICE:

- Generate a SPICE netlist for the GasP design and its environment.

- Generate SPICE simulation set-up files.

# **Step 4:** Modify the SPICE input files:

- In the netlist, create sweep parameters for wid1 and wid2.

- In the simulation set-up files, add sweep statements for wid1 and wid2, and measurement statements for in[1] and out[1].

**Step 5:** Run SPICE and capture the look up table results in an output file.

The outline for the rest of Chapter 3 is as follows. Sections 3.2 to 3.6 each discuss one step in our 5-step look up table generation procedure. We use the 6-4 GasP circuit of Figure 3.1 on page 19 as our baseline example. Section 3.7 compares the results obtained by applying the 5-step procedure to this circuit to the results obtained from the alternative approach: i.e. from a reference design where all sweeps are embedded in parallel at the schematics entry level and where the results are obtained in one SPICE run. The reference design follows in Figure 3.7, page 31. Section 3.8 concludes Chapter 3. All the SPICE input and output files for the baseline example and the reference design can be found in Appendix A and B.

### Note:

We postpone the comparison between our library characterization work and prior work at USC by Mallika Prakash [21, 22] and Prasad Joshi [2, 3] to Chapter 7.

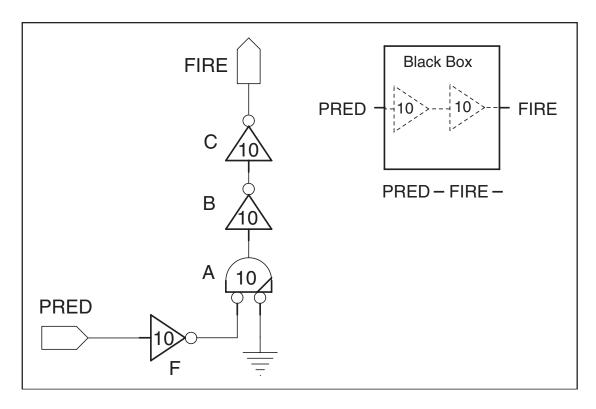

## 3.2 Step 1: Use Electric to Access the GasP Design

Figure 3.1 shows the schematic diagram of the 6-4 Half-way GasP circuit that we use as our design example throughout Chapter 3. The circuit name is Half-way GasP because it represents about half of a 6-4 GasP module in Figure 2.1. The Half-way GasP circuit has one input pin, PRED, and one output pin, FIRE. Input PRED drives an inverter called F which subsequently drives a NOR gate called A. The other input to the NOR gate is grounded. Output FIRE is the output of the NOR gate, delayed by two inversions through gates B and C. Half-way GasP is a fictional circuit which uses gate size 10 for all its gates rather than the step-up of 3 sizing strategy of Logical Effort designs [32]. The operation of the Half-way GasP circuit is as follows. When PRED goes low, the corresponding input to NOR gate A goes high, which results in FIRE going low. The nominal delay between PRED going low and FIRE going low is about 4 gate delays. The delay decreases if the output load driven by FIRE decreases or the input drive to PRED increases. The delay increases if the output load driven by FIRE increases or the input drive to PRED decreases. Likewise, when PRED goes high, FIRE will go high

Circuit and path are represented by a black box whose icon is shown in the upper right corner of Figure 3.1. Only the information that we need from the black box is visible:

after a delay of about 4 gate delays, with a decrease or increase in delay as before. We

will characterize the falling path delay from PRED going low to FIRE going low.

- Input PRED and output FIRE, as these connect to the simulation environment.

- Size of initial gate in the path, i.e. 10 (for F), and of final gate, i.e. 10 (for C), as these determine the sweep sizes for the input driver and output load inverters in the simulation set-up discussed in the next section.

- The path we're characterizing: PRED- to FIRE-.

**Figure 3.1** Half-way GasP circuit. The icon in the upper right corner of the picture shows the black box representation of the circuit, which has just enough information to characterize the path from PRED falling to FIRE falling.

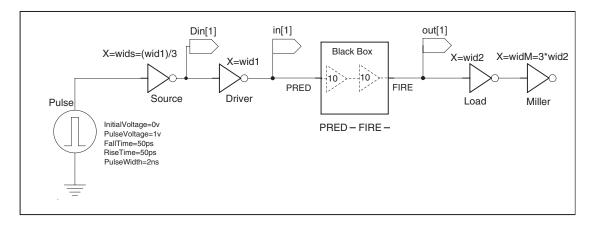

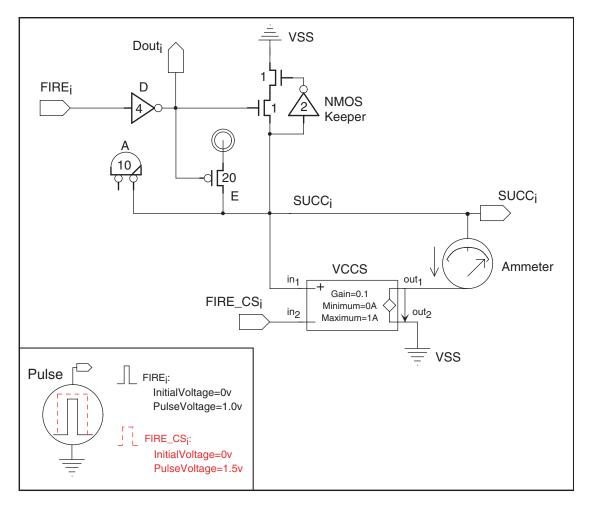

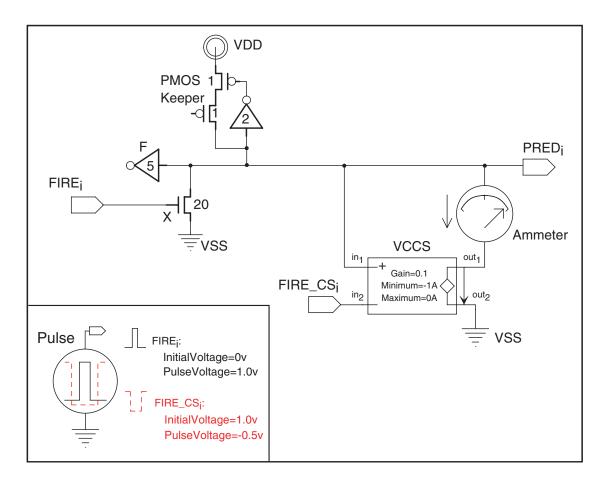

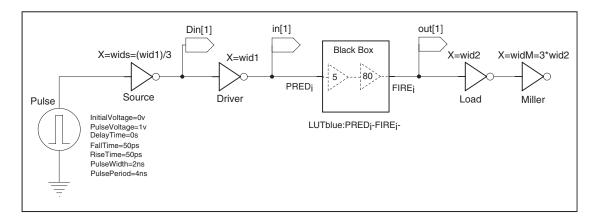

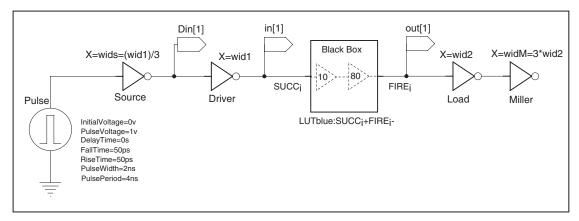

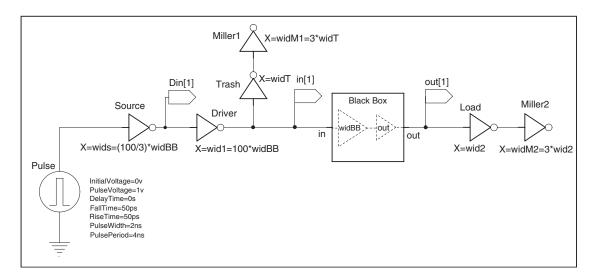

**Figure 3.2** Schematics of the simulation environment for the Half-way GasP circuit in Figure 3.1, with sweep parameters wid1, wid2 and observation nodes in[1], out[1].

### 3.3 Step 2: Create a Simulation Environment for the Design

Figure 3.2 shows the schematics of the simulation environment using the black box icon for the Half-way GasP circuit in Figure 3.1. We use this simulation environment to generate different input slopes for PRED and different output loads for FIRE. We do this by generating different driver sizes wid1 for the inverter that drives PRED, and by using different load sizes wid2 for the inverter that is driven by FIRE. Labels Din[1], in[1] and out[1] are the observation points for measuring delay and slope information. We added a pulse generator to start the different simulation measurements — one per pulse. The generator creates a pulse with a 2ns width and a full-swing slope of 50ps.<sup>3.1</sup> Note that we use a series connection of two inverters between the pulse generator and black box input PRED: a so-called source inverter followed by the already mentioned driver inverter. Note also the step-down of 3 from the size wid1 of the driver inverter to the size wids of the source inverter upstream. A step-down of 3 upstream matches the Logical Effort design strategy [32], and ensures a realistic input slope for the driver input, independent of the slope generated by the pulse generator. We also use a series connection of two inverters for the simulation environment at black box output FIRE: a so-called Miller inverter following the already mentioned load inverter. Note the step-up of 3 downstream from the size wid2 of the load inverter to the size widM of the Miller inverter. The step-up of 3 downstream matches the Logical Effort design strategy, and ensures that the load inverter produces a realistic output load, i.e. it produces just enough source-to-gate 'Miller Effect' for the load inverter as a real environment designed with Logical Effort would produce for the given load size.

<sup>&</sup>lt;sup>3.1</sup>A slope of 50ps works fine for this fictitious example. However, for realistic simulation set-ups, we recommend to use a slope or slew time more typical of a standard inverter operation. For the 90nm CMOS process that we currently use, a typical slope for a full signal swing would correspond to 20ps.

## 3.4 Step 3: Generate Input Files for SPICE

The next two Sections 3.4.1 and 3.4.2 cover the following items:

- Generate a SPICE netlist for the GasP design and its environment.

- Generate a SPICE simulation set-up file.

#### 3.4.1 Generate a SPICE Netlist

The SPICE netlist generated from Electric for the simulation environment in Figure 3.2 is listed in Appendix A.1. The file extension is '.spi'. Unfortunately, we have thus far been unable to force Electric and SPICE to retain the parameter names for the sizes of the driver and load inverters, wid1 and wid2. Instead of a sweep parameter, we get a 'null' value in the SPICE formulas embedded in the inverter and transistor schematics, as is visible from the highlighted yellow-colored text in Figure 3.3. Fortunately, this is not a show-stopper, and so we will proceed to work with the resulting netlist with 'null' values. In Section 3.5.1 we will substitute the 'null' formulas with the correct parameterized formulas containing wid1 and wid2. However, we will add the challenge of finding a more direct solution for generating an Electric-to-SPICE netlist with sweep parameters to our list of future research items — see Section 3.8.

#### 3.4.2 Generate SPICE Simulation Files: HEADER and TRAILER

The two basic SPICE simulation files, the HEADER and the TRAILER, generated from Electric for the simulation environment in Figure 3.2 are listed in Appendix A.2 and Appendix A.3. The file extension is '.hsp'. The header file has additional content with process information. We excluded process information for reasons of confidentiality.

```

*** SUBCIRCUIT NMOS-X_wids FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X wids d g s

** GLOBAL gnd

MNMOSf@0 d g s gnd nch W='null*(1+ABN/sqrt(null*null)))' L='null'

+DELVTO='AVTON/sqrt(null*null)'

.ENDS NMOS-X wids

*** SUBCIRCUIT PMOS-X wids FROM CELL redSix:PMOS{sch}

.SUBCKT PMOS-X wids d g s

** GLOBAL vdd

MPMOSf@0 d g s vdd pch W='null*(1+ABP/sqrt(null*null)))' L='null'

+DELVTO='AVTOP/sqrt(null*null)'

.ENDS PMOS-X wids

*** SUBCIRCUIT NMOS-X wid1 FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X wid1 d g s

** GLOBAL gnd

MNMOSf@0 d g s gnd nch W='null*(1+ABN/sqrt(null*null)))' L='null'

+DELVTO='AVTON/sqrt(null*null)'

.ENDS NMOS-X wid1

*** SUBCIRCUIT PMOS-X_wid1 FROM CELL redSix:PMOS{sch}

.SUBCKT PMOS-X widM d g s

** GLOBAL vdd

MPMOSf@0 d g s vdd pch W='null*(1+ABP/sqrt(null*null)))' L='null'

+DELVTO='AVTOP/sqrt(null*null)'

.ENDS PMOS-X wid1

*** SUBCIRCUIT NMOS-X wid2 FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X_wid2 d g s

** GLOBAL gnd

MNMOSf@O d g s gnd nch W='null*(1+ABN/sqrt(null*null)))' L='null'

+DELVTO='AVTON/sqrt(null*null)'

.ENDS NMOS-X wid2

*** SUBCIRCUIT PMOS-X wid2 FROM CELL redSix:PMOS{sch}

.SUBCKT PMOS-X wid2 d g s

** GLOBAL vdd

MPMOSf@0 d g s vdd pch W='null*(1+ABP/sqrt(null*null)))' L='null'

+DELVTO='AVTOP/sqrt(null*null)'

.ENDS PMOS-X wid2

*** SUBCIRCUIT NMOS-X widM FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X widM d g s

** GLOBAL gnd

MNMOSf@0 d g s gnd nch W='null*(1+ABN/sqrt(null*null)))' L='null'

+DELVTO='AVTON/sgrt(null*null)'

.ENDS NMOS-X_widM

*** SUBCIRCUIT PMOS-X widM FROM CELL redSix:PMOS(sch)

.SUBCKT PMOS-X widM d g s

** GLOBAL vdd

MPMOSf@0 d q s vdd pch W='null*(1+ABP/sqrt(null*null))' L='null'

+DELVTO='AVTOP/sqrt(null*null)'

.ENDS PMOS-X widM

```

**Figure 3.3** SPICE netlist fragments for the source, driver, load and Miller inverters in Figure 3.2. The width and length calculations of the PMOS and NMOS transistors in these parameterized inverter netlists wrongly get 'null' values inserted where the size parameters wid1 and wid2 are used. This incorrect insertion is clearly visible in the highlighted yellow text.

### 3.5 Step 4: Modify the SPICE Input Files

The next two Sections 3.5.1 and 3.5.2 cover the following items:

- In the netlist, create sweep parameters for wid1 and wid2.

- In the simulation set-up files, add sweep and measurement statements.

# 3.5.1 Create Sweep Parameters in the SPICE Netlist

In Section 3.4.1, Figure 3.3, we observed that the parameterized sizes wid1 and wid2 for the driver and load inverters are wrongly expanded into formulas with 'null' in the SPICE netlist parts for the source, driver, load and Miller inverters. We will fix this by substituting the correct formulas. We can derive the correct formulas from the original SPICE text in Electric, or simply by looking at the results for the other inverting gates. Figure 3.4 shows the updated netlist parts with the correct formulas. This substitution process can be easily automated, using a Perl script.

Note that the formulas have size parameters wid1 and wid2. This will enable us to do simulation sweeps and generate look up tables for different values of wid1 and wid2. For completeness and continuity in the Appendices part of this thesis, we have repeated these corrected SPICE netlist portions in Appendix A.4.

```

*** SUBCIRCUIT NMOS-X wids FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X_wids d g s

** GLOBAL and

+DELVTO='AVT0N/sqrt(3*(wid1/3)*2)'

.ENDS NMOS-X_wids

*** SUBCIRCUIT PMOS-X_wids FROM CELL redSix:PMOS{sch}

.SUBCKT PMOS-X_wids dg s

** GLOBAL vdd

+DELVTO='AVTOP/sqrt(2*3*(wid1/3)*2)'

.ENDS PMOS-X wids

*** SUBCIRCUIT NMOS-X wid1 FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X wid1 d q s

* GLOBAL gnd

MNMOSf@0 d g s gnd nch W='3*wid1*(1+ABN/sqrt(3*wid1*2))' L='2'

+DELVTO='AVTON/sqrt(3*wid1*2)'

.ENDS NMOS-X_wid1

*** SUBCIRCUIT PMOS-X wid1 FROM CELL redSix:PMOS{sch}

.SUBCKT PMOS-X_wid1 d g s

** GLOBAL vdd

MPMOSf@0 d g s vdd pch W='2*3*wid1 * (1+ABP/sqrt(2*3*wid1*2 ))' L='2' +DELVTO='AVT0P/sqrt(2*3*wid1*2 )'

.ENDS PMOS-X wid1

*** SUBCIRCUIT NMOS-X wid2 FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X_wid2 d g s

** GLOBAL gnd

MNMOSf@0 d g s gnd nch W='3*wid2*(1+ABN/sqrt(3*wid2*2))' L='2'

+DELVTO='AVTON/sqrt(3*wid2*2)'

.ENDS NMOS-X wid2

*** SUBCIRCUIT PMOS-X_wid2 FROM CELL redSix:PMOS{sch}

.SUBCKT PMOS-X_wid2 d g s

** GLOBAL vdd

\label{eq:MPMOSf00}  \mbox{MPMOSf00 d g s vdd pch W='2*3*wid2*(1+ABP/sqrt(2*3*wid2*2))' L='2' }

+DELVTO='AVTOP/sqrt(2*3*wid2*2)'

.ENDS PMOS-X wid2

*** SUBCIRCUIT NMOS-X widM FROM CELL redSix:NMOS{sch}

.SUBCKT NMOS-X_widM d g s

** GLOBAL gnd

MNMOSf@0 d g s gnd nch W='3*3*wid2*(1+ABN/sqrt(3*3*wid2*2))' L='2'

+DELVTO='AVTON/sqrt(3*3*wid2*2)'

.ENDS NMOS-X widM

*** SUBCIRCUIT PMOS-X widM FROM CELL redSix:PMOS(sch)

.SUBCKT PMOS-X widM d g s

* GLOBAL vdd

MPMOSf@0 d g s vdd pch W='2*3*3*wid2*(1+ABP/sqrt(2*3*3*wid2*2)))' L='2'

+DELVTO='AVTOP/sqrt(2*3*3*wid2*2)

.ENDS PMOS-X widM

```

**Figure 3.4** Corrected SPICE netlist for the source, driver, load and Miller inverters in Figure 3.2. The corrections are highlighted in blue.

# 3.5.2 Add Sweep and Measurement Statements to the TRAILER File

This is the step where we add the sweep commands for simulating the *now correctly* parameterized netlist for a specific range of driver and load sizes (wid1  $\times$  wid2) and where we specify what we want to measure at the observation nodes in[1] and out[1] to generate the slope and delay information discussed on page 15:

- 1.  $(wid1 \times wid2) \rightarrow slope (in[1])$

- 2.  $(\text{wid1} \times \text{wid2}) \rightarrow \text{delay (in[1] to out[1])}$

- 3.  $(wid1 \times wid2) \rightarrow slope (out[1])$

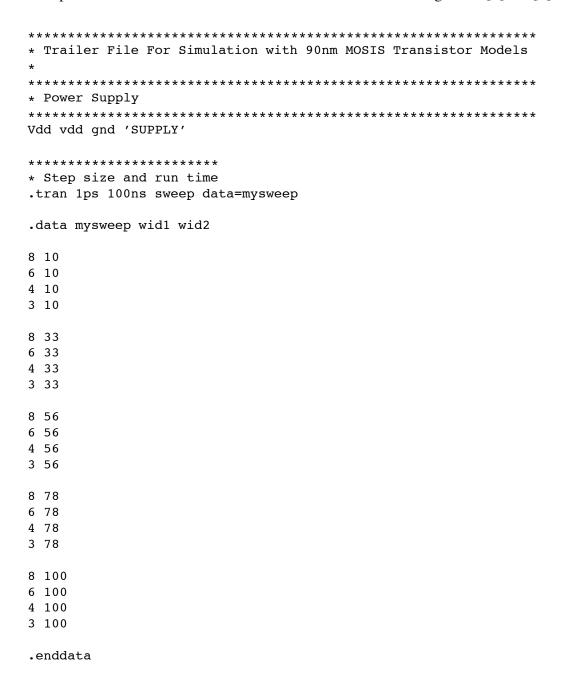

As sweep command, we use the .DATA sweep command explained in HSPICE reference manual [34], Chapter 2: HSPICE and HSPICE RF Netlist Commands, pages 60–66. Our .DATA command uses a row-column matrix input format, where each column contains the values of a single sweep variable and each row contains the full set of sweep values needed for a single sweep. For instance,

.DATA mysweep wid1 wid2

9 5

12 5

#### .ENDDATA

specifies that the first sweep uses value 9 for driver size wid1 and 5 for load size wid2, the second sweep uses the value 12 for wid1 and 5 for wid2, etcetera.

The type of analysis done for our DATA sweep 'mysweep' is specified separately. We use a transient analysis similar to the one specified in [34], Chapter 2, page 62. Each of our sweeps starts by default at 0ps, uses time increments of 1ps, and stops at 100ns:

.TRAN 1ps 100ns SWEEP DATA=mysweep

The measurements done per sweep are specified in a separate .MEASURE statement. The type of .MEASURE statements that we need relate to rise, fall and delay measurements, and are specified in the HSPICE reference manual in [34], Chapter 2, on pages 162–165. We measure rise times from 20% to 80% of the full signal swing from GROUND level (Gnd, VSS) to SUPPLY voltage level (VDD), and we measure fall times from 80% to 20%. We measure input-to-output delays from 50% voltage swing at the input to 50% voltage swing at the output. The syntax for all three measurements is very similar. Here is an example of the syntax for measuring a falling transition on in[1]:

### .MEASURE tfall\_i\_1

- + trig v(in[1]) val='0.8\*SUPPLY' fall=3

- + targ v(in[1]) val='0.2\*SUPPLY' fall=3

The above example specifies that the measurement is triggered as soon as the voltage level for the third falling transition (fall=3) on in[1] reaches 80% of the SUPPLY voltage (val='0.8\*SUPPLY'). It specifies that the measurement ends when the third falling transition on in[1] reaches the target voltage level of 20% the SUPPLY voltage.

Figure 3.5 gives the combined text with the .DATA sweep and the transient analysis, and the slope measurement on input in[1]. Note that there is no need to use capitals for the commands, as we did above. The complete text with all the sweep, analysis and measurement statements for the parameterized netlist of Figure 3.2 follows in Appendix A.5.

## 3.6 Step 5: Generate a SPICE Output File with Look Up Tables

We are now ready to run the two SPICE input files modified in Step 4 (Section 3.5) and to generate an output file with the look up table information that we want. The SPICE output file has extension '.mt0'. The full printout follows in Appendix A.6.

```

* Step size and run time

.tran 1ps 100ns sweep data=mysweep

.data mysweep wid1 wid2

95

125

20 5

9 20

12 20

20 20

9 40

12 40

20 40

9 50

12 50

20 50

.enddata

.measure tfall_i_1

+ trig v(in[1]) val='0.8*SUPPLY' fall=3

+ targ v(in[1]) val='0.2*SUPPLY' fall=3

```

**Figure 3.5** SPICE simulation file fragment, showing the .DATA sweep command and the transient analysis that we use for our library characterizations. We show just one measurement statement, measuring the slope of a falling transition on input in[1].

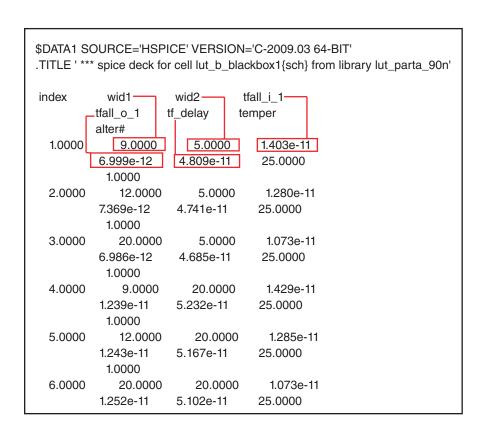

Figure 3.6 contains an excerpt, that we'll use to explain the formatting of the output file:

**Column 1:** The index in the first column gives the sweep iteration number. Note that the numbers use an excessive amount of significant digits. We kept these, because these are the exact results as produced by SPICE. We propose to do any necessary post-processing afterwards, using for instance Microsoft Excel.

Column 2: The second column contains a sequence of three values for each sweep: wid1, tfall\_o\_1 and alter#. The last value is of no importance. The value for wid1 is the width of the driver inverter for the current sweep, and the value for tfall\_o\_1 is the slope or transition time of the falling output transition on out[1]. The significant numbers in the output file are probably realistic only down to a tenth of a picosecond. We can read from Figure 3.6 that the first sweep finds wid1=9 and tfall\_o\_1=6.9ps.

Column 3: The third column contains a sequence of two values for each sweep: wid2 and tf\_delay. Here, wid2 is the width of the load inverter for the current sweep, and tf\_delay the input-to-output or propagation delay for a falling transition on in[1] to the corresponding falling transition on out[1]. We can read from Figure 3.6 that the first sweep finds wid2=5 and tf\_delay=48.1ps

Column 4: The fourth column contains again a sequence of two values for each sweep: tfall\_i\_1 and temper. We will ignore the latter sweep variable for temperature here and focus on tfall\_i\_1 which is the slope or transition time of the falling input transition on in[1]. We can read from Figure 3.6 that the first sweep finds tfall\_i\_1=14ps.

So, all with all, columns 1 to 4 together give us the look up table results that we want, phrased as:  $(wid1 \times wid2) \rightarrow (tfall_i_1, tf_delay, tfall_o_1)$ .

**Figure 3.6** Fragment of the SPICE output file with the look up table data, showing  $(wid1 \times wid2) \rightarrow (tfall\_i\_1, tf\_delay, tfall\_o\_1)$ .

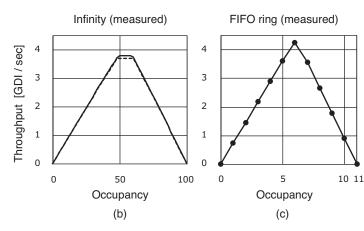

#### 3.7 Validation

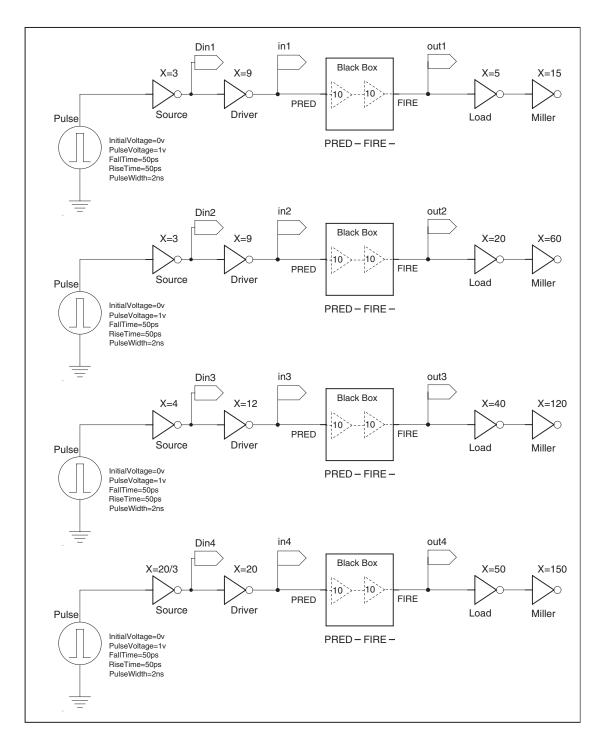

In the introduction Section 3.1, we indicated that there are two ways to sweep the search key values for (wid1  $\times$  wid2) and to generate the resulting delay and slope information for a simple path in a GasP circuit. 'Way one' is to do the sweep work at design time in Electric, and 'way two' is to do the sweep work in SPICE. We followed 'way two' because the alternative produces much larger SPICE output file sizes. In this section, we compare our results against the results obtained with 'way one'.

Figure 3.7 shows four out of the total of twelve sweeps that we ran, covering all possible driver sizes and all possible load sizes, but only four combinations of driver and load sizes. The four sweeps appear as four parallel designs, all designed in Electric. SPICE will run all four designs in parallel. It does this without needing a .DATA sweep command. However, we do need to specify analysis and measurement statements. So, the original five steps that were needed for 'way two' can be simplified to:

**Step 1:** (as before) Use Electric to access the GasP design of Figure 3.1.

**Step 2:** In Electric, create Figure 3.7 with parallel design sweep environments.

**Step 3:** (as before) From Electric, generate input files for SPICE:

- Generate a SPICE netlist for the GasP design and its environment.

- Generate a SPICE simulation set-up file.

**Step 4:** Modify only the SPICE simulation set-up file:

Add transient analysis and measurement statements.

**Step 5:** Run SPICE and capture the look up table results in an output file.

The corresponding SPICE input and output files follow in Appendix B.

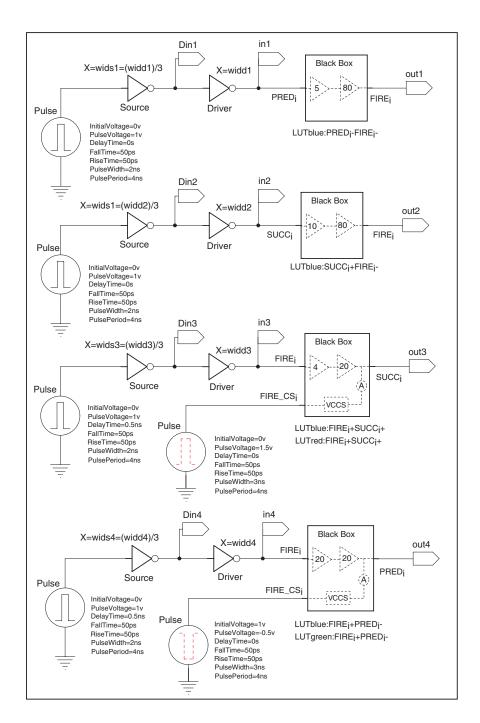

**Figure 3.7** Array schematics for sweeping four combinations of driver and source widths in parallel, using four different instances of the simulation set-up of Figure 3.2. Note that the observation signals are now named Din1 to Din4, in1 to in4, out1 to out 4.

|                                | Driver                    | wid1=9 Load w            | /id2=5       | Driver wid1=9 Load wid2=20  |                          |              |  |  |

|--------------------------------|---------------------------|--------------------------|--------------|-----------------------------|--------------------------|--------------|--|--|

|                                | "Way One"<br>Design Sweep | "Way Two"<br>SPICE Sweep | % Difference | "Way One"<br>Design Sweep   | "Way Two"<br>SPICE Sweep | % Difference |  |  |

| Input Fall time in ps          | 1.38E-11                  | 1.40E-11                 | 1%           | 1.38E-11                    | 1.43E-11                 | 3%           |  |  |

| Output Fall time in ps         | 6.86E-12                  | 7.00E-12                 | 1.9%         | 1.23E-11                    | 1.24E-11                 | 1%           |  |  |

| Transition delay falling in ps | 4.79E-11                  | 4.81E-11                 | 0%           | 5.22E-11                    | 5.23E-11                 | 0%           |  |  |

|                                | Driver v                  | vid1=12 Load v           | /id2=40      | Driver wid1=20 Load wid2=50 |                          |              |  |  |

|                                | "Way One"<br>Design Sweep | "Way Two"<br>SPICE Sweep | % Difference | "Way One"<br>Design Sweep   | "Way Two"<br>SPICE Sweep | % Difference |  |  |

| Input Fall time in ps          | 1.25E-11                  | 1.27E-11                 | 2%           | 1.11E-11                    | 1.08E-11                 | -3%          |  |  |

| Output Fall time in ps         | 1.98E-11                  | 2.03E-11                 | 2%           | 2.41E-11                    | 2.44E-11                 | 1%           |  |  |

| Transition delay falling in ps | 5.68E-11                  | 5.69E-11                 | 0%           | 5.87E-11                    | 5.87E-11                 | 0%           |  |  |

**Figure 3.8** Comparison of the simulation results between 'way one' and 'way two'. 'Way one' is a sweep performed at the design level, using parallel instances of four different simulation environments as illustrated in Figure 3.7. 'Way two' is the approach that we presented in Sections 3.2 to 3.6, where we perform the sweep as part of the SPICE simulation, using .DATA sweep commands.

The table in Figure 3.8 shows a comparison of the results of the four sweeps for 'way one' versus the earlier SPICE sweeps which we have dubbed 'way two'. As before, all measured simulation delays are shown in seconds, with a precision in the order of one tenth of a picosecond. In addition to measured times, we also show the relative difference between 'way one' and 'way two' measurement results, calculated as:

(('way two' or our result) ('way one' or array schematics result)) / ('way two' result)

The results are very similar. The largest differences of -3% and 3% are for input fall times. The good news is that the differences disappear over the length of the path: the differences between the input-to-output path delays are a negligibly 0%.

This is good news because, in the end, it is the path delays that matter. The rise and fall times at input and output nodes are used only to connect the simulation results from one path to the next path in the overall circuit operation, and to compute the combined path delay. The end goal of our look up table results is to allow static timing analysis tools like PrimeTime to compute path delays for relative timing validation of GasP. Relative timing validation amounts to validating that one path has less delay than another path.

Given this background knowledge and the results in Figure 3.8, we may conclude that a difference of 3% for the input slope of a path is not going to matter. In summary: the results obtained via 'way one' are similar to those obtained by 'way two'.

# 3.8 Conclusion and Future Work for Chapter 3

We created a characterization flow for generating look up tables with timing information for a simple input-to-output transition in a simplified 6-4 GasP circuit. This chapter is dubbed 'PART-A' because it has a follow-up part. PART-B, in the next chapter, shows how to characterize a complete 6-4 GasP module. In PART-B, we will partition the behavior of a 6-4 GasP FIFO circuit into simple input-to-output transitions and simplified circuits that can be fed back into the library characterization flow developed here in PART-A. Given that "the proof of the pudding is in the eating", we will feed the look up tables that we generate in PART-B to a standard static timing analysis tool to validate the relative timing constrains of the 6-4 GasP FIFO module. This happens in Chapter 5. As far as future work goes, the characterization flow in PART-A can benefit from:

### 1. Flow automation:

- We need templates for Steps 1–2, to automate the creation of simulation environments like Figure 3.2 and 3.7, for different GasP circuits in Electric.

- We need scripts to automate the SPICE simulation part in Steps 3–5.

- 2. A direct solution for creating sweep variables wid1 and wid2 for the driver and load inverters in the simulation environment at the schematic level of Electric:

- Currently, Electric produces 'null' values for the sweep parameters wid1 and wid2 in Figure 3.2. This is visible from the SPICE netlist that we generate in Step 3. We correct this in Step 4, but it would be much better to avoid the need for such a correction.

# Chapter 4

#### LIBRARY CHARACTERIZATION PART-B: FROM GASP TO LUTS