# Portland State University PDXScholar

Dissertations and Theses

Dissertations and Theses

1-1-2011

# Evolving Nano-scale Associative Memories with Memristors

Arpita Sinha

Portland State University

# Let us know how access to this document benefits you.

Follow this and additional works at: http://pdxscholar.library.pdx.edu/open access etds

#### Recommended Citation

Sinha, Arpita, "Evolving Nano-scale Associative Memories with Memristors" (2011). Dissertations and Theses. Paper 445.

10.15760/etd.445

This Thesis is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact pdxscholar@pdx.edu.

## Evolving Nano-scale Associative Memories with Memristors

# by

# Arpita Sinha

A thesis submitted in partial fulfillment of the requirements for the degree of

> Thesis Committee: Christof Teuscher, Chair Dan Hammerstrom Xiaoyu Song

Portland State University 2011

#### Abstract

Associative Memories (AMs) are essential building blocks for brain-like intelligent computing with applications in artificial vision, speech recognition, artificial intelligence, and robotics. Computations for such applications typically rely on spatial and temporal associations in the input patterns and need to be robust against noise and incomplete patterns. The conventional method for implementing AMs is through Artificial Neural Networks (ANNs).

Improving the density of ANN based on conventional circuit elements poses a challenge as devices reach their physical scalability limits. Furthermore, stored information in AMs is vulnerable to destructive input signals. Novel nano-scale components, such as memristors, represent one solution to the density problem. Memristors are non-linear time-dependent circuit elements with an inherently small form factor. However, novel neuromorphic circuits typically use memristors to replace synapses in conventional ANN circuits. This sub-optimal use is primarily because there is no established design methodology to exploit the memristor's non-linear properties in a more encompassing way.

The objective of this thesis is to explore denser and more robust AM designs using memristor networks. We hypothesize that such network AMs will be more area-efficient than the traditional ANN designs if we can use the memristor's non-linear property for spatial and time-dependent temporal association. We have built a comprehensive simulation framework that employs Genetic Programming (GP) to evolve AM circuits with memristors. The framework is based on the ParadisEO metaheuristics API and uses naspice for the circuit evaluation.

Our results show that we can evolve efficient memristor-based networks that have the potential to replace conventional ANNs used for AMs. We obtained AMs that a) can learn spatial and temporal correlation in the input patterns; b) optimize the trade-off between the size and the accuracy of the circuits; and c) are robust against destructive noise in the inputs. This robustness was achieved at the expense of additional components in the network.

We have shown that automated circuit discovery is a promising tool for memristorbased circuits. Future work will focus on evolving circuits that can be used as a building block for more complicated intelligent computing architectures.

### Acknowledgements

I would like to express my heart-felt gratitude to a number of people without whose support this thesis would not have been possible. My advisor Dr. Christof Teuscher for his continuous guidance and encouragement throughout the course of my graduate studies. Alireza and Haera, with whom I had many interesting and stimulating discussions. Prof. Dan Hammerstrom and Prof. Xiaoyu Song for agreeing to serve as members of my thesis committee. Fellow graduate students (both past and present) of our lab for their help, inspiration, exchange of ideas, and sincere feedback. My friends at PSU, for making the time spent here a memorable one. And most of all, my husband for his unending support and love.

# Contents

| $\mathbf{A}$ | bstra | ıct     |                                                              | i   |

|--------------|-------|---------|--------------------------------------------------------------|-----|

| $\mathbf{A}$ | ckno  | wledger | nents                                                        | iii |

| Li           | st of | Tables  |                                                              | ix  |

| Li           | st of | Figure  | ${f s}$                                                      | Х   |

| 1            | Inti  | oductio | on                                                           | 1   |

|              | 1.1   | High-L  | evel Associative Memories: Biological Implication            | 2   |

|              | 1.2   | Associa | ative Memory Implementation with Artificial Neural Networks: |     |

|              |       | Design  | and Challenges                                               | 3   |

|              | 1.3   | Exploit | ting Memristors: Towards Nano-scale Designs                  | 7   |

|              | 1.4   | Genetic | c Programming: Exploring the Memristor Design Space          | 9   |

|              | 1.5   | Thesis  | Statement                                                    | 10  |

|              | 1.6   | Thesis  | Contribution                                                 | 12  |

|              | 1.7   | Thesis  | Organization                                                 | 14  |

| 2            | Me    | thodolo | $\mathbf{g}\mathbf{y}$                                       | 16  |

|              | 2.1   | Genetic | e Programming: History and Context                           | 16  |

|              | 2.2   | The Ba  | asics of GP                                                  | 18  |

|              |       | 2.2.1   | Node assignment                                              | 18  |

|              |       | 2.2.2   | Genetic representation                                       | 19  |

|              |       | 223     | Population initialization                                    | 19  |

|      | 2.2.4              | Genetic operations                                                                                                                                                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 2.2.5              | Fitness function                                                                                                                                                      | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.2.6              | Replacement strategy                                                                                                                                                  | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.2.7              | The GP algorithm                                                                                                                                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3  | Adapt              | ing GP for Automated Circuit Design                                                                                                                                   | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.3.1              | Circuit initialization                                                                                                                                                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.3.2              | Circuit representation                                                                                                                                                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.3.3              | Circuit evaluation                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.3.4              | Mutation operation                                                                                                                                                    | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.3.5              | GP implementation in C3EA                                                                                                                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.4  | Archit             | ecture of C3EA                                                                                                                                                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.4.1              | The evolver algorithm                                                                                                                                                 | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.4.2              | Features of C3EA                                                                                                                                                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.5  | Param              | eter Exploration                                                                                                                                                      | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.5.1              | Population size                                                                                                                                                       | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.5.2              | Mutation functions                                                                                                                                                    | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.5.3              | Mutation rates                                                                                                                                                        | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.5.4              | Replacement strategy                                                                                                                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.6  | Discus             | sion                                                                                                                                                                  | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Vali | dation             |                                                                                                                                                                       | <b>4</b> 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.1  | Low-P              | ass Filter                                                                                                                                                            | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.1.1              | Embryo circuit                                                                                                                                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.1.2              | Component, function, and terminal nodes                                                                                                                               | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.1.3              | Fitness measure                                                                                                                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.1.4              | Control parameters                                                                                                                                                    | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.4<br>2.5<br>Vali | 2.2.5 2.2.6 2.2.7 2.3 Adapt 2.3.1 2.3.2 2.3.3 2.3.4 2.3.5 2.4 Archit 2.4.1 2.4.2 2.5 Param 2.5.1 2.5.2 2.5.3 2.5.4 2.6 Discus  Validation 3.1 Low-P 3.1.1 3.1.2 3.1.3 | 2.2.5 Fitness function 2.2.6 Replacement strategy 2.2.7 The GP algorithm  2.3 Adapting GP for Automated Circuit Design 2.3.1 Circuit initialization 2.3.2 Circuit representation 2.3.3 Circuit evaluation 2.3.4 Mutation operation 2.3.5 GP implementation in C3EA  2.4 Architecture of C3EA 2.4.1 The evolver algorithm 2.4.2 Features of C3EA 2.5 Parameter Exploration 2.5.1 Population size 2.5.2 Mutation functions 2.5.3 Mutation rates 2.5.4 Replacement strategy 2.6 Discussion  Validation  3.1 Low-Pass Filter 3.1.1 Embryo circuit 3.1.2 Component, function, and terminal nodes 3.1.3 Fitness measure |

|   |     | 3.1.5   | Results for low-pass filter                             | 49 |

|---|-----|---------|---------------------------------------------------------|----|

|   | 3.2 | Hodgl   | xin-Huxley Neuron Model                                 | 52 |

|   |     | 3.2.1   | Embryo circuit                                          | 52 |

|   |     | 3.2.2   | Component, function, and terminal nodes                 | 52 |

|   |     | 3.2.3   | Fitness measure                                         | 54 |

|   |     | 3.2.4   | Control parameters                                      | 57 |

|   |     | 3.2.5   | Results for the Hodgkin-Huxley model                    | 57 |

|   | 3.3 | Discus  | ssion                                                   | 60 |

| 4 | Res | ults: I | Evolving Spatial Associative Memories                   | 61 |

|   | 4.1 | The S   | Spatial Association Problem                             | 61 |

|   | 4.2 | Exper   | iment 1: Basic spatial AM with sinusoidal input signals | 61 |

|   |     | 4.2.1   | Embryo circuit                                          | 63 |

|   |     | 4.2.2   | Component, function, and terminal nodes                 | 64 |

|   |     | 4.2.3   | Fitness measure                                         | 66 |

|   |     | 4.2.4   | Control parameters                                      | 67 |

|   |     | 4.2.5   | Results for basic spatial AM                            | 67 |

|   |     | 4.2.6   | Discussion                                              | 71 |

|   | 4.3 | Exper   | iment 2: The size vs. accuracy trade-off                | 71 |

|   |     | 4.3.1   | Fitness measure                                         | 72 |

|   |     | 4.3.2   | Results for size vs. accuracy trade-off                 | 72 |

|   |     | 4.3.3   | Discussion                                              | 74 |

|   | 4.4 | Exper   | iment 3: Basic spatial AM with pulsed input signals     | 74 |

|   |     | 4.4.1   | Fitness measure                                         | 74 |

|   |     | 4.4.2   | Results for basic spatial AM with pulsed inputs         | 76 |

|   |     | 443     | Discussion                                              | 70 |

|   | 4.5 | Exper   | iment 4: Noise tolerant spatial AM 82             |

|---|-----|---------|---------------------------------------------------|

|   |     | 4.5.1   | Embryo circuit                                    |

|   |     | 4.5.2   | Fitness measure                                   |

|   |     | 4.5.3   | Results for noise-tolerant AM                     |

|   |     | 4.5.4   | Discussion                                        |

|   | 4.6 | Discus  | ssion                                             |

| 5 | Res | ults: I | Evolving Temporal Associative Memories 93         |

|   | 5.1 | Temp    | oral Association Problem                          |

|   | 5.2 | Exper   | iment 4: Context sensitive system                 |

|   |     | 5.2.1   | Embryo circuit                                    |

|   |     | 5.2.2   | Component, function and terminal nodes            |

|   |     | 5.2.3   | Fitness measure                                   |

|   |     | 5.2.4   | Control parameters                                |

|   |     | 5.2.5   | Results for context-sensitive system design       |

|   |     | 5.2.6   | Discussion                                        |

|   | 5.3 | Exper   | iment 5: Sequence test and limitation check       |

|   |     | 5.3.1   | Experiment 5a: Sequence test                      |

|   |     | 5.3.2   | Experiment 5b: Voltage limit test                 |

|   |     | 5.3.3   | Experiment 5c: Frequency limit test               |

|   |     | 5.3.4   | Discussion                                        |

|   | 5.4 | Exper   | iment 6: Evolving variation tolerant AM           |

|   |     | 5.4.1   | Experiment 6a: Evolving voltage-tolerant AM 109   |

|   |     | 5.4.2   | Experiment 6b: Evolving frequency-tolerant AM 113 |

|   |     | 5.4.3   | Discussion                                        |

|   | 5.5 | Discus  | ssion 110                                         |

| 6  | Conclusion     |                   |     |  |  |  |

|----|----------------|-------------------|-----|--|--|--|

|    | 6.1            | Contributions     | 121 |  |  |  |

|    | 6.2            | Future directions | 123 |  |  |  |

| Re | References 124 |                   |     |  |  |  |

# List of Tables

| 3.1 | Components and parameter ranges used in low-pass filter evolution. | 47 |

|-----|--------------------------------------------------------------------|----|

| 3.2 | Additional components and their parameter ranges used in Hodgkin-  |    |

|     | Huxley model evolution                                             | 54 |

| 4.1 | Memristors as component nodes used in AM evolution                 | 65 |

| 4.2 | Summarizing the size vs. accuracy trade-off                        | 73 |

# List of Figures

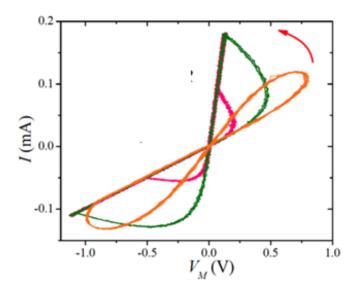

| 1.1 | An example of the non-linear characteristic in the I–V plot of a               |    |

|-----|--------------------------------------------------------------------------------|----|

|     | memristor. Figure re-drawn from [11]                                           | 8  |

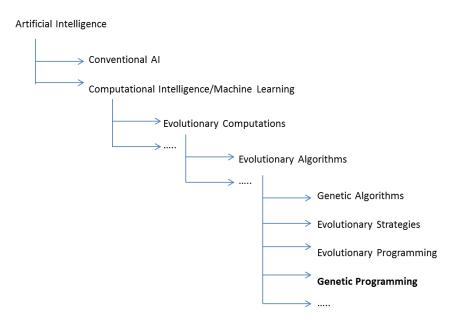

| 2.1 | Placing Genetic Programming in the context of related research.                |    |

|     | Figure redrawn from [13]                                                       | 17 |

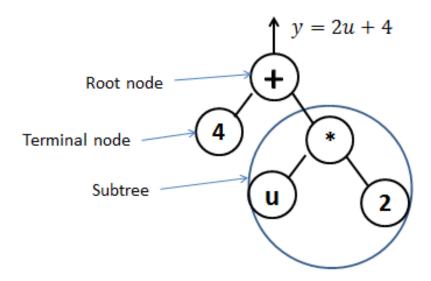

| 2.2 | An example of a program tree illustrating how the root, terminals              |    |

|     | and subtrees are defined in tree-based GP. Depth-first execution of            |    |

|     | this tree would yield the output $y = 4 + 2u$                                  | 20 |

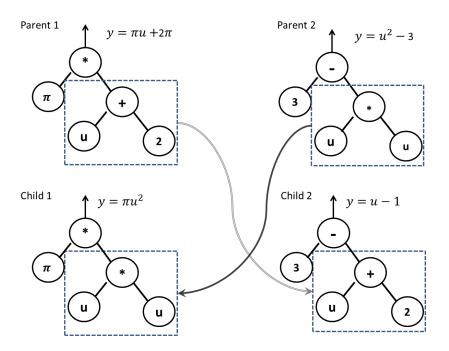

| 2.3 | An example of crossover operation carried out on parents 1 and 2               |    |

|     | to yield children 1 and 2. The crossover operator picks randomly               |    |

|     | chosen subtrees from parent 1 (at node +) and parent 2 (at node *)             |    |

|     | and switch them in child 1 and child 2                                         | 21 |

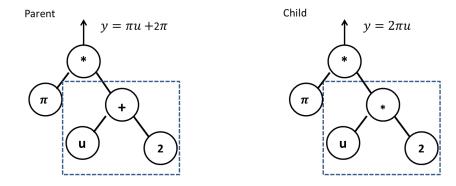

| 2.4 | An example of mutation operation working on functional node '+'                |    |

|     | of the parent and transforming it to functional node '*' in the child          |    |

|     | thus changing the interpreted output from $y = \pi u + 2\pi$ to $y = 2\pi u$ . | 22 |

| 2.5 | The GP learning algorithm.                                                     | 25 |

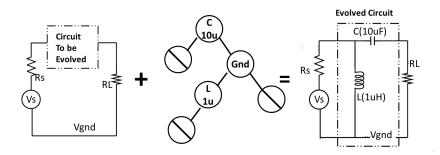

| 2.6 | An example of an embryo circuit and a randomly generated tree,                 |    |

|     | mapped together into a fully developed circuit                                 | 27 |

| 2.7 | Examples of how the additional mutation operators transform the                |    |

|     | parent tree. Nodes in blue are inherited from the parent and nodes             |    |

|     | in red are transformed because of the respective mutation function.            | 32 |

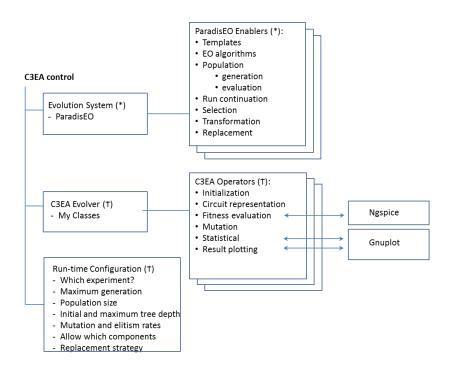

| 2.8  | The architecture of C3EA, a mix of elements inherited from the         |    |

|------|------------------------------------------------------------------------|----|

|      | ParadisEO framework (*) and elements added or redefined by C3EA        |    |

|      | (†)                                                                    | 36 |

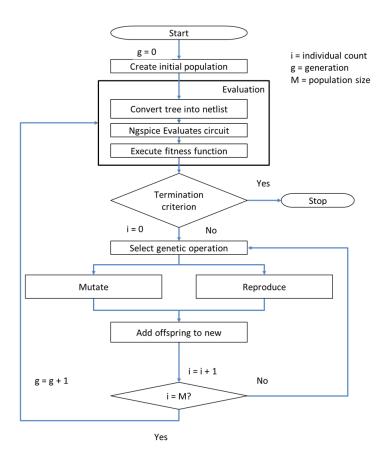

| 2.9  | A flowchart of the GP algorithm as used by C3EA                        | 37 |

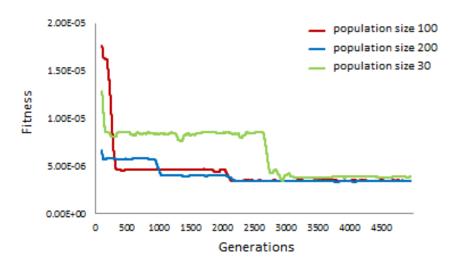

| 2.10 | Comparison of different population sizes and their effect on evolution |    |

|      | of basic associative memory. We observe that population sizes of 100   |    |

|      | and 200 converge around generation 2,000, while a population size      |    |

|      | of 30 takes 1,200 more generations to converge to the best fitness     |    |

|      | value                                                                  | 40 |

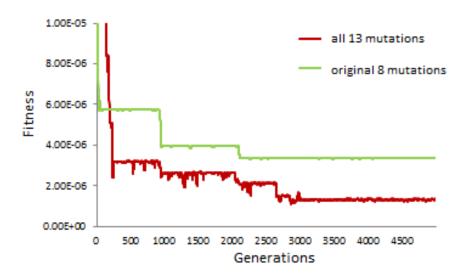

| 2.11 | Justification for additional mutation functions. We compare evolu-     |    |

|      | tion of basic associative memories using original 8 original mutations |    |

|      | vs. using all 13 mutations. While runs using original 8 mutations      |    |

|      | converge at a local optima, the runs using all 13 mutations converge   |    |

|      | at the actual solution                                                 | 41 |

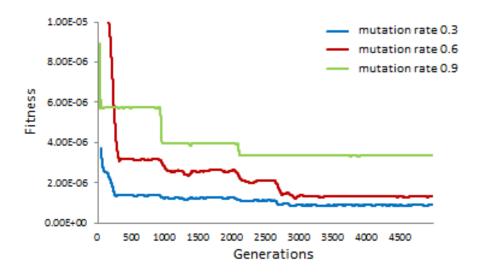

| 2.12 | Comparison of different mutation rates for basic AM evolution. We      |    |

|      | observe that a lower mutation rate of $0.3$ ensures smoother evolution |    |

|      | and converges faster than higher mutation rates of 0.6 and 0.9. $$     | 42 |

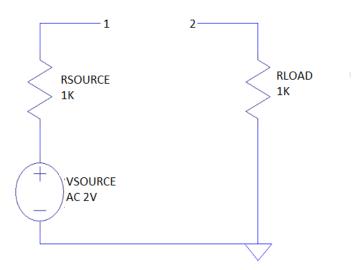

| 3.1  | A one-input one-output embryo circuit used for the low-pass filter     |    |

|      | circuit. The input appears at VSOURCE, and the output is probed        |    |

|      | at node 2. The mapped sub-circuit from a tree is added between         |    |

|      | connection points 1 and 2. RSOURCE and RLOAD are $1k\Omega$ resistors. | 46 |

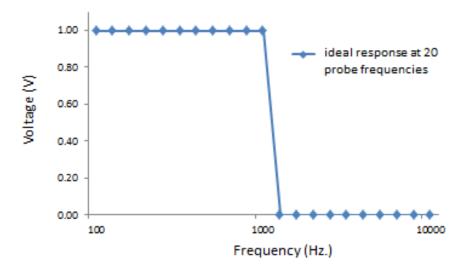

| 3.2  | The ideal $1kHz$ low-pass filter frequency-domain response and 20      |    |

|      | probe frequencies ranging from $100Hz$ to $10kHz$ used in fitness      |    |

|      | evaluation for the candidate solution circuits                         | 48 |

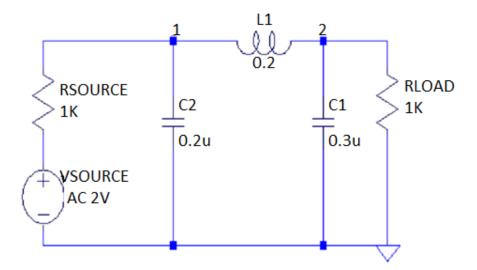

| 3.3 | The best-evolved low-pass filter circuit with two capacitors and one        |    |

|-----|-----------------------------------------------------------------------------|----|

|     | inductor. All five GP runs converged to the same circuit as the             |    |

|     | optimum solution                                                            | 50 |

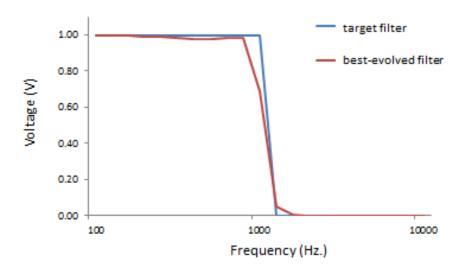

| 3.4 | Frequency response of the best-evolved circuit compared with the            |    |

|     | ideal low-pass filter response. Here the average error for each of the      |    |

|     | 20 frequency probe points is $5mV$ , which implies the circuit is $99.5\%$  |    |

|     | similar to the ideal behavior                                               | 50 |

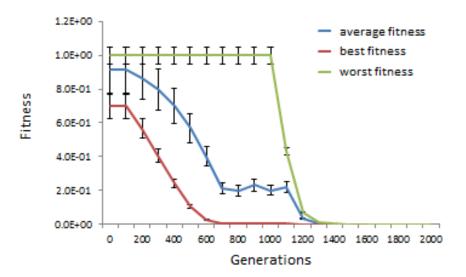

| 3.5 | Fitness averaged over five GP runs for evolving low-pass filter. Here       |    |

|     | the error-bars denote the standard deviation over the five runs. Both       |    |

|     | the standard deviation and the fitness value decrease as the evolu-         |    |

|     | tion progresses toward the solution                                         | 51 |

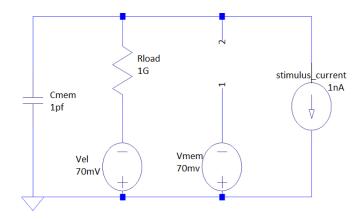

| 3.6 | A one-input one-output embryo circuit used for the Hodgkin-Huxley           |    |

|     | potassium-ion-channel circuit. The stimulus current of $1nA$ desta-         |    |

|     | bilizes the system. The $V_{el}$ and $R_{load}$ combination, drive the ions |    |

|     | through the membrane sub-circuit to be evolved between connec-              |    |

|     | tion points 1 and 2. The voltage source $V_{mem}$ (70mV) represents         |    |

|     | the membrane potential and capacitor $C_{mem}$ represents the mem-          |    |

|     | brane capacitance. The output is probed at connection point 2               | 53 |

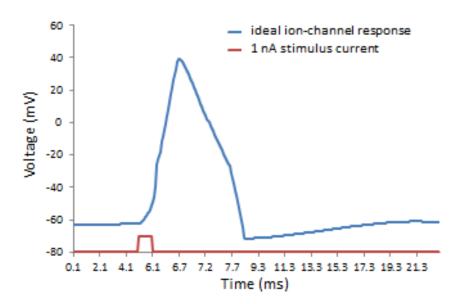

| 3.7 | The ideal Hodgkin-Huxley potassium-ion-channel response to $1nA$            |    |

|     | stimulus current presented between the 5 ms and 6 ms time-steps.            |    |

|     | This ideal response has been extracted from the <i>HHsim</i> simulation     |    |

|     | environment. There are 201 data points for the fitness evaluation           |    |

|     | of the candidate circuits. The data points are sampled every $0.1ms$        |    |

|     | between $0ms$ and $23ms$                                                    | 55 |

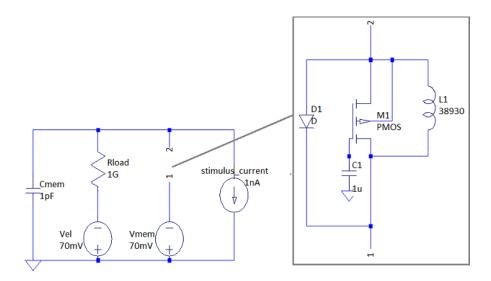

| 3.8  | The best-evolved equivalent circuit for the Hodgkin-Huxley potassium-   |    |

|------|-------------------------------------------------------------------------|----|

|      | ion-channel model. It comprised of four components: a capacitor,        |    |

|      | an inductor, a p-type MOSFET, and a diode. Three of the five GP         |    |

|      | runs converged to the same circuit as the optimum solution. The         |    |

|      | other two had additional redundant component                            | 58 |

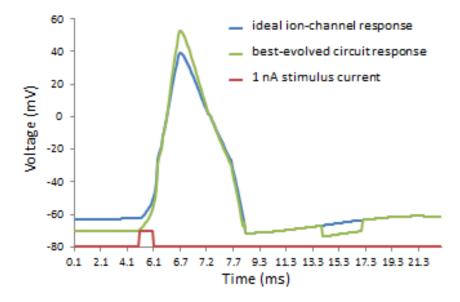

| 3.9  | The transient response of the best-evolved circuit compared with        |    |

|      | the ideal Hodgkin-Huxley potassium-ion-channel response. Here the       |    |

|      | average error for each of the 231 data points is $0.5mV$ . The sudden   |    |

|      | drop in the voltage between $14ms$ and $17ms$ is due to the discharging |    |

|      | of the capacitor when the p-type MOSFET turns temporarily on            |    |

|      | during the same time-frame                                              | 58 |

| 3.10 | The fitness averaged over five GP runs for evolving the Hodgkin-        |    |

|      | Huxley model. Here, the worst and the average fitness plots are         |    |

|      | noisy because the plots presented are averaged over five runs each      |    |

|      | having a different replacement strategy, and hence the evolution        |    |

|      | would vary a lot from one run to the other                              | 59 |

| 3.11 | The best-evolved fitness averaged over five GP runs for evolving the    |    |

|      | Hodgkin-Huxley model. Here the error-bars represent the standard        |    |

|      | deviation between the runs. Both the fitness value and the error de-    |    |

|      | crease as the evolution progresses and finally converge to a solution   |    |

|      | in less than a 1,000 generations.                                       | 60 |

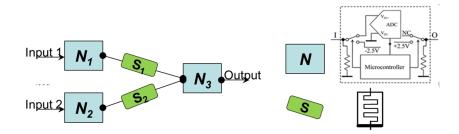

| 4.1 | An example of the ANN-based AM design. N1, N2 are neurons that            |

|-----|---------------------------------------------------------------------------|

|     | lie on the input layer and N3 is a neuron on the output layer. S2 and     |

|     | S2 are the synapses interconnecting the input and the output neuron       |

|     | layers. Both neurons and synapses are traditionally implemented           |

|     | using resistors, op-amps, etc. More recently, Yuriy and Massimiliano      |

|     | [69] have implemented synapses with memristors. Figure re-drawn           |

|     | from [69]                                                                 |

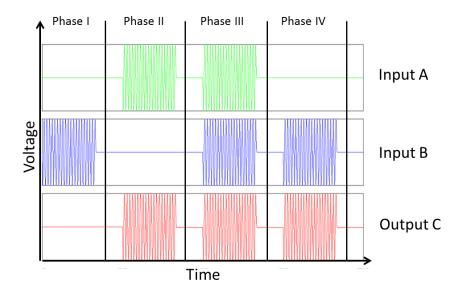

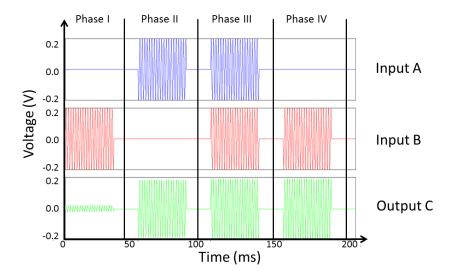

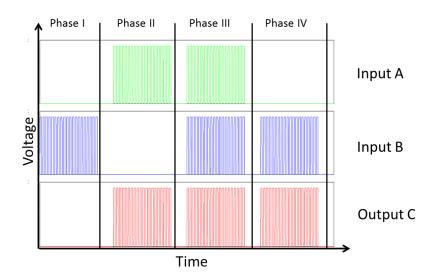

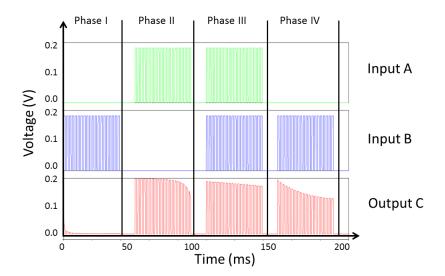

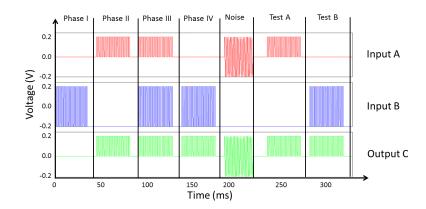

| 4.2 | The four phases in the evaluation of an AM block. Phase I, where          |

|     | the second $Input\ B$ does not stimulate the $Output\ C$ . Phase II,      |

|     | where the first $Input\ A$ strongly stimulates $Output\ C$ . Phase III is |

|     | the training phase, where the two inputs become associated. Phase         |

|     | IV, where the $Input\ B$ starts strongly stimulating the $Output\ C$ .    |

|     | The ideal basic AM response to inputs presented during the four           |

|     | phases as sinusoidal signal trains, each of amplitude $0.2V$ , frequency  |

|     | of $600Hz$ and of duration $33.3ms$ . There are 2,001 data points for     |

|     | fitness evaluation of candidate circuits. The data points are sampled     |

|     | every $0.1ms$ between $0ms$ and $200ms$ 63                                |

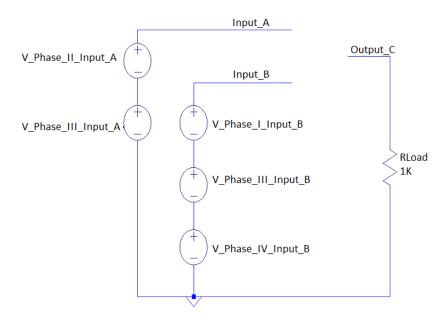

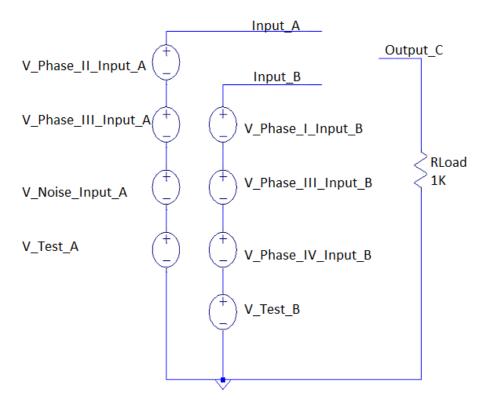

| 4.3 | The embryo circuit for basic AM experiments. There are five volt-                                  |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | age sources. $V\_Phase\_I\_Input\_B$ creates excitatory inputs at con-                             |    |

|     | nection point Input_B during Phase I, $V\_Phase\_II\_Input\_A$ cre-                                |    |

|     | ates excitatory inputs at connection point Input_A during Phase                                    |    |

|     | $II,\ V\_Phase\_III\_Input\_A\ {\it and}\ V\_Phase\_III\_Input\_A\ {\it create}\ {\it excitation}$ |    |

|     | tatory inputs at connection point Input_A and Input_B respectively                                 |    |

|     | during Phase III and V_Phase_IV_Input_B excites Input_B during                                     |    |

|     | Phase IV. $R_{Load}$ is a $1k\Omega$ load resistor and Output_C is the probe                       |    |

|     | point. The candidate AM block design evolves as a sub-circuit be-                                  |    |

|     | tween the connection points Input_A, Input_B, and Output_C                                         | 64 |

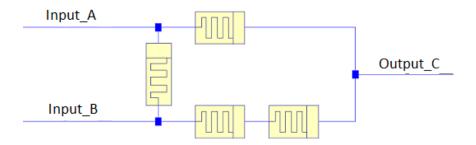

| 4.4 | The best-evolved equivalent circuit for the basic spatial AM func-                                 |    |

|     | tionality. It comprised of four two-terminal memristors. Seven of                                  |    |

|     | the ten GP runs with weight $w$ set to 50% converged to the same cir-                              |    |

|     | cuit as the optimum solution. The other three runs evolved circuits                                |    |

|     | with more components                                                                               | 68 |

| 4.5 | The transient response of the best-evolved basic AM circuit. Here                                  |    |

|     | the error was observed mostly in the $Phase\ I$ of the basic AM eval-                              |    |

|     | uation. The maximum noise amplitude is observed as $20mV$ giving                                   |    |

|     | a signal-to-noise ratio of 10                                                                      | 69 |

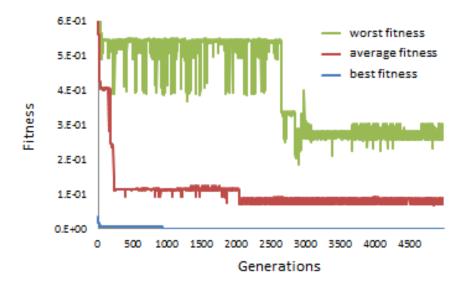

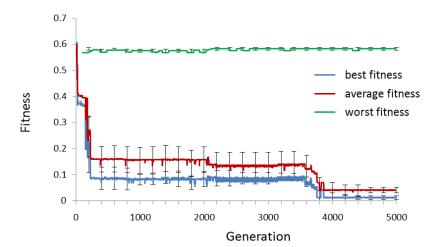

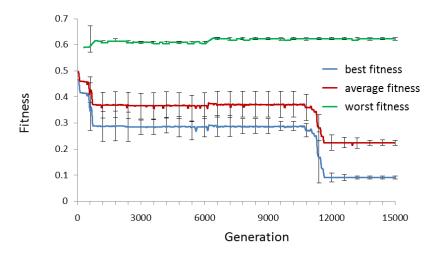

| 4.6 | The fitness averaged over ten GP runs for evolving the basic spatial                               |    |

|     | AM design. Here, the average fitness plots are noisy because the                                   |    |

|     | plots presented are averaged over ten runs each having a different                                 |    |

|     | replacement strategy and hence the evolution would vary a lot from                                 |    |

|     | one run to the other                                                                               | 70 |

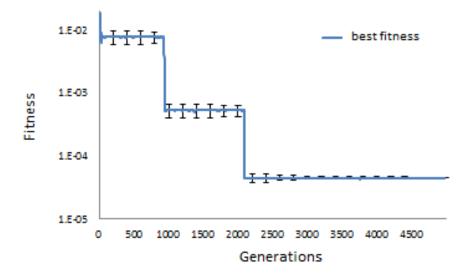

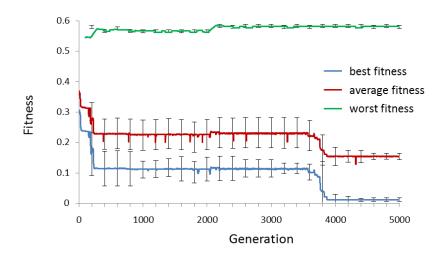

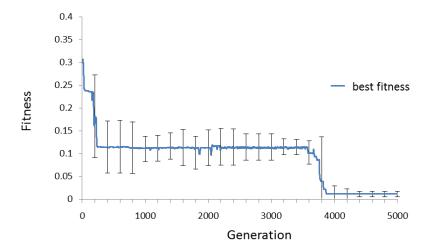

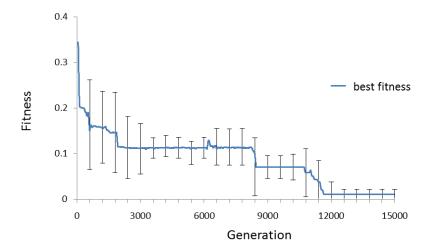

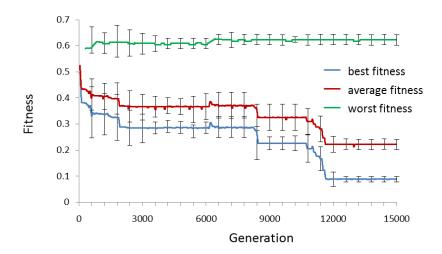

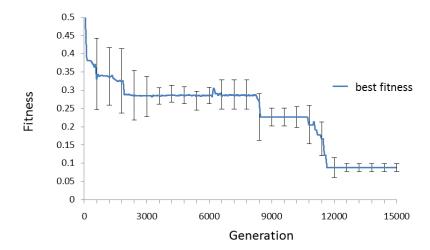

| 4.7  | The best-evolved fitness averaged over ten GP runs for evolving         |    |

|------|-------------------------------------------------------------------------|----|

|      | the basic spatial AM design. Here, the error-bars represent the         |    |

|      | standard deviation between the runs. Both the fitness value and         |    |

|      | the error decrease as the evolution progresses and finally converge     |    |

|      | to a solution around $4{,}000^{th}$ generation                          | 70 |

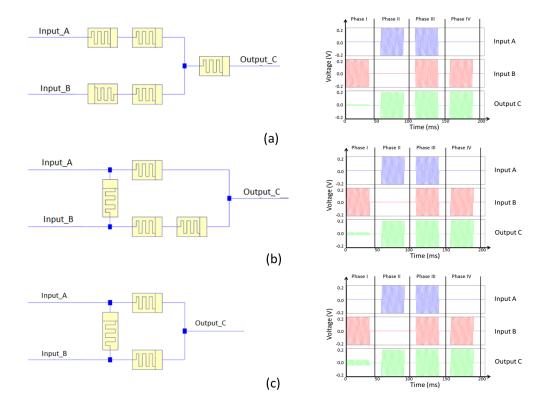

| 4.8  | The best-evolved basic AM designs and their transient responses         |    |

|      | with (a) weight $w=1\%$ , (b) weight $w=50\%$ , and (c) $w=75\%$ .      |    |

|      | We observe that the noise amplitude in $Phase\ I$ drops considerably    |    |

|      | as the weight on size is lowered                                        | 73 |

| 4.9  | The ideal basic AM response to pulsed inputs presented during the       |    |

|      | four phases of evaluation. In each phase, the inputs are presented      |    |

|      | as 20 pulse signal trains, each of amplitude $0.2V$ , pulse duration of |    |

|      | 1ms and time period of $2ms$ . There are 2,001 data points for fitness  |    |

|      | evaluation of candidate circuits. The data points are sampled every     |    |

|      | 0.1ms between $0ms$ and $200ms$                                         | 75 |

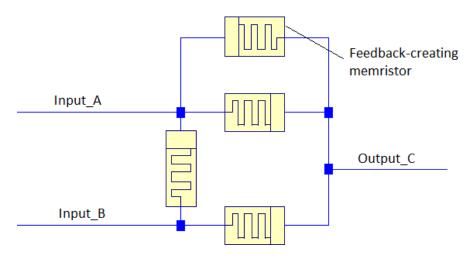

| 4.10 | The best-evolved equivalent circuit for the basic spatial AM design     |    |

|      | using pulse train as input. It comprised of four two-terminal mem-      |    |

|      | ristors. This design is fundamentally different from the basic AM       |    |

|      | design using sinusoidal inputs because of the presence of a feedback-   |    |

|      | creating memristor                                                      | 77 |

|    | The transient response of the best-evolved basic AM circuit. Here      | 4.11 |

|----|------------------------------------------------------------------------|------|

|    | the error was observed mostly in the $Phase\ I$ of the basic AM evalu- |      |

|    | ation. The average noise amplitude is observed in $Phase\ I$ is $12mV$ |      |

|    | giving a signal-to-noise ratio of 16. We also observe that the am-     |      |

|    | plitude of voltage observed during $Phases\ II-IV$ at the probe point  |      |

|    | Output_C changes its value incrementally with each pulse in the sig-   |      |

|    | nal train, indicating that the memristor's non-linearity is being put  |      |

| 78 | to use                                                                 |      |

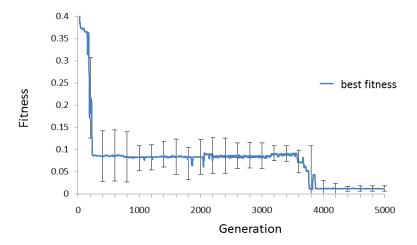

|    | 2 The fitness averaged over ten GP runs for evolving the pulsed input  | 4.12 |

|    | spatial AM design. Here, the error-bars represent the standard de-     |      |

|    | viation between the runs. The average fitness plots are noisy because  |      |

|    | the plots presented are averaged over ten runs each having a differ-   |      |

|    | ent replacement strategy and the evolution varies from one run to      |      |

| 80 | the other                                                              |      |

|    | 3 The best-evolved fitness averaged over ten GP runs for evolving the  | 4.13 |

|    | pulsed input spatial AM design. Here, the error-bars represent the     |      |

|    | standard deviation between the runs. Both the fitness value and the    |      |

|    | error decrease as the evolution progresses and finally converge to a   |      |

| 81 | solution around, the $4{,}000^{th}$ generation                         |      |

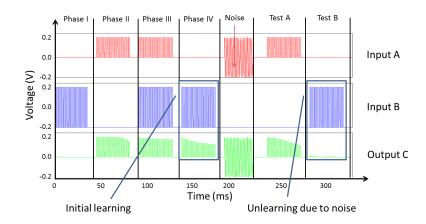

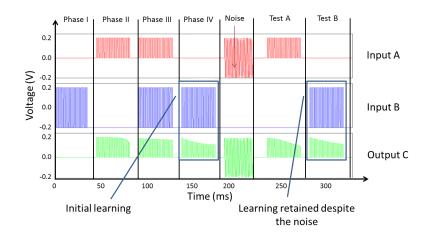

| 4.14 | The best-evolved spike-based AM design was subjected to sinusoidal           |    |

|------|------------------------------------------------------------------------------|----|

|      | noise on Input_A during the phase Noise. Subsequently, in phase              |    |

|      | $Test\ A$ and $Test\ B$ , we tested if the original spike train could retain |    |

|      | its initial learning and still stimulate the probe point Output_C.           |    |

|      | We observed that while Input_A could still stimulate the Output_C,           |    |

|      | the noise was destructive for Input_B's learnt association. Input_B          |    |

|      | could no longer stimulate the Output_C. The evolved circuit was not          |    |

|      | robust against the destructive noise                                         | 83 |

| 4.15 | The seven phases in the evaluation of a noise-tolerant AM block.             |    |

|      | Phases I-IV are the same as in the basic AM evaluation. The                  |    |

|      | three additional phases are: <i>Noise</i> , where the destructive noise is   |    |

|      | introduced at Input_A; Test A, where we test whether Input_A still           |    |

|      | strongly stimulates $Output_C$ ; and $Test\ B$ , where we test that the      |    |

|      | circuit retains Input_B's learnt "association" and strongly stimu-           |    |

|      | lates Output_C. The noise-tolerant AM response, at the probe point           |    |

|      | Output_C, to the inputs presented during the seven phases has 3,501          |    |

|      | data points for fitness evaluation of the candidate circuits. The data       |    |

|      | points are sampled every $0.1ms$ between $0ms$ and $350ms$                   | 85 |

| 4.16 | The embryo circuit for the noise-tolerant AM experiments. There              |    |

|      | are three additional voltage sources. The source<br>V_Noise_Input_A          |    |

|      | creates sinusoidal noise at connection point Input_A during the              |    |

|      | phase Noise. The sources $V\_Test\_A$ and $V\_Test\_B$ create excita-        |    |

|      | tory inputs at connection points Input_A and Input_B during the              |    |

|      | phases $Test\ A$ and $Test\ B$ respectively                                  | 86 |

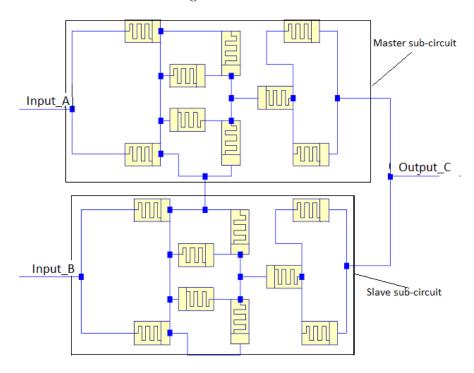

| 4.17 | The best-evolved equivalent circuit for the noise-tolerant spatial AM  |    |

|------|------------------------------------------------------------------------|----|

|      | design comprises of 18 two-terminal memristors. This design has        |    |

|      | evolved with components evenly divided between master and slave        |    |

|      | sub-circuits of nine memristors each. The master and slave sub-        |    |

|      | circuits are connected via some common nodes. The evolved sub-         |    |

|      | circuit shows a lot of feedback in its design                          | 88 |

| 4.18 | The transient response of the best-evolved noise-tolerant AM circuit.  |    |

|      | Here the transient response was within $10\%$ of the target during     |    |

|      | all seven of the evaluation phases. The average noise amplitude is     |    |

|      | observed in $Phase\ I$ is $10mV$ giving a signal-to-noise ratio of 20. |    |

|      | We also observe that the amplitude of voltage at the probe point       |    |

|      | Output_C changes its value incrementally with each pulse in the        |    |

|      | signal train, indicating that the memristor's non-linearity is being   |    |

|      | put to use                                                             | 89 |

| 4.19 | The fitness averaged over ten GP runs for evolving the noise-tolerant  |    |

|      | AM design. Here, the error-bars represent the standard deviation       |    |

|      | between the runs. The average fitness plots are noisy because the      |    |

|      | plots presented are averaged over ten runs, each pair with a different |    |

|      | replacement strategy and hence the evolution varies from one pair      |    |

|      | to the other                                                           | 90 |

| 4.20 | The best-evolved fitness averaged over ten GP runs for evolving        |    |

|      | the noise-tolerant AM design. Here, the error-bars represent the       |    |

|      | standard deviation between the runs. Both the fitness value and        |    |

|      | the error decrease as the evolution progresses and finally converge    |    |

|      | to a solution around, the $12,000^{th}$ generation                     | 91 |

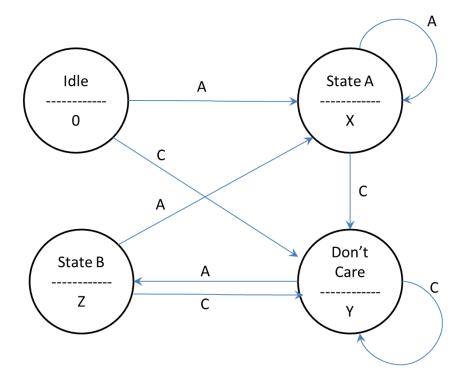

| 5.1 | The state transition diagram for the task of context-recognition.                                                  |    |

|-----|--------------------------------------------------------------------------------------------------------------------|----|

|     | The transitions occur when the system is presented with either the                                                 |    |

|     | input signal (letter $\mathtt{A}$ ) or the context signal (letter $\mathtt{C}$ ). Letters $\mathtt{X},\mathtt{Y},$ |    |

|     | and Z are output signals assigned to $\mathit{state}\ 1,\ \mathit{don't}\ \mathit{care},\ and\ \mathit{state}\ 2$  |    |

|     | respectively                                                                                                       | 95 |

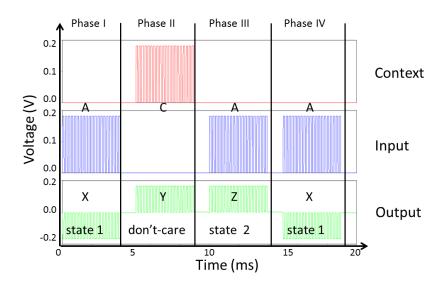

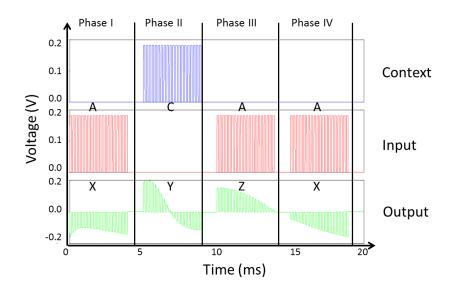

| 5.2 | The four phases in the evaluation of a context-sensitive AM block.                                                 |    |

|     | Phase $I$ , where the input pulses (coded as letter $\mathtt{A}$ ) stimulates the                                  |    |

|     | output in $state\ 1$ (coded as letter X). Phase II, where the context                                              |    |

|     | signal is presented (coded as letter ${\tt C}$ ). We do not evaluate the output                                    |    |

|     | during this phase. The output state during this phase is essentially                                               |    |

|     | $\emph{don't-care}$ (coded as letter Y). $\emph{Phase III}$ , the context is acknowledged                          |    |

|     | and the input pulses (letter A) stimulate the output in $state\ 2$ (coded                                          |    |

|     | as letter Y). Phase IV, we present input pulse (letter A) again, and                                               |    |

|     | this switches the output back to $state\ 1$ (letter X). This is the target                                         |    |

|     | context-sensitive AM response to inputs presented during the four                                                  |    |

|     | phases as a train of 20 pulsed signals, each of an amplitude $0.2V$ ,                                              |    |

|     |                                                                                                                    |    |

a pulse duration of 0.1ms and a time-period of 0.2ms. There are

2,001 data points for fitness evaluation of candidate circuits. The

data points are sampled every 0.01ms between 0ms and 20ms. . . .

96

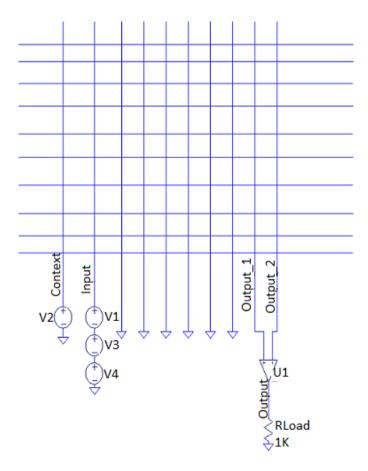

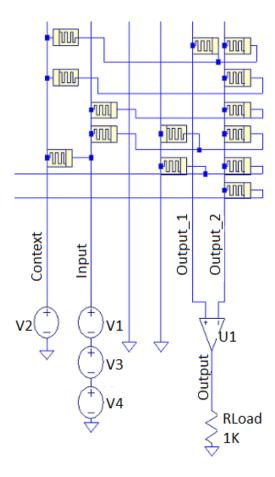

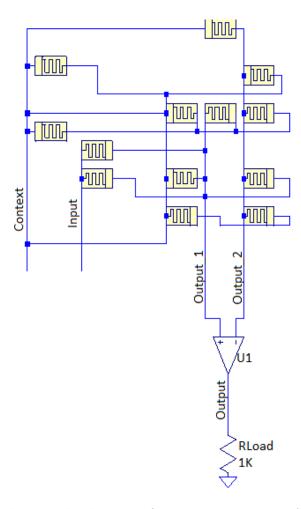

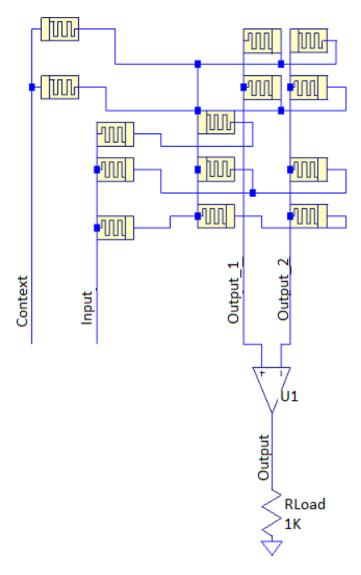

| 5.3 | The $10 \times 10$ cross-wire embryo structure for context-sensitive AM ex-                |     |

|-----|--------------------------------------------------------------------------------------------|-----|

|     | periments. There are four voltage sources, each creating excitatory                        |     |

|     | inputs at connection point Input or Context during a designated                            |     |

|     | phase. The final output at the probe point Output is the difference                        |     |

|     | of the voltages at Output_1 and Output_2, amplified with a gain                            |     |

|     | factor of 3. $R1$ is a $1k\Omega$ load resistor isolating the probe terminal               |     |

|     | Output from the ground                                                                     | 98  |

| 5.4 | The best-evolved equivalent circuit for the context-sensitive AM de-                       |     |

|     | sign. It comprised of 14 memristors. This design evolved with no                           |     |

|     | feedback-creating memristors                                                               | 101 |

| 5.5 | The transient response of the best-evolved context-sensitive AM net-                       |     |

|     | work. At the probe point $\mathtt{Output}$ , the $\mathit{state}\ 1$ (with negative ampli- |     |

|     | tude) during $Phase\ I$ and $Phase\ III$ is clearly distinguishable from                   |     |

|     | $state\ 2$ (with positive amplitude during $Phase\ III.$ We also observe                   |     |

|     | that the amplitude of the voltage during Phase II at the probe                             |     |

|     | point changes its value incrementally with each pulse in the signal                        |     |

|     | train, indicating that the memristor properties of non-linearity and                       |     |

|     | time-dependency are being used to store and switch states                                  | 102 |

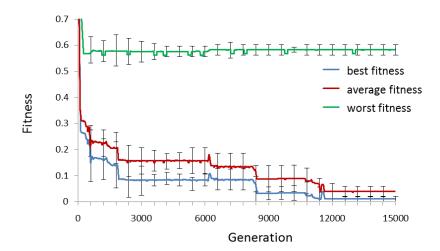

| 5.6 | The fitness averaged over five GP runs for evolving the context-                           |     |

|     | sensitive AM design. Here, the average fitness plots are noisy be-                         |     |

|     | cause the plots presented are averaged over five runs, each having a                       |     |

|     | different replacement strategy, and hence the evolution varies a lot                       |     |

|     | from one run to another                                                                    | 104 |

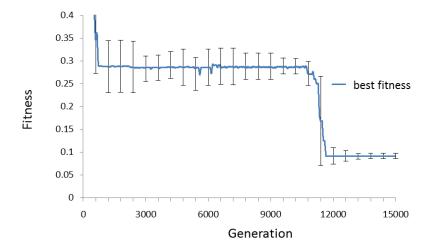

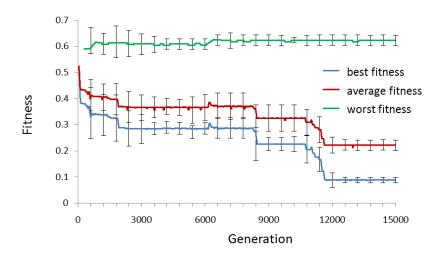

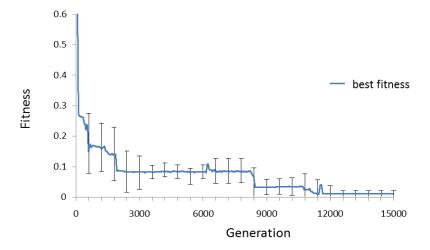

| 5.7  | The best-evolved fitness averaged over five GP runs for evolving            |

|------|-----------------------------------------------------------------------------|

|      | the context-sensitive AM design. Here, the error-bars represent the         |

|      | standard deviation between the runs. Both the fitness value and the         |

|      | error decrease as the evolution progresses and finally converges to a       |

|      | solution around generation 12,000                                           |

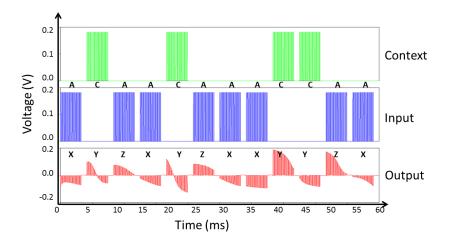

| 5.8  | The best-evolved circuit from Experiment 4 was subjected to a               |

|      | longer sequence of random inputs (A C A A C A A A C C A A). The             |

|      | network recognizes the context signal in the stream and switches to         |

|      | a correct state for the following input signal (X Y Z X Y Z X X Y           |

|      | Y Z X)                                                                      |

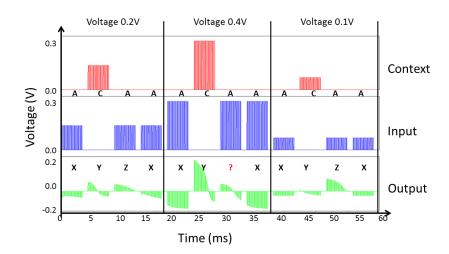

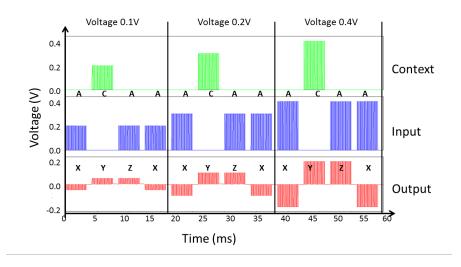

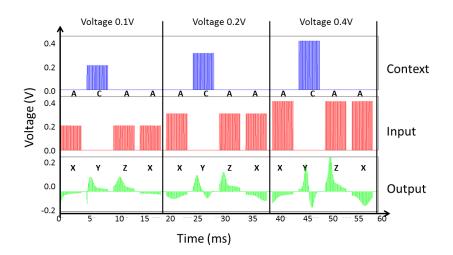

| 5.9  | The best-evolved circuit from Experiment 4 was subjected to the             |

|      | input pattern (A C A A) with varying amplitudes of: $0.1V,\ 0.2V,$          |

|      | and $0.4V$ . The network gave the correct output response for the           |

|      | 0.1V and $0.2V$ signals (output (X Y Z X), but the response for the         |

|      | 0.4V signal was ambiguous in <i>Phase III</i> (X Y ? X) 107                 |

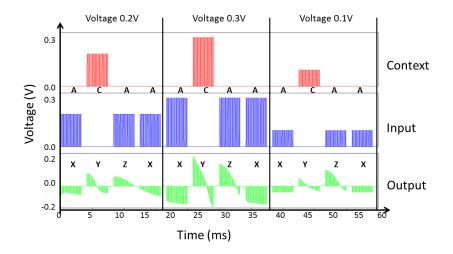

| 5.10 | The best-evolved circuit from Experiment 4 was subjected to the             |

|      | input pattern (A C A A) with varying amplitudes of: $0.1V,\ 0.2V,$          |

|      | and $0.3V$ . The network gave the correct output response (X Y Z            |

|      | X) for all three amplitudes. The evolved design was tested to be            |

|      | functional for the signals with amplitudes in the range of $0.1-0.3V.107$   |

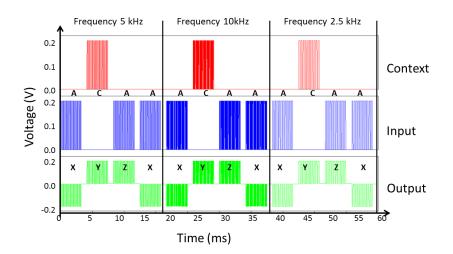

| 5.11 | The best-evolved circuit from Experiment 4 was subjected to the             |

|      | input pattern (A C A A) with varying frequencies of: $5kHz$ , $10kHz$ ,     |

|      | and $2.5kHz$ . The network gave the correct output response (X Y Z          |

|      | X) for all three amplitudes. The evolved design was tested to be            |

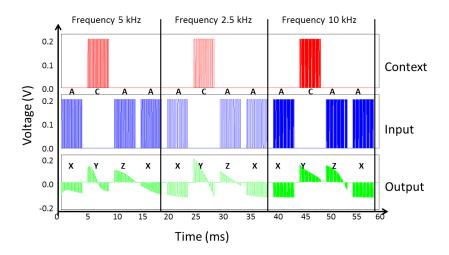

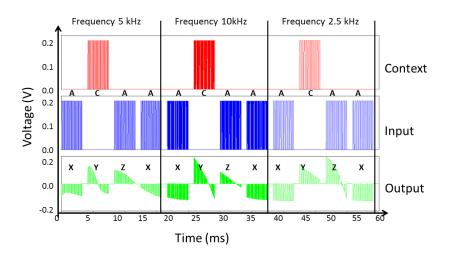

|      | functional for the signals with frequencies in the range of $2.5-10kHz.108$ |

| 5.12 | Ideal response for the three blocks of the input pattern (A C A A),        |

|------|----------------------------------------------------------------------------|

|      | with signal amplitudes of: $0.1V$ , $0.2V$ , and $0.4V$ . The network must |

|      | learn to give the correct output response $(X\ Y\ Z\ X)$ for all three     |

|      | amplitudes. The variation-tolerant AM response, at the probe point         |

|      | Output has 6,001 data points for fitness evaluation of candidate           |

|      | networks. The data points are sampled every $0.01ms$ between $0ms$         |

|      | and 60ms                                                                   |

| 5.13 | The best-evolved circuit for context-sensitive AM design that could        |

|      | tolerate $100\%$ variation in signal amplitude. It comprised of $13$       |

|      | memristors. The evolved circuit had some bridging between distant          |

|      | points that created feedback in the design                                 |

| 5.14 | The transient response of the best-evolved context-sensitive AM net-       |

|      | work tolerant of $100\%$ variation in the signal amplitude. The input      |

|      | pattern (A $$ C $$ A $$ A) was presented in three blocks with varying am-  |

|      | plitudes of: $0.1V$ , $0.2V$ , and $0.4V$ . The network gave the correct   |

|      | output response (X Y Z X) for all three amplitudes. The evolved            |

|      | design show distant connections that create feedback in the design. 112    |

| 5.15 | The fitness averaged over five GP runs for evolving the context-           |

|      | sensitive AM design, tolerant of a $100\%$ variation in the signal am-     |

|      | plitude                                                                    |

| 5.16 | The best-evolved fitness averaged over five GP runs for evolving           |

|      | the context-sensitive AM design, tolerant of a $100\%$ variation in        |

|      | the signal amplitude. Here, the error-bars represent the standard          |

|      | deviation between the runs                                                 |

| 5.17 | Ideal response for the three blocks of the input pattern (A C A A),             |

|------|---------------------------------------------------------------------------------|

|      | with signal amplitudes of: $5kHz$ , $10kHz$ , and $2.5kHz$ . The net-           |

|      | work must learn to give the correct output response (X Y Z X) for               |

|      | all three frequencies. The variation-tolerant AM response, at the               |

|      | probe point $\mathtt{Output}$ has $6,001$ data points for fitness evaluation of |

|      | candidate networks. The data points are sampled every $0.01ms$                  |

|      | between $0ms$ and $60ms$                                                        |

| 5.18 | The best-evolved circuit for context-sensitive AM design that could             |

|      | tolerate 100% variation in signal amplitude. It is comprised of $13$            |

|      | memristors. The evolved circuit had some bridging between distant               |

|      | points that created feedback in the design                                      |

| 5.19 | The transient response of the best-evolved context-sensitive AM net-            |

|      | work tolerant of 100% variation in the signal frequency. The input              |

|      | pattern (A $$ C $$ A $$ A) was presented in three blocks with varying fre-      |

|      | quencies of: $5kHz$ , $10kHz$ , and $2.5kHz$ . The network gave the             |

|      | correct output response (X Y Z X) for all three amplitudes 117                  |

| 5.20 | The fitness averaged over five GP runs for evolving the context-                |

|      | sensitive AM design, tolerant of a $100\%$ variation in the signal fre-         |

|      | quency                                                                          |

| 5.21 | The best-evolved fitness averaged over five GP runs for evolving                |

|      | the context-sensitive AM design, tolerant of a $100\%$ variation in             |

|      | the signal frequency. Here, the error-bars represent the standard               |

|      | deviation between the runs                                                      |

#### Introduction

The real-world computational problems today have to deal with massive quantities of low precision and ambiguous data. An example for such problems can be seen in artificial intelligence that deals with unifying computer vision, speech recognition, content and context recognition etc. [53]. Conventional computational models used in numerical simulations, model fitting, data analysis etc. are inherently designed to solve problems that are precise and well-defined. Additionally, they lack the ability to learn from the complex relationships that exist in space and time. Hence, conventional models are inefficient in solving this class of problems. There is an increasing interest in using neuro-cortical models as inspiration for intelligent computing. Intelligent computing here refers to inference-based models that act upon real world data and learn/adapt while computing results. The motivation behind developing intelligent computing models is the human brain. In support, the *BrainScaleS* program in Europe [31] and *DARPA SyNAPSE* program in the US [28] intend to realize novel computing paradigms that exploit the observations in biological nervous systems.

Associative Memories (AMs) are regarded as essential building blocks for the human brain [2]. Hence, drawing from biological inspiration, AMs in intelligent computing are candidate building blocks capable of memorization as well as learning and adaptation. An AM block based on a robust circuit design would allow the realization of hierarchical models.

We hypothesized memristor networks can be useful in robust nano-scale AM

designs. In this thesis, we propose a novel methodology for implementing AMs using memristors as circuits elements.

## 1.1 High-Level Associative Memories: Biological Implication

An Associative Memory (AM) has the ability to associate different memories to specific events. Such memories form an integral part of cognition in life forms, including humans [2]. This ability allows the brain to react or adapt to external stimuli based on past experiences. The famous Pavlov experiments [47] are a good example of associative memory: Pavlov observed that if a particular stimulus in the dog's surroundings was present when the dog was presented with meat powder, this stimulus would become associated with food and cause salivation on its own. The desired characteristics of associative memories have been summarized by Pao [45] as follows:

- It should store many associated pattern pairs through a self-organizing process in a distributed manner.

- It should generate the appropriate response output response despite distorted or incompletely received inputs.

- It should dynamically append new associations to the existing stored memory.

Research in high-level AM models inherits these important properties along with biological plausibility and fast training times. Central to these ideas is the learning matrix [60], the Hopfield network [27], the bidirectional associative memory (BAM) [33], and the hierarchical temporal memory (HTM) [20]. The learning matrix adapts the connection weights using a Hebbian learning rule [24]. In case of

the Hopfield network, feedback creates a system which uses input and output patterns to represent its states. The BAM is similar to the Hopfield network, but has two layers of neurons, and additionally uses connection matrix to calculate both a) outputs given some inputs and b) inputs given a set of outputs. The HTM concept involves having a hierarchy of spatial and temporal operators with multiple nodes in each layer of the hierarchy. All nodes perform identical computations except for the top layer node, which has additional features for performing classification.

AMs also form a specific area of research within self-organizing systems, commonly referred as *Kohonen networks or self-organized maps* [32]. Kohonen networks are rigorous mathematical models for two dimensional array of neurons, where the weight of each element corresponds to its coordinates in an ordered map. There are numerous application areas for high-level AMs within the intelligent computing paradigm, such as: pattern recognition, language learning, fact retrieval, inference and decision making, robotic controls etc. [2].

High-level AM models as above rely on low-level building blocks that can associate pairs of inputs or detect sequence/context within an encoded input stream. Low-level AMs have been traditionally implemented using *Artificial Neural Networks* (ANNs) [58]. The next section describes traditional designs and associated challenges.

# 1.2 Associative Memory Implementation with Artificial Neural Networks: Design and Challenges

We chronologically review here some traditional designs for electronic ANN implementations of AMs, with an emphasis on the challenges in their large-scale integration.

The first description of ANN integrated circuit [58] implements a continuous-time analog circuit for AM. The design used a 22 x 22 matrix with 20,000 transistors, averaging 40 transistors per node to implement a Hopfield AM network. The design faced a scalability challenge at higher levels of integration. The paper advocates handling larger problems by a collection of smaller networks or hierarchical solutions, while predicting, "significantly different connection technologies" as essential for success in larger systems.

The next seminal work by Sage and Withers [54] built AMs using discrete-time analog technology for high-speed computation in combination with analog nonvolatile storage for synaptic weights. The network demonstrated was a 9x9 Hopfield associative memory network. The issue with the design was that although the synaptic weights could dynamically adapt, there were only three possible states to the weights (1, 0, -1). Thus, the network could demonstrate learning for a very few specific computations only. The message from this study was that a continuous range weights would be a desirable feature for the synapses. In an attempt to achieve high resolution synaptic weights, Schwartz and Howard [57] proposed representing each weight as a difference in voltage between two capacitors. With the additional circuitry for sense-amplifiers, a 32 x 32 matrix with 75,000 transistors averaged 70 transistors per neural node. The high-level integration required scaling of the components to nano-scale levels and further simplification of the node design.

Other efforts from Holler *et al.* [26] use floating gate technology for the representation of synaptic weights to achieve higher synapse density, but the design has electrically programmable static weights, and the dynamics of input presentation

has no bearing on the real-time network associations. A mix of 8 x 8 matrix of digitally stored weights gate the inhibitory/excitatory pulse stream from 4 x 4 input layer. The pulse stream generation, integration and modulation results in much lower densities (140 transistors per neural node) than the aforementioned designs.

Among biological applications, Lyon et al. [40] implemented an electronic analog equivalent for the human cochlea (inner-ear). The design uses CMOS transconductance amplifiers circuits, follower-integrator circuits and second-order filter circuits to emulate perceptron machines. The authors see inherent deficiencies with digital threshold logic and emphasize the need for high-density analog learning-based implementations for more precise biological equivalence.

Hammerstrom et al. demonstrated one of the first custom digital ANN processor CNAPS [21]. The CNAPS architecture, customized for ANN simulations, had significant performance vs. cost improvements over arrays of commercial microprocessors. The authors proposed that further speed-ups could be achieved by exploiting the high-speed memory structure and the inherent parallelism of field-programmable-gate-arrays (FPGAs). Along the lines of exploiting the FPGA advantage, Changian et al. [8] have demonstrated a best-match association using distributed representations on FPGA hardware. Similarly, Deshpande [12] implemented a Bayesian-memory (BM) module on a FPGA. The term BM is used by the author to describe a building block in the hierarchical design of an equivalent HTM model [20]. Both these studies show that the performance of the FPGA based designs for associative memory models is dominated by the available chip area and the logic resources. Hammerstrom and Zaveri [22] analyzed the optimum use of such resources, and compared the performance vs. price trade-off for different architectures. They concluded that the mixed-signal CMOL design had the

best performance-to-price ratio. The authors also suggested that [22], "if in the future, nano devices/materials research provides robust solutions for implementing various analog functions using nanotechnology, this performance over price advantage is going to increase even further."

Other fully digital implementations of ANN AM integrated circuits can be seen in [14,29,41], which present various trade-offs between silicon area and computation time. 16 x 16 pattern storage and recognition networks are implemented using multi-chip modules. All authors were convinced that their proposed architectures would benefit in terms of more complex computations, if digital devices scaled down another 1,000 fold from then existing 3- $\mu$ m CMOS fabrication technology. Additionally, the proposed designs have only one stable state. More than one stable state exponentially increases the component count within each building block.

A fair insight into the algorithmic implementation of high-level AM algorithm including learning is achieved from the work of [1]. The design employed analog amplifiers to act as 'neurons', five-bit registers as synapses, and noise amplifiers for the simulated annealing. The research highlighted several challenges:

- lack of an effective algorithm for learning in modular, hierarchical networks;

- necessity of modularity to manage connectivity;

- simplification of node design in addition to synaptic density;

- constraints, such as power dissipation and capacitive loading across the chips;

- at least 100 x 100 neurons interconnected by 1000 x 1000 synapse for the simplest of meaningful computation.

As Pao et al. [45] set the rules for high-level AM models, the above experiments stressed the need for optimizing low-level AM designs that could be hierarchically

integrated in densities not achievable even with the current 22nm nand-flash technologies. Additionally, Bailey et al. [4] assert the need for multiplexed interconnects for large scale ANN based AM system integration.

The implementation of building-blocks for high-level AMs memories is a challenging problem in artificial vision, image recognition, and other intelligent and adaptive computing areas. This challenge has previously been addressed in many different ways, for example by modeling artificial neural networks using traditional components such as resistors, capacitors, operational amplifiers, including voltage and current sources, as summarized above. However, the traditional approaches lack scalability. The other problem is that an AM building block unlearns as well if destructive input patterns are introduced.

## 1.3 Exploiting Memristors: Towards Nano-scale Designs

This thesis explores denser designs with novel nano-scale components that bypass the scalability hurdle with their inherently small form factors and with new properties. The device of choice for our investigation is a memristor.