# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author:

Martineau, Matt J

On the Porting and Optimisation of Physics Simulations for Heterogeneous Parallel **Processors**

**General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

**Take down policy**Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

- · Your contact details

- Bibliographic details for the item, including a URL

- An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# On the Porting and Optimisation of Physics Simulations for Heterogeneous Parallel Processors

Matt Martineau University of Bristol, Merchant Venturers Building, Bristol, UK m.martineau@bristol.ac.uk

June 3, 2019

### Abstract

Modern science is increasingly reliant on computer simulations to model natural systems, and is limited by the available computational power. Modern supercomputers are regularly increasing in parallelism to meet the scientific throughput demands, while limited by power budgets and architectural restrictions such as heat emissions.

Those supercomputers now contain heterogeneous processors that range from CPUs that are latency optimised, and provide large complex cache hierarchies and DRAM, to GPUs that are latency hiding with many low power cores, and relatively simple caches and high bandwidth main memory. There is also a middle-ground offered by the Intel Xeon Phi, which is latency optimised and offers a modest number of low power cores with four hardware threads, a large but simplified cache hierarchy, and high bandwidth main memory. This thesis will consider the performance of all of these highly parallel processors, and the implications of the growing complexity of targeting modern processors.

Production physics simuations, of the kinds that simulate nuclear reactions, for instance, can often be monolithic, with millions of lines of code that can lack documentation and consistent coding style. Porting and optimising those applications to target modern supercomputers is a process of many choices, some with clearly defined options, and others requiring extensive investigation and research. Those choices are investigated in great depth in this thesis using a newly developed suite of exemplar applications that characterise important classes of physics applications: hydrodynamics, heat diffusion, and Monte Carlo neutral particle transport.

An informed choice of parallel programming model is essential to avoid inadvertently limiting future performance and portability. This thesis will consider some popular parallel programming models, and demonstrate their effectiveness and limitations in the context of the exemplar applications. The range of cutting edge algorithms for Monte Carlo neutral particle transport will be explored, and a novel approach to vectorising the application will be presented. With the search space of choices explored, a discussion is presented of those features of production applications often ignored in research codes, acknowledging the significant risks that are introduced with the complexity of real physics applications.

### Dedication

I want to thank my supervisor, Professor Simon McIntosh-Smith, for his continued support and guidance throughout the entire post-graduate process. I would also like to thank Wayne Gaudin for his expert supervision, and enthusiasm for the craft. I have learnt a lot from both of them. Thank you to both of my examiners, Professor Stephen Jarvis, and Professor David May, for taking the time to read and critique my thesis, and providing insightful feedback. I am also grateful to the supervisors who mentored me on my internships: Carlo Bertolli with IBM Research at the T.J. Watson Resarch Center, and David Beckingsale and Richard Hornung at Lawrence Livermore National Laboratories. Thank you to the team at Intel, John Pennycook, Douglas Jacobsen, Jason Sewall, and Andy Mallinson for their continued collaboration on the neutral project. Finally, thanks to my wife, Sarah, who supported me in every way possible, making every step infinitely more enjoyable than if tackled alone.

# Acknowledgements

Results presented in this research have been collected on the Swan XC50 supercomputer, where access was kindly granted by Cray Inc., as part of the Cray Marketing Partner Network. Results have also been collected on the Isambard test cluster, a GW4 collaboration, hosted by the Met Office. Extensive analysis was performed on the University of Bristol High Performance Group's Zoo testbed. Oxford University's Advanced Research Computing provided access to the IBM POWER8 system, Saffron. Simon Hammond at Sandia National Laboratories kindly arranged access to the Advanced Systems Technology Test Beds. Christopher Woods kindly setup and hosted the NVIDIA V100 GPU used in this thesis in the BlueGem compute cluster at the University of Bristol. Access to the Lawrence Livermore National Laboratories test clusters was provided by Richard Hornung. Alice Koniges arranged access to the Cori and Edison supercomputers at the National Energy Research Scientific Computing Center. This PhD was sponsored as part of a CASE converted DTP funded by EPSRC and the UK Atomic Weapons Establishment.

# **Author's Declaration**

I declare that the work in this dissertation was carried out in accordance with the requirements of the Universitys Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidates own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

| Signed: |  |  |  |

|---------|--|--|--|

| Date:   |  |  |  |

# Contents

| 1 | Intr | oducti | ion                                                          | 1  |

|---|------|--------|--------------------------------------------------------------|----|

|   | 1.1  | Contri | ibutions                                                     | 3  |

|   |      | 1.1.1  | The arch Project: Physics Proxy Applications                 | 3  |

|   |      | 1.1.2  | Analysis of Performance Portability for Physics Applications | 3  |

|   |      | 1.1.3  | Benchmarking of HPC Architecture Performance                 | 3  |

|   |      | 1.1.4  | Optimisation of Monte Carlo Neutral Particle Transport       | 4  |

|   |      | 1.1.5  | Analysis of Complex Production Concerns                      | 4  |

|   | 1.2  | Struct | ure of Thesis                                                | 4  |

|   | 1.3  | Reaso  | ning for arch                                                | 5  |

| 2 | Bac  | kgroui | $\mathbf{ad}$                                                | 7  |

|   | 2.1  | Parall | el Computing Architecture                                    | 7  |

|   |      | 2.1.1  | Instruction Pipelining                                       | 7  |

|   |      |        | 2.1.1.1 Superscalar Processing                               | 8  |

|   |      | 2.1.2  | Vector Processing                                            | 8  |

|   |      | 2.1.3  | Multi-core Computer Architecture                             | 9  |

|   |      |        | 2.1.3.1 Cache coherency                                      | 9  |

|   |      |        | 2.1.3.2 Multi-socketing                                      | 10 |

|   |      |        | 2.1.3.3 Non-Uniform Memory Access                            | 10 |

|   |      |        | 2.1.3.4 Simultaneous Multithreading                          | 11 |

|   |      | 2.1.4  | Distributed Computer Architecture                            | 11 |

|   |      | 2.1.5  | Many-core Computer Architecture                              | 12 |

|   |      |        | 2.1.5.1 Graphics Processing Units                            | 12 |

|   |      |        | 2.1.5.2 Intel Xeon Phi                                       | 13 |

|   | 2.2  | Parall | el Software                                                  | 13 |

|   |      | 2.2.1  | Fundamental Approaches to Parallel Programming               | 13 |

|   |      |        | 2.2.1.1 Threads                                              | 13 |

|   |      |        | 2.2.1.2 Tasks                                                | 14 |

|   |      |        | 2.2.1.3 Message Passing                                      | 14 |

|   | 2.3  | Parall | el Performance                                               | 15 |

|   |      | 2.3.1  | Amdahl's Law                                                 | 15 |

|   |      | 2.3.2  | Limiting Bounds                                              | 15 |

|   |      | 2.3.3  | Scaling                                                      | 16 |

|   |      |        | 2.3.3.1 Vector and Thread Scaling                            | 16 |

|   |      |        | 2.3.3.2 Inter-processor Scaling                              | 16 |

|   | 2.4  | Nume   | rical Simulations                                            | 17 |

CONTENTS vi

|   |                      | 2.4.1  | Partial Differential Equations                         |

|---|----------------------|--------|--------------------------------------------------------|

|   |                      |        | 2.4.1.1 Boundary Conditions                            |

|   |                      | 2.4.2  | Discretisation                                         |

|   |                      | 2.4.3  | Decomposition                                          |

|   |                      | 2.4.4  | Numerical Accuracy and Reproducibility                 |

|   |                      | 2.4.5  | Structured Mesh                                        |

|   |                      | 2.4.6  | Unstructured Meshes                                    |

|   |                      | 2.4.7  | Explicit Solvers                                       |

|   |                      | 2.4.8  | Implicit Solvers                                       |

|   |                      | 2.4.9  | Stencil Operations                                     |

|   | 2.5                  | Applio | eation Domains                                         |

|   |                      | 2.5.1  | Heat Diffusion                                         |

|   |                      | 2.5.2  | Eulerian Hydrodynamics                                 |

|   |                      | 2.5.3  | Lagrangian Hydrodynamics                               |

|   |                      | 2.5.4  | Probabilistic Methods                                  |

|   |                      |        |                                                        |

| 3 | $\operatorname{Pro}$ | gramn  | ning Models and Performance Portability 27             |

|   | 3.1                  | Introd | uction                                                 |

|   | 3.2                  | Non P  | Performance Portable Programming Models                |

|   |                      | 3.2.1  | OpenMP 3 and Intrinsics                                |

|   |                      | 3.2.2  | CUDA                                                   |

|   |                      |        | 3.2.2.1 Execution Model                                |

|   |                      |        | 3.2.2.2 Memory Model                                   |

|   |                      |        | 3.2.2.3 Compilation and PTX                            |

|   |                      | 3.2.3  | Exception to the Rule                                  |

|   | 3.3                  | Direct | ive-based Models                                       |

|   |                      | 3.3.1  | Background                                             |

|   |                      | 3.3.2  | Models and Syntax                                      |

|   |                      |        | 3.3.2.1 Execution Model                                |

|   |                      |        | 3.3.2.2 Parallel Hierarchy                             |

|   |                      |        | 3.3.2.3 Memory Models                                  |

|   | 3.4                  | Abstra | action Layers                                          |

|   |                      | 3.4.1  | RAJA                                                   |

|   |                      |        | 3.4.1.1 Execution Model                                |

|   |                      |        | 3.4.1.2 Memory Model                                   |

|   | 3.5                  | Messa  | ge Passing                                             |

|   | 3.6                  | Doma   | in Specific Languages                                  |

|   | 3.7                  | Perfor | mance, Portability and Productivity                    |

|   |                      | 3.7.1  | Performance                                            |

|   |                      | 3.7.2  | Functional Portability                                 |

|   |                      | 3.7.3  | Productivity                                           |

|   |                      | 3.7.4  | Performance Portability                                |

|   |                      |        | 3.7.4.1 Definition                                     |

|   |                      |        | 3.7.4.2 Inter-compiler Performance Portability         |

|   |                      |        | 3.7.4.3 Performance Portability for Programming Models |

|   |                      |        | 3.7.4.4 Algorithmic Performance Portability            |

CONTENTS vii

|   |     | 3.7.4.5 Achieving Performance Portability 4          |

|---|-----|------------------------------------------------------|

|   | 3.8 | Summary                                              |

| 4 | HP  | C Architectures 4                                    |

|   | 4.1 | Introduction                                         |

|   | 4.2 | Processor Configurations                             |

|   |     | 4.2.1 Intel CPUs                                     |

|   |     | 4.2.2 NVIDIA GPUs                                    |

|   | 4.3 | Intel CPU Background                                 |

|   | 4.4 | NVIDIA GPU Background                                |

|   |     | 4.4.0.1 Scheduling in Streaming Multiprocessors      |

|   |     | 4.4.0.2 Kernel Launch Overhead                       |

|   | 4.5 | Memory Bandwidth                                     |

|   | 4.6 | Memory Latency                                       |

|   | 1.0 | 4.6.1 Implementation                                 |

|   |     | 4.6.2 Results                                        |

|   | 4.7 | In Flight Memory Requests                            |

|   | 4.8 | Random Memory Access                                 |

|   | 4.0 | 4.8.1 Random Memory Access Benchmark                 |

|   |     | 4.8.1.1 Implementation                               |

|   |     | •                                                    |

|   |     |                                                      |

|   |     | 4.8.3 Results                                        |

|   |     | 4.8.3.1 Unvectorised Results                         |

|   | 4.0 | 4.8.3.2 Vectorised and GPU Results                   |

|   | 4.9 | Summary                                              |

| 5 | Mo  | nte Carlo Neutral Particle Transport 6               |

|   | 5.1 | Introduction                                         |

|   | 5.2 | Problems in Monte Carlo Neutral Particle Transport 6 |

|   | 5.3 | Monte Carlo Particle Transport Applications          |

|   |     | 5.3.1 MCNP 6                                         |

|   |     | 5.3.2 OpenMC                                         |

|   |     | 5.3.3 Quicksilver                                    |

|   |     | 5.3.4 Branson                                        |

|   | 5.4 | neutral: Monte Carlo Neutral Particle Transport 6    |

|   |     | 5.4.1 Particle Tracking                              |

|   |     | 5.4.2 Tallying                                       |

|   |     | 5.4.2.1 Random Number Generation 6                   |

|   |     | 5.4.3 Nuclear Cross-Sections                         |

|   |     | 5.4.4 Core Algorithm                                 |

|   |     | 5.4.4.1 Over Histories                               |

|   |     | 5.4.4.2 Over Events                                  |

|   |     | 5.4.4.3 Sort-free Over Events                        |

|   |     | 5.4.5 Parameters                                     |

|   |     | 5.4.5.1 Particle Population                          |

|   |     | 5.4.5.1 Farticle Population                          |

|   |     | 0.4.0.2 I ar note bourding                           |

CONTENTS viii

|   |      |         | 5.4.5.3 Timestep                                          |

|---|------|---------|-----------------------------------------------------------|

|   |      |         | 5.4.5.4 Mesh Dimensions                                   |

|   |      | 5.4.6   | Problems                                                  |

|   |      |         | 5.4.6.1 The streaming problem                             |

|   |      |         | 5.4.6.2 The scattering problem                            |

|   |      |         | 5.4.6.3 The csp problem                                   |

|   | 5.5  | Impler  | mentation on CPU                                          |

|   |      | 5.5.1   | Over Histories                                            |

|   |      | 5.5.2   | Performance Analysis of Over Histories                    |

|   |      |         | 5.5.2.1 Profiling the scattering Problem                  |

|   |      |         | 5.5.2.2 Memory Bandwidth of the scattering Problem        |

|   |      |         | 5.5.2.3 Computational Throughput of scattering Problem 79 |

|   |      | 5.5.3   | Profiling the streaming Problem                           |

|   |      |         | 5.5.3.1 Memory Bandwidth of the streaming Problem         |

|   |      | 5.5.4   | Profiling the csp Problem                                 |

|   |      | 5.5.5   | Incidental Locality                                       |

|   |      | 5.5.6   | Thread Scheduling                                         |

|   |      | 5.5.7   | Hyperthreading                                            |

|   |      | 5.5.8   | Over Events                                               |

|   |      | 5.5.9   | Sort-free Over Events                                     |

|   | 5.6  | Impler  | mentation on GPU                                          |

|   |      | 5.6.1   | Over Histories                                            |

|   |      |         | 5.6.1.1 Sort-free Over Events                             |

|   | 5.7  | Enabli  | ng Vectorisation via Blocked Over Events                  |

|   |      | 5.7.1   | Vectorising the Collision Event Routine                   |

|   |      |         | 5.7.1.1 Restructuring of the Binary Search                |

|   |      |         | 5.7.1.2 Intrinsic Atomic Call                             |

|   |      | 5.7.2   | Tunable Block Size                                        |

|   |      | 5.7.3   | Particle Data Structures                                  |

|   |      |         | 5.7.3.1 Performance                                       |

|   | 5.8  | Increas | sing the Lookup Table Size                                |

|   | 5.9  | Perfor  | mance Portability                                         |

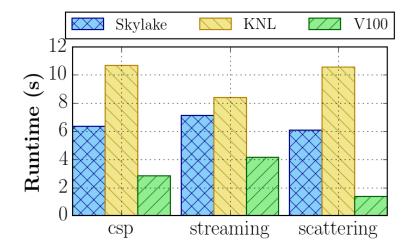

|   |      | 5.9.1   | Best Cases Across Architectures                           |

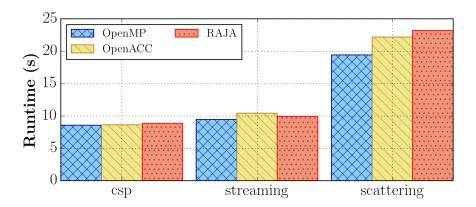

|   |      | 5.9.2   | Programming Model Performance                             |

|   | 5.10 | Summ    | ary                                                       |

| 6 | Цор  | 4 D:#.  | usion via a Conjugate Gradient Solver 97                  |

| U | 6.1  |         | uction                                                    |

|   | 0.1  | 6.1.1   | Associated Research                                       |

|   |      | 0.1.1   | 6.1.1.1 Libraries                                         |

|   | 6.2  | Impler  | nentation                                                 |

|   | 0.4  | 6.2.1   | The Conjugate Gradient Method                             |

|   |      | 6.2.2   | The Conjugate Gradient Algorithm                          |

|   |      | 6.2.3   | The hot Application                                       |

|   | 6.3  |         | mance Analysis                                            |

|   | 0.0  |         | Default Test Case                                         |

|   |      | 6.3.1   | Default Test Case                                         |

CONTENTS ix

|   |     | 6.3.2  | Kernels                                                |

|---|-----|--------|--------------------------------------------------------|

|   |     | 6.3.3  | Performance on CPU and KNL                             |

|   |     | 6.3.4  | Vectorisation                                          |

|   | 6.4 | Perfor | mance on GPU                                           |

|   | 6.5 | Balan  | ce                                                     |

|   | 6.6 | Distri | buted Performance                                      |

|   | 6.7 | Perfor | mance Portability                                      |

|   |     | 6.7.1  | Preliminary Performance for Default Test Case          |

|   |     |        | 6.7.1.1 CPU Performance                                |

|   |     |        | 6.7.1.2 KNL Performance                                |

|   |     |        | 6.7.1.3 GPU Performance                                |

|   |     | 6.7.2  | Performance for Small Problems                         |

|   | 6.8 | Summ   | ary                                                    |

| 7 | Hvd | drodyn | namics 112                                             |

|   | 7.1 |        | luction                                                |

|   | 7.2 |        | sured Eulerian Hydrodynamics                           |

|   |     | 7.2.1  | Performance Analysis                                   |

|   |     |        | 7.2.1.1 Default Test Case                              |

|   |     |        | 7.2.1.2 Kernels                                        |

|   |     |        | 7.2.1.3 Vectorisation                                  |

|   |     |        | 7.2.1.4 GPU Performance                                |

|   |     | 7.2.2  | Performance Portability                                |

|   |     | 7.2.3  | Productivity                                           |

|   |     | 1.2.0  | 7.2.3.1 OpenMP                                         |

|   |     |        | 7.2.3.2 OpenACC                                        |

|   |     |        | 7.2.3.3 RAJA                                           |

|   | 7.3 | Unstr  | uctured Lagrangian Hydrodynamics                       |

|   | 1.0 | 7.3.1  | Performance Analysis                                   |

|   |     | 1.0.1  | 7.3.1.1 Default Test Case                              |

|   |     |        | 7.3.1.2 CPU Performance                                |

|   |     |        | 7.3.1.3 Preliminary GPU Performance                    |

|   |     |        | 7.3.1.4 Implications of Supporting Unstructured Meshes |

|   |     |        | 7.3.1.5 Implications of Supporting Subcell Forces      |

|   |     |        | 7.3.1.6 GPU Data Structure Transposition               |

|   | 7.4 | Summ   | ary                                                    |

| 0 | Duc | dat:a  | n Challenges 126                                       |

| 8 | 8.1 |        | tructural Code                                         |

|   | 0.1 | 8.1.1  |                                                        |

|   |     | 0.1.1  | The arch project                                       |

|   |     |        | 8.1.1.1 Communication                                  |

|   |     |        | 8.1.1.2 Meshes and Mesh Data                           |

|   |     | 010    | 8.1.1.3 Performance and Portability                    |

|   | 0.0 | 8.1.2  | Note on Programming Language Choice                    |

|   | 8.2 |        | res Sometimes Ignored in Proxy Applications            |

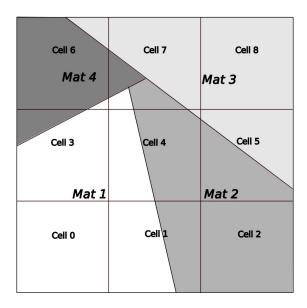

|   |     | 8.2.1  | Multiple Materials                                     |

CONTENTS

|   |      |         | 8.2.1.1 Eulerian Flow Field                 | 132 |

|---|------|---------|---------------------------------------------|-----|

|   |      | 8.2.2   | Large Lookup Tables                         | 133 |

|   |      | 8.2.3   | Load Imbalance                              | 133 |

|   |      | 8.2.4   | Internal Error Handling and Diagnostics     | 134 |

|   |      | 8.2.5   | Dynamic Connectivity in Unstructured Meshes | 134 |

|   |      | 8.2.6   | Mesh Quality Control                        | 134 |

|   | 8.3  | Proble  | ms for Proxy Applications                   | 135 |

|   |      |         | 8.3.0.1 Applications in the arch Suite      | 135 |

|   |      |         | 8.3.0.2 Validation of Proxy Applications    | 136 |

|   | 8.4  | Summ    | ary                                         | 136 |

| 9 | Con  | clusion | ns and Future Work                          | 137 |

| A | Inst | ructio  | n Latency                                   | 141 |

| В | Cac  | he Bar  | $\operatorname{ndwidth}$                    | 142 |

|   |      | B.0.1   | Skylake and KNL Cache Bandwidth             | 142 |

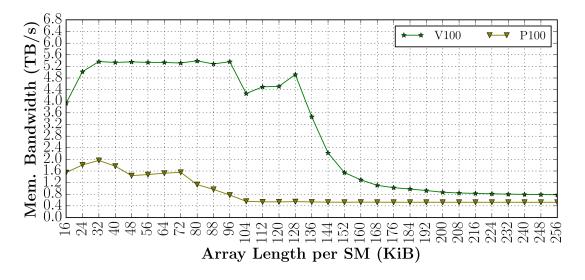

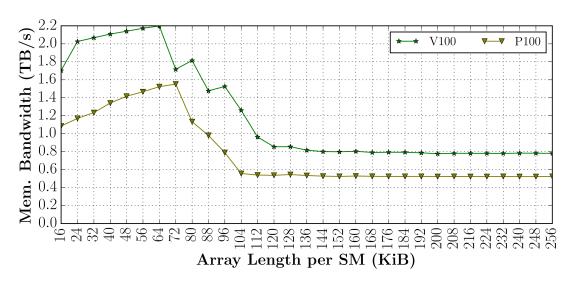

|   |      | B.0.2   | NVIDIA GPU Cache Bandwidth                  | 143 |

# List of Figures

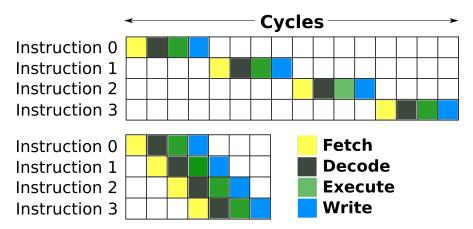

| 2.1  | Instructions issued with (bottom), and without (top) instruction pipelining. The   |    |

|------|------------------------------------------------------------------------------------|----|

|      | colours represent stages required to issue full instruction, e.g. fetch, decode,   |    |

|      | execute, write.                                                                    | 7  |

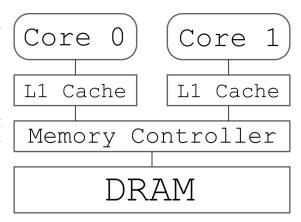

| 2.2  | A cache layout for a hypothetical CPU architecture                                 | 10 |

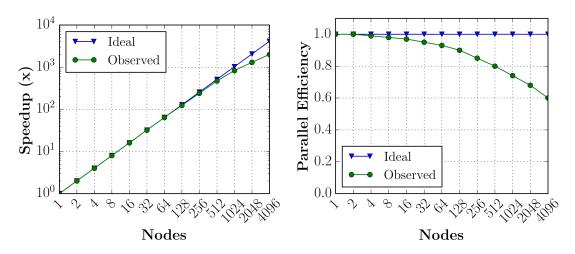

| 2.3  | Hypothetical scaling graphs for strong scaling (left) and weak scaling (right)     | 17 |

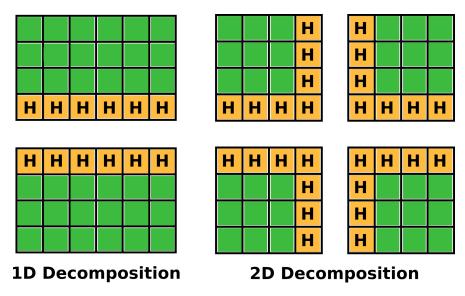

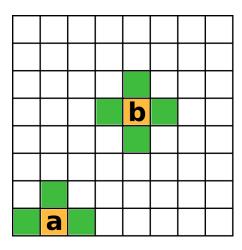

| 2.4  | Two approaches to decomposing a two dimensional space: 1D decomposition            |    |

|      | (left), and 2D decomposition (right) where the orange cells containing 'H' are     |    |

|      | halo cells                                                                         | 19 |

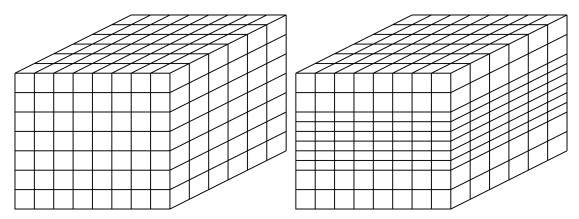

| 2.5  | Three-dimensional structured meshes: a Cartesian mesh with congruent cells         |    |

|      | (left); a rectilinear mesh with non-congruent cells (right)                        | 20 |

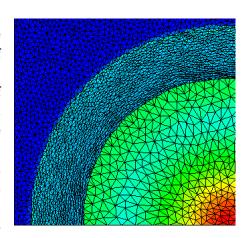

| 2.6  | An example of a unstructured mesh in lags (Chapter 7)                              | 21 |

| 2.7  | A Cartesian mesh with two five point stencil computations depicted                 | 23 |

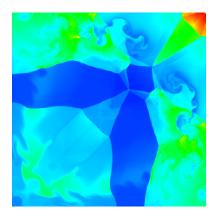

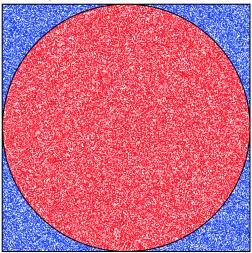

| 2.8  | Example output of the flow hydro proxy application                                 | 24 |

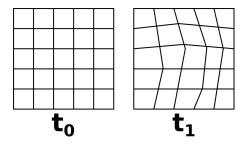

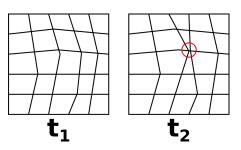

| 2.9  | An example of a Lagrangian mesh deforming after a single timestep                  | 25 |

| 2.10 | Monte Carlo calculation of $\pi$                                                   | 26 |

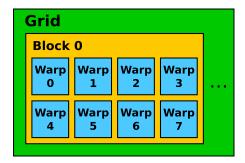

| 3.1  | The parallel hierarchy exposed by the CUDA programming model                       | 31 |

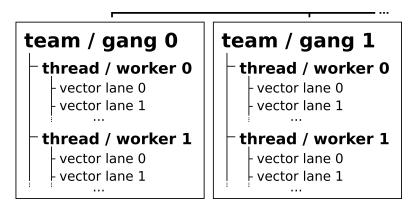

| 3.2  | The models of parallel hierarchies provided by OpenMP and OpenACC                  | 35 |

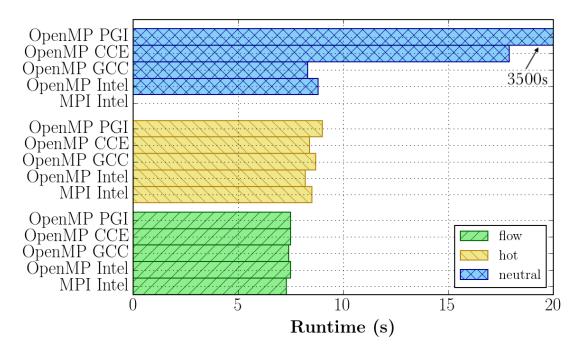

| 3.3  | Inter-compiler performance portability of arch applications on a Skylake CPU       | 43 |

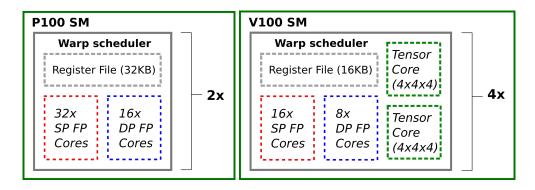

| 4.1  | The layout of streaming multiprocessors in the P100 and V100 GPUs                  | 50 |

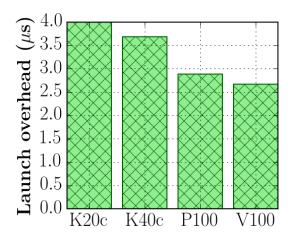

| 4.2  | Overhead of individual kernel launch per generation                                | 50 |

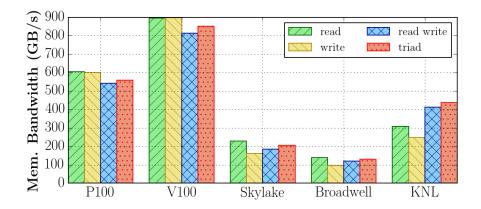

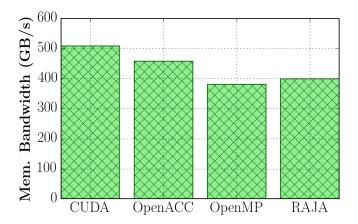

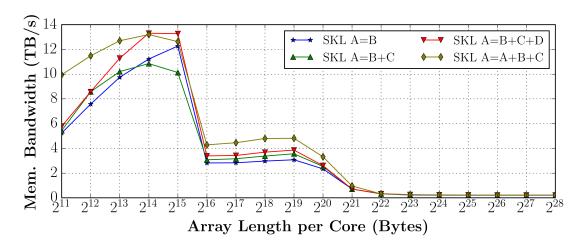

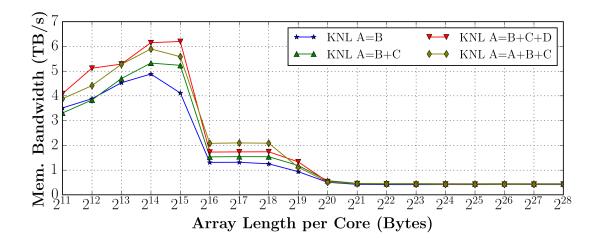

| 4.3  | Memory bandwidth of four streaming kernels on parallel processors (see Section     |    |

|      | 4.2)                                                                               | 51 |

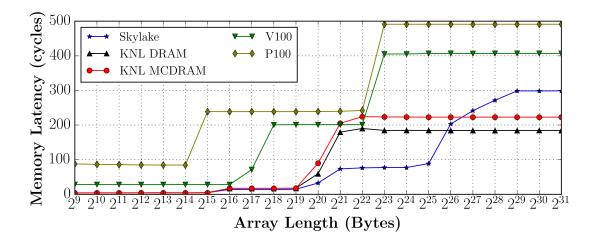

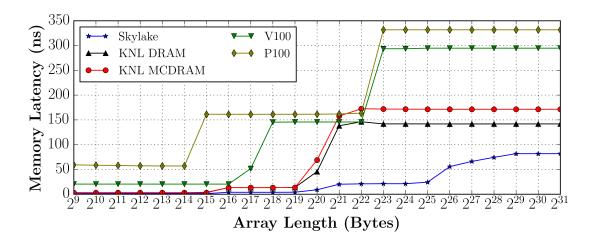

| 4.4  | Memory latency in cycles for all considered HPC processors                         | 53 |

| 4.5  | Memory latency in nanoseconds for all considered HPC processors                    | 54 |

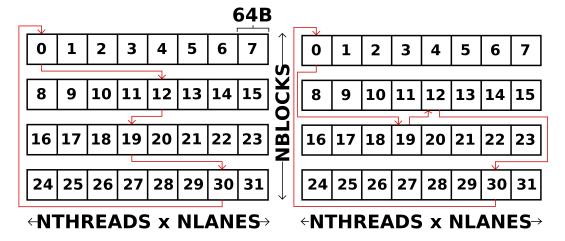

| 4.6  | Block layout for the initialisation (left) and block shuffling (right) of memory   |    |

|      | in the random memory access benchmark. Each numbered square represents a           |    |

|      | unique cache line                                                                  | 56 |

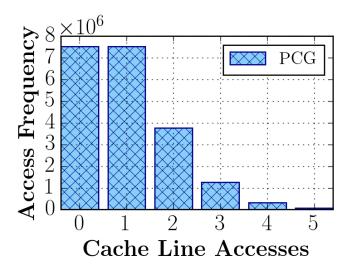

| 4.7  | Frequency of cache lines accesses                                                  | 56 |

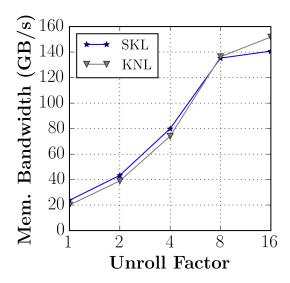

| 4.8  | Unvectorised results for the <i>pchase</i> benchmark, by unroll factor             | 58 |

| 5.1  | The particle tracking concept of Monte Carlo neutral particle transport, depicting |    |

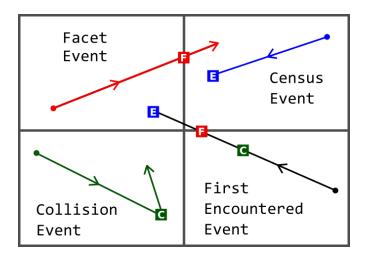

|      | the three events, and the determination of the first encountered event             | 65 |

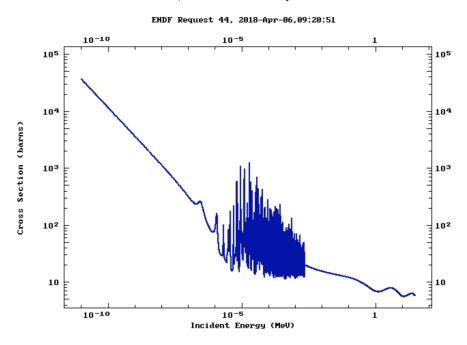

| 5.2  | The nuclear cross section of U-235 in log-log scale                                | 67 |

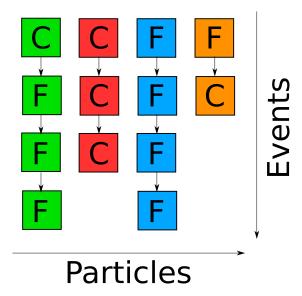

| 5.3  | Matrix depicting the organisation of events and particles throughout time          | 68 |

LIST OF FIGURES xii

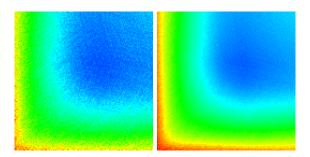

| 5.4  | Tuning the number of particles towards convergence, 1e6 particles (left) and 1e7                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | particles (right)                                                                                                                                                             |

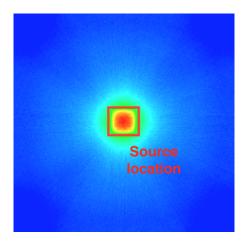

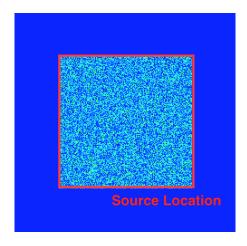

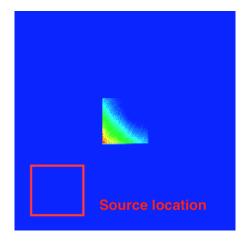

| 5.5  | Example plot of energy deposition for the streaming problem                                                                                                                   |

| 5.6  | Example plot of energy deposition for the scattering problem                                                                                                                  |

| 5.7  | Example plot of energy deposition for the csp problem                                                                                                                         |

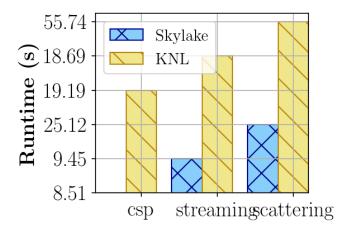

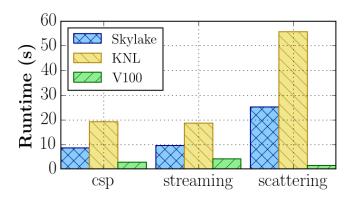

| 5.8  | Performance of the over histories approach for the Skylake and KNL                                                                                                            |

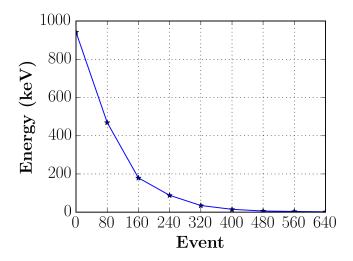

| 5.9  | The energy profile of a particle throughout the scattering problem                                                                                                            |

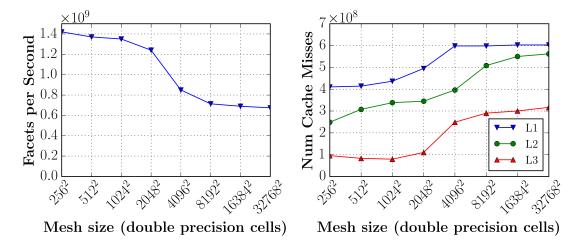

| 5.10 | Scaling the streaming problem and plotting cache misses                                                                                                                       |

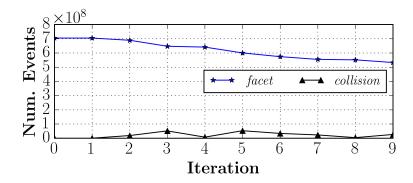

| 5.11 | The balance of events in the csp problem                                                                                                                                      |

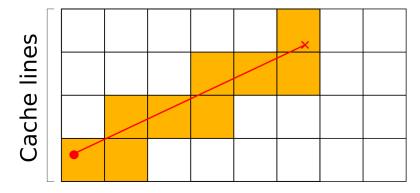

| 5.12 | The incidental locality of a random particle trajectory in neutral 81                                                                                                         |

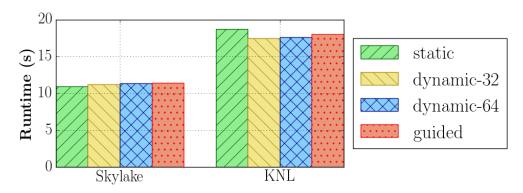

| 5.13 | Adjusting the OpenMP thread scheduling for the csp problem 82                                                                                                                 |

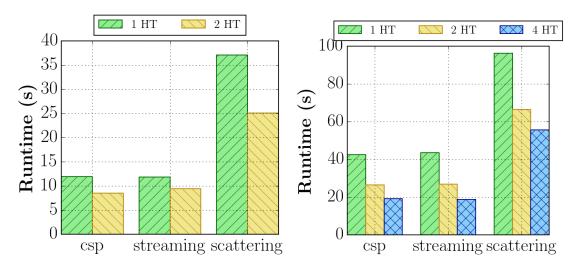

| 5.14 | Adjusting the number of hardware threads for the problems in neutral. The                                                                                                     |

|      | results are for Skylake (left) and KNL (right)                                                                                                                                |

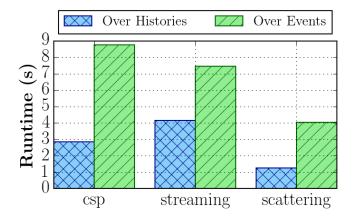

| 5.15 | The performance of the over events approach with respect to the over histories                                                                                                |

|      | approach                                                                                                                                                                      |

| 5.16 | Performance of the V100 compared to the Skylake for the over histories approach. 85                                                                                           |

| 5.17 | Performance of the <i>predicated over events</i> approach on a V100 GPU 87                                                                                                    |

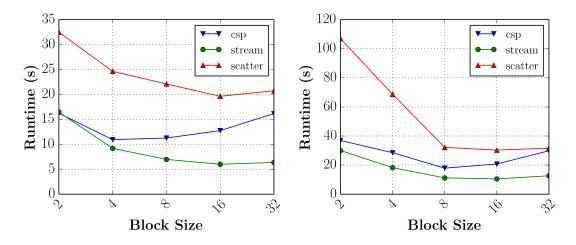

| 5.18 | Tuning the block size for the blocked over events algorithm, for the Skylake (left)                                                                                           |

|      | and KNL (right) CPUs                                                                                                                                                          |

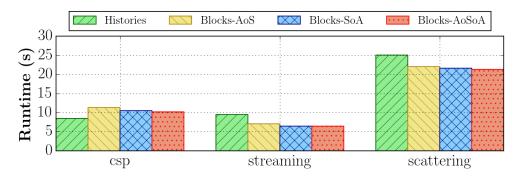

| 5.19 | Altering the data structure for the blocked over events approach on the Skylake                                                                                               |

|      | CPU                                                                                                                                                                           |

| 5.20 | Altering the data structure for the blocked over events approach on the KNL 91                                                                                                |

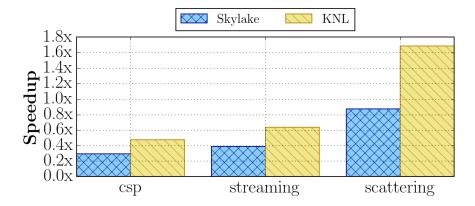

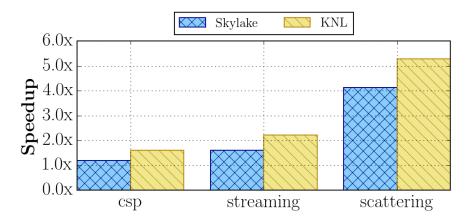

| 5.21 | The speedup of the <i>over blocks</i> approach compared to the <i>over histories</i> approach                                                                                 |

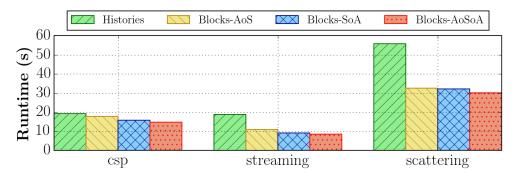

|      | for the Skylake and KNL                                                                                                                                                       |

| 5.22 | The performance of the best performing versions of neutral on the 3 parallel                                                                                                  |

|      | processors                                                                                                                                                                    |

| 5.23 | The performance on neutral executed on a Skylake CPU with varying program-                                                                                                    |

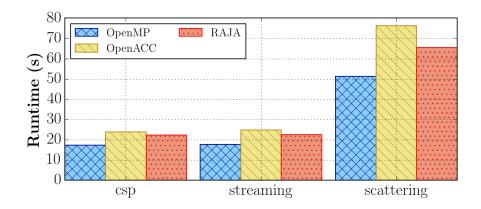

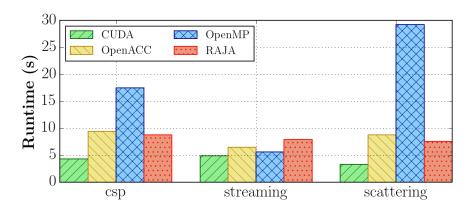

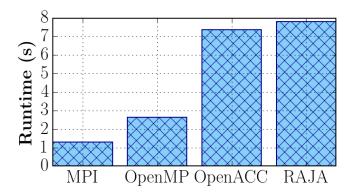

|      | ming models                                                                                                                                                                   |

| 5.24 | The performance on neutral executed on a KNL with varying programming                                                                                                         |

|      | models                                                                                                                                                                        |

| 5.25 | The performance on neutral executed on an NVIDIA P100 GPU with varying                                                                                                        |

|      | programming models                                                                                                                                                            |

|      |                                                                                                                                                                               |

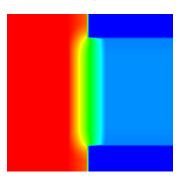

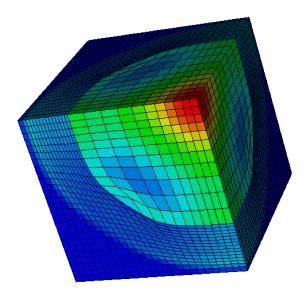

| 6.1  | Solution of a heat diffusion problem solved by the hot application                                                                                                            |

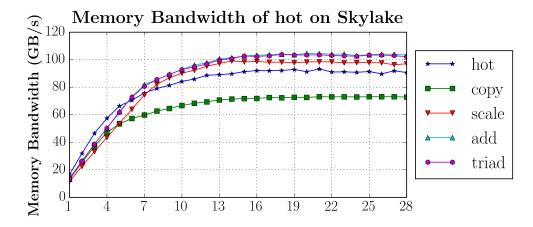

| 6.2  | The memory bandwidth achieved by hot relative to STREAM kernels on a single                                                                                                   |

|      | socket of Skylake CPU                                                                                                                                                         |

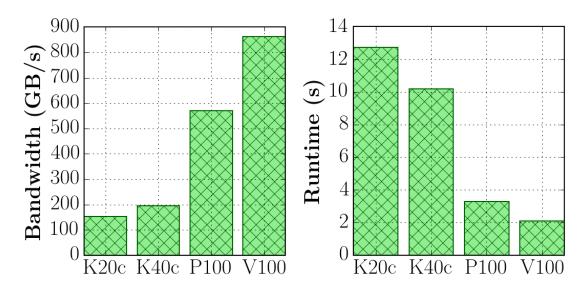

| 6.3  | Performance of hot executing on NVIDIA GPUs, bandwidth (left) and runtime                                                                                                     |

|      | (right)                                                                                                                                                                       |

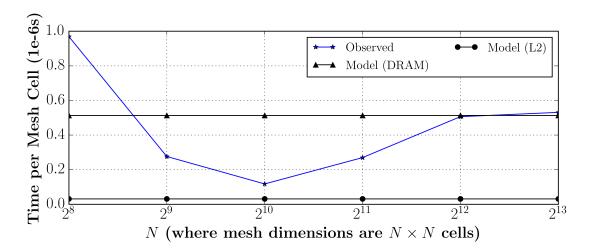

| 6.4  | Varying mesh dimensions for $hot$ with modeled and observed runtime results $105$                                                                                             |

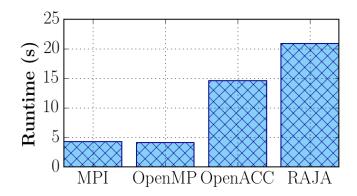

| 6.5  | The performance of hot on a Skylake CPU                                                                                                                                       |

| 6.6  | The performance of hot on a KNL                                                                                                                                               |

| 6.7  | The performance of hot on a P100 GPU                                                                                                                                          |

| 6.8  | The performance of hot for a small test problem on a Skylake CPU 109 $$                                                                                                       |

| 6.9  | The performance of hot for a small test problem on a KNL. $\dots \dots \dots$ |

| 6.10 | The performance of hot for a small test problem on a P100 GPU 110                                                                                                             |

LIST OF FIGURES xiii

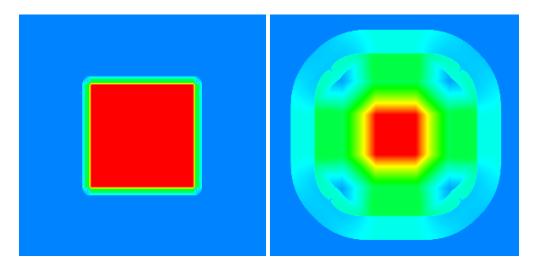

| 7.1 | Default test problem (left), and the same problem after 1000 timesteps (right). $$ . $$ 114 |

|-----|---------------------------------------------------------------------------------------------|

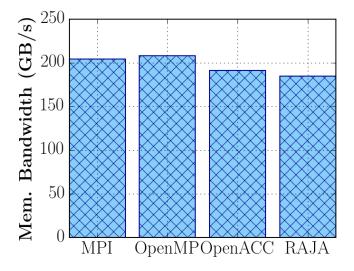

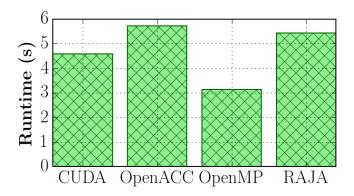

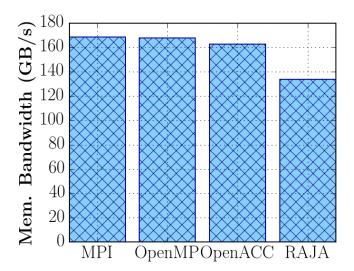

| 7.2 | The memory bandwidth achieved by ports of flow executing on a Skylake CPU. 116              |

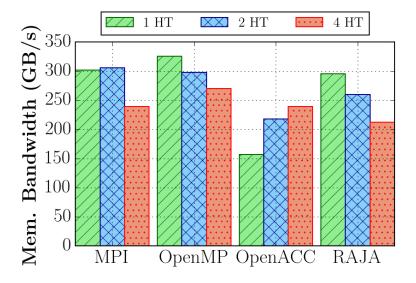

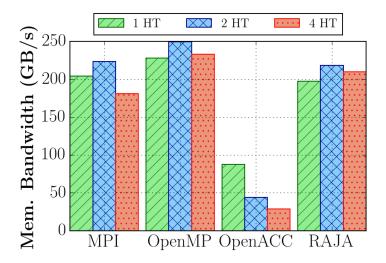

| 7.3 | The memory bandwidth achieved by ports of flow executing on a KNL 117                       |

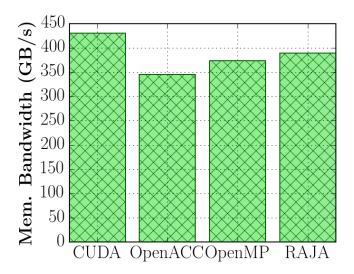

| 7.4 | The memory bandwidth achieved by ports of ${\tt flow}$ executing on a P100 GPU 117          |

| 7.5 | Problem solved by lags, note that the grid is structured but the algorithms                 |

|     | assume an unstructured mesh                                                                 |

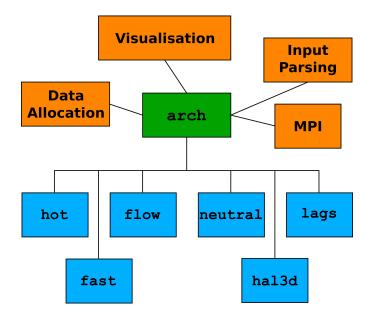

| 8.1 | The arch infrastructure                                                                     |

| 8.2 | Multi-material layout for a structured mesh, showing material interfaces [49] 131           |

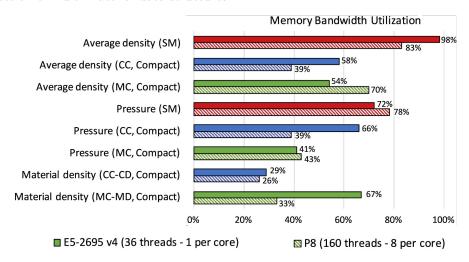

| 8.3 | Performance of multi-material data structures ported to two CPUs, where P8                  |

|     | refers to the IBM POWER8 [49]                                                               |

| 8.4 | Performance of multi-material data structures ported to the KNL and P100                    |

|     | GPU [49]                                                                                    |

| 8.5 | A mesh where compression will lead to a reduced timestep                                    |

| D 1 |                                                                                             |

| B.1 | Cache bandwidth measured for the Intel Xeon Skylake                                         |

| B.2 | Cache bandwidth measured for the Intel Xeon Phi Knights Landing 143                         |

| B.3 | Bandwidth targeting L1 cache for P100 and V100 GPUs                                         |

| B.4 | Bandwidth targeting L2 cache for P100 and V100 GPUs                                         |

# List of Tables

| 2.1        | Number of simultaneous threads per core                                                                                                                      | 1  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2        | Figures for the newest Department of Energy (DoE) supercomputers, for Lawrence Livermore National Laboratories (LLNL), Oak Ridge National Laboratory (ORNL), |    |

|            | and Los Alomos National Laboratories (LANL)                                                                                                                  | 2  |

| 4.1        | Details of the key Intel processors used in this thesis                                                                                                      | 7  |

| 4.2        | Details of the key NVIDIA GPUs used in this thesis, including streaming multi-                                                                               |    |

| 4.3        | processor (SM) count                                                                                                                                         | 7  |

|            | of cores on a KNL                                                                                                                                            | 8  |

| 4.4<br>4.5 | Details of the key NVIDIA GPUs used in this thesis                                                                                                           | 9  |

|            | socket)                                                                                                                                                      | 8  |

| 5.1        | Bandwidth results collected with nvprof on a V100 GPU                                                                                                        | 6  |

| 5.2        | The memory bandwidth achieved by the different processors when executing the scattering problem for 300 nuclides                                             | 2  |

| 6.1        | Performance by kernel for hot on a Skylake CPU                                                                                                               | 1  |

| 6.2<br>6.3 | Statically analysed arithmetic intensities for routines in hot                                                                                               |    |

|            | KNL                                                                                                                                                          | 4  |

| 6.4        | Performance of key routines in hot for small test problem on Skylake CPU 109                                                                                 | 9  |

| 6.5        | Performance of key routines in hot measured by nvprof on P100 GPU 110                                                                                        | 0  |

| 7.1        | Performance by kernel for flow on Skylake CPU                                                                                                                | 5  |

| 7.2        | Performance by kernel for flow on V100 GPU                                                                                                                   | 5  |

| 7.3        | Performance by kernel for the Lagrangian solve in lags on a Skylake CPU 12                                                                                   |    |

| 7.4        | Memory bandwidth by kernel for the Lagrangian solve in lags on a Skylake CPU.12                                                                              | 2  |

| 7.5        | Memory bandwidth by kernel for the Lagrangian solve in lags on a NVIDIA                                                                                      | _  |

|            | V100 GPU                                                                                                                                                     | 2  |

| 7.6        | Memory bandwidth by kernel for the Lagrangian solve in lags on a NVIDIA V100 GPU, with transposed data structures                                            | 4  |

| A.1        | Latencies observed when executing different instructions on NVIDIA GPUs; the                                                                                 |    |

|            | ${\rm `FM'\ label\ indicates\ that\ the\ latency\ benchmark\ was\ compiled\ with\ the\ 'use\_fast\_math}$                                                    | ι, |

|            | flag passed to nvcc                                                                                                                                          | 1  |

# Listings

| 2.1 | Example of vectorisable loop in C                       |

|-----|---------------------------------------------------------|

| 2.2 | Scalar loop in the x86 instruction set                  |

| 2.3 | Vector instruction in AVX2 instruction set              |

| 2.4 | Example of a simple parallel loop                       |

| 3.1 | Simple CUDA example                                     |

| 3.2 | Parallel offload directives OpenMP / OpenACC            |

| 3.3 | Parallel offload directives in OpenMP                   |

| 3.4 | Parallel offload directives in OpenACC                  |

| 3.5 | Unstructured data movement directives                   |

| 3.6 | RAJA simple loop example                                |

| 5.1 | The over histories algorithm for neutral                |

| 5.2 | The over events algorithm based on Brown et al          |

| 5.3 | The over events algorithm for neutral using predication |

| 5.4 | The blocked over events algorithm for neutral           |

| 5.5 | Access to particle data within the SIMD region for AoS  |

| 6.1 | The local CG algorithm                                  |

| 7.1 | Example kernel ported with OpenMP                       |

| 7.2 | Example kernel ported with OpenACC                      |

| 7.3 | Example kernel ported with RAJA                         |

| 7.4 | Kernel with RAJA outer loop and inner for loop          |

| 7.5 | Energy correction routine in lags                       |

| B 1 | Cache bandwidth benchmark                               |

# Acronyms

ALE Arbitrary Lagrangian Eulerian.

AMR Adaptive Mesh Refinement.

AoS Array of Structures.

AoSoA Array of Structures of Arrays.

**API** Application Programming Interface.

**ARB** Architecture Review Board.

ASC Advanced Simulation and Computing.

AVX Advanced Vector Extensions.

**BIOS** Basic Input/Output System.

CBRNG Counter-Based Random Number Generation.

$\mathbf{CFL}$  Courant-Friedrichs-Lewy condition.

**CG** Conjugate Gradient.

**CPU** Central Processing Unit.

**CUDA** Compute Unified Device Architecture.

**DOE** Department of Energy.

**DP** Double Precision.

**DRAM** Dynamic Random Access Memory.

**DSL** Domain Specific Language.

${\bf ENDF}\,$  Evaluated Nuclear Data File.

${\bf EOS}\;$  Equation of State.

**FLOP** Floating Point Operation.

FMA Fused Multiply Addition.

Acronyms xvii

**FP** Floating Point.

GCC GNU Compiler Collection.

**GPU** Graphics Processing Unit.

**HBM** High Bandwidth Memory.

**HPC** High Performance Computing.

**ISA** Instruction Set Architecture.

KNL Intel Xeon Phi Knights Landing.

LANL Los Alomos National Laboratories.

LCG Linear Congruential Generator.

LLNL Lawrence Livermore National Laboratories.

LOC Lines of Code.

MCDRAM Multi-Channel Dynamic Random-Access Memory.

MCNP Monte Carlo N-Particle Tranport Code.

MPI Message Passing Interface.

**NUMA** Non-Uniform Memory Access.

**ORNL** Oak Ridge National Laboratories.

**PCI** Peripheral Component Interface.

**PDE** Partial Differential Equation.

${\bf POSIX}\,$  Portable Operating System Interface.

PTX Parallel Thread Execution.

**SASS** Streaming Assembler.

**SDE** Intel Software Development Emulator.

${\bf SIMD}\,$  Single Instruction Multiple Data.

**SIMT** Single Instruction Multiple Thread.

**SM** Streaming Multiprocessor.

**SMT** Simultaneous Multi-Threading.

**SoA** Structure of Arrays.

TLB Translation Lookaside Buffer.

**TRT** Thermal Radiative Transfer.

WOC Words of Code.

### Chapter 1

### Introduction

Supercomputing is an essential component of modern scientific progress. Many areas of science reached the limits of analytical and numerical analysis on paper decades ago, and this pushed computer-assisted simulation to the forefront. The use of computers to solve complex mathematical problems spans the last century, and the prevalence of computational simulations in the sciences has lead to many scientists being directly involved in or responsible for the development of software projects.

The scale of the challenge from a computational perspective is astounding, and the continual increase in parallelism and architectural nuances increase the complexity greatly. To use any modern supercomputer, scientists are required to develop their code for parallel computation, notoriously one of the most challenging and error prone branches of software development. It is essential that the task is made as accessible as possible so that the majority of focus can be directed towards solving scientific problems. Over the last century, computing for science has grown from individual calculations on high speed single core processors, to computations spanning tens of thousands of nodes containing heterogeneous processors. The scientific applications can potentially span millions of lines of code, and can be expected to port to modern parallel processors and scale across millions of cores. A typical scientific workload might even involve multiple distinct packages co-operating in the solution of a system of equations.

Given a single persistent supercomputing architecture, it would be possible to develop scientific simulations while focusing purely on the computational concerns, optimising to the greatest possible extent for that particular platform. In reality, modern supercomputing resources are being constantly updated and replaced, to the extent that applications written for previous generations of CPU likely might not perform optimally on modern generations of CPU without tuning. The rapid rate of growth of computing in the sciences, and unpredictable technological changes, has introduced a multitude of problems for long standing scientific software applications.

With the repurposing of GPUs for general computing, compute architectures began to diversify even further, and targeting the new processors has become a highly challenging problem in of itself. Many supercomputers are now comprised of heterogeneous parallel processors, such as the 26000 NVIDIA V100 GPUs and 9000 POWER9 CPUs present in the world's fastest supercomputer, Summit, at Oak Ridge National Laboratory [154]. The Trinity supercomputer at Los Alomos National Laboratory will contain thousands of Intel Xeon and Intel Xeon Knights Landing CPUs. There is an expectation that the Department of Energy (DoE) simulations will be ported to both platforms; however, maintaining code bases for individual architectures

represents an unacceptable overhead, and so performance portable approaches are needed.

Many production scientific applications have been written to target clusters using the Message Passing Interface (MPI), which enables distributed computing and parallel execution on multi-core CPUs. The legacy codes written with MPI must be ported to enable threaded parallelism, which is in the best case an exercise in adding parallelisation to each computational loop, and in the worst case might require total redevelopment of the code and internal algorithms. Not only is the portability an important concern with porting legacy applications, but it is also imperative for scientific progress that the applications are not unduly inefficient. Enabling performance in large scientific software applications targeting modern parallel processors is a challenging area that requires an intimate understanding of the architecture, relevant algorithms, and the nuances of efficient parallel programming.

The size and structure of legacy applications makes it essentially impossible to perform agile experiments threading or optimising algorithms, without a large dedicated code team. The use of proxy applications has become the popular vehicle for such investigations, enabling research to quickly determine ideal algorithms, data structures, and parallel descriptions [63]. This thesis will concentrate on four new exemplar proxy applications that represent important classes of applications simulating physical processes: Eulerian and Lagrangian hydrodynamics, heat diffusion via conjugate gradient (CG) solve, and Monte Carlo neutral particle transport. Hydrodynamics and heat diffusion are quite general methods that can represent fluid motion and diffusive processes for a number of scientific areas. Monte Carlo neutral particle transport is more specific, and is particularly used in medical imaging and dosimetry, and reactor simulation [5] [133].

Although the principal focus of this thesis is the simulation of physical processes, it is expected that the techniques and concepts generalise to many areas of science, as the principles are relatively consistent. Most processes in science measure the phenomenon of change, requiring the numerical solution of partial differential equations, which is fundamentally the focus of the subsequent discussions. The expectation is that the work in this thesis will present important information about the state of existing parallel processors, optimisation techniques, and the performance portability of parallel programming models, in relation to applications that cover a sufficiently broad range of techniques for numerical solution of such PDEs. Several of the computational dwarves proposed by Asanovic et al. are represented within the thesis: Structured Grids, Unstructured Grids, Monte Carlo methods, and Sparse Linear Algebra [6].

The Structured Grid and Sparse Linear Algebra applications, Eulerian hydrodynamics and heat diffusion via CG solve, are well understood and have previously been shown to achieve good performance on modern parallel processors [61] [42] [112]. In this thesis it has been possible to use those exemplar applications to evaluate a number of modern parallel programming models, considering the impact from the perspective of performance, portability and productivity. The Monte Carlo neutral particle transport problem was first published about in 1954, and the performance of the application on modern parallel architectures is an important and challenging topic [76]. During this thesis it has been possible to discover optimal approaches to parallelising Monte Carlo neutral particle transport applications on CPUs, GPUs, and KNLs. This required extensive experimentation at the algorithmic and data structure level, and the development of a novel sort-free algorithm to enable vectorisation on modern parallel architectures. Unstructured grids have been well considered in the literature, but the particular application considered in this thesis is Lagrangian hydrodynamics using a subcell discretisation for arbitrary polyhedra, which includes some interesting subtleties that will be discussed.

An challenge with all of the applications, but particularly Monte Carlo neutral particle

transport, is problem dependence. It is shown throughout that the results determined with proxy applications are greatly affected by changes in the target problem, and each of the applications is considered for a range of different parameters to account for this. There is also the challenge of faithful representation of the production application features, as missing important features in a proxy application could potentially lead to optimisations and parallel descriptions that do not scale into real applications. Where possible, the potential features of each of the exemplar applications are considered.

#### 1.1 Contributions

The following contributions are complementary towards the core aim of presenting a thorough treatise of concerns related to the porting of production scientific applications.

#### 1.1.1 The arch Project: Physics Proxy Applications

To support this thesis, a suite of physics proxy applications have been developed under a common architectural framework and permissive MIT license named the arch project<sup>1</sup>. Each of the proxy applications represents a reduced feature-set proxy for production applications solving a multitude of scientific problems, and analysis of those applications is presented in Chapters 5 to 7. The supporting infrastructural project, arch, provides cross-cutting concerns, such as MPI communications, memory management, and support for structured and unstructured meshes. Although the suite was intended to support and motivate the discussions in this thesis, it is becoming adopted as a tool for performance optimisation and algorithmic studies by the wider community [150].

#### 1.1.2 Analysis of Performance Portability for Physics Applications

Performance portability has been shown to be a major challenge facing the future of large-scale scientific simulation, and achieving performance portability has been described as the gold standard for programming environments [82]. For scientific developers, performance portability starts with the choice of parallel programming model. Choosing an appropriate parallel programming model will have vast implications for the success of a large scientific applications. There are many models available, each presenting different characteristics and trade-offs, making the decision-making process highly challenging for scientific application developers. This thesis considers some of the most successful parallel programming models, OpenMP, CUDA, OpenACC, and RAJA, and their impact on performance, portability and productivity. The thesis contains recommendations for best practices when using performance portable parallel programming models, based on experiences porting the arch applications (Chapters 5 to 7).

#### 1.1.3 Benchmarking of HPC Architecture Performance

In some cases there are publicly available details regarding the low level performance of particular processors, but it is not always possible to find this information for specific SKUs. Further, in some cases the vendors do not publicly expose such information or provide benchmarking tools. In order to reason about the performance of the applications, particularly the Monte Carlo neutral particle transport application (Chapter 5), it was necessary to benchmark the fine

<sup>&</sup>lt;sup>1</sup>https://github.com/uob-hpc/arch

details of the architectures. This benchmarking process considers details like memory latency, memory bandwidth at all cache levels, and random memory access performance (Chapter 4). The results supported later reasoning and modeling of the performance of the arch applications.

#### 1.1.4 Optimisation of Monte Carlo Neutral Particle Transport

This thesis considers a subset of proposed parallel computational patterns, their performance patterns, and the techniques required to optimise them on the most modern supercomputing resources. In particular, the best algorithms are found for the Monte Carlo neutral particle transport problem targeting NVIDIA GPUs, demonstrating impressive performance in spite of the divergent code (Chapter 5). Poor performance due to lack of vectorisation and challenging issues of latency on the CPU and KNL are improved through the development and optimisation of a novel sort-free algorithm for vectorising the particle tracking loop. The extent of problem dependence is demonstrated using a number of different case study problems, and results are presented in such a manner that they should be relevant to the transport of any neutral particle.

#### 1.1.5 Analysis of Complex Production Concerns

Porting and optimising scientific software applications requires a rigorous consideration of key algorithms, often requiring the use of proxy applications to reduce the computational complexity to a minimal level so that a computer scientist can investigate optimisations. The success of those proxy apps is measured on their ability to translate optimisations back into their production counterparts, demanding careful consideration of the included features chosen as a subset.

Proxy apps tend to exclude complex features of production applications, and this thesis posits that this can inhibit the generalisation of results in many cases. For instance, there are few scientific simulations that handle only individual materials, with most instead requiring complex interfaces, which is something rarely included in proxy applications. The treatment of multimaterial interfaces is a significant burden to the computer scientist but has major implications for the portability and performance on modern architectures. This issue is explored alongside the arch applications in Chapter 8.

#### 1.2 Structure of Thesis

In this chapter the motivation for this thesis has been presented, and the subsequent chapters in this thesis address the following problems:

- Background (Chapter 2): This chapter includes the fundamental concepts of parallel and distributed computing, as well as some basic details regarding computational solution of partial differential equations necessary to follow the subsequent sections.

- Programming Models and Performance Portability (Chapter 3): Parallel programming models are an important aspect of porting applications to use modern hardware. This chapter provides a light background to the parallel programming models OpenMP (3.0 and 4.5), OpenACC, RAJA, and CUDA. A discussion about the current understanding and literature relating to the state of the art in performance portability is then presented.

- HPC Architecture Performance (Chapter 4): In order to optimise for the considered parallel processors, it is important to understand the performance characteristics of the

processors themselves. In this chapter, empirical results are presented for many aspects of the processors. This was either because accurate data was not available from the hardware vendor for the particular processor variant, or the results are markedly different between the marketed data.

- Monte Carlo Neutral Particle Transport (Chapter 5): This is the first application optimisation chapter, and focuses on the Monte Carlo neutral particle transport application neutral, which is part of the arch project. A thorough performance investigation is undertaken at the algorithmic, data structure and parallel programming level. An optimal GPU implementation is developed that greatly improves upon the performance of the traditional methods on the CPU. A novel algorithm is developed that enables vectorisation of the particle tracking loop without requiring sorting of particles. The problem dependence of the application is also considered, and a discussion is presented about those features not considered that could result in different performance characteristics.

- Heat Diffusion via a Conjugate Gradient Solver (Chapter 6): This chapter considers the performance of the conjugate gradient solver, through the arch application hot. In particular, the performance portability of the application with respect to modern parallel programming models is explored. The issue of solving problems with cache-resident meshes is explored with respect to the parallel programming models, to show that there are significant overheads present in the models that might show up in other application domains.

- Hydrodynamics (Chapter 7): Hydrodynamics is a particularly important application class that is used in the majority of areas of science and engineering. This chapter will explore two hydrodynamics proxy applications from arch, the 2D structured Eulerian hydrodynamics application flow, and the 3D unstructured Lagrangian hydrodynamics application lags. The flow application will be considered in terms of parallel programming models, and the capability of each to provide performance portability for the application. The lags application is used to explore the space of unstructured meshes and subcell computations, and the implications on parallel performance.

- Production Challenges (Chapter 8): This chapter presents some critical analysis of the work in the preceding chapters, by considering the impact of those features that might be present in production applications but that were not directly optimised for. Results are presented for a set of benchmarks directly targeting the complex production problem of multi-material data structures, and a consideration for how those features are extended into the dynamic structures of Eulerian flow fields. Through this discussion it is possible to consider the potential impact on the final efficacy of results from using proxy application in performance studies.

#### 1.3 Reasoning for arch

The principal focus of this thesis will be directed towards a number of exemplar applications that have been chosen due to their relevance to the wider area of simulating physical processes. Each of the exemplar applications has been developed from scratch specifically for the project described in this thesis. There are a number of reasons that made it essential to use new

applications rather than rely upon existing applications, some specific to the application and others more generally.

- An open source Monte Carlo proxy application was not available with the particular characteristics required for the performance studies performed. Towards the end of the thesis project, the Quicksilver proxy application was released by Lawrence Livermore National Laboratories, which might have been a suitable candidate but the neutral application was already developed, and the majority of the research was already published.

- Many different hydrodynamical simulations were developed, including Eulerian, Lagrangian, and ALE. In order to maintain a fair comparison it was essential that they were all consistently developed and this cannot be offered by existing proxy applications. The proxy applications CloverLeaf and PENNANT offer similar features to the Eulerian and Lagrangian applications in the arch project, but are written in different programming languages and are many times larger than flow and hot. One important characteristic that was explored with lags was the concept of subcell computations, which had a significant impact on the performance and was not available in the alternative applications.

- Developing the applications to rely upon a single common infrastructural layer means that it is possible to make commentary about the issues of hosting multiple physics packages within a single framework. This will be shown to have important consequences in terms of portability in Chapter 8.

- The common infrastructural layer meant that the core computational code of each application was generally limited to 1000 lines of code, except for the ALE application hal3d, which was purposefully developed to consider the issue of large applications. This means that experiments could be performed in much less time than would be required to port larger applications such as the hydrocode PENNANT (5000 LOC) and the Monte Carlo application Quicksilver (13000 LOC).

It can be noted that the proxy applications CloverLeaf, TeaLeaf, and PENNANT were all used as part of this project and many of the relevant publications are relative to those applications. Although the arch applications have been developed from scratch using open source methods, the individual applications were optimised using already published techniques to avoid duplication of efforts.

### Chapter 2

# Background

#### 2.1 Parallel Computing Architecture

Moore's law states that the number of transistors per chip grows at an exponential rate with a constant cost, doubling roughly every 18 months [118]. Dennard et al. observed that reducing the size of transistors meant that voltages could be decreased, thereby maintaining a constant power based on area rather than density [38]. More recently, since around 2006, transistors have become so small that leakage and threshold voltage restrictions have ended Dennard scaling, limiting the potential for single core performance.

There are a number of architectural adjustments that can aid in reducing the impact of heat while allowing an increase in performance. This section includes a succinct foundation in parallel computing to form a basis for the subsequent discussions in the thesis.

#### 2.1.1 Instruction Pipelining

Instruction pipelining exploits inherent parallelism in the architectural processing of machine instructions.

Figure 2.1: Instructions issued with (bottom), and without (top) instruction pipelining. The colours represent stages required to issue full instruction, e.g. fetch, decode, execute, write.

In modern processors, machine instructions are broken into micro-operations, which are the dependent stages in an instruction [60]. The top of Figure 2.1 depicts the scenario that 4 instructions are issued, requiring 16 micro-operations. Each stage, the coloured squares, of each instruction takes one cycle to complete before the next stage can occur, a throughput of 1 instruction per 4 cycles.

The benefits of pipelining can be realised from the observation that this approach underutilises the available pipeline stages, as when decoding, for instance, the fetch and other units will sit idle. To improve the throughput, each micro-operation can be added to a pipeline, allowing overlapped processing of those micro-operations of independent instructions. The bottom of Figure 2.1 depicts 4 machine instructions issued to a processor that supports pipelining.

It can be seen that following an initial latency of 3 cycles, the 4 deep pipeline can keep all four pipeline stages active during a single cycle. Given an increasingly long stream of instructions the 4 deep pipeline can asymptote to a throughput of 1 instruction per cycle.

#### 2.1.1.1 Superscalar Processing

Superscalar processing is an architectural feature of many processors, where multiple instructions can be issued within a single clock cycle [74]. Of course this requires that pipeline stages are duplicated, but it allows several instructions to be passed into the pipeline on each cycle, increasing instruction throughput. This is another important feature of modern processors that must be accounted for when modelling and analysing performance.

#### 2.1.2 Vector Processing

Vector processing is an architectural design where vector registers can be filled with multiple operands, and arithmetic units operate on the set of operands with a single instruction, proven in early vector processors like the Cray-1 [142]. The benefit to this approach is that algorithms often apply the same instructions to multiple operands, and if those instructions are independent there is an inherent parallelism that vector processing exploits.

In modern CPUs, most core designs include vector registers and support SIMD instructions that can perform, for instance, a fused multiplication and addition on 16 words in a single cycle. For algorithms that are sensitive to computational performance this is a significant increase in throughput.

Code Sample 2.1: Example of vectorisable loop in C.

```

// C loop

for(int i = 0; i < 8; ++i) {

a[i] = b[i] * c[i];

}</pre>

```

The C loop in Code Sample 2.1 is a canonical loop with a small constant trip count. On a scalar processor the loop iterations would need to be handled sequentially.

Code Sample 2.2 shows the C loop's x86 assembly code, where each individual element of the set of arrays is multiplied and stored in turn. Due to the small, constant trip count, the loop could be fully unrolled by an optimising compiler at high optimisation levels, removing the loop control instructions. This could potentially allow multiple instructions to be pipelined, taking advantage of the superscalar nature of the target processor. Considering that 'a', 'b' and 'c' are 8 floats in length, the arrays would be situated in L1 cache on current CPUs, and so the number of instructions is theoretically important to the performance of this loop.

Code Sample 2.2: Scalar loop in the x86 instruction set.

```

// Compiles to x86 scalar loop

..loop:

movss (%rdx,%rax,4), %xmm0  // Move b[i] to register xmm0

mulss (%rcx,%rax,4), %xmm0  // b[i] * c[i] (result in xmm0)

movss %xmm0, (%rsi,%rax,4)  // Store result in a[i]

incq %rax  // Increment counter 'i'

cmpq 8, %rax  // Compare counter 'i' with 8

jl ..loop  // Loop back if 'i < 8'

```

Code Sample 2.3 depicts the same code but compiled with the Advanced Vector Extensions 2 (AVX2), an extension to the x86 instruction set for SIMD parallelism. There is no longer a loop, as the AVX2 instruction set includes 256-bit instructions capable of processing 8 floats with a single instruction. Given a possible instruction latency of 1 cycle for the multiplication, the vector processing approach is highly effective in algorithms where the operands are readily available.

Code Sample 2.3: Vector instruction in AVX2 instruction set.

```

vmovups (%rsi), %ymm0

// Move b[] to register ymm0

vmulps (%rdx), %ymm0, %ymm1

// b[] * c[] (result in ymm1)

vmovups %ymm1, (%rdi)

// Move result to a[]

```

It is only correct to vectorise loops where there are no loop carried dependencies, or the loops can be transformed to have independent work for vector processing. Modern optimising compilers use a range of transformations to ensure that the majority of sane code is vectorised automatically, but there are many situations where programmer intervention is required. Enabling vectorisation or encouraging auto-vectorisation is discussed in the chapter discussing Programming Models (Chapter 3), and throughout the subsequent chapters dealing with individual scientific applications (Chapters 5 to 7).

#### 2.1.3 Multi-core Computer Architecture

Once the practical limits of single core designs had been reached, the next source of processing power growth came from increasing core counts. In 2001, IBM designed the first dual-core processor, demonstrating the feasibility of placing multiple cores on a single die [156].

Increasing the number of cores in a CPU allows the processing power to be increased while maintaining consistent clock speeds and staying within a reasonable power envelope. There have been many different approaches to architecting multi-core processors: varying core counts, speeds, memory locations, and other factors. Once an additional core is added to a processor, the complexity of the architecture and programming approach is significantly increased, and modern CPUs can contain hundreds of cores.

#### 2.1.3.1 Cache coherency

The introduction of multiple cores means that cache coherency mechanisms need to be added to ensure that the cores do not read or write incorrect data [60]. In Figure 2.2, a hypothetical multi-core architecture is presented, depicting the cores and cache hierarchy. Each core is directly connected to a private L1 cache, and it is possible for data to be duplicated from DRAM into both L1 caches at the same time.

In the event that there is duplicate data and one thread wants to write while the other wants to read from the same address, then there is a data race, but one which cannot be predicted as a programmer. The hardware has to include some mechanism for updating all caches when one of the cores attempts to change a value in an individual cache, which is known as write propagation.

If both caches contain a duplicate memory entry and subsequently write back to that memory address there is a data race. The hardware is only responsible to ensure that those writes are fulfilled in cache in the origi-

Figure 2.2: A cache layout for a hypothetical CPU architecture.

nal order requested. As such, if Core 0 writes a value to cache and Core 1 subsequently writes to the same location, the value residing within cache after the operations are complete must be the value output by Core 1. It is the province of the programmer to ensure that such output dependencies are avoided.

#### 2.1.3.2 Multi-socketing