## This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Jin, Bosen

Title:

Topology, Efficiency Analysis and Control of Four-level -type Converters

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

**Take down policy** Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

Your contact details

Bibliographic details for the item, including a URL

• An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Topology, Efficiency Analysis and Control of Four-level $\pi$ -type Converters

By

## Bosen Jin

A dissertation submitted to the University of Bristol in accordance with requirements of the degree of Doctor of Philosophy in the Faculty of Engineering, Department of Electrical and Electronic

Engineering

Jan 2019

Word count: 60859

#### Abstract

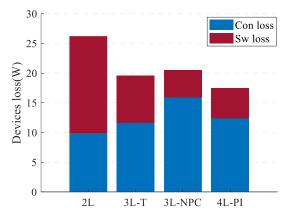

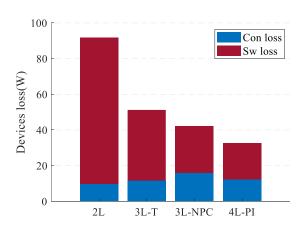

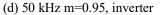

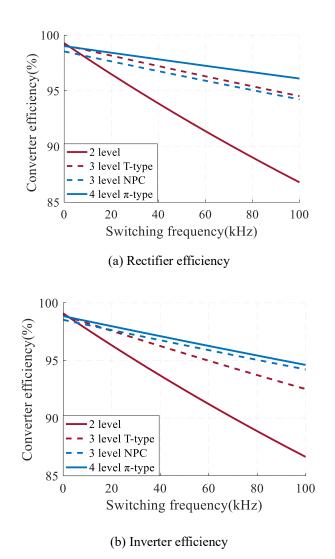

The main focus of my PhD is to investigate and explore more efficient, reduced switching devices count four-level  $\pi$ -type converter topologies for low voltage applications ( $V_{dc}$ <600V). This thesis presents the work on four-level  $\pi$ -type converters during my PhD period. Average analytical mathematical models for analyzing the device power loss and the efficiency of the four-level  $\pi$ -type converter topology have been established. It has been found out that with the same input power level and the same dc input voltage, the four-level  $\pi$ -type converter can provide higher efficiency when switching frequencies are above 5 kHz compared to two-level and three-level converters due to lower switching losses.

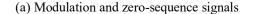

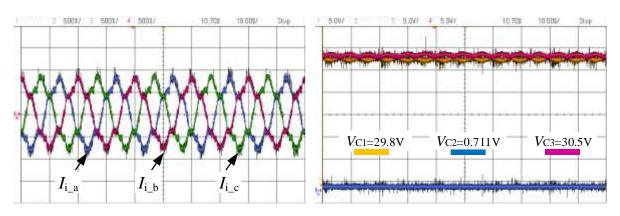

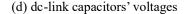

In order to resolve dc-link neutral points (NP) voltages unbalancing issues of neutral points clamped (NPC) multilevel converters, a carrier-based modulation (CB-PWM) NPs' voltages balancing control with optimum zero-sequence signals injection for the four-level  $\pi$ -type converter has been investigated. Simulations and 300V dc input voltage experimental results proved that with a back-to-back configuration, the proposed control method is able to balance the three dc-link capacitors' voltages even at high modulation indices and high-power-factor conditions.

For the purpose to make the four-level  $\pi$ -type converter topology work as a single-end converter (inverter or rectifier) with balanced dc-link capacitors' voltages, a modified topology based on the original four-level  $\pi$ -type converter has been developed and analyzed. This new topology is named as the hybrid-clamped four-level  $\pi$ -type converter with one more flying capacitor (FC) as well as two additional switching devices. With such layout modification, more redundant switching states can be generated to regulate neutral path currents. Therefore, the hybrid clamped four-level  $\pi$ -type converter does not have modulation index or power factor limitations when operating as a single-end converter.

#### Acknowledgements

I would like to take this opportunity to acknowledge my gratitude to the people who have kindly given their help to my study and research over the last four years.

First, I must thank my primary supervisor, Prof. Xibo Yuan, for his continuous guidance, support and encouragement throughout my whole PhD study and research. He believed in me and allowed me to take the research towards the direction that I found more interesting. I would also like to thank my second supervisor, Prof. Philip Mellor for his support and feedback throughout my studies.

I would like to thank Dr. David Drury for being my reviewer during my PhD study in suggesting and improving the details of my research.

I would like to thank Dr. Neville McNeill for assisting in my hardware design knowledge improvement, and for his valuable technical input throughout the course of my research.

I gratefully acknowledge the support from the colleagues in the Electrical Energy Management Group. They provide such a supportive environment to me. Particularly, I would like to thank Apollo Charalampous, Mo Al-Akayshee, Yonglei Zhang, Xu Liu, Jun Wang for all their help and assistant.

Finally, I would like to thank my parents, my friends, and especially my wife Yi Zeng, who were always next to me during this long journey.

Page intentionally left blank

#### **Author's Declaration**

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and code of Practice for Research Degree Program and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

Signed: ..... Name: Bosen Jin Date: Jan 2019

#### **Publications**

- B. Jin, X. Yuan, "Power Loss and Efficiency Analysis of a Four-level π-type Converter," in *Proc. IEEE EPE'15 Conf.*, pp. 1-10, Oct 2015.

- B. Jin, X. Yuan, "Control of a Four-level Active Neutral Point Clamped Converter with Neutral Point Voltage Balance," in *Proc. IEEE IPEMC'16 Conf.*, pp. 2337-2344, May 2016.

- B. Jin, X. Yuan, "Neutral Points Voltage Balancing Control of a Four-level π-type Converter," *IEEE ECCEc'16 Conf.*, pp. 1-8, Sept 2016.

- N. McNeill, B. Jin, X. Yuan, "Proportional Regenerative Base Driver Circuit with Negative Off-State Voltage for SiC Bipolar Junction Transistors," in *Proc. IET PEMD'16 Conf.*, pp. 1-6, Apr 2016.

- I. Laird, B. Jin, N. McNeill, X. Yuan, "Performance Comparison of 3-phase DC/AC Converters using SiC MOSFETs or SiC BJTs," in *Proc. IEEE IECON'17 Conf.*, pp. 1393-1398, Dec 2017.

- I. Laird, X. Yuan, B. Jin, N. McNeill, "High Temperature Design Optimization of DC/AC Power Converters using SiC BJTs," in *Proc. IEEE ECCE'18 Conf.*, pp. 1505-1512, Sept 2018.

- N. McNeill, X. Yuan, B. Jin, "A Super-Junction MOSFET-based 99%+ Efficiency T-Type Multilevel Converter," in *Proc. IEEE ECCE'18 Conf.*, pp. 5643-5650, Sept 2018.

- B. Jin, X. Yuan, "Topology, Efficiency Analysis and Control of a Four-level π-type Converter," *IEEE JESTPE.*, vol. 7, No. 2, pp. 1044-1059, June 2019.

#### Submitted

N. McNeill, X. Yuan, B. Jin, "Evaluation of the Off-State Base-Emitter Voltage Requirement of the SiC BJT with a Regenerative Proportional Based Driver Circuit and their Application in an Inverter," *IEEE Trans. Ind. Electron.*  Page intentionally left blank

## List of abbreviations

| CB-PWM  | Carrier-based pulse width modulation                  |

|---------|-------------------------------------------------------|

| DSP     | Digital signal processer                              |

| EV      | Electric vehicle                                      |

| FC      | Flying capacitor                                      |

| FPGA    | Field programmable logic array                        |

| FTT     | Fast Fourier Transform                                |

| KVL     | Kirchhoff's Voltage Law                               |

| NP      | Neutral point                                         |

| NPC     | Neutral point clamped                                 |

| NTV PWM | Nearest three vectors pulse width modulation          |

| p.u.    | Per-unit                                              |

| PI      | Proportional-Integral                                 |

| PS      | Phase-shifted                                         |

| PV      | Photovoltaic                                          |

| SHE-PWM | Selective harmonic elimination pulse width modulation |

| SVM     | Space vector modulation                               |

| THD     | Total harmonic distortion                             |

| VV PWM  | Virtual vector pulse width modulation                 |

|         |                                                       |

## Contents

| Ab  | stract. |                                                                                | 2 |

|-----|---------|--------------------------------------------------------------------------------|---|

| Acl | knowl   | edgements                                                                      | 3 |

| Au  | thor's  | Declaration                                                                    | 5 |

| Puł | olicati | ons                                                                            | 6 |

|     | Sub     | mitted                                                                         | 6 |

| Lis | t of al | obreviations                                                                   | 8 |

| Lis | t of sy | /mbols                                                                         | 1 |

| 1   | Intro   | oduction                                                                       | 1 |

|     | 1.1     | Why multilevel converters and background                                       | 1 |

|     | 1.2     | Research objectives                                                            | 5 |

|     | 1.3     | Thesis layout                                                                  | 6 |

| 2   | Lite    | rature review                                                                  | 8 |

|     | 2.1     | Multilevel converter topologies review                                         | 8 |

|     |         | 2.1.1 Cascaded H-bridge converter                                              | 8 |

|     |         | 2.1.2 Flying capacitor (FC) converter 1                                        | 1 |

|     |         | 2.1.3 Neutral point clamped (NPC) converter 1                                  | 5 |

|     |         | 2.1.4 Generalized multilevel converter topologies 1                            | 8 |

|     |         | 2.1.5 Discussion about different applications of topologies with their designs | 1 |

|     | 2.2     | Popular NPC multilevel converters                                              | 3 |

|     |         | 2.2.1 Three-level diode NPC converter                                          | 3 |

|     |         | 2.2.2 Three-level T-type converter                                             | 6 |

|     |         | 2.2.3 Four-level diode NPC converter                                           | 9 |

|     | 2.3     | Power loss and efficiency analysis for the converter                           | 0 |

|     |         | 2.3.1 Why power loss analysis and kinds of power loss                          | 0 |

|     |         | 2.3.2 Average analytical model                                                 | 2 |

|     |         | 2.3.3 Numerical simulation                                                     | 6 |

|     | 2.4     | Converter dc-link NP voltages balancing 4                                      | 1 |

|     |         | 2.4.1 The effect of the converter dc-link NP voltages unbalancing issue        | 1 |

|   | 2.4.2 Existing converter dc-link voltage balancing control strategy                             | 44      |

|---|-------------------------------------------------------------------------------------------------|---------|

|   | 2.5 Summary                                                                                     | 60      |

| 3 | Four-level $\pi$ -type converter topology and modulation technique                              | 62      |

|   | 3.1 Introduction                                                                                | 62      |

|   | 3.2 Topology introduction and modulation scheme                                                 | 63      |

|   | 3.3 Switching devices voltage rating analysis                                                   | 70      |

|   | 3.4 Topology comparison between four-level $\pi$ -type converter, three-level T-type converter, | three-  |

|   | level diode NPC converter, and two-level converter                                              | 75      |

|   | 3.4.1 Layout characteristics comparison between four-level $\pi$ -type converter, three-le      | evel T- |

|   | type converter, three-level diode NPC converter, and two-level converter                        | 75      |

|   | 3.4.2 Operation comparison between four-level $\pi$ -type converter, three-level T-type con     | verter, |

|   | three-level diode NPC converter, and two-level converter                                        | 77      |

|   | 3.5 Summary of Chapter 3                                                                        | 88      |

| 4 | Power loss analysis for the four-level $\pi$ -type converter                                    | 90      |

|   | 4.1 Introduction                                                                                | 90      |

|   | 4.2 Average analytical power loss model establishment                                           | 91      |

|   | 4.2.1 Average analytical model of conduction losses                                             | 91      |

|   | 4.2.2 Average analytical model of the switching loss                                            | 102     |

|   | 4.3 Power loss calculation analysis based on the proposed power loss model                      | 113     |

|   | 4.3.1 Loss model comparison                                                                     | 119     |

|   | 4.4 Prototype design and converter efficiency measurement                                       | 123     |

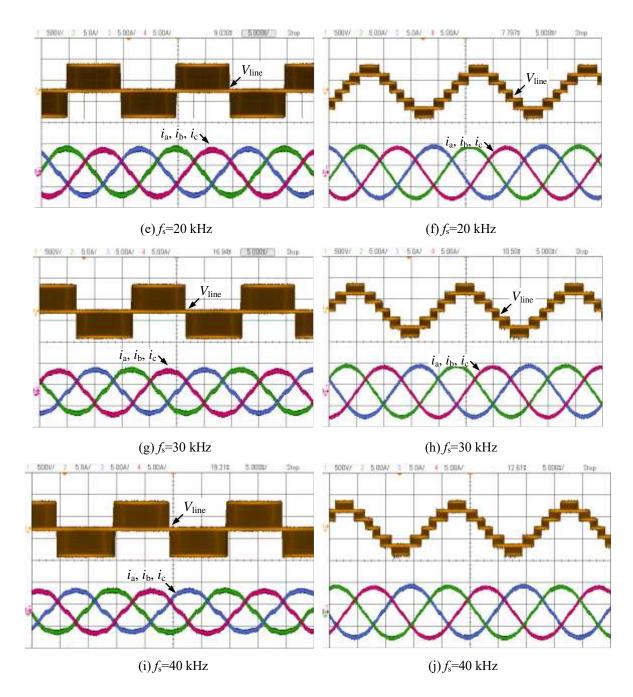

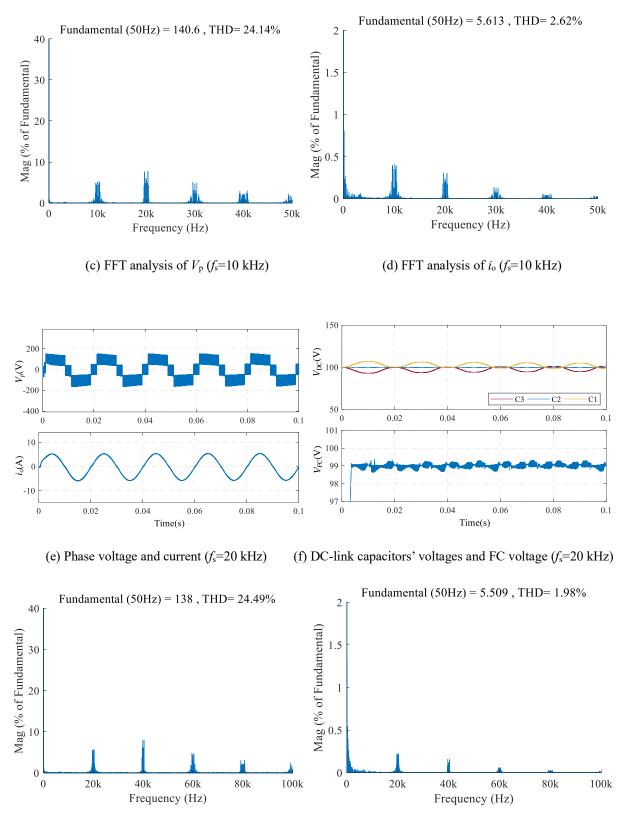

|   | 4.4.1 Test output waveforms comparison                                                          | 129     |

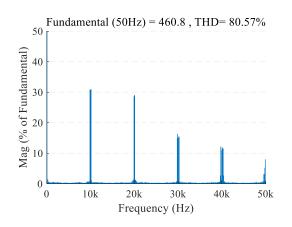

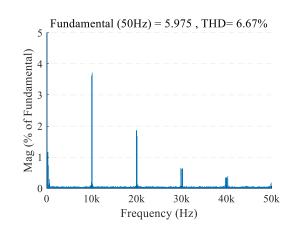

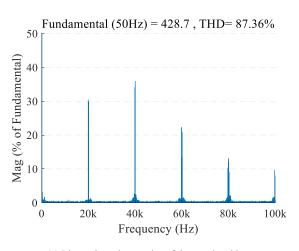

|   | 4.4.2 Harmonic analysis and comparison                                                          | 130     |

|   | 4.4.3 Efficiency simulation and test comparison                                                 | 133     |

|   | 4.5 Summary of Chapter 4                                                                        | 135     |

| 5 | Control strategy for the four-level $\pi$ -type converter                                       | 137     |

|   | 5.1 Introduction                                                                                | 137     |

|   | 5.2 DC-link NP voltages unbalancing analysis based on the four-level $\pi$ -type converter      | 138     |

|   | 5.3 DC-link NP voltages balancing control                                                       | 145     |

|     | 5.4 Simulation analysis                                                                 | 54  |

|-----|-----------------------------------------------------------------------------------------|-----|

|     | 5.5 Exprimental tests                                                                   | 62  |

|     | 5.5.1 Single-end system test and investigation without the proposed control strategy 10 | 63  |

|     | 5.5.2 Single-end system test and investigation with the proposed control strategy       | 67  |

|     | 5.5.3 Back-to-back configuration test                                                   | 71  |

|     | 5.6 Summary of Chapter 5 18                                                             | 84  |

| 6   | New hybrid-clamped four-level $\pi$ -type converter                                     | 87  |

|     | 6.1 Introduction                                                                        | 87  |

|     | 6.2 Converter Controllability and Switching States                                      | 88  |

|     | 6.3 DC-link NP voltages balancing control and FC voltage control strategy               | 92  |

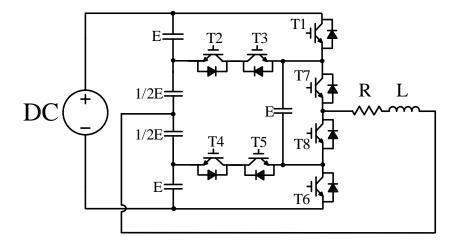

|     | a) FC voltage control                                                                   | 93  |

|     | b) DC-link NP voltages balancing control                                                | 95  |

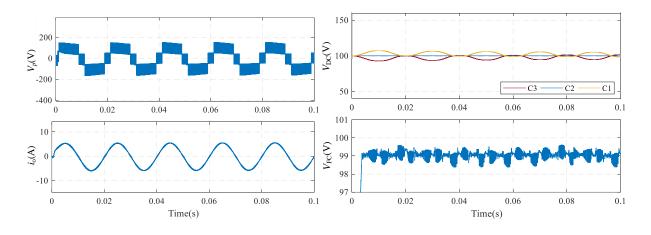

|     | 6.4 Simulation                                                                          | 06  |

|     | 6.5 Prototype and exprimental results                                                   | 11  |

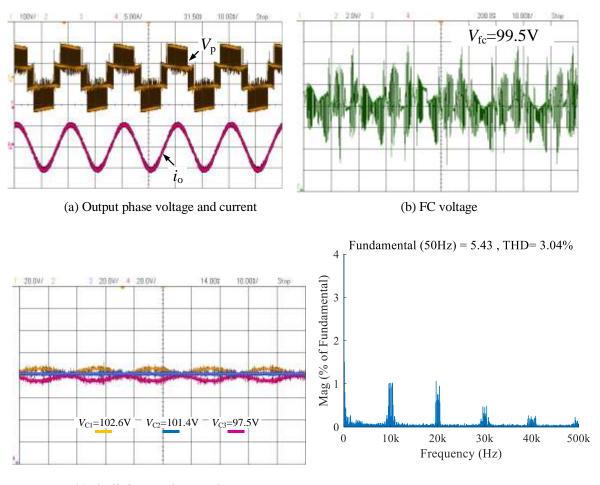

|     | a) Experimental results with the presented control                                      | 11  |

|     | b) FC voltage variation                                                                 | 15  |

|     | 6.6 Three-phase inverter operation simulation                                           | 21  |

|     | 6.7 Summary of Chapter 6                                                                | 24  |

| 7   | Conclusions and future work                                                             | 26  |

|     | 7.1 Contributions and conclusions                                                       | 26  |

|     | 7.2 Future work                                                                         | 30  |

| App | pendix2                                                                                 | 32  |

|     | Appendix A. Devices conduction loss and switching loss equation                         | 32  |

|     | I. Two-level converter                                                                  | 32  |

|     | II. Three-level NPC converter                                                           | 32  |

|     | III. Three-level T-type converter                                                       | 33  |

|     | IV. Four-level $\pi$ -type converter                                                    | 34  |

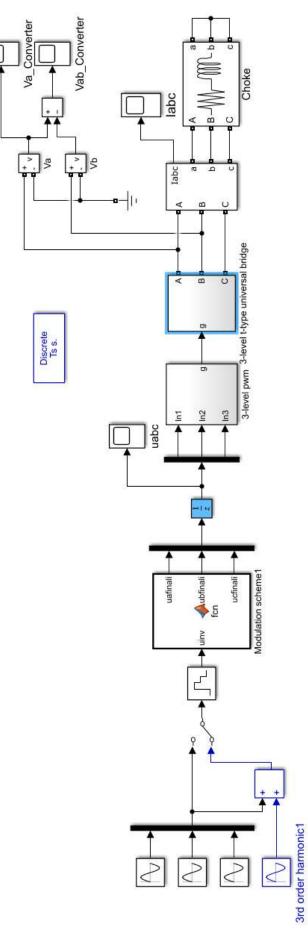

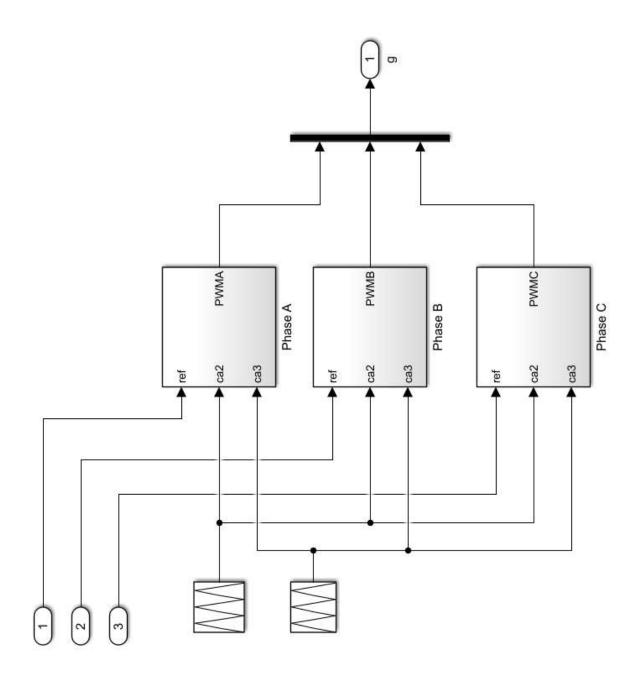

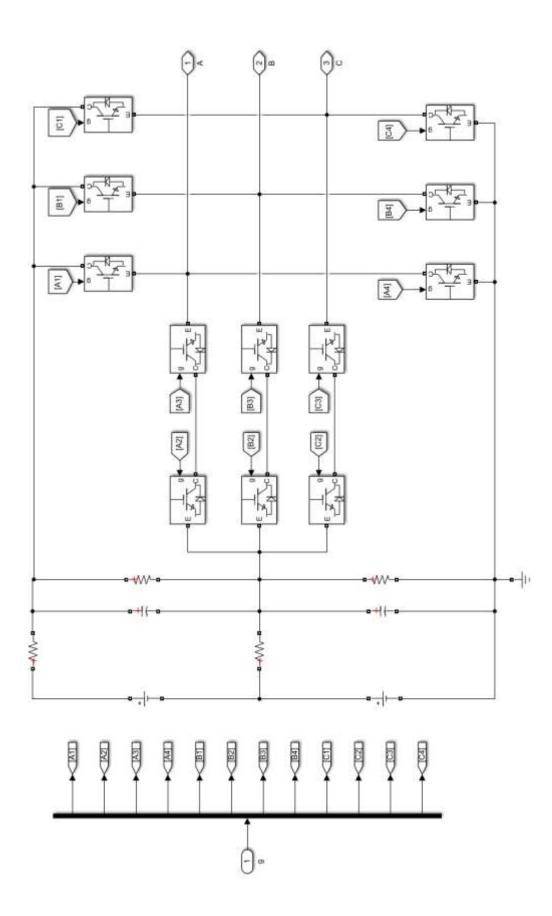

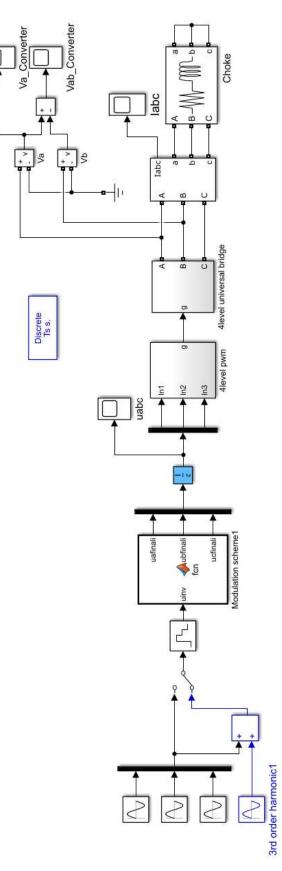

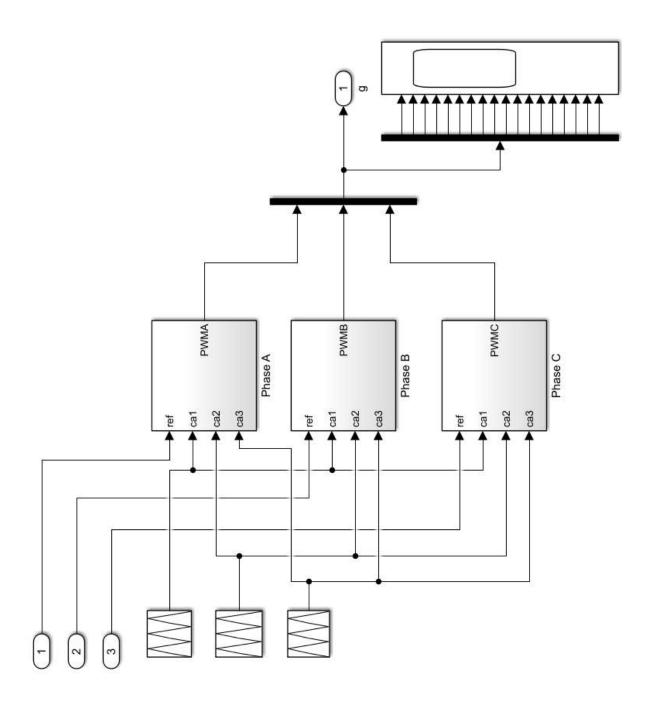

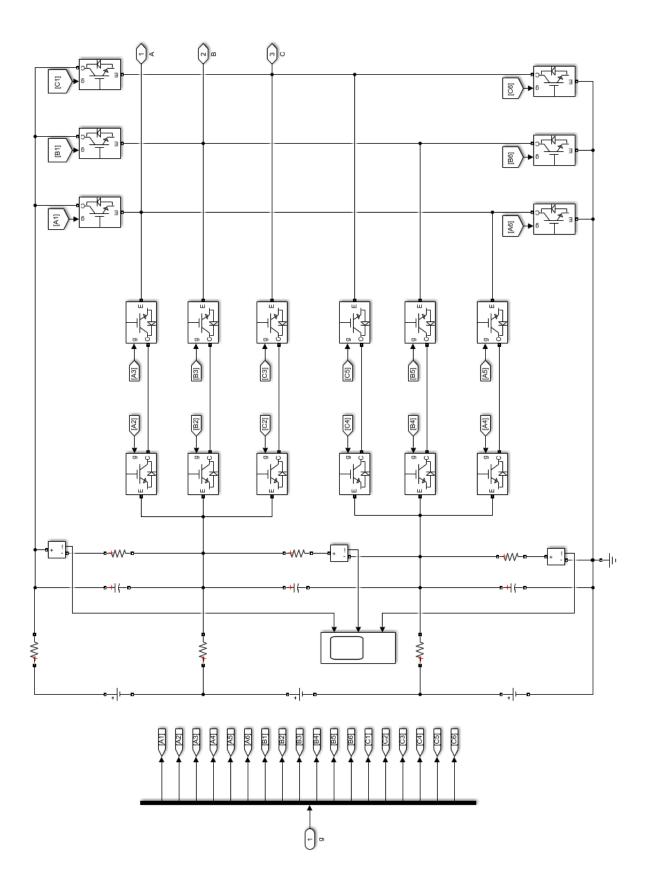

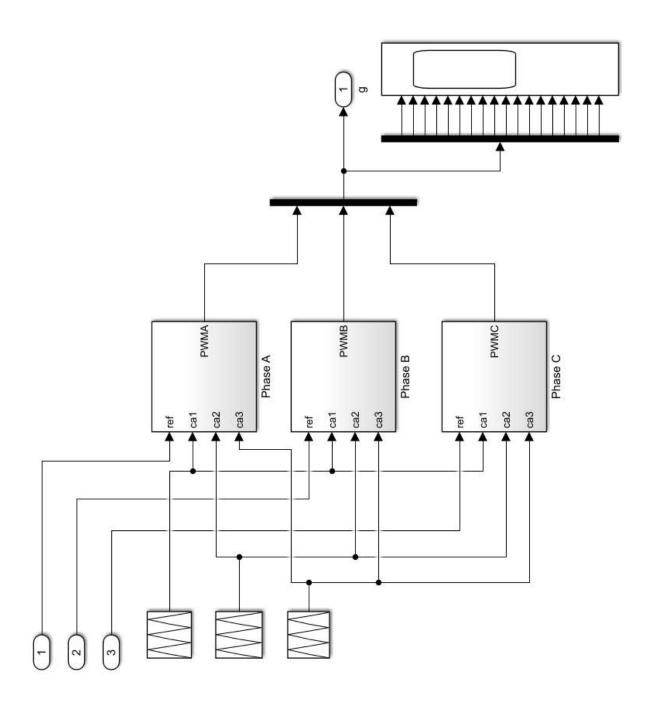

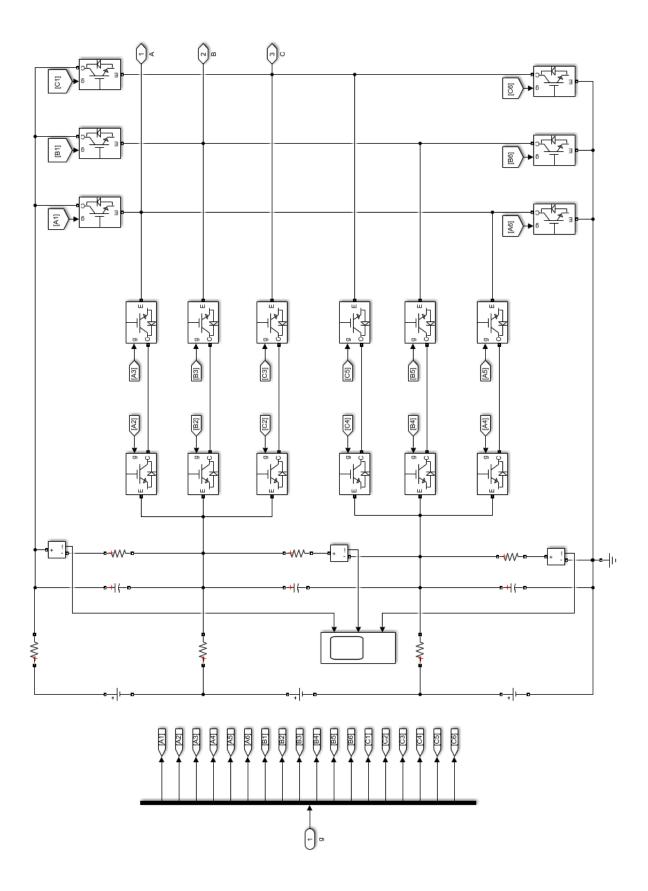

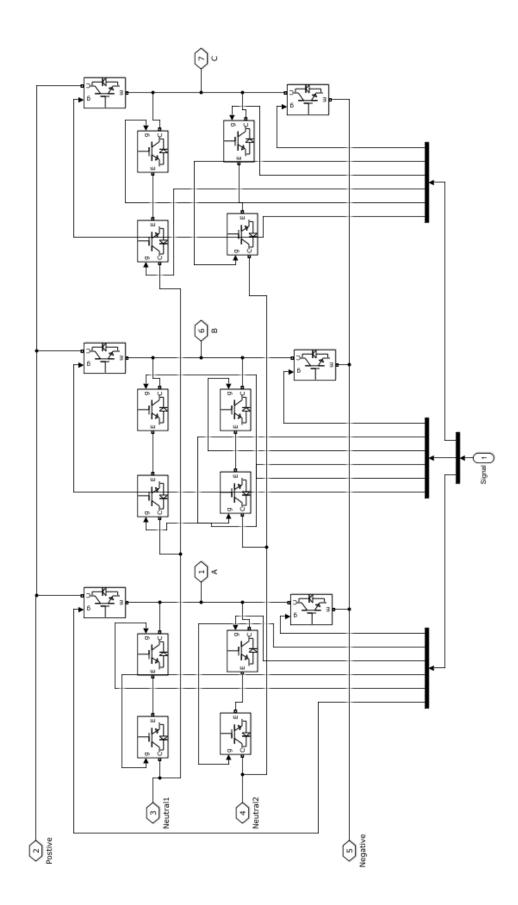

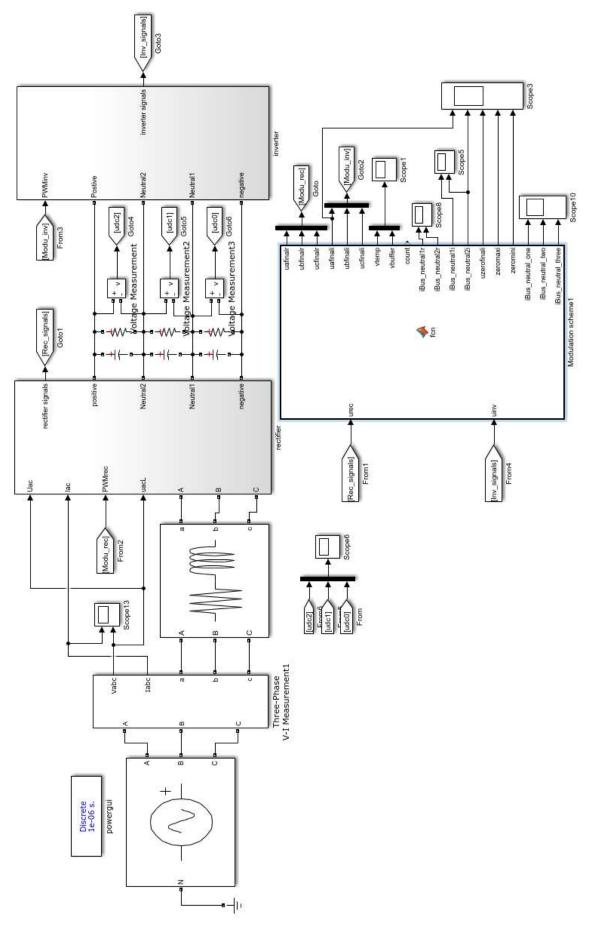

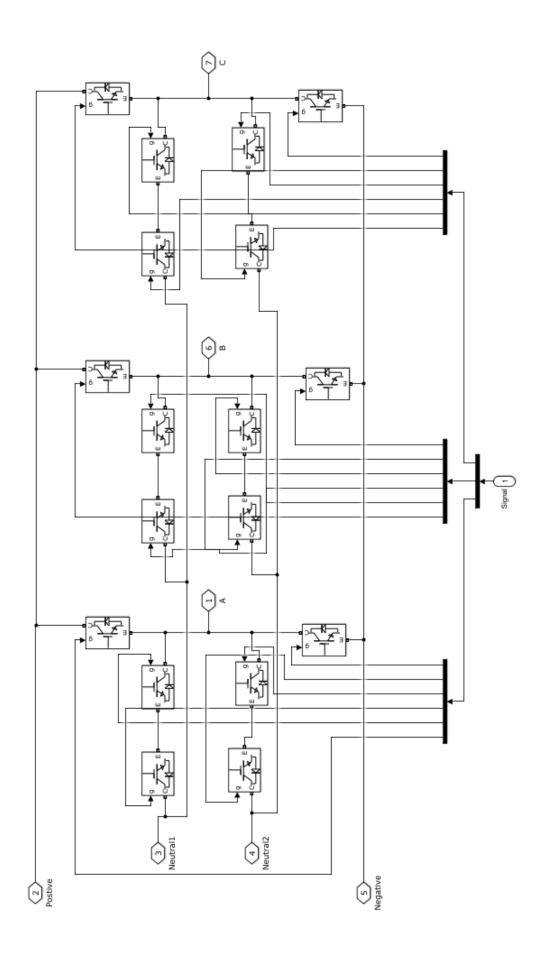

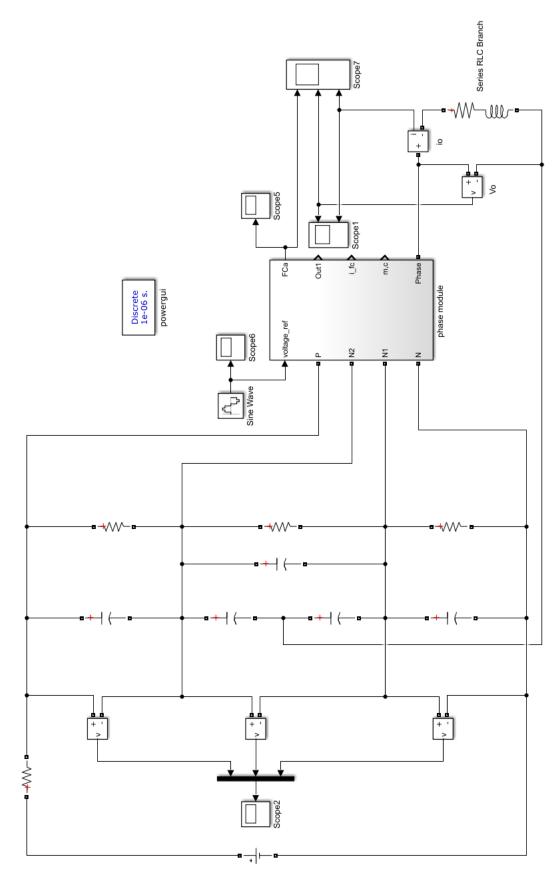

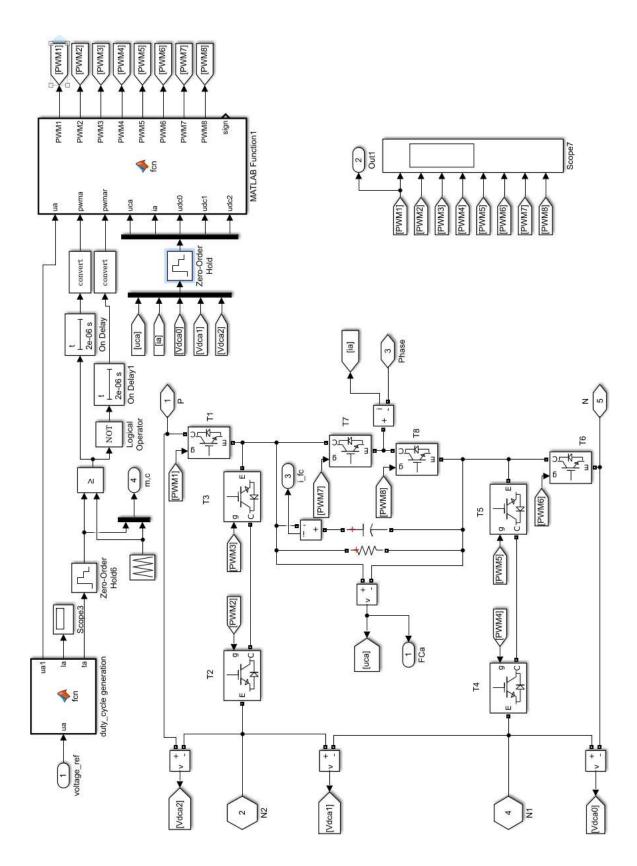

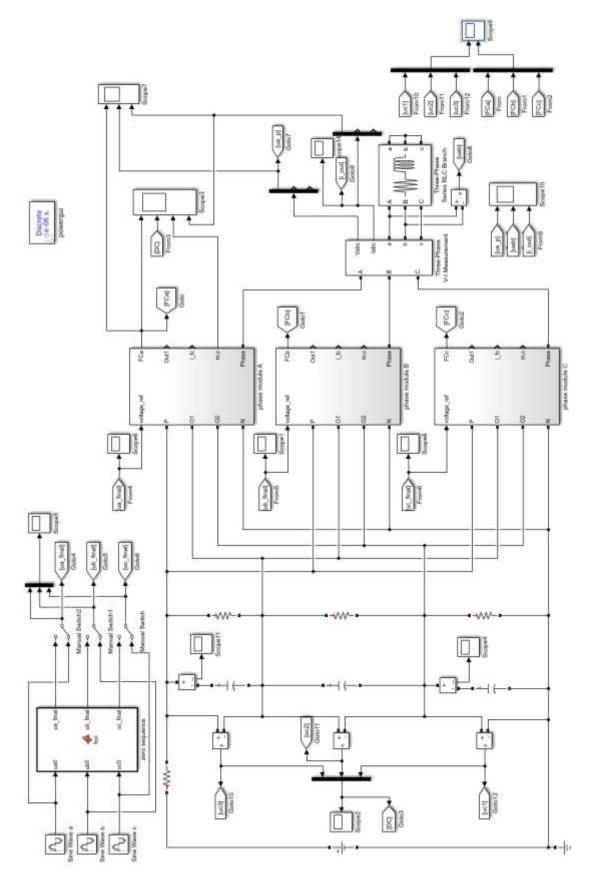

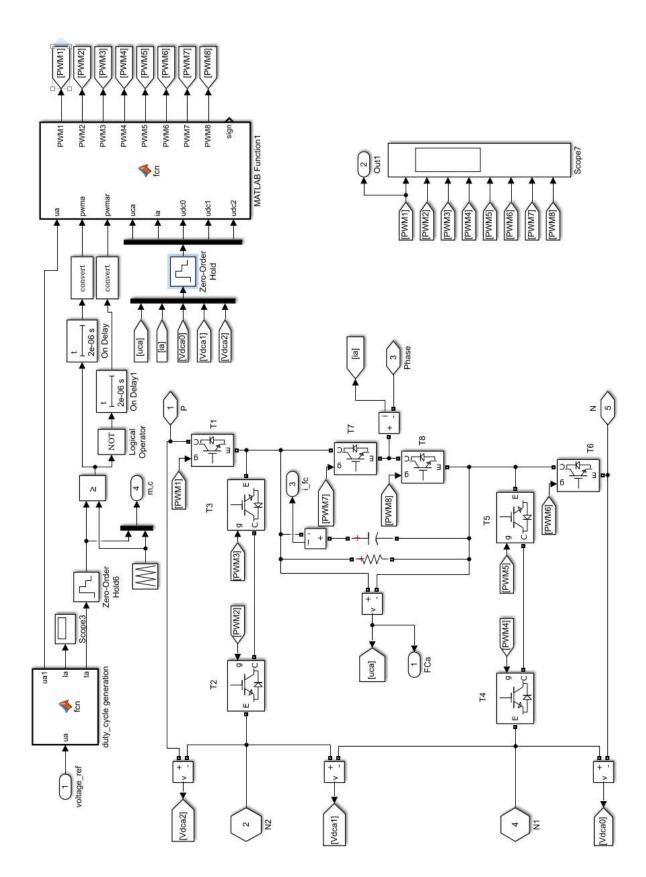

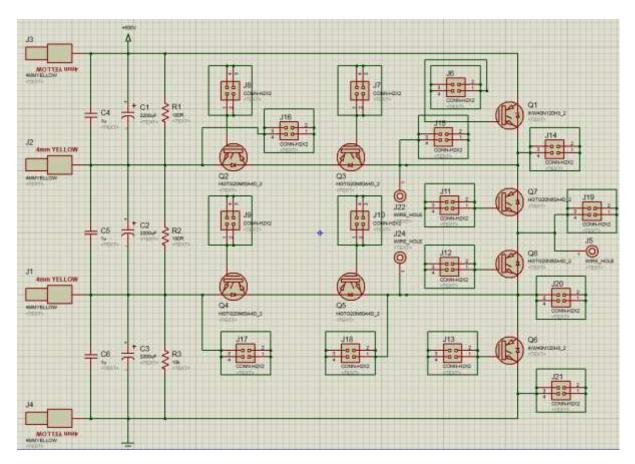

|     | Appendix B. MATLAB/Simulink Simulation layout for converter topologies operation        | ıal |

|     | verification                                                                            | 45  |

| I. Three-phase two-level converter                                                       | 245          |

|------------------------------------------------------------------------------------------|--------------|

| II. Three-phase three-level NPC converter                                                |              |

|                                                                                          |              |

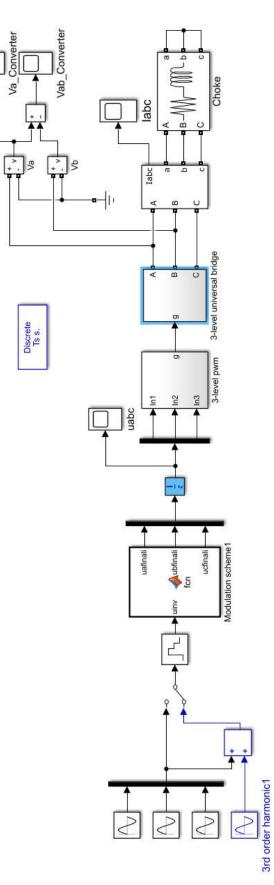

| III. Three-phase three-level T-type converter                                            |              |

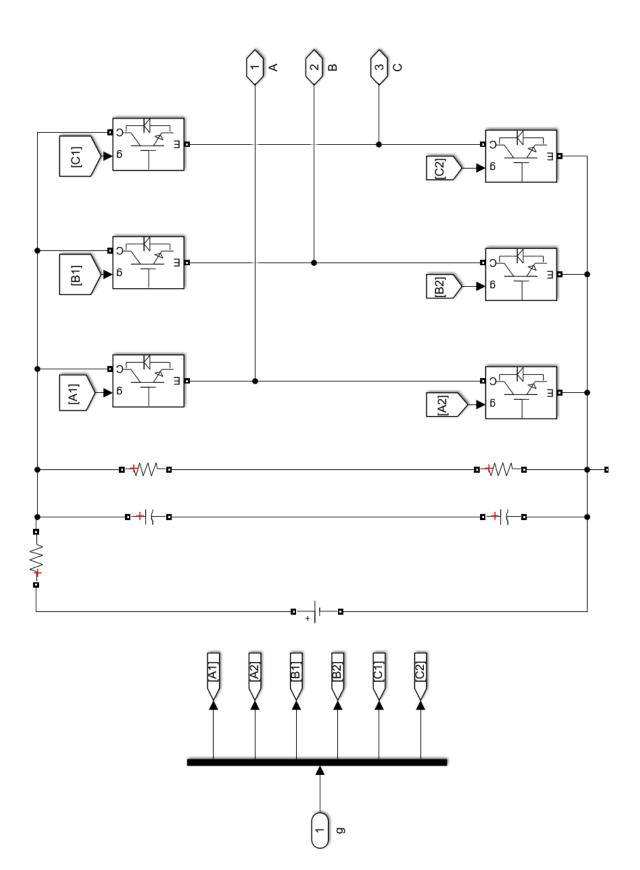

| IV. Three-phase four-level $\pi$ -type converter                                         |              |

| Appendix C. Power loss analysis calculation through MATLAB/Simulink Simulation.          |              |

| I. Power loss distribution of the four-level $\pi$ -type converter                       |              |

| II. Power loss vs power factor angle curve of the four-level $\pi$ -type converter       |              |

| III. Converter topologies efficiencies comparison                                        |              |

| IV. Simulation models of four-level $\pi$ -type converter to validate the effect on dc-l | ink parallel |

| resistors                                                                                |              |

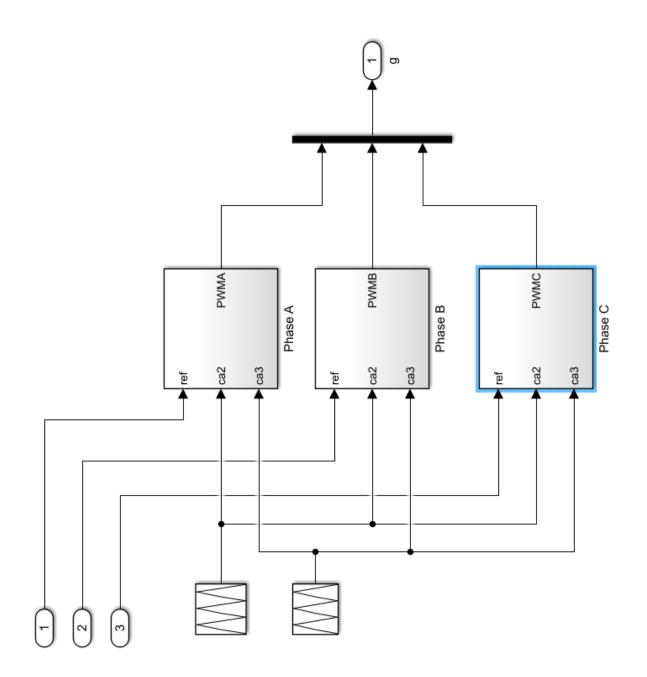

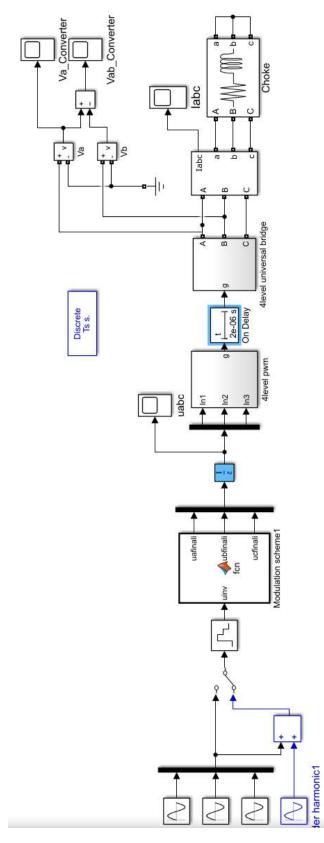

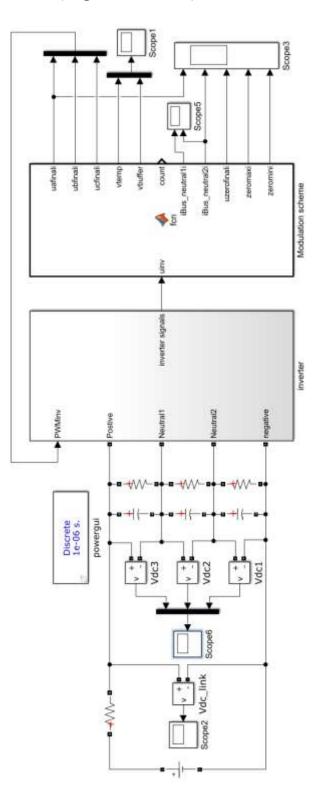

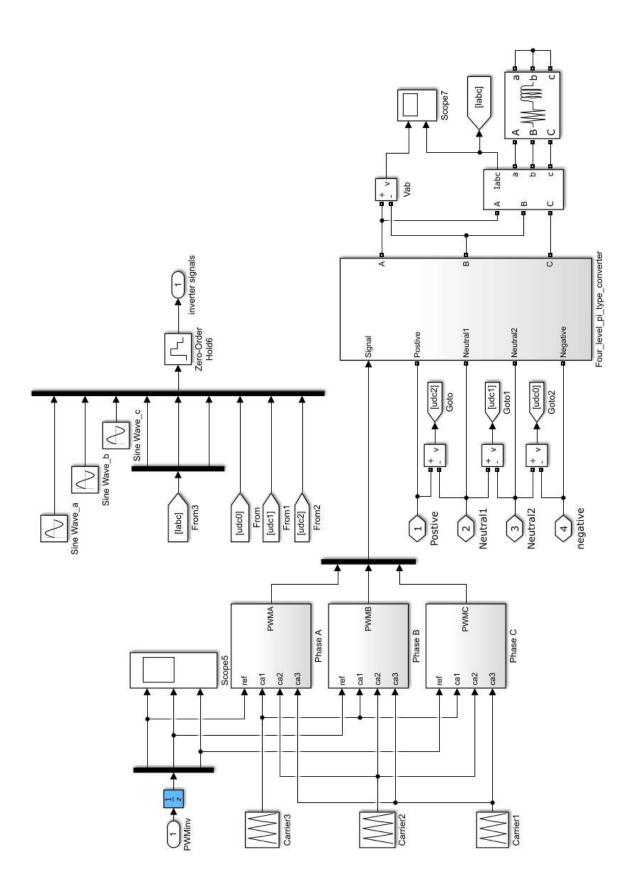

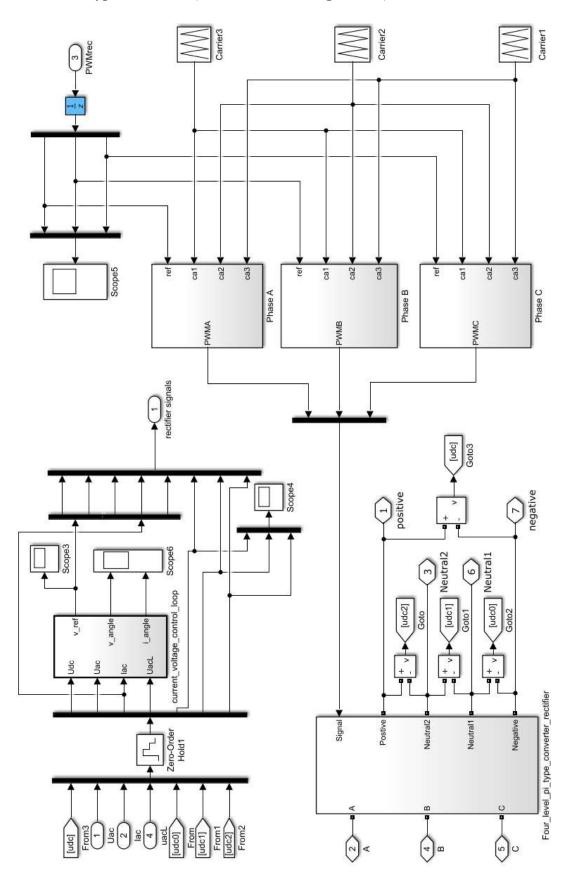

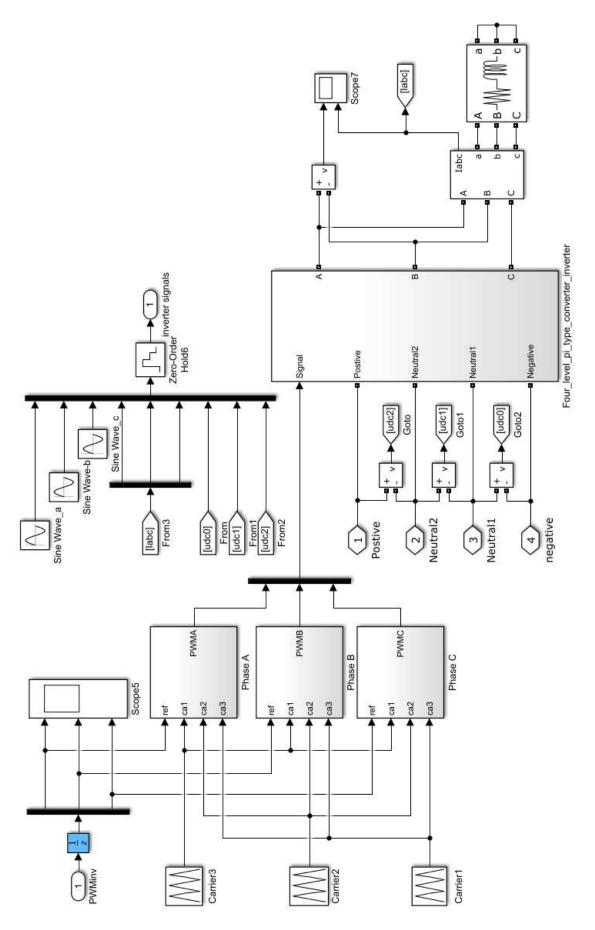

| Appendix D. MATLAB/Simulink Simulation layout for the dc-link NP voltage balance         | ing control  |

|                                                                                          |              |

| I. Four-level $\pi$ -type converter (single-end inverter)                                |              |

| II. Four-level $\pi$ -type converter (back-to-back configuration)                        | 301          |

| III. Hybrid-clamped four-level $\pi$ -type converter (single-phase)                      |              |

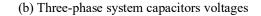

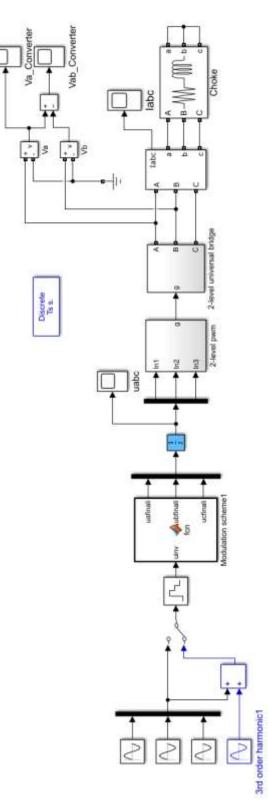

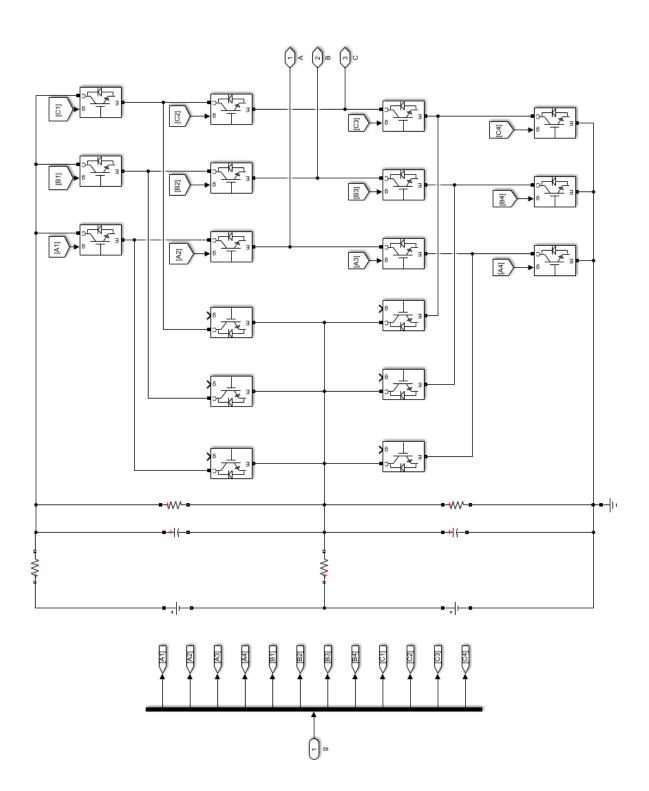

| IV. Hybrid-clamped four-level $\pi$ -type converter (three-phase)                        | 310          |

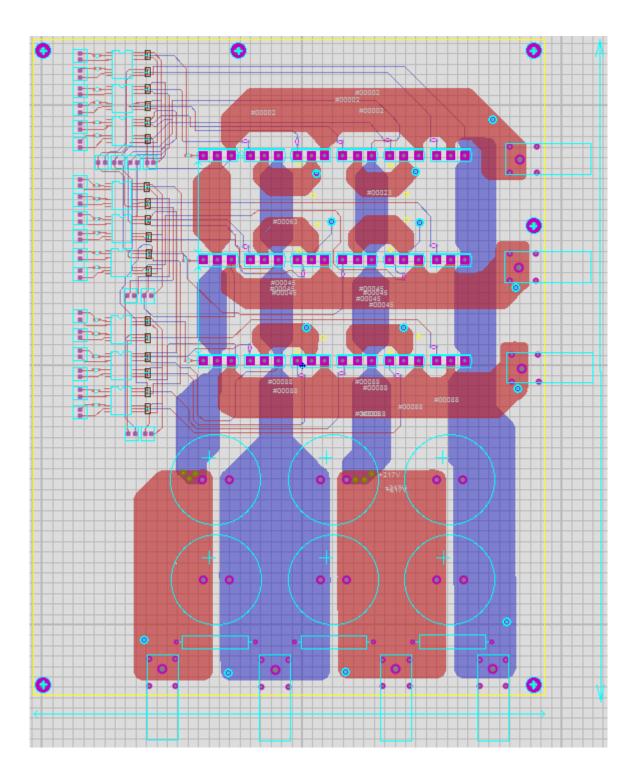

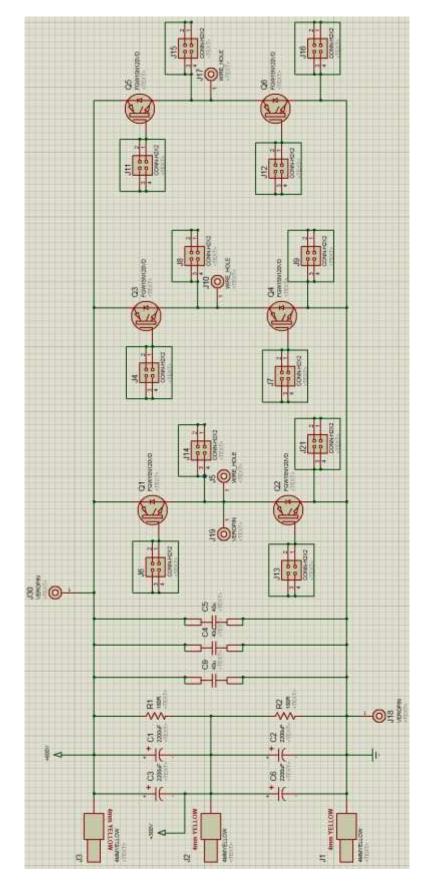

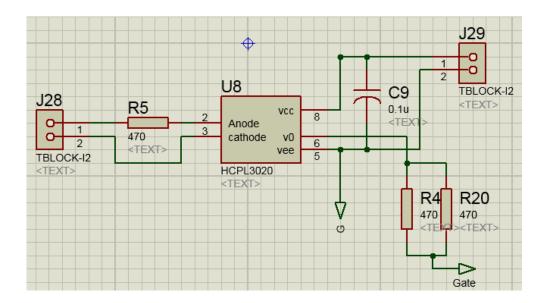

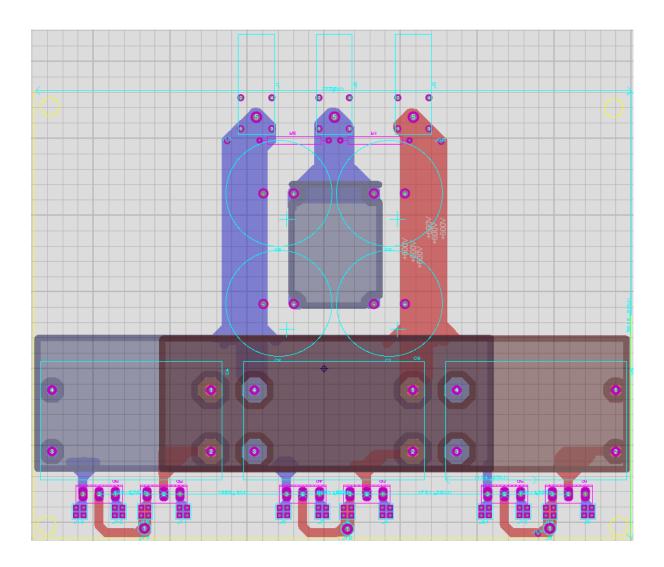

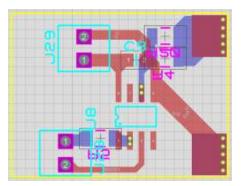

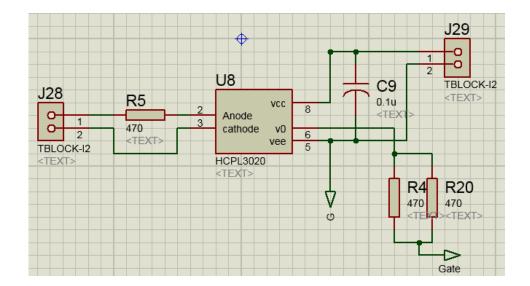

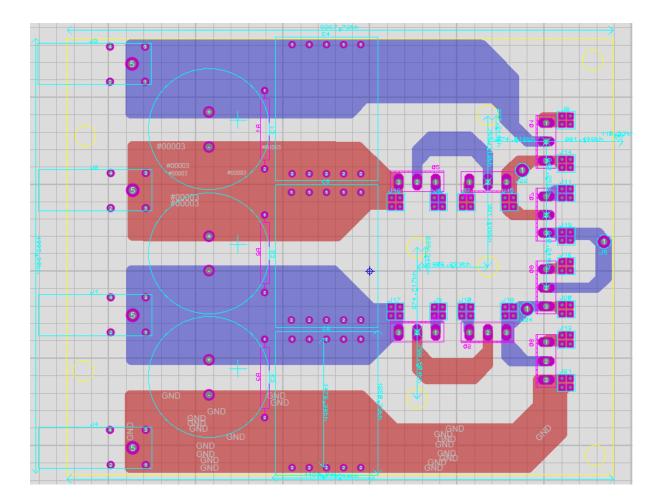

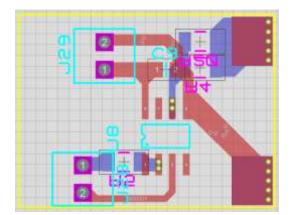

| Appendix E. Prototype schematic and PCB layouts                                          |              |

| I. Four-level $\pi$ -type converter                                                      | 321          |

| II. Two-level converter                                                                  | 323          |

| III. Hybrid clamped four-level π-type converter                                          |              |

| Appendix F. DSP/FPGA control board related information                                   |              |

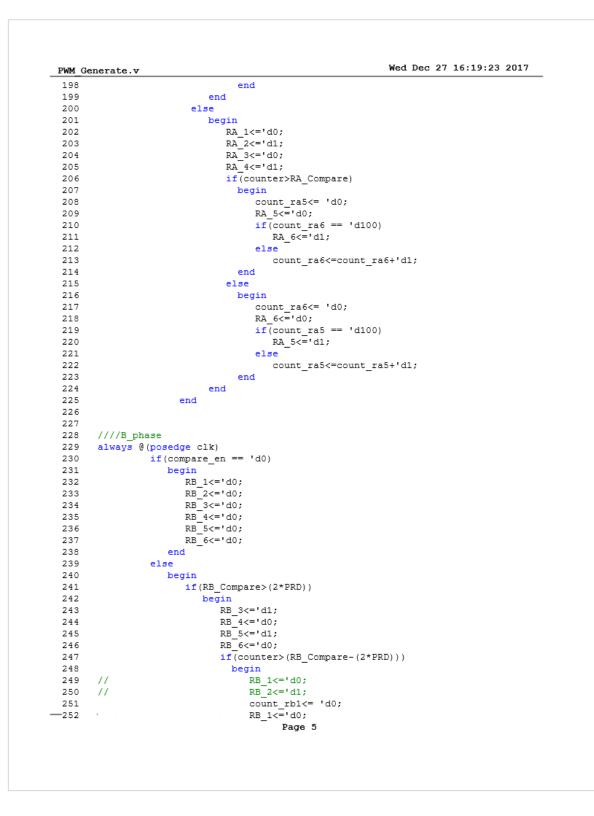

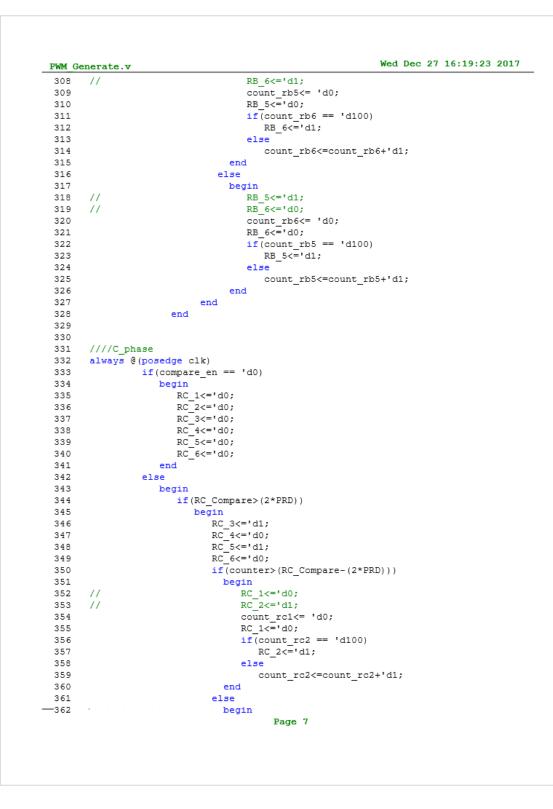

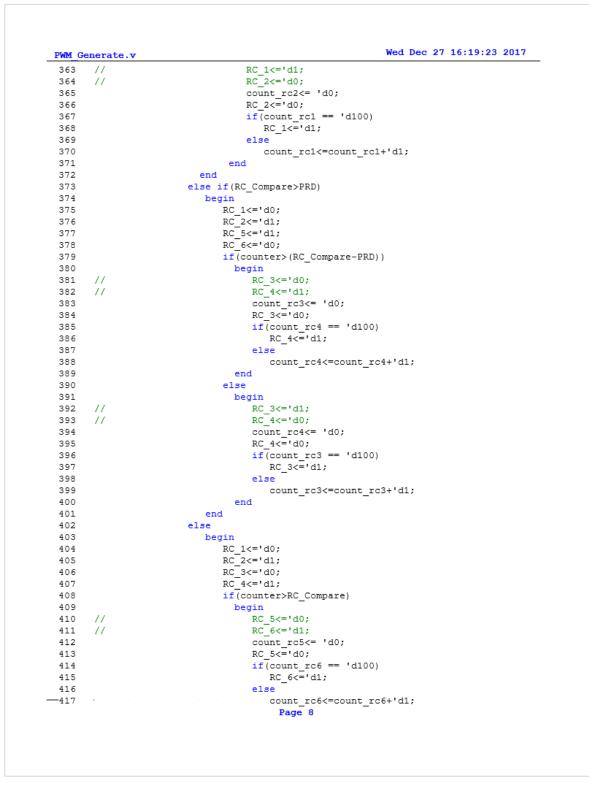

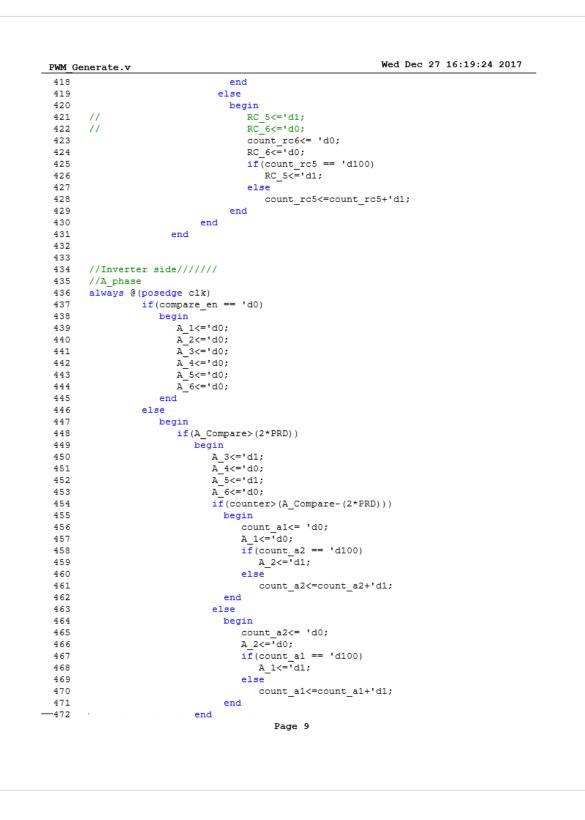

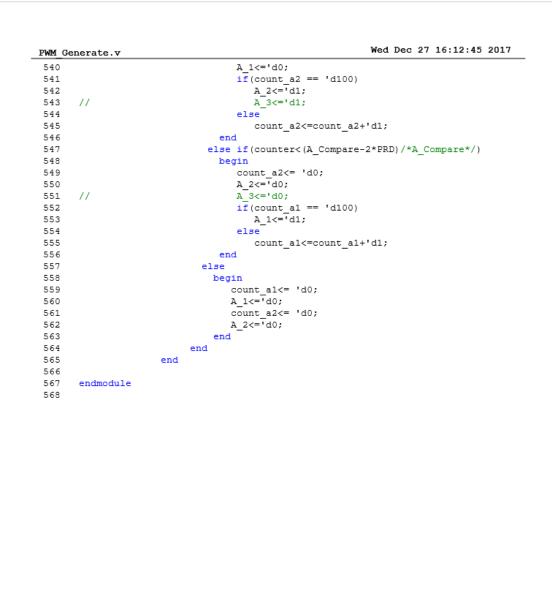

| I. Code for NP voltages balancing control code for four-level $\pi$ -type converter (ba  | ack-to-back  |

| configuration)                                                                           |              |

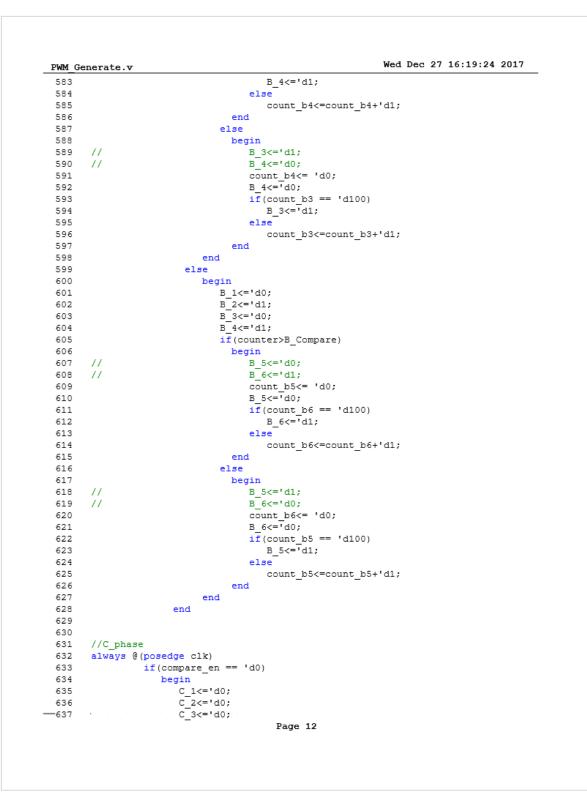

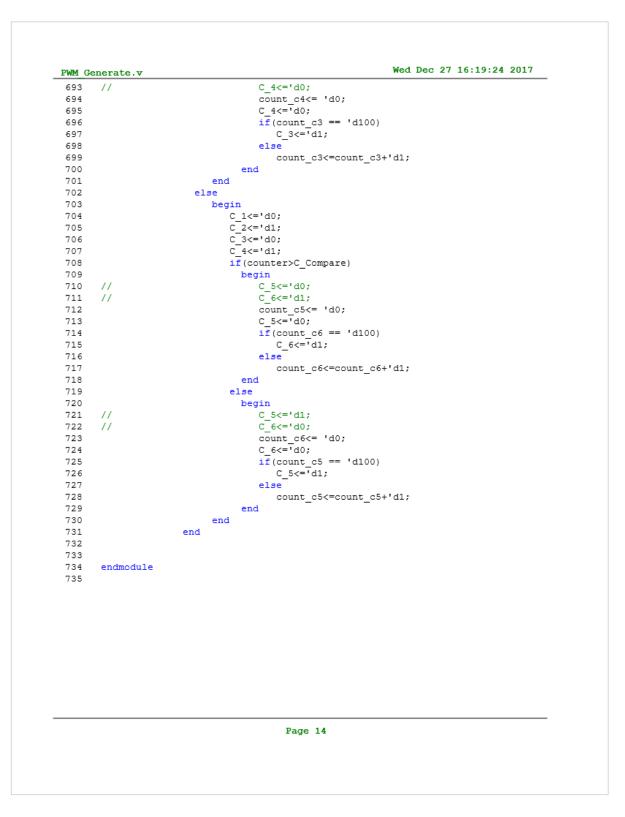

| II. Code for NP voltage and FC voltage balancing control code for hybrid clamped         | d four-level |

| $\pi$ -type converter                                                                    | 359          |

| III. Code execution principle of the DSP/FPGA control board                              |              |

| Appendix G. Hybrid four-level $\pi$ -type converter supplementary information            | 390          |

| I. Two-level jump phenomenon in the hybrid four-level $\pi$ -type converter operatio     | n 390        |

| II. ADC input filter modification and its effect on FC voltage control                   |              |

## Table of figures

| Figure 2.1 Phase-leg structure of a five-level cascaded H-bridge converter8                                 |

|-------------------------------------------------------------------------------------------------------------|

| Figure 2.2 Phase-leg structure of the asymmetrical seven-level cascaded H-bridge converters9                |

| Figure 2.3 Phase-leg structures of (a) three-level FC converter (b) four-level FC converter                 |

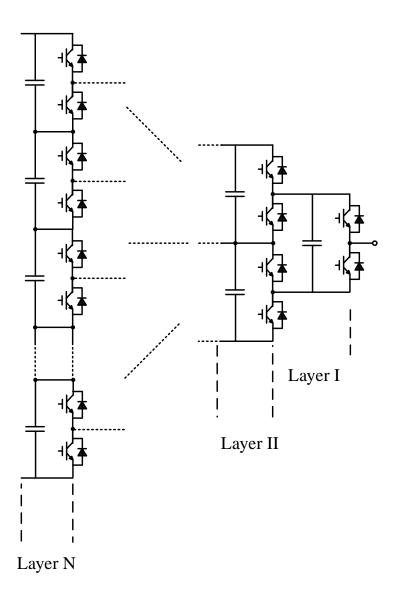

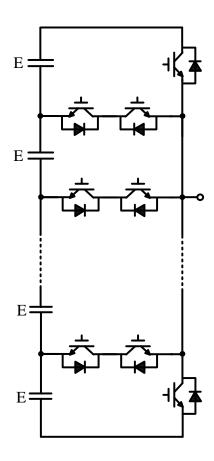

| Figure 2.4 Concept of the n-level NPC converter15                                                           |

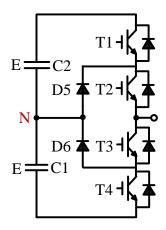

| Figure 2.5 Three-level diode NPC converter16                                                                |

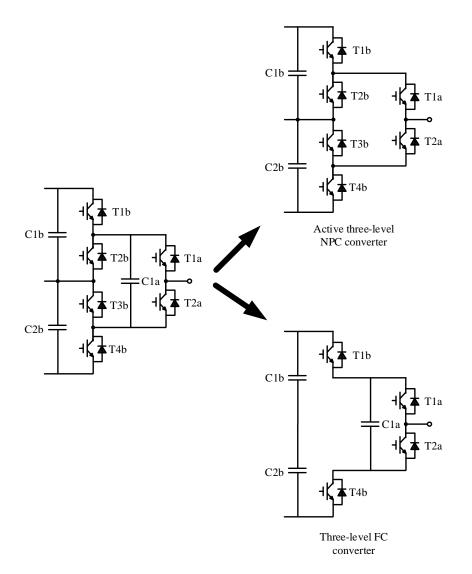

| Figure 2.6 Generalized topology I19                                                                         |

| Figure 2.7 Transfer generalized topology I to the active three-level NPC converter and the three-level FC   |

| converter20                                                                                                 |

| Figure 2.8 Generalized topology II21                                                                        |

| Figure 2.9 Phase-leg structure of the three-level diode NPC converter                                       |

| Figure 2.10 Switching states and current flow paths of the three-level diode NPC converter25                |

| Figure 2.11 Phase-leg structure of the three-level T-type converter27                                       |

| Figure 2.12 Switching states and current flow paths of the three-level T-type converter                     |

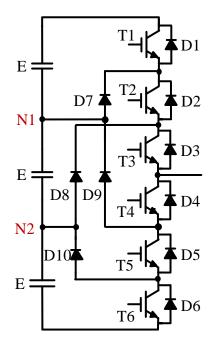

| Figure 2.13 Phase-leg structure of the four-level diode NPC converter                                       |

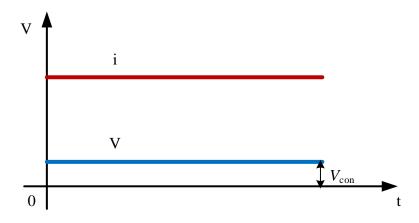

| Figure 2.14 Switching device conduction voltage                                                             |

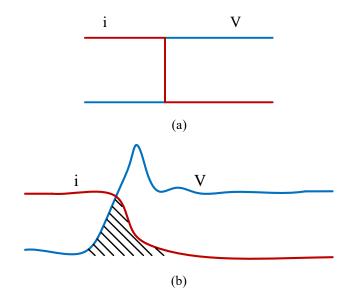

| Figure 2.15 Relationship between voltage and current of the switching device during the switching transient |

| (a) ideal switching device, (b) practical switching device                                                  |

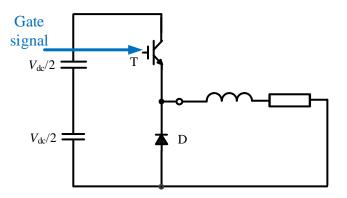

| Figure 2.16 IGBT based buck converter                                                                       |

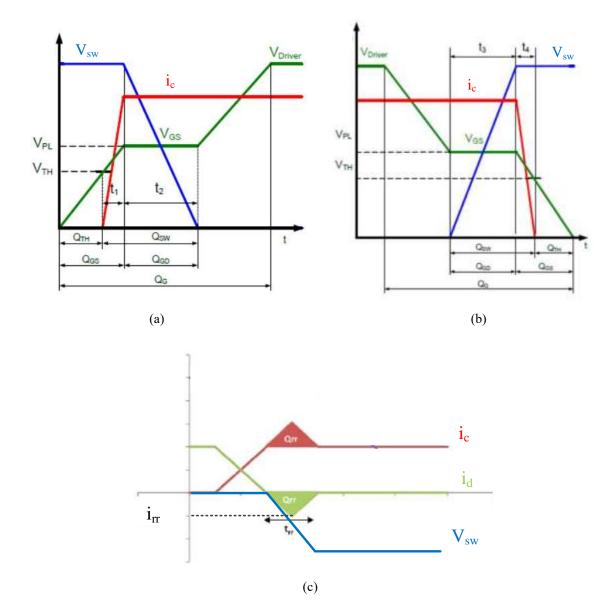

| Figure 2.17 Switching transient processes of the switching devices (a) IGBT turn-on (b) IGBT turn-off (c)   |

| freewheeling diode reverse recovery                                                                         |

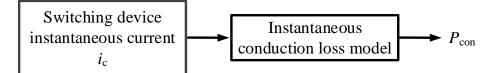

| Figure 2.18 Conduction loss numerical simulation diagram                                                    |

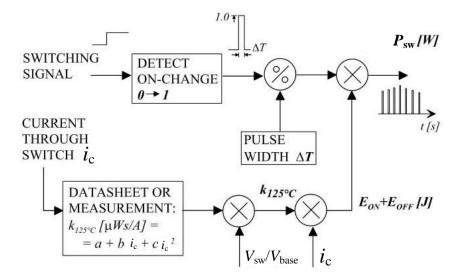

| Figure 2.19 Implementation of the switching loss to numerical simulation diagram[117]37                     |

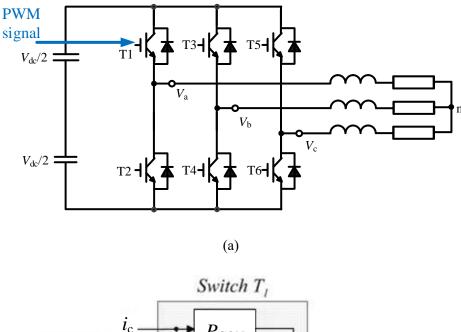

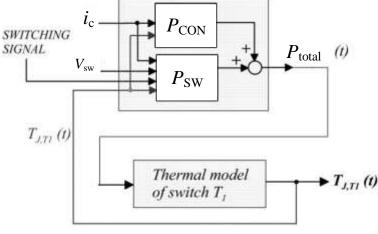

| Figure 2.20 Example of the numerical simulation (a) three-phase two-level converter system (b)              |

| Implementation of the numerical power loss simulation as well as the junction temperature simulation [124]  |

|                                                                                                             |

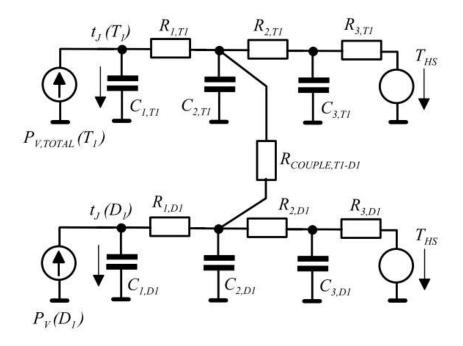

| Figure 2.21 Thermal equivalent model of the switching device T1 and D1 in Fig.2.20 [117]                    |

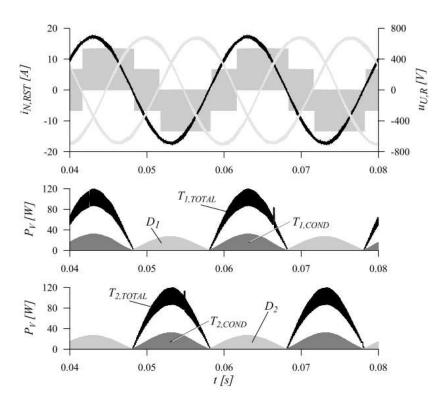

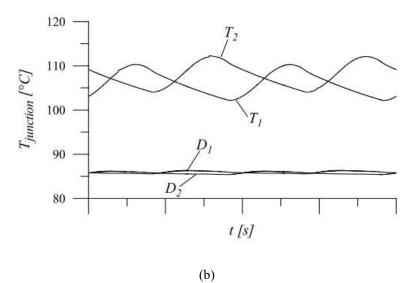

| Figure 2.22 Simulation output concept example (a) live time power loss of switching devices (b) live time     |

|---------------------------------------------------------------------------------------------------------------|

| junction temperature of switching devices [117]40                                                             |

| Figure 2.23 Neutral current flows condition for three-level NPC converter (a) power factor=1, (b) power       |

| factor=042                                                                                                    |

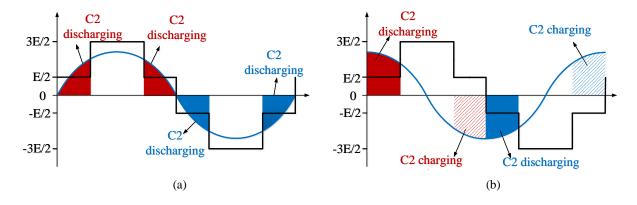

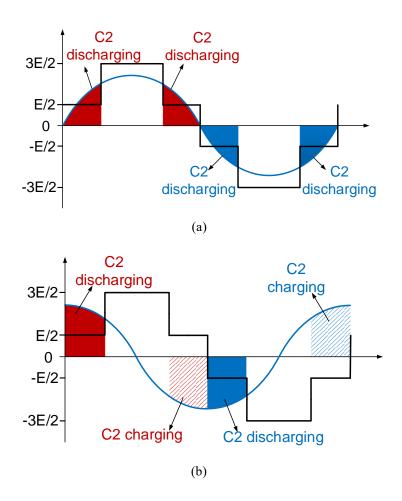

| Figure 2.24 Charge and discharge conditions of C2 for the four-level NPC converter (a) power factor=1, (b)    |

| power factor=043                                                                                              |

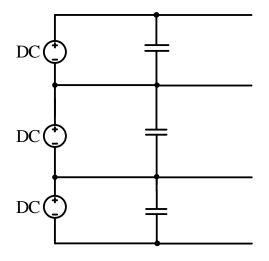

| Figure 2.25 Concept of separated dc voltage supplies for the four-level NPC converter                         |

| Figure 2.26 DC-link capacitors voltage balancing by using circuit remedy (a) four-level case (b) five-level   |

| case[65]45                                                                                                    |

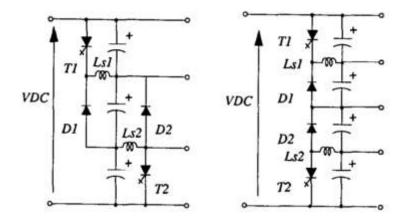

| Figure 2.27 Bidirectional buck-boost chopper for dc-link capacitors voltage balancing for the five-level NPC  |

| converter[136] [137]45                                                                                        |

| Figure 2.28 Three-phase two-level inverter layout47                                                           |

| Figure 2.29 Principle of the SVM hexagon of the two-level converter                                           |

| Figure 2.30 Switching pattern based on two active vectors and two zero vectors of two-level converter50       |

| Figure 2.31 Switching pattern based on two active vectors and one zero vectors of two-level converter51       |

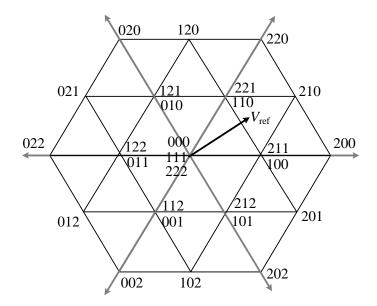

| Figure 2.32 SVM hexagon for the three-level NPC converter condition                                           |

| Figure 2.33 Concept of three-phase modulation waves with third order harmonic components as zero              |

| sequence signals injection                                                                                    |

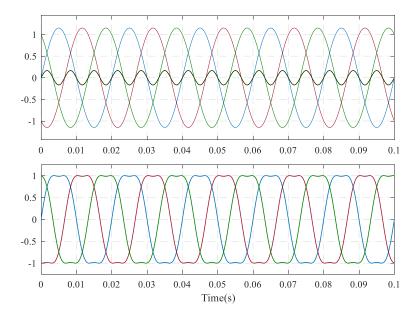

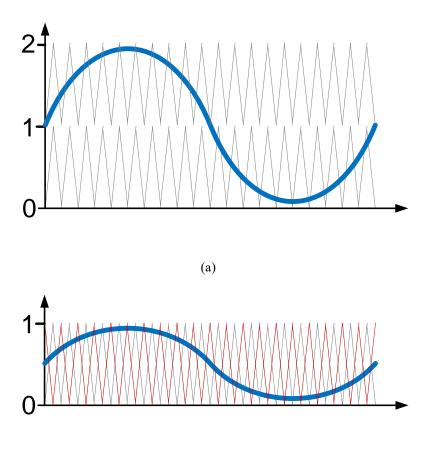

| Figure 2.34 Concepts of CB-PWM (a). level shifted (b). phase shifted55                                        |

| Figure 2.35 Different THD values of three-level T-type converter output line voltage based on (a) (b) level   |

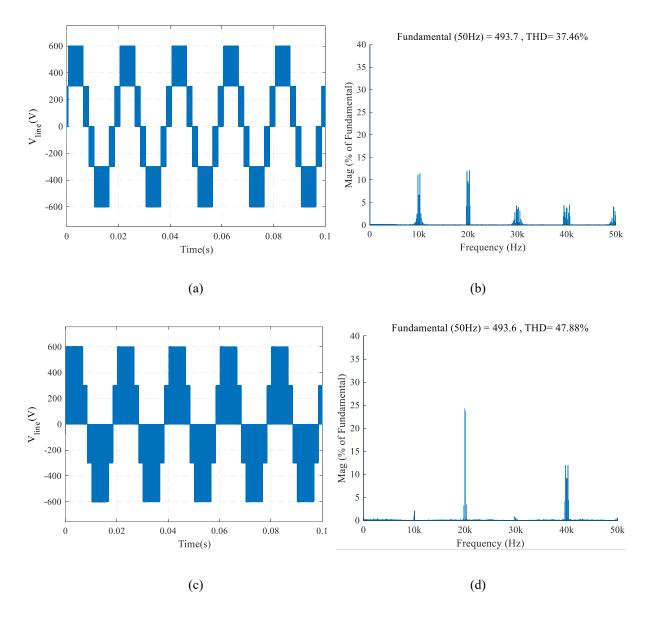

| shifted CB-PWM (c) (d) phase shifted CB-PWM56                                                                 |

| Figure 2.36 DC-link NP voltage balancing control limit for single-end NPC multilevel converters[41]57         |

| Figure 2.37 Theoretical dc-link capacitor voltage balancing control limit for the back-to-back three-level    |

| NPC converter[129]58                                                                                          |

| Figure 2.38 concept of output voltage switching sequence within one switching period for a four-level NPC     |

| converter                                                                                                     |

| Figure 2.39 Concept of CB-PWM implementation of VV PWM based control                                          |

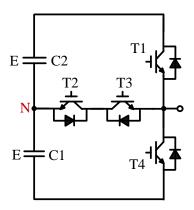

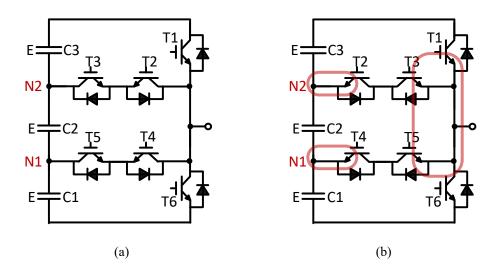

| Figure 3.1 Phase-leg structure of a four-level $\pi$ -type converter (a) common-emitter connection in neutral |

| paths (b) common-collector connection in neutral paths                                                        |

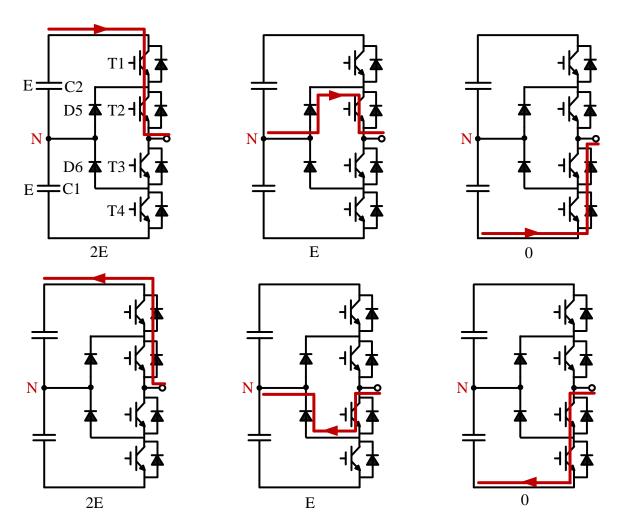

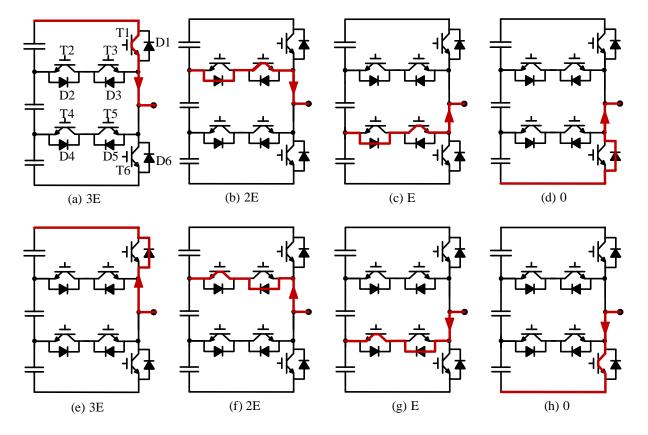

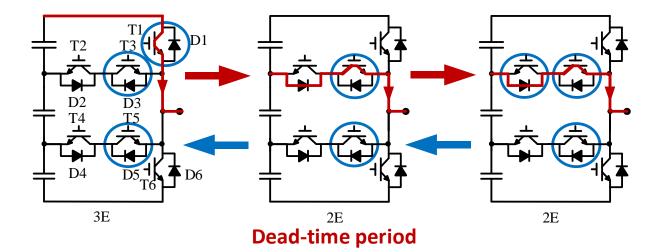

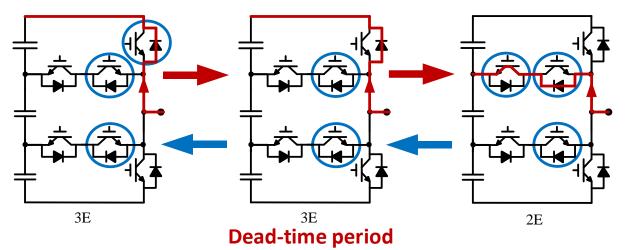

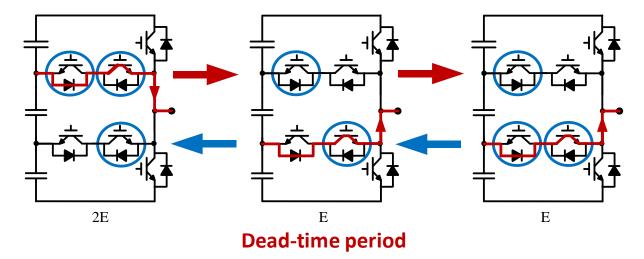

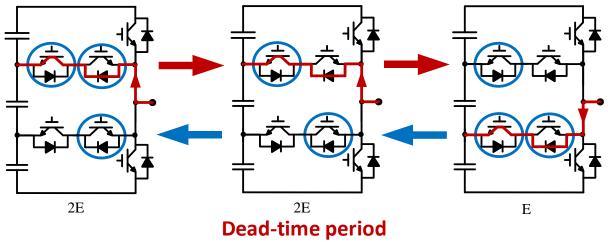

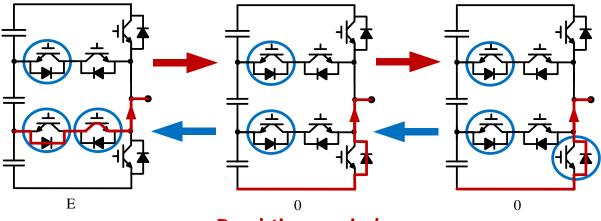

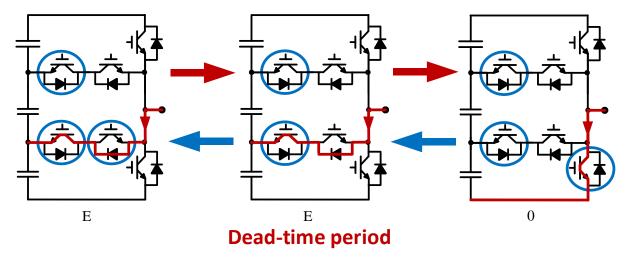

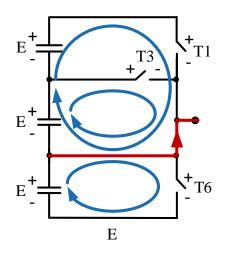

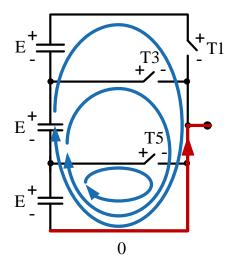

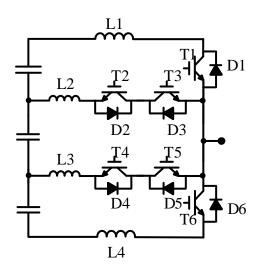

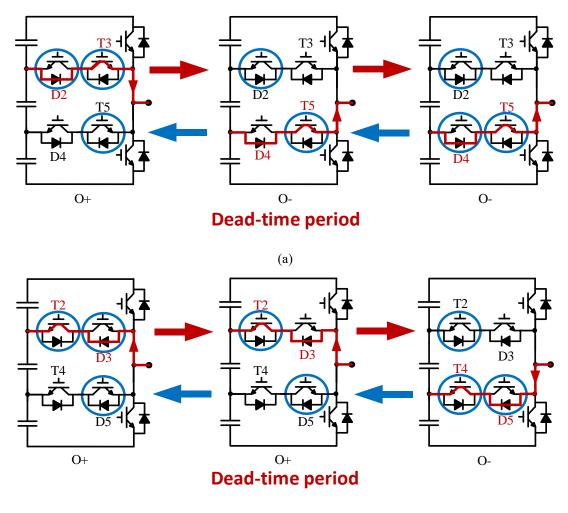

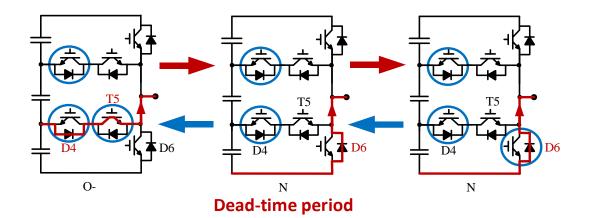

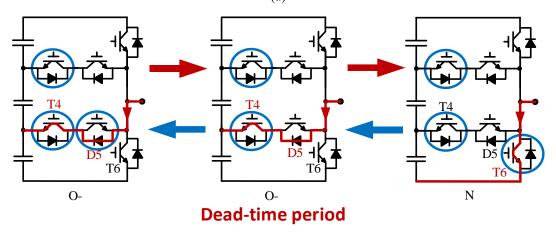

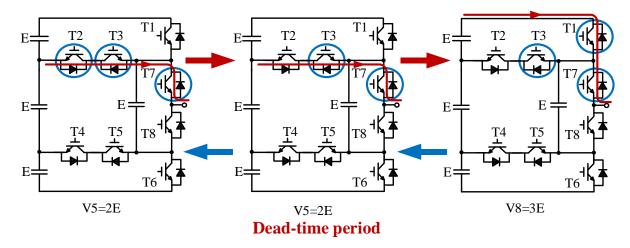

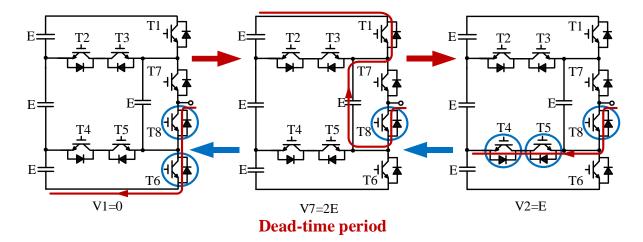

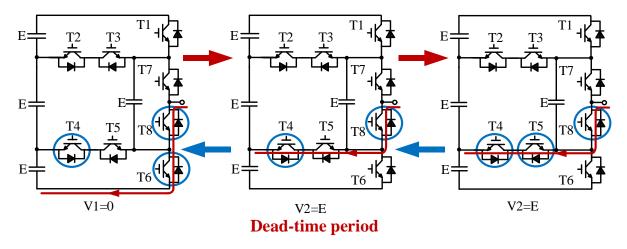

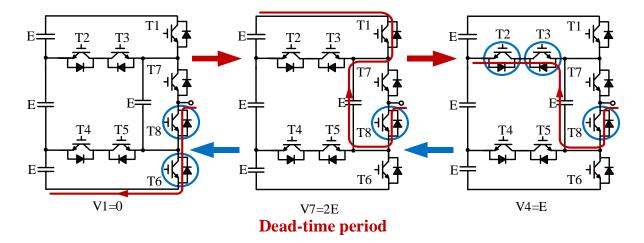

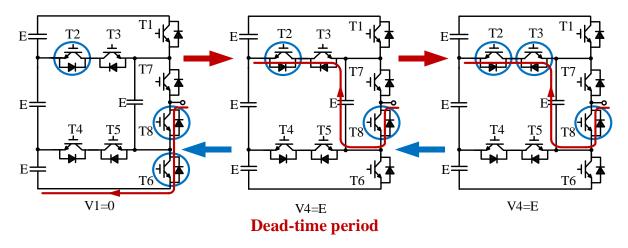

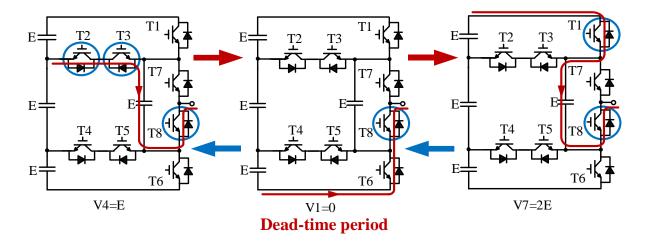

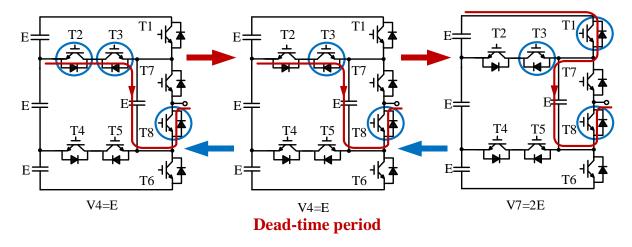

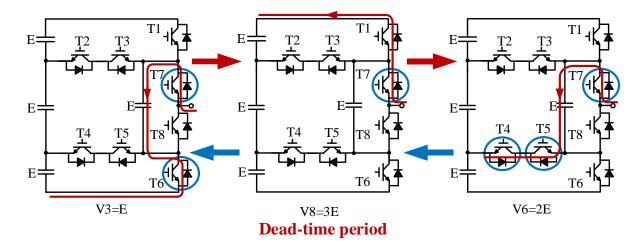

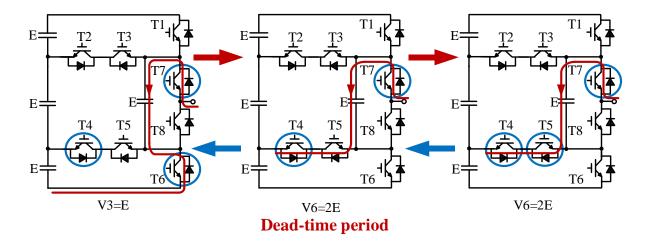

| Figure 3.2 Switching states and current flow paths                                                                      |

|-------------------------------------------------------------------------------------------------------------------------|

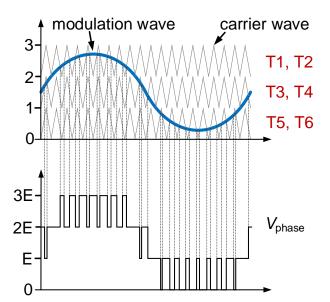

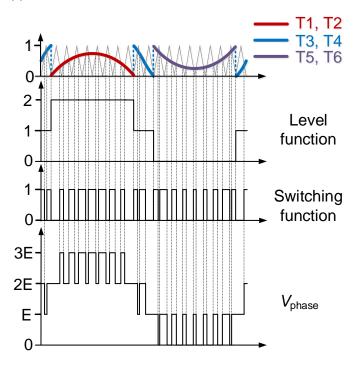

| Figure 3.3 Traditional level shifted CB-PWM scheme for the four-level $\pi$ -type converter                             |

| Figure 3.4 Commutation process of the four-level $\pi$ -type converter with consideration of the dead-time              |

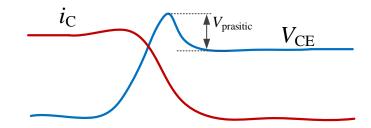

| effect                                                                                                                  |

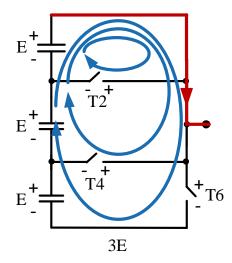

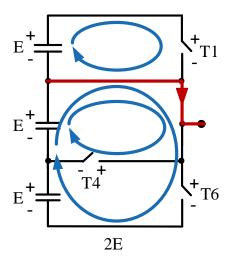

| Figure 3.5 Devices blocking voltages during 3E70                                                                        |

| Figure 3.6 Devices blocking voltages during 2E71                                                                        |

| Figure 3.7 Devices blocking voltages during E71                                                                         |

| Figure 3.8 Devices blocking voltages during 072                                                                         |

| Figure 3.9 Simplified phase-leg structure of the four-level $\pi$ -type converter with parasitic inductance73           |

| Figure 3.10 Turn-off process of the collector current and the collector-emitter voltage74                               |

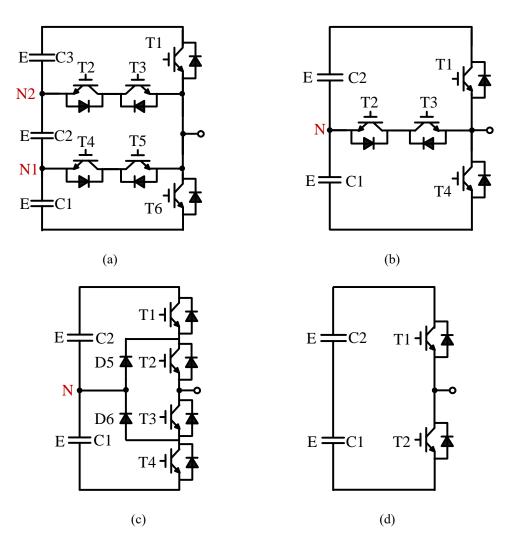

| Figure 3.11 Phase-leg structures: (a) four-level $\pi$ -type converter, (b) three-level T-type converter, (c) three-    |

| level diode NPC converter, (d) two-level converter76                                                                    |

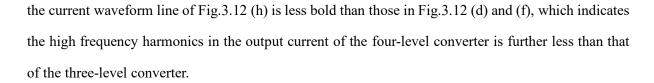

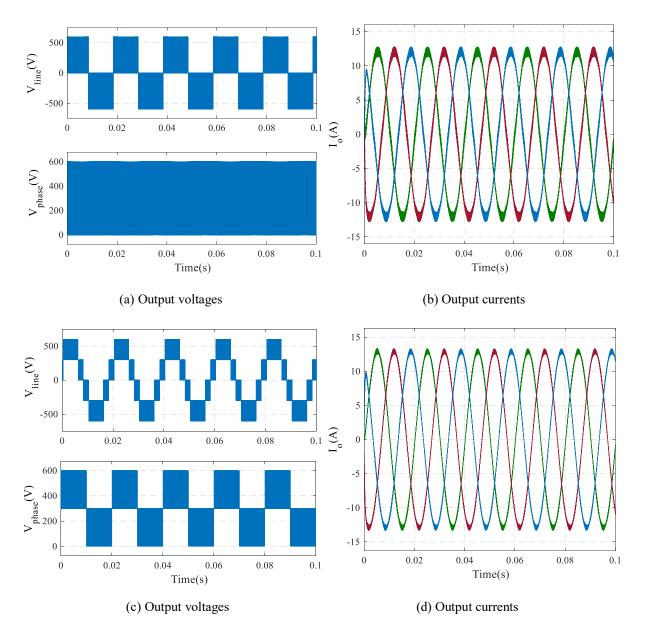

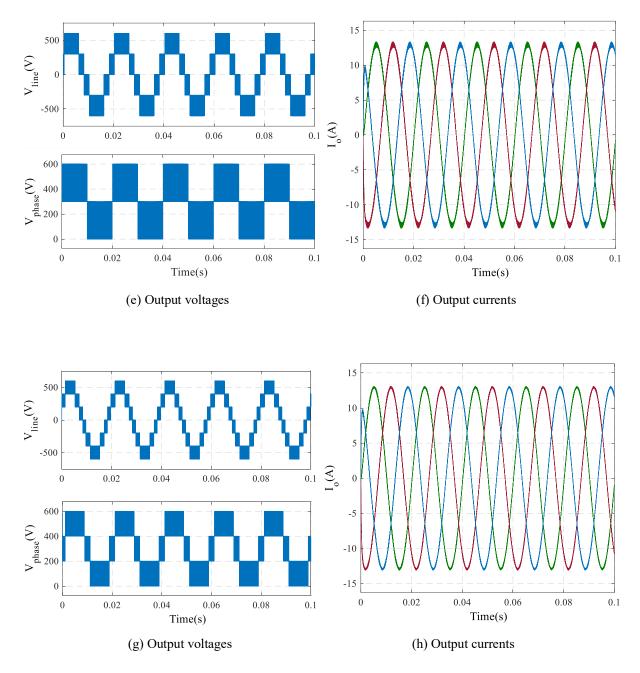

| Figure 3.12 Simulation waveforms of (a) (b): two-level converter, (c) (d): three-level NPC converter, (e) (f):          |

| three-level T-type converter, (g) (h): four-level π-type converter84                                                    |

| Figure 3.13 FFT analysis of simulation waveforms of (a) (b): two-level converter, (c) (d): three-level NPC              |

| converter, (e) (f): three-level T-type converter, (g) (h): four-level $\pi$ -type converter                             |

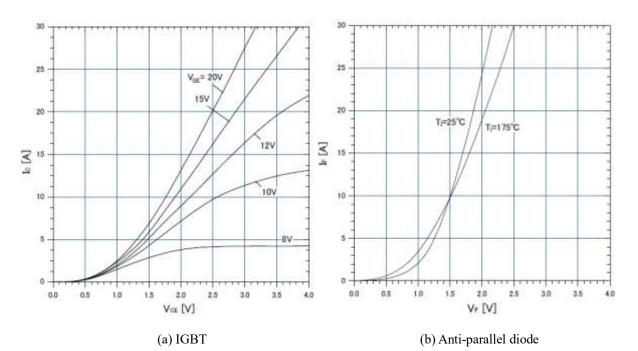

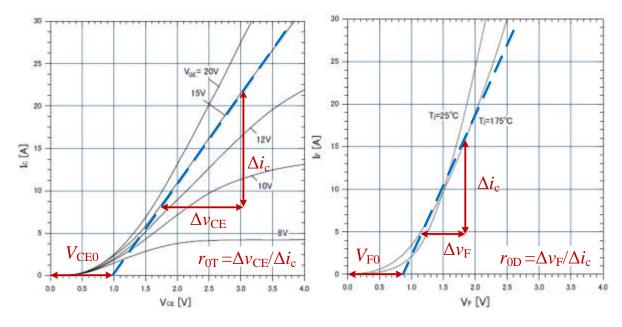

| Figure 4.1 Curves of conducting collector/diode currents vs turn-on voltages of FGW15N120VD93                           |

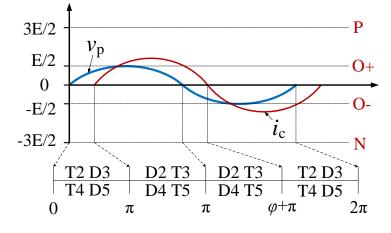

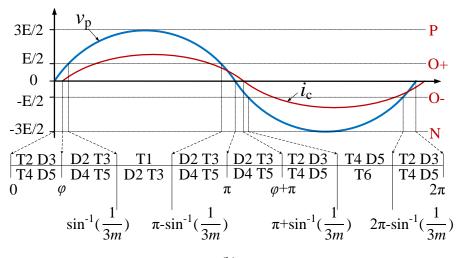

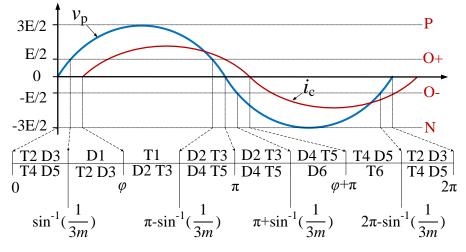

| Figure 4.2 Conduction intervals for switching devices(a) $m \le 13$ . (b) $m > 13$ , $0 < \varphi \le \sin(113m)$ . (c) |

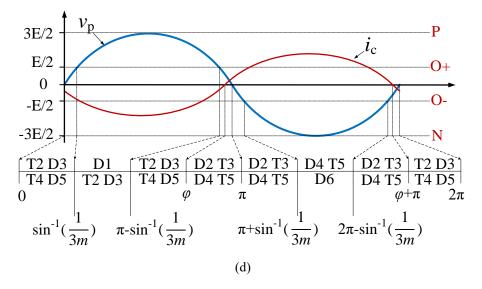

| $m > 13$ , sin-1(13m) < $\varphi < \pi$ -sin-1(13m). (d) $m > 13$ , $\pi$ -sin-1(13m) $\leq \varphi < \pi$              |

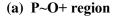

| Figure 4.3 The switching state when the modulation wave between P and O+ (P ~ O+ commutation)99                         |

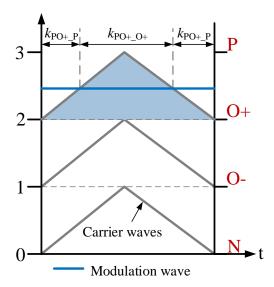

| Figure 4.4 The switching state when the modulation wave between O+ and O- (O+ ~ O- commutation) 100                     |

| Figure 4.5 The switching state when the modulation wave between O- and N (O- $\sim$ N commutation)101                   |

| Figure 4.6 FGW15N120VD switching energy vs collector current and MATLAB curve fitting103                                |

| Figure 4.7 Switching transition between P and O+ (a) i > 0, (b) i < 0106                                                |

| Figure 4.8 Switching transition between O+ and O- (a) i > 0, (b) i < 0                                                  |

| Figure 4.9 Switching transition between O- and N (a) i > 0, (b) i < 0                                                   |

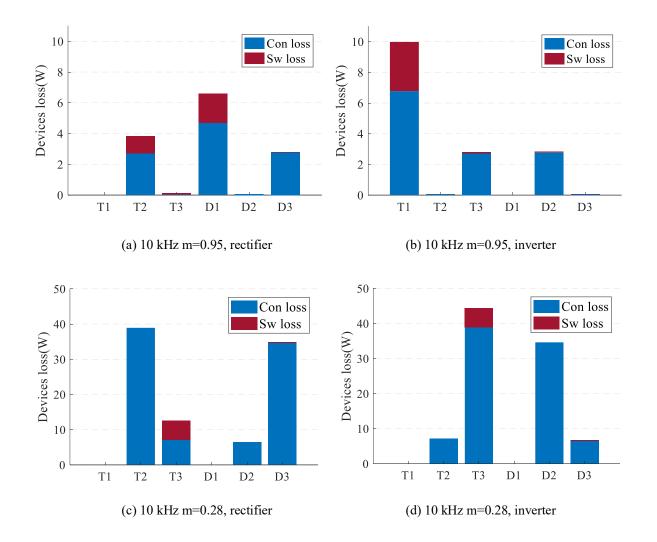

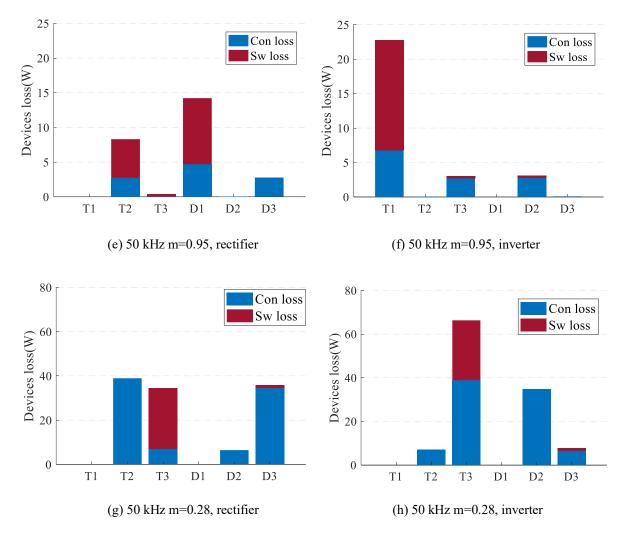

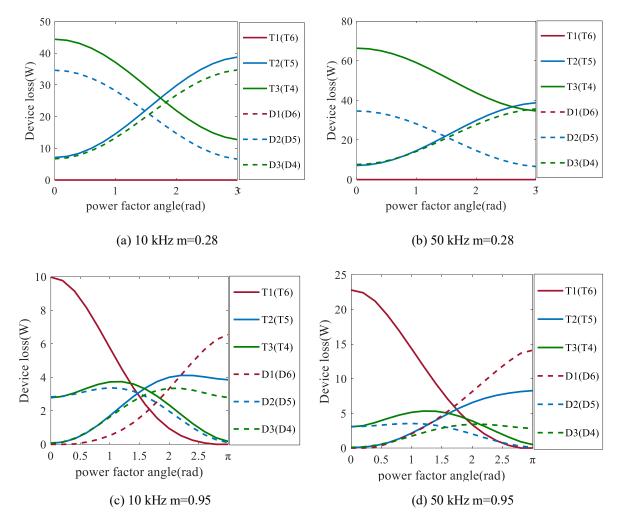

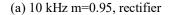

| Figure 4.10 Calculation average power losses of the four-level $\pi$ -type converter                                    |

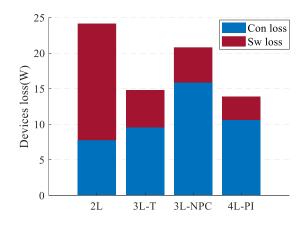

| Figure 4.11 Variation of devices losses with different power factor angles                                              |

| Figure 4.12 Power losses comparison among different converter topologies                                                |

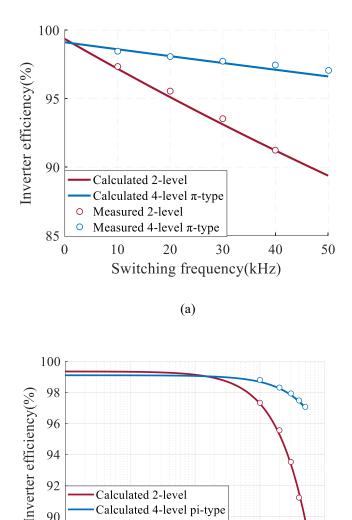

| Figure 4.13 Calculated efficiencies vs switching frequencies curves of different converter topologies122              |

|-----------------------------------------------------------------------------------------------------------------------|

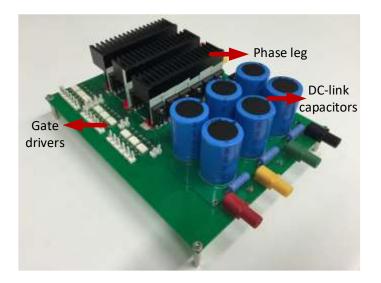

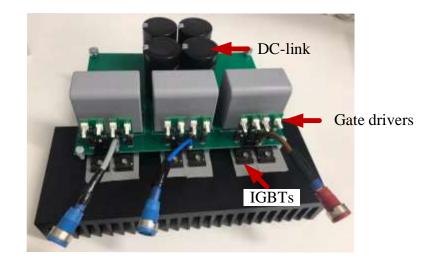

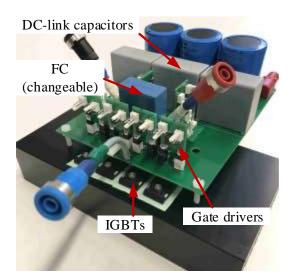

| Figure 4.14 Three-phase four-level π-type converter prototype                                                         |

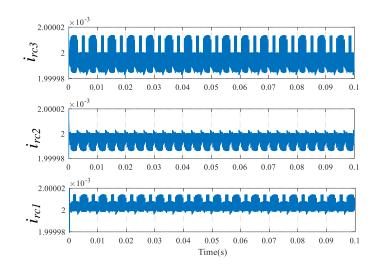

| Figure 4.15 Simulation results of currents flow through dc-link parallel resistors                                    |

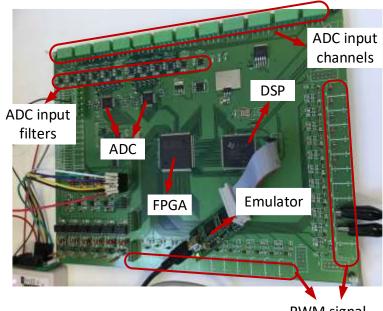

| Figure 4.16 DSP/FPGA board125                                                                                         |

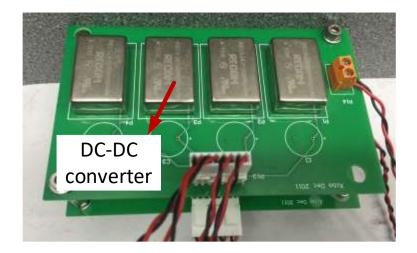

| Figure 4.17 Gate driver supply board126                                                                               |

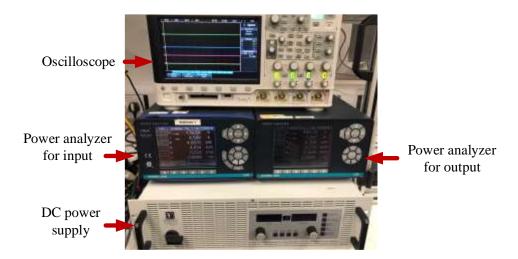

| Figure 4.18 Power efficiency measurement test equipment127                                                            |

| Figure 4.19 Three-phase two-level converter prototype128                                                              |

| Figure 4.20 Gate driver board for the two-level converter                                                             |

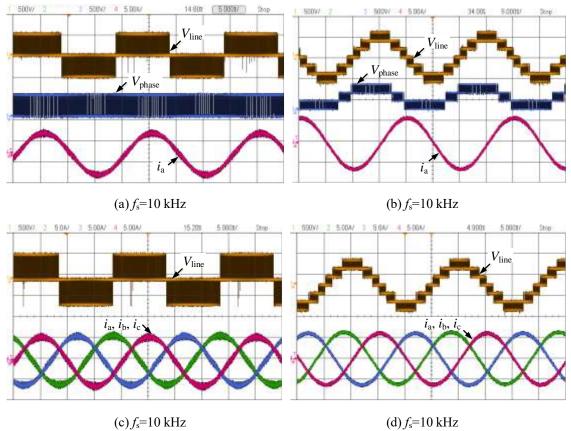

| Figure 4.21 Test waveforms of the two-level inverter (a) (c) (e) (g) (i), and the four-level $\pi$ -type inverter (b) |

| (d) (f) (h) (j)                                                                                                       |

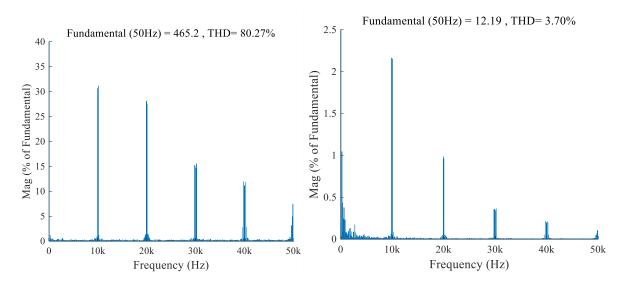

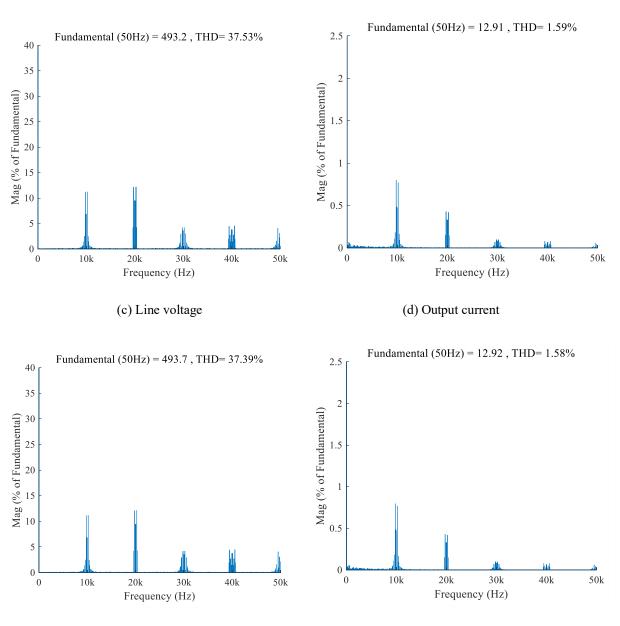

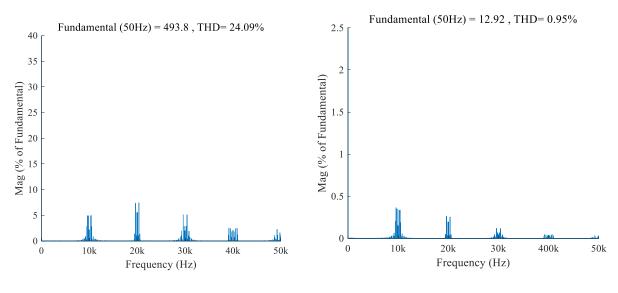

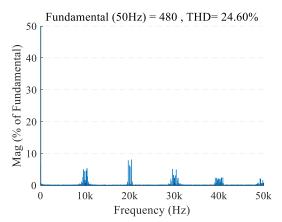

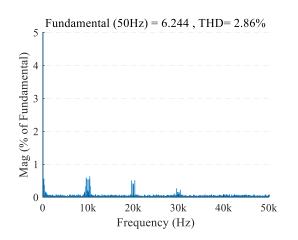

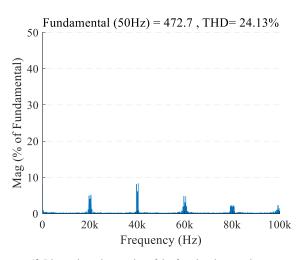

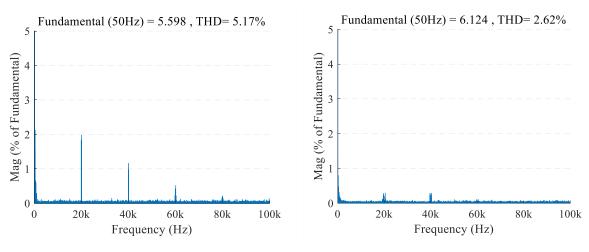

| Figure 4.22 Harmonic analysis of test waveforms, fs=10 kHz: (a) (b) (c) (d), fs=20 kHz: (e) (f) (g) (h) 133           |

| Figure 4.23 Experimental results of efficiency measurements for four-level $\pi$ -type converter and two-level        |

| converter (a) linear frequency axis (b) logarithm frequency axis134                                                   |

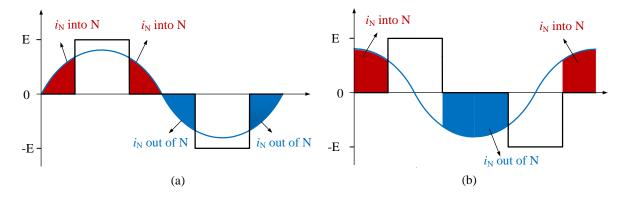

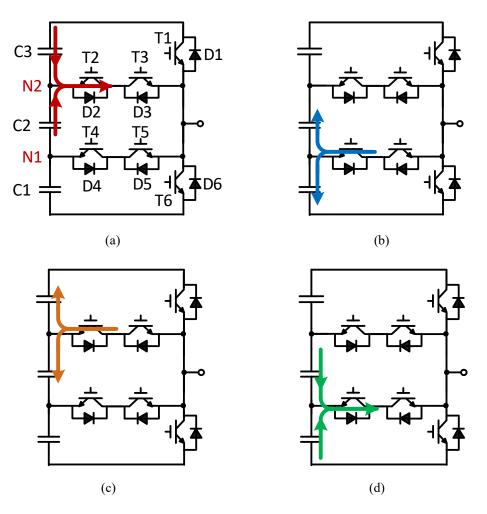

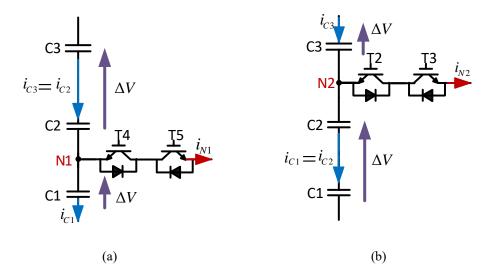

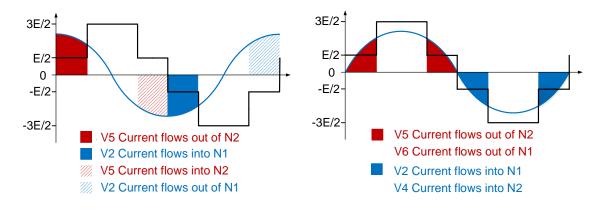

| Figure 5.1 Situations of current flow paths with regards to N2 and N1. (a) current flows through N2 out of            |

| the converter (b) current flows through N1 into the converter (c) current flows through N2 into the                   |

| converter (d) current flows through N1 out of the converter140                                                        |

| Figure 5.2 Charge and discharge conditions of C2 (a) unity power factor, (b) zero power factor                        |

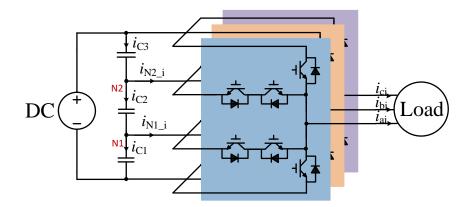

| Figure 5.3 Neutral path currents and three-phase output currents of the three-phase four-level $\pi$ -type            |

| inverter142                                                                                                           |

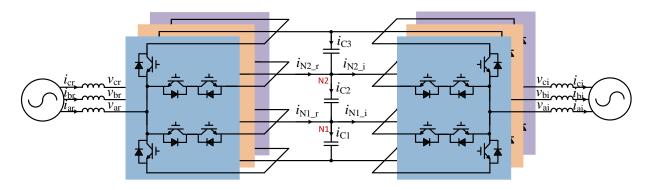

| Figure 5.4 Back-to-back four-level $\pi$ -type converter structure with a bidirectional power-flow structure          |

|                                                                                                                       |

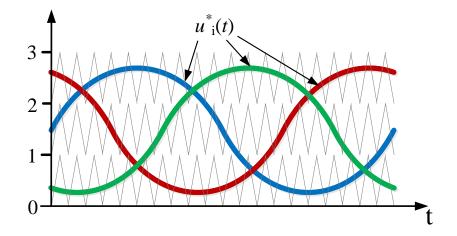

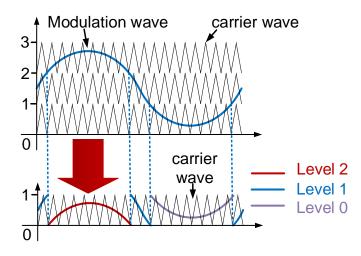

| Figure 5.5 The relationship between carrier waves and modulation waves in a level shifted CB-PWM146                   |

| Figure 5.6 Modulation waves maximum approachable region147                                                            |

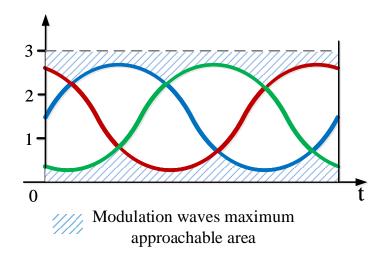

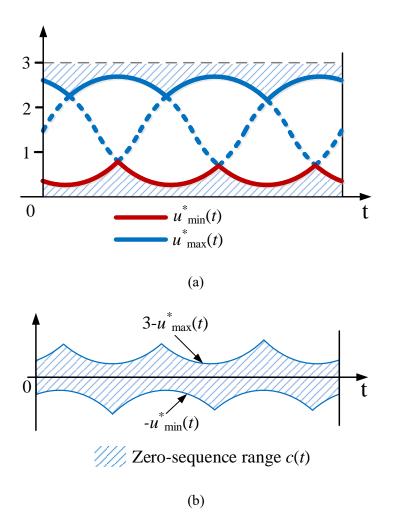

| Figure 5.7 Visual concept of (a) u*max and u*min (b) available zero-sequence component148                             |

| Figure 5.8 Discretization implementation concept of the zero-sequence components sampling method from                 |

| the available zero-sequence components range149                                                                       |

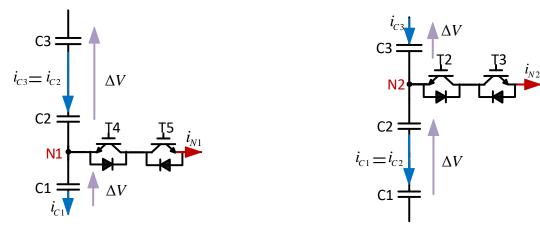

| Figure 5.9 Relationship between dc-link capacitor current and neutral path currents (a) current flows                 |

| through N1 (b) current flows through N2152                                                                            |

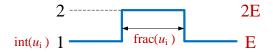

| Figure 5.10 Concept of the modulation wave level and corresponding duty cycle                                         |

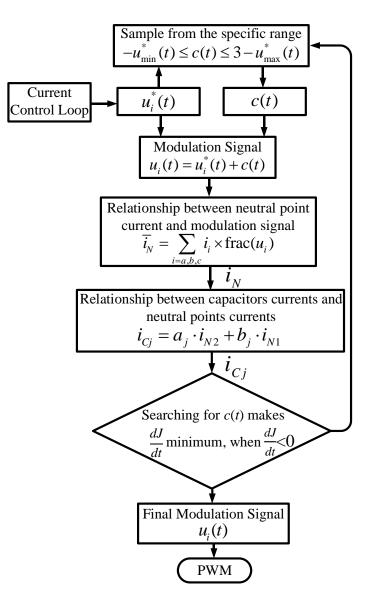

| Figure 5.11 DC-link NP voltages balancing control algorithm flow chart154                                     |

|---------------------------------------------------------------------------------------------------------------|

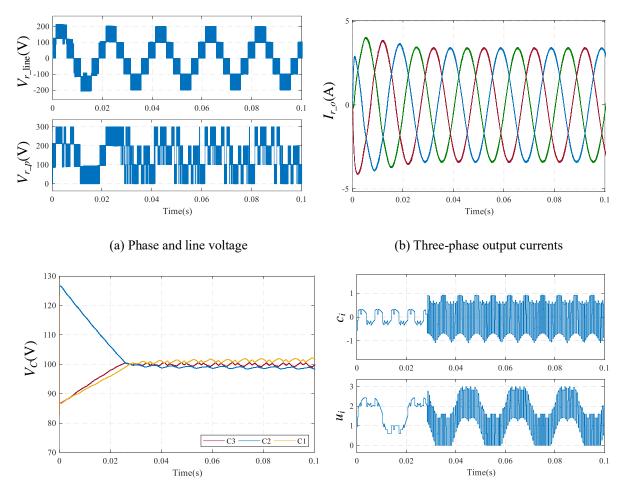

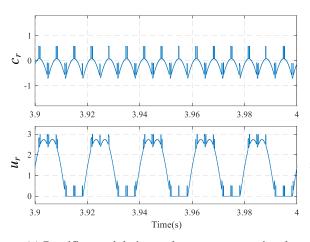

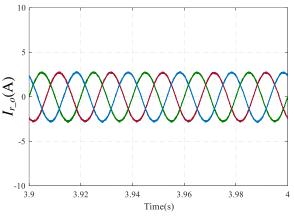

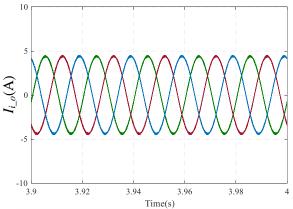

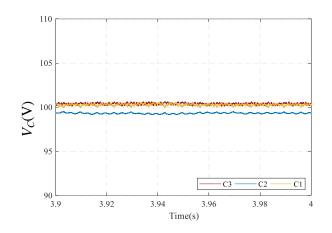

| Figure 5.12 Simulation results of three-phase single-end four-level $\pi$ -type inverter, mi=0.55             |

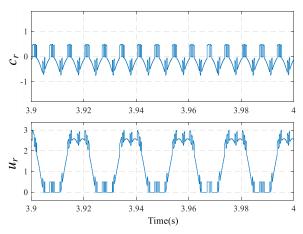

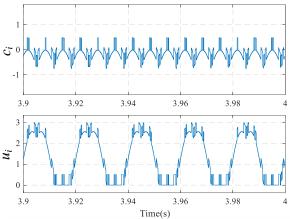

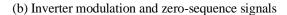

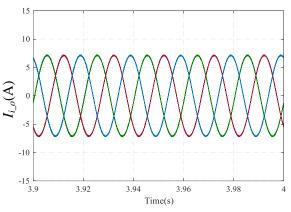

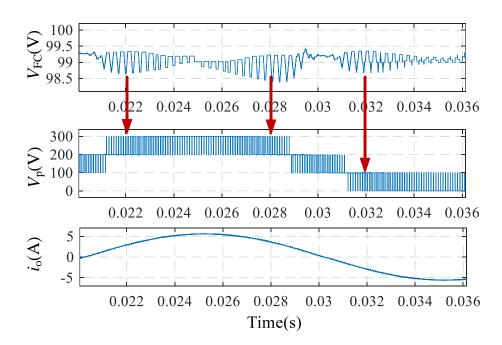

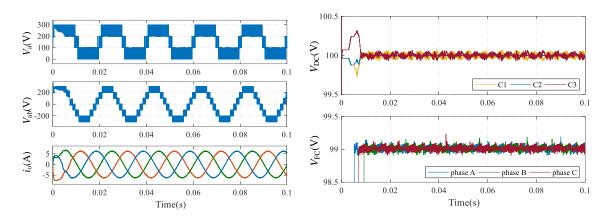

| Figure 5.13 Simulation results of three-phase back-to-back four-level π-type inverter, mr= mi =1.1160         |

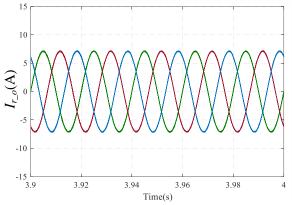

| Figure 5.14 Simulation results of three-phase back-to-back four-level $\pi$ -type inverter, mr=1.1, mi =0.65  |

|                                                                                                               |

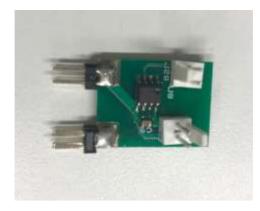

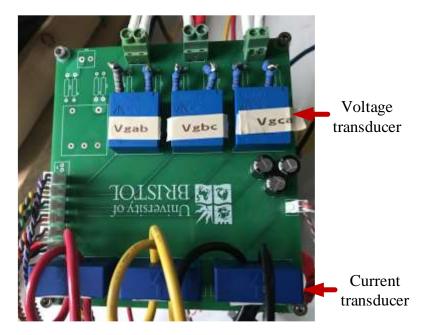

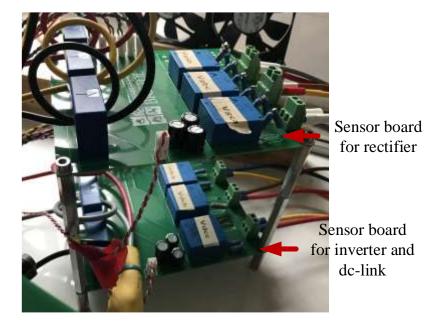

| Figure 5.15 Sensor board prototype163                                                                         |

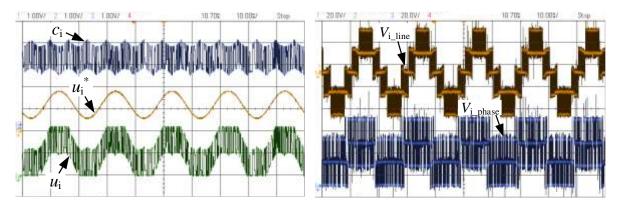

| Figure 5.16 Inverter open loop operation when m=0.5165                                                        |

| Figure 5.17 Inverter open loop operation when m=0.85166                                                       |

| Figure 5.18 Concept diagram of the single-end three-phase inverter with proposed dc-link NP voltages          |

| balancing control strategy                                                                                    |

| Figure 5.19 Single-end inverter operation with proposed control strategy m=0.6                                |

| Figure 5.20 Single-end inverter operation with proposed control strategy m=0.65                               |

| Figure 5.21 Concept diagram of the back-to-back three-phase four-level $\pi$ -type converter with proposed    |

| dc-link NP voltages balancing control strategy                                                                |

| Figure 5.22 Experimental prototype of the back-to-back four-level $\pi$ -type converter                       |

| Figure 5.23 Sensor boards prototype                                                                           |

| Figure 5.24 Grid-side isolation transformer as well as the variac174                                          |

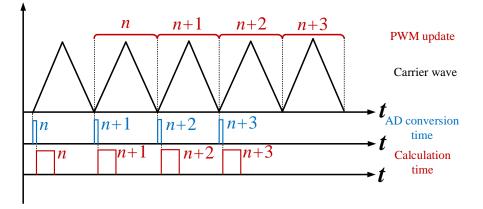

| Figure 5.25 signal delay concept within in the DSP/FPGA control board                                         |

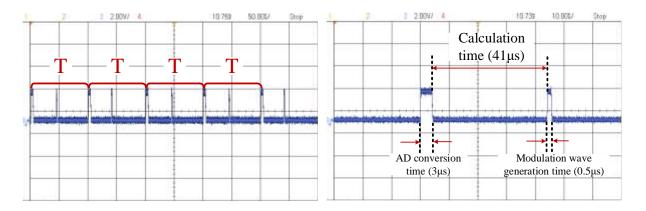

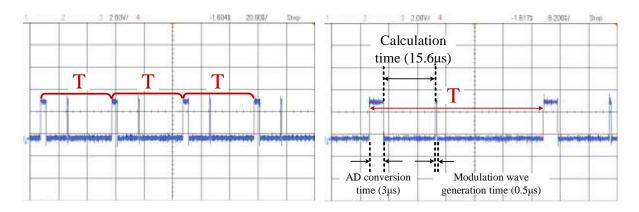

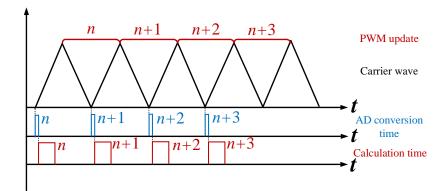

| Figure 5.26 Monitored back-to-back system DSP/FPGA code execution time through DAC175                         |

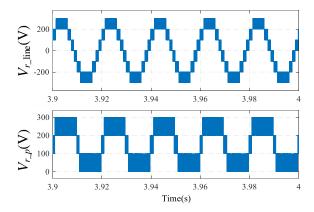

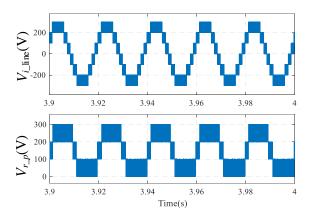

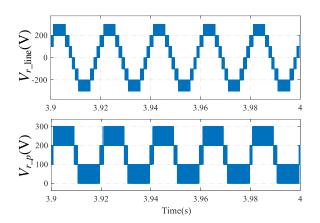

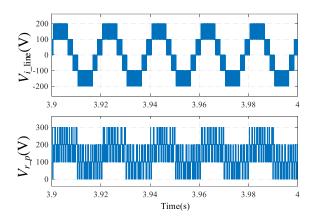

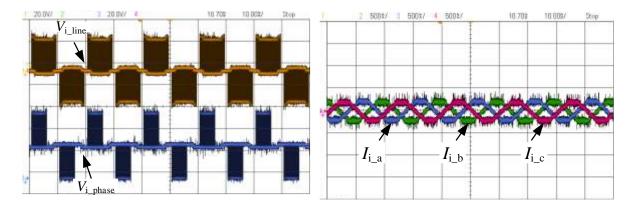

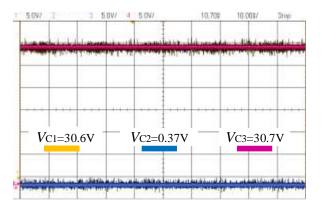

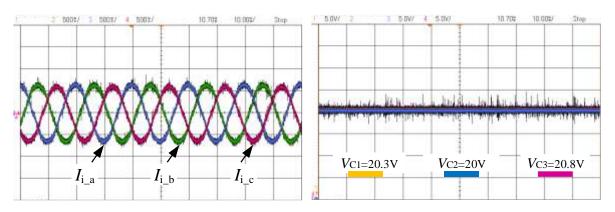

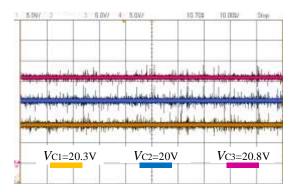

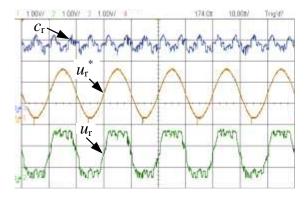

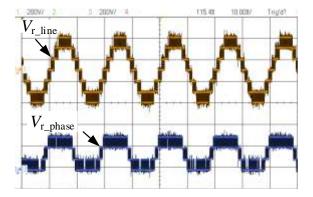

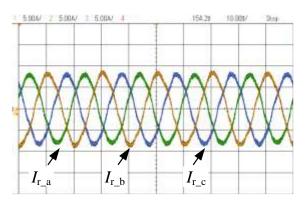

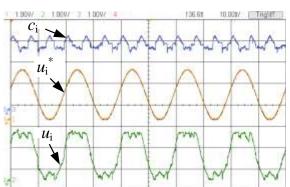

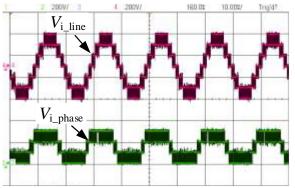

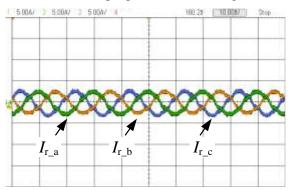

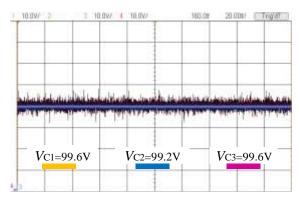

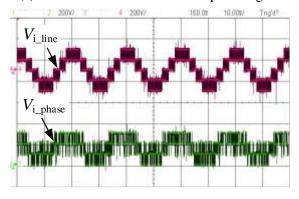

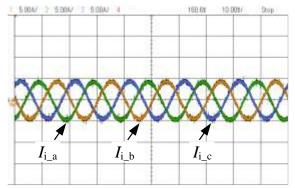

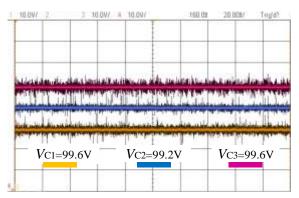

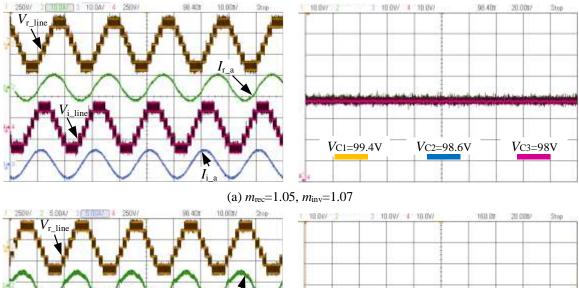

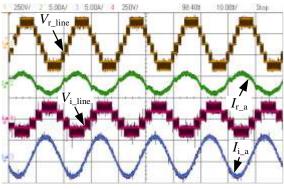

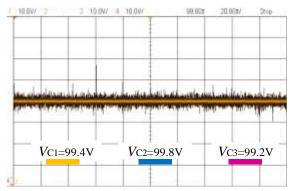

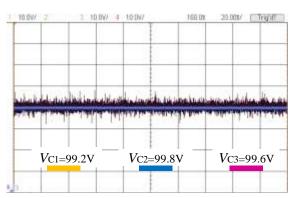

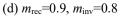

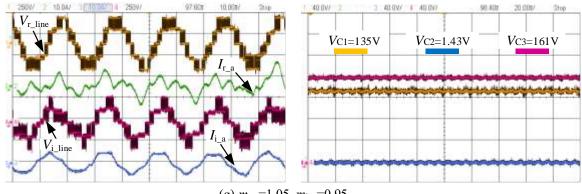

| Figure 5.27 Test waveforms when mrec=minv=1.1177                                                              |

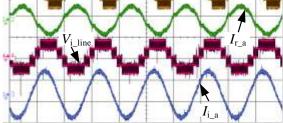

| Figure 5.28 Test waveforms when mrec=0.9, minv=0.6179                                                         |

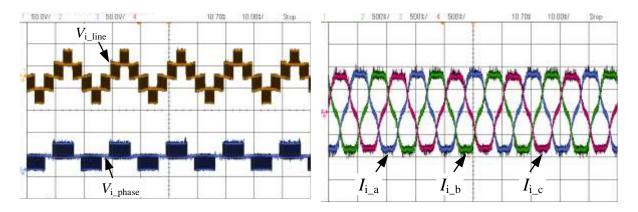

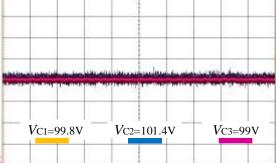

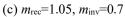

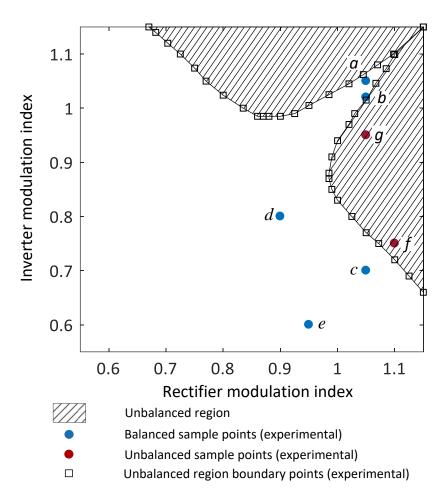

| Figure 5.29 More experimental results of the different modulation indices on both sides                       |

| Figure 5.30 Controllable and uncontrollable region for dc-link capacitors voltage balancing based on          |

| experimental measurements under unity power factor operation on both sides184                                 |

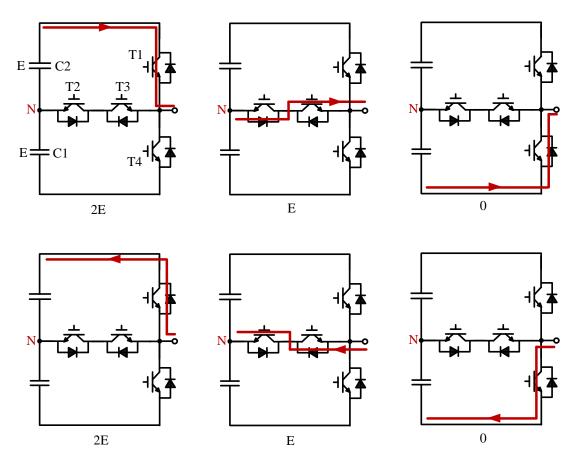

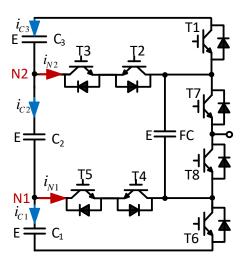

| Figure 6.1 Phase-leg of the hybrid-clamped four-level $\pi$ -type converter                                   |

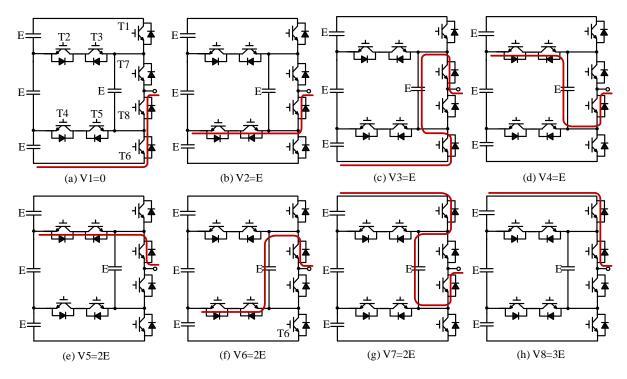

| Figure 6.2 Switching states with corresponding output voltage levels                                          |

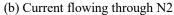

| Figure 6.3 Neutral path currents flow conditions (a) power factor=0, (b) power factor=1191                    |

| Figure 6.4 Level shifted carrier-based sinusoidal modulation scheme for the hybrid-clamped four-level $\pi$ - |

| type converter                                                                                                |

| Figure 6.5 Relationship between dc-link capacitors currents and neutral path currents                       |

|-------------------------------------------------------------------------------------------------------------|

| Figure 6.6 Control and modulation flowchart199                                                              |

| Figure 6.7 V6, V8 switching states when io>0                                                                |

| Figure 6.8 V5, V8 switching states when io>0                                                                |

| Figure 6.9 V1, V2 switching states when io<0                                                                |

| Figure 6.10 V1, V4 switching states when io<0                                                               |

| Figure 6.11 V4, V7 switching states when io>0204                                                            |

| Figure 6.12 V3, V6 switching states when io<0                                                               |

| Figure 6.13 Concept configuration of the single-phase hybrid clamped four-level $\pi$ -type converter 207   |

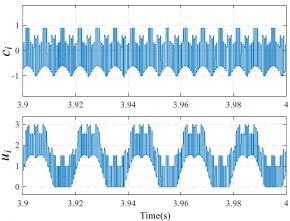

| Figure 6.14 Simulation results of the single-phase hybrid clamped four-level $\pi$ -type converter          |

| Figure 6.15 Experimental prototype of the hybrid-clamped four-level $\pi$ -type single-phase inverter 211   |

| Figure 6.16 Monitored back-to-back system DSP/FPGA code execution time through DAC213                       |

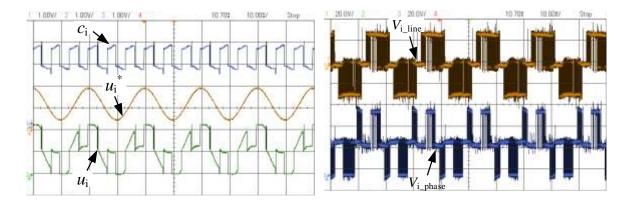

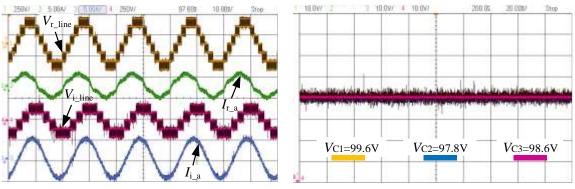

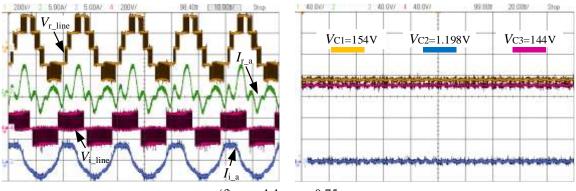

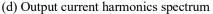

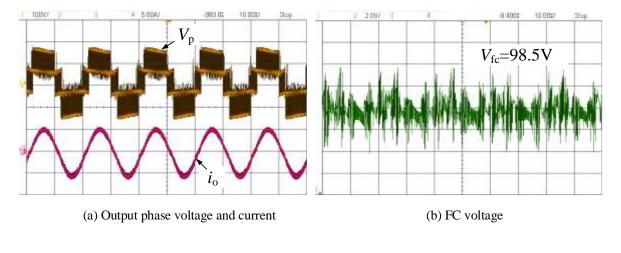

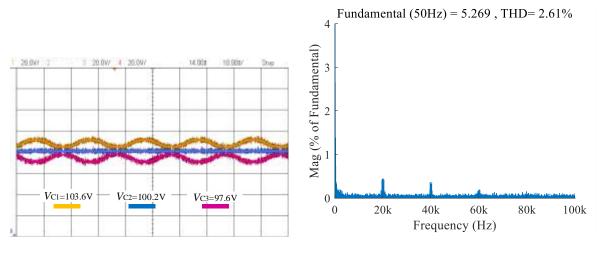

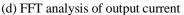

| Figure 6.17 Single-phase hybrid clamped four-level $\pi$ -type converter test waveforms at 10 kHz switching |

| frequency                                                                                                   |

| Figure 6.18 Single-phase hybrid clamped four-level $\pi$ -type converter test waveforms at 20 kHz switching |

| frequency                                                                                                   |

| Figure 6.19 Single-phase simulation FC voltage, output phase voltage and current (Zoomed)216                |

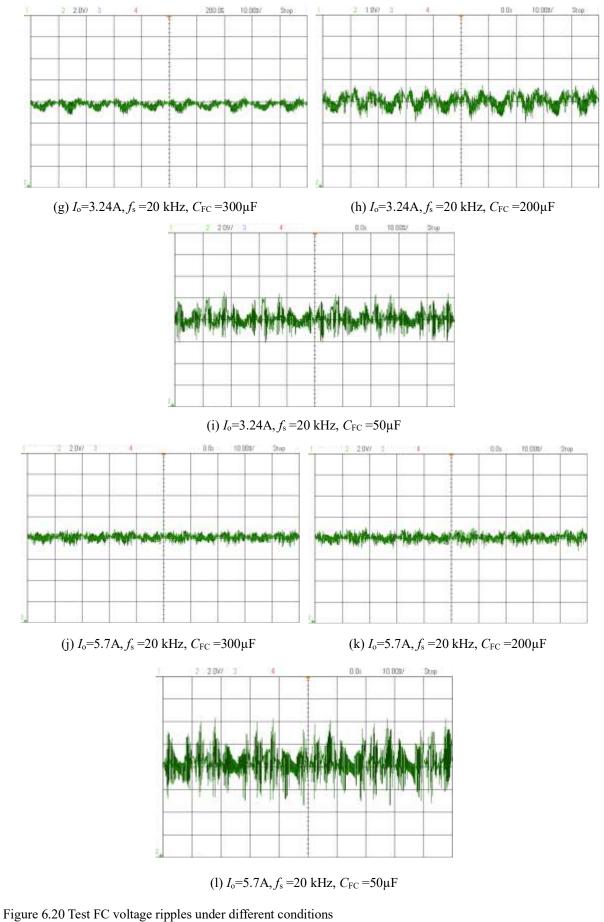

| Figure 6.20 Test FC voltage ripples under different conditions                                              |

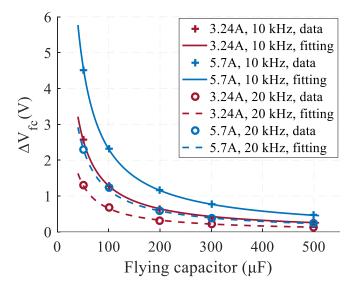

| Figure 6.21 Curves of $\Delta V_{fc}$ p vs $C_{fc}$                                                         |

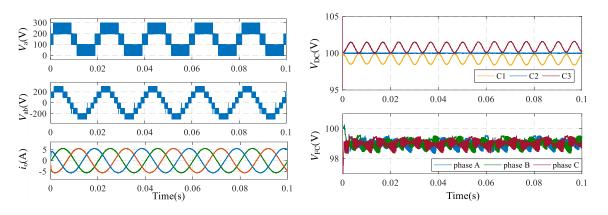

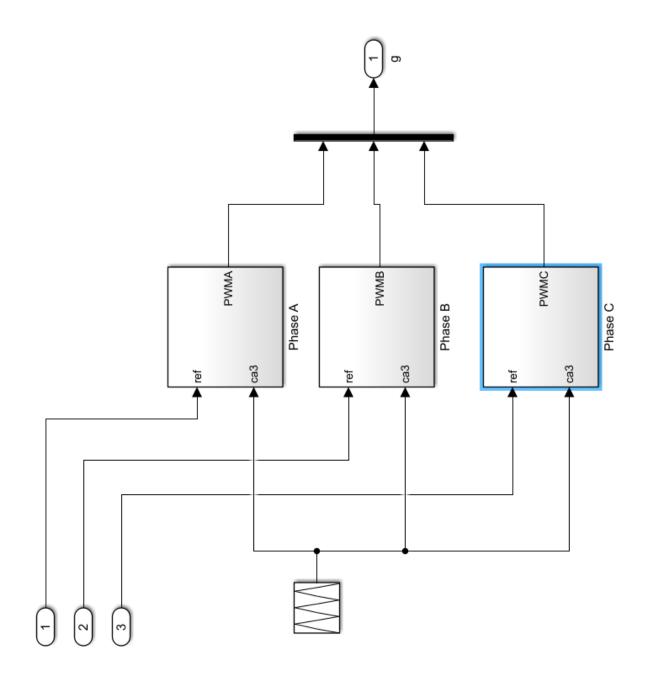

| Figure 6.22 Three-phase hybrid clamped four-level $\pi$ -type converter simulation results                  |

| Figure 6.23 Three-phase hybrid clamped four-level $\pi$ -type converter simulation results                  |

## List of symbols

| Symbol             | Description                                                   | Units |

|--------------------|---------------------------------------------------------------|-------|

| a, b, c            | switching energy curve fitting parameters                     | -     |

| $E_{ m sw\_ins}$   | Switching device switching energy                             | J     |

| $f_{ m sw}$        | IGBT switching frequency                                      | Hz    |

| <i>i</i> c         | IGBT switching current                                        | А     |

| i <sub>C</sub>     | DC-link capacitor current                                     | А     |

| $i_{ m rr}$        | Diode reverse recovery current                                | А     |

| J                  | Energy on the dc-link capacitor                               | J     |

| $P_{\rm con}$      | Average conduction loss                                       | W     |

| $P_{ m con\_ins}$  | Instantaneous conduction loss                                 | W     |

| $P_{\mathrm{on}}$  | Switching device turn-on loss                                 | W     |

| $P_{ m off}$       | Switching device turn-off loss                                | W     |

| $P_{\rm rr}$       | Diode reverse recovery loss                                   | W     |

| $P_{ m sw}$        | Average switching loss                                        | W     |

| $P_{ m sw\_ins}$   | Instantaneous switching loss                                  | W     |

| $Q_{ m rr}$        | Diode reverse recovery charge                                 | С     |

| t1                 | IGBT switching current rising time during turn-on transient   | S     |

| t2                 | IGBT switching voltage falling time during turn-on transient  | S     |

| t3                 | IGBT switching voltage rising time during turn-off transient  | S     |

| t4                 | IGBT switching current falling time during turn-off transient | S     |

| trr                | Diode reverse recovery time                                   | S     |

| Т0-Т7              | Dwell time for zero vectors V0, V7 and active vectors V1-V6   | S     |

| Ts                 | Switching period                                              | S     |

| $V_{\text{base}}$  | Switching device blocking voltage on the datasheet            | V     |

| $V_{lpha},V_{eta}$ | alpha-beta variables on alpha-beta frame                      | V     |

| $V_{ m an}$ , $V_{ m bn}$ , $V_{ m cn}$ | A,B,C phase variables on A, B, C frame                         |     |  |

|-----------------------------------------|----------------------------------------------------------------|-----|--|

| $V_{ m dc}$                             | dc-link input voltage                                          | V   |  |

| $V_{ m ref}$                            | Reference vector for SVM                                       | V   |  |

| $V_{ m sw}$                             | IGBT blocking or switching voltage                             | V   |  |

| α                                       | Vref location angle on the $\alpha\beta$ plane                 | rad |  |

| $\Delta v_{ m c}$                       | Difference between the ideal dc-link capacitor voltage and the | V   |  |

|                                         | actual dc-link capacitor voltage                               |     |  |

| ΔΤ                                      | Pre-defined pulse width in power loss simulation model         | 1/s |  |

| Symbol             | Description                                                       | Units |

|--------------------|-------------------------------------------------------------------|-------|

| $L_{\rm i}(t)$     | Level function                                                    | -     |

| m                  | Modulation index                                                  | -     |

| $T_{\rm i}(t)$     | Modified modulation index                                         | -     |

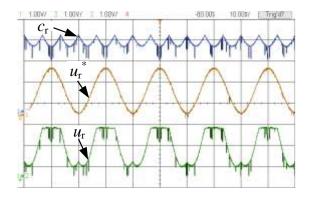

| $u_{\rm i}(t)$     | Modulation wave                                                   | -     |

| $V_{ m dc}$        | Total dc-link voltage                                             | V     |

| $V_{ m parasitic}$ | Voltage overshoot during switching transient induced by parasitic | V     |

|                    | components in the circuit                                         |       |

| ω                  | Fundamental frequency                                             | rad/s |

| Chapter 4 | 4 |

|-----------|---|

|-----------|---|

| Symbol             | Description                                                     | Units |

|--------------------|-----------------------------------------------------------------|-------|

| $A_0, B_0, C_0$    | Parameters of relationship between the switching energy and the | -     |

|                    | device current                                                  |       |

| $E_{ m off}$       | IGBT turn-off energy                                            | J     |

| $E_{on}$           | IGBT turn-on energy                                             | J     |

| $E_{ m rr}$        | Diode reverse recovery energy                                   | J     |

| $E_{ m sw\_ins}$   | Instantaneous switching energy                                  | J     |

| $E_{ m sw}$        | Average switching energy over one fundamental cycle             | J     |

| $f_{ m s}$         | Carrier frequency/switching frequency                           | Hz    |

| <i>i</i> c         | Device conduction current                                       | А     |

| $I_{\rm CM}$       | Load current peak value                                         | А     |

| k                  | IGBT conduction duty cycle                                      | -     |

| $P_{\rm con\_ins}$ | Instantaneous conduction power loss                             | W     |

| $P_{\text{con_T}}$ | Average IGBT conduction loss                                    | W     |

| $P_{\rm con_D}$    | Average anti-parallel diode conduction loss                     | W     |

| $P_{ m sw}$        | Average switching power loss                                    | W     |

| $r_{0\mathrm{D}}$  | Diode equivalent turn-on resistance                             | Ω     |

| Кот                | IGBT equivalent turn-on resistance                              | Ω     |

| $T_{ m d}$         | Deadtime                                                        | S     |

| To                 | Fundamental period                                              | Hz    |

| Ts                 | Switching period                                                | S     |

| $v_{\rm CE}$       | Switching device forward conduction voltage                     | V     |

| $v_{\rm p}$        | Converter output phase voltage fundamental component            | V     |

| V <sub>base</sub>  | Reference switching voltage                                     | V     |

| $V_{\rm CE0}$      | Equivalent IGBT on-state threshold voltage                      | V     |

| $V_{ m F0}$        | Equivalent diode on-state threshold voltage                     | V     |

| $V_{\rm GE}$       | IGBT gate driver voltage                                        | V     |

| $V_{ m sw}$        | Actual switching voltage                                        | V     |

| $\Delta V_{ m d}$    | Decay on the output voltage | V   |

|----------------------|-----------------------------|-----|

| arphi                | Power factor angle          | rad |

| $\theta_2, \theta_1$ | Integration boundaries      | rad |

| Symbol                                                                                        | Description                                                         | Units |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------|

| c(t)                                                                                          | Zero-sequence components                                            | -     |

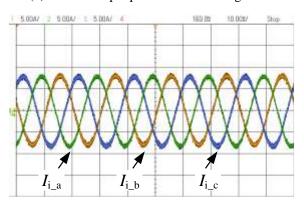

| $\dot{l}_{ m ai}$ , $\dot{l}_{ m bi}$ , $\dot{l}_{ m ci}$                                     | Inverter three-phase output currents                                | А     |

| $i_{\mathrm{ar}}, i_{\mathrm{br}}, i_{\mathrm{cr}}$                                           | Rectifier three-phase ac currents                                   | А     |

| $i_{\mathrm{C1}},i_{\mathrm{C2}}$ , $i_{\mathrm{C3}}$                                         | DC-link capacitor currents                                          | А     |

| $\overline{\iota}_{N2\_r}, \ \overline{\iota}_{N1\_r}$                                        | Average rectifier neutral path currents                             | А     |

| $I_{\mathrm{N1}\_\mathrm{i}}$ , $i_{\mathrm{N2}\_\mathrm{i}}$                                 | Inverter neutral path currents                                      | А     |

| $I_{\mathrm{N1}_\mathrm{r}}, i_{\mathrm{N2}_\mathrm{r}}$                                      | Rectifier neutral path currents                                     | А     |

| $\overline{\iota}_{N2_{}i}$ , $\overline{\iota}_{N1_{}i}$                                     | Average inverter neutral path currents                              | А     |

| $I_{ m i}$                                                                                    | Inverter output current peak value                                  | А     |

| $I_{ m r}$                                                                                    | Rectifier ac current peak value                                     | А     |

| $K_{\mathrm{aN1}_{\mathrm{i}}}, K_{\mathrm{bN1}_{\mathrm{i}}}, K_{\mathrm{cN1}_{\mathrm{i}}}$ | Duty cycles of inverter three-phase currents contribute to neutral  | -     |

|                                                                                               | path currents flows through N1                                      |       |

| $K_{\mathrm{aN2}_{i}}, K_{\mathrm{bN2}_{i}}, K_{\mathrm{cN2}_{i}}$                            | Duty cycles of inverter three-phase currents contribute to neutral  | -     |

|                                                                                               | path currents flows through N2                                      |       |

| $K_{aN1_r}, K_{bN1_r}, K_{cN1_r}$                                                             | Duty cycles of rectifier three-phase currents contribute to neutral | -     |

|                                                                                               | path currents flows through N1                                      |       |

| $K_{aN2_r}, K_{bN2_r}, K_{cN2_r}$                                                             | Duty cycles of rectifier three-phase currents contribute to neutral | -     |

|                                                                                               | path currents flows through N2                                      |       |

| m <sub>i</sub>                                                                                | Inverter modulation index                                           | -     |

| m <sub>r</sub>                                                                                | Rectifier modulation index                                          | -     |

| <i>P</i> <sub>r</sub> , <i>P</i> <sub>i</sub>                                                 | Active power of the rectifier and inverter                          | W     |

| $u^*_{\max}$ , $u^*_{\min}$                                                                   | Maximum and minimum values of the three-phase sinusoidal            | -     |

|                                                                                               | fundamental components                                              |       |

|                                                                                               |                                                                     |       |

| $u_{\rm i}(t)$            | Modified final modulation waveforms               | -   |

|---------------------------|---------------------------------------------------|-----|

| $u_i^*(t)$                | Original sinusoidal fundamental waveforms         | -   |

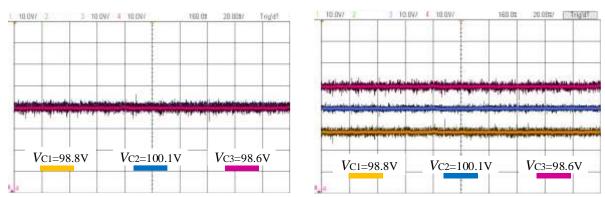

| $v_{\rm Cj}$              | Actual measured voltage of the dc-link capacitor  | V   |

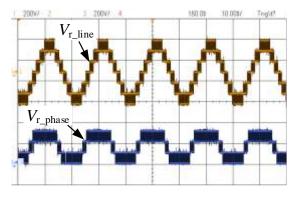

| $V_{ m rp}$ , $V_{ m ip}$ | Peak phase voltages of the rectifier and inverter | V   |

| $arphi_{ m i}$            | Inverter output power factor angle                | rad |

| $arphi_{ m r}$            | Rectifier ac-side power factor angle              | rad |

| Symbol                      | Description                                                                       | Units |

|-----------------------------|-----------------------------------------------------------------------------------|-------|

| $C_{ m fc}$                 | FC capacitance value                                                              | F     |

| d                           | Duty cycle when the current flowing through neutral points                        | -     |

| $d_{ m fc}$                 | Duty cycle of the switching period that current flows through FC                  | -     |

| $d_{ m fc\_p}$              | Proportion of the switching period where the current flowing                      | -     |

|                             | through the flying capacitor causes the maximum FC voltage ripple                 |       |

| $g_{ m p}$                  | coefficient which represents the corresponding value of the unity                 | -     |

|                             | load current trigonometric function $\sin(\omega_0 t + \varphi)$ when the maximum |       |

|                             | FC voltage ripple occurs                                                          |       |

| Io                          | Converter output current                                                          | А     |

| k                           | Values determine which NP the current should flow through                         | -     |

| $V_{ m tol}$                | Voltage error tolerance range for the FC voltage                                  | V     |

| $V_{ m p}$                  | Single-phase output phase voltage                                                 | V     |

| $\Delta V_{ m fc}$          | Variation of the FC voltage                                                       | V     |

| $\Delta V_{\mathrm{fc}\_p}$ | Peak voltage ripple on FC                                                         | V     |

#### **1** Introduction

#### 1.1 Why multilevel converters and background

Since the invention of semiconductor devices, power electronics has become the core technology in the industry to manipulate the electrical power [1][2][3]. Semiconductor devices make the electronics controllable power supply system available, which is helpful for the automatic control system development in the industry [4]. Meanwhile, with the popularization of the power electronics system, the demand of power electronics in the low-voltage applications market (nominal line voltage up to 690V under the IEC standard, or 575 V under the ANSI standard) [5] includes commercial use area as well as civil use area have increased [6]. These applications include the renewable energy generation such as wind turbines and photovoltaic (PV) energy systems [7][8][9][10], the electric vehicle (EV) drive system [11], electric train traction, more electric ship propulsion systems and more electric aircraft systems[4][8][12]. All these low voltage applications require compact system volume as well as lighter system weight.

All these applications areas require high power density power converter systems. Which means under the same power level requirement, the total converter volume and the system weight are the important factors which should be considered. This creates a challenge for the power electronics system development. Meanwhile, the traditional two-level converter is still the standard industry solution for low-voltage and medium voltage applications. The efficiency of this topology restricted by the high switching losses at high switching frequencies can be deemed as the main drawback of this topology [2][13][14]. However, it has the simple structure and the simple modulation scheme which is still preferred in most industries and companies. Engineers faced in two ways. The first way is to employ or develop semiconductors with high current ratings in order to increase the power rating of traditional two-level converter topologies. Alternatively, advanced SiC and GaN devices with high switching speed are currently under development and can be employed to reduce the switching losses [15][16][17]. Even though, their cost is still very high which will increase the total expense of the whole system. The second way is to use and develop advanced multilevel converter topologies based on conventional low power rating semiconductors [18][19]. A multilevel converter is able to provide an ac output voltage waveform with multiple steps, synthesize the staircase output voltage waveform in order to follow the sinusoidal modulation waveform [20]. Multilevel converters are normally employed for high voltage applications (>33kV) and medium-voltage applications(3-33kV) [21][22], as they allow working at the high dc-link voltage levels due to the shared voltage drop on each device on the series interconnection of the devices. Therefore, compare to the traditional two-level converter, they provide a series of advantages as follow. 1) Lower output harmonic content [23][24]. The higher output voltage levels, the closer sinusoidal output waveforms. Which means at the same switching frequency, the output harmonic content is less than that of the two-level converter and three-level converters. It can provide a higher power quality at the ac side and reduce the output filter size.

2) Lower voltage stress [22]. With the same dc-link voltage, the higher output voltage level, the lower switching voltage on each switching device. Consequently, device dv/dt is lower. This feature can make the multilevel converter be able to employ lower voltage ratings switching devices with lower price, which can save the total cost of the converter system.

3) Lower switching losses [25][26]. With the same dc-link voltage level, due to the lower switching voltage on switching devices, switching losses can be kept low. The converter efficiency drops less with the switching frequency increasing [27]. Meanwhile, in order to keep the equivalent output harmonics, the switching frequency of the converter can be set as a lower value compares to a two-level or three-level converter. This feature can also reduce switching losses. Both aspects increase the converter output efficiency and shrink the heatsink size.

Therefore, the multilevel converter has the ability to be used in low voltage applications as well.

Even multilevel converters have advantages mentioned above, however, they do possess some drawbacks. For example, each phase-leg will have greater number of switching devices, which will increase the total converter system complexity regarding the circuit configuration as well as the control strategy. And this phenomenon becomes more obvious with output voltage levels increase [28]. Therefore, a multilevel converter topology with reduced complexity but without losing original advantages is required.

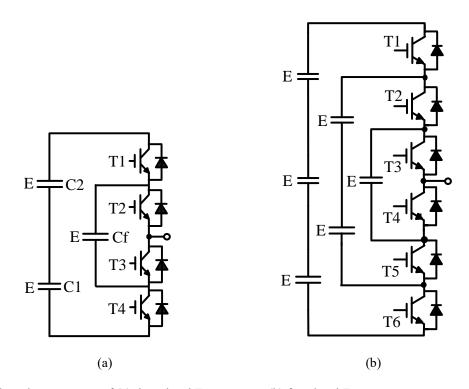

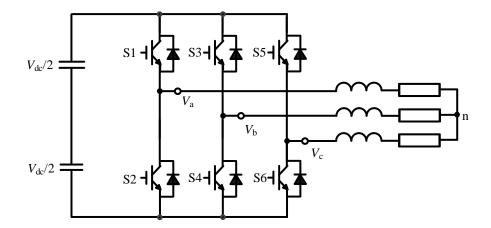

Currently, three main types of multilevel converters are generally used in the industry: cascaded H-

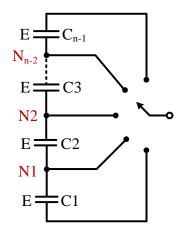

bridge converters, flying capacitor (FC) converters and neutral point clamped (NPC) converters [18] [19][29][30]. Among which the NPC converter does not require numbers of FCs or separated dc voltage supplies compares to the other two types multilevel converters. Therefore, the NPC converter can have the smaller total size with the same output voltage levels. It then can be the best candidate among these three types of multilevel converters. According to the derivation principle of reduced-devices-count multilevel converters [18][31][32][33][34], an active NPC four-level  $\pi$ -type converter (in the rest part of this thesis, it will be called as the four-level  $\pi$ -type converter for short) was introduced. This converter topology has only six active switching devices (IGBT or MOSFET) in each phase leg [20][35][36]. Compares to other traditional four-level or even five-level NPC converters, no clamping diodes in the phase-leg configuration. The configuration characteristic shows this topology has less total switching devices count compare to other four-level converters or even higher-level converters, which simplifies the converter configuration, reduces the total conduction loss. Meanwhile, compares to three-level converters as well as two-level converters, it has advantages such as lower switching voltages and lower harmonics. All these make the four-level  $\pi$ -type converter suitable for low-voltage applications. So far, there are no comprehensive topology characteristic and performance analysis as well as control strategy design for this converter topology. Among which, the power loss analysis based on effective converter power loss models require to be developed in order to quantitatively evaluate the loss distribution as well as the efficiency of the  $\pi$ -type converter against the traditional two-level converter and other popular low voltage applications multilevel converters.

One big challenging issue for the four-level  $\pi$ -type converter is to resolve the dc-link capacitors' voltages/neutral point (NP) voltages unbalancing problem as other NPC multilevel converters have [28][37][38][39][40][41][42]. The unbalancing of the dc-link capacitors votlages can cause couple of issues such as the unwanted higher switching votlage, the higher output harmonics, which may affect the system stability and reilability. Among various dc-link NP voltages regulation methods, the active NP voltage control methods based on advanced modulation strategies are still most popular technical approaches, and have been researched in [26][37][38][40][41][42][43][44][45][46] [47][48][49][50][51].

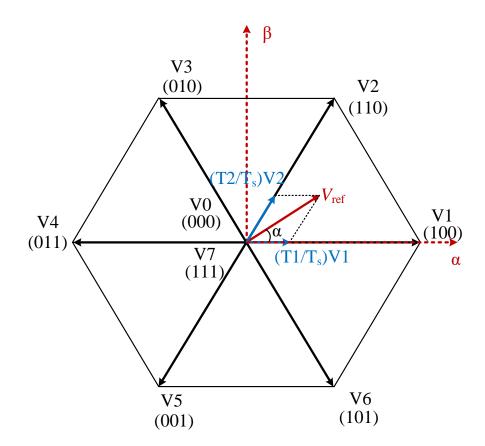

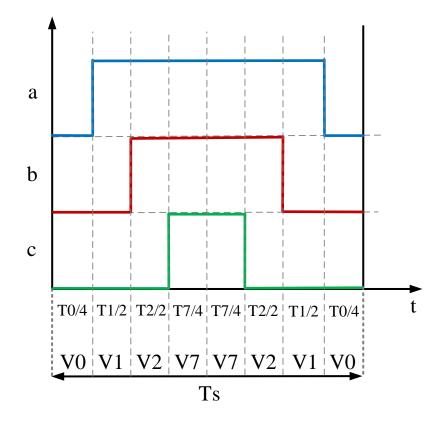

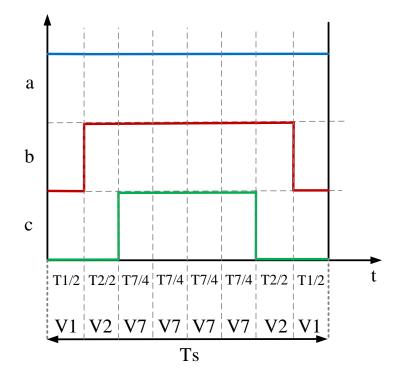

One method is to use control methods based on a virtual vector PWM (VV PWM) [26][47][48][49]. This method can guarantee the dc-link NP voltage balancing with passive front-ends for any voltage

level converters with any power factors and modulation indices. However, the main disadvantage of this method is the switching pattern of each phase-leg within every switching period involves more than two output voltage levels. It consequently increases the total number of switching actions in each switching period, which eventually increases the total switching loss as well as the output harmonics.

Another method is more popular which uses the conventional nearest-three-vectors PWM (NTV PWM) in order to balance the dc-link NP voltage, optimize the switching loss and the total harmonic distortion (THD) at the mean time [28][41][42][46][50][51]. In this case, there are only two voltage levels involved in each switching period and only two switching actions are within each switching period. This NTV PWM based control method can also be realized with a CB-PWM implementation with appropriate zero-sequence signals injection to the original sinusoidal modulation signal for each phase [24][36][40][44][45][52][53][54][55]. Compares to the VV PWM based control method above, the CB-PWM implementation of this method is relatively easy to implement. The main disadvantage of this control method is it cannot guarantee the dc-link capacitor voltage balancing at high modulation indices and high power factors, if only the single-end inverter or rectifier is employed [41][42][46][50][51].

Experimental verifications on NTV PWM based dc-link NP voltage balance control exist for some other specific topologies. Experimental verifications based on a back-to-back five-level NPC converter by the NTV PWM method have been published in [41][42][46]. [24][40] present the case study based on the method by manipulating power angles on both the rectifier side and the inverter side with offline modulation wave calculation. Therefore, an appropriate analysis and implementation for the dc-link NP voltage balancing control of the four-level  $\pi$ -type converter is required. Appropriate experimental verification for the four-level  $\pi$ -type converter is also required.

#### **1.2 Research objectives**

The primary target of the research work for this PhD thesis is the theoretical investigation and experimental implementation on a four-level  $\pi$ -type converter under the low voltage condition. As it is designed for low voltage applications such as renewable energy boat, electric aircraft, electric vehicle, or photovoltaic system, therefore, some specifications for the research should be briefly listed.

- The whole system volume should be kept small. As the main space occupying components are the converter ac-side filter, therefore, it should employ small output filter to realize the same output harmonics or employ the same size output filter to realize the smaller output harmonics compares to the two-level and three-level converters under the same input voltage and power condition.

- High and stable efficiency with the change of the switching frequency in order to make the system has higher power density for the applications such as electric car, renewable energy boat, or electric aircraft. Given the small switching voltage on the four-level  $\pi$ -type converter compares to the two-level and three-level converters, it has the less switching loss. System efficiency should be kept high and drops as minimum as possible with the increase of the switching frequency. This feature should be better than that of the two-level converters and three-level converters.

- Appropriate control strategy needs to be developed and implemented in order to eliminate the dc-link NP voltage unbalance issue.

Therefore, according to the system specification, the primary research target can be expanded to several sub-objectives as follows.

- As no cascaded cells are required in the phase-leg layout, meanwhile, over three output voltage levels are still required, therefore, compares to the three-level T-type converter or even two-level converter, the overall NO. of the switching devices of each phase-leg increases. It is required to investigate the structure characteristic of the four-level π-type converter, and compare with the other popular NPC multilevel converters in order to prove its advantage on output filter size selection and switching device selection.

- As for the low voltage applications such as renewable energy boat or electric vehicle, high power density is required. Therefore, it is required to use mathematical method to investigate the power

loss distribution as well as total efficiency to prove its advantage on lower switching losses based on the same power input and load conditions. Relevant experimental works will be needed to prove this investigation.

- > As the intrinsic unbalancing issue on the dc-link NP voltages of NPC multilevel converter, investigations on the dc-link NP voltage unbalancing situation of the four-level  $\pi$ -type converter should be investigated. After that, appropriate NP voltage balancing control strategy should be developed and implemented on it. Theoretically or experimentally summarize the control applicable region for the back-to-back four-level  $\pi$ -type converter.

- > If possible, try to find the NP voltage balancing solution in order to make the four-level  $\pi$ -type converter be able to work as the single-end converter without the restriction.

#### 1.3 Thesis layout

This thesis is separated into 7 chapters. Except for the chapter 1 introduction part, the remaining 6 chapters in the following cover the key aspects of the work.

#### Chapter 2

Literature review on the popular NPC multilevel converter topologies, the various sorts of converter power loss analysis methods, and the development review of the dc-link NP voltages balancing control.

#### Chapter 3

The four-level  $\pi$ -type converter topology configuration introduction. Its phase-leg layout characteristic is presented based on the each switching device selection, modulation scheme introduction, and the voltage rating selection on each switching device. Comparison with the other popular topology which includes two-level converter, three-level diode NPC converter, three-level T-type converter.

#### Chapter 4

Analytical average power loss models of the four-level  $\pi$ -type converter have been analyzed. Depending on the modulation index, the analytical average loss model on each individual switching device has been separately analyzed. The three-phase converter operation efficiency has been verified by simulations as well as experiments. The efficiency measurement experiments of a traditional two-level converter have been taken in order to provide the intuitive comparison with the four-level  $\pi$ -type converter.

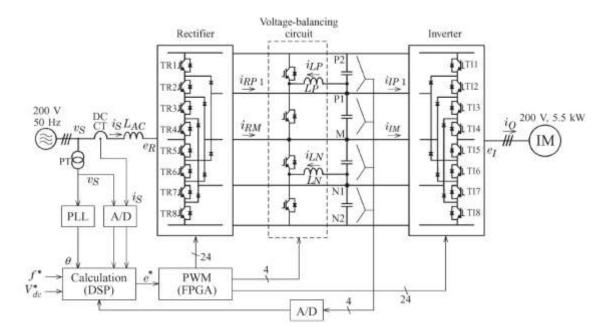

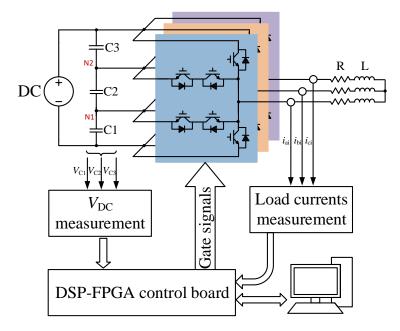

A NP voltage balancing control method for the four-level  $\pi$ -type converter based on NTV PWM has been analyzed. This control scheme has been implemented with an NTV PWM equivalent level shift CB-PWM with the dynamic optimum zero-sequence signals injections in order to simplify the control algorithm and provide the NP voltage balancing function at the meantime. A back-to-back configuration is used to realize the high modulation index operation when both sides are in the unity power factor conditions. The fully controllable region for the back-to-back system when both sides in the unity power factor has been verified by simulations as well as experiments.

#### Chapter 6

A hybrid-clamped four-level  $\pi$ -type converter based on the original four-level  $\pi$ -type converter has been proposed. This new topology is able to operate at high modulation index and high power factor conductions as a single-end inverter or rectifier. It improved the operation limit of the original fourlevel  $\pi$ -type converter. Due to the FC includes in each phase-leg, one important feature of this topology is able to operate with the single phase-leg structure. Simulation and experimental results verified the proposed topology and the control scheme.

#### Chapter 7

Conclusions based on the work presented in this thesis and recommendations of the additional work which could further develop and improve the ideas proposed and presented in this thesis

#### 2 Literature review

#### 2.1 Multilevel converter topologies review

This section presents main kinds of multilevel converter topologies. Generally, there are three basic kinds of multilevel converter topologies employed in the industry and the commercial areas: NPC converters, FC converters, and cascaded H-bridge converters.

#### 2.1.1 Cascaded H-bridge converter

A cascaded H-bridge converter is based on couples of H-bridge converter cells connected in series with several individual dc voltage sources [30]. Each H-bridge cell in this converter topology is a H-bridge converter which consists of four switching devices, and is supplied by separate dc power supplies. The output voltage level of the H-bridge cascaded converter increases with the increase of the cell number. Due to its highly scalable and modularized features, it is a good candidate for high voltage applications. which is widely used in the industry.

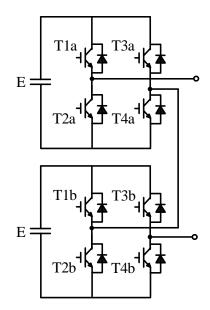

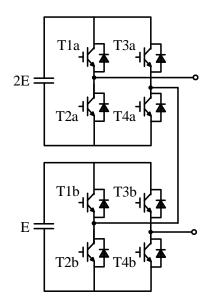

Figure 2.1 Phase-leg structure of a five-level cascaded H-bridge converter

Fig.2.1 presents the phase-leg structure of a five-level cascaded H-bridge inverter [30]. This topology is able to output 5 voltage levels at the ac side. And due to each H-bridge cell is supplied by the individual dc voltage supply with the same voltage value, this kind of cascaded H-bridge converter is

also known as the symmetrical cascaded H-bridge converter [8]. A symmetrical cascaded H-bridge converter is able to produce 2N+1 output voltage level with N H-bridge cells connected in series.

Figure 2.2 Phase-leg structure of the asymmetrical seven-level cascaded H-bridge converters

Fig.2.2 presents an asymmetrical 7-level cascaded H-bridge converter phase-leg configuration [30]. It can be found out that structure is similar to that of the symmetrical 5-level cascaded H-bridge converter as shown in Fig.2.1. The difference is the top H-bridge cell of the asymmetrical 7-level cascaded H-bridge converter is supplied twice the dc voltage than that of the bottom H-bridge cell. With such configuration, the asymmetrical H-bridge converter is able to generate more output voltage levels which is exponential to the H-bridge cells number N. An asymmetrical cascaded H-bridge converter with N H-bridge cells is able to generate  $2^{(N+1)} - 1$  output voltage levels with dc voltage supplies varying in multiple of constant 2 like: E, 2E, 4E,...  $2^{(N+1)}E$  [56]. Meanwhile, due to different H-bridge cells are supplied by different dc voltages, switching devices in different cells have different voltage stress as well as the switching losses.

Consequently, the advantages and disadvantages of the cascaded H-bridge converter can be summarized as follow.

#### Advantages

• Cascaded H-bridge converter has highly modularity feature due to the repeatability connection of each H-bridge cell. Therefore, the cost as well as the complexity to build any desired voltage level converter are relatively lower than the other multilevel converters which requires

customization such as NPC converters or FC converters. This feature makes it be popular in high voltage and high power industries. And this feature makes it allow easy manufacturing and packaging.

#### Disadvantages

• As each H-bridge cell requires isolated dc voltage source, therefore, this topology is not suitable for low voltage applications such as EV, more electric aircraft where the converter size and weight are main concerns.

#### Reliability

- Block voltage rating on switching devices: With the same input voltage level, compare to the two-level converter, the H-bridge cascaded converters with more than three voltage levels at output voltage definitely have less block voltage rating. It means if using the same type of the switching devices, the actual block voltage of the switching devices of the H-bridge cascaded converter is less, which will reduce the risk of overvoltage shoot through due to the parasitic inductance [57][58].

- Fault tolerance: Assume the fault occurs at the specific switching devices. For the H-bridge cascaded converter, if the faulty devices in the system with redundant H-bridge cells standing by, then the redundant cell can take over the faulty cell to maintain the whole system continue working as normal. If the faulty devices in the system without redundant H-bridge cells, and the other cells are still in healthy condition, the whole system will continue the operation but loss the symmetrical operation condition and the total output voltage level will be affected [57]. On the opposite, the two-level converter will immediately shut down if any fault occurs on the switching devices.

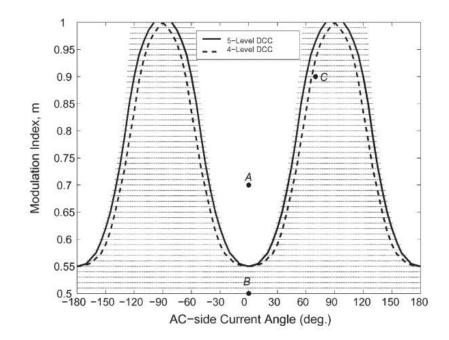

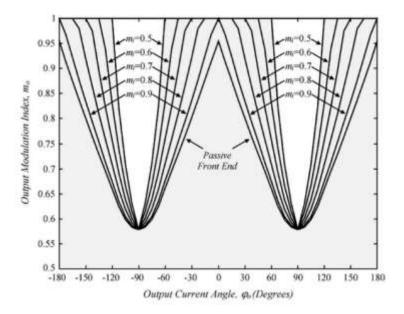

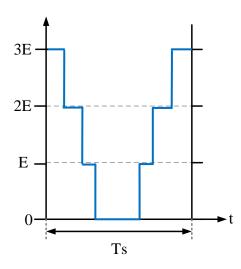

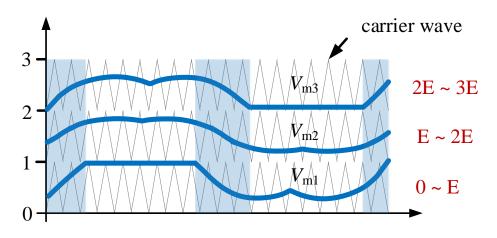

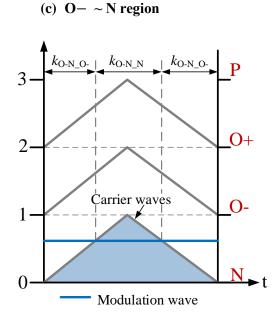

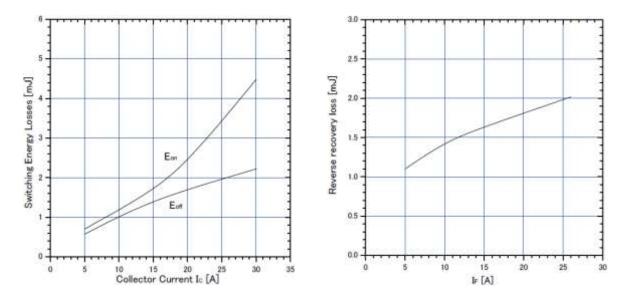

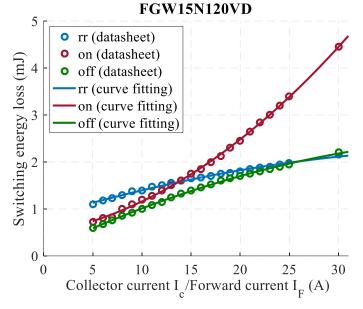

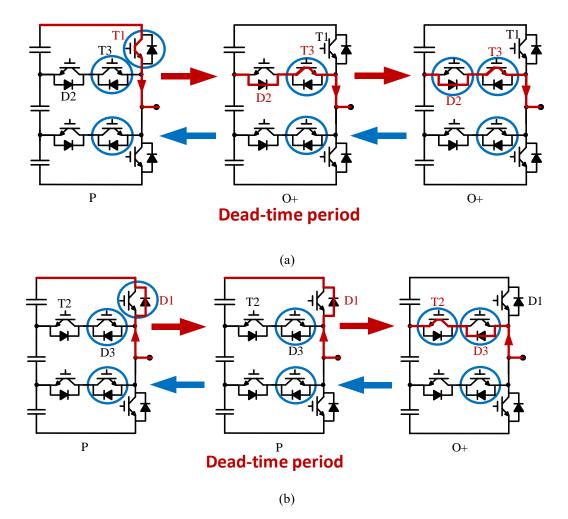

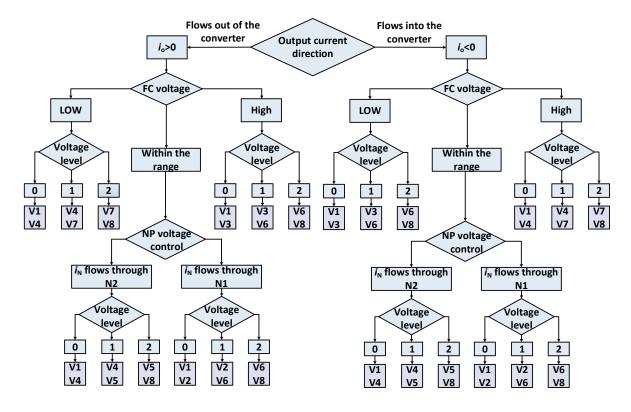

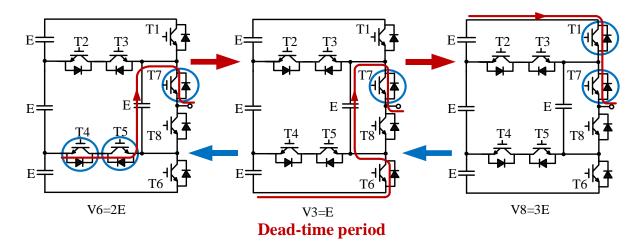

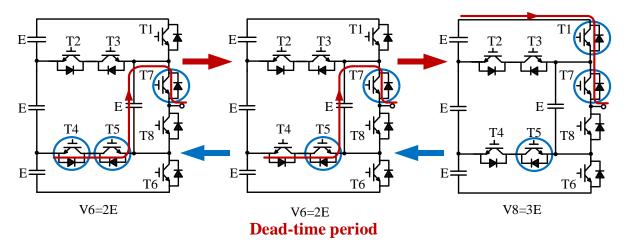

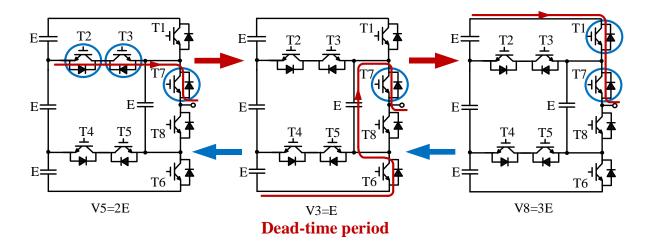

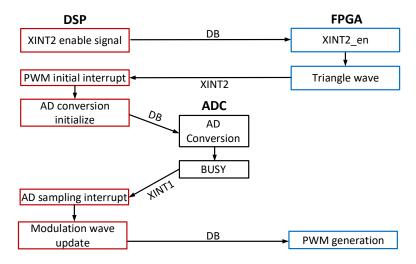

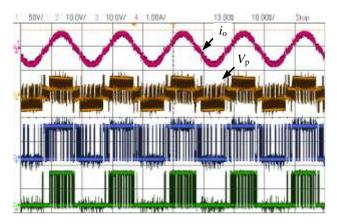

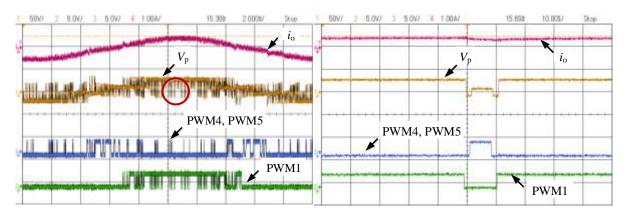

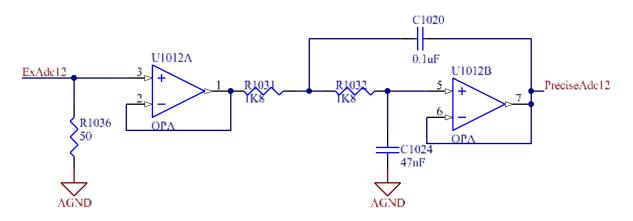

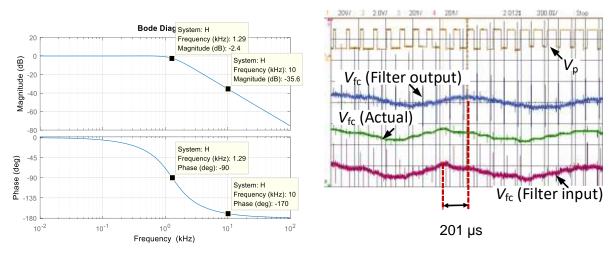

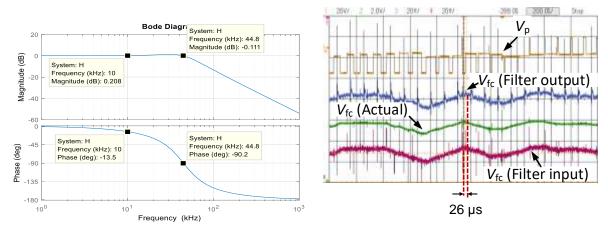

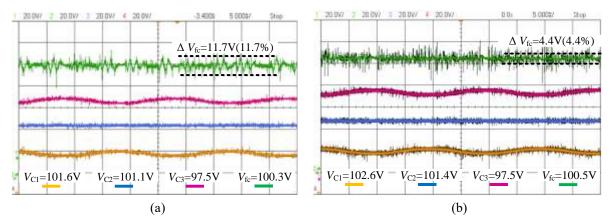

#### Output harmonics