## This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Wang, Jun

Design Trade-off Analysis and Optimisation of a High-density Active Shunt Regulator

**General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

Take down policy

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research.

However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

- · Bibliographic details for the item, including a URL

- An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Design Trade-off Analysis and Optimisation of a High-density Active Shunt Regulator for Aircraft

by

Jun Wang

A thesis submitted to the University of Bristol in accordance with the requirements for award of the degree of Doctor of Philosophy in the Faculty of Engineering

February 2019

Word count: 43801

# **Contents**

| Abs  | tract     |                                                                          | v    |

|------|-----------|--------------------------------------------------------------------------|------|

| Ack  | nowledg   | gement                                                                   | vi   |

| Decl | laration  |                                                                          | vii  |

| Mer  | norandu   | ım                                                                       | viii |

| Pub  | lications |                                                                          | ix   |

| List | of Syml   | ools                                                                     | x    |

| List | of Abbr   | eviations and Acronyms                                                   | xii  |

| List | of Figu   | res                                                                      | xiv  |

| List | of Table  | es                                                                       | xvii |

| CH   | APTER     | 1 Application Background and Research Aims                               | 1    |

| ]    | 1.1       | More Electric Aircraft (MEA) and electrical power generation in aircraft | 1    |

| ]    | 1.2       | Permanent Magnet (PM) Generator with an Active Shunt Regulator (ASR)     | 1    |

| ]    | 1.3       | Power Electronics in MEA                                                 | 5    |

|      | 1.3.1     | Converter topologies                                                     | 7    |

|      | 1.3.2     | Power devices                                                            | 9    |

|      | 1.3.3     | Device/topology combinations                                             | 12   |

|      | 1.3.4     | Passive components in the ASR                                            | 13   |

|      | 1.3.5     | Optimisation of power converters                                         | 15   |

| į    | 1.4       | Research objectives                                                      | 16   |

| į    | 1.5       | Structure of Thesis                                                      |      |

| CH   | APTER     | 2 Modelling of Active Power Devices                                      | 18   |

| 2    | 2.1       | Topologies and power devices                                             | 18   |

| 2    | 2.2       | Operation of the ASR as a voltage source converter                       | 19   |

| 2    | 2.3       | Analytical power loss modelling                                          | 21   |

|      | 2.3.1     | Conduction loss                                                          | 21   |

|      | 2.3.2     | Switching loss                                                           |      |

|      | 2.3.3     | Total converter loss                                                     |      |

| 2    | 2.4       | Two-level converter with SPWM                                            |      |

|      | 2.4.1     | Two-level structure with Si IGBT and Si diode (2L-Si)                    |      |

|      | 2.4.2     | 7 ( )                                                                    |      |

| - 2  | 2.5       | Three-level converter with SPWM                                          | 28   |

|     | 2.5.1  | Three-level T-type structure with Si IGBT and Si diode (3LT-Si)            | 30 |  |  |

|-----|--------|----------------------------------------------------------------------------|----|--|--|

|     | 2.5.2  | Three-level T-type structure with SiC MOSFET + SiC Shottky Diode (3LT-SiC) | 31 |  |  |

| 2   | .6     | Case study                                                                 |    |  |  |

| 2   | .7     | Summary                                                                    | 36 |  |  |

| СНА | PTER   | R 3 Neutral Point Voltage Balancing in Three-level Converters              |    |  |  |

| 3   | .1     | Neutral point voltage oscillation in three-phase, three-level converters   | 38 |  |  |

| 3   | .2     | Zero-sequence Signal Injection (ZSI)                                       | 41 |  |  |

| 3   | .3     | Virtual Zero-level Modulation (VZM)                                        | 42 |  |  |

|     | 3.3.1  | Principles of NP voltage balancing based on VZM                            | 42 |  |  |

|     | 3.3.2  | Case study                                                                 | 45 |  |  |

| 3   | .4     | Analytical loss model with VZM                                             | 46 |  |  |

|     | 3.4.1  | 3LT-Si configuration                                                       | 48 |  |  |

|     | 3.4.2  | 3LT-SiC configuration                                                      | 49 |  |  |

|     | 3.4.3  | Case study                                                                 | 49 |  |  |

|     | 3.4.4  | Exprimental verification                                                   | 50 |  |  |

| 3   | .5     | Hybrid Voltage Balancing Scheme                                            | 52 |  |  |

|     | 3.5.1  | Principles of novel NP voltage balancing scheme                            | 53 |  |  |

|     | 3.5.2  | Performance evaluation by simulation                                       | 55 |  |  |

|     | 3.5.3  | Experimental verification                                                  | 58 |  |  |

| 3   | .6     | Summary                                                                    | 61 |  |  |

| СНА | PTER - | Modelling of Passive Components                                            | 63 |  |  |

| 4   | .1     | DC-link capacitors                                                         | 63 |  |  |

|     | 4.1.1  | Sizing of DC-link capacitance and DC-link voltage ripple modelling         | 64 |  |  |

|     | 4.1.2  | Volume/weight modelling of DC-link film capacitors                         | 65 |  |  |

|     | 4.1.3  | Case study                                                                 | 66 |  |  |

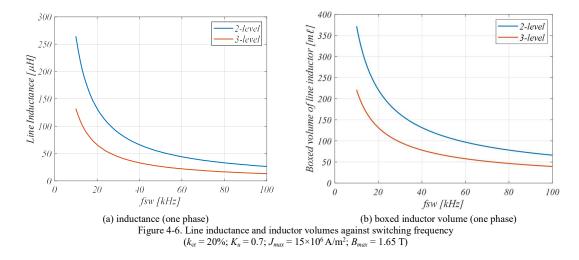

| 4   | .2     | Line inductors                                                             | 68 |  |  |

|     | 4.2.1  | Sizing of line inductance and modelling of ouput current ripple            | 68 |  |  |

|     | 4.2.2  | Design and modelling of line inductors                                     | 69 |  |  |

|     | 4.2.3  | Case study                                                                 | 71 |  |  |

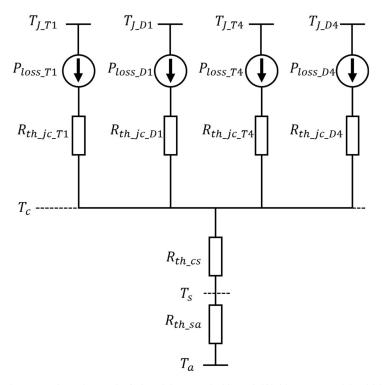

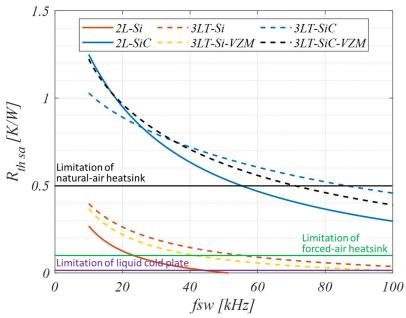

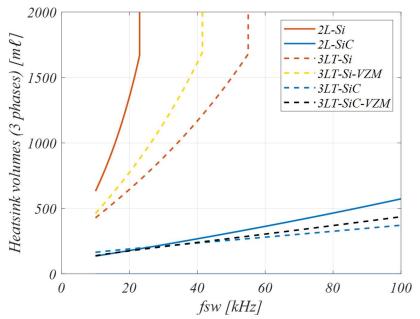

| 4   | .3     | Heatsinks                                                                  | 73 |  |  |

|     | 4.3.1  | Heatsink sizing for power devices                                          | 73 |  |  |

|     | 4.3.2  | Volume/weight modelling of heatsinks                                       | 76 |  |  |

|     | 4.3.3  | Case study                                                                 | 77 |  |  |

| 4   | .4     | Summary                                                                    | 81 |  |  |

| СНА | PTER:  | Power Loss Modelling of Inductors                                          | 83 |  |  |

| 5.   | 1     | Background on inductor core loss modelling                              | 83  |

|------|-------|-------------------------------------------------------------------------|-----|

| 5.2  | 2     | Empirical core loss characterization                                    | 88  |

|      | 5.2.1 | Core loss Measurement                                                   | 88  |

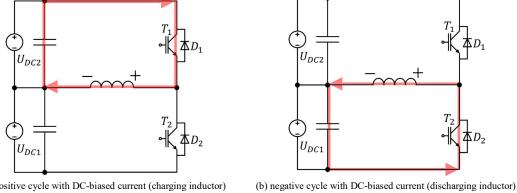

|      | 5.2.2 | Power Converter Configuration                                           | 89  |

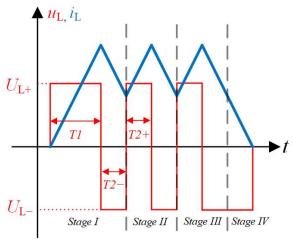

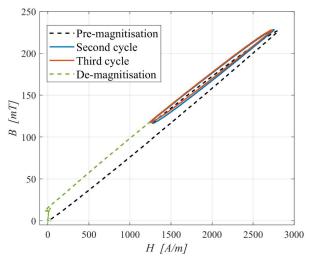

|      | 5.2.3 | Test Procedure – Triple Pulse Test                                      | 92  |

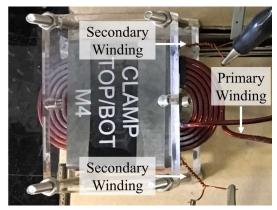

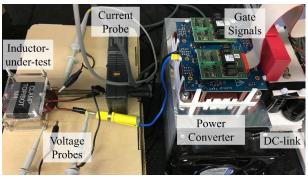

|      | 5.2.4 | Test setup                                                              | 94  |

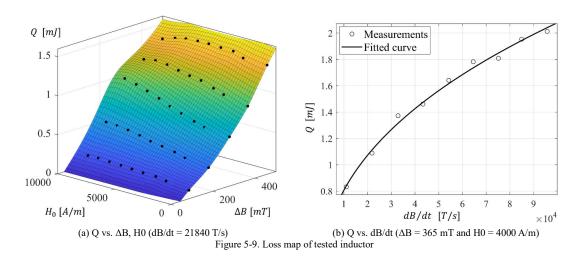

| 5    | 3     | Loss Map Approach                                                       | 96  |

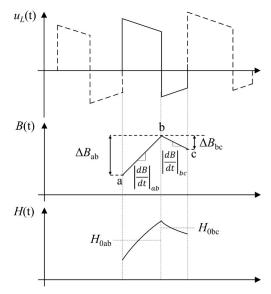

|      | 5.3.1 | Core Loss Calculation for PWM operations                                | 98  |

|      | 5.3.2 | User-Friendly Loss Map and Core Loss Calculation                        | 101 |

| 5.4  | 4     | Analytical loss map inputs for two-level and three-level PWM converters | 104 |

|      | 5.4.1 | Analytical core loss model in a two-level converter                     | 105 |

|      | 5.4.2 | Analytical core loss model in a three-level converter                   | 109 |

| 5.:  | 5     | Analytical copper loss modelling                                        | 111 |

|      | 5.5.1 | AC resistance of windings                                               | 111 |

|      | 5.5.2 | Analytical prediction of voltage/current harmonics                      | 112 |

| 5.0  | 6     | Experimental verification                                               | 113 |

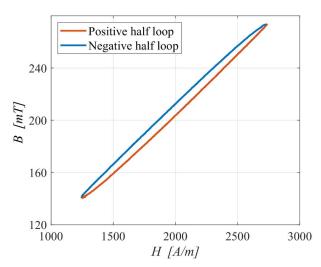

|      | 5.6.1 | Loss map approach and core loss calculation                             | 113 |

|      | 5.6.2 | Analytical loss map inputs for core loss estimation                     | 117 |

| 5.   | 7     | Summary                                                                 | 120 |

| CHAI | PTER  | 6 System-level Trade-off Analysis and Optimisation                      | 122 |

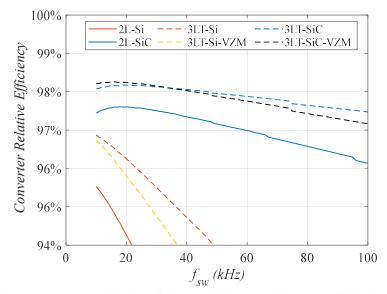

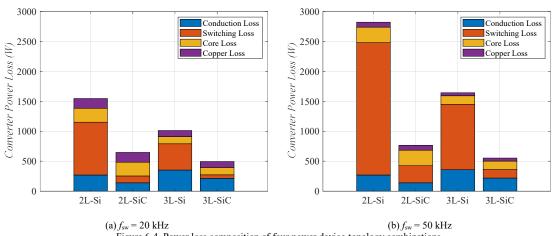

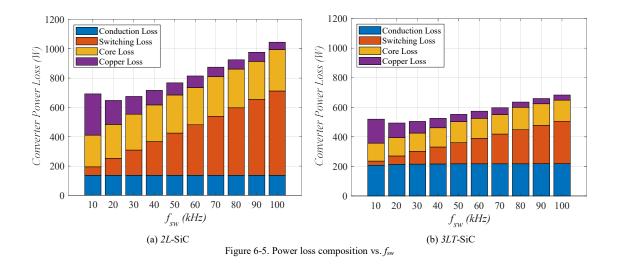

| 6.   | 1     | Efficiency analysis                                                     | 124 |

| 6.2  | 2     | Power density/specific power analysis                                   | 126 |

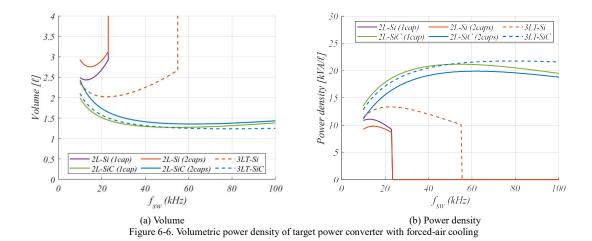

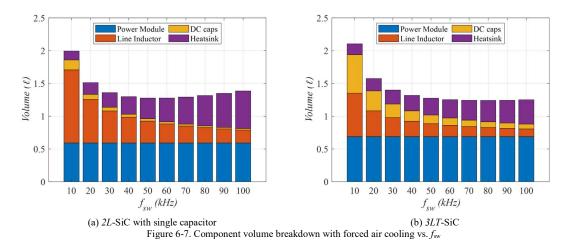

|      | 6.2.1 | Power density with fored-air-cooling                                    | 126 |

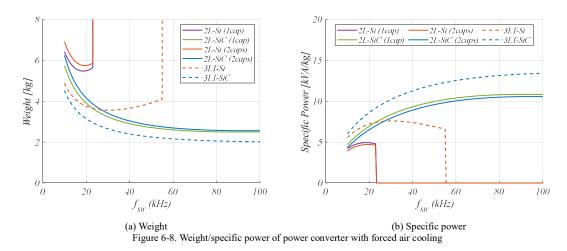

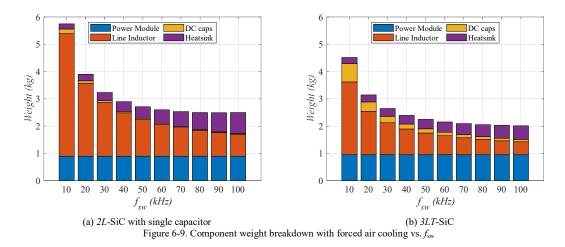

|      | 6.2.2 | Specific power with fored-air-cooling                                   | 128 |

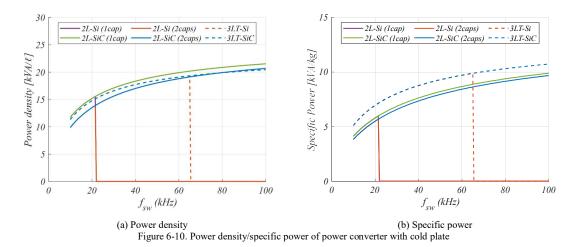

|      | 6.2.3 | Power density/specific power with liquid cold plate                     | 130 |

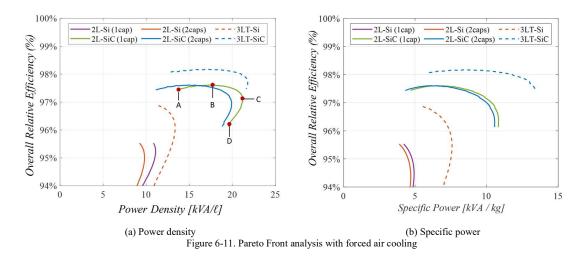

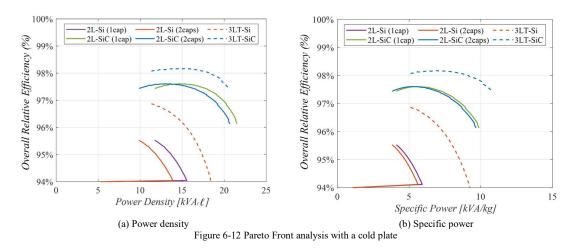

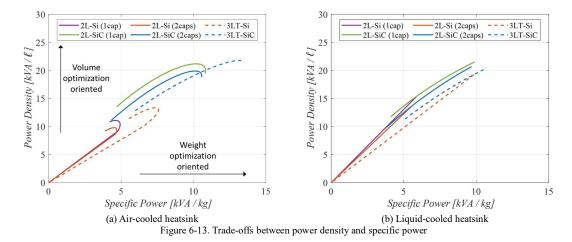

| 6    | 3     | Multi-objective optimisation                                            | 131 |

| 6.4  | 4     | Prototyping                                                             | 134 |

| 6.:  | 5     | Summary                                                                 | 138 |

| CHAI | PTER  | 7 Conclusion & Future work                                              | 140 |

| 7.   | 1     | Summary                                                                 | 140 |

| 7.3  | 2     | Main contributions                                                      | 143 |

| 7.   | 3     | Future work                                                             | 144 |

|      | 7.3.1 | Thermal constraint of inductors                                         | 145 |

|      | 7.3.2 | Power loss profiles of inductors                                        | 145 |

|      | 7.3.3 | EMI filter modelling                                                    | 146 |

| References | S                                            | 147 |

|------------|----------------------------------------------|-----|

| Appendix A | A Analytical averaged loss model expressions | 150 |

| A.1        | Two-level converter                          | 156 |

| Δ2         | Three-level T-type converter                 | 15′ |

## **Abstract**

Moving towards More Electric Aircraft (MEA) demands for high efficiency and high power density power electronics. There are two important areas that are pushing the boundaries of future power converters: advanced converter topologies (e.g. three-level topology) and emerging power semiconductor devices (e.g. Wide Band Gap power devices). The benefits of these new technologies are still subject to quantified analysis from the system level point of view over a particular application.

The aim of this work is to investigate the design trade-offs and optimisation of a 27 kVA three-phase Active Shunt Regulator (ASR) system regarding three main design variables: topology, power device and switching frequency. The emerging technologies, the three-level T-type topology and Silicon Carbide (SiC) devices, are evaluated against the state-of-the-art commercial solution, i.e. Silicon IGBT and two-level topology. To realize a holistic view of the system, not only the active power devices, but also the passive components require designing and accurate modelling. Passive components considered in this work include the heatsinks, the filter inductors and the DC-link capacitors, which account for a substantial contribution to the power loss and volume/weight of the converter system. Power loss models, design procedures and volume/weight models are established for individual components of the ASR system. As the most challenging part, the core loss of inductors is thoroughly investigated and evaluated. Additionally, the neutral point voltage balancing issue in three-level converters is addressed in this work when the ASR system operates at a low power factor.

The developed mathematical optimisation tool shows a prediction on the achievable performance of the converter and the quantified design trade-offs. For example, increasing the switching frequency reduces the size of filter components while it requires larger heatsink for increased switching loss. Prototypes are built to validate the theoretical models and realize the optimal design identified.

## Acknowledgement

I would like to take this opportunity to thank Prof. Xibo Yuan for guiding me with no reservation. I wouldn't be able to go this far without his enthusiastic encouragement and continuous support, both in academic and personal development. I would also like to thank Dr. Dave Drury and Prof. Phil Mellor for their kindness and support throughout my PhD.

Special thanks to my colleague Dr. Kfir Pzenica for kind encouragement and technical discussions. It has been a pleasure to work with him side by side in this project.

I am lucky enough to join the Electrical Energy Management group with the University of Bristol. I have learned so many things from the skilled and talented group members, which include Dr. Yonglei Zhang, Dr. Xu Liu, Dr. Niall Oswald, Dr. Sam Walder, Dr. Apollo Charalambous, Dr. Joanne Kitson, Dr. Jonathan Godbehere, Dr. Harry Dymond, Dr. Jianjing Wang, Dr. Rafal Wrobel, Dr. Sam Williamson, Dr. Jason Yon and Dr. Nick Simpson.

I gratefully appreciate Safran Power UK for generously funding my PhD project. It has been an honour and wonderful learning experience to work closely with Grzegorz Popek, Clive Frederickson, Bushra Hai, Andrew Bloor, Naveed Sheikh and Giovanni Raimondi from Safran Electrical & Power UK, who have been working at the very front of world-class engineering.

I would also like to express my gratitude to Prof. Toshihisa Shimizu, who has shared invaluable insights regarding the core loss modelling topic.

Finally, I want to thank my wife/partner/friend Junxi Yao for her company, love and understanding, in good times and bad times. And I couldn't thank my parents enough for everything. I wish they are proud of me.

## **Declaration**

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

| SIGNED: DA | ATE: |

|------------|------|

|------------|------|

## Memorandum

This PhD thesis with the title "Design Trade-off Analysis and Optimisation of a High-density Active Shunt Regulator for Aircraft" is based on the work carried out by the author as a member of the Electrical Energy Management Group (EEMG) in the Department of Electrical and Electronic Engineering of the University of Bristol. The main contributions claimed by the author are as follows:

- I. Neutral Point balancing scheme for three-level three-phase converters

- a. Proposed an analytical model to analyse the device power losses impacted by Virtual Zero-level

Modulation (VZM), which is a novel control scheme to balance the neutral point voltage.

- b. Experimentally implemented VZM in a test rig and evaluated the power losses.

- Proposed a hybrid NP balancing algorithm integrating VZM and conventional Zero-sequence

Signal Injection to improve the efficiency performance.

### II. Core loss modelling of filter inductors

- a. Proposed a test circuit with the ability to compensate asymmetric amplitude of square-wave inductor voltage caused by power device voltage drops.

- Proposed a discontinuous test procedure aiming at minimized testing process, the Triple Pulse

Test, which reduces the requirement/stress of the hardware in the testing.

- c. The power loss of a customized high-power-density inductor based on Cobalt Iron alloys is experimentally characterized with the proposed approach.

- d. Proposed a user-friendly loss map for straightforward calculation of the inductor core loss.

- e. Proposed an analytical approach to estimate the inductor core loss for given PWM operation of the power converter. The analytical model is developed on both two-level and three-level converters.

- III. System-level trade-off analysis and optimisation of a 27 kVA Active Shunt Regulator system

### **Publications**

### **Journal Publications**

J. Wang, K.J. Dagan, X. Yuan, W. Wang and P.H. Mellor, "A Practical Approach for Core Loss Estimation of a High-current Gapped Inductor in PWM Converters with a User-friendly Loss Map", *IEEE Transactions* on Power Electronics, vol. 34, no. 6, pp. 5697–5710, Jun. 2019

### **Conference Publications**

- J. Wang, X. Yuan, Y. Zhang, K.J. Dagan, X. Liu, D. Drury, P.H. Mellor and A. Bloor, "Analytical Averaged Loss Model of Three-Phase T-type NPC STATCOM with Virtual Zero Voltage Level Synthesis Modulation," in *Proceedings of IEEE Energy Conversion Congress and Exposition (ECCE)*, 2017

- J. Wang, X. Yuan, K.J. Dagan, P.H. Mellor, D. Drury and A. Bloor, "Universal Neutral Point Balancing Algorithm for Three-phase Three-level Converters with Hybrid of Zero-sequence Signal Injection and Virtual Zero-level Modulation" in *Proceedings of IEEE Energy Conversion Congress and Exposition (ECCE)*, 2018

- 3. **J. Wang**, K.J. Dagan, X. Yuan, "An Efficient Analytical Inductor Core Loss Calculation Method for Two-level and Three-level PWM Converters based on a User-friendly Loss Map" in *Proceedings of IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2019

# **List of Symbols**

| A            | Area                                                                  | $m^2$       |

|--------------|-----------------------------------------------------------------------|-------------|

| $A_c$        | Cross section area of the magnetic core                               | $m^2$       |

| $A_{cu}$     | Cross section area of copper conductor                                | $m^2$       |

| $A_p$        | Area product                                                          | $m^2$       |

| В            | Magnetic flux density                                                 | T           |

| $B_{DC}$     | DC component of magnetic flux density                                 | T           |

| $B_m$        | Amplitude of the ac component of magnetic flux density                | T           |

| $B_{pk}$     | Peak value of total magnetic flux density ( $B_{pk} = B_{DC} + B_m$ ) | T           |

| $B_{sat}$    | Saturation flux density                                               | T           |

| C            | Capacitance                                                           | F           |

| D            | Duty cycle (0~1)                                                      |             |

| $E_{sw}$     | Switching energy                                                      | J or mJ     |

| $f_0$        | Fundamental frequency                                                 | Hz          |

| $F_R$        | Winding resistance factor                                             |             |

| $f_{sw}$     | Switching frequency (carrier frequency)                               | Hz          |

| Н            | Magnetic Field Strength                                               | A/m         |

| I            | Current                                                               | A           |

| J            | Current density                                                       | $A/m^2$     |

| $J_n(x)$     | Bessel function of order n and argument x                             |             |

| $k_{sw}$     | Switching loss factor                                                 |             |

| L            | Inductance                                                            | Н           |

| M            | Modulation index                                                      |             |

| MTL          | Mean Turn Length of the inductor windings                             | m           |

| N1/N2        | Number of turns (primary winding/secondary winding)                   |             |

| P            | Power                                                                 | W or kW     |

| $R_{on}$     | On-state resistance                                                   | Ω           |

| $R_{th}$     | Thermal resistance                                                    | K/W or °C/W |

| $R_{wac}$    | Winding total equivalent resistance considering AC effects            | Ω           |

| $R_{wdc}$    | Winding DC resistance                                                 | Ω           |

| $T_{\theta}$ | Period of a fundamental cycle                                         | S           |

| $T_a$        | Ambient temperature                                                   | °C          |

| $T_{j}$      | Junction temperature                                                  | °C          |

| $T_{sw}$     | Switching period                                                      | S           |

| U            | Voltage                                                               | V           |

| V          | Volume                     | $m^3$ or $\ell$  |

|------------|----------------------------|------------------|

| W          | Weight                     | kg               |

| γ          | Specific power             | kVA/kg           |

| η          | (relative) Efficiency      |                  |

| $\mu_0$    | Permeability of free space | H/m              |

| $\mu_r$    | Relative permeability      |                  |

| ρ          | Power density              | kVA/ $\ell$      |

| $ ho_{cu}$ | Conductivity of copper     | $\Omega{\cdot}m$ |

| $\varphi$  | Power factor angle         | deg or rad       |

|            |                            |                  |

## **List of Abbreviations and Acronyms**

2L Two-level 3L Three-level

3LT Three-level T-type AC Alternating Current APU Auxiliary Power Unit ASR Active Shunt Regulator

CM Common Mode

CoFe Cobalt Iron

CSPI Cooling System Performance Index

DCDirect CurrentDMDifferential ModeDPTDouble Pulse Test

DSP Digital Signal Processor

EMF Electromotive force

EMI Electromagnetic Interference

FACTS Flexible AC Transmission System

FFT Fast Fourier Transform

IGBT Insulated Gate Bipolar Transistor

IGSE Improved Generalised Steinmetz Equation

MEA More Electric Aircraft

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NP Neutral Point

NPC Neutral Point Clamped

PFC Power Factor Correction

PM Permanent Magnet

PWM Permanent Magnet Generator

PWM Pulse Width Modulation

RMS Root Mean Square

SE Steinmetz Equation

Si Silicon

SiC Silicon Carbide

SPWM Sinusoidal Pulse Width Modulation

STATCOM Static Synchronous Compensator

TPT Triple Pulse Test

VS Variable Speed

VSC Voltage Source Converter

VSG Variable Speed Generator

VZM Virtual Zero-level Modulation

WBG Wide Band Gap

WFG Wound Field Generator

ZSI Zero-sequence Signal Injection

# **List of Figures**

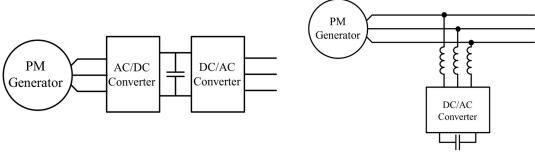

| Figure 1-1. Candidate PM generator/power converter configurations                                                           | 2  |

|-----------------------------------------------------------------------------------------------------------------------------|----|

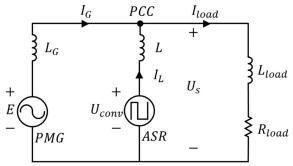

| Figure 1-2. Phasor diagram of the loaded ASR system                                                                         | 4  |

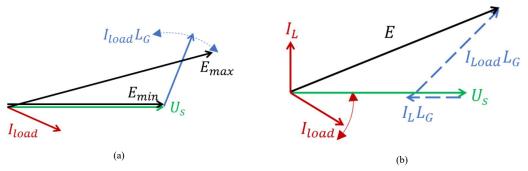

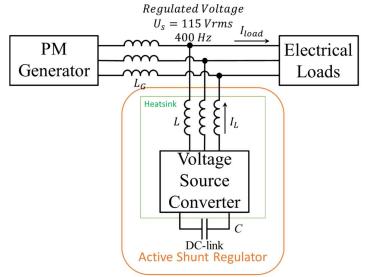

| Figure 1-3. Active Shunt Regulator system for the PM generator based power generation system                                | 5  |

| Figure 1-4. Converter topology concept                                                                                      | 8  |

| Figure 1-5. Four considered device-topology combinations                                                                    | 13 |

| Figure 1-6. Footprint of selected reference power modules                                                                   | 13 |

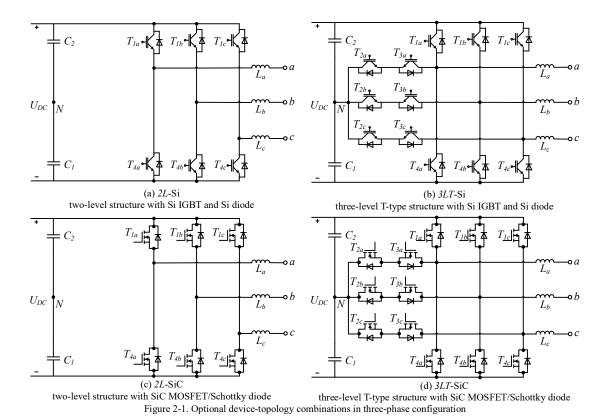

| Figure 2-1. Optional device-topology combinations in three-phase configuration                                              | 19 |

| Figure 2-2. Generic model of a three-phase Voltage Source Converter                                                         | 19 |

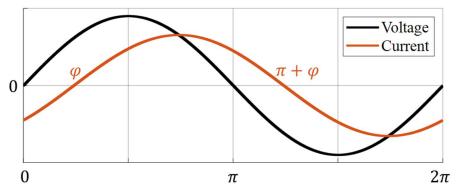

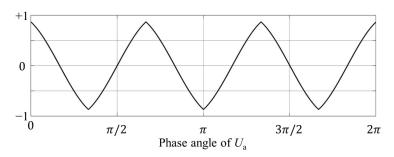

| Figure 2-3. Phase reference voltage and load current of the power converter (fundamental frequency)                         | 20 |

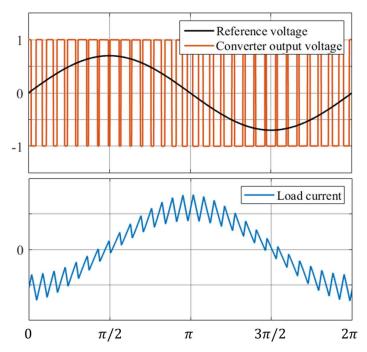

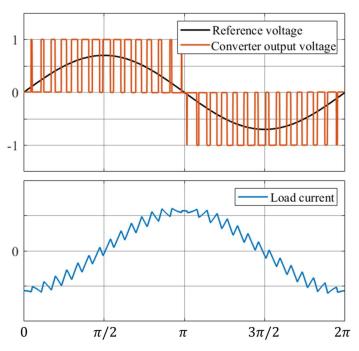

| Figure 2-4. Voltage/current waveforms of a two-level phase leg with SPWM ( $\varphi = \pi/2$ )                              | 24 |

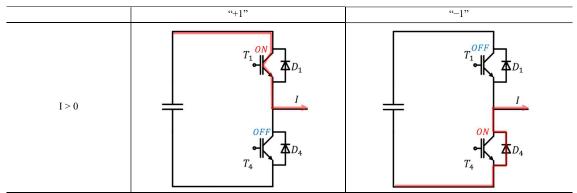

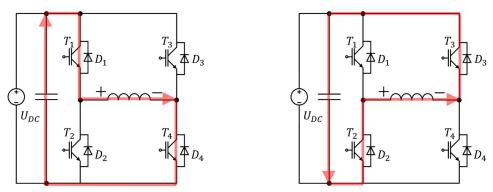

| Figure 2-5. Example of conduction and commutation states of the two-level topology (IGBT based)                             | 25 |

| Figure 2-6. Voltage/current waveforms of a three-level phase leg with SPWM ( $\varphi = \pi/2$ )                            | 28 |

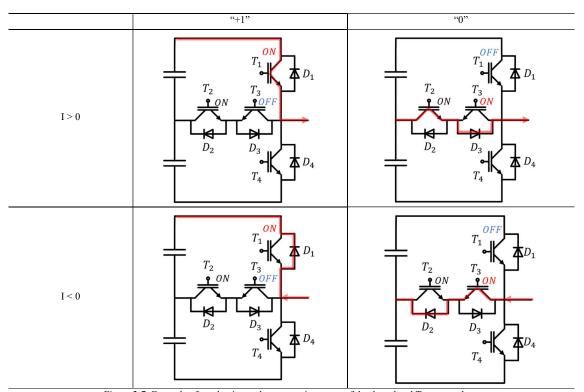

| Figure 2-7. Example of conduction and commutation states of the three-level T-type topology                                 | 29 |

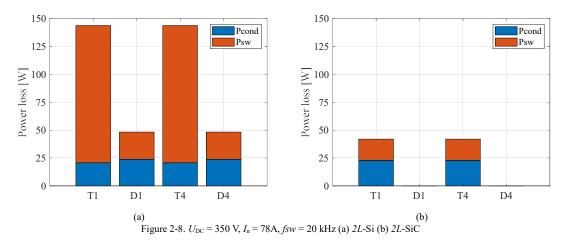

| Figure 2-8. $U_{DC} = 350 \text{ V}$ , $I_n = 78 \text{A}$ , $fsw = 20 \text{ kHz}$ (a) $2L\text{-Si}$ (b) $2L\text{-Si}$ C | 32 |

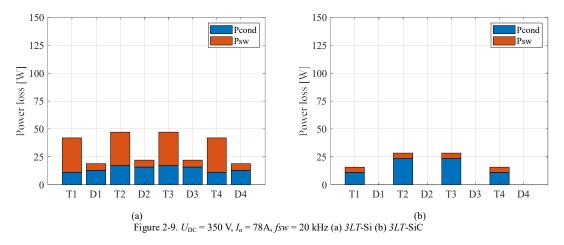

| Figure 2-9. $U_{DC} = 350 \text{ V}, I_n = 78 \text{A}, fsw = 20 \text{ kHz (a) } 3LT\text{-Si (b) } 3LT\text{-Si C}$       | 33 |

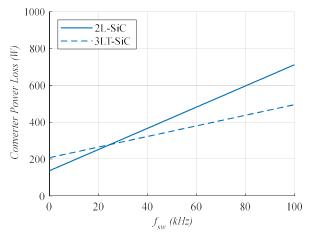

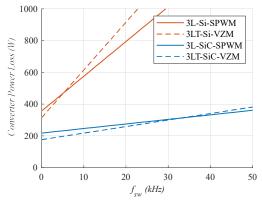

| Figure 2-10. Converter power loss (2L-SiC and 3LT-SiC) against fsw                                                          | 33 |

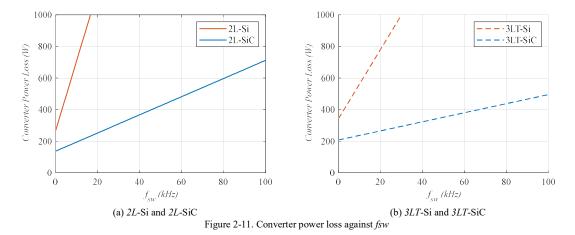

| Figure 2-11. Converter power loss against fsw                                                                               | 34 |

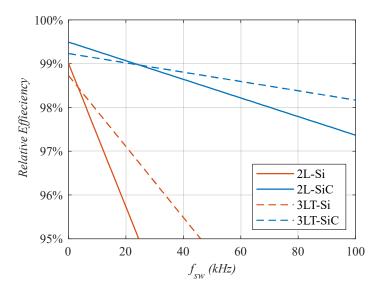

| Figure 2-12 Converter relative efficiency against fsw considering power devices                                             | 35 |

| Figure 3-1. Illustration of the neutral point current $i_{NP}$                                                              | 39 |

| Figure 3-2. Example of uncontrolled, filtered neutral point current normalized to peak load current                         | 40 |

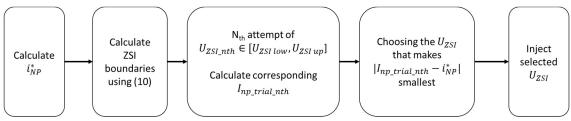

| Figure 3-3. Process of ZSI to balance the neutral point voltage                                                             | 42 |

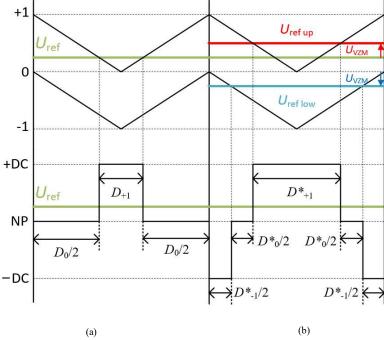

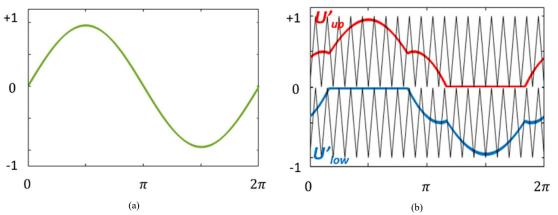

| Figure 3-4. Multilevel-carrier-based modulation ( $U_{ref} > 0$ ) (a) SPWM (b) VZM                                          | 43 |

| Figure 3-5. Strategy of using VZM to balance the neutral point voltage                                                      | 43 |

| Figure 3-6. Modulating waves (a) original SPWM (b) Split modulating waves with $U_{VZM}$ injected                           | 45 |

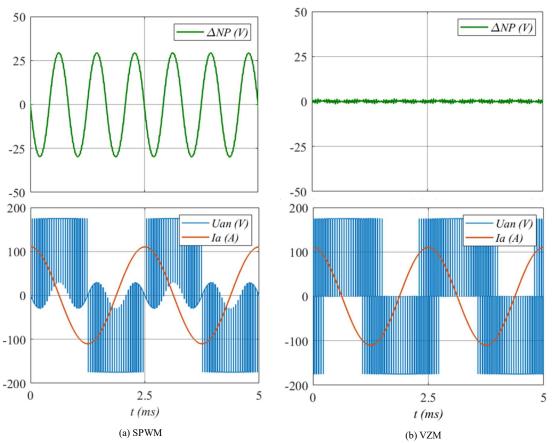

| Figure 3-7. Simulation waveform of the three-phase three-level system                                                       | 46 |

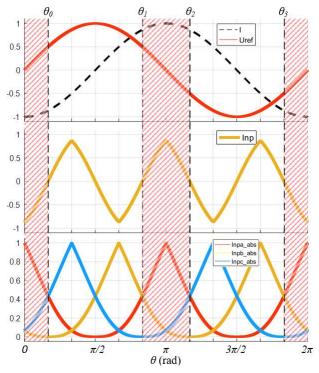

| Figure 3-8. VZM activated intervals when $\varphi = \pi/2$                                                                  | 47 |

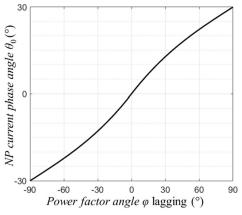

| Figure 3-9. NP current angle $\theta_0$ as a function of power factor angle $\varphi$ (lagging)                             | 47 |

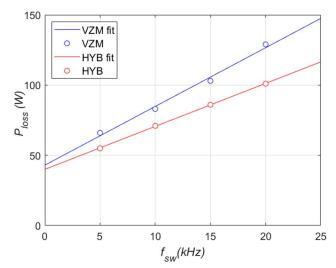

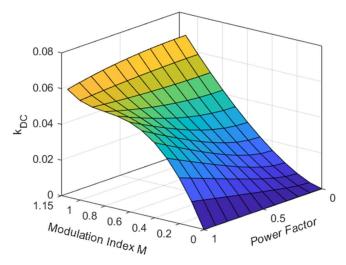

| Figure 3-10. Converter power loss vs. switching frequency                                                                   | 50 |

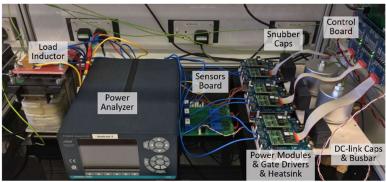

| Figure 3-11. Test Rig 1                                                                                                     | 51 |

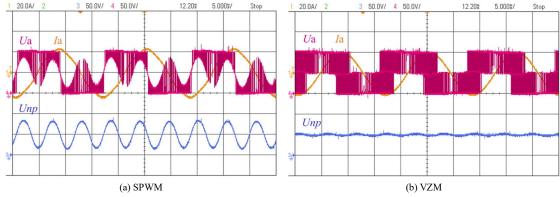

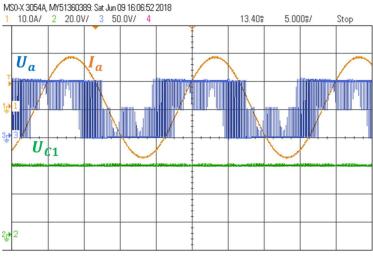

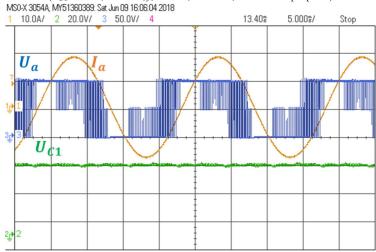

| Figure 3-12. Experimental waveforms                                                                                         | 51 |

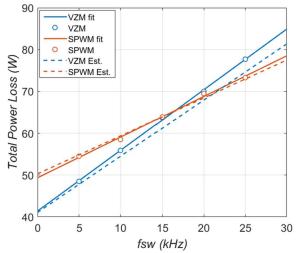

| Figure 3-13. Experimental converter power loss vs. theoretical estimation $(T = 25^{\circ}\text{C})$                        | 52 |

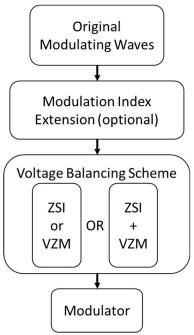

| Figure 3-14. Top-level control scheme                                                                                       | 53 |

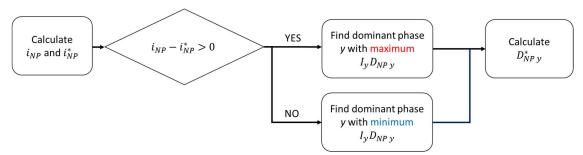

| Figure 3-15. Proposed hybrid voltage balancing scheme                                                                       | 54 |

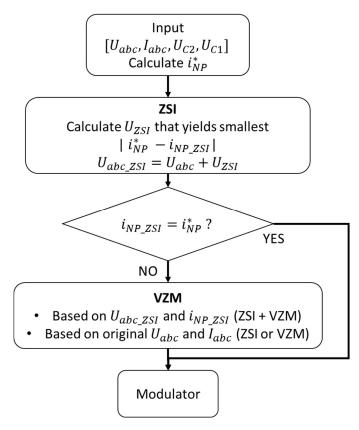

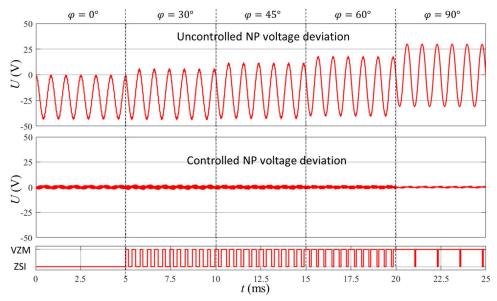

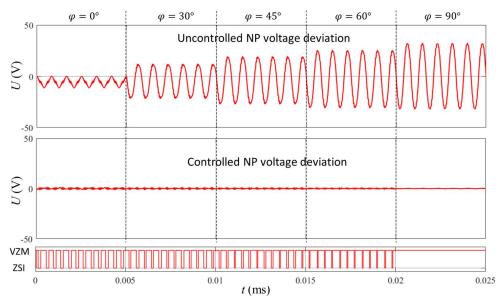

| Figure 3-16. Uncontrolled NP voltage; controlled NP voltage; switching between ZSI and VZM, M = 1                           | 55 |

| Figure 3-17. Uncontrolled NP voltage; controlled NP voltage; switching between ZSI and VZM, M = 1.15                        | 56 |

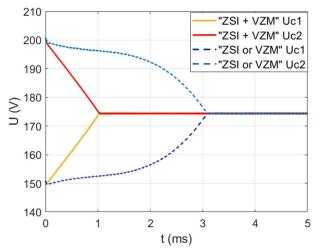

| Figure 3-18. Dynamic balancing performace, "ZSI + VZM" vs. "ZSI or VZM"                                                     | 56 |

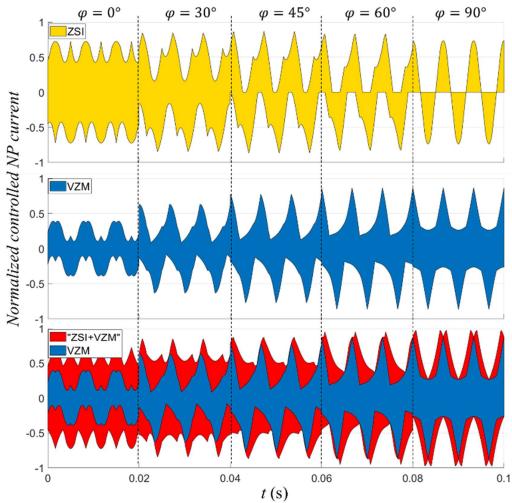

| Figure 3-19. Achievable NP current under various control schemes, M = 0.85                                                  | 58 |

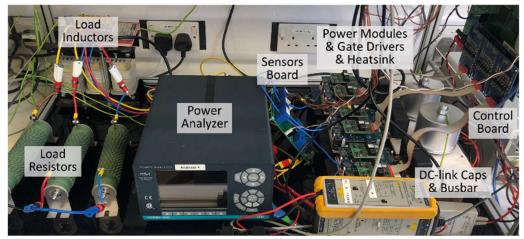

| Figure 3-20. Test rig 2                                                                                                     | 59 |

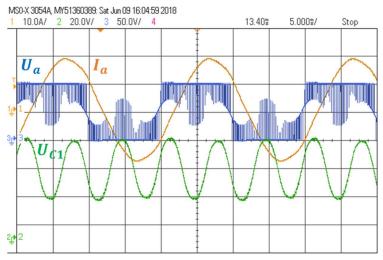

| Figure 3-21. Experimental waveforms with SPWM                                                                               | 59 |

| Figure 3-22. Experimental waveforms with VZM                                                                                | 60 |

| Figure 3-23. Experimental waveforms with proposed hybrid scheme                                                                    | 60  |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3-24. Comparison of power loss measured experimentally                                                                      | 61  |

| Figure 4-1. High-frequency ripple voltage factor in VSC with SPWM                                                                  | 65  |

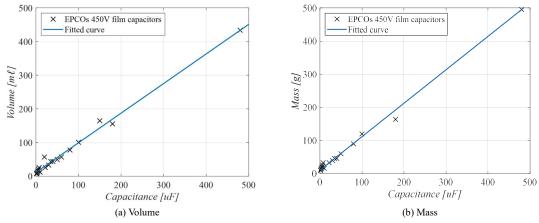

| Figure 4-2. Volume/mass of capacitor with respect to capacitance                                                                   | 66  |

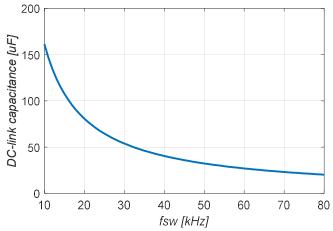

| Figure 4-3. DC-link capacitance vs. switching frequency ( $k_{vr}$ = 1%)                                                           | 67  |

| Figure 4-4. Total volume of DC-link capacitors vs. switching frequency $(k_{vr} = 1\%)$                                            | 67  |

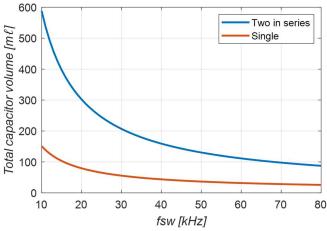

| Figure 4-5. Illustration of EE core Reprinted from [108]                                                                           | 69  |

| Figure 4-6. Line inductance and inductor volumes against switching frequency                                                       | 72  |

| Figure 4-7. Customized inductor with EE cores made from CoFe alloys                                                                | 73  |

| Figure 4-8. Thermal network of a heatsink mounted with one half-bridge power module with base plate                                | 74  |

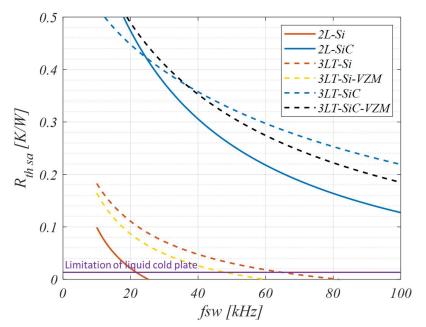

| Figure 4-9. Required thermal resistance with $T_a = 40  ^{\circ}\text{C}$ .                                                        | 78  |

| Figure 4-10. Air-cooled heatsink volumes (CSPI = 17.7 W/K·litre)                                                                   | 79  |

| Figure 4-11. Required thermal resistance with $T_{\rm a}$ = 80 °C                                                                  | 80  |

| Figure 4-12. Customized aluminum cold plate                                                                                        | 81  |

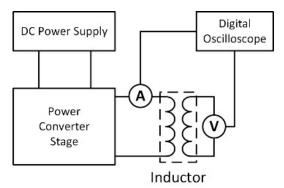

| Figure 5-1. Overview of the B-H loop test system                                                                                   | 88  |

| Figure 5-2. Typical inductor voltage/current waveforms for B-H loop measurement with DC-biased current                             | 89  |

| Figure 5-3. H-bridge test circuit                                                                                                  | 90  |

| Figure 5-4. Half bridge test circuit                                                                                               | 91  |

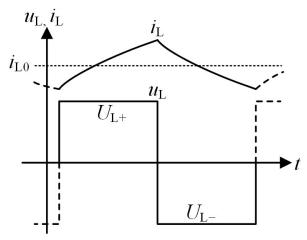

| Figure 5-5. Inductor current/voltage waveform of Triple Pulse Test                                                                 | 93  |

| Figure 5-6. Example of measured B-H trajectory from Triple Pulse Test (H0 $\approx$ 2000 A/m, $\Delta$ B $\approx$ 130 mT)         | 94  |

| Figure 5-7. The tested inductor with added secondary windings for TPT                                                              | 95  |

| Figure 5-8. Test rig no. 3: B-H loop measurement                                                                                   | 95  |

| Figure 5-9. Loss map of tested inductor                                                                                            | 98  |

| Figure 5-10. Typical waveforms of the filter inductor with a single-phase two-level PWM converter                                  | 98  |

| Figure 5-11. Example of a measured B-H loop excited by symmetric square wave with DC-bias                                          | 99  |

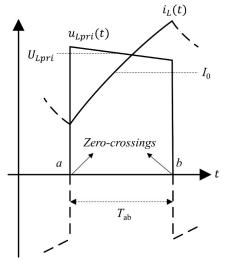

| Figure 5-12. Example of half-loop segment ab with only electrical and time-domain measurements                                     | 101 |

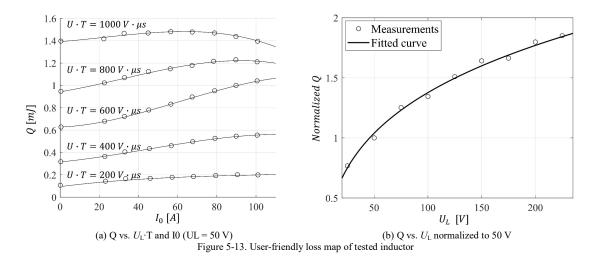

| Figure 5-13. User-friendly loss map of tested inductor                                                                             | 103 |

| Figure 5-14. Core loss calculation flow for a given voltage/current waveform                                                       | 104 |

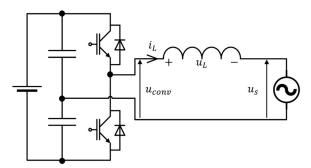

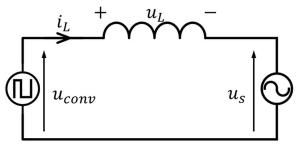

| Figure 5-15. Grid-tied single-phase two-level converter                                                                            | 105 |

| Figure 5-16. Equivalent circuit for core loss calculation                                                                          | 105 |

| Figure 5-17. Two-level inverter with a passive load and low-pass LC filter                                                         | 106 |

| Figure 5-18. Phasor diagram of converter with RLC load at fundamental frequency                                                    | 106 |

| Figure 5-19. Example of a two-level converter in one switching window ( $U_{\text{ref}} > 0$ )                                     | 106 |

| Figure 5-20 Analytical core loss computation process.                                                                              | 108 |

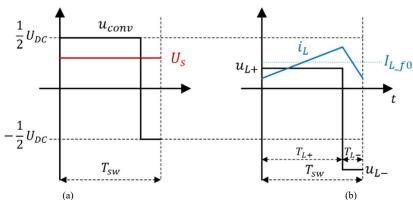

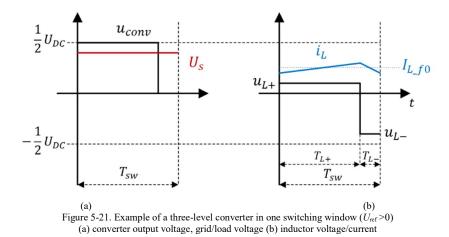

| Figure 5-21. Example of a three-level converter in one switching window ( $U_{\text{ref}} > 0$ )                                   | 110 |

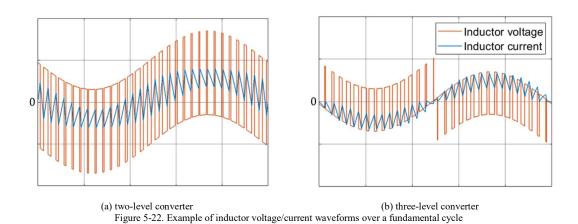

| Figure 5-22. Example of inductor voltage/current waveforms over a fundamental cycle                                                | 110 |

| Figure 5-23. Single -phase two-level inverter.                                                                                     | 113 |

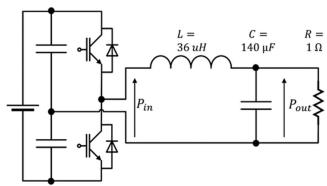

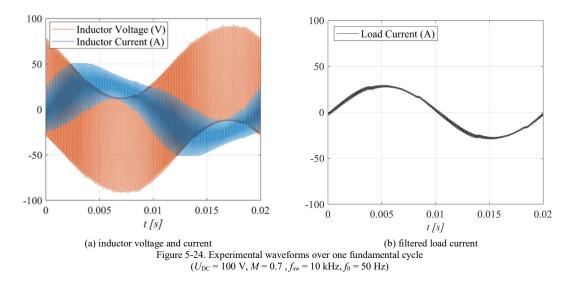

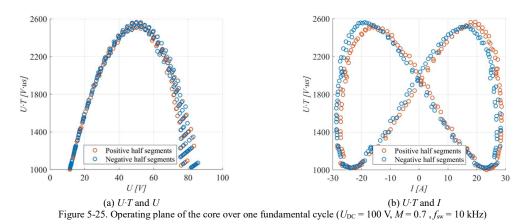

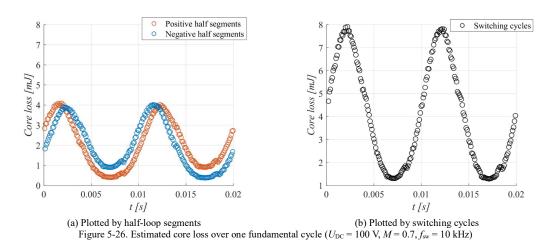

| Figure 5-24. Experimental waveforms over one fundamental cycle                                                                     | 114 |

| Figure 5-25. Operating plane of the core over one fundamental cycle ( $U_{\rm DC}$ = 100 V, $M$ = 0.7 , $f_{\rm sw}$ = 10 kHz)     | 114 |

| Figure 5-26. Estimated core loss over one fundamental cycle ( $U_{\rm DC} = 100 \text{ V}, M = 0.7, f_{\rm sw} = 10 \text{ kHz}$ ) | 115 |

| Figure 5-27. Experimental results of inductor losses over one fundamental cycle (0.02 s)                                           | 116 |

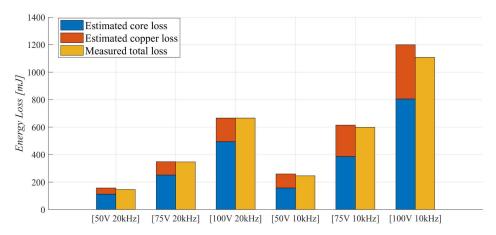

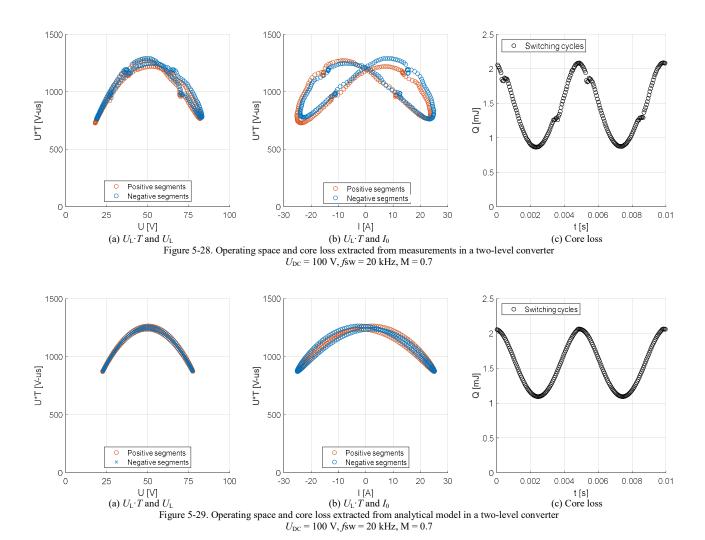

| Figure 5-28. Operating space and core loss extracted from measurements in a two-level converter                                    | 118 |

| Figure 5-29. Operating space and core loss extracted from analytical model in a two-level converter                                | 118 |

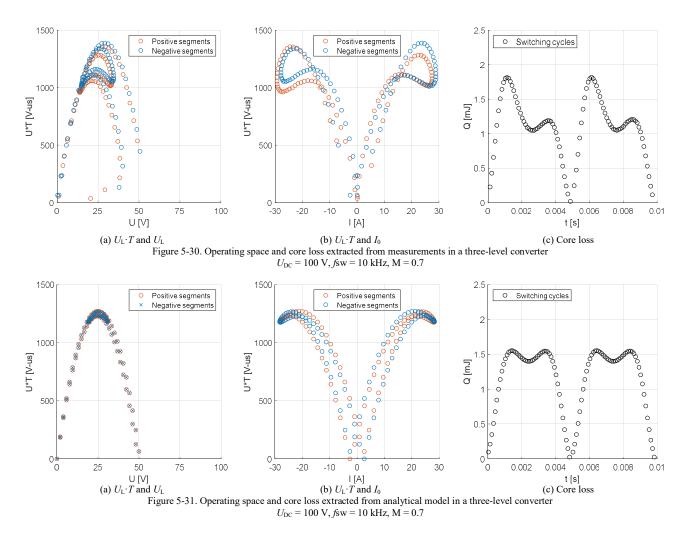

| Figure 5-30. Operating space and core loss extracted from measurements in a three-level converter                                  | 119 |

| Figure 5-31. Operating space and core loss extracted from analytical model in a three-level converter      | 119 |

|------------------------------------------------------------------------------------------------------------|-----|

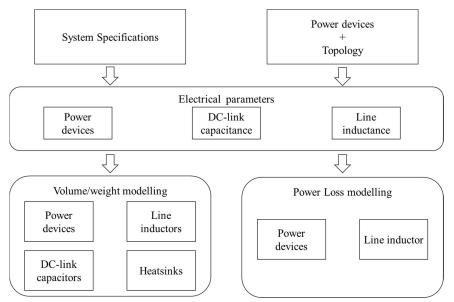

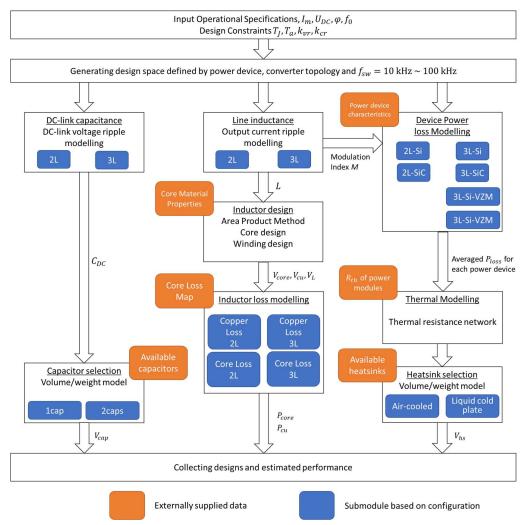

| Figure 6-1. Overview of system-level trade-off analysis                                                    | 122 |

| Figure 6-2. Process of analytical design optimisation.                                                     | 123 |

| Figure 6-3. Converter overall relative efficiency considering power device losses and line inductor losses | 124 |

| Figure 6-4. Power loss composition of four power device-topology combinations                              | 125 |

| Figure 6-5. Power loss composition vs. $f_{sw}$                                                            | 126 |

| Figure 6-6. Volumetric power density of target power converter with forced air cooling                     | 127 |

| Figure 6-7. Component volume breakdown with forced air cooling vs. $f_{sw}$                                | 128 |

| Figure 6-8. Weight/specific power of power converter with forced air cooling                               | 129 |

| Figure 6-9. Component weight breakdown with forced air cooling vs. $f_{sw}$                                | 129 |

| Figure 6-10. Power density/specific power of power converter with cold plate                               | 131 |

| Figure 6-11. Pareto Front analysis with forced air cooling                                                 | 132 |

| Figure 6-12 Pareto Front analysis with a cold plate                                                        | 133 |

| Figure 6-13. Trade-offs between power density and specific power                                           | 134 |

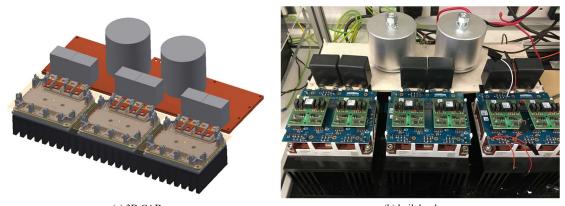

| Figure 6-14. Prototype I: 3LT-Si prototype with power module SKiM301TMLI12E4B                              | 135 |

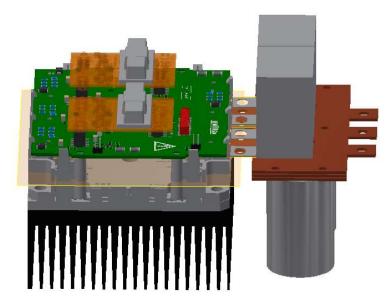

| Figure 6-15. Virtual view of designed single-phase three-level converter                                   | 135 |

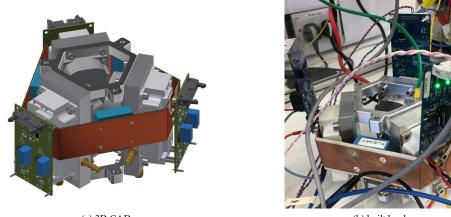

| Figure 6-16. Prototype II:2L-SiC prototype with power module CAS300M12BM2 and liquid cold plates           | 136 |

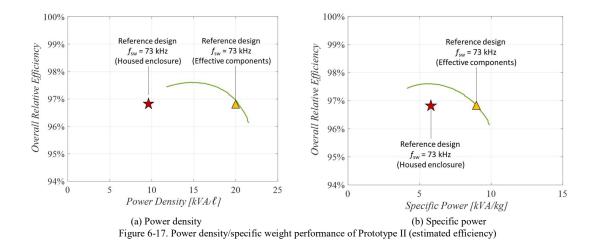

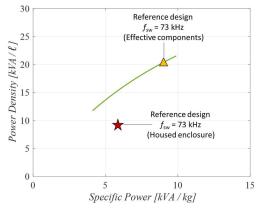

| Figure 6-17. Power density/specific weight performance of Prototype II (estimated efficiency)              | 136 |

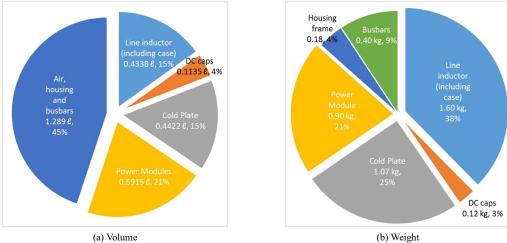

| Figure 6-18. Volume/weight contribution of each component in Prototype II                                  | 137 |

| Figure 6-19. Volume/weight performance of Prototype II                                                     | 137 |

# **List of Tables**

| Table 1-1. Specifications of the ASR system                                                  | 5   |

|----------------------------------------------------------------------------------------------|-----|

| Table 2-1. Switching states in a two-level converter                                         | 24  |

| Table 2-2. Device conduction functions (2L-Si)                                               | 26  |

| Table 2-3. Switching loss energies (2L-Si)                                                   | 26  |

| Table 2-4. Device switching intervals (2L-Si)                                                | 26  |

| Table 2-5. Device Conduction intervals (2L-SiC)                                              | 27  |

| Table 2-6. Switching states in a three-level T-type converter                                | 29  |

| Table 2-7. Output voltage levels in 3L topology and duty cycles with SPWM                    | 29  |

| Table 2-8. Devices conduction functions (3LT-Si)                                             | 30  |

| Table 2-9. Switching loss energies (3LT-Si)                                                  | 31  |

| Table 2-10. Device switching intervals (3LT-Si)                                              | 31  |

| Table 2-11. Devices conduction functions (3LT-SiC)                                           | 31  |

| Table 2-12. Device characteristics extracted from datasheet ( $T_j = 150 ^{\circ}\text{C}$ ) | 32  |

| Table 3-1. Specifications of a statcom system                                                | 45  |

| Table 3-2. Device conduction intervals applying VZM (3LT-Si)                                 | 48  |

| Table 3-3. Device switching intervals applying VZM (3LT-Si)                                  | 48  |

| Table 3-4. Device conduction intervals applying VZM (3LT-SiC)                                | 49  |

| Table 3-5. Comparison of total converter power loss (T-type, SiC, 10 kHz)                    | 49  |

| Table 3-6. Specifications of downscaled test rig                                             | 51  |

| Table 3-7 Simulation parameters of the ASR system                                            | 55  |

| Table 3-8. Components in the downscaled test rig 2                                           | 58  |

| Table 4-1. Relative dimensions of one design of EE cores                                     | 71  |

| Table 4-2. Thermal parameters of power modules                                               | 76  |

| Table 5-1. Comparison between DPT and TPT                                                    | 94  |

| Table 5-2. Specifications of the inductor under test                                         | 95  |

| Table 5-3. Instruments and components in the test rig                                        | 96  |

| Table 5-4. Specifications of Test Rig 4                                                      | 117 |

| Table 5-5. Comparison of averaged core loss                                                  | 119 |

| Table 6-1. Design Inputs                                                                     | 123 |

## **CHAPTER 1**

## **Application Background and Research Aims**

### 1.1 More Electric Aircraft (MEA) and electrical power generation in aircraft

More Electric Aircraft (MEA) is the current trend in modern aircrafts which aims to increase the use of electrical power systems that fully or partially replaces the conventional mechanical, hydraulic and pneumatic power systems [1]–[7]. MEA offers several attractive benefits, such as increased reliability, reduced complexity and lower installation and maintains cost [7], [8]. The electrification of aviation also leads to low-emission, low-energy-consumption and low-noise aircrafts that attract prioritized interests and resources from the governments and the industry [9], [10]. Moving towards MEA demands for increased on-board electric power generation. In current aircrafts, Variable Speed (VS) system is the preferred option for electrical power generation due to its simplicity, reliability and better flexibility [11]–[13]. For example, the latest Boeing 787 is equipped with four 250-kVA Variable Speed Generators (VSGs) as the main source of electric power generation [5], [11]. VS based aircraft electric systems show promising advances and implementations in the past decades [13], [14], in which the core components are the electric machines and power electronics [2], [6]. As the advances of aircrafts constantly call for the reduction of weight and volume, advanced technologies for the electric machines and power electronics are being actively explored to achieve better performance.

### 1.2 Permanent Magnet Generator (PMG) with an Active Shunt Regulator (ASR)

For future MEA, the power density of the electric machine is predicted to advance to 10 kVA/kg by 2025, and 20 kVA/kg by 2035 [11], [15]. As the VSG in the VS system, three-stage Wound Field Generators (WFG) are

the most commonly used option on commercial and military aircrafts [16]. However, WFGs are limited in power density because they cannot run at a very high speed due to the complex rotor windings. To achieve a higher power density, Permanent Magnet (PM) machines are considered a better option for future high-power generation systems on aircrafts. Permanent Magnet Generator (PMG) features many advantages compared to the WFG [7], [11], [17]:

- High power density (e.g. 3.3 16 kVA/kg)

- High efficiency throughout the frequency range (e.g. loss-less excitation, low rotor loss)

- Simple, robust construct and improved reliability

Due to the fixed excitation of a PM machine, the operation of a PM generator requires Pulse Width Modulation (PWM) power electronics converters to regulate the terminal voltage [16]–[18]. There are two options for the PM generator/converter configurations as shown in Figure 1-5.

(a) Back-to-back converter (b) Active Shunt Regulator

Figure 1-1. Candidate PM generator/power converter configurations

The back-to-back structure in Figure 1-5(a) can be considered as the state-of-the-art [11], [19], [20], in which the power converter is formed by a rectifier end and an inverter end with an internal DC-link. As the main advantage, this back-to-back converter can accommodate a wide speed range of the generator and has the ability to turn off the output voltage. The main disadvantage of the back-to-back configuration is the lower efficiency and lower power density as a result of the two-stage conversion.

In this work, the power generation system is considered in an Auxiliary Power Unit (APU) system with a shaft speed of 400±5 Hz. Because the shaft speed is relatively constant in this case, an Active Shunt Regulator (ASR) configuration shown in Figure 1-1(b) is considered. The ASR system has a simpler structure and potentially offers better efficiency and power density with less power electronics components required. The parallel power converter is a Voltage Source Converter (VSCs) that export capacitive/inductive reactive power to the coupled AC grid to regulate the generator output voltage. A circuit diagram of the target power generation system is shown in Figure 1-2.

Figure 1-2. Circuit diagram of a power generation system with PMG, ASR and RL load

Where E is the induced EMF of the generator;  $I_{\rm L}$  is the ASR output current;  $I_{\rm load}$  is the load current;  $I_{\rm G}$  is the generator output current;  $U_{\rm conv}$  is ASR output voltage;  $U_{\rm s}$  is the regulated generator terminal voltage. Figure 1-3 illustrates a comparison of the operation principle between WFG system and a PMG/ASR system. A WFG operates with the adjustable excitation to adapt to the load condition, while the PMG relies on the ASR to regulate the output voltage.

Figure 1-3. Phasor diagram of a loaded (a) WFG (b)PMG

From the ASR point of view, the ideal power converter only inject/absorb reactive power to regulate the

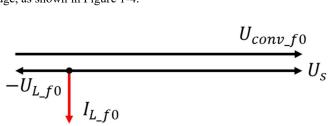

generator terminal voltage, as shown in Figure 1-4.

Figure 1-4. Phasor diagram of the loaded ASR system

Where  $U_{\text{conv\_0}}$  is the fundamental-frequency voltage generated by the ASR;  $I_{\text{L}}$  and  $U_{\text{L}}$  are the voltage and current on the line inductor. The operation principle of the ASR is similar to a Static Synchronous Compensator (STATCOM). STATCOMs are widely employed in AC power grid applications as reactive power compensators [21], which play an important role in Flexible AC Transmission System (FACTS) [22]. There are also examples applying STATCOMs to regulate the terminal voltage for self-excited induction generators [23] and PMGs for wind power generation [24]. Due to the distributed load on the aircraft, the Point of Common Coupling (PCC) for the shunt regulation is defined as the generator output terminal voltage. The regulated generator output terminal voltage must comply with the MIL-STD-704 standard [25]. Differently, the PCC in a typical STATCOM system is defined to be close to the load end. Because the PM + ASR configuration for aircrafts is relatively novel at the time of this work, there is only limited research can be found in the literatures while its performance is still under evaluation both in academia and industry.

The electrical systems on an aircraft have various specifications. As the widely adopted standard since 1950s, the 115/200 V AC system with a frequency of 400 Hz is commonly used for modern aircrafts such as Airbus A380-800 [11]. This work intends to develop PMG system to provide a like-to-like comparison with an existing 45 kVA, 115V WFG system that has been characterized. Therefore, a PMG/ASR system with 45 kVA continuous output and 115 Vrms regulated voltage has been designed in this project. Considering the predefined load condition in the target system, a 27-kVA rated ASR is designed as the subject of research in this work, as shown in Figure 1-5.

Figure 1-5. Active Shunt Regulator system for the PM generator based power generation system

The specifications of the PMG/ASR are summarized in Table 1-1.

TABLE 1-1. SPECIFICATIONS OF THE ASR SYSTEM

| Regulated generator terminal voltage $U_{\rm s}$ | 115 Vrms           |

|--------------------------------------------------|--------------------|

| Rated output of the generator                    | 45 kVA             |

| Lowest load power factor                         | 0.75               |

| Continuous rated current                         | 130 Arms           |

| Sustained overload current                       | 200 Arms           |

| Regulated voltage frequency $f_0$                | 400 Hz             |

| Generator configuration                          | 4 poles, 12000 rpm |

| Current rating $I_n$                             | 78 Arms            |

| DC-link voltage $U_{\rm DC}$                     | 350 V              |

| ASR Capacity S                                   | 27 kVA             |

The following major components of the ASR system will be investigated in this work:

- Power device

- Line inductor

- DC-link capacitor

- Heatsink

### 1.3 Power Electronics in MEA

As one of the most important technologies for MEA [15], power electronics converters are also demanding advances in both efficiency and power density. For instance, a power density of 33 kW/ $\ell$  and a efficiency of >

98% are targeted by 2025 for the automotive electric traction drive systems [26]. Previous research has been intensively conducted to identify the performance limitations and the future trends of the development of power converters [27]–[30].

For comparing and benchmarking the performance of power converters, several metrics are defined and widely used in the previous research and roadmaps [26]–[29]. For the ASR system, the performance metrics of interest are the overall converter efficiency  $\eta$ , power density  $\rho$  and specific power  $\gamma$ . The efficiency  $\eta$  is normally defined as follows ([27], [28]):

$$\eta = 1 - \frac{P_{loss}}{P_{out}} \tag{1-1}$$

Where  $P_{loss}$  is the power loss;  $P_{out}$  is the output power. However, in this study, the efficiency of the ASR system is not straightforward because it mainly generates reactive power rather than real power. Therefore, a Relative Efficiency of the converter system is defined in this study as

$$\eta = 1 - \frac{P_{loss}}{S_{out}} \tag{1-2}$$

Where S<sub>out</sub> is the rated capacity of the converter, which is 27 kVA in the target system.

The power density of the converter is defined for per unit volume as

$$\rho = \frac{S_{rated}}{V_{total}} \left( \frac{kW}{dm^3}, \frac{kVA}{dm^3} \right) \tag{1-3}$$

For aircraft applications, the weight of components is equally important as the volume. For per unit weight, the specific power of the converter is defined as

$$\gamma = \frac{S_{rated}}{W_{total}} \left( \frac{kW}{kg}, \frac{kVA}{kg} \right) \tag{1-4}$$

To achieve a high power density of the power electronics system in discussion, a key aspect is to effectively reduce the passive components, such as heatsinks and filter components, which account for a major portion of the volume, weight and cost [26]–[29], [31]. For example, the filter components occupy 40% of the total volume and

weight of the converter system in [32]. [33] reported that the passive components contribute over 80 % weight of a converter. As for the efficiency, moving from 96% to 99% efficiency would significantly reduce the heatsink size and would allow a transformative change from liquid cooling to air cooling. However, there are several conflicting design constraints which need to be considered together. For example, lower switching frequency may lead to improved efficiency, but it comes with the cost of larger filter components. Increasing the switching frequency results in the reduced size of the filters, but the associated additional switching losses will require bigger heatsink to extract the heat.

There are two important areas that drive further improvement of the power density of power converters: converter topologies and power semiconductor devices [30]. Naturally, an optimal solution may involve both the advanced converter topologies and emerging semiconductor devices, which are expected to lead to a significant reduction of the passive components.

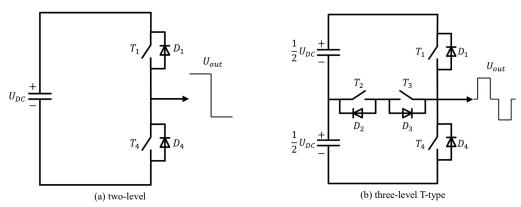

### 1.3.1 Converter topologies

Two-level (2L) converter topology is the most widely used configuration for low-voltage industry applications, such as motor drives, due to its simple structure and maturity [34]. The basic concept of the two-level converter is illustrated in Figure 1-6. However, the two-level converters feature several disadvantages due to the switching over the full DC-link voltage, such as high switching losses and high output harmonics. The high switching losses prevent the two-level converters to operate at a higher switching frequency (e.g. 50 kHz instead of 10 kHz), because the switching losses and the associated thermal stress increases significantly at a higher switching frequency. The high output harmonics require large filter components to attenuate.

Figure 1-6. Converter topology concept

As the advanced technology, multilevel topologies have been intensively researched over the past decades [35], [36]. For low/medium-voltage applications, three-level (3L) converters show a range of attractive benefits, such as improved efficiency and low output voltage/current harmonics. These benefits are mainly a result of the commutation voltage at only half of the DC-link voltage, as shown in Figure 1-6(b).

Previous research [34], [37]–[39] have provided comparative studies to demonstrate the benefits of advanced three-level topologies over the conventional two-level topology. [34], [38], [40] demonstrated the benefits of reduced switching loss of the three-level topology. The reduced switching loss enables the converter to operate at a higher switching frequency or require a smaller heatsink. [34], [38], [39], [41] draws a conclusion that three-level inverters offer reduced voltage/current harmonics, which lead to smaller and lighter filter components. Other benefits of the 3L topology such as reduced machine insulation stress and machine harmonic losses are also reported [34], [38]. Note both the two-level and three-level topologies introduced here are hard-switching topologies. Soft-switching topologies have been proposed to reduce the switching losses and achieve high switching frequency. However, it requires many auxiliary components with accurate parameters and greatly increases the circuit and control complexity [42], [43].

There are various options and derivations of the three-level topology [34], [35], such as Neutral Point Clamped (NPC) topology and three-level T-type (3LT) topology [44] (shown in Figure 1-6(b)). The NPC topology was firstly proposed in 1981 [45] and already has been widely used in medium-voltage applications [34]. But the

NPC topology suffers from unevenly distributed power loss between devices and increased conduction loss due to the current constantly flowing through series-connected devices [46]. As an alternative, the 3LT topology is free from the two clamping diodes in the NPC and become a more attractive option for low-voltage applications nowadays. [34], [40] states that the 3LT topology combines the positives of both 2L and NPC topologies.

However, the three-level topology also poses several challenges and drawbacks at the same time. If a neutral point is not required, the three-level topology requires four times installed capacitance at the DC-link compared to the two-level topology [34], due to the series connection of the DC link. The conduction losses in a 3L could increase due to the use of series-connected devices [34] compared to the 2L topology. Originally, the series-connected devices in three-level topology was to overcome the limited voltage rating of the devices for medium-voltage applications. But for low-voltage applications in this case, reducing the required device voltage ratings is not necessary anymore, because the available power devices can sufficiently block the full DC-link voltage [34]. Additionally, the voltage balancing issue of a three-level topology must be solved, which poses a challenge for low-power-factor operations [47], [48].

Regarding the ASR system, the performance of the three-level topology is still subject to comprehensive evaluation considering both the efficiency and power density. In this work, the *3LT* topology is considered to compare against the traditional two-level topology.

### 1.3.2 Power devices

Silicon (Si) based Insulated Gate Bipolar Transistor (IGBT) is the most common option in industrial products for high power (1~100kW), low-voltage (≤ 600 V DC-link voltage) applications due to the maturity of this technology. However, Silicon IGBT/diode suffers from the tail current associated turn-off loss and the reverse-recovery loss in the diode [49], which limits the power density of the converters [50]. The typical switching

frequency of multi-kW power converters based on Si IGBT is only 10 kHz  $\sim$  20 kHz. To rise the switching frequency of Si devices, large heatsinks are required to counter the high switching losses, which can degrade the power density of the converter substantially.

Nowadays, the Silicon based transistors are facing the challenge of emerging Wide Band Gap (WBG) devices such as Silicon Carbide (SiC) transistors and Gallium Nitride (GaN) transistors. These new-generation WBG power devices offer substantially lower power losses and faster switching speed [50]. 1200 V rated SiC Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) are commercially available by the time of this work targeting as the direct replacement of Si IGBT for low/medium voltage applications [51]. The main advantages of the SiC MOSFET over the Si IGBT are:

- Lower switching energies (e.g. 70% lower than Si devices [52])

- Higher thermal conductivity [27]

- Higher operating temperature

Apart from the SiC MOSFET, SiC diodes are also available, which features zero reverse-recovery loss compared to Si diodes [49]. There is an option of replacing only the Si diode with SiC diodes for the improved reverse-recovery loss and lower cost at the same time [49]. But it is still preferred to employ all-SiC (SiC MOSFET + SiC Schottky diode) solution for optimised converter performance, because a major portion of the switching losses are in the Si IGBTs as analysed in [34]. These merits of SiC MOSFET/diode open up the possibility of realizing power converters with substantially improved power efficiency and power density. The low switching loss of SiC devices enables the converter to operate at a higher switching frequency without considerable cooling efforts demanded. A higher switching frequency can lead to smaller filter components required target at attenuating the switching frequency harmonics, such as reduced line inductors and DC-link capacitors, which

allow the power converter to achieve a smaller volume and a lighter weight. However, high switching frequency at a certain degree can also degrade the system power density due to the enlarged heatsink, the increased EMI emissions and associated EMI filters [52].

Comparative evaluations are conducted in many publications to investigate the benefits of replacing Si devices with SiC devices in inverters/motor drives and DC/DC converters [49], [52]–[54]. These studies confirm the benefits of employing SiC devices regarding the power density and efficiency. For example, SiC devices can lead to a 159.4% increase of power density over Si devices as demonstrated in [52]. [55] shows a 70% reduction of switching loss by using SiC technology over Si devices. However, the precise improvement that the SiC devices can bring on the system still needs to be established on a particular application. Depending on the system specifications and constraints, the weighing of conflicting impact caused by increasing switching frequency, such as increased heatsink size against reduced filter size, still requires quantified analysis. Therefore, the design trade-offs considering Si IGBT/diode and SiC MOSFET/diode are subject to thorough investigation regarding the ASR application in discussion.

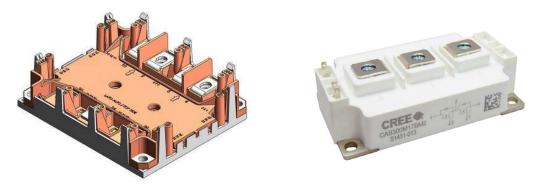

To investigate the power devices, this work is based on representative commercial products. To select an adequate product, the voltage ratings of power devices are normally over-rated as 1.5 to 2 times of the DC-link voltage [56], considering the overshoot voltage caused by the parasitic inductance. Considering the 350 V rated DC-link voltage in the ASR system and the commercially available options, 1200-V rated power devices are selected. Additionally, the commercially available Silicon Carbide (SiC) power devices are all rated at 1200 V or above. Next, considering the rated current at 78 Arms, it is preferred to select power modules over discrete devices. Off-the-shelf discrete SiC devices are rated at <100 A (e.g. C2M0025120D from © CREE). Considering the availability of commercial products, 300-A rated power modules are targeted for this application. To summarise, this work focuses on 1200-V, 300-A rated power modules and evaluate their performance in the target ASR system.

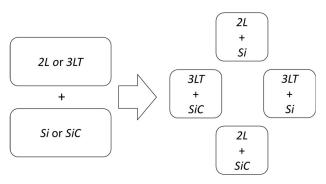

#### 1.3.3 Device/topology combinations

As introduced, the topology and the power device are two fundamental directions to improve the power converter performance. For the given application, it is worth exploring whether the use of improved devices, more complex topologies or a combination of both results in the best overall solution.

Previous studies focusing on power devices are established on certain topologies. For example [54] demonstrated the benefits of SiC MOSFET in 3LT inverters, which reports a 50% reduction of total power loss compared to a Si IGBT based configuration. [53] provides a benchmarking of SiC devices in single-phase T-type inverters regarding both the efficiency and power density. [52], [57] focuses on the optimisation of high power density 3-phase two-level converter with SiC device. [58], [59] evaluated commercially available two-level, 1200-V SiC MOSFET module and Si IGBT module. For the studies focusing on comparing topologies, mainly one type of power device is studied. For example, [38] compares two-level and three-level topologies based on only IGBT devices. [60] shows the design of a high power density converter for aircrafts considering two-level and three-level topologies based on Si devices. [34] considered the Si devices and SiC diode in two-level converters, but not considering the all-SiC options.

Therefore, there is still limited research providing a comparative study of the converter performance over various device-topology combinations within the same context. It is not clear how much a weighed improvement can be made through the advanced topology, the advanced power device or both, especially when multiple performance metrics are considered, i.e. the efficiency and power density. Therefore, this work intends to investigate, quantify and weigh the performance of several device-topology combinations. The considered devices are: 1. Si IGBT + Si diode; 2. SiC MOSFET + SiC Schottky diode. The considered topologies are: 1. Two-level 2. Three-level T-type. Two options of power devices and two topologies generate four combinations as shown in Figure 1-7.

Figure 1-7. Four considered device-topology combinations

The four device-topology combinations are analysed in this study. The 2L-Si option is considered the state-of-the-art industrial standard for benchmarking. Two representative commercial power modules are selected for the investigation:

- (1) 1200-V, 300-A SKiM301TMLI12E4B power module from Semikron with Si IGBT + Si diode and three-level T-type topology. This power module can be treated as the reference of Si based solution for both two-level and three-level topology, with its footprint shown in Figure 1-8 (a).

- (2) 1200-V, 300-A power module CAS300M12BM2 from CREE with SiC MOSFET + SiC Schottky diode and two-level topology. The footprint of this power module is shown in Figure 1-8 (b).

(a) SKiM301TMLI12E4B (b) CAS300M12BM2 Figure 1-8. Footprint of selected reference power modules

### 1.3.4 Passive components in the ASR

There are three main passive components in the target ASR system: (1) line inductor (2) DC-link capacitor (3) heatsink. The line inductors (also referred as the boost inductor) interface the power converter and the power

grid (generator output voltage), which provides the filtering of the switching-frequency current ripples. The line inductor L can contribute a significant portion of volume/weight among the passive components. For example, the line inductor can account for 32% of the converter volume enclosure [61], [62] and 59  $\sim$ 78 % of the weight of the converter [52].

The DC-link of the ASR system is formed by capacitors as the energy buffer to stabilize the DC-link voltage.

The DC-link capacitors also contributes to the converter volume/weight (e.g. 15% of the volume [63]). It should be noted that the DC-link voltage in the ASR system is floating. Referring to the phasor diagram Figure 1-4, the DC-link voltage needs to satisfy the following equation so that the converter can generate sufficient amplitude of AC voltage for the regulation considering the voltage drop on the line inductance.

$$\frac{U_{DC}}{2\sqrt{2}} \cdot M \ge U_s + \omega_0 L I_L \tag{1-5}$$

Where M is the modulation index of the converter, which varies between  $0 \sim 1.15$ . Considering the rated current of the converter, the DC-link voltage is rated at  $300 \sim 350$  V. Therefore, the DC-link in this case cannot be connected to the existing 115 V AC/270 V DC systems in the aircrafts [4].

For the target power generation system, the standard of load current harmonics and Electromagnetic Interference (EMI) is defined by DO-160E for aerospace applications [64]. Apart from the line inductors, normally there are Differential Mode (DM) and Common Mode (CM) EMI filters installed within the power converter to satisfy the EMI standard [39], [52], which also contribute to the volume/weight of the converter system [30], [63], [65]. In the target system, the EMI filters can be placed inside the ASR converter, or at the generator output terminal (after the regulation point). Due to the scope of this thesis, EMI filters are not considered as part of the ASR system in the analysis.

Cooling system is another important component to dissipate the heat generated in the power converter.

Designed to cool the power converter, the heatsink size is directly relating to the converter power loss, of which the majority is the power device loss. Heatsinks also occupy significant portion of mass/weight of a power converter [27], [66] and therefore require careful design and analysis.

#### 1.3.5 Optimisation of power converters

In industry, the typical process of developing a power converter is a repetitive process of prototyping, evaluation and improvement [67]. To achieve faster development and better performance, the use of Virtual Prototyping has been advocated [30], [68]–[70] in the industrial design procedure. Virtual Prototyping utilizes mathematical modelling and/or multi-physics software to aid and boost the design process of power converters towards optimized performance of the overall system. Previous studies have shown intensive efforts towards the optimisation of power converters, such as [30], [52], [63], [67], [71]–[75]. The optimisation of power electronics requires multi-domain and multi-objective considerations [30], [63]. A power electronics system does not only involve electrical design, but also involve the thermal stresses, electromagnetic issues and mechanical considerations. The efficiency, power density and specific power are all important metrics in modern power converters and are demanded as the objectives of the optimisation [28].

The multi-objective optimisation of power electronics consists of the following main sectors [30], [76]:

- Generation of design space (e.g. power device, topology and switching frequency)

- Definition of constraints (e.g. thermal limit and harmonics requirement)

- Performance functions (e.g. efficiency, volume and weight)

- Visualization and identification of design options and trade-offs for optimal searching

The Pareto Front analysis is commonly used to visualize and identify the performance trade-off limits in the optimisation of power converters [30], [77]. The most common Pareto Front analysis is the between the efficiency

and power density of power converters [63], [67], [72]. In recent studies, the cost is also considered as an important objective that requires Pareto Front optimisation [30].

In aerospace applications, the weight of systems is of great consideration as it impacts the fuel efficiency [5].

Therefore, the Pareto Front analysis in this work considers efficiency, power density and specific power as the three main optimisation objectives of the ASR system.

The multi-objective optimisation requires the utilization of software and programming, which provides efficient computation and handling of vast data and mathematical models [30]. In this work, the optimisation analysis is implemented in MATLAB based on analytical models of the system and individual components.

In the optimisation of a power converter, there are many coupling effects and considerations between individual components. In order to reduce the complexity of the optimisation algorithm, problem simplifications are necessary to break the whole system into individual sub-modules to be optimized [30]. In this work, simplifications to a certain extent will be introduced in the analysis of each individual components. Overall, the purpose of the optimisation analysis is to provide a top-level guidance of the design/selection of the key components of the system, such as topology, power device and switching frequency.

# 1.4 Research objectives

In this work, the enabling technologies, mainly SiC devices and three-level converter topology, are investigated aim at improving the system power density/specific weight by reducing the passive components. Design procedures and analytical models are developed for each individual component to serve the Virtual Prototyping purpose and predict the performance. A system-level optimisation tool is developed mathematically to explore the design trade-offs and performance limitations of the converter system. The ultimate objective is to identify the optimal design of the ASR system considering multiple conflicting performance objectives.

#### 1.5 Structure of Thesis

CHAPTER 2 presents the models of the power losses of power devices. Quantified benchmarking is performed to compare the power loss performance of the considered device-topology combinations. Analytical formulas are established to estimate the device power loss over a range of operating points of the converter. Estimated device power loss enables the design/analysis of the heatsink.

CHAPTER 3 addresses the low-frequency Neutral Point voltage oscillation issue in three-level three-phase converters. A literature review is conducted to identify the existing Neutral Point voltage balancing schemes to counter this issue without adding additional DC-link capacitance. Limitations of the existing approaches/models are investigated. Improved voltage balancing scheme is explored and implemented.

CHAPTER 4 details the design process of the three main passive components: DC-link capacitor, line inductor and heatsinks. Literature reviews are conducted for the design/analysis of each individual component.

The design concerns and the performance modelling of the passive components are explored.

CHAPTER 5 addresses the modelling of the inductor losses, especially the core loss. The literature review shows the challenges and state-of-the-art of modelling the inductor core loss in PWM converters. The testing approach and modelling method are investigated considering the inductor exposed in PWM excitation. Following empirical measurements, an analytical approach is presented to utilize the pre-measured loss map to estimate the inductor core loss for a given operating point of the two-level or three-level power converter.

CHAPTER 6 presents the system-level optimisation process. Based on the optimisation analysis, design trade-offs and performance limitations can be visualized in the form of Pareto Fronts. Prototypes are built to demonstrate the selected optimal of design.

CHAPTER 7 summarizes this work and presents an outlook of the future work.

# **CHAPTER 2**

# **Modelling of Active Power Devices**

Typically, power devices are the main source of power losses in a power converter. The modelling of the device power losses is important for the thermal considerations and the estimation of the converter efficiency. The device power loss reflects on the required heatsink performance, which is designed to extract the heat generated during the operation of power devices to prevent the devices exceeding a safe operating temperature. Previous studies have investigated the device power losses in PWM converters using analytical models [78]–[81]. Through analytical models, the averaged steady-state power loss of each power device can be estimated for a given operating point of the power converter.

As discussed in the introduction, the benefits of the emerging SiC devices and three-level topology is subject to quantified evaluation on the target system. Therefore, this chapter intends to develop analytical models for the four hard-switched device-topology combinations in discussion to benchmark their power loss performance.

#### 2.1 Topologies and power devices

As introduced in Section 1.3.3, this work intends to investigate four device-topology combinations:

- Two-level topology with Si IGBT/diode (2L-Si)

- Two-level topology with SiC MOSFET/Schottky diode (2L-SiC)

- Three-level T-type topology with Si IGBT/diode (3LT-Si)

- Three-level T-type topology with SiC MOSFET/Schottky diode (3LT-SiC)

The three-phase based configuration of these four device-topology combinations are shown in Figure 2-1.

The 2L-Si option is considered as the state-of-the-art industrial standard for benchmarking. Note the lower switch of the two-level phase leg is labeled as "T4" with reference to the T-type topology.

# 2.2 Operation of the ASR as a voltage source converter

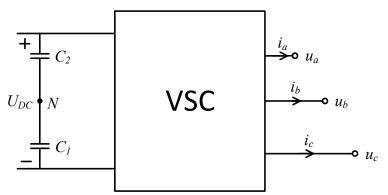

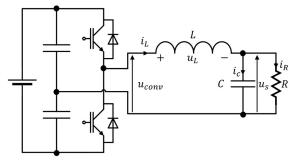

In the target ASR system, the power converter is a three-phase, DC/AC, bidirectional VSC. Figure 2-2 shows a generic model of such a power converter.

Figure 2-2. Generic model of a three-phase Voltage Source Converter

From the system point of view, the power converter is considered as a controllable voltage source generating

fundamental-frequency sinusoidal voltage superposed with high-frequency harmonics. The mathematical model of the power converter is expressed as (2-1) and (2-2) with regards to its output voltage and current at fundamental frequency.

$$\begin{cases} u_a = M \cdot \sin \theta \\ u_b = M \cdot \sin \left(\theta - \frac{2}{3}\pi\right) \\ u_c = M \cdot \sin \left(\theta + \frac{2}{3}\pi\right) \end{cases}$$

(2-1)