# The Transputer Virtual Memory System.

by Sias Mostert June 7, 1990

Thesis presented in partial fulfillment of the requirements for the Master of Engineering at the University of Stellenbosch.

STUDY LEADER: Mr P.J. Bakkes

#### **DECLARATION**

I hereby declare that the work for this thesis was done and written by myself and that it has not been submitted to any other university for the purpose of obtaining a degree.

i

June 7, 1990

#### **ACKNOWLEDGEMENTS**

I would like to thank the following for their support and encouragement during the my work on the thesis:

- Mr P.J. Bakkes, my study leader, for his guidance, advice and patience.

- Prof J.J. du Plessis for his guidance and advice.

- My wife Belinda for her support.

- The heavenly Father without whom this would not be possible.

ij

#### Abstract

The transputer virtual memory system provide, for the transputer without memory management primitives, a viable virtual memory system. This report evaluates the architecture and its parameters. The basic software is also implemented and described. The disk subsystem with software and hardware is also evaluated in a single disk environment.

It is shown that the unique features of the TVM system has advantages and disadvantages when compared to conventional virtual memory systems. One of the advantages is that a conventional operating system with memory protection can now also be implemented on the transputer. The main conclusion is that this is a performance effective implementation of a virtual memory system with unique features that should be exploited further.

#### OPSOMMING

Die transputer virtuele geheue verskaf, vir 'n verwerker sonder virtuele geheue ondersteuning, 'n doeltreffende virtuele geheue stelsel. Die verslag evalueer die argitektuur en sy parameters. Die skyfsubstelsel met programmatuur en apparatuur word ook geevalueer in 'n enkel skyfkoppelvlak omgewing.

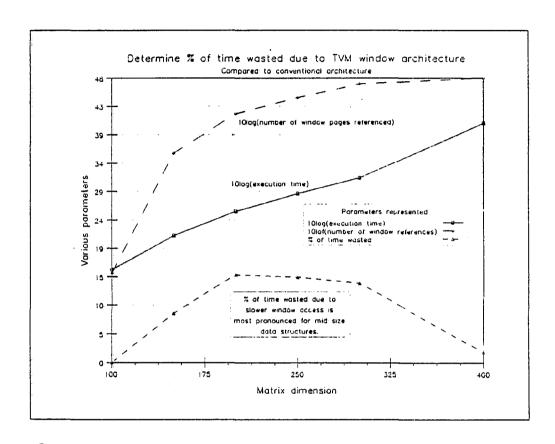

Daar word bewys dat die unieke eienskappe van die TVG (transputer virtuele geheue) voor- en nadele besit wanneer dit vergelyk word met konvensionele virtuele geheue stelsels. Een van die voordele is dat 'n konvensionele bedryfstelsel met geheue beskerming nou op 'n transputer ge-implementeer kan word. Die hoofnadeel agv die spesifieke argitektuur gee slegs 'n 15% degradering in werkverrigting. Dit word egter slegs oor 'n sekere datagrootte ervaar en kom tipies nie ter sprake wanneer daar massiewe programme geloop word nie.

iii

# Contents

| 1 | Intr                | oducti | ion                                                       | 1  |

|---|---------------------|--------|-----------------------------------------------------------|----|

| Ι | Relevant literature |        |                                                           | 3  |

| 2 | Intr                | oducti | ion to Literature Study                                   | 4  |

|   | 2.1                 | Tradit | ional workloads                                           | 4  |

| 3 | Vir                 | tual m | emory hardware                                            | 5  |

|   | 3.1                 | Basic  | hardware                                                  | 5  |

|   | 3.2                 | Hardw  | vare support                                              | 6  |

|   |                     | 3.2.1  | Distributed and Slave memory                              | 6  |

|   |                     | 3.2.2  | Hardware support for measurements                         | 7  |

|   |                     | 3.2.3  | Addressing mechanisms                                     | 7  |

|   | 3.3                 | Deteri | mining page size                                          | 8  |

| 4 | Mei                 | mory r | nanagement                                                | 10 |

|   | 4.1                 | Basic  | principles                                                | 10 |

|   | 4.2                 | Measu  | res for evaluation                                        | 11 |

|   | 4.3                 | Page 1 | replacement strategies                                    | 11 |

|   |                     | 4.3.1  | Terminology                                               | 12 |

|   |                     | 4.3.2  | The optimal page replacement strategy                     | 12 |

|   |                     | 4.3.3  | Algorithm classification according to amount of data used | 12 |

|   |                     | 4.3.4  | Algorithm classification according to inclusion property  | 13 |

| C( | ONTI            | ENTS   |                                        | ν  |  |  |  |  |

|----|-----------------|--------|----------------------------------------|----|--|--|--|--|

|    |                 | 4.3.5  | Known page replacement algorithms      | 13 |  |  |  |  |

|    | 4.4             | Page p | prediction strategies                  | 17 |  |  |  |  |

|    |                 | 4.4.1  | Demand prepaging                       | 17 |  |  |  |  |

|    |                 | 4.4.2  | Sequential prepaging                   | 20 |  |  |  |  |

|    |                 | 4.4.3  | Determining optimal buffer sizes       | 20 |  |  |  |  |

|    | 4.5             | Other  | methods of improving performance       | 21 |  |  |  |  |

| 13 | T               | ransp  | outer virtual memory                   | 23 |  |  |  |  |

| 5  | TVM Hardware 24 |        |                                        |    |  |  |  |  |

|    | 5.1             | Basic  | architecture mechanisms                | 25 |  |  |  |  |

|    |                 | 5.1.1  | Two processor system                   | 25 |  |  |  |  |

|    |                 | 5.1.2  | Memory hierarchy                       | 26 |  |  |  |  |

|    |                 | 5.1.3  | Hardware in support of TVM             | 27 |  |  |  |  |

|    | 5.2             | TVM    | system architecture                    | 28 |  |  |  |  |

|    | 5.3             | Optim  | nal parameters for TVM                 | 28 |  |  |  |  |

|    |                 | 5.3.1  | The benchmarks                         | 30 |  |  |  |  |

|    |                 | 5.3.2  | The measure for comparison             | 35 |  |  |  |  |

|    |                 | 5.3.3  | The active cache size                  | 35 |  |  |  |  |

|    |                 | 5.3.4  | The non-active cache size              | 39 |  |  |  |  |

|    |                 | 5.3.5  | The window size                        | 42 |  |  |  |  |

|    |                 | 5.3.6  | Page size                              | 42 |  |  |  |  |

|    | 5.4             | Perfor | mance implications of TVM architecture | 45 |  |  |  |  |

|    | 5.5             | Detail | HW design                              | 47 |  |  |  |  |

| 6  | TV              | M Soft | ware                                   | 48 |  |  |  |  |

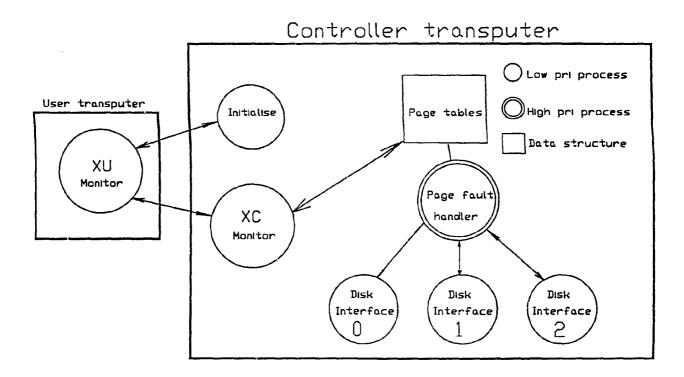

|    | 6.1             | Progra | am specification                       | 48 |  |  |  |  |

|    | 6.2             | Progra | am design                              | 49 |  |  |  |  |

|    |                 | 6.2.1  | Process harness                        | 49 |  |  |  |  |

| $C_0$ | ONT  | ENTS     |                             |   | vi        |

|-------|------|----------|-----------------------------|---|-----------|

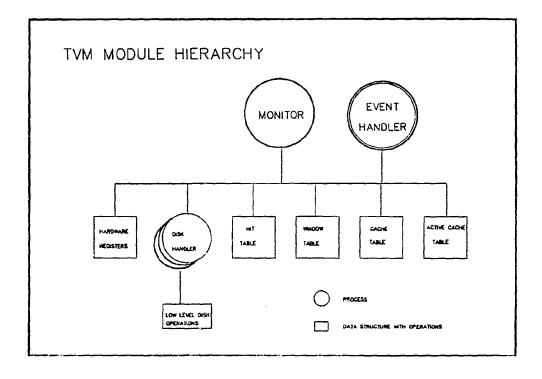

|       |      | 6.2.2    | Modular construction        | • | 49        |

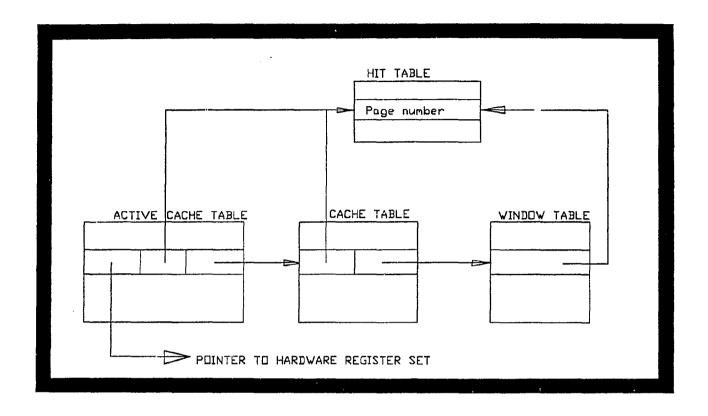

|       |      | 6.2.3    | Data structures             |   | 49        |

|       |      | 6.2.4    | Program flow                | • | 53        |

|       | 6.3  | Progra   | am evaluation               | • | 54        |

|       |      | 6.3.1    | Execution times             | • | 55        |

|       |      | 6.3.2    | Replacement algorithms      |   | 55        |

|       | 6.4  | Future   | e development               |   | 57        |

|       |      | 6.4.1    | Stack algorithms            |   | 57        |

|       |      | 6.4.2    | Prediction                  | • | 57        |

|       |      | 6.4.3    | Disk organization           |   | 58        |

|       | 6.5  | Other    | ways to improve performance |   | 59        |

| II    |      |          | dary memory system          |   | 61        |

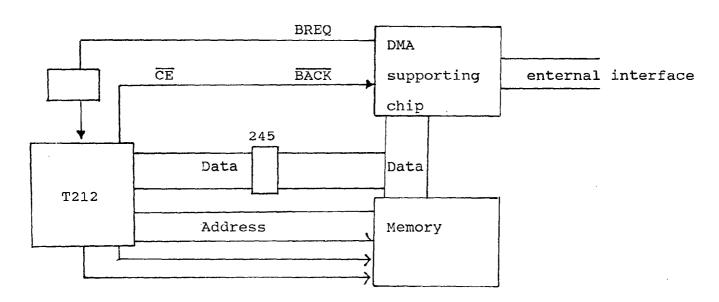

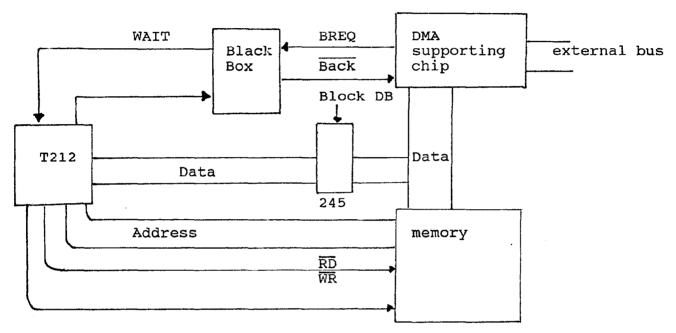

| 7     | Har  | rdware   |                             |   | <b>62</b> |

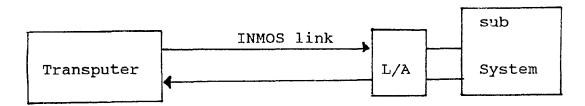

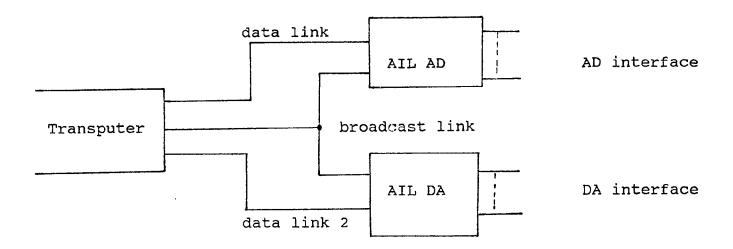

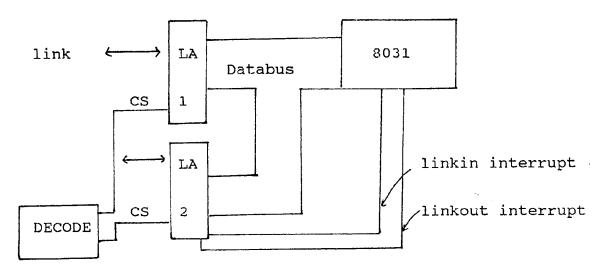

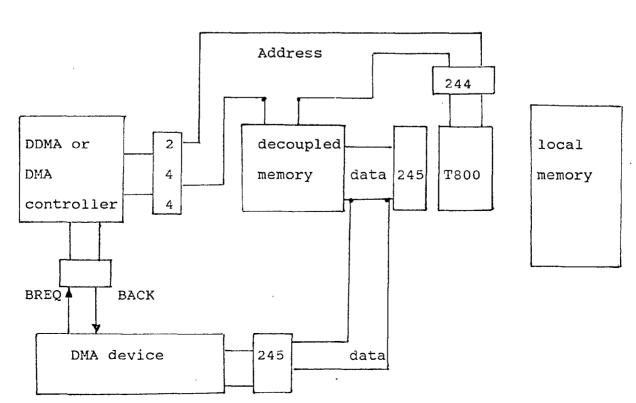

|       | 7.1  | Overv    | iew of solutions            |   | 62        |

|       |      | 7.1.1    | XC to diskinterfaces        |   | 62        |

|       |      | 7.1.2    | Disk subsystem architecture | • | 63        |

|       |      | 7.1.3    | Diskinterface architecture  | • | 64        |

|       | 7.2  | Diskin   | terface design              | ٠ | 66        |

|       | 7.3  | Perfor   | mance evaluation            | ٠ | 66        |

| 8     | Sof  | tware    |                             |   | 68        |

|       | 8.1  | Progra   | am specification            |   | 68        |

|       | 8.2  | Progra   | am design                   |   | 68        |

|       | 8.3  | Perfor   | mance evaluation            | • | 70        |

| IJ    | J ]  | In cor   | nclusion                    | , | 71        |

| 9     | Effe | ect of V | VM on program execution     |   | 72        |

| C(           | ONTENTS                            | vii |

|--------------|------------------------------------|-----|

| 10           | Conclusions                        | 74  |

| V            | Appendices                         | 78  |

| $\mathbf{A}$ | Transputer virtual memory hardware | 79  |

| В            | TVM registers                      | 80  |

| С            | TVM PAL equations                  | 81  |

| D            | TVM users manual                   | 82  |

| $\mathbf{E}$ | M212 disk interface                | 83  |

| F            | SCSI disk interface                | 84  |

| G            | Interfacing transputers            | 85  |

# List of Figures

| 3.1  | Lower bound on access times                                                    | 8  |

|------|--------------------------------------------------------------------------------|----|

| 4.1  | A typical lifetime function                                                    | 15 |

| 4.2  | Life time knee nd space time minimum                                           | 16 |

| 4.3  | The effect of prepaging on matrix multiplication.                              | 19 |

| 4.4  | Obtaining access frequencies from a success function                           | 21 |

| 5.1  | Simplified memory hierarchy diagram.                                           | 26 |

| 5.2  | Block diagram of TVM system                                                    | 29 |

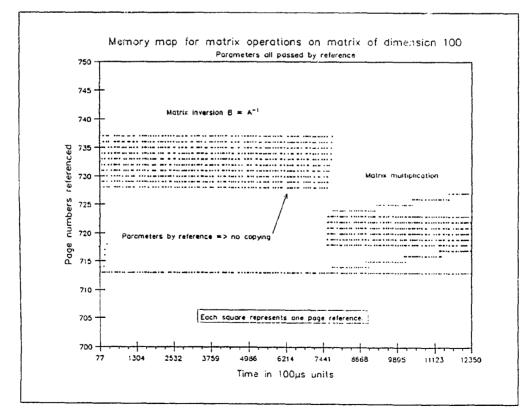

| 5.3  | The memory map for mat100 with VAL parameters and VAR parameters               | 31 |

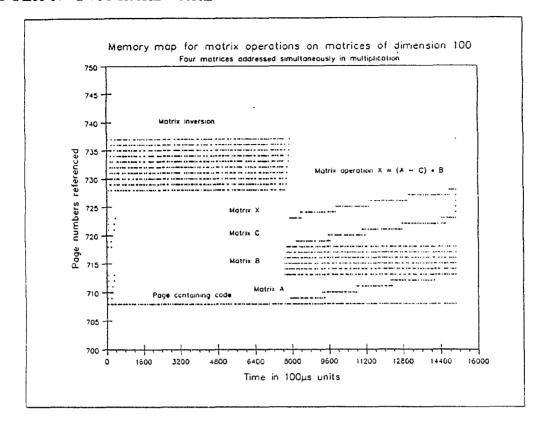

| 5.4  | Memory maps for increasing number of simultaneous accessed data structures     | 33 |

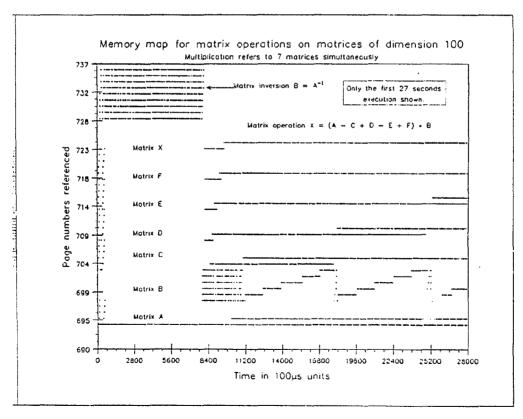

| 5.5  | Memory map for the NORM benchmark                                              | 34 |

| 5.6  | Norm program: execution time against increasing active cache size              | 36 |

| 5.7  | Matrix program: various parameters against active cache size                   | 37 |

| 5.8  | Increasing the number of simultaneous accessed data structures                 | 38 |

| 5.9  | Execution times for matrices of different dimensions against active cache size | 39 |

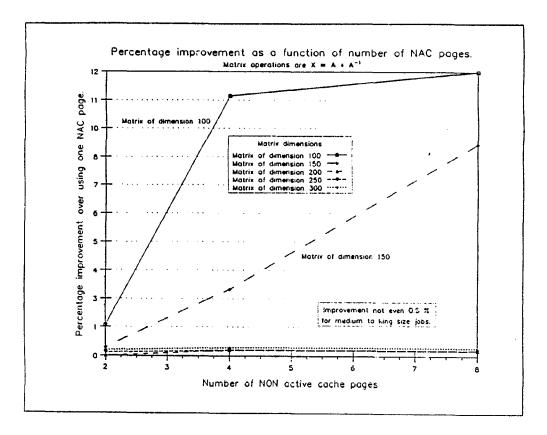

| 5.10 | The improvement over one NAC in execution time for bigger NAC's                | 40 |

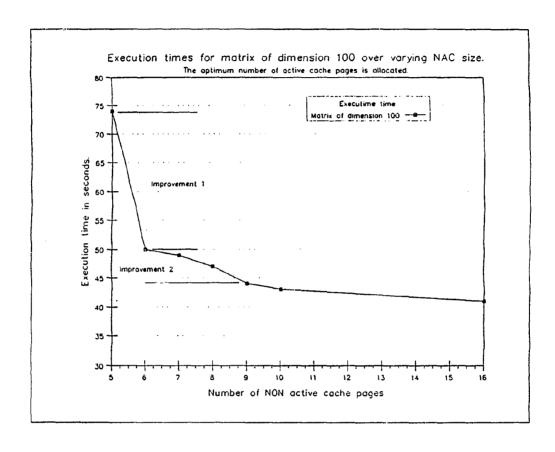

| 5.11 | Execution time versus NAC size for optimum—mount of ac pages                   | 41 |

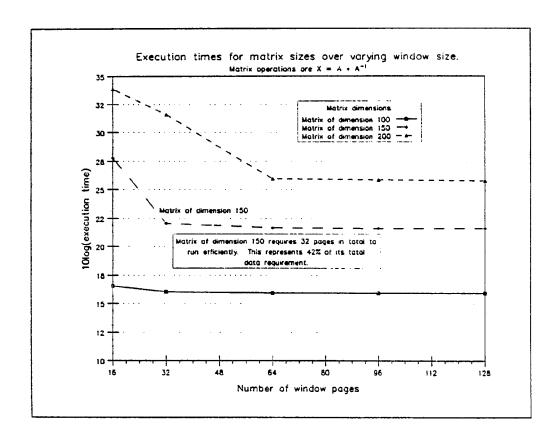

| 5.12 | The execution times for the various matrix dimensions against window size      | 43 |

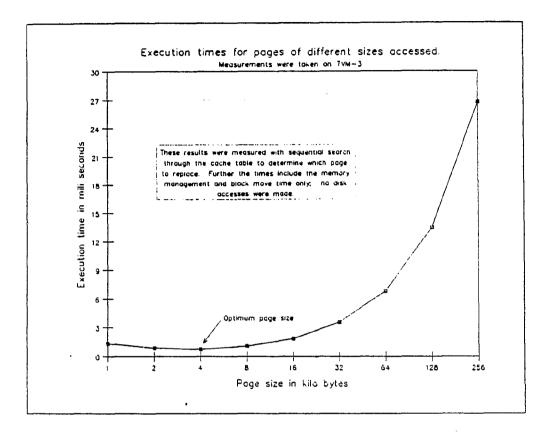

| 5.13 | Page fault handling time vs page size                                          | 44 |

| 5.14 | The effect on execution time when the page size is variable                    | 45 |

| 5.15 | The % of time wasted vs the dimensional size for matrix                        | 46 |

| 6.1  | Process diagram for TVM                                                        | 50 |

| IST C | OF FIGURES                                                                                                        | ix |

|-------|-------------------------------------------------------------------------------------------------------------------|----|

| 6.2   | Module hierarchy for TVM                                                                                          | 51 |

| 6.3   | The inter relationship between the tables                                                                         | 53 |

| 6.4   | Main algorithm on MMU                                                                                             | 54 |

| 6.5   | The execution time for matrix 150 under FIFO and RANDOM replacement algorithms                                    | 56 |

| 6.6   | The execution time for matrix 200 under FIFO and RANDOM replacement algorithms.                                   | 56 |

| 6.7   | Disk access times for different page sizes                                                                        | 59 |

| 6.8   | Execution times for matrix algorithm and its transpose algorithm                                                  | 60 |

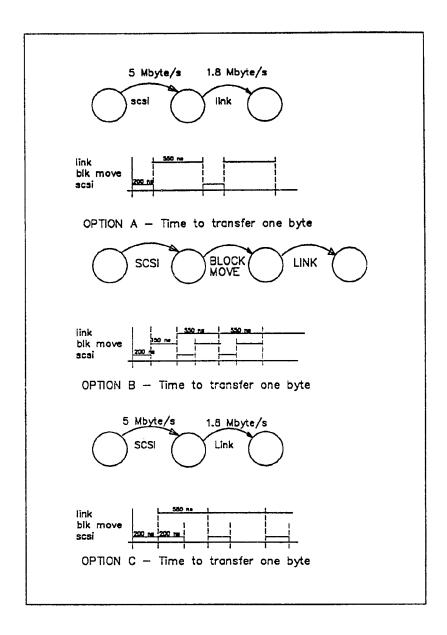

| 7.1   | Evaluation of disk channel architecture                                                                           | 65 |

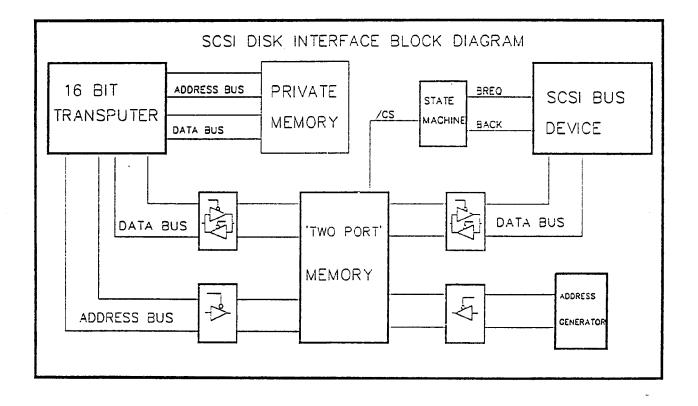

| 7.2   | TVM scsi disk interface block diagram                                                                             | 67 |

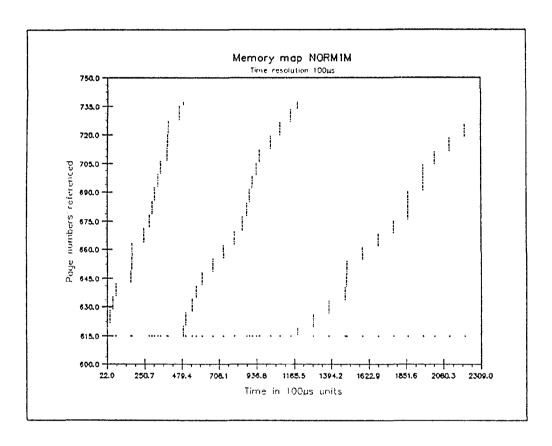

| 9.1   | Percentage performance of virtual memory system when compared to execution in real memory                         | 72 |

| 9.2   | Percentage performance of virtual memory system with very small window when compared to execution in real memory. | 73 |

# Chapter 1

## Introduction

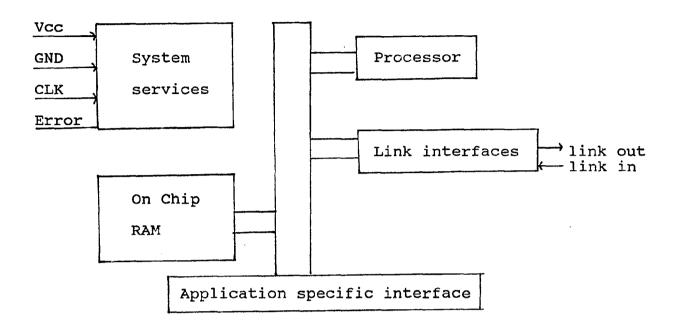

The transputer is a very fast microprocessor (10 MIPS) with an onboard scheduler and communication processors. A basic design aim of the manufacturer was one processor per user. Thus no multiuser support in the form of memory management and protection have been included in the transputer. This includes a lack of virtual memory supporting hardware.

Many applications need the fast processor in addition to more memory than can be provided in the form of fast read/write memory. The transputer virtual memory system provide in this need.

Fundamental differences between the TVM system and conventional virtual memory systems are:

- 1. The virtual memory provided must be totally transparent to the user. Specifically no operating primitives must be necessary to use the virtual memory.

- 2. A dedicated disk storage subsystem will be available for the paged system.

- 3. The workload designed for is large scientific programs and NOT a multiprogramming environment.

This report will investigate the performance of the designed architecture and will show that this is a performance efficient virtual memory system when king size jobs are run on it.

The TVM system will be investigated with different size jobs. For small jobs with a data requirement less than 8 mega byte this system provides directly supported read/write memory, thus no performance degradation will result. The medium size jobs from 8 Mbyte to 13 Mbyte expose the systems' weak spots. King size jobs, that is with memory requirements greater than 13 Mbyte will run as efficiently as on any other virtual memory system with the same memory size parameters.

The unique features of the TVM system can be exploited to further enhance the performance efficiency of the TVM system. One performance influence of particular interest is the multiple disk channels which is connected to the memory management unit. The other unique feature

#### CHAPTER 1. INTRODUCTION

open for exploitation is the memory management unit when it is not busy servicing a page fault.

The report begins with a literature survey of virtual memory systems. The first reported virtual memory system was reported in 1961! The report continues with the architecture description and evaluation. This is followed by a description of the current software implemented and an evaluation thereof. The disk subsystem hardware and software follows with a basic evaluation of its performance. The report is concluded with the final conclusions and recommendations.

2

# ${f Part\ I}$ Relevant literature

# Chapter 2

# Introduction to Literature Study

The first machine to use virtual memory was the ATLAS computer from Manchester. Since then virtual memory has been investigated and many results have been published. Thus more than twenty nine years have past since the introduction of virtual memory. It is then expected that many advances would have been made and that the theory of virtual memory would be relatively well known. In the rest of this chapter existing virtual memory systems will be considered to extract from them the lessons learnt so far in the design of virtual memory systems.

Any virtual memory system can be decomposed into the hardware architecture and the management software running on it. Both these subjects will now be considered independently.

## 2.1 Traditional workloads

Virtual memory was invented with the purpose of giving programmers the much needed unlimited supply of memory. The principles of virtual memory were soon utilized in multiprogrammed and time-sharing computers. It provided a mechanism for holding in main memory many user processes much larger than the available memory space. Thus many of the early studies considered evaluation of a virtual memory system within a multiprogramming environment of utmost importance [Denning 70].

The TVM system was designed to provide a powerful workstation for a single user. The main purpose is to provide one programmer with a powerful processor with 'unlimited' memory. Thus under most circumstances the evaluation of virtual memory under multiprogrammed workloads is of little use. However the transputer supports parallel execution threads which again is a multiprogrammed workload. This document does not look into the performance evaluation of the TVM under multiprogrammed workloads, but for the right user base this evaluation could be very applicable.

# Chapter 3

# Virtual memory hardware

## 3.1 Basic hardware

The basis of virtual memory is to disassociate the address referenced by a process from the address space available in primary storage. It follows that some kind of mapping mechanism must exist to facilitate this transformation. This transformation mechanism must not slow down the memory references of a process.

Due to efficiency considerations the main memory is divided into equally sized sections called pages. These pages are then the smallest unit managed by the virtual memory system. The mapping mechanism then consists of a address transformation unit taking an address which can be considered as a composite address consisting of a pair (p,d). Where the first n bits form to the page address and the last m bits form d the distance into the currently addressed page.

Due to the obvious limitation on the size of main memory, a mechanism must exist to stop the executing process when an address referenced does not exist in the main storage. This condition should generate a page fault event which interrupts the executing processor which will then execute the page management software. On completion of making the addressed page available in the main store, the processor then restarts the interrupted process by re-executing the interrupted instruction.

The above mechanism implies a few assumptions:

- 1. Only one processor is used for both process execution and page fault handling.

- 2. The processor must have restartable instructions referring to memory.

It will be shown that the transputer virtual memory system functions while not satisfying any of the above assumptions.

The main store not containing all the address space of a process, must be backed up by a second level of storage. In all cases known this second level of storage is a moving arm disk.

The main memory of the processor then is just a 'managed buffer' for the processors' address space which is mapped onto the disk. This leads one to belief that virtual memory systems are very slow because the memory speed is the speed of the disk. Fortunately programs exhibit certain behaviour patterns which makes virtual memory in many cases not much slower than real memory.

## 3.2 Hardware support

Described in the previous section is the basic hardware required to support virtual memory. There are however a few hardware implementable options to be considered. Three specific areas are considered in [Denning 70]:

- Slave memory vs distributed memory.

- Hardware support for measurements to improve the management software.

- Addressing mechanisms.

#### 3.2.1 Distributed and Slave memory

Both slave memory and distributed memory consists of memory hierarchies. The difference is in accessing the different levels of the hierarchy. In a slave memory system access to the memory level closest to the processor does not result in any delay. But any access to a data item in a level further away from the closest level results in a page fault event and the data item must be loaded into the closest level before program execution can continue. One example of slave memory is a cache.

Distributed memory although also consisting of different levels of memory does no generate a page fault event for accessing a data item in any level. Thus the processor can access any data item in any level. The cost of accessing data items further away from the processor lays in the longer time taken by the address translation mechanisms for levels further away from the closest level.

None of the virtual memory systems found by the author in literature employs the distributed memory hierarchy. This can be attributed to the difficulty in implementing such a mechanism. Nearly all modern cache systems does however employ the distributed memory hierarchy. This could be ascribed to the fundamental difference between cache and virtual memory systems. Cache systems provide faster access to addressed items than main memory allows and the cache is normally a small subset of the main memory. The probability of finding the item in main memory when it is not in the cache is 100times in the order of 2 to 5 times as slow as the cache, which means that there is a small time penalty paid for accessing the main memory.

Virtual memory systems though provide the user with a much larger address space that can be provided by fast random access memory. Access times to disk are orders of magnitude longer

than to main memory. Thus any hardware translation mechanism addressing the disk is a gross under utilization of the speed achievable in hardware.

However if a virtual memory system consisted of more than the two levels of memory associated with main memory and disk memory then, accesses to the intermediate levels might warrant a hardware address translation unit as found in a distributed memory environment.

#### 3.2.2 Hardware support for measurements

For efficient management of the virtual memory space information is needed. Many of the management policies known today require information with regard to page accesses which cannot be measured with software. The following measures can easily be measured with the minimal of hardware support.

- 1. Setting a modify bit.

- 2. Setting a referenced bit.

- 3. Setting an unused bit.

- 4. Incrementing counters for each access to a page.

The significance of these measures can be deduced from the section on virtual memory management.

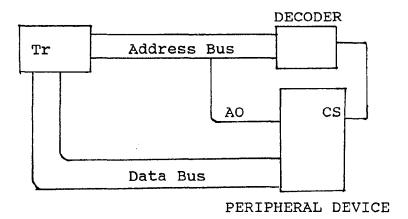

## 3.2.3 Addressing mechanisms

These mechanisms refer to the basic address translation mechanisms. The basic criteria for any such mechanism is the minimal extra delay introduced due to the mapping process. The first level of memory is accessed with the normal memory address cycle. If a multilevel memory hierarchy exist then the access to lower levels must introduce a minimal delay.

The only hardware mechanism satisfying the no delay requirement of the memory level closest to the processor is associative mapping. This is however a costly mechanism in terms of the amount of hardware required. The largest mechanism known to the author is a 512 page unit used with a modern cache controller.

There is however a result reported in [Deitel 83] which indicates that a small associative mapping mechanism of 16 pages combined with a slower mechanism for all the other cases, results in a performance of 90 % of a full associative mapping mechanism for all the pages in main memory.

The lower levels in a multi level memory hierarchy virtual memory use a slower mapping mechanism, some of which is described in [Deitel 83]. These slower mechanisms could be implemented in two ways. One mechanism would be a real time virtual address translator

#### CHAPTER 3. VIRTUAL MEMORY HARDWARE

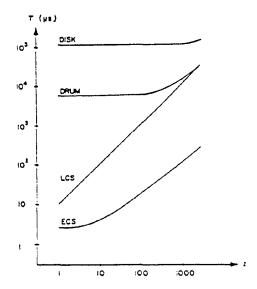

Figure 3.1: Lower bound on access times

with a delay time of two memory accesses. On subsequent accesses to the page a page fault is generated and the page number moved into the associative mapping. The alternative is that on the first reference to a page a page fault is generated and the page number moved into the associative mapping mechanism.

It will be shown later that because of the locality property of programs executing, there is little need for the first slower mapping mechanism described because the probability that another location in the same page will be referenced is very high.

### 3.3 Determining page size

The optimal page size for a virtual memory system depends on hardware and software considerations. In this section only the hardware aspects which influence the page size are considered.

The lookup and transfer time for a page from the secondary storage to primary storage and memory fragmentation are the two hardware parameters influenced by the page size. Both lookup and transfer times will further be referred to as the access time of a device.

In the article by [Denning 70] a relation between the access time for different memory technologies is given. The relations of importance to us is the moving arm disk and an intermediate memory level. From fig 3.1 it can be seen that for page sizes up to 1000 words the access time to a disk is constant due to the dominance of the seek and rotational delay. The technologies indicated on the graph are completely outdated, but the principle of a slower memory than main memory in a hierarchy is very relevant. If such a level existed corresponding to the ECS graph, then smaller page sizes would perform better.

Memory fragmentation consists of two types in a paged memory system [Denning 70] viz. internal fragmentation and table fragmentation. The previous of the two refers to a page not

completely filled with items to be referenced by the processor on requesting that page to be loaded. This phenomena indicates smaller pages are to be preferred for efficient memory use.

Table fragmentation refers to the amount of table space needed to manage the pages in a virtual memory system. The more pages the bigger the tables and the less memory available for buffering pages. This phenomena indicates that larger pages will be better because the tables will then be smaller.

From the above discussion it is clear that the use of a disk for secondary storage implies that for page sizes from one word to around 1000 words the access time is the same. Thus there is an advantage to use a page size of 1000 words. Fragmentation though has another influence. Internal fragmentation indicates the smaller the page the better. While table fragmentation advocates bigger page sizes. The page size decision from a hardware point of view is thus a compromise which must take into account the current technology.

# Chapter 4

# Memory management

The memory management system for a virtual memory system also have a first order effect on the performance of a virtual memory system. The main function of a management system is to make sure that the next location the main process wants to access will be available.

Some basic strategies investigated and reported on in literature will be discussed. This is followed by some measures of performance used by researchers. From the basic strategy chosen some page replacement algorithms follow. Another way for the management software to increase performance is by prediction. This concept have also been investigated and will be reported on.

## 4.1 Basic principles

According to [Deitel 83] there are two main strategies ie. fetch strategies and replacement strategies. The first has to do with when to bring a page into real memory and the second with when to remove a page from virtual memory.

Fetch strategies can be divided into demand fetching and prediction fetching. Demand fetching only fetches a page when addressed by the executing program. While prediction fetching tries to predict the next page which will be requested and then loads that page. Demand paging is the dominant method employed today. Prefetching can however improve the execution time of a program by 10 to 20 % according to [Smith 78]. While [Trivedi 76] only states that there is an improvement but he does not quantify it.

Replacement strategies are numerous and even an optimal algorithm has been suggested. These various algorithms are first classified according to existing criteria and then there relative performance compared.

Other methods to increase the execution speed of virtual memory programs is to restructure the program to fit the underlying hardware better. A few of these methods have also been investigated and will be reported on.

Hence will be considered the most important measures for comparing the different strategies. Then different replacement strategies will be discussed. Lastly the question of when to fetch a page will be addressed.

#### 4.2 Measures for evaluation

[Trivedi 76], in a paper on the effects of prepaging for an array workload, gives three measures for comparing virtual memory systems. Each of these measures are the most appropriate in optimizing some parameter of a virtual memory system. The parameter to optimize will be discussed in the context of each of the measures.

- 1. Number of 'page pulls'. This is the number of transfers from secondary storage to main memory. This parameter is of importance when the channel traffic is to be minimized.

- 2. Number of page faults. This measure is of importance when the CPU utilization is to be maximized.

- 3. The space time product. This parameter is defined as

$$c(t_1, t_2) = \int_{t_1}^{t_2} m(t) dt$$

where m(t) indicates the occupation of m(t) pages in memory at time t. This measure is of importance when maximizing memory utilization.

The author is of opinion that not any one measure should dominate, but that at least a combination if the first two measures should be used. The most important measure should be the program execution speed. This is however very restricted in that it only accounts for one type of program. Most computer systems are however used for specific purposes and the system architecture should be optimized for these.

Another important measure is described in [Mattson 70] with regard to the evaluation of storage hierarchies. The success function is defined as

The relative frequency of successes as a function of capacity is given by the success function. Where a success is defined as an access into a level of a multilevel c and the item searched for was there.

This success function will be shown to be useful in determining the various buffer sizes of the various levels of memory given the trace of a program.

## 4.3 Page replacement strategies

The page replacement strategy of a virtual memory system can truly be called the crux of any virtual memory system. Its behaviour determines to a great extent the performance of a virtual

memory system where no king size jobs are run [Yoshizawa 88]. Page replacement comes into play when the main processor has requested a page and the question is which page must be replaced. There is an optimal algorithm [Denning 70] which is discussed first followed by many approximations realizable in computer systems.

#### 4.3.1 Terminology

The abbreviations used further have the following meaning:

LRU Least recently used page replacement algorithm.

FIFO First in First out page replacement algorithm.

NUR Not used recently page replacement algorithm.

LFU Least frequently used page replacement algorithm.

WS Working set memory management strategy.

### 4.3.2 The optimal page replacement strategy

The optimal page replacement algorithm will replace the page not to be used for the furthest time into the future [Denning 70]. This algorithm is not realizable since it requires advance information about the behaviour of the program to run. Any practical algorithm then approximates the optimal algorithm.

### 4.3.3 Algorithm classification according to amount of data used

Belady [Belady 66] carried out a study on page replacement algorithms and classified them according to the amount of information used to make a decision. This classification is:

- The replacement algorithm is not based on any information about memory usage. The algorithms falling under this category are random replacement and FIFO replacement.

- Pages are classified according to the history of their most recent use in memory. Algorithms falling in this category are LRU and NUR.

- Pages are classified according to their presence and absence from main memory. All pages are considered. These types of algorithms never developed very far.

From this classification it can be deduced how well certain types of algorithms will fare. Also can be deduced what type of information is necessary for the efficient management of virtual memory.

#### 4.3.4 Algorithm classification according to inclusion property

Replacement algorithms whose traces obey the inclusion property [Mattson 70] are called stack algorithms because for any program trace the stack can be efficiently computed and from the stack the success function can be deduced. Refer to [Mattson 70] for more details.

A stack algorithm will always lead to less page faults in a larger buffer space, while a non stack algorithm would not. What is of importance however is that the FIFO replacement strategy is not a stack algorithm while LRU, LFU, NUR and even the random replacement policies are.

#### 4.3.5 Known page replacement algorithms

The optimal page replacement algorithm has been described in a previous section. Some of the algorithms which follow tries to approximate the optimal algorithm while others go out from certain assumptions about program behaviour.

There is one parameter which influences the basic outlook on replacement algorithms. The real memory window mapping onto virtual memory could either be of a fixed size or a variable size. In the former case it is easy to manage the free pages, ie. it is wise to fill as many pages as possible with pages referenced by the program to increase the likelihood of another 'hit' or 'success'. In the latter case the decision of exactly how many pages must be allocated to each job at a specific time is a hard choice. It is in the latter case where not only the replacement but also the freing mechanism are important.

The TVM system has only a fixed size window onto virtual memory. This leads one to believe that these more sophisticated techniques are not relevant, but in the case of freing pages to make place for a sudden surge of page faults or for prepaged pages these techniques could lead to improved performance. The two techniques which falls under the last category are the working set strategy and the page fault frequency algorithms.

#### Random page replacement

This strategy assumes that the pages referenced in a program follows a random pattern normally uniformly distributed. With the assumption made, there is little reason to replace pages other than random. One reassuring fact about a random replacement algorithm is that [Mattson 70] has shown that a random replacement algorithm for a specific buffer size c can be represented by an equivalent stack algorithm. This implies that for bigger buffer sizes the random replacement algorithm will indeed perform better.

[Belady 66] has shown that for king size jobs (program memory requirement far greater than real memory) the random replacement algorithm did not fare much worse than the other more optimal algorithms tested by him. This can be ascribed to the fact that king size jobs flush the real memory every so often that there is little value in keeping extra information about the used pages.

#### FIFO page replacement

Two schools of thought could arrive at this algorithm. On the one hand, one could argue that to approximate the optimal page replacement algorithm a possible solution would be to replace the page the longest in memory. This is just the tail of a FIFO queue. The other way to arrive at the FIFO replacement algorithm is to argue that it is just a special case of the random algorithm involving much less computation.

While both arguments is true, it has been proved that the FIFO replacement algorithm is not a stack algorithm. This implies that for bigger buffer sizes c there is not necessarily an improvement of the virtual memory system with a FIFO replacement algorithm.

#### LRU-Least recently used

This algorithm is most likely the best performer of the demand replacement algorithms. The page to be replaced is the one who has been referenced the longest time back. This approximates the page that will not be used for the longest time in the future very well because of the working set behaviour of program execution.

#### LFU-Least Frequently Used

An approximation of LRU. Measure how intensively a page has been referenced. Those pages with the least number of references within the last time frame are replaced. This algorithm has a grave possibility of removing a page just moved into memory.

#### NUR-Not Used Recently

An approximation of LRU with little overhead [Deitel 83]. Pages are divided into four groups according to how they were referenced. Pages not referenced at all forms the group to be replaced first. Pages modified but not referenced form the second group to be replaced. Pages referenced but not modified forms the third group to be replaced. And then if none of the previous type of pages are in the virtual memory to be replaced then pages modified and referenced are selected for replacement.

This scheme ensures that the last group does not contain all the pages by periodically resetting the referenced bits of all the pages. This ensures that those pages actively referenced remains in the last two groups and these pages are then selected last for replacement.

Unfortunately the writer [Deitel 83] does not compare the performance of the techniques described by him. This could be a subject of further investigation.

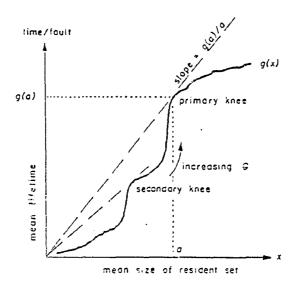

Figure 4.1: A typical lifetime function.

#### The working set principle

It has been shown by many authors of whom [Denning 72], [Denning 80] is the most notable that it models the memory demand of a running program very well. The principle states that the working set is the set of pages used during the most recent sample interval. Algorithms for exercising working set control is given in [Denning 80]. The same author has shown that it is a policy which performs very well because all the stack algorithms are just special cases of this policy [Denning 80].

This policy also provide the mechanism to remove from memory all those pages not to be referenced in the next time interval, thereby creating open page slots for either prediction or a sudden surge of new pages requested.

The key parameter in the working set algorithm is the inter-reference interval [Gupta 78]. This is the time between successive references to the same page. The idea is that pages not referenced for a time T will not be referenced soon and could therefor be removed from the working set. In the case where memory is bounded and filled with pages all referenced within time shorter than T, this algorithm is exactly the same as the LRU algorithm. It increases performance of the system in those cases where there are more than one page not referenced within time T. These pages can then be removed from memory to make space for either the surge or predicted pages as mentioned before. It is in this last context that it might be of relevance to the TVM system.

The previous paragraph describes the principle of working sets, but it is in general not easily implemented. Another way to determine the optimum working set size is through use of the lifetime function. This function g(x) gives the mean number of references between page faults when the resident set size is x. These functions have been shown to exhibit a knee, fig. 4.1. This kneed corresponds to the 'optimum' working set size of the program whose lifetime function

Figure 4.2: Life time knee nd space time minimum.

has been measured. In [Denning 80] he goes on to show that of all the criteria to maintain the smallest working set size, holding the working set size near to the corresponding knee size is the most robust.

Recall that the parameter which is a measure of the efficient use of memory is the space-time product. This measure has also been shown to be within 2 % of its minimum on the knee of the life-time function. See fig 4.2 for an example.

The working set policy as well as the next policy called page fault frequency are both so called *local* policies. This applies in a multiprogramming environment where the choice is between managing all the pages at the same time or managing each processes pages as a unit. The last mentioned option is referred to as local. It has been shown that for a high level of multiprogramming with small jobs the local policies perform better [Denning 80]. But for king size jobs the two policies exhibit performance of equal magnitude [Oliver 74].

#### Page fault frequency algorithm

The page fault frequency algorithm was introduced by Chu and Opderbeck which was to be an easily implemented alternative to WS [Denning 80]. It relies only on hardware usage bits and

an interval timer and is invoked only on page faults. This makes this policy easy to implement on most hardware bases.

For the page fault frequency algorithm the locality set of pages is estimated by observing the page fault rate. If the fault rate is greater than P, the allocation of pages is increased. If the fault rate is lower than P the allocation of pages is decreased. The fault rate is indirectly measured by considering the interfault interval. If this interval is less than 1/P then at the time of a page fault an extra page is allocated. If this interval is more than 1/P then the allocation is decreased by paging out all those pages not referenced within this interval.

The above algorithm described in [Gupta 78] also reverts to a LRU in a bounded memory buffer where all the pages have been allocated. There is still performance to be gained even in a fixed size buffer with this mechanism as mentioned in the previous section.

The writer [Gupta 78] goes on to investigate the sensitivity of the working set algorithm and the page fault frequency algorithm and concludes that the working set algorithm maintains a better representation of the working set over a much wider class of processes executing in virtual memory.

## 4.4 Page prediction strategies

## 4.4.1 Demand prepaging

Prepaging has been the subject of research from the very start of virtual memory systems. It has however not been widespread implemented. This can be attributed to the following [Trivedi 76]:

- 1. Difficult to implement.

- 2. If probability of wrong prediction is high, page faults may increase.

- 3. It may increase 'page pulls' significantly.

The same author then goes on to define an optimal demand prepage algorithm which is not realizable, but provides an upper bound on performance attainable with demand prepaging algorithms. This algorithm can shortly be described by:

```

event ? page fault

scan future reference string

fetch the first c pages that will be referenced in future

goto event

```

It can be clearly seen that for this algorithm to work a complete future reference string must be available to the page fault handler. This could be obtained by running the program once and recording its references, but in general this would not be possible.

The same algorithm is proven not to be a stack algorithm. Stack algorithms has the property that the page fault rate decreases with increasing buffer size. But for this algorithm alone it can be proved that with increasing c the page fault rate is a non-increasing function.

[Trivedi 76] goes on to investigate two approximations to the optimal algorithm. Two bits of information are associated with each page. One called the dead bit which indicates that the page involved can be removed. The other being a prepage bit which indicates that the page should be made available in the main store as soon as possible. One principle adhered to is that no predicted pages can be pulled in if there aren't any dead pages around. This prevents the prepage mechanism to negatively influence the demand mechanism when the prediction mechanism would make the wrong decision. The algorithm in pseudo code then is:

```

event ? page fault

remove all dead pages from memory (Free dead pages)

get page demanded

from list of pages marked as prepaged pull in as many as

there is space

goto event

```

Where this freing mechanism is utilized the prefix F is added to the replacement policy eg. LRU becomes FLRU.

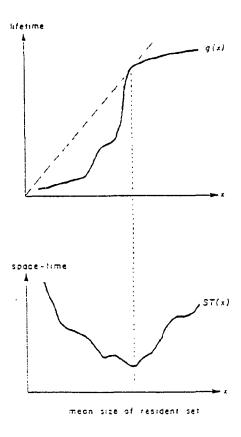

The same author then compares the performance of this algorithm called FDPLRU, with the optimal algorithm DPMIN and with conventional demand page only replacement algorithms on the specific problem of matrix operations. There are some remarkable improvements over all the matrix operations. The graph for matrix multiplication is given in fig 4.3. The notation is as follow:

```

n_1 dimension of full matrix m dimension of sub matrices c=m^2 \pi(c) the number of page faults with c pages available

```

The page replacement algorithms compared are:

- LRU. Least Recently Used.

- FLRU. Free policy combined with LRU.

#### CHAPTER 4. MEMORY MANAGEMENT

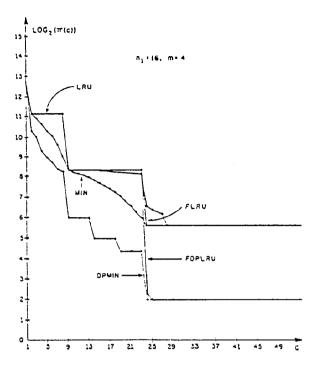

Figure 4.3: The effect of prepaging on matrix multiplication.

- MIN. Optimal page replacement algorithm as defined by [Denning 70] and [Belady 66].

- FDPLRU. Free policy, Demand Prepaging, LRU policy.

- DPMIN. Optimal prepaging algorithm as suggested by [Trivedi 76].

It has been shown that given the following assumptions, there is a significant decline in the number of page faults if a prepaging algorithm is used in a matrix environment. The assumptions are:

- The programmer must know the memory reference pattern of his program with regard to dead pages and prepagable pages.

- There must exist a mechanism to represent this information in the program and to transfer this information timely to the memory manager process.

- The rise in the number of prepage pulls must either overlap other disk operations or not be significantly higher than the case where no prepaging is done. It will be shown later for the TVM system that the number of page pulls has a much more profound effect on the execution time as the number of page faults.

- From the previous point it is clear that the measure for comparison by [Trivedi 76] was taken as page faults alone. It has been discussed under performance measures why this cannot be taken as the only measure.

The above two assumptions can easily be realized in a library environment where the effort to calculate the parameters are only done once. Further it will be shown that this should be the method of preference for implementing prepaging on the TVM system.

Another important observation from fig 4.3 is that freing dead pages does not lead to a significant decline in the number of page faults. This is contrary to the authors earlier remarks that having empty pages to cope with emergencies might improve performance.

# 4.4.2 Sequential prepaging

Another author investigated the improvements realizable with sequential prefetching. That is whenever a page is referenced its successor is also pulled in from secondary storage. The conclusions reached by [Smith 78] are:

- 1. Sequential prefetching is most effective for small page sizes ie. 32 to 64 bytes as performance degrade for bigger page sizes.

- 2. For such a strategy to work it must be efficiently implemented.

- 3. A 10% to 25% improvement in the execution speed has been measured.

The above conclusions make one big assumption ie. that the transfer time increases with some linear function for increasing page size. This is only true of a cache system where the source of the pages is the main memory. In a virtual memory system the average cost of transferring a page from disk to main memory is almost constant up to 1000 words. Refer to hardware paragraph on page size influences.

The fact that can be deduced from the above is that in general it would not pay to implement sequential prefetching unless the prefetching disk access time can be overlapped with another demand paged access time. It will be shown that because of the secondary storage organization in the TVM this it is indeed possible to overlap disk operations and sequential prefetching thus becomes a viable alternative to investigate.

## 4.4.3 Determining optimal buffer sizes.

In designing a virtual memory system with a multilevel memory system it is important to be able to determine the amount of memory that must be available in each level. [Mattson 70] showed that under certain conditions the size of the various levels could be played off against each other with reasonable precision.

The technique he developed takes an address trace and efficiently determines the exact number of references to each level of a c as a function of page size, replacement algorithm, number of levels and the capacity of each level. The conditions under which this analysis can be done are:

1. The replacement algorithm must induce a single priority list for all the levels.

#### CHAPTER 4. MEMORY MANAGEMENT

Figure 4.4: Obtaining access frequencies from a success function

2. The replacement algorithms must belong to the class of stack algorithms.

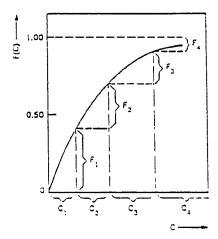

As a graphic example of this technique consider fig 4.4.3 where a success function for a given program is given. From this success function the various buffer capacities can be read off for certain access frequencies to the various levels.

The notation is:

- F(C) is the success function for the program running in unrestricted memory.

- $C_1...C_4$  are the buffer capacities at the various levels.

- $F_1, ... F_4$  are the relative access frequencies to the corresponding levels of memory.

The implications of this theory are immense. For a given algorithm class which is to run on a virtual memory machine it can be exactly determined what is the optimum configuration to minimize the execution time.

## 4.5 Other methods of improving performance

Of all the improvements that can be implemented to a virtual memory system there is one the user can make. The user can restructure the program to fit the underlying architecture better. This would in general require a lot of effort from a programmer who is actually using a virtual memory machine as a huge linear addressable memory space. [Hatfield 71] however has shown that improvements in the order of 2 to 1 up to 10 to 1 has been achieved by restructuring a program.

[Hatfield 71] has suggested three ways to improve the performance of a program running on a virtual memory machine. These are:

- 22

- 1. Minimize the number of page faults be constructing a nearness matrix to determine reordering of program parts that will reduce page faults.

- 2. Reordering and duplication of code usage.

- 3. Optimizing compilers.

From applying the first two principles the following conclusions were reached by him.

- 1. The method applied favoured bigger size pages because the effect of reordering code and data means that items referenced together are grouped in the same or adjacent pages.

- 2. Improvements an order of magnitude has been found.

The measures suggested by the author are in general difficult to apply. Again they could be implemented in a library where the effort is done once and utilized many times. There are however other guidelines which should be followed which will lead to a significant improvement with very little effort. These will be discussed under running programs efficiently in the TVM system.

# Part II Transputer virtual memory

# Chapter 5

## TVM Hardware

The transputer is a very fast microprocessor (10 MIPS) with an onboard scheduler and communication processors. A basic design aim was one processor per user. Thus no multiuser support in the form of memory management and protection have been included in the transputer. This includes a lack of virtual memory supporting hardware.

The TVM project started out in July 1988 to provide the transputer with viable virtual memory. The design was reported in September 1988 on by one of its inceptors [Bakkes 89]. The first design was completed in December 1988 by [Pina 89] and debugged in January 1989 by [Dorgeloh 89] and the author. The improvements in the first prototype was included in design of prototype 2 and this was again debugged by the author and [Dorgeloh 89]. Design revision three including more memory was completed and debugged. Through use of revision three a major design error was discovered; only one active window on virtual memory was available at any time. By now revision 4 was designed including even more real memory and parity checking. This design was never realized.

Revision 5 was designed by the author and completely debugged by March 1990. Revision 5 included up to 16 simultaneous active windows on the virtual memory, overcoming the main problem of earlier versions.

In all the designs the system parameters were determined by the available technology. Never were there any study to determine the optimum size for any of the system parameters. For example the main memory is now selectable between 4 Megabytes and 8 Megabytes. This technology is currently very cheap. In the earlier designs only 2 Megabytes were available. Regardless of the fact that no in depth study was made to determine optimum parameters, a viable system was realized. The question were how ever, how 'good' is the system?

This chapter goes on to describe the basic architecture. The optimal parameters for TVM will then be determined. The performance implications of the TVM architecture will then be compared to other systems. The final details of the hardware can be found in appendix A.

#### 5.1 Basic architecture mechanisms

The TVM system consists of three distinct subsystems viz.

- 1. Two transputers each with its private memory and a method to stop the one transputer in the address phase of an instruction.

- 2. A system memory hierarchy as seen from the one transputer.

- 3. An address translation unit for the one transputer to address more than its physical memory.

The first two subsystems contain some unique features not found in other virtual memory machines. The last subsystem is just an implementation of a mechanism inherently found in all virtual memory systems. Each of these will now be described in more detail.

The following notation will be used in the rest of the report.

main transputer Also called the user transputer is the processor the virtual memory is supplied for. Abbreviated: XU.

memory manage unit The second transputer on the TVM system. Also called the controller. Abbreviated: XC.

main memory The physical memory associated with the XU.

cache The window in the XU memory space available to point to virtual memory. It does not include the main memory.

active cache The section of the cache available to point simultaneously into virtual memory.

non-active cache The part of the cache not allocated to the active cache.

window The memory managed by the XC not visible to XU, but faster than the disk.

secondary memory Also referred to as disk memory.

### 5.1.1 Two processor system

The transputer not having any virtual memory support in hardware such as a restartable instruction, must be immediately stopped and isolated from its memory on detection of a page fault. The only way to achieve this with a transputer is to put it in wait. This leaves no processing power available to process the page fault. Another processor is thus needed.

This second processor chosen was also a transputer. This facilitated easier common access to the same memory and provided a fast processor to handle the page faults in the shortest time. Using a second processor also meant that memory management could carry on while the main

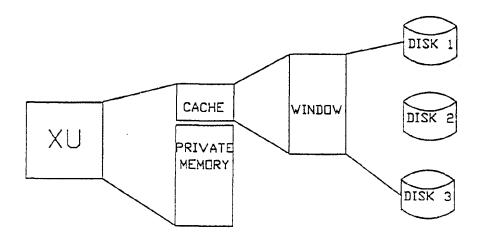

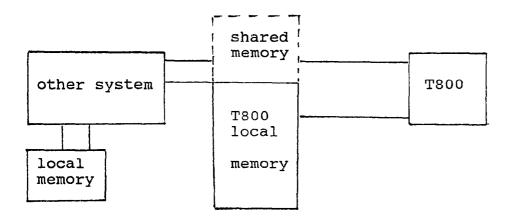

Figure 5.1: Simplified memory hierarchy diagram.

processor was not generating a page fault! This provides for the first level of parallelism in the system which is not found in other systems.

The other significant advantage of the second processor is that a mechanism have been provided to implement a multiprogramming environment on the transputer supporting memory protection! This can be done because the operating system would then reside over the two processors with the second transputer implementing amongst other operations the memory protection function.

### 5.1.2 Memory hierarchy

The two processor model also brought with it its share of problems. Allowing common access to dynamic memory can be done, but the circuitry becomes complex. This last problem is manifested in the hand back cycle where a valid RAS cycle must be reconstructed by the XC. One solution for the problem was to use static ram for the shared memory. This again implied for the same PCB space less memory could be accommodated. This last decision lead to another deviation from conventional architectures.

To provide the main transputer with 1 Megabyte or more of static RAM was at the time of the project definition too expensive, component wise and PCB space wise. So it was decided to create a much smaller window onto the virtual address space viz. 256kbyte. This smaller window will henceforth be called the cache. The rest of the memory which would normally be found on a processor ie. 1 Megabyte to 8 Megabyte, would still be provided to the main transputer but without any ability to swap pages into and out from this memory. The performance implications of this design decision will be dealt with in section 5.4.

The XC processor doing the memory management also needed some memory of its own to run

the memory management software. But primarily it needed memory to keep the page tables in. The size of the controller memory is primarily determined by the page size, because this in turn determines how many pages will fit into the virtual memory space provided. The first versions had 2 Megabyte of memory which would not provide for all the space needed when 1 kbyte pages were used in a 2 Gigabyte virtual memory, but if the need arose the page table itself could be kept on disk and only the current section in use could be kept in the XC's main memory. Fig 5.1 illustrates the full memory hierarchy.

The page size is also determined by the transfer speed of the different page sizes from disk. The page size also depend on management parameters. For instance is the program restructured to localize execution? If so, larger pages will give better performance. The optimal page size is thus not a cut and dry case.

The main determiner of page size came from quite a different source. Hardware considerations have played the major role from the start in determining the page size. In the early hardware versions the page size went from 1kbyte to 256kbyte. Where the upper limit is just due to the size of the cache. This smallest page size fitted just into the width of the comparitors and registers used which made it a handy size. These page sizes were to be more or less compatible with existing virtual memory systems where a page size from 512 bytes to 16kbytes have been reported.

During the redesign of the address translation mechanism the minimum page size was changed to 16kbyte. This again was due to hardware considerations as it saved enough PCB space so that four of these mechanism could fit on the same PCB piggyback. The effect of this page size change will be discussed in the section on optimal parameters for the TVM system.

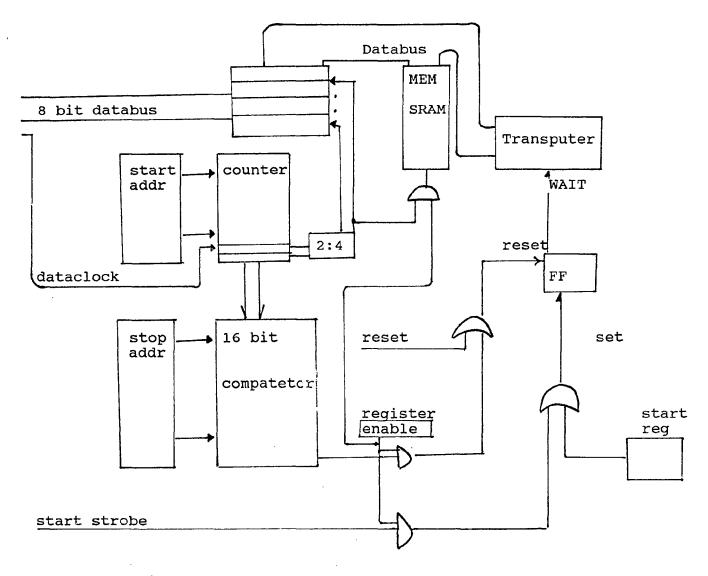

## 5.1.3 Hardware in support of TVM

The hardware needed to support virtual memory on the main transputer consists of a stopping mechanism which has to cut of the XU control signals to main memory before they take effect and it must put the XU in wait. The first action is the most important and implies that a decision on page fault must be taken in the first section of the address phase.

A hand back mechanism must also exist which allow the XC to hand control of the main memory and the cache back to the XU. This mechanism in the case of dynamic memory must reconstruct a valid RAS cycle before handing back. In general this is difficult and therefor a static ram sharable cache was designed. The address from the XU processor have to be redirected in the active cache to the correct corresponding address. This mechanism is done with bitforcing the corresponding cache page address.

The address translation mechanism to force a XU address onto a page in the cache is the most important parameter in any virtual memory system. In the first three versions of the hardware there were only one such mechanism or also called an active cache page. This meant that a program running in virtual memory with its code in one location and just one data structure at another location would incur a page fault cost for every instruction fetched and every data item referenced. This page fault cost was to be small if the page to be referenced would be in

the rest of the cache. It was possible to bring this page fault handling time down to  $10\mu s$ . But this just constituted a  $1/10\mu s = 100kHz$  computer! This is clearly not a step forward.

The author then redesigned the mapping mechanism to incorporate up to 16 active cache pages. This meant that 16 disjoint areas in the virtual memory space could be addressed at the same time. This is also in line with existing architectures [Hyde 88] which describes Motorola devices supporting from 16 to 64 active cache pages simultaneously. The question arises is 16 enough? This will be answered in the next section when the optimal amount of active cache pages will be predicted for the TVM system.

The mapping mechanism described above is exactly equivalent to the mechanism described by [Deitel 83]. Thus it will be of interest to determine whether the 90 % performance marked could be reached.

Various other subsystems exist, but the above are the only relevant to a performance analysis of the TVM system.

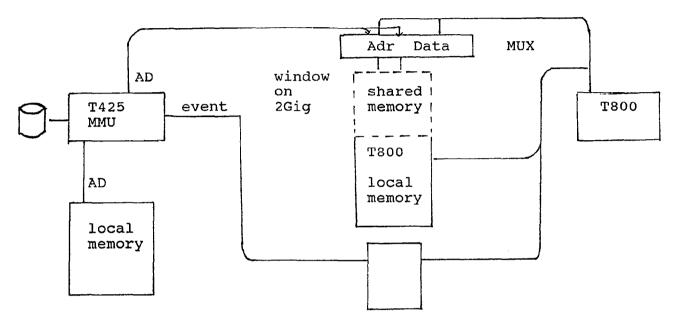

## 5.2 TVM system architecture

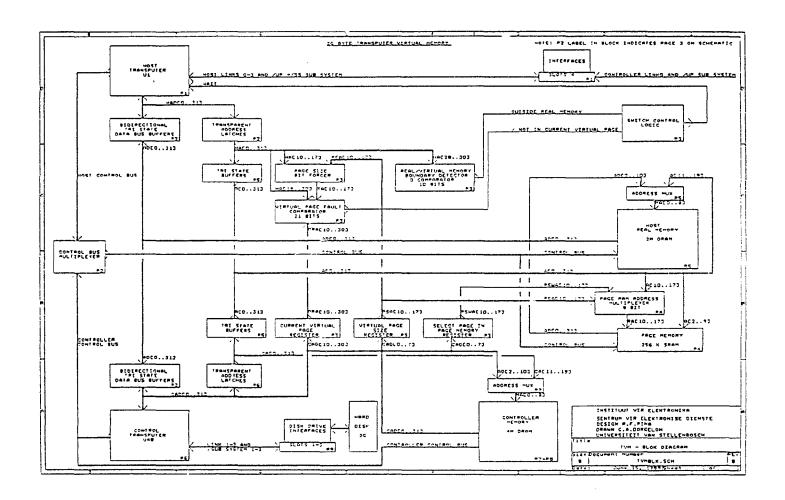

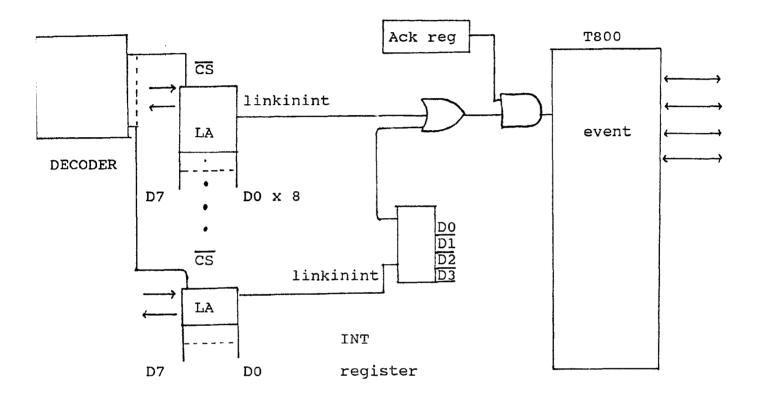

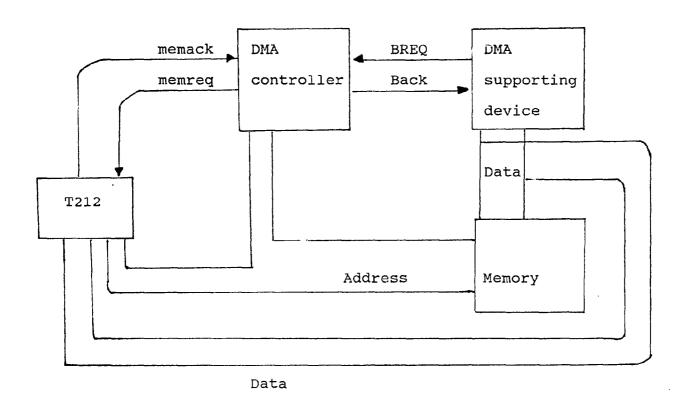

The complete TVM system architecture for one active register set is given in fig 5.2. The parts in green are duplicated for each active register set. The detailed schematic diagrams, PAL device listings and register legends can be found in appendix A.

The system parameters for the various buffers are:

active cache up to 16 pages in 4 page increments.

window up to 8 Megabyte in 4 Megabyte increments.

page size from 16 kbyte to 256 kbyte.

## 5.3 Optimal parameters for TVM

This section will evaluate the effectiveness of the various memory hierarchy levels and the page size. An optimum will be determined in every case.

To evaluate a virtual memory system the various workloads to be run on it must be investigated. In the case of the TVM the fact that virtual memory starts only after the main memory of the XU transputer implies that a very small subset of applications need to be considered in evaluating the performance of the TVM. For instance all compilations, editing and programs with small memory requirements will run in the main memory without ever using the virtual memory. This means that NO performance penalty is paid using the virtual memory system for smaller problems.

Figure 5.2: Block diagram of TVM system.

From the previous paragraph it is clear that the only application programs of interest are those with memory requirements greater than the available main memory. In this category are only a few applications. One being the manipulation of large matrices and the other a large data base. So it is necessary to evaluate the TVM system only for these problem classes.

The benchmarks chosen will be run in virtual memory alone. This means that no section of the program will run in the real memory provided with the XU. This imply that the virtual memory alone is evaluated and no second order effects due to the real memory need to be considered.

Notice that nowhere was there any reference to multiuser applications as this does not make sense in a transputer environment with one processor per user. Even though the conventional virtual memory systems were implemented for better CPU and system utilization in a multi-programming environment, the TVM implementation of virtual memory again tries to provide a large address space as intended by virtual memory in the first place.

#### 5.3.1 The benchmarks

The two benchmarks ran to evaluate the TVM system are the following programs for which the memory requirements can easily be adjusted to evaluate certain parameters.

$$A = A * A^{-1}$$

$$B = 1/max(B) * B$$

#### The matrix benchmark.

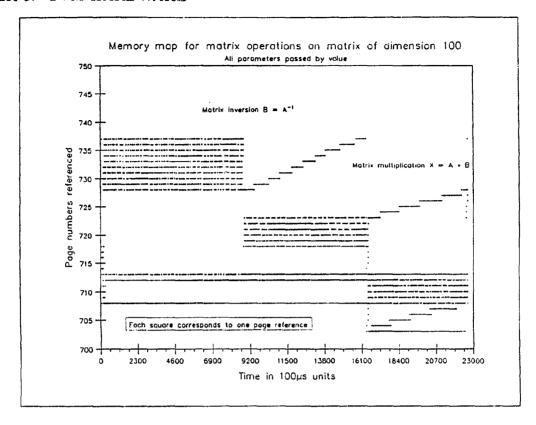

The first benchmark generates the matrix A with random numbers, inverts the matrix and then multiplies it with itself. This results in the identity matrix as answer. This program will be referred to as MATRIX. For the dimension of A given as N the memory requirement is the relation  $56 * N^2$  for the algorithm with parameters passed by value and  $40 * N^2$  for parameters passed by reference.

Of particular interest is the memory map produced when running this benchmark. The memory reference map gives an indication of the locality of the program, which in turn provides the user with feedback on whether to restructure his program and on the optimum number of active cache pages to use.

The memory map for the basic matrix algorithm with pass by value parameters is given in fig 5.3. When comparing this with the memory map for the pass by reference, it is clear that the pass by value implies a copying of the data structures before it is used inside a procedure.

From the memory map one could deduce that the working set size of the matrix inversion is eleven pages. This however corresponds to the complete data structure accessed during the inversion operation. The time interval resolution is to course to make a clear distinction of

Figure 5.3: The memory map for mat100 with VAL parameters and VAR parameters.

exactly how many pages are required. It will be shown that only a fraction of the data structure size need be accessed simultaneously for efficient execution in the TVM system.

The courseness of the memory reference map stems from the sampled nature of the memory map. There are from eight upwards pages sampled at the same instant depending on the sampling interval. These eight pages correspond to the eight active cache pages. Because the implemented algorithm does not yet detect all the pages' status on each page fault, the information as to which pages were not accessed during a specific interval are not yet available. Under close examination it is clear that there are eight or more samples in any one column. This gives rise to not being able to deduce the efficient working set size from the memory map. The information contained in the memory map is of interest though as it shows clearly the locality of the program execution versus time.

The question now arise how would the memory map develope if more data structures were to be accessed simultaneously. The matrix benchmark was expanded so that during the multiplication phase more and more data structures were accessed simultaneously. The memory reference maps for increasing number of data structures can be found in fig 5.4. From the results given it is clear that for each additional data structure and additional active cache page would result in a performance improvement.

The second memory reference map of the two uses enough simultaneous active cache pages to make the pattern clearly visible despite the resolution courseness. The memory reference pattern of the B matrix is now also clearly visible.

#### Normalising benchmark.

The second benchmark generates a vector of random numbers, scans the whole vector to determine the maximum value and then divide the vector with the maximum. This program will be referred to as NORM. The memory requirements for the program is 8 \* M where M is the dimension of the vector operated on.

The memory reference map for the NORM benchmark is given in fig 5.5. It is quite like one would expect given the resolution problem. Clearly the data structure is scanned three times during the execution of the program.

#### Default TVM system parameters.

The memory management software running in all the benchmarks under the hardware chapter uses a FIFO page replacement algorithm on all three memory levels. Further demand paging is utilized. If nothing else about the size of any of the variables is said assume the following.

- 1. The active cache size is 8.

- 2. The non active cache size is 8.

- 3. The window size is 128.

Figure 5.4: Memory maps for increasing number of simultaneous accessed data structures.

Figure 5.5: Memory map for the NORM benchmark.

4. The benchmark program is run in virtual memory mapped at 20 Megabyte.

#### 5.3.2 The measure for comparison

The measure for comparison used in all the hardware evaluations is primarily the execution time. This deviates from the specific measures such as number of page faults, number of page pulls and the success function described in section 4.2. This is because the execution time incorporates all the individual measures and with the correct weight function. The other measures would then just be used where execution time does not provided any information w.r.t. an improvement or deterioration of performance.

#### 5.3.3 The active cache size

This is one of the two single most important parameters in any virtual memory system. In section 3.2.3 it was already reported the lessons learnt from using only one active cache page. The question now is what is the optimum size for the active cache?

The answer is, it depends on the workload being run in the following way. Take for instance the database search program. If run completely in virtual memory ie. code and data, the number of simultaneous accessed sections in the virtual address space depends on which phase the program is in. During the initialization phase there is the code (which may be fragmented over two pages) and one data structure. This implies at most three active cache pages will be enough at any given time to address any place in the initial matrix. During the scanning phase it is only the code and one data structure again only two pages are needed. The same applies for the normalising phase. So it would be reasonable to expect that two or at most three active cache pages would give the same performance benefit as four or more pages would give.

The above argument rests on the assumption that the application program does not reference one data item per page before jumping to another page. In the latter case the minimum number of active cache pages giving acceptable performance would be far greater. It will be shown in section 6.5 that for the application classes the TVM needs to be evaluated, the data can be restructured in most cases to localize accesses. In the latter case the argument in the previous paragraph is valid.

#### Executing benchmark normalise

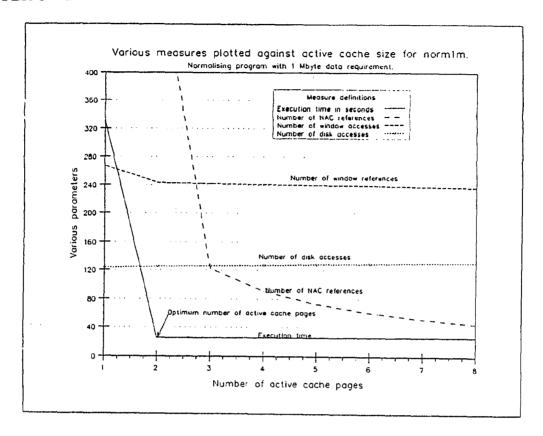

The normalise benchmark was discussed in section 5.3.1 and from the memory reference map there and the knowledge about the problem behaviour it is expected that the NORM benchmark will not run significantly faster in three or more active cache pages than in two active cache pages. Considering fig 5.6 it is clearly seen that increasing the number of active cache pages above two has no significant effect on the execution time. Also shown on the graph are the number of references to the non-active cache, window and disk for each active cache size.

Figure 5.6: Norm program: execution time against increasing active cache size.

From the figure can be seen that as the active cache was made smaller, more and more references to the non active cache were made. At two active cache pages the number of active cache references increased substantially, but the execution time stayed constant. The number of disk accesses or page pulls decreased by one though. This supports the authors' argument that the number of page pulls alone is not a significant measure on its own.

Another interesting observation is that the number of page pulls decrease with decreasing active cache size. This is a by product of the FIFO replacement algorithm used which fares better with a smaller active cache.

#### The matrix benchmark.

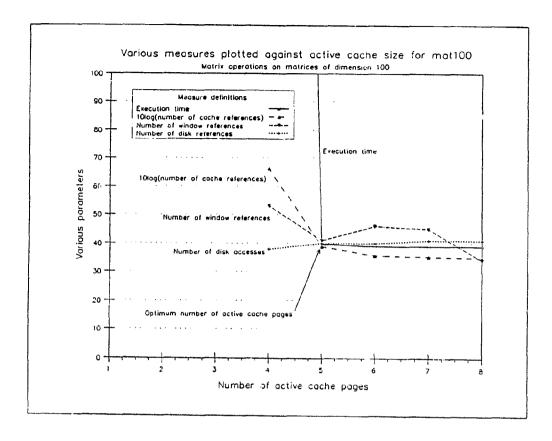

Considering the matrix application, there is also an optimal number of active cache pages, but it is more difficult to predict. The first phase consists of generating the matrix. This is similar to the database search problem so two pages should ensure optimum performance. The second phase consists of gaussian elimination to determine the inverse of a matrix. In this phase two rows of the matrix are accessed simultaneously in addition to the code. This leads to at least three pages being referenced simultaneous.

The last phase consists of a matrix multiplication where three data structures and the code is referenced at any one time. This implies at least four active cache pages for optimum results.

Figure 5.7: Matrix program: various parameters against active cache size.

The measured results are given in fig 5.7. From the graph it is clear that the minimum number of active cache pages required for optimal performance is five. Considering the memory map the it cannot clearly be seen why five is the optimum number. Instead looking at the first section of the memory map it seems that 11 pages would be optimum. This phenomena has been explained in section 5.3.1 as due to the sampled nature of the memory map.

From 5.7 it is observed that the number of page pulls is again a decreasing function and that the number of non active cache references again dominate. The number of window references reaches a local minimum at five active cache pages. This could be attributed to the FIFO replacement algorithm running on the active cache which would reach its optimum operating point at five active cache pages. Thus less wrong decisions would force pages out to the window.

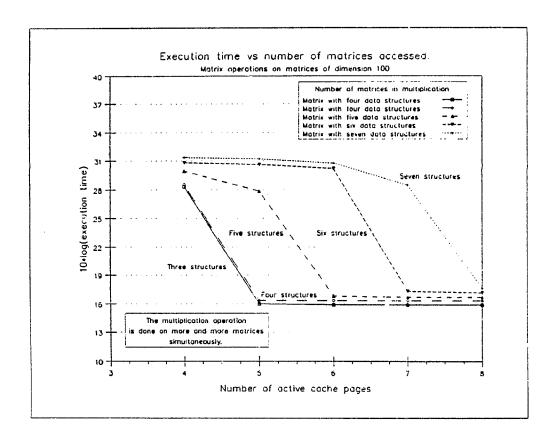

The TVM system as available at the time of the measurements had eight active cache pages to use. Another relevant question is how many simultaneous active data structures can be efficiently run with eight active cache pages? The number of data structures in the matrix multiplication phase were increased and the execution time and other parameters measured for this increase. The results are shown in fig 5.8. From the matrix multiplication phase it can clearly be seen the number of pages required to execute the operation efficiently.

From 5.8 it can be observed that the increase from three to four simultaneously accessed data structures in the multiplication phase has no detrimental effect on the execution time. This gives the clue that the inverse operation accesses four structures simultaneously. From four

Figure 5.8: Increasing the number of simultaneous accessed data structures.

Figure 5.9: Execution times for matrices of different dimensions against active cache size.

so uctures onwards it is clear that the multiplication phase dominates the execution time.

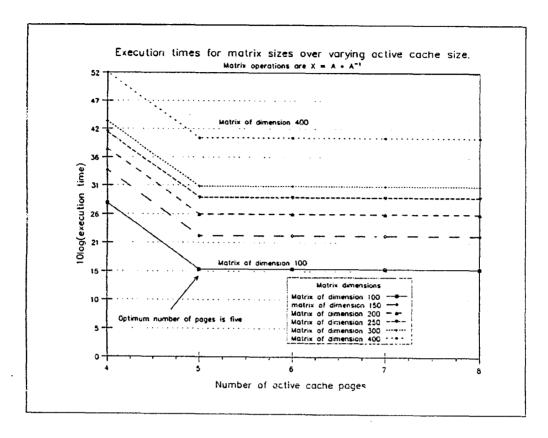

One result of particular importance is that it does not matter what the dimension of the matrix or vector is, it is the number of simultaneously accessed data structures which determine the optimum active cache size. See fig 5.9 for a comparison between the execution time for matrix dimensions N = 100, ... 400.

#### 5.3.4 The non-active cache size

The non-active cache refers to the cache not directly pointed to by the address translation mechanism, but the access time to it is still faster than the window because it only takes the overhead of updating the tables and moving the address translation pointers to address into this memory level. The total cost can be as low as  $20\mu s$  but is normally in the region of  $60\mu s$  to  $80\mu s$ . This high value depends on how much data is collected for each page fault.

It was decided to manage this as a separate memory level because in general the number of simultaneous active cache pages could be less than the available amount of so called cache pages.

The non-active cache could be or not be a first order influence on the performance of the virtual memory system. No where in literature has a similar structure been reported on. Although it

Figure 5.10: The improvement over one NAC in execution time for bigger NAC's.

corresponds exactly to the not directly addressable memory in conventional systems, its size is so small the results partaining to the conventional architectures does not apply.