## Predictive Control of a Series-Input, Parallel-Output, Back-to-Back, Flying-Capacitor Multilevel Converter

by

Daniël Josias du Toit

Thesis presented in partial fulfilment of the requirements for the degree of Master of Science in Engineering at Stellenbosch University

Department of Electrical and Electronic Engineering University of Stellenbosch Private Bag X1, 7602, Matieland, South Africa.

Supervisor: Prof. H. du T. Mouton

December 2011

## Declaration

By submitting this thesis electronically, I declare that the entirety of the work contained therein is my own, original work, that I am the owner of the copyright thereof (unless to the extent explicitly otherwise stated) and that I have not previously in its entirety or in part submitted it for obtaining any qualification.

November 2011

Copyright © 2011 Stellenbosch University All rights reserved.

## Summary

This thesis investigates the viability of constructing a solid-state transformer (SST) with a series-input, parallel-output connection of full-bridge, three-level flying-capacitor converters. It focusses on the active rectifier front-end of the SST which is used to control the input current to be sinusoidal and in-phase with the sinusoidal input voltage. A stack of two converters are built and tested. The input current, as well as the flying capacitor voltages of the two active rectifiers in the stack, are actively controlled by a finite-state model-based predictive (FS-MPC) controller.

The use of multiple flying-capacitor converters poses a problem when using FS-MPC because of the large number of possible switching states to include in the prediction equations. Three FS-MPC control algorithms are proposed to attempt to overcome the problem associated with the large number of switching states. They are implemented on an FPGA digital controller. The algorithms are compared on the bases of voltage and current errors, as well as their responses to disturbances that are introduced into the system. The simulation and experimental results that are presented shows that by interleaving the control actions for the two converters, one can obtain fast and robust responses of the controlled variables. The viability of extending the interleaving control algorithm beyond two converters is also motivated.

## Opsomming

Hierdie tesis ondersoek die moontlikheid van volbrug, drievlak vlieënde-kapasitoromsetters wat gebruik word om 'n serie-intree, parallel-uittree drywingselektroniese transformator (DET) te bou. Dit fokus op die aktiewe gelykrigter van die DET wat gebruik word om die intreestroom te beheer om sinusvormig en in fase met die sinusvormige intreespanning te wees. 'n Stapel van twee omsetters word gebou en getoets. Die intreestroom, sowel as die vlieënde kapasitorspannings van die twee aktiewe gelykrigters in die stapel, word aktief beheer met behulp van 'n eindige-toestand, model-gebaseerde voorspellende beheerder (ET-MVB).

Die gebruik van veelvuldige vlieënde-kapasitoromsetters bemoeilik die implementering van 'n ET-MVB-beheerder as gevolg van die groot aantal skakeltoestande wat in die voorspellende vergelykings in ag geneem moet word. Drie ET-MVB-algoritmes word voorgestel om te poog om die probleme, wat met die groot aantal skakeltoestande geassosieer word, te oorkom. Die algoritmes word in 'n FPGA digitale verwerker geïmplementeer. Die algoritmes word vergelyk op grond van hul stroom- en spanningsfoute, asook hul reaksie op steurings wat op die stelsel ingevoer word. Die simulasie en praktiese resultate toon dat, deur die beheeraksies vir die twee omsetters te laat oorvleuel, die gedrag van die beheerde veranderlikes vinniger en meer robuust is. Die moontlikheid om die oorvleuelende beheeraksies uit te brei tot meer as twee omsetters word ook gemotiveer.

## Acknowledgements

I would like to extend my gratitude to the following persons:

My supervisor, Prof. H. du T. Mouton, for his guidance and for providing me the opportunity of continuing my studies.

The Wilhelm Frank Trustees for providing me with the financial support necessary to complete my studies.

Wim van der Merwe, Louis Schietekat and Francois Breet for their assistance in the design and implementation of the hardware and software used in this project.

My parents and fiancée for their support, love and encouragement.

## Contents

| De            | eclara | i                          |

|---------------|--------|----------------------------|

| Su            | ımma   | ii                         |

| Oj            | psom   | ming                       |

| A             | cknov  | vledgements iv             |

| Co            | onter  | ts                         |

| $\mathbf{Li}$ | st of  | Figures x                  |

| $\mathbf{Li}$ | st of  | Tables xiv                 |

| No            | omen   | clature xv                 |

| 1             | Intr   | oduction 1                 |

|               | 1.1    | Background                 |

|               | 1.2    | Study Objectives           |

|               | 1.3    | Thesis Overview            |

| <b>2</b>      | The    | Solid-State Transformer 8  |

|               | 2.1    | Converter Overview         |

|               | 2.2    | Bus Voltage Balancing      |

|               | 2.3    | Control                    |

|               | 2.4    | Summary                    |

| 3             | Dio    | de-Clamped Converter 14    |

|               | 3.1    | Converter Layout           |

|               | 3.2    | Basic Operation            |

|               |        | 3.2.1 Voltage Synthesizing |

|               |        | 3.2.2 Clamping Mechanism   |

|               | 3.3    | Voltage Balancing          |

|          | 3.4  | Simula  | ations                     | 18        |

|----------|------|---------|----------------------------|-----------|

|          |      | 3.4.1   | PD PWM Scheme              | 20        |

|          |      | 3.4.2   | APOD PWM Scheme            | 20        |

|          | 3.5  | Summ    | ary                        | 22        |

| 4        | Flyi | ing-Ca  | pacitor Converter          | <b>24</b> |

|          | 4.1  | Conve   | rter Layout                | 25        |

|          | 4.2  | Basic   | Operation                  | 26        |

|          |      | 4.2.1   | Voltage Synthesizing       | 26        |

|          |      | 4.2.2   | Clamping Mechanism         | 27        |

|          | 4.3  | Voltag  | ge Balancing               | 27        |

|          | 4.4  | Simula  | ations                     | 29        |

|          |      | 4.4.1   | Pre-charging of Capacitors | 29        |

|          |      | 4.4.2   | PWM Scheme                 | 31        |

|          |      | 4.4.3   | Look-up Table              | 32        |

|          | 4.5  | Summ    | ary                        | 35        |

| <b>5</b> | Pre  | dictive | e Control                  | 36        |

|          | 5.1  | Contro  | ol Components              | 37        |

|          |      | 5.1.1   | Predictions                | 37        |

|          |      | 5.1.2   | System Model               | 37        |

|          |      | 5.1.3   | Cost Function              | 37        |

|          |      | 5.1.4   | Receding Horizon           | 37        |

|          |      | 5.1.5   | Computation                | 38        |

|          | 5.2  | Contro  | ol Methods                 | 38        |

|          |      | 5.2.1   | Hysteresis-based           | 38        |

|          |      | 5.2.2   | Trajectory                 | 39        |

|          |      | 5.2.3   | Deadbeat                   | 40        |

|          |      | 5.2.4   | Model-based                | 41        |

|          | 5.3  | Open-   | Loop vs Closed-Loop        | 42        |

|          | 5.4  | System  | n Modelling                | 43        |

|          | 5.5  | Appro   | ximations                  | 44        |

|          |      | 5.5.1   | Euler Forward              | 44        |

|          |      | 5.5.2   | Euler Backward             | 45        |

|          |      | 5.5.3   | Runge-Kutta                | 45        |

|          | 5.6  | Stabili | ity                        | 45        |

|          | 5.7  | Simula  | ation                      | 46        |

|          |      | 5.7.1   | Modelling                  | 47        |

| C( | ONTE | ENTS                              |   |      |      |   | vii |

|----|------|-----------------------------------|---|------|------|---|-----|

|    |      | 5.7.2 Simulation Results          |   | <br> | <br> |   | 48  |

|    | 5.8  | Summary                           |   | <br> | <br> |   | 48  |

| 6  | Con  | nverter Design                    |   |      |      |   | 50  |

|    | 6.1  | Active Rectifier                  |   | <br> | <br> |   | 51  |

|    |      | 6.1.1 Power Switches              |   | <br> | <br> |   | 52  |

|    |      | 6.1.2 DC-Link Capacitors          |   |      |      |   |     |

|    |      | 6.1.3 Boost Inductor              |   |      |      |   |     |

|    | 6.2  | Isolation Stage                   |   |      |      |   |     |

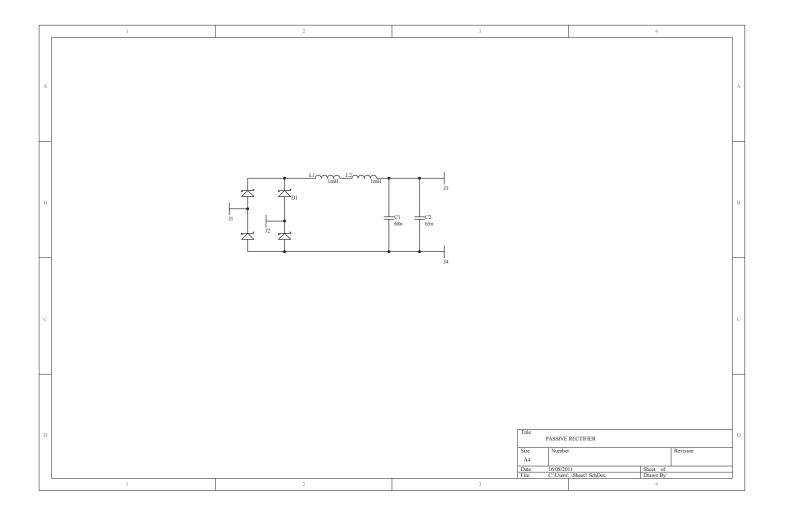

|    |      | 6.2.1 Passive Rectifier           |   | <br> | <br> |   | 59  |

|    |      | 6.2.2 Power Switches              |   | <br> | <br> |   | 61  |

|    |      | 6.2.3 DC-Link Capacitors          |   | <br> | <br> |   | 62  |

|    |      | 6.2.4 Transformer                 |   | <br> | <br> |   | 64  |

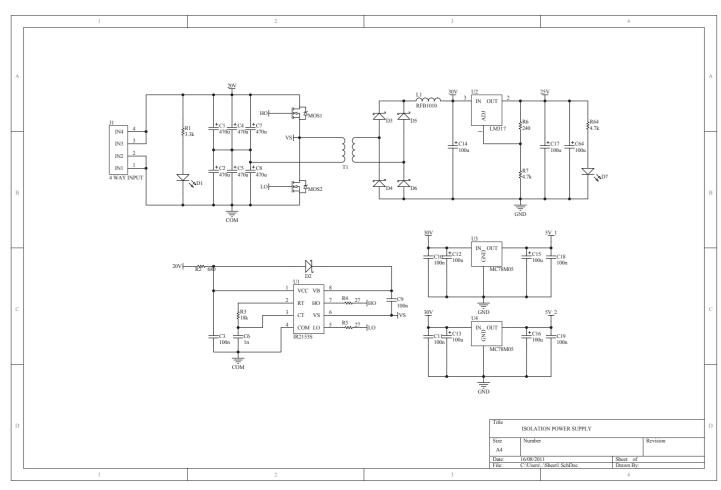

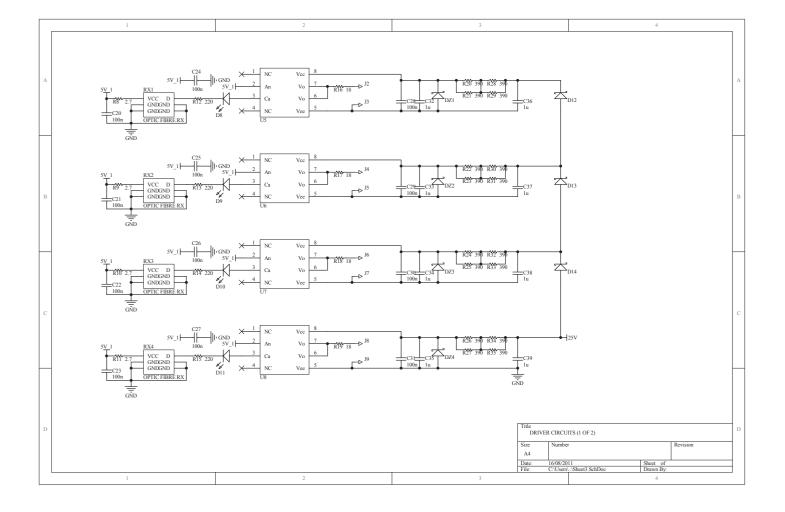

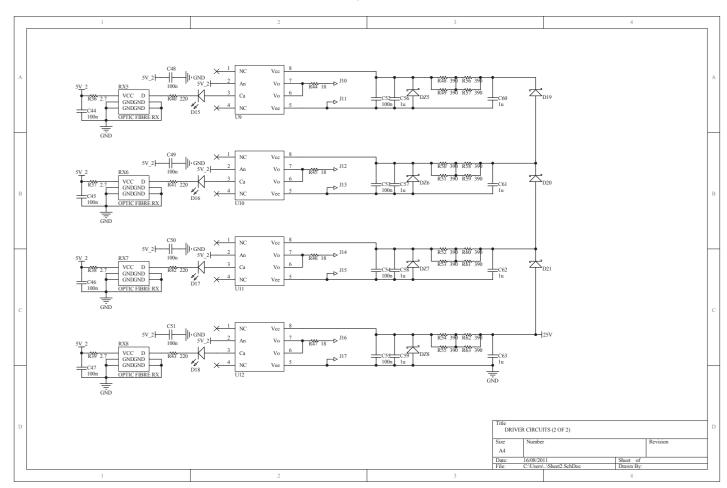

|    | 6.3  | Driver Circuits                   |   |      |      |   |     |

|    | 6.4  | Converter Hardware                |   |      |      |   |     |

|    | 6.5  | Summary                           |   |      |      |   |     |

| 7  | Con  | ntroller Design                   |   |      |      |   | 71  |

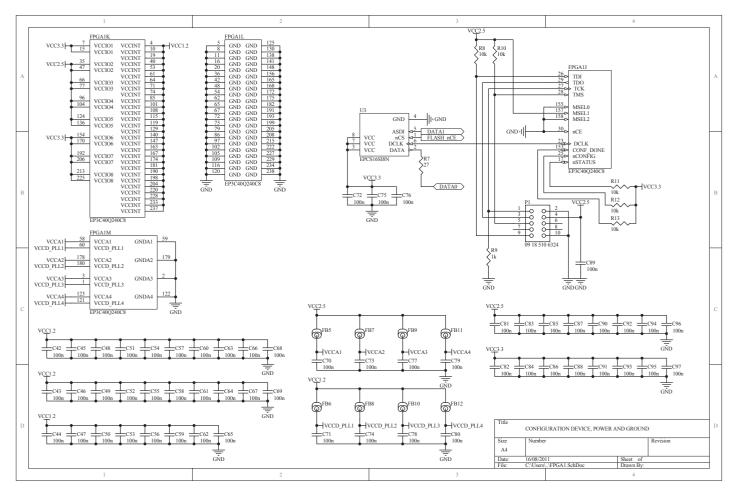

|    | 7.1  | FPGA vs DSP                       |   | <br> | <br> |   | 72  |

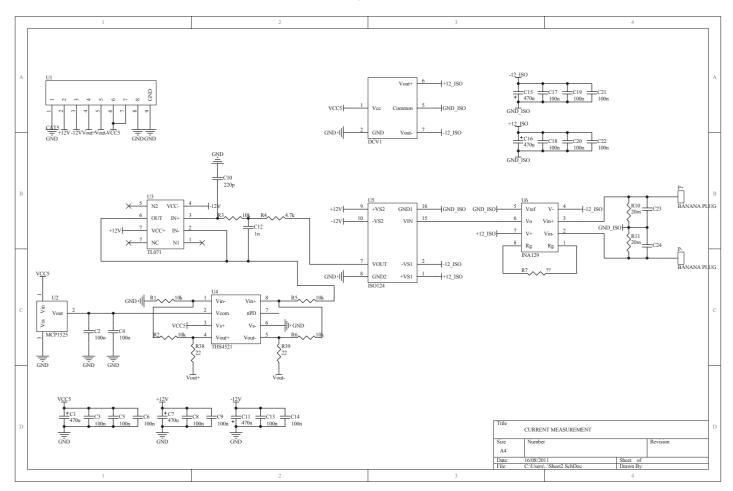

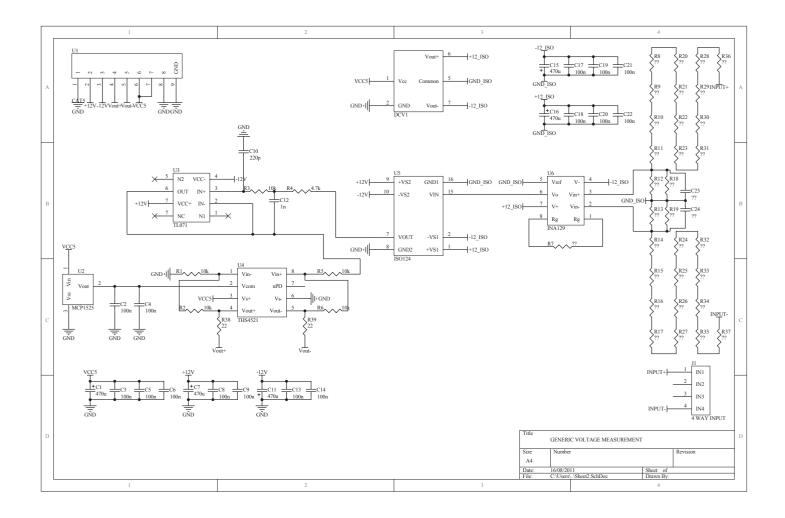

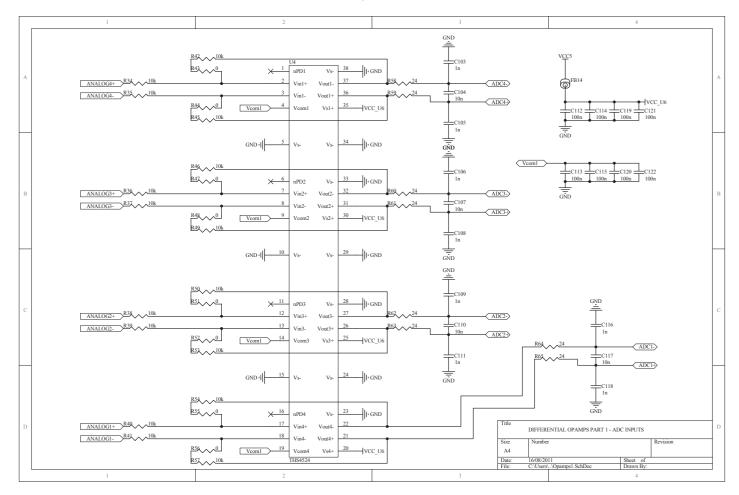

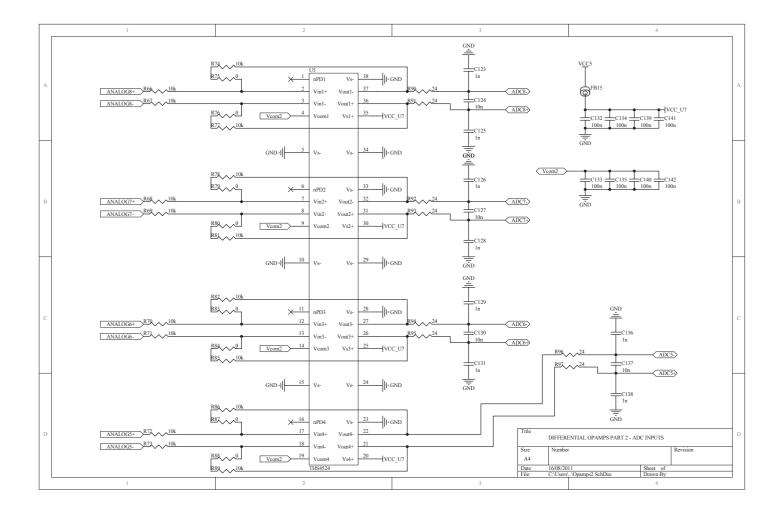

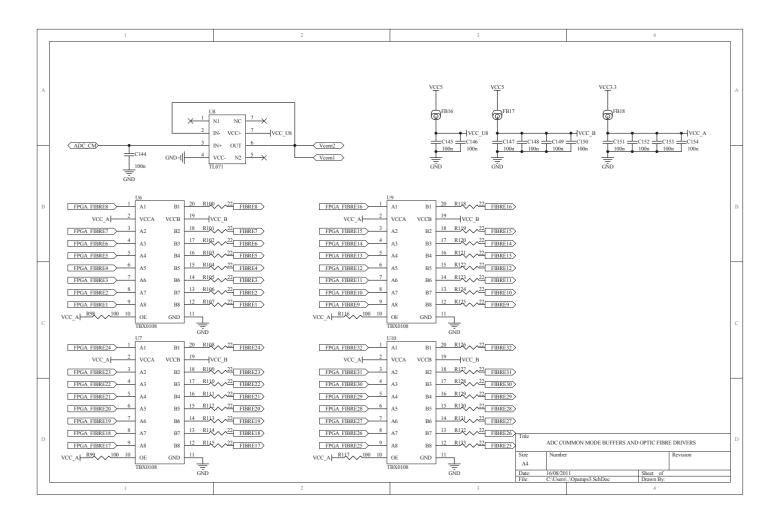

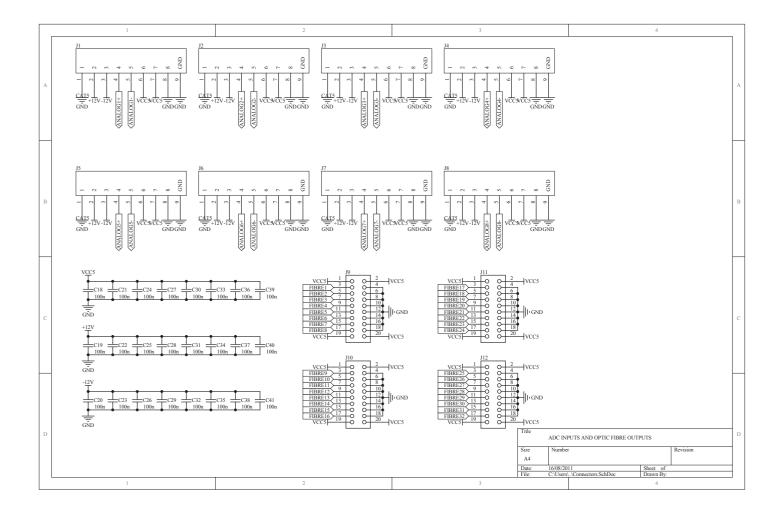

|    | 7.2  | Measurement Circuits              |   | <br> | <br> |   | 72  |

|    |      | 7.2.1 Voltage Measurement         |   |      |      |   |     |

|    |      | 7.2.2 Current Measurement         |   |      |      |   |     |

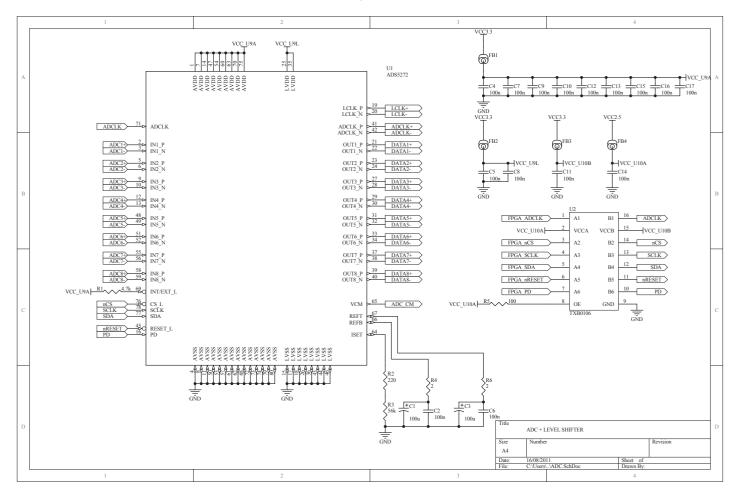

|    | 7.3  | Analogue-to-Digital Converter     |   |      |      |   |     |

|    | 7.4  | Switching Signals                 |   |      |      |   |     |

|    | 7.5  | Controller Hardware               |   |      |      |   |     |

|    |      | 7.5.1 FPGA Attributes             |   |      |      |   |     |

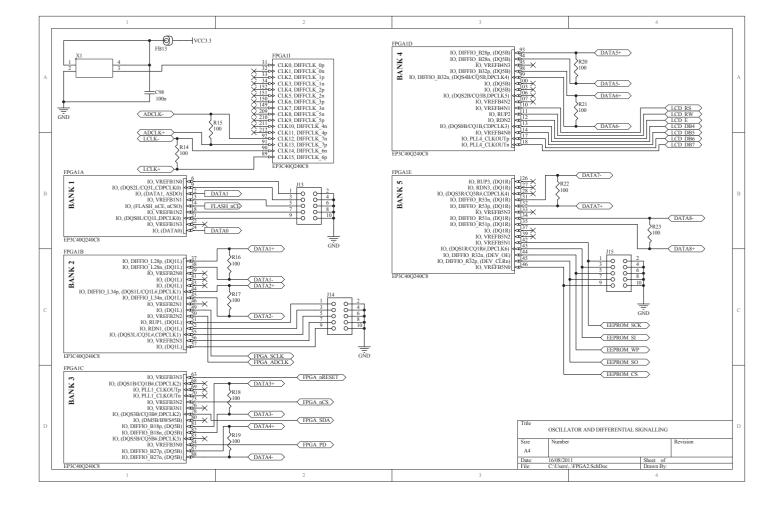

|    |      | 7.5.2 Low-Voltage Differential Si |   |      |      |   |     |

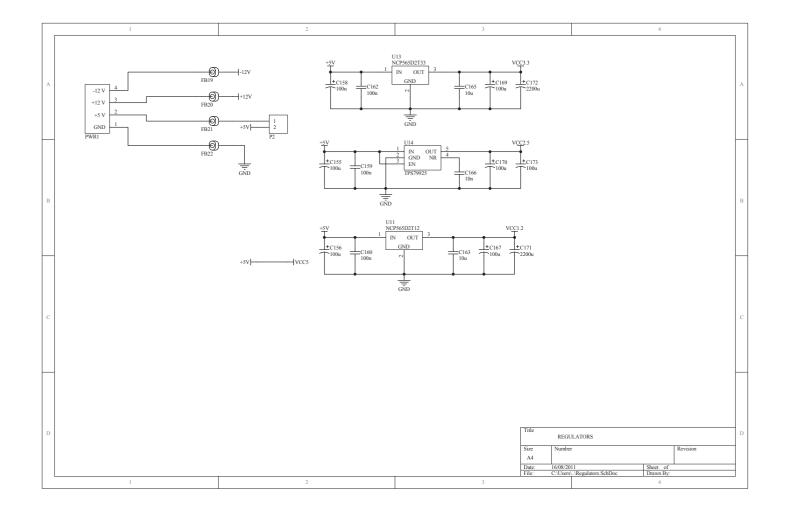

|    |      | 7.5.3 Power Management            | - |      |      |   |     |

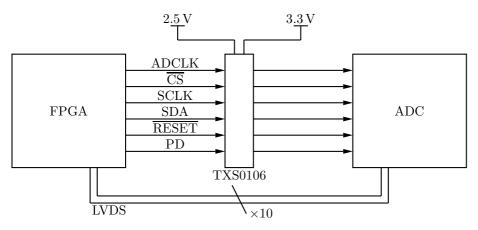

|    |      | 7.5.4 Voltage Level Shifters      |   | <br> | <br> |   | 81  |

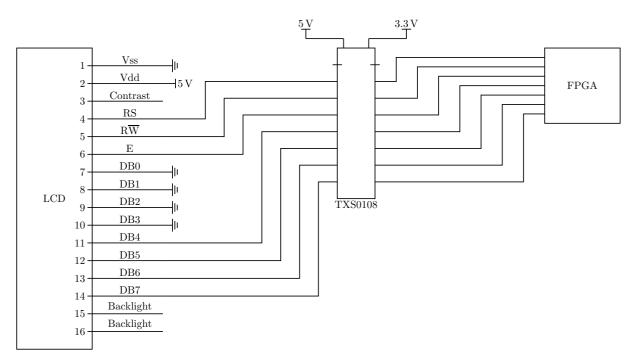

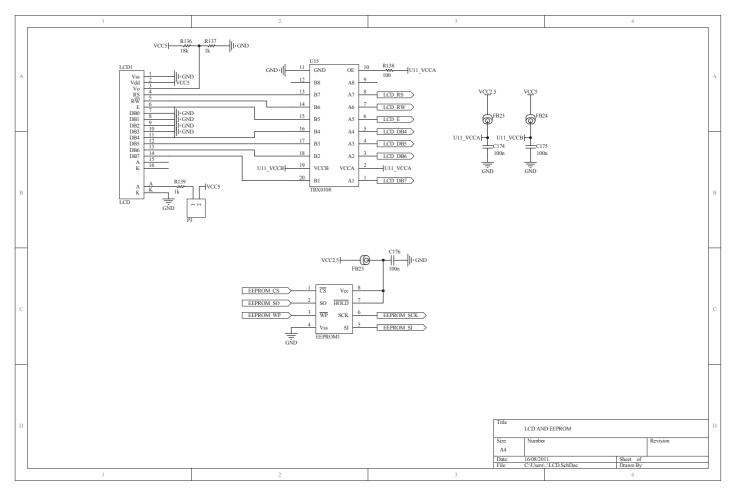

|    |      | 7.5.5 LCD Interface $\ldots$      |   |      |      |   |     |

|    | 7.6  | Control Algorithms                |   | <br> | <br> |   | 83  |

|    |      | 7.6.1 Isolation Stage             |   |      |      |   |     |

|    |      | 7.6.2 Cost Function Weights       |   |      |      |   |     |

|    |      | 7.6.3 Single Rectifier            |   |      |      |   |     |

|    |      | 7.6.4 Dual Rectifier              |   |      |      |   |     |

|    |      | 7.6.5 Voltage Regulation          |   |      |      |   |     |

|    |      | 7.6.6 Software                    |   |      |      |   |     |

|    | 7.7  | Summary                           |   |      |      |   |     |

|    |      | v                                 | - |      | -    | - | -   |

| 8 | Sim  | ulation  | Results                                                                                                   | 95  |

|---|------|----------|-----------------------------------------------------------------------------------------------------------|-----|

|   | 8.1  | Isolatio | on Stage                                                                                                  | 95  |

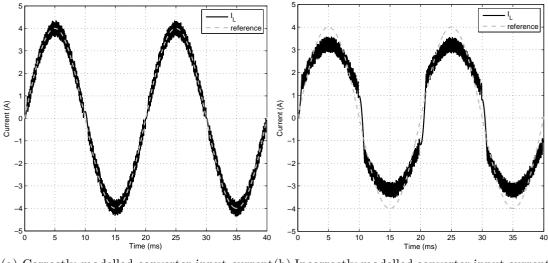

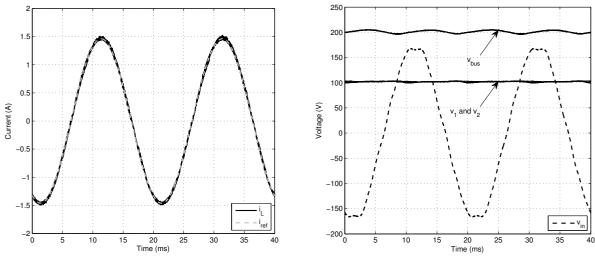

|   | 8.2  | Single   | Converter                                                                                                 | 96  |

|   | 8.3  | Dual C   | Converters                                                                                                | 99  |

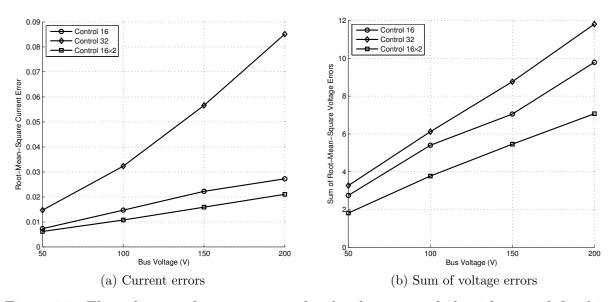

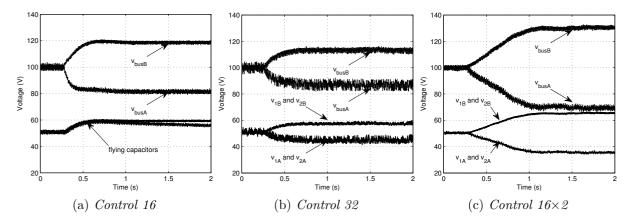

|   |      | 8.3.1    | Control 16                                                                                                | 99  |

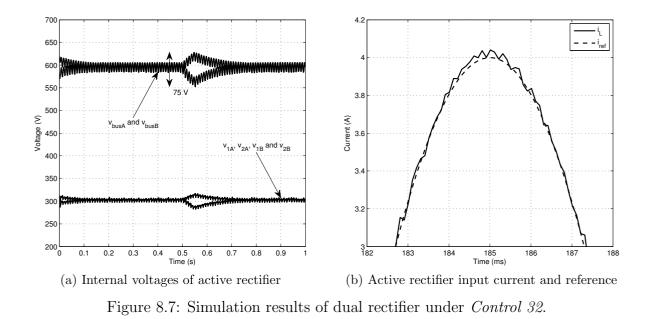

|   |      | 8.3.2    | Control 32                                                                                                | 100 |

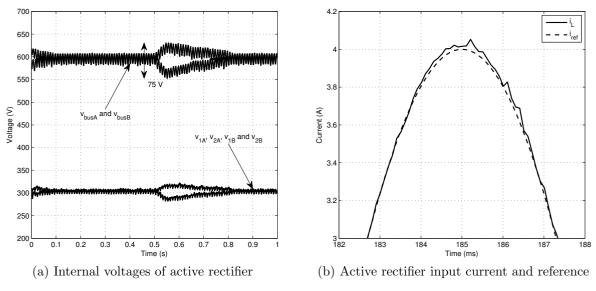

|   |      | 8.3.3    | Control $16 \times 2$                                                                                     | 101 |

|   |      | 8.3.4    | Comparison                                                                                                | 101 |

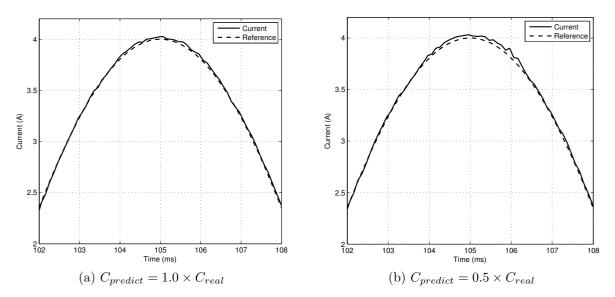

|   | 8.4  | Inaccu   | rate Model                                                                                                | 103 |

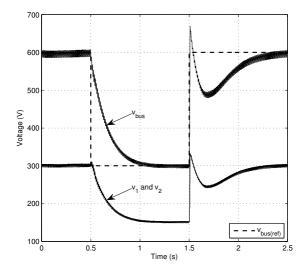

|   | 8.5  | Voltag   | e Regulation                                                                                              | 104 |

|   | 8.6  | Summa    | ary                                                                                                       | 105 |

| 9 | Exp  | erimer   | atal Results                                                                                              | 107 |

|   | 9.1  | Single   | Converter                                                                                                 | 108 |

|   |      | 9.1.1    | Control Algorithm                                                                                         | 109 |

|   |      | 9.1.2    | Voltage Unbalance                                                                                         | 109 |

|   |      | 9.1.3    | Isolation Stage                                                                                           | 110 |

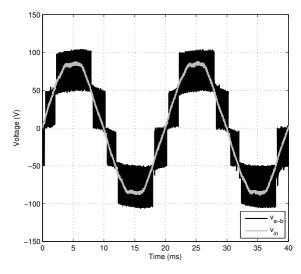

|   |      | 9.1.4    | Terminal Voltage                                                                                          | 111 |

|   |      | 9.1.5    | Bootstrap Supply                                                                                          | 112 |

|   | 9.2  | Dual C   | Converter (without isolation stage)                                                                       | 113 |

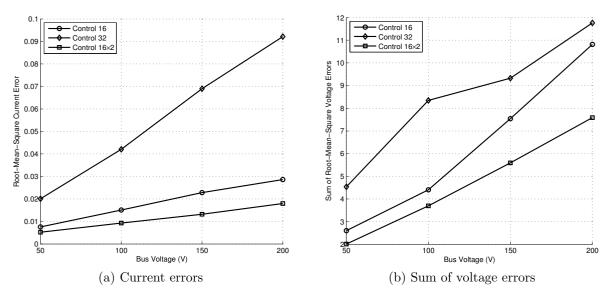

|   |      | 9.2.1    | Voltage and Current Errors                                                                                | 114 |

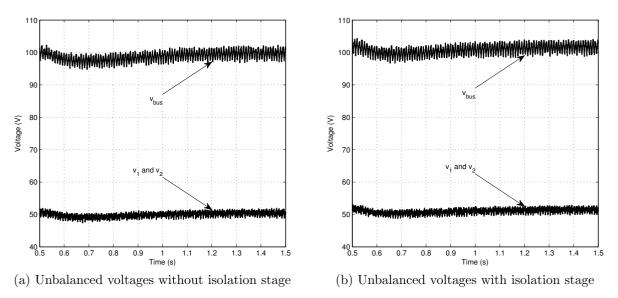

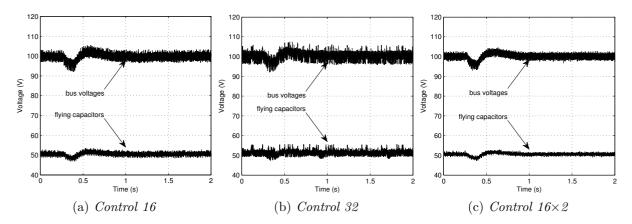

|   |      | 9.2.2    | Voltage Unbalance                                                                                         | 114 |

|   | 9.3  | Dual C   | Converter (with isolation stage)                                                                          | 116 |

|   |      | 9.3.1    | Voltage and Current Errors                                                                                | 117 |

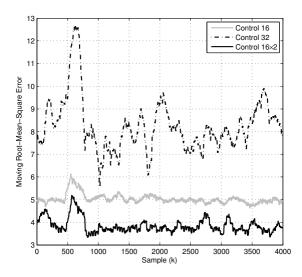

|   |      | 9.3.2    | Voltage Unbalance                                                                                         | 118 |

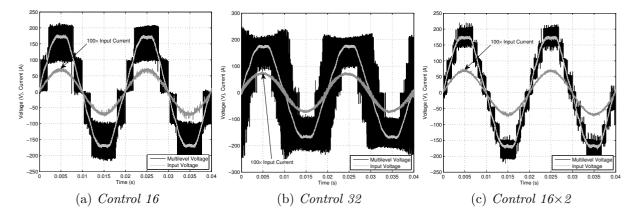

|   |      | 9.3.3    | Terminal Voltages                                                                                         | 118 |

|   |      | 9.3.4    | Input Currents                                                                                            | 120 |

|   |      | 9.3.5    | Load Step                                                                                                 | 120 |

|   |      | 9.3.6    | Current Reference Step                                                                                    | 121 |

|   |      | 9.3.7    | Switching Frequency                                                                                       | 121 |

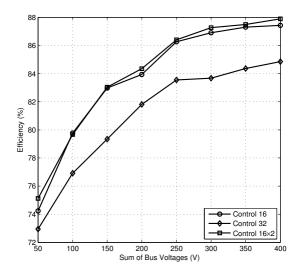

|   |      | 9.3.8    | Efficiency                                                                                                | 123 |

|   | 9.4  | Summa    | ary                                                                                                       | 123 |

|   |      | clusior  |                                                                                                           | 125 |

|   | 10.1 | Summa    | ary of Study                                                                                              | 125 |

|   | 10.2 | Conclu   | sions $\ldots$           | 126 |

|   |      | 10.2.1   | Controller Hardware $\ldots \ldots \ldots$ | 126 |

|   |      | 10.2.2   | Control Algorithms                                                                                        | 126 |

| CC           | ONTE  | NTS                                                                                                         | ix  |

|--------------|-------|-------------------------------------------------------------------------------------------------------------|-----|

|              | 10.9  | 10.2.3 Converter Hardware                                                                                   |     |

|              | 10.5  | Further Work                                                                                                | 128 |

| Bi           | bliog | raphy                                                                                                       | 129 |

| A            | opene | dices                                                                                                       | 138 |

| $\mathbf{A}$ | Cost  | t Analysis                                                                                                  | 139 |

|              | A.1   | Cells                                                                                                       | 139 |

|              | A.2   | Power Switches                                                                                              | 139 |

|              | A.3   | Capacitors                                                                                                  | 140 |

|              | A.4   | Diodes                                                                                                      | 142 |

| в            | Con   | verter Modelling                                                                                            | 143 |

|              | B.1   | Approximation Methods                                                                                       | -   |

|              | B.2   | Flying-Capacitor Converter Modelling                                                                        |     |

|              |       | B.2.1 State 1                                                                                               |     |

|              |       | B.2.2 State 2(a)                                                                                            |     |

|              |       | B.2.3 State 2(b)                                                                                            |     |

|              |       | B.2.4 State 2(c)                                                                                            | 146 |

|              |       | B.2.5 State $2(d)$                                                                                          | 147 |

|              |       | B.2.6 State $3(a)+(b)$                                                                                      | 147 |

|              |       | B.2.7 State 3(c)                                                                                            | 148 |

|              |       | B.2.8 State 3(d)                                                                                            | 148 |

|              |       | B.2.9 State 3(e)                                                                                            | 149 |

|              |       | B.2.10 State 3(f)                                                                                           | 150 |

|              |       | B.2.11 State $4(a)$                                                                                         | 150 |

|              |       | B.2.12 State 4(b) $\ldots$ | 151 |

|              |       | B.2.13 State $4(c)$                                                                                         | 151 |

|              |       | B.2.14 State 4(d) $\ldots$ | 152 |

|              |       | B.2.15 State 5                                                                                              | 152 |

|              | B.3   | Converter State-Space Models                                                                                | 153 |

| С            | PCF   | 3 Schematics                                                                                                | 155 |

| 2            | C.1   | Measurement Boards                                                                                          |     |

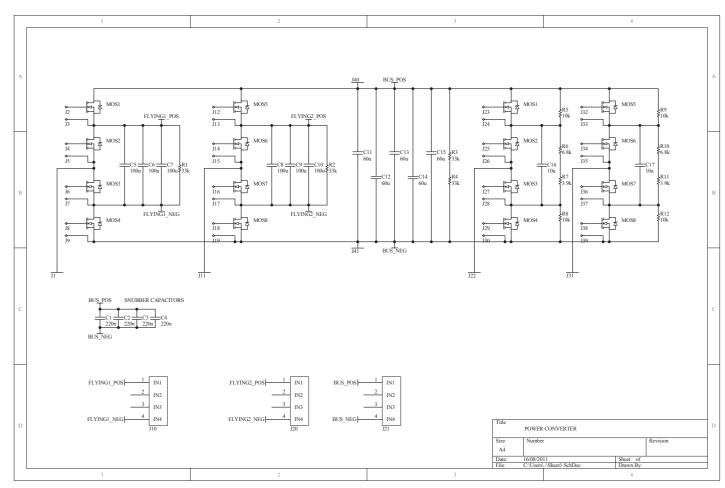

|              | C.2   | Converter Hardware                                                                                          |     |

|              |       | FPGA Board                                                                                                  |     |

|              | C.4   |                                                                                                             |     |

## List of Figures

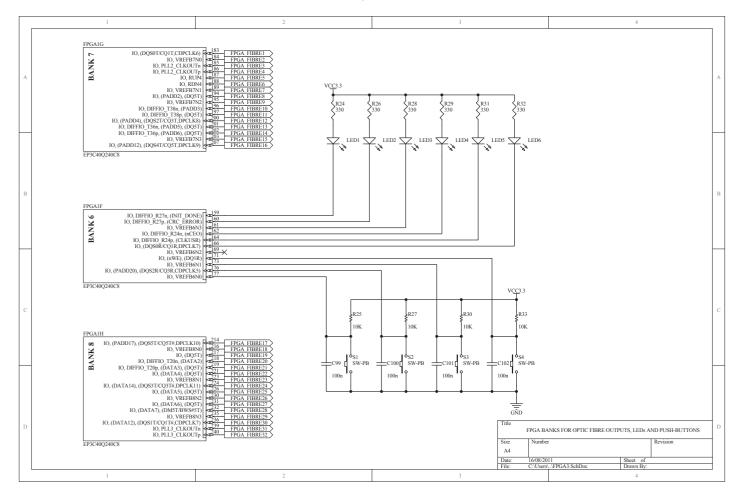

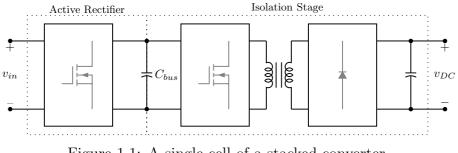

| 1.1 | A single cell of a stacked converter                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

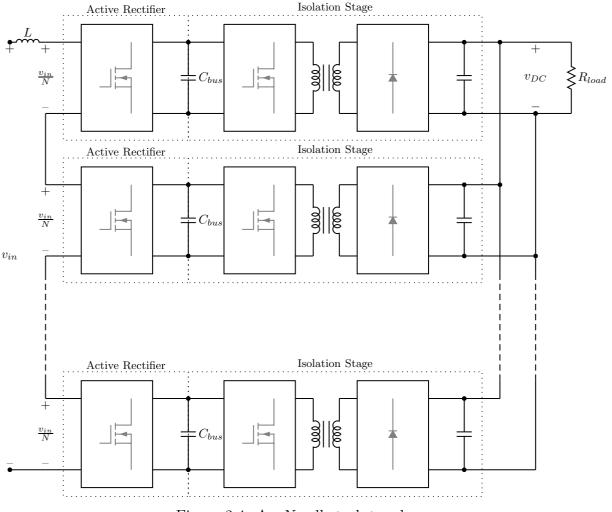

| 1.2 | An N-cell stack topology.                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

| 1.3 | Twelve-cell stack of the 6.6 kV SST                                                                                                                                                                                                                                                                                                                                                                                      | 4  |

| 2.1 | AC/AC buck converter.                                                                                                                                                                                                                                                                                                                                                                                                    | 9  |

| 2.2 | Alternative solid-state transformer topology                                                                                                                                                                                                                                                                                                                                                                             | 10 |

| 2.3 | A single cell of a stacked converter                                                                                                                                                                                                                                                                                                                                                                                     | 10 |

| 2.4 | An N-cell stack topology. $\ldots$ . $\ldots$ | 11 |

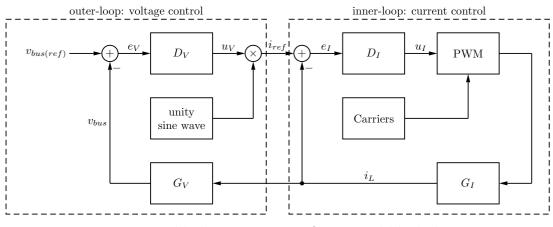

| 2.5 | Double-loop active rectifier control block diagram                                                                                                                                                                                                                                                                                                                                                                       | 12 |

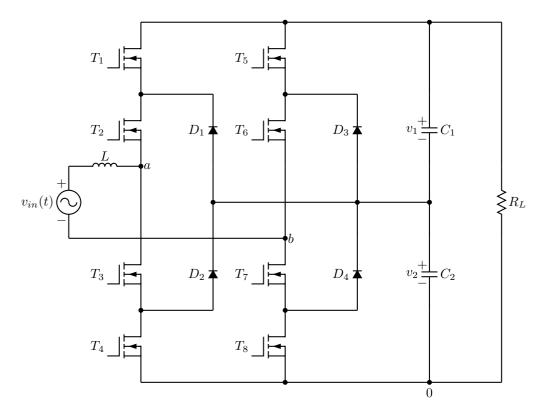

| 3.1 | A full-bridge, three-level, diode-clamped active rectifier                                                                                                                                                                                                                                                                                                                                                               | 15 |

| 3.2 | Equivalent circuit of phase leg when $T_1$ and $T_2$ are on $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                         | 17 |

| 3.3 | Currents flowing into capacitor junctions                                                                                                                                                                                                                                                                                                                                                                                | 18 |

| 3.4 | Phase disposition and alternative phase opposition disposition PWM carrier                                                                                                                                                                                                                                                                                                                                               |    |

|     | waves                                                                                                                                                                                                                                                                                                                                                                                                                    | 19 |

| 3.5 | Control circuit used in simulation                                                                                                                                                                                                                                                                                                                                                                                       | 19 |

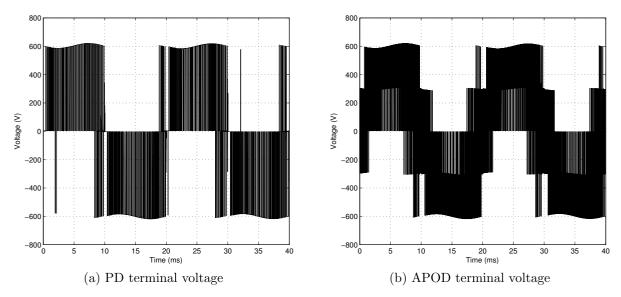

| 3.6 | PD PWM control for full-bridge, three-level, diode-clamped active rectifier                                                                                                                                                                                                                                                                                                                                              | 21 |

| 3.7 | APOD PWM control for full-bridge, three-level, diode-clamped active rectifier.                                                                                                                                                                                                                                                                                                                                           | 22 |

| 3.8 | The terminal voltages of the PD and APOD PWM schemes for the full-bridge,                                                                                                                                                                                                                                                                                                                                                |    |

|     | three-level, diode-clamped active rectifier.                                                                                                                                                                                                                                                                                                                                                                             | 22 |

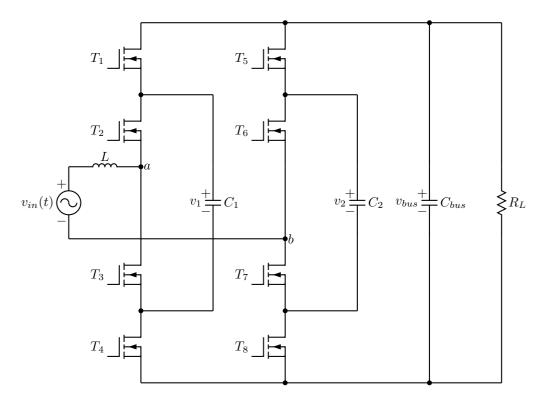

| 4.1 | A full-bridge, three-level, flying-capacitor converter                                                                                                                                                                                                                                                                                                                                                                   | 25 |

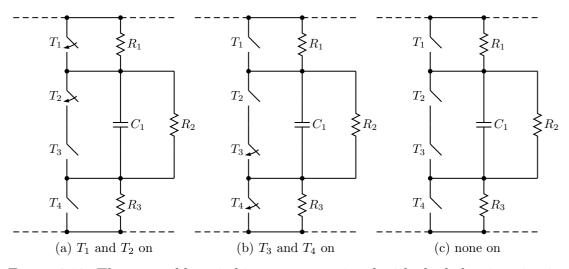

| 4.2 | Equivalent circuit of phase leg when $T_1$ and $T_2$ are on $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                         | 27 |

| 4.3 | Control strategy for voltage balancing of flying capacitor voltages                                                                                                                                                                                                                                                                                                                                                      | 28 |

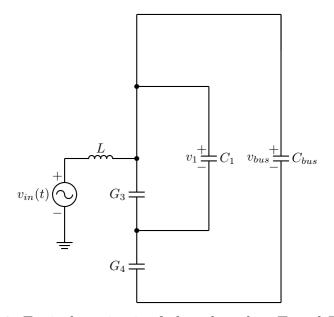

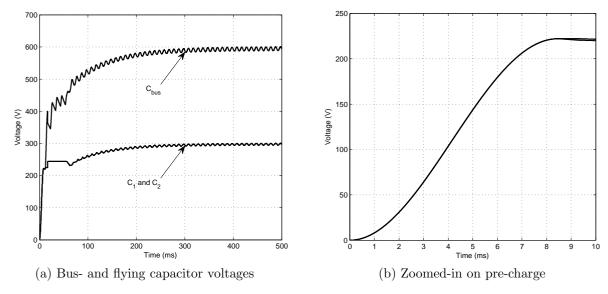

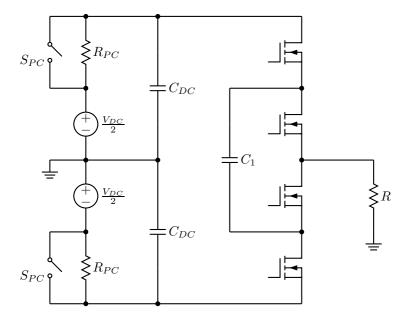

| 4.4 | Pre-charging of capacitors                                                                                                                                                                                                                                                                                                                                                                                               | 30 |

| 4.5 | Pre-charging circuit for flying-capacitor inverter                                                                                                                                                                                                                                                                                                                                                                       | 31 |

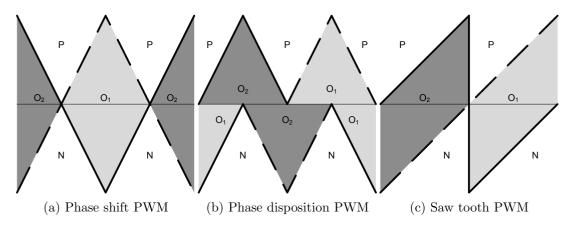

| 4.6 | Different PWM carriers for a half-bridge, three-level, flying-capacitor converter                                                                                                                                                                                                                                                                                                                                        | 32 |

| 4.7 | PWM control for full-bridge, three-level, flying-capacitor converter. $\ldots$ .                                                                                                                                                                                                                                                                                                                                         | 32 |

| 4.8 | Look-up table control for full-bridge, three-level, flying-capacitor converter                                                                                                                                                                                                                                                                                                                                           | 35 |

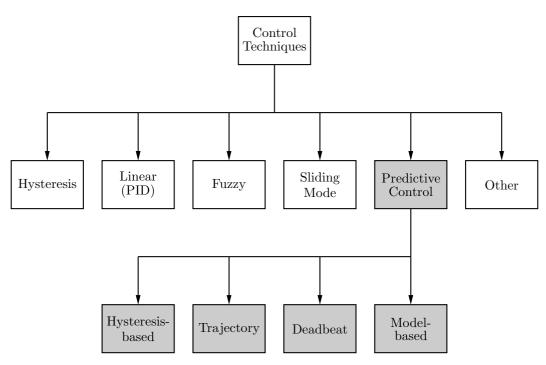

| 5.1 | Breakdown of different control techniques                                                                                                                                                                                                                                                                                                                                                                                | 39 |

| LIST | OF | FIGURES |

|------|----|---------|

|------|----|---------|

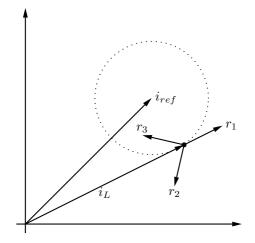

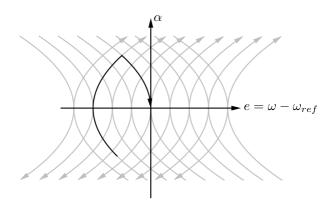

| 5.2  | Hysteresis-based predictive control                                                                                        | 39 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

| 5.3  | Trajectory-based predictive control $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$         | 40 |

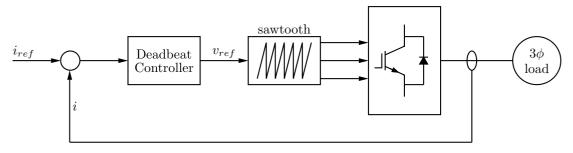

| 5.4  | Deadbeat predictive control                                                                                                | 41 |

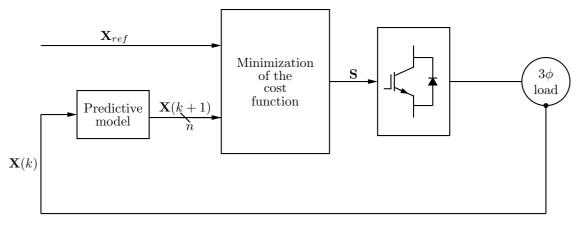

| 5.5  | Finite control set MPC                                                                                                     | 42 |

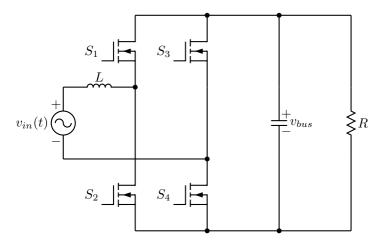

| 5.6  | Full-bridge active rectifier                                                                                               | 46 |

| 5.7  | Control circuit for active rectifier $\ldots \ldots \ldots$ | 47 |

| 5.8  | Full-bridge active rectifier under FS-MPC control                                                                          | 48 |

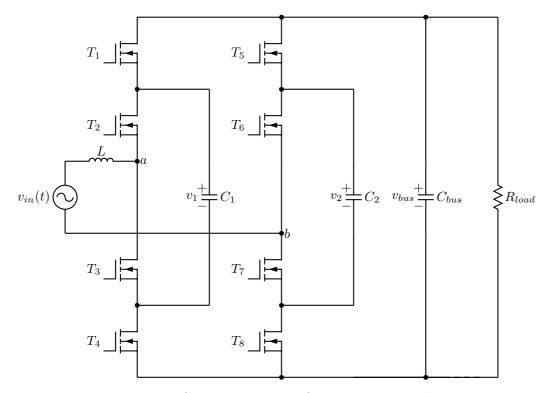

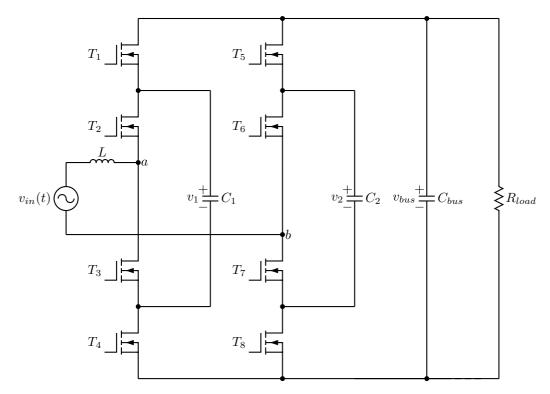

| 6.1  | Full-bridge, three-level flying-capacitor active rectifier                                                                 | 51 |

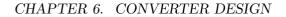

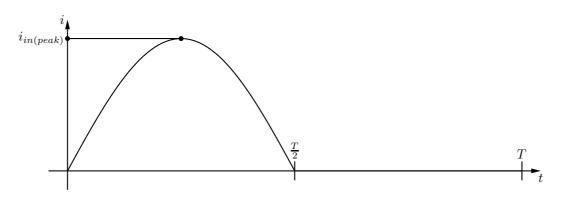

| 6.2  | Current flow through MOSFETs for worst-case losses                                                                         | 53 |

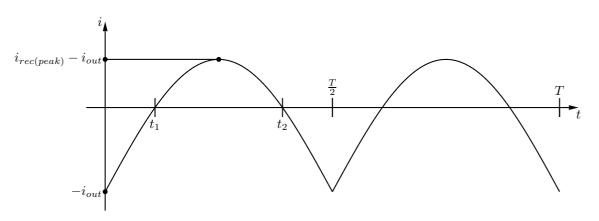

| 6.3  | Worst-case current through switch $T_1$ when it is not switched $\ldots \ldots \ldots$                                     | 54 |

| 6.4  | Current through switch $T_1$ when it is switching $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                       | 54 |

| 6.5  | Bus capacitor current waveform                                                                                             | 56 |

| 6.6  | Bus capacitor current waveform                                                                                             | 57 |

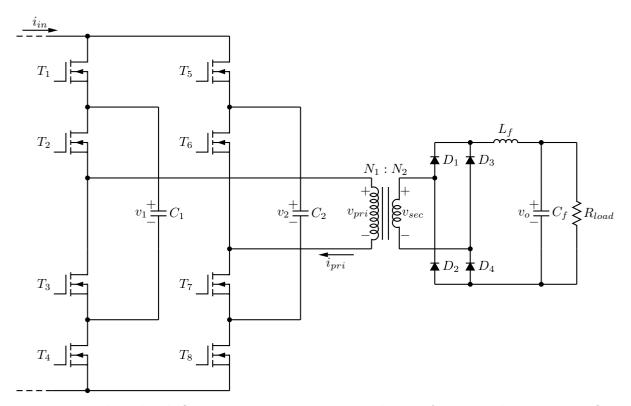

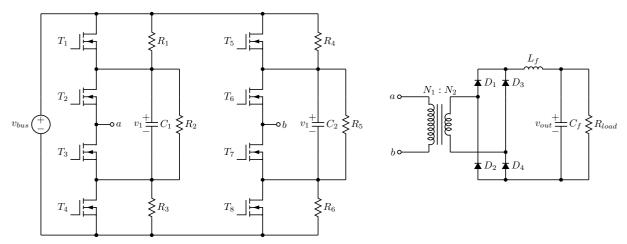

| 6.7  | Three-level, flying-capacitor converter with transformer and passive rectifier $\ .$                                       | 59 |

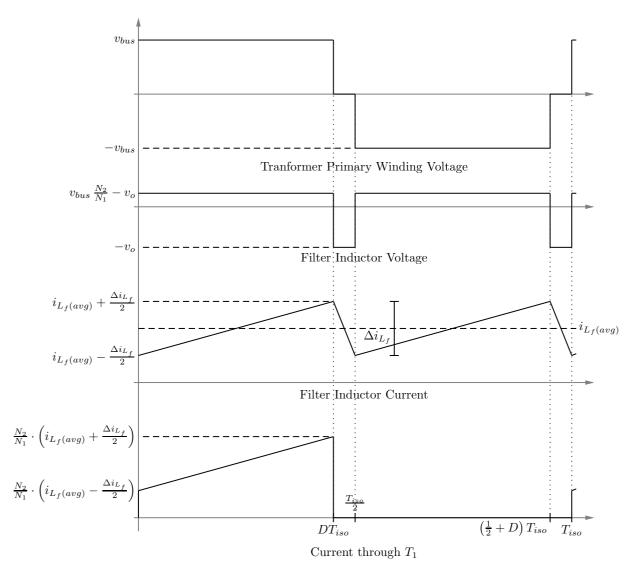

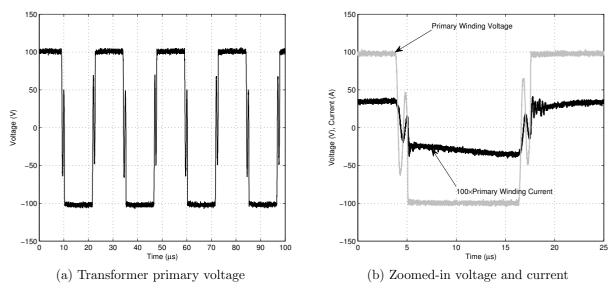

| 6.8  | Voltage and current waveforms for the inverter                                                                             | 60 |

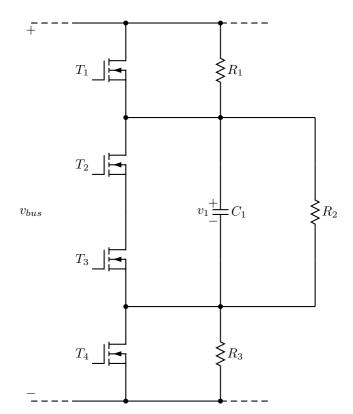

| 6.9  | Balancing resistors for the inverter's flying-capacitors                                                                   | 62 |

| 6.10 | Three possible switching state associated with the balancing circuit                                                       | 63 |

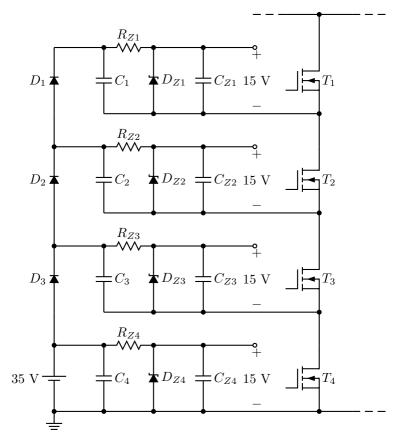

| 6.11 | Bootstrap driver circuit for one leg                                                                                       | 66 |

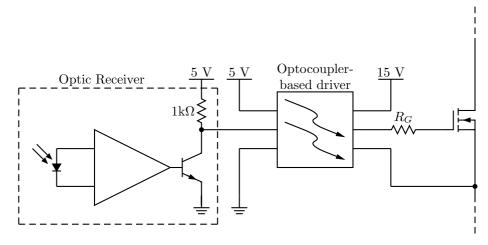

| 6.12 | Optic receiver and driver circuitry                                                                                        | 67 |

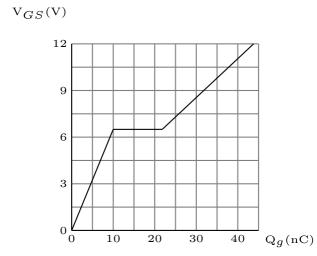

| 6.13 | Gate charge vs gate-source voltage of <i>STP20NM60FD</i>                                                                   | 67 |

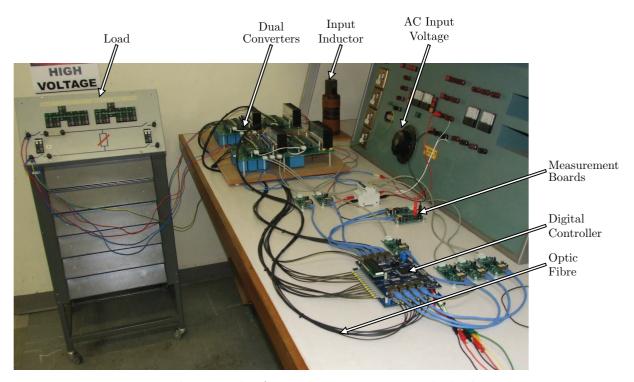

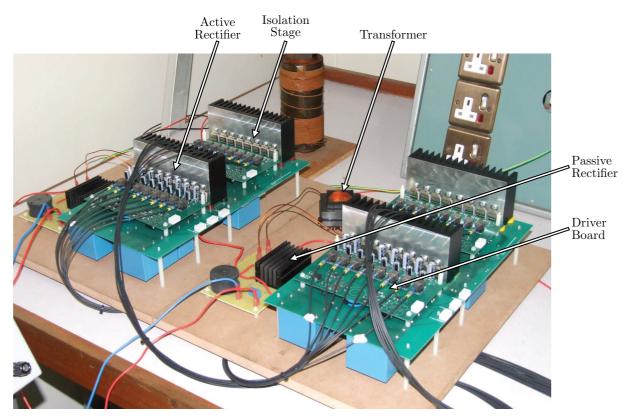

| 6.14 | Photograph of complete test setup with dual converters                                                                     | 69 |

| 6.15 | Photograph of dual converters.                                                                                             | 70 |

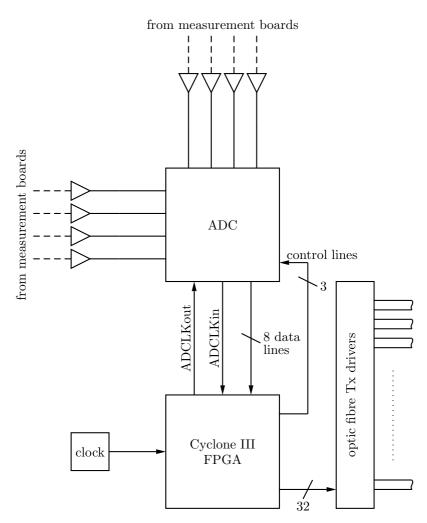

| 7.1  | Controller hardware.                                                                                                       | 73 |

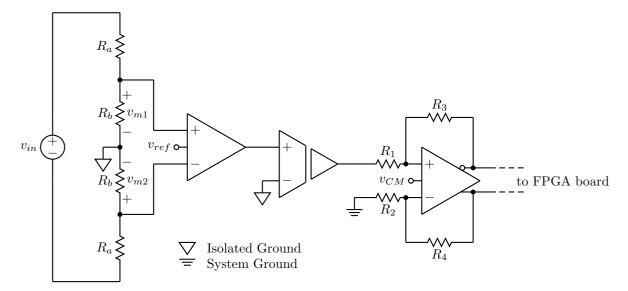

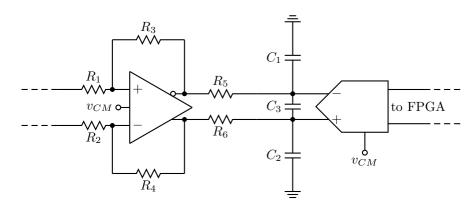

| 7.2  | Voltage measurement circuit                                                                                                | 74 |

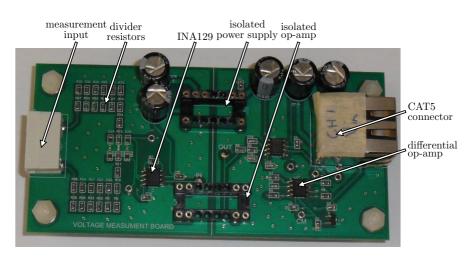

| 7.3  | Voltage measurement PCB                                                                                                    | 76 |

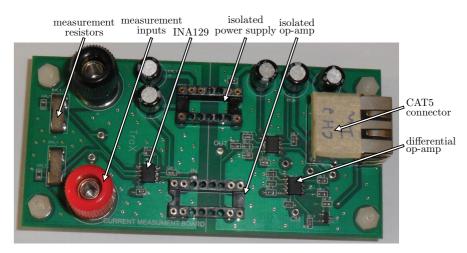

| 7.4  | Current measurement PCB                                                                                                    | 76 |

| 7.5  | Differential input buffer and analogue-to-digital converter                                                                | 77 |

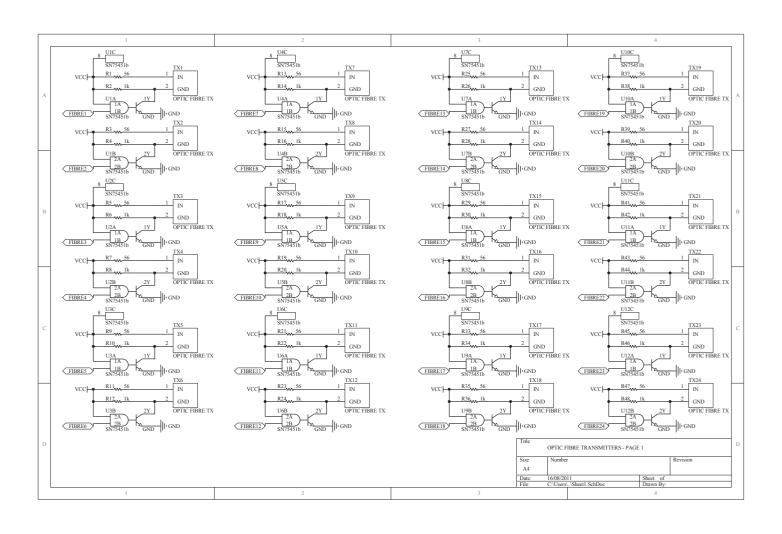

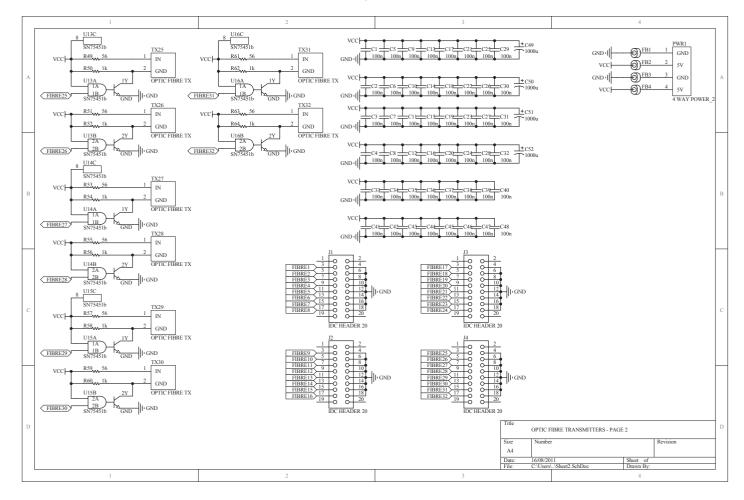

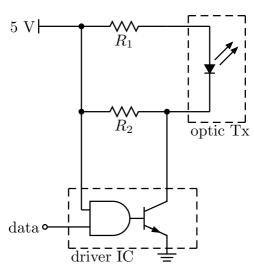

| 7.6  | Optic fibre transmitter and driver for sending switching signals                                                           | 78 |

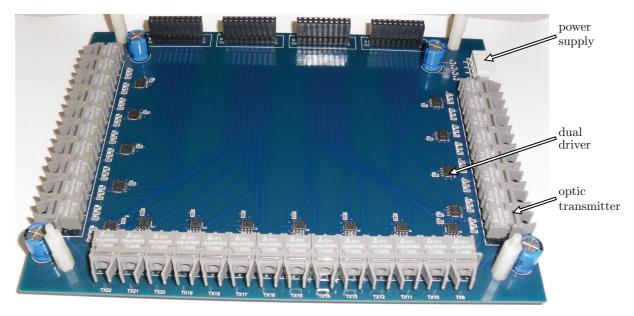

| 7.7  | Optic fibre transmitters PCB                                                                                               | 78 |

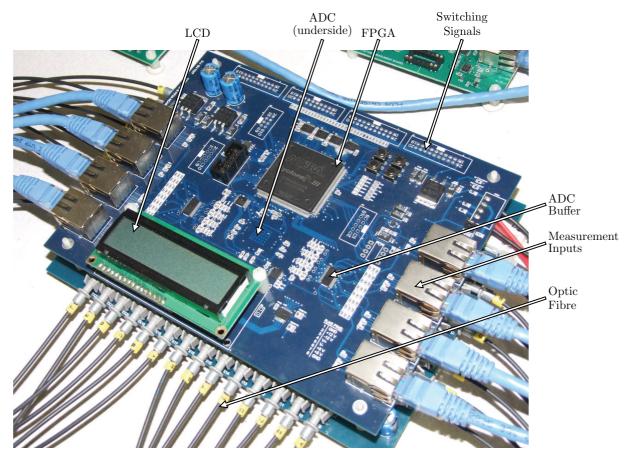

| 7.8  | Photograph of FPGA board                                                                                                   | 79 |

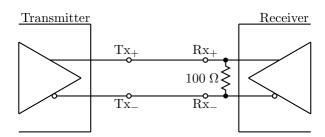

| 7.9  | Low-voltage differential signalling                                                                                        | 80 |

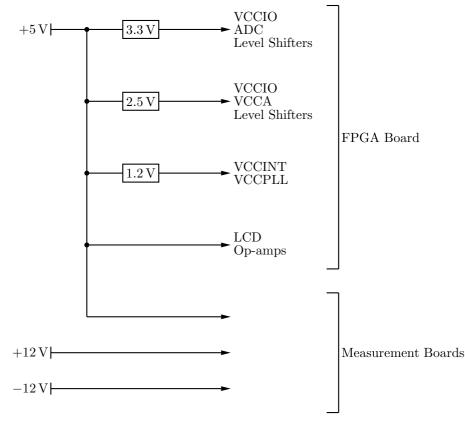

| 7.10 | Power distribution for FPGA host board                                                                                     | 81 |

| 7.11 | Digital connections of FPGA and ADC through voltage level shifter                                                          | 82 |

| 7.12 | Digital connections of FPGA and LCD module through voltage level shifter.                                                  | 82 |

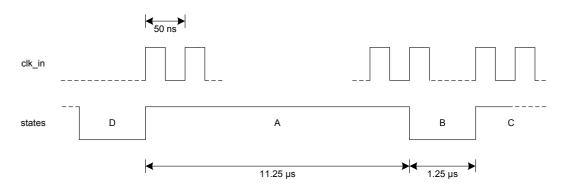

| 7.13 | Relationship between the input clock and converter states $\ldots \ldots \ldots \ldots$                                    | 83 |

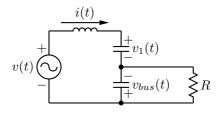

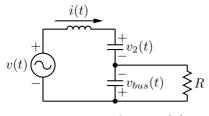

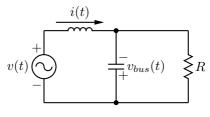

| 7.14 | Single active rectifier with resistive load.                                                                               | 84 |

#### LIST OF FIGURES

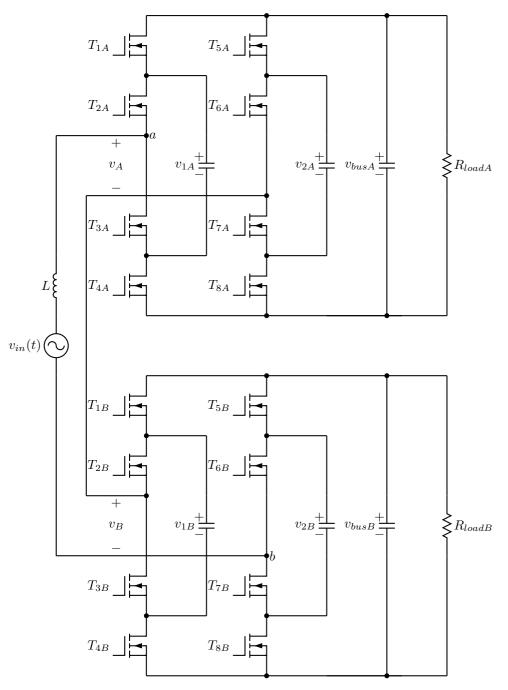

| 7.15 | Dual active rectifier with resistive loads.                                                 | 86  |

|------|---------------------------------------------------------------------------------------------|-----|

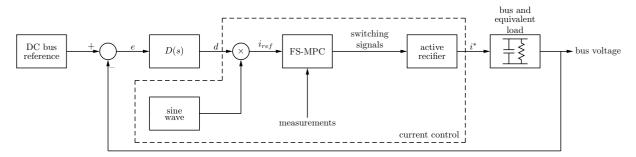

| 7.16 | Double-loop controller to control input current and regulate bus voltage(s)                 | 91  |

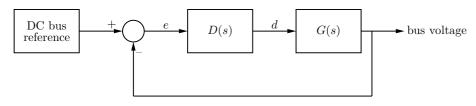

| 7.17 | Voltage controller.                                                                         | 92  |

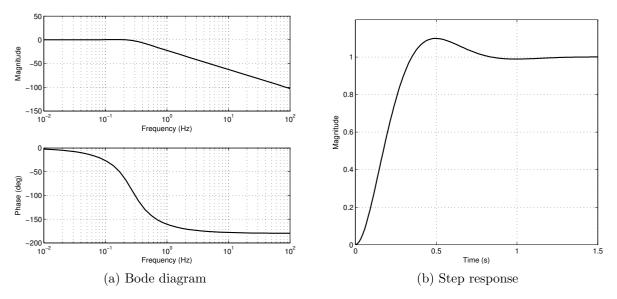

| 7.18 | Voltage controller bode diagram and step response                                           | 93  |

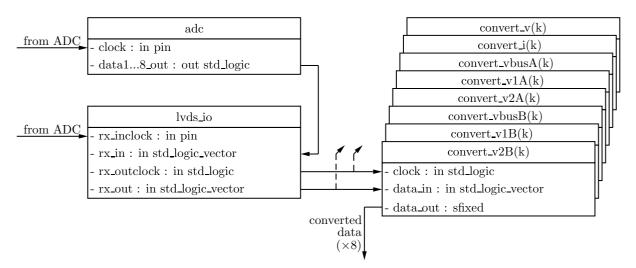

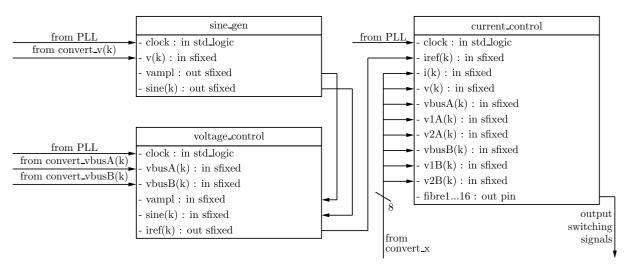

| 7.19 | VHDL entities implementing the control code for ADC operation.                              | 93  |

| 7.20 | VHDL entities implementing the voltage and current control algorithms                       | 94  |

| 8.1  | Isolation stage circuit with balancing resistors included                                   | 96  |

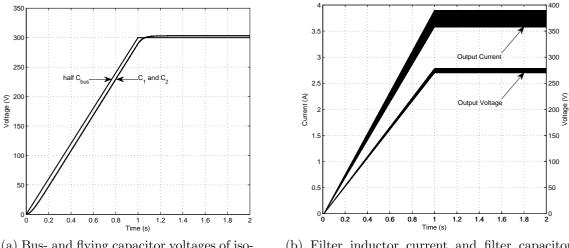

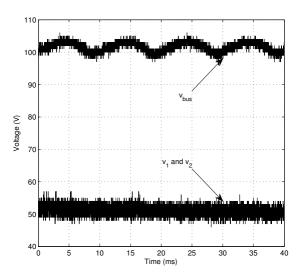

| 8.2  | Isolation stage simulation results                                                          | 97  |

| 8.3  | Single active rectifier with resistive load                                                 | 98  |

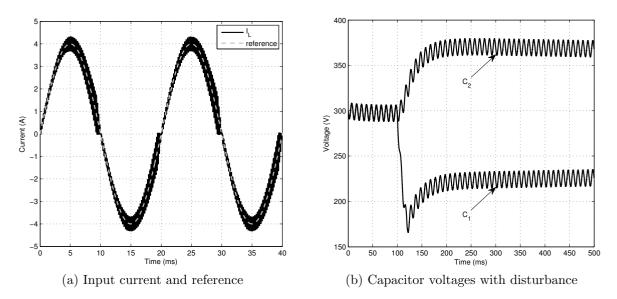

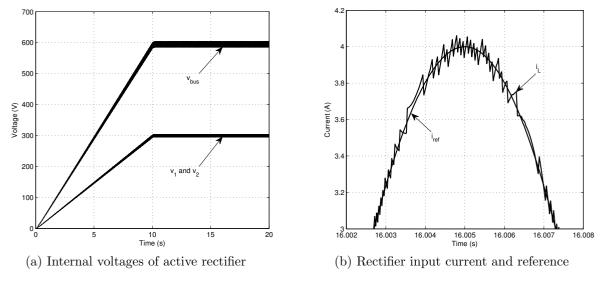

| 8.4  | Single rectifier simulation results                                                         | 98  |

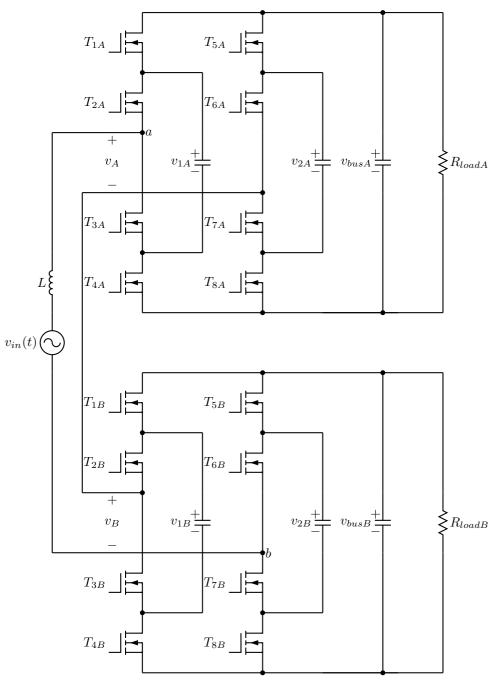

| 8.5  | Dual active rectifier with resistive loads.                                                 | 100 |

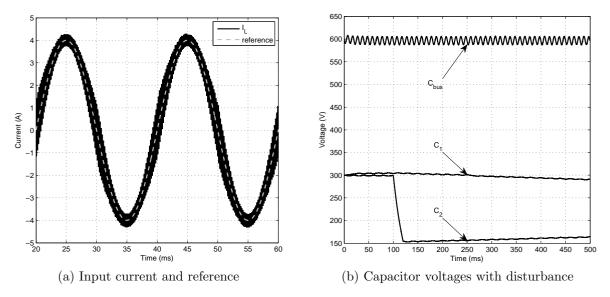

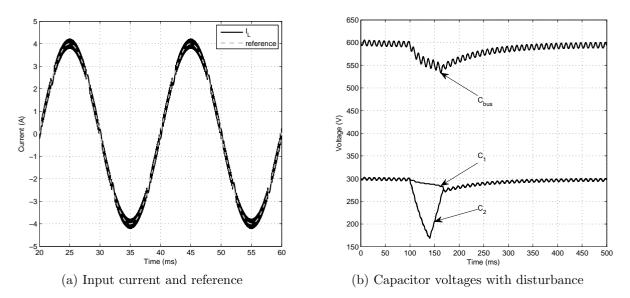

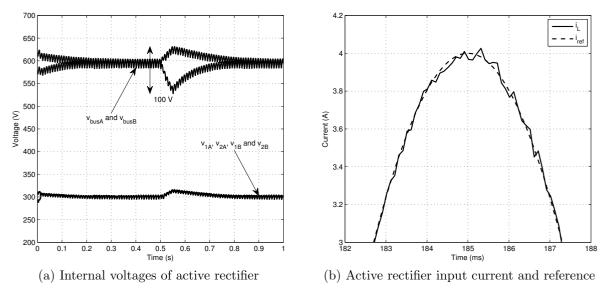

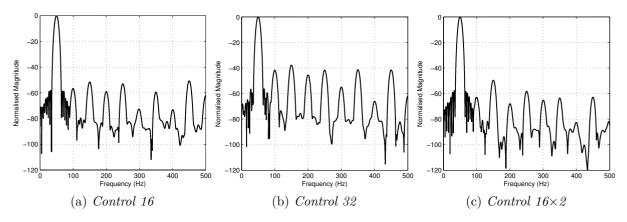

| 8.6  | Simulation results of dual rectifier under Control 16                                       | 101 |

| 8.7  | Simulation results of dual rectifier under Control 32                                       | 101 |

| 8.8  | Simulation results of dual rectifier under Control $16 \times 2$                            | 102 |

| 8.9  | Input current with <i>Control</i> $16 \times 2$ and inaccurately modelled capacitor values. | 104 |

| 8.10 | Internal voltages of single rectifier with input voltage changes                            | 105 |

| 8.11 | Single rectifier with load changes                                                          | 105 |

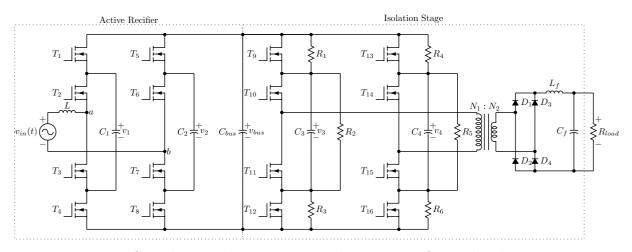

| 9.1  | Complete single converter with active rectifier and isolation stage                         | 108 |

| 9.2  | The input current, input voltage and internal voltages of the single converter              |     |

|      | active rectifier.                                                                           | 109 |

| 9.3  | A single converter's internal voltages with an unbalanced disturbance                       | 110 |

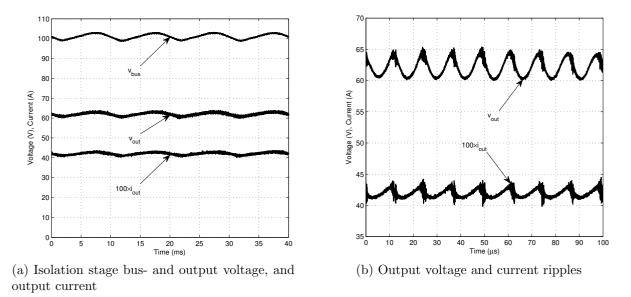

| 9.4  | Isolation stage flying capacitor- and bus voltages.                                         | 111 |

| 9.5  | Isolation transformer terminal voltage and primary current                                  | 111 |

| 9.6  | The DC output voltage and current of the isolation stage.                                   | 112 |

| 9.7  | The terminal voltage and input voltage of a single active rectifier                         | 112 |

| 9.8  | Dual, series stacked converters with individual loads                                       | 114 |

| 9.9  | The voltage and current errors for the three control algorithms as defined in               |     |

|      | (9.2.1) and $(9.2.2)$                                                                       | 115 |

| 9.10 | Response of internal voltages of dual active rectifiers to an unbalanced load I             | 115 |

| 9.11 | Dual, series stacked converters with their isolation stages for a parallel output.          | 116 |

| 9.12 | The voltage and current errors for the three control algorithms                             | 117 |

| 9.13 | Response of internal voltages of dual active rectifiers to an unbalanced load 1             | 118 |

| 9.14 | Moving RMS error for momentary introduced unbalance of Figures 9.13(a)-(c).                 | 119 |

| 9.15 | The dual active rectifier terminal voltage for the three control algorithms                 | 119 |

| 9.16 | FFT analysis of the input currents of the three control algorithms                          | 120 |

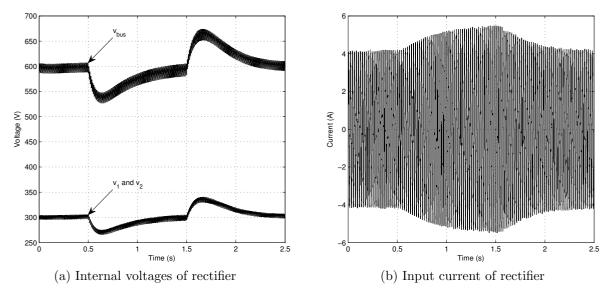

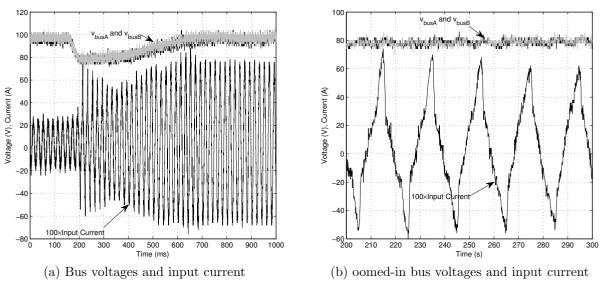

| 9.17 | Load step for dual converters                                                               | 121 |

### LIST OF FIGURES

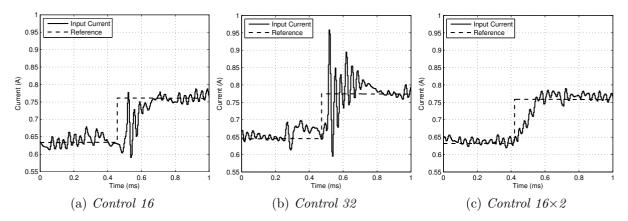

| 9.18 | Input current responses to a step in the their reference                                                           |

|------|--------------------------------------------------------------------------------------------------------------------|

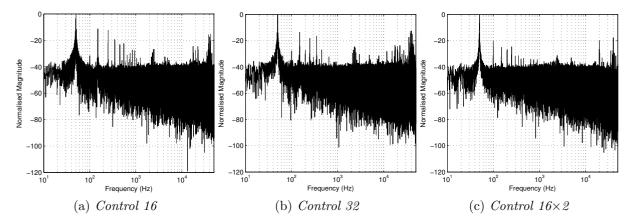

| 9.19 | FFT of the switching signal for switch $T_1$ for the three control algorithms 122                                  |

| 9.20 | Efficiencies of the three control algorithms with a $35.5 \Omega$ load. $\ldots \ldots \ldots 123$                 |

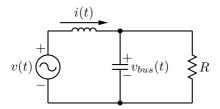

| B.1  | State 1                                                                                                            |

| B.2  | State 2(a)                                                                                                         |

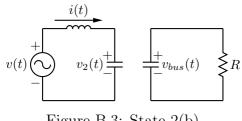

| B.3  | State 2(b)                                                                                                         |

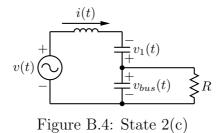

| B.4  | State 2(c)                                                                                                         |

| B.5  | State 2(d)                                                                                                         |

| B.6  | State $3(a)+(b)$                                                                                                   |

| B.7  | State 3(c)                                                                                                         |

| B.8  | State 3(d)                                                                                                         |

| B.9  | State 3(e)                                                                                                         |

| B.10 | State 3(f)                                                                                                         |

| B.11 | State 4(a)                                                                                                         |

| B.12 | State 4(b)                                                                                                         |

| B.13 | State 4(c)                                                                                                         |

| B.14 | State 4(d)                                                                                                         |

| B.15 | State 5                                                                                                            |

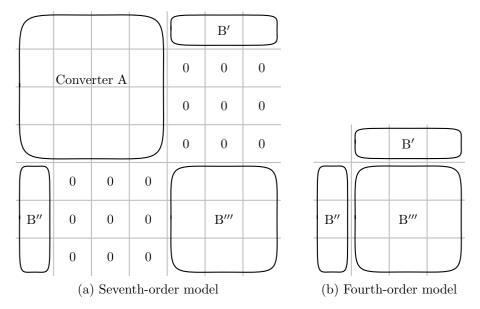

| B.16 | Constructing the seventh-order model for the dual active rectifiers from the                                       |

|      | two fourth-order models. $\ldots$ |

## List of Tables

| 1.1 | Cost comparison of SST topologies                                                     |

|-----|---------------------------------------------------------------------------------------|

| 3.1 | Diode-clamped converter simulation parameters                                         |

| 4.1 | Flying-capacitor converter simulation parameters                                      |

| 4.2 | Look-up table for full-bridge, three-level, flying-capacitor input current control 34 |

| 5.1 | Full-bridge converter simulation parameters                                           |

| 6.1 | MOSFET Parameters                                                                     |

| 6.2 | EPCOS ETD 54/28/19 ferrite core parameters                                            |

| 7.1 | Component values for voltage measurements                                             |

| 8.1 | Isolation stage simulation parameters                                                 |

| 8.2 | Active rectifier simulation parameters                                                |

| 8.3 | Active rectifier simulation parameters                                                |

| 8.4 | Comparison of control algorithms                                                      |

| 8.5 | Effect on control algorithms of inaccurate modelling of load resistance 103           |

| 8.6 | Effect on control algorithms of inaccurate modelling of capacitors 104                |

| 9.1 | Single converter experimental setup                                                   |

| 9.2 | Bootstrap supply voltages                                                             |

| 9.3 | Dual active rectifiers without the isolation stages                                   |

| 9.4 | Unbalanced measurements of the two converters without their isolation stages. 116     |

| 9.5 | Dual active rectifiers with the isolation stages                                      |

| 9.6 | Input current THD+N                                                                   |

| 9.7 | Average switching frequencies of the power switches                                   |

| A.1 | Cost Analysis: Number of cells for each SST topology                                  |

| A.2 | Cost Analysis: Number of power switches for each SST topology                         |

| A.3 | Cost Analysis: Number of capacitors for each SST topology                             |

| A.4 | Cost Analysis: Number of diodes for each SST topology                                 |

## Nomenclature

| AC        | Alternating Current                                 |

|-----------|-----------------------------------------------------|

| ADC       | Analogue-to-Digital Converter                       |

| α         | Cost Function Weight                                |

| APOD      | Alternative Phase Opposition Disposition            |

| β         | Cost Function Weight                                |

| C         | Capacitance                                         |

| CAT5      | Unshielded Twisted Pair Type Cable Connector        |

| D         | Duty Cycle                                          |

| DC        | Direct Current                                      |

| DCM       | Discontinuous Conduction Mode                       |

| DSP       | Digital Signal Processor                            |

| EEPROM    | Electrically Erasable Programmable Read-Only Memory |

| $f_{iso}$ | Isolation Stage Switching Frequency                 |

| FPGA      | Field-Programmable Gate Array                       |

| $f_{pre}$ | Predictive Controller Prediction Frequency          |

| $f_s$     | Switching Frequency                                 |

| FS-MPC    | Finite-State Model-based Predictive Control         |

| ΙΟ        | Input-Output                                        |

| L         | Inductance                                          |

| LCD       | Liquid Crystal Display                              |

#### NOMENCLATURE

| LVDS      | Low-Voltage Differential Signalling               |

|-----------|---------------------------------------------------|

| LV        | Low Voltage                                       |

| MOSFET    | Metal Oxide Semiconductor Field Effect Transistor |

| MPC       | Model-based Predictive Control                    |

| MV        | Medium Voltage                                    |

| N         | Number of Stacked Converters                      |

| PCB       | Printed Circuit Board                             |

| PD        | Phase Disposition                                 |

| PID       | Proportional-Integral-Derivative                  |

| PI        | Proportional-Integral                             |

| PLL       | Phase-Locked Loop                                 |

| PWM       | Pulse-Width Modulation                            |

| R         | Resistance                                        |

| RMS       | Root-Mean-Square                                  |

| SIPO      | Series-Input, Parallel-Output                     |

| SPWM      | Sinusoidal Pulse-Width Modulation                 |

| SST       | Solid-State Transformer                           |

| $T_{iso}$ | Isolation Stage Switching Period                  |

| $T_{pre}$ | Predictive Controller Prediction Period           |

| $T_s$     | Switching Period                                  |

# Chapter 1 Introduction

## 1.1 Background

In recent years the applications of power electronics in power systems have increased due to the advancements in available hardware, namely faster digital controllers and power switches with higher voltage and current ratings. This led to the study of a solidstate transformer (SST) consisting of high voltage power electronics with the purpose of replacing existing iron core transformers. The first mention of the SST concept is found in 1980 [1], although the technology did not exist at the time the concept's future viability was clear. With better hardware available today the concept made a new attempt to be implemented [2–4]. This replacement of iron core transformers does have its advantages [5,6]:

- Input power factor correction: Depending on the topology used the converter can be able to draw currents on its medium voltage (MV) side which are sinusoidal and have a specific phase relation with the input voltage. The SST can therefore be used as an active power factor correction tool while delivering power to its low voltage (LV) side.

- Near perfect output voltage regulation: The three-phase output of the SST is generated with an actively controlled inverter. The fast response of these converters ensures that the output voltages are regulated even under load changes or non-linear load conditions.

- **Harmonic filtering:** Harmonic content generated by non-linear loads are not transferred to the MV side of the SST.

- **Output short circuit protection:** The controller of the SST will be able to sense fault conditions and limit the output current as to not disturb the primary side.

- Voltage dip and swell compensation: The added capacitance of the SST can be used to keep the output voltages regulated under input voltage dip or swell conditions.

- Single phase or three phase operation: The SST can be configured to operate from either a single or three-phase supply and it can either supply a single- or three-phase load.

- Supply frequency variation: The primary and secondary sides of the SST are controlled separately and can therefore operate where the input and output frequencies are not necessarily the same.

- Capable of supplying a DC voltage: The DC voltages of the bus capacitors are available for DC supplies.

- **Operation under a fault condition:** Depending on the fault conditions, the SST may be able to only cut out one of its output phase while still delivering power to the remaining two.

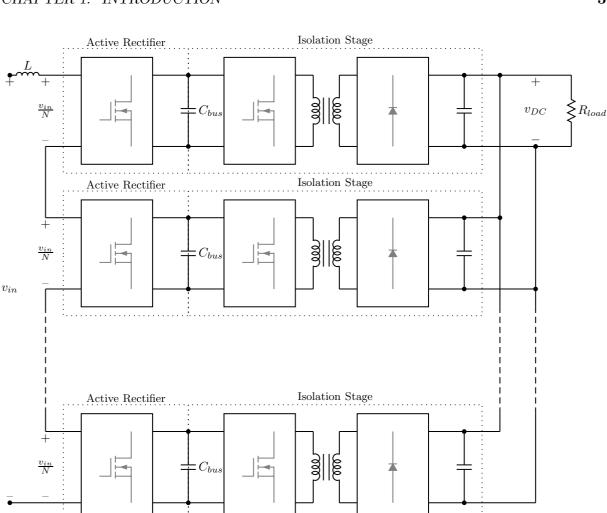

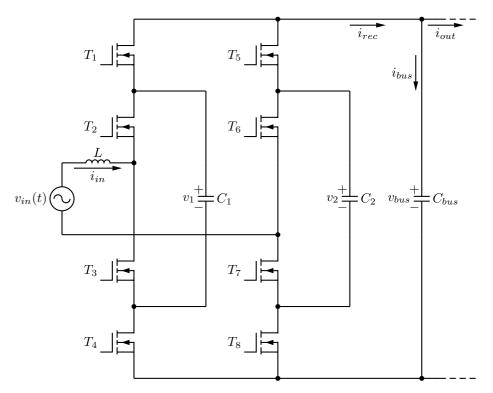

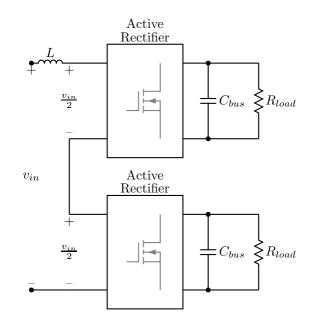

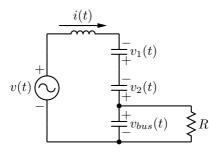

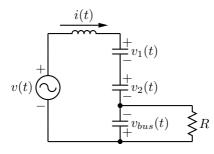

The project in this report stems from work done by Stellenbosch University on such an SST [6]. The topology used for the 11 kV-to-400 V three-phase solid state transformer is based on a series stack of full-bridge, back-to-back converters [5]. Each back-to-back converter forms a cell, shown in Figure 1.1. These cells are stacked, shown in Figure 1.2, to obtain the required input voltage rating. Because the total working voltage of the SST is much higher than the blocking voltage capability of each of the power transistors used, the correct voltage balancing of the cell voltages were important. The natural balancing of the cell voltages was proved by [7,8].

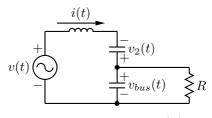

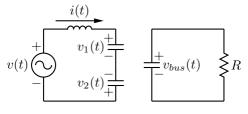

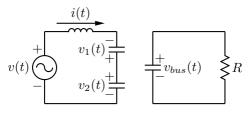

Figure 1.1: A single cell of a stacked converter.

The SST prototype was successfully implemented on a 6.6 kV scale using 36 cells. One stack consisting of 12 cells is shown in Figure 1.3. Also, 36 cell controllers and three main controllers [9,10] were needed to control the three-phase, stacked converter. The question arises whether it is possible to reduce the amount of hardware. If three-level, instead

Figure 1.2: An *N*-cell stack topology.

of the full-bridge, converters are used, the amount of cells needed will be halved. The amount of cell controllers will also be halved. This will reduce the cost and complexity of the system. The problem with using multilevel converters is that their internal voltages that to be balanced. Furthermore, the SST call for a cell converter than can be stacked in series to achieve a total voltage rating that is higher that a single cell's rating.

Although [11] suggested against the use of multilevel converters due to their cost, it became necessary to be able to compare the use of different cell topologies. Multilevel inverters have been successfully implemented [12, 13] the difficulty being to balance the internal voltages of the converter [14–19]. These converters have also been coupled with predictive control methods [20–26]. These were able to regulate the internal voltages of the converters have also been coupled as series stacked active rectifiers.

The authors of [11] compared the diode-clamped, flying-capacitor and series stacked fullbridge converters mostly on their cost. They did not, however, consider using a series stack of multilevel converters such as this thesis will investigate. Therefore, repeating their

Figure 1.3: Twelve-cell stack of the 6.6 kV SST.

comparison, the cost of a three-phase 6.6 kV SST for a series stacked full-bridge, diodeclamped and flying-capacitor converter is given in Table 1.1. The breakdown of the cost analysis is shown in Appendix A. The diode-clamped and flying-capacitor converters are both taken to be full-bridge, three-level converters. Each, therefore, has eight transistors in both the rectifier and isolation stage. The total amount of transistors is therefore the same between the three topologies. The assumption is made that the bus- and flying capacitors should equal  $300 \,\mu\text{F}$  with the bus capacitors having a voltage rating of  $800 \,\text{V}$ and the flying capacitors a minimum rating of  $400 \,\text{V}$ .  $800 \,\text{V}$ ,  $60 \,\mu\text{F}$  and  $450 \,\text{V}$ ,  $100 \,\mu\text{F}$ capacitors are available to make up the  $300 \,\mu\text{F}$  totals. Furthermore, the assumption is made that each cell controller carries a cost of R1 500.00.

From the cost evaluation it is clear the diode-clamped and flying-capacitor topologies have similar costs. The cost therefore does not have any influence on deciding on the topology for this thesis. A detail analysis of the cost should however be done but for the purpose of defending the choice in topology for this thesis the analysis is sufficient. The flying-capacitor converter does have the added advantage of larger internal capacitance. This could prove useful in dip/swell prone power systems where the added capacitance could provide longer periods of ride-through during dip conditions. The flying-capacitor topology is therefore chosen for this thesis.

|                                            | Full-Bridge | Flying-Capacitor | Diode-Clamped |

|--------------------------------------------|-------------|------------------|---------------|

| Cells                                      | 36          | 18               | 18            |

| Controllers                                | 36          | 18               | 18            |

| Controllers                                | m R54000    | R27000           | R27000        |

| 800 V, 20 A Transistors                    | 288         | 288              | 288           |

| $60\mu\text{F},800\text{V}$ Capacitors     | 180         | 90               | 0             |

| $00\mu\mathrm{r},000\mathrm{v}$ Capacitors | R19000      | m R9500          | 0             |

| $100 \mu\text{F}, 450 \text{V}$ Capacitors | 0           | 216              | 216           |

|                                            | 0           | R26000           | R26000        |

| 400 V 20 A Diodog                          | 0           | 0                | 144           |

| $400 \mathrm{V},  20 \mathrm{A}$ Diodes    | 0           | 0                | m R5750       |

| Comparative Total                          | m R73000    | m R62500         | R58750        |

Table 1.1: Cost comparison of SST topologies.

## 1.2 Study Objectives

The aim of this project is to provide a proof-of-concept for replacing the full-bridge converters in the SST prototype with multilevel converters. A laboratory prototype of two stacked full-bridge, three-level flying-capacitor converter cells should be built and tested. To achieve this objective the following needs to be completed:

- Study series-input, parallel-output converters and controllers to be able to re-design the converter cell.

- Study diode-clamped and flying-capacitor converters to be able to choose and design a converter that is suited for a series stacked application.

- Study predictive control techniques to be able to choose and design a predictive controller for the series stacked converter.

- Design a suitable multilevel converter.

- Design a suitable predictive controller to control a series stack of two converters.

- Simulate the proposed converter topology and controller.

- Confirm the correct working of both the stacked converter and the predictive controller on a laboratory prototype.

- Comment on the viability of extending the two converters for a medium voltage application.

### 1.3 Thesis Overview

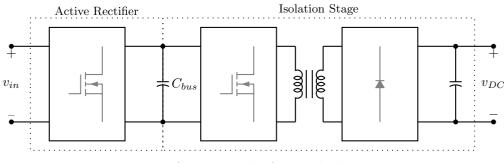

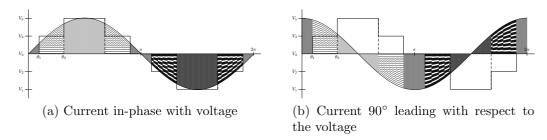

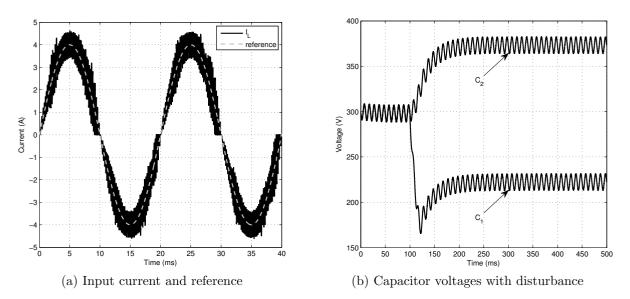

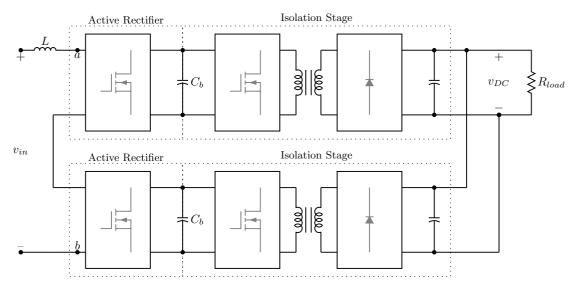

The literature review starts in Chapter 2 with an overview of the solid-state transformer concept. Different SST topologies are given and the series-input, parallel-output (SIPO) topology is further discussed. The contents of one cell of such a SIPO converter is given. The active rectifier front-end of the cell is used to let the converter operate at unity power factor on its primary side. This is achieved by controlling the input current of the converter to be sinusoidal and in-phase with the input voltage. The front-end thus converts the AC input to DC. The isolation stage converts the DC voltage to a high frequency square wave, passes it through a high frequency transformer and then rectifies it again by means of a passive rectifier. This stage is needed to be able to connect all the outputs from the cells in parallel when they are stacked in series. The reason for stacking the converters is to be able to achieve higher voltage rating on the input side. The voltage balancing required by the series stack is also discussed. It relies on the fact the a higher DC bus voltage will deliver more power to the load resulting in a drop in the voltage of that bus. The bus voltages will therefore balance naturally. Although the bus voltages will balance with respect to each other they will not balance naturally to a specific reference voltage. The double loop controller for this is shown. It consists of the inner loop that controls the input current to be sinusoidal and the outer loop that regulates the sum of the bus voltages. The outer loop controls the magnitude of the input current in order to regulate the bus voltages.

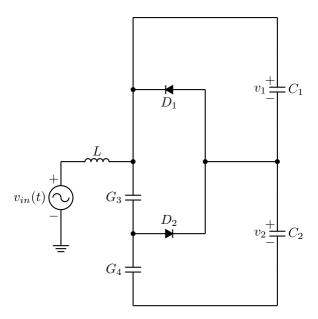

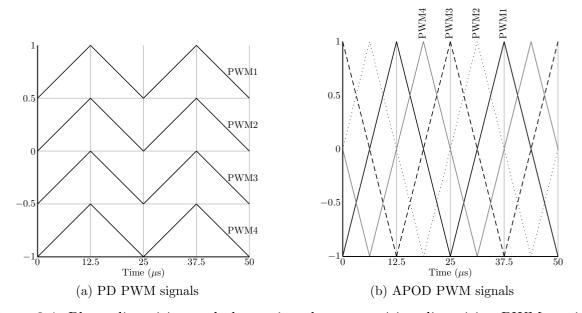

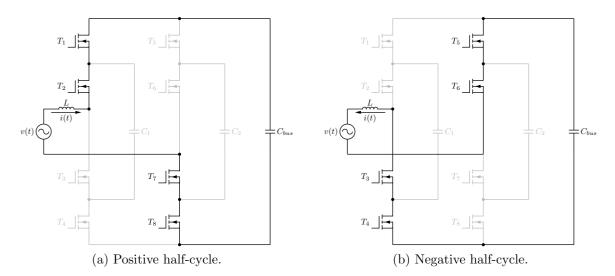

Chapters 3 and 4 give overviews of the diode-clamped and flying-capacitor multilevel converters, respectively. The basic converter layout and operation of both is given. The diode-clamped multilevel converter has a split DC bus capacitor that provides different voltage levels. The three-level converter has two bus capacitors each having voltage of  $\frac{1}{2}v_{bus}$ . Apart from the four power switches this three-level converter also requires two clamping diodes. Its clamping mechanism uses the different voltages from the DC bus capacitors to clamp the voltage across an off-state power switch. The flying-capacitor converter has only a single bus capacitor but the three-level converter requires one flying capacitor. This flying capacitor needs to have a balanced voltage of  $\frac{1}{2}v_{bus}$  in order for the switching waveform and clamping mechanism to function correctly. Simulation results for both converter types are given.

Different predictive control strategies are discussed in Chapter 5. The concepts of a cost function, receding horizon and computational effort are discussed. Hysteresis-based control aims to keep the controlled variable within a defined boundary while trajectory-based control aims to keep the variable on the shortest trajectory towards the reference. Deadbeat control uses a modulator to produce the switching signals for a power electronic

converter. The reference value for the modulator that will result in a zero error between the converter output and output reference is calculated at each sampling instant. Modelbased predictive control, with and without a modulator, where a cost function is used to choose the control action is also discussed. Modelling a system to be used with predictive controllers and approximating differential and integral operations in these models are also reviewed. Euler backward and forward, and the fourth-order Runge-Kutta approximations are mentioned while Euler's forward method is used in an example simulation of model-based predictive control.

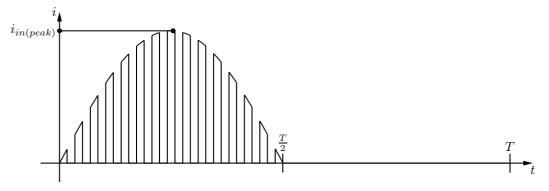

The designing of the converter is done in Chapter 6. The active rectifier and isolation stage is handled separately. For the active rectifier we have to adapt the well known PWM design equations to accommodate the predictive controller. The losses in the power switches are calculated on a worst-scenario case: for the conduction losses we assume the switch conducts 100% of the time, and for the switching losses we assume that the switch switches at every possible instance. The bus capacitor and flying capacitors are also designed for a less than 5% voltage ripple. For the isolation stage the balancing of the flying capacitor voltages need to be considered. As the back-end is not actively controlled, while the flying capacitor voltages still need to be balanced, balance resistors are used. Knowing that the isolation stage operates at a fixed duty cycle and frequency the resistors can be designed.

Chapter 7 concludes the designs with the controller hardware and control algorithms. The measurement circuits are designed taking into account that some of the voltage measurements will have to be taken at a floating ground reference. An isolated op-amp and power supply unit are used to isolate the measurement resistors from the ADC . The input current is measured with a series resistor instead of a hall-effect sensor. The small amount of current makes an hall-effect sensor inaccurate. The switching signals for the power switches are carried via optic fibre links. The control algorithms is developed next. The algorithms for controlling the input current and the internal voltages for a single and dual converters are given. The voltage controller to regulate the bus voltages is also designed.

Simulation and experimental results are given in Chapters 8 and 9, respectively. Simulations are done to verify the correct design of the converters, as well as the functioning of the control algorithms. The experimental results include measurements taken to compare the three proposed control algorithms. Step disturbances and steady-state measurements are used for the comparisons. Chapter 10 concludes this thesis with some conclusions and recommendations.

## Chapter 2

## The Solid-State Transformer

The author of [1] was the first to propose the use of power electronics for a medium voltage solid-state transformer (SST) application. The advantages that an SST has over a conventional line frequency transformer is plentiful: active power filtering; perfect output voltage; ability to output any frequency; ability to interconnect systems with different frequencies or phases; and voltage dip/sag compensation to name but a few. The authors of [11] compared the use of different converter topologies by means of cost and proposed the use of a series-input, parallel-output converter topology. It was compared to the flying-capacitor and diode-clamped multilevel converters. The series connection of smaller converters on the medium voltage input side is to overcome the voltage limitations of available power switches as the applied voltage is divided between all the converters in the series stack. A  $6.6 \,\mathrm{kV}$  three-phase prototype was constructed [5,9,10]. Each phase consisted of 12 cells, each with its own digital controller receiving commands from three main controllers. The voltage balancing between the converters in the stack is of utmost importance to keep the total system voltage divided equally between the stacked converters. Voltage balancing mechanisms were investigated in [8, 27-29]. Other implementations of SST converters, also known as intelligent universal transformers, can be found in [3, 4, 30].

This chapter will give a brief overview of the series-input, parallel-output converter topology proposed by [11] and constructed by [5, 9, 10]. It will also discuss the balancing mechanisms present at the topology and the basic double-loop control strategy to control the active rectifier front-ends will be shown.

## 2.1 Converter Overview

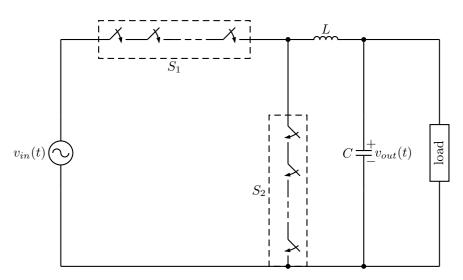

The AC/AC buck converter is possibly the most simple approach to a single phase, power electronics-based transformer. Such an AC/AC converter is shown in Figure 2.1. Each

power switch consists of n power devices to make up the desired voltage rating of the converter and  $S_1$  and  $S_2$  operate complimentary to each other. The relationship between the input and output voltage is given by  $\frac{v_{out}}{v_{in}} \approx D$  [31] where D is the duty cycle of  $S_1$ .

Figure 2.1: AC/AC buck converter.

This approach, although simple and easy to control, is problematic in several areas. Both switch groups  $S_1$  and  $S_2$  need to block total input voltage. For that reason each group consists of several individual power switches. The switches should also be capable of conducting the full load current. The high voltage, high current requirements of the power devices makes the design costly. Other drawbacks are the lack of magnetic isolation; inability to do power factor correction on the input; and its inability to provide dip/sag compensation [4]. These, and other disadvantages, make the use of the AC/AC buck converter unsuitable for the use in medium voltage applications.

An alternative to the AC/AC buck converter has been proposed by [32]. The author's proposed topology is shown in Figure 2.2. The sinusoidal input voltage is modulated by the front-end converter to a high frequency square wave and then passed through the high frequency transformer. The back-end converter synchronously demodulates the output voltage at the secondary winding of the transformer. The topology provides the advantages of reducing the transformer size and voltage stresses on components. It does not, however, provide any added benefits regarding control or power factor improvements.

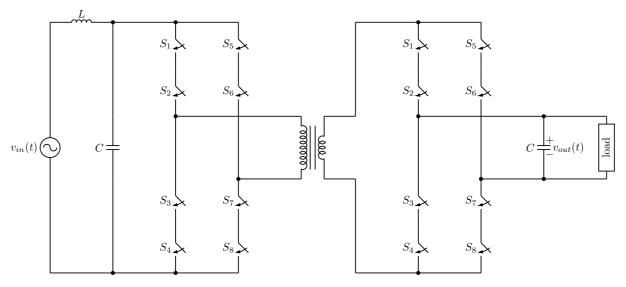

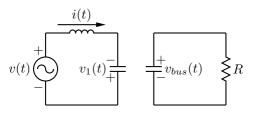

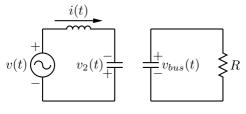

The topology suggested by [11] has the same advantages as mentioned above, as well as control over the power factor, dip/sag compensation and other power quality benefits. A single cell of such a series-input, parallel-output converter is shown in Figure 2.3. The cell is the building block of the SST concept. The front-end is an active rectifier to convert the 50 Hz input voltage to DC. The isolation stage then converts the DC to a high frequency square wave to pass it through the isolation transformer to the passive rectifier. For the

Figure 2.2: Alternative solid-state transformer topology.

implementation by [6] each cell consists of a back-to-back full-bridge converter, isolation transformer, passive rectifier and LC-low-pass filter. Other implementations made use of diode-clamped converters [3, 30] and boost converters [4] to construct the cell.

Figure 2.3: A single cell of a stacked converter.

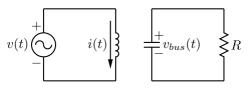

The series-input, parallel-output converter topology is shown in Figure 2.4. The series input will let the input voltage divide between the cells in the stack. An input voltage larger than the blocking voltage of a single power switch can therefore be handled. The DC outputs are connected in parallel to produce a low voltage DC bus. This bus can be connected to an inverter to produce a line frequency, low voltage output for residential use.

The active rectifier front-end of the converter provides the user with control over the input power factor of the SST. The converter can operate at unity power factor or be applied for power factor correction when used in conjunction with conventional transformers. Furthermore, the bus capacitors of each cell provides energy storage capacity that can be utilised during times of input voltage dips in order to provide an uninterrupted output.

Figure 2.4: An *N*-cell stack topology.

## 2.2 Bus Voltage Balancing

The use of a series-input, parallel-output converter has the challenge that the bus voltages of all the cells need to be balanced in steady-state. The authors of [7] proved that a two cell, series-input, parallel-output converter with synchronous rectifiers has a natural balancing mechanism. This proof was extended to a 12-cell converter with passive rectifiers in [33]. Series-input, parallel-output converters exhibits two types of natural balancing: a weak and strong mechanism.

The weak mechanism is first mentioned in [34–36] in the study of flying-capacitor converters. It depends on the use of an interleaved switching scheme where the same reference value is used for all the converters in the stack but their PWM carriers are phase shifted with respect to each other. Any unbalance in the bus voltages will result in an increased current ripple on the actively rectified input current. The unbalanced energy will be dissipated in this increased ripple and therefore attempt to rebalance the bus voltages.

The addition of the isolation back-end to the active rectifier brings with it the strong

balancing mechanism. An unbalance in the bus voltages will be opposed by the fact that a higher bus voltage will deliver more power across the isolation barrier. If more power is delivered the bus voltage will tend to decrease. It is therefore important that all isolation stages be switched at equal effective duty cycles. A larger duty cycle also has the effect of delivering more power across the isolation barrier and will thus let its bus voltage decrease below the nominal.

The sensitivity to component mismatches is also described in [33]. Unequal transformer turn ratios between cells will let unequal amounts of power across the various isolation barriers. The leakage inductance of the transformer has the effect of reducing the effective duty cycle of the isolation stage converter. A mismatch in the leakage inductances will again let unequal amounts of power across the various isolation barriers. The leakage inductance mismatch will affect the voltage balancing the most at high power levels where the transformer currents are higher. With variations in the filter inductors of the passive rectifiers the cells will go into discontinuous conduction mode at different (DCM) times. DCM will only appear at small output currents and will therefore occur at low power levels.

### 2.3 Control

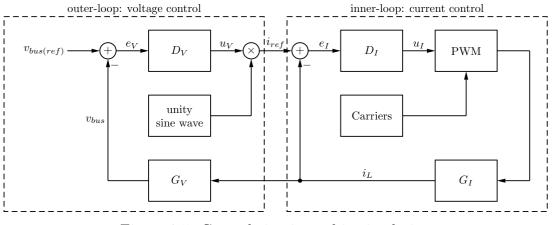

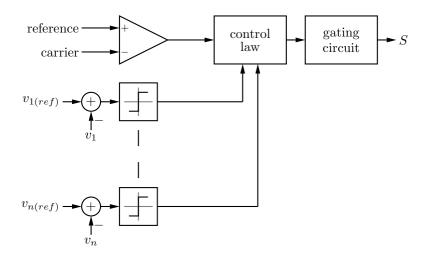

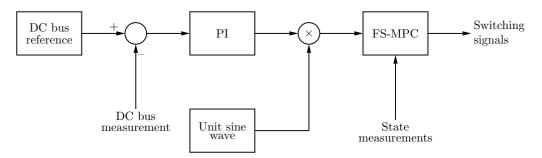

The author of [9] used a double loop control scheme to control the sinusoidal input current and bus voltages of a 12-cell series-input, parallel-output converter. The scheme is shown in Figure 2.5 where  $v_{bus}$  is the sum of the bus voltages. The control scheme's output  $u_I$ is the duty cycle command that will be compared to phase shifted carriers to obtain the switching signals for the power switches of the active rectifiers.

Figure 2.5: Double-loop active rectifier control block diagram.

The converter is divided into two plant transfer functions:  $G_I$  and  $G_V$ .  $G_I$  receives the switching signals and produces the input current for the active rectifier.  $G_V$  takes

this current as input and produces the bus voltage. The control scheme has two loop compensators, both of which are PI compensators.  $D_V$  is responsible for regulating the total bus voltage. Its output is multiplied with an unity sine wave which is in-phase with the input voltage. This gives the input current reference for which  $D_I$  is the compensator.  $D_I$  has a large gain integral component to have a fast current tracking response.  $D_V$  also has a integral component to ensure a zero steady-state tracking error but this is much slower than the inner current loop. The current loop can thus be designed and then considered as a current source to design the voltage compensator.

### 2.4 Summary

This chapter introduced the solid-state transformer concept and discussed various converter topologies associated with it. The series-input, parallel-output topology was highlighted and discussed further. The contents, and purpose thereof, of each cell in an n-stack SST as implemented by [6] were given. The natural voltage balancing mechanism present was also discussed. The importance of balanced bus voltages throughout the stack of series-input converters should be respected. In the event of a severe unbalance in the bus voltages the operating voltage of one or more cells could be exceeded. This could happen while the input voltage is still within the voltage limitation of the SST as a whole.

Fortunately, the balancing of the bus voltages occurs naturally and quite strongly. The use of series-input converters is therefore an effective way to increase the operating voltage of a converter beyond that of a single power switch. Furthermore, the parallel-output converters, as in Figure 2.4, has the advantage of providing the user with a low voltage DC bus that could be used for industrial applications.

## Chapter 3

## **Diode-Clamped Converter**

The diode-clamped converter was developed in the late 1970s and early 1980s [13,37]. It was developed to reduce the harmonic content in the outputs of motor drives as PWM techniques have their limitations when trying to reduce harmonic content [38,39]. The new converter was able to eliminate the fifth and seventh harmonics of the output voltage. Another advantage of the new converter type is the fact that the voltage stresses on the power switches are only half that of conventional converters. The number of power switches in the converter is, however, double that of a conventional full-bridge converter.

After the publications of [13,37] variations of the diode-clamped concept was proposed to further increase the voltage handling capability of the converter. These include expanding the three-level converter to an arbitrary number of levels as in [12] and some modifications to the layout of the converter such as proposed by [40]. The authors of [40] proposed a solution to the different blocking voltages need for the clamping diodes. A simple solution is to tie the appropriate amount of diodes in series. The large RC snubbers required to ensure even voltage division between the series diodes lead to an expensive and large system. They proposed a new *pyramid* structure for the clamping diodes where all diodes have the same voltage rating and no diodes are connected in series.

This chapter gives the basic layout for a full-bridge, three-level, diode-clamped active rectifier. The switching states for the possible output voltages are given and the clamping mechanism for the power switches is discussed. Next, the importance and methods of voltage balancing of the bus capacitors are discussed and simulation results are presented to show the inability of PWM to control a full-bridge, three-level, diode-clamped converter as an active rectifier front-end.

## 3.1 Converter Layout