# The Design and Development of an ADCS OBC for a CubeSat

By

Pieter Johannes Botma

Thesis presented in partial fulfilment of the requirements for the degree

Master of Science in Engineering

at the Faculty of Engineering, Stellenbosch University

Supervisor: Prof. W.H. Steyn Department of Electrical and Electronic Engineering

December 2011

Stellenbosch University http://scholar.sun.ac.za

**DECLARATION**

By submitting this thesis electronically, I declare that the entirety of the work

contained therein is my own, original work, that I am the sole author thereof (save to

the extent explicitly otherwise stated), that reproduction and publication thereof by

Stellenbosch University will not infringe any third party rights and that I have not

previously in its entirety or in part submitted it for obtaining any qualification.

Date: December 2011

Copyright © 2011 StellenboschUniversity

All rights reserved.

# **ABSTRACT**

The Electronic Systems Laboratory at Stellenbosch University is currently developing a fully 3-axis controlled *Attitude Determination and Control Subsystem* (ADCS) for CubeSats. This thesis describes the design and development of an *Onboard Computer* (OBC) suitable for ADCS application. A separate dedicated OBC for ADCS purposes allows the main CubeSat OBC to focus only on command and data handling, communication and payload management.

This thesis describes, in detail the development process of the OBC. Multiple *Microcontroller Unit* (MCU) architectures were considered before selecting an ARM Cortex-M3 processor due to its performance, power efficiency and functionality. The hardware was designed to be as robust as possible, because radiation tolerant and redundant components could not be included, due to their high cost and the technical constraints of a CubeSat.

The software was developed to improve recovery from lockouts or component failures and to enable the operational modes to be configured in real-time or uploaded from the ground station. Ground tests indicated that the OBC can handle radiation-related problems such as latchups and bit-flips. The peak power consumption is around 500 mW and the orbital average is substantially lower. The proposed OBC is therefore not only sufficient in its intended application as an ADCS OBC, but could also stand in as a backup for the main OBC in case of an emergency.

# **OPSOMMING**

Die Elektroniese Stelsels Laboratorium by die Universiteit van Stellenbosch is tans besig om 'n volkome 3-as gestabiliseerde oriëntasiebepaling en -beheerstelsel (Engels: *ADCS*) vir 'n *CubeSat* te ontwikkel. Hierdie tesis beskryf die ontwerp en ontwikkeling van 'n aanboordrekenaar (Engels: *OBC*) wat gebruik kan word in 'n *ADCS*. 'n Afsonderlike *OBC* wat aan die *ADCS* toegewy is, stel die hoof-*OBC* in staat om te fokus op beheer- en datahantering, kommunikasie en loonvragbestuur.

Hierdie tesis beskryf breedvoerig die werkswyse waarvolgens die *OBC* ontwikkel is. Verskeie mikroverwerkers is as moontlike kandidate ondersoek voor daar op 'n ARM Cortex-M3-gebaseerde mikroverwerker besluit is. Hierdie mikroverwerker is gekies vanweë sy spoed, effektiewe kragverbruik en funksionaliteit. Die hardeware is ontwikkel om so robuust moontlik te wees, omdat stralingbestande en oortollige komponente weens kostebeperkings, asook tegniese beperkings van 'n *CubeSat*, nie ingesluit kon word nie.

Die programmatuur is ontwikkel om van 'n uitsluiting en 'n komponentfout te kan herstel. Verder kan programme wat tydens vlug in werking is, verstel word en vanaf 'n grondstasie gelaai word. Grondtoetse het aangedui dat die *OBC* stralingverwante probleme, soos 'n vergrendeling (*latchup*) of bis-omkering (*bit-flip*), kan hanteer. Die maksimum kragverbruik is ongeveer 500 mW en die gemiddelde wentelbaankragverbruik is beduidend kleiner. Die voorgestelde *OBC* is dus voldoende as *ADCS OBC* asook hoof-*OBC* in geval van nood.

# **ACKNOWLEDGEMENTS**

The author would like to thank and acknowledge the following for their contribution towards this project:

- **Prof W.H. Steyn** for his knowledge, guidance and patience throughout this project.

- All the people of the ESL, especially Hanco Loubser, AM de Jager, Arno Barnard and Johan Arendse, for their helpful inputs.

- My family and friends, especially Elzaan Kotzé, for their support and understanding during my long hours at work.

- God, for giving me the talents and opportunities to follow my dream.

# **CONTENTS**

| D  | eclarati | on                               | i    |

|----|----------|----------------------------------|------|

| Αl | bstract. |                                  | . ii |

| Oj | psomm    | ing                              | iii  |

| A  | cknowl   | edgements                        | iv   |

| Co | ontents. |                                  | . v  |

| Li | st of Fi | gures                            | ix   |

| Li | st of Ta | ibles                            | хi   |

| No | omencl   | ature                            | xii  |

| 1  | Bacl     | cground                          | . 1  |

|    | 1.1      | Mission                          | . 1  |

|    | 1.2      | CubeSat                          | . 3  |

|    | 1.3      | ADCS                             | . 4  |

|    | 1.4      | Space Environment                | . 6  |

|    | 1.4.1    | Radiation Effects                | . 6  |

|    | 1.4.2    | 2 Remoteness                     | . 7  |

|    | 1.5      | Document Outline                 | . 8  |

| 2  | Hard     | lware Design                     | . 9  |

|    | 2.1      | Requirement Definition           | . 9  |

|    | 2.1.1    | Performance                      | . 9  |

|    | 2.1.2    | 2 Efficiency                     | . 9  |

|    | 2.1.3    | Reliability                      | . 9  |

|    | 2.2      | Microcontroller Selection        | 10   |

|    | 2.2.1    | 8-Bit vs. 16-Bit vs. 32-Bit MCUs | 10   |

|    | 2.2.2    | 2 Microcontroller Comparisons    | 11   |

|    | 2.2.3    | B EFM Gecko MCU                  | 13   |

|   | 2.3   | System Overview and Design     | 19 |

|---|-------|--------------------------------|----|

|   | 2.3.  | 1 MCU                          | 19 |

|   | 2.3.2 | 2 External Memory Subsystem    | 22 |

|   | 2.3.3 | Power Subsystem                | 27 |

|   | 2.3.4 | 4 Monitoring Subsystem         | 29 |

|   | 2.3.5 | 5 Communication Subsystem      | 31 |

| 3 | Soft  | ware Development               | 33 |

|   | 3.1   | Hardware Abstraction Layer     | 33 |

|   | 3.2   | Drivers                        | 34 |

|   | 3.2.  | 1 External Bus Interface       | 34 |

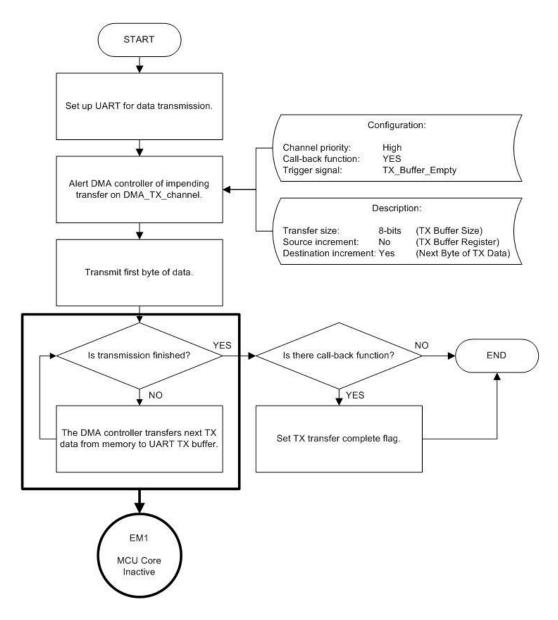

|   | 3.2.2 | 2 Direct Memory Access         | 35 |

|   | 3.2.3 | 3 Analog to Digital Converter  | 37 |

|   | 3.2.4 | 4 Real-Time Clock              | 38 |

|   | 3.2.5 | 5 Watchdog                     | 39 |

|   | 3.2.0 | 6 UART                         | 40 |

|   | 3.2.7 | 7 SPI                          | 40 |

|   | 3.2.8 | 8 I2C                          | 41 |

|   | 3.3   | Error Detection and Correction | 42 |

|   | 3.3.  | 1 Linear Block Codes           | 42 |

|   | 3.3.2 | 2 Reed-Muller Code             | 44 |

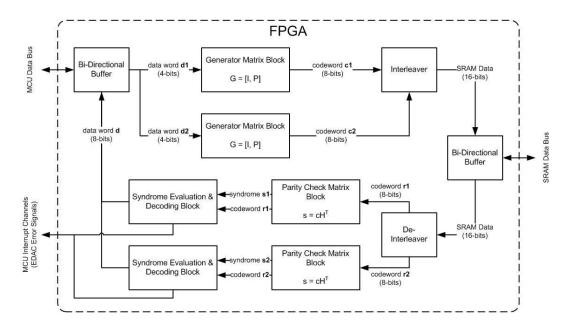

|   | 3.3.3 | 3 Implementation               | 45 |

|   | 3.3.4 | 4 Error Handling               | 46 |

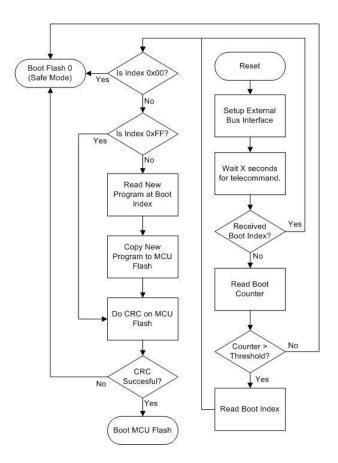

|   | 3.4   | Bootloader                     | 47 |

|   | 3.4.  | 1 Program Types                | 48 |

|   | 3.4.2 | 2 Implementation               | 48 |

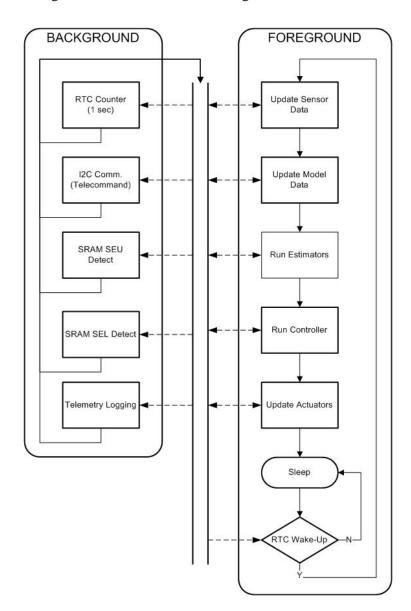

|   | 3.5   | Operating System               | 50 |

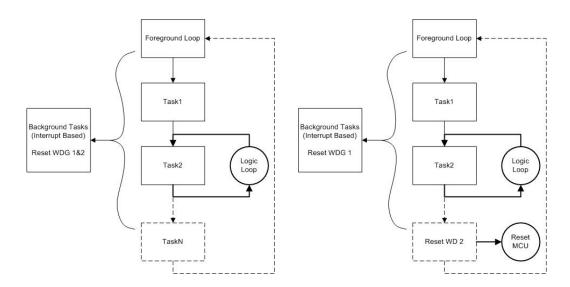

|   | 3.5.  | 1 Foreground Application       | 50 |

|   | 3.5.  | 2 Background Tasks/Services    | 51 |

| 4 | Test  | s and Measurements.            | 53 |

|   | 4.1   | Background Services          | 53 |

|---|-------|------------------------------|----|

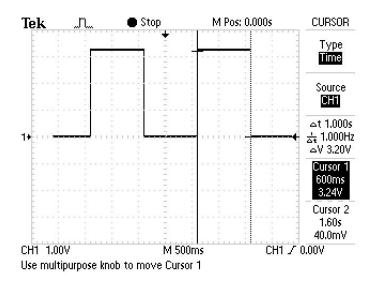

|   | 4.1.  | 1 RTC                        | 53 |

|   | 4.1.2 | 2 Telemetry Logging          | 54 |

|   | 4.1.  | 3 Single Event Upsets        | 55 |

|   | 4.1.4 | 4 Single Event Latchup       | 58 |

|   | 4.1.  | 5 Communication              | 59 |

|   | 4.2   | Hardware In The Loop         | 60 |

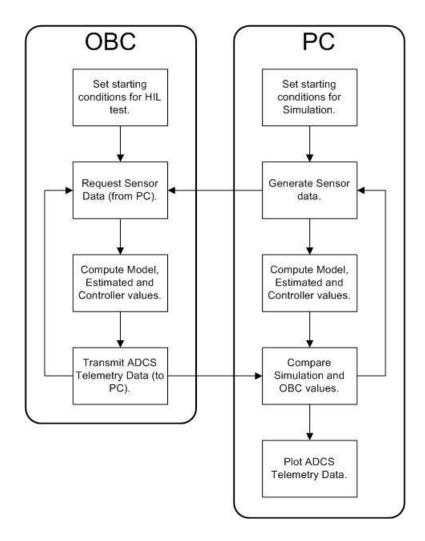

|   | 4.2.  | 1 Setup                      | 60 |

|   | 4.2.2 | PC Communication Protocol    | 62 |

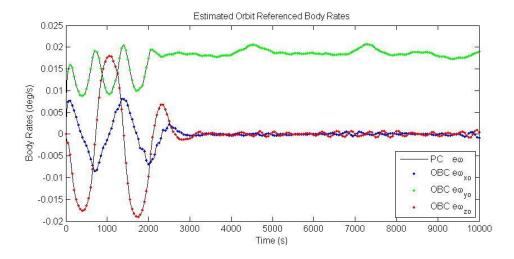

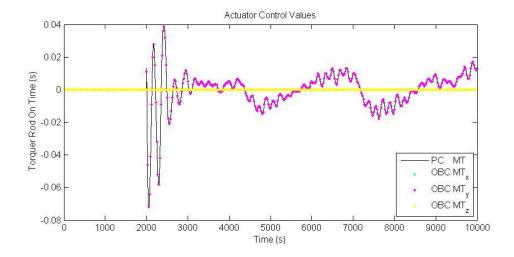

|   | 4.2.3 | 3 Results                    | 63 |

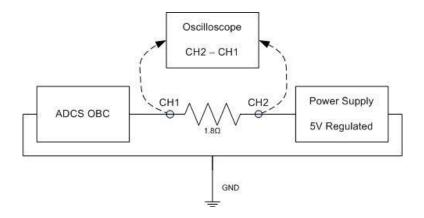

|   | 4.3   | Power Consumption            | 64 |

| 5 | Con   | clusions and Recommendations | 66 |

|   | 5.1   | Conclusions                  | 66 |

|   | 5.2   | Recommendations              | 67 |

|   | 5.2.  | 1 Layout                     | 67 |

|   | 5.2.2 | 2 Microcontroller            | 67 |

|   | 5.2.3 | 3 EEPROM                     | 68 |

|   | 5.2.4 | 4 Protocol                   | 69 |

|   | 5.2.  | 5 Real-Time Operating System | 70 |

| 6 | Sum   | nmary                        | 71 |

| A | Hard  | dware Design Details         | 73 |

|   | A.1   | Hardware Design Guidelines   | 73 |

|   | A.2   | Current Sensor Design        | 73 |

| В | Sch   | ematics                      | 74 |

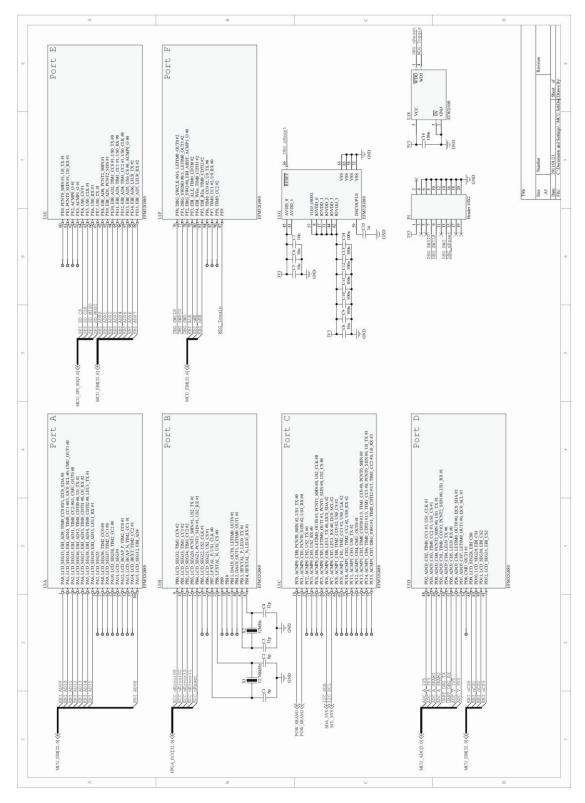

|   | B.1   | MCU                          | 74 |

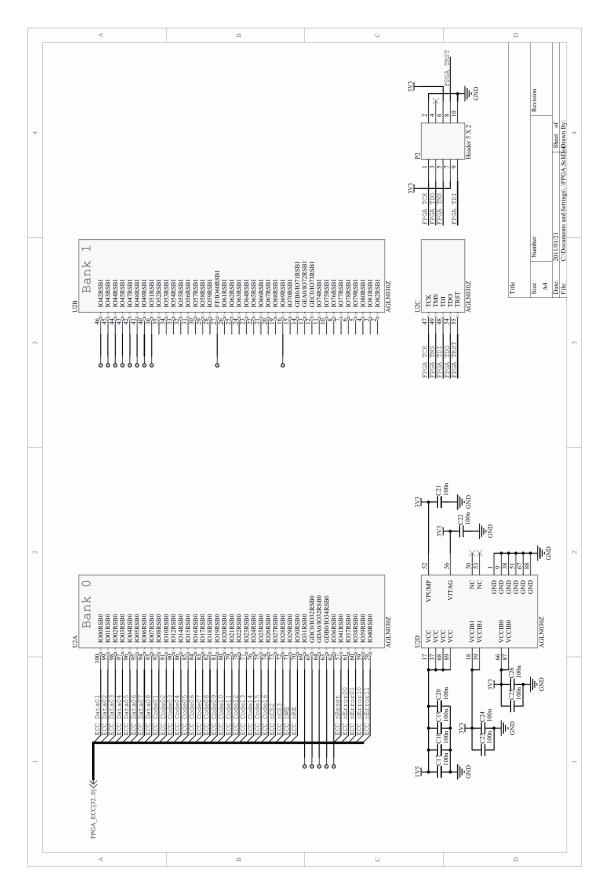

|   | B.2   | FPGA                         | 75 |

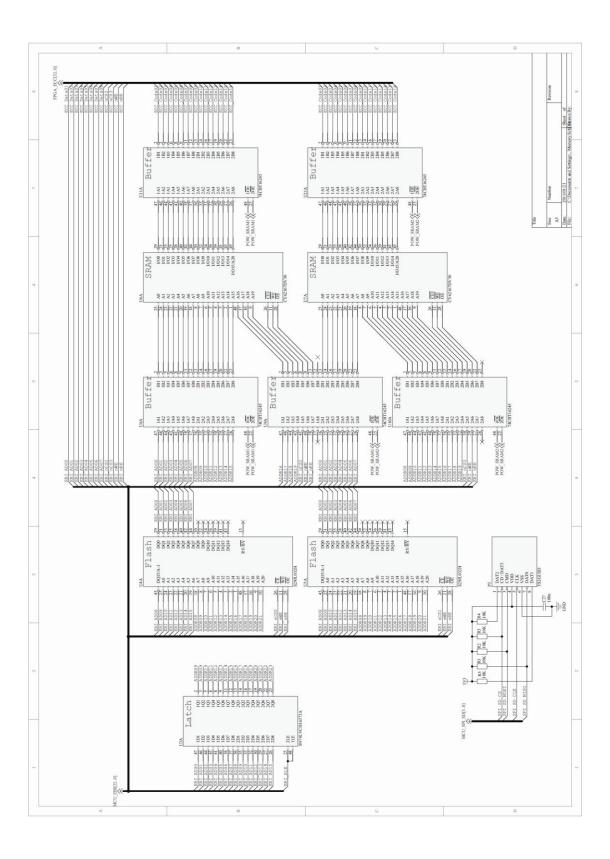

|   | B.3   | Memory Bus                   | 76 |

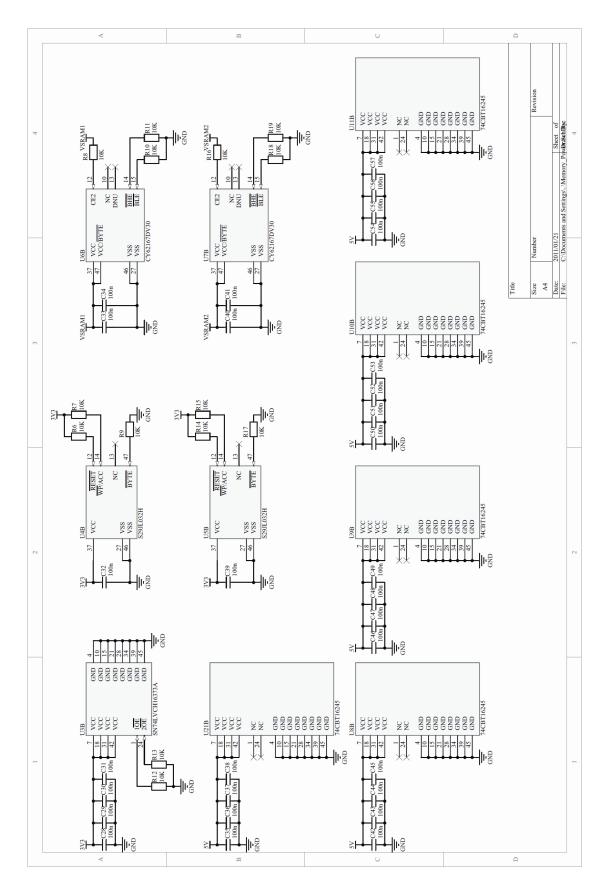

|   | B.4   | Memory Power                 | 77 |

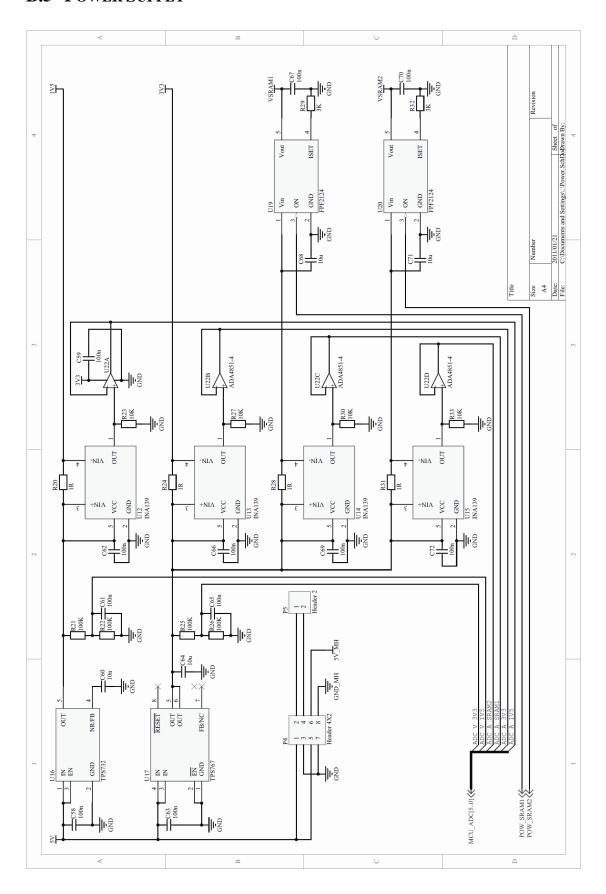

|   | B.5   | Power Supply                 | 78 |

| C   | PCE         | 3 Lay  | out                                                | 79 |

|-----|-------------|--------|----------------------------------------------------|----|

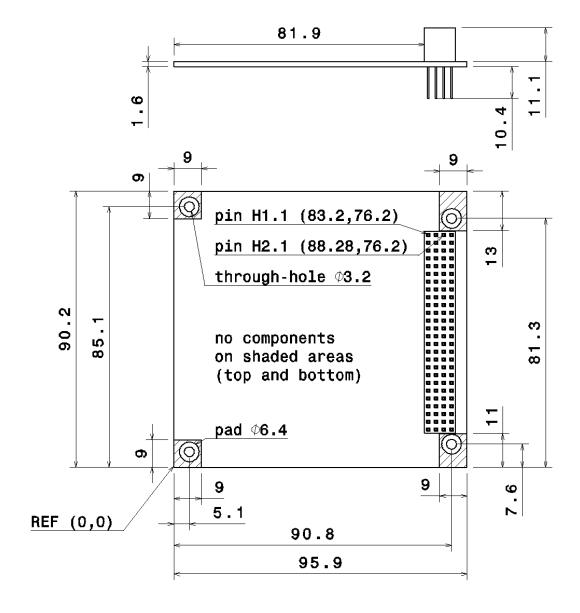

| (   | C.1         | Cub    | peSat Layout Standard                              | 79 |

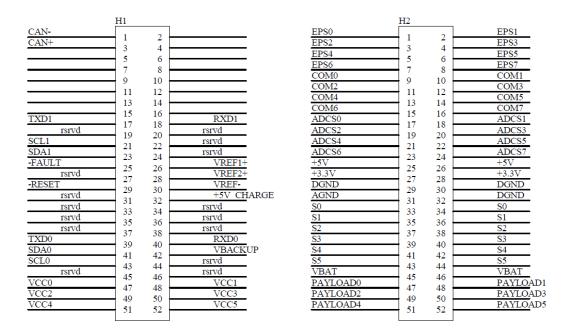

|     | C.1.        | .1     | Electrical Layout Standard (Header Pin Allocation) | 79 |

|     | C.1.        | .2     | Mechanical Layout Standard (PCB Design)            | 79 |

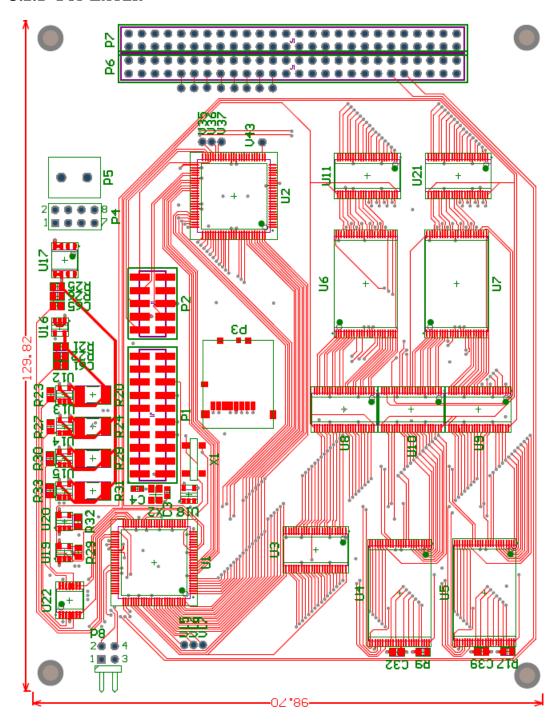

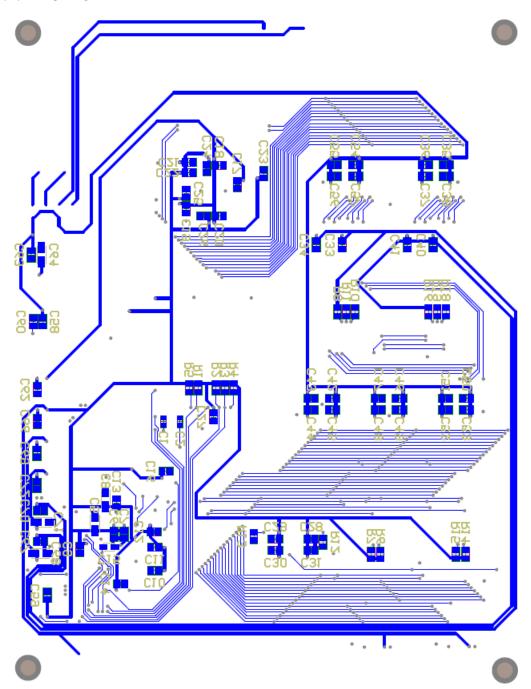

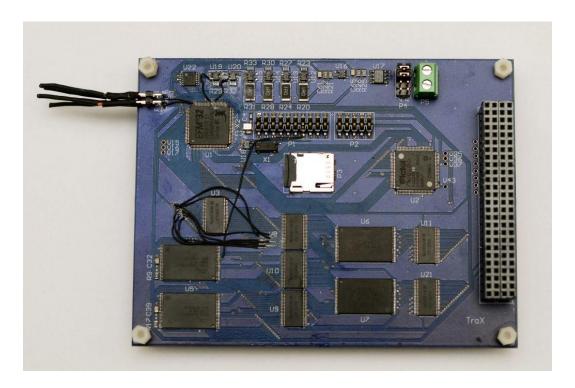

| (   | C.2         | AD     | CS OBC Layout                                      | 81 |

|     | C.2.        | .1     | Top Layer                                          | 81 |

|     | C.2.        | .2     | Bottom Layer                                       | 82 |

|     | C.2.        | .3     | ADCS OBC Photo                                     | 83 |

| D   | Deta        | ailed  | Driver Descriptions                                | 84 |

| I   | D.1         | Rea    | ıl Time Clock                                      | 84 |

| I   | D.2         | Wat    | tchdog                                             | 85 |

| I   | D.3         | Ana    | alog to Digital Converter                          | 86 |

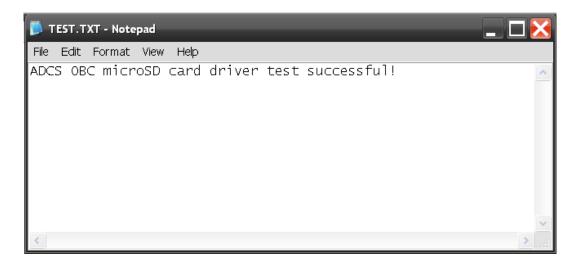

| I   | D.4         | Mic    | eroSD                                              | 87 |

| I   | D.5         | Exte   | ernal Bus Interface                                | 88 |

| I   | <b>D</b> .6 | Uni    | versal Asynchronous Receiver / Transmitter         | 89 |

| Е   | EDA         | AC D   | Design                                             | 91 |

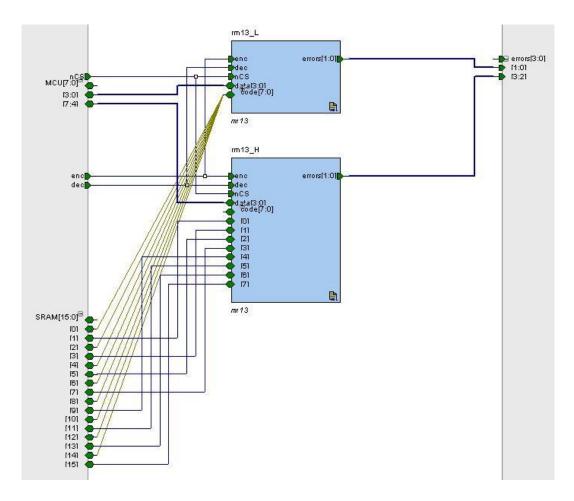

| I   | Ξ.1         | EDA    | AC FPGA Implementation                             | 91 |

| I   | E.2         | Exa    | mple                                               | 94 |

| F   | Sup         | port l | Files CD                                           | 97 |

| Bib | oliogra     | aphy.  |                                                    | 98 |

# **LIST OF FIGURES**

| Figure 1.1: SSTL STRaND CubeSat. [4]                                    | 2  |

|-------------------------------------------------------------------------|----|

| Figure 1.2: Examples of CubeSat Unit Sizes. [44]                        | 4  |

| Figure 1.3: ADCS Control Loop for a Satellite. [7]                      | 5  |

| Figure 1.4: South Atlantic Anomaly. [40]                                | 6  |

| Figure 2.1: Cortex-M Energy Efficiency Solution. [10]                   | 11 |

| Figure 2.2: Diagram of EFM32 Gecko MCU. [12]                            | 14 |

| Figure 2.3: Cortex-M3 Processor Core. [17]                              | 15 |

| Figure 2.4: Cortex-M3 Memory and Bus System. [16]                       | 16 |

| Figure 2.5: Cortex-M3 System Address Space. [16]                        | 17 |

| Figure 2.6: Energy Mode Indicator. [16]                                 | 19 |

| Figure 2.7: ADCS OBC Block Diagram.                                     | 20 |

| Figure 2.8: External Memory System of ADCS OBC.                         | 22 |

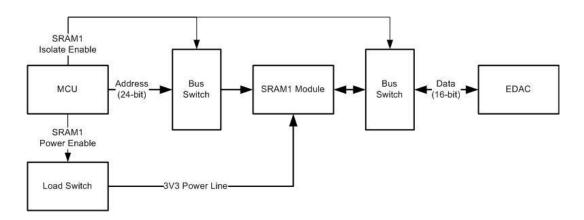

| Figure 2.9: SRAM Isolation Design Diagram.                              | 26 |

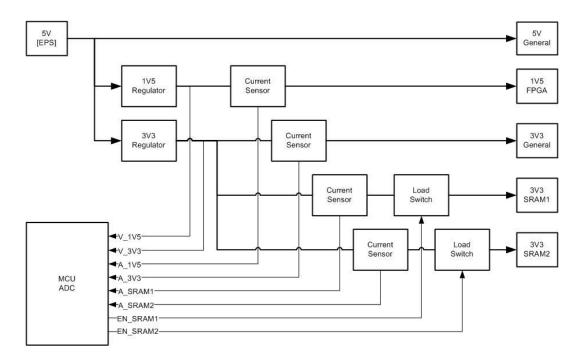

| Figure 2.10: OBC Power System Block Diagram.                            | 28 |

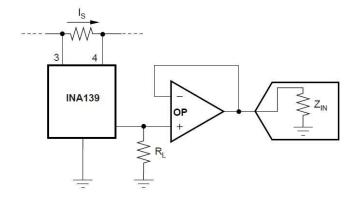

| Figure 2.11: Current Sensor Implementation. [28]                        | 31 |

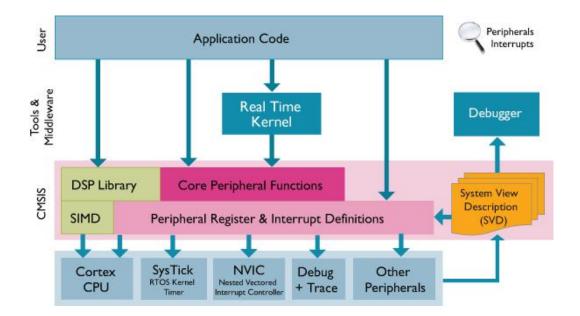

| Figure 3.1: ARM CMSIS Structure. [9]                                    | 34 |

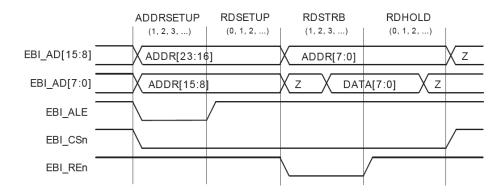

| Figure 3.2: EBI Read Operation. [12]                                    | 35 |

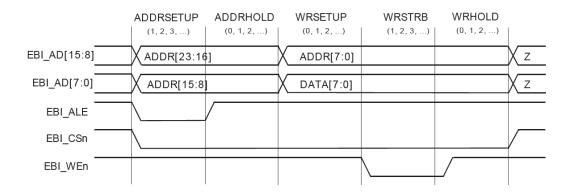

| Figure 3.3: EBI Write Operation. [12]                                   | 35 |

| Figure 3.4: Flowchart of DMA Transfer for ADC.                          | 36 |

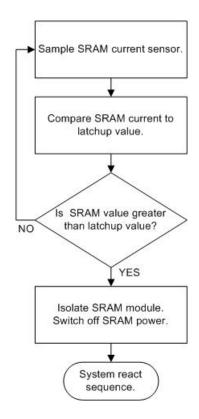

| Figure 3.5: SRAM Latchup Detection                                      | 38 |

| Figure 3.6: Logic Loop.                                                 | 39 |

| Figure 3.7: Logic Loop Prevention.                                      | 39 |

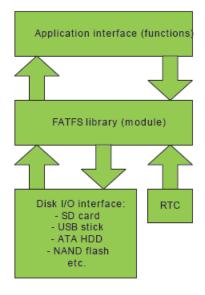

| Figure 3.8: Interface between an Application and the MicroSD Card. [45] | 41 |

| Figure 3.9: Multi Master Bus.                                           | 42 |

| Figure 3.10: Time Shared Bus.                                           | 42 |

| Figure 3.11: Separate Buses.                                            | 42 |

| Figure 3.12: Error Detection and Correction Subsystem on FPGA.          | 45 |

| Figure 3.13: Proposed Bootloader Sequence                               | 49 |

| Figure 3.14: Operating System Flow Diagram for the ADCS OBC.            | 50 |

| Figure 4.1: External Watchdog Toggle Line.                              | 53 |

| Figure 4.2: Text Retrieved from MicroSD Driver Test File                | 54 |

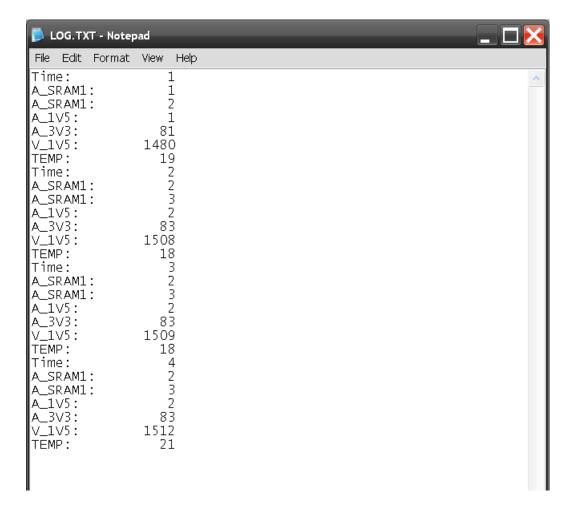

| Figure 4.3: Text Retrieved from Telemetry Logging Test File.            | 55 |

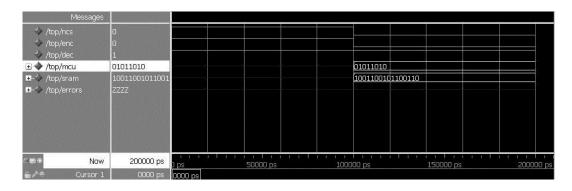

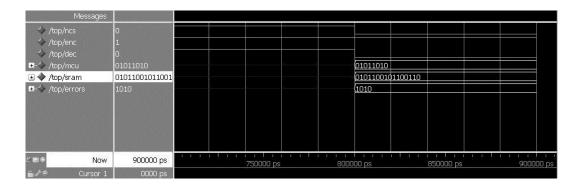

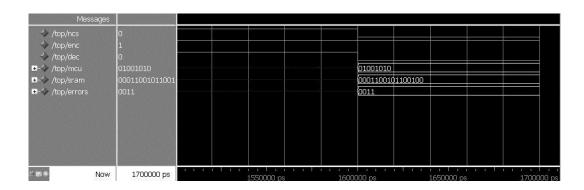

| Figure 4.4: Encoding Process of EDAC.                                        | . 57 |

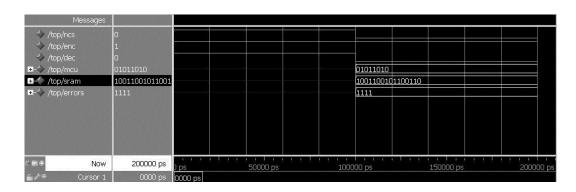

|------------------------------------------------------------------------------|------|

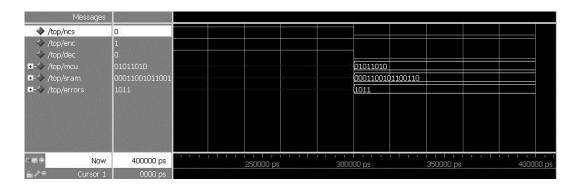

| Figure 4.5: Decoding Process of EDAC with No Errors.                         | . 57 |

| Figure 4.6: Decoding Process of EDAC with One Error.                         | . 57 |

| Figure 4.7: Decoding Process of EDAC with Two Errors.                        | . 58 |

| Figure 4.8: Decoding Process of EDAC with Uncorrectable Errors.              | . 58 |

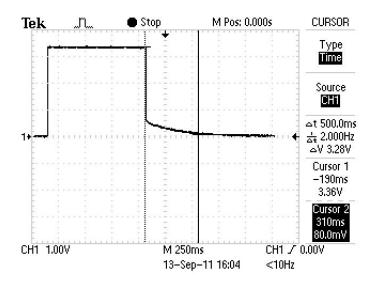

| Figure 4.9: SRAM Supply Voltage Toggled by MCU.                              | . 59 |

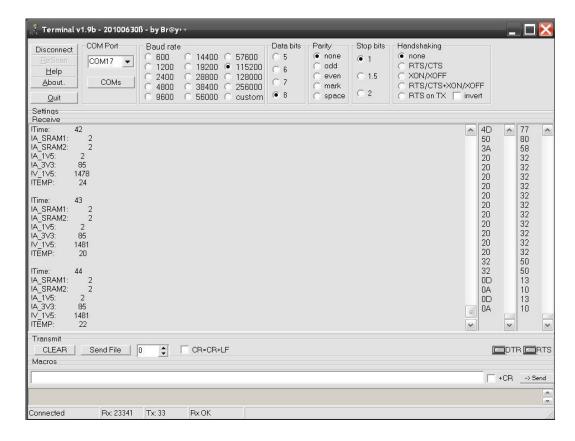

| Figure 4.10: OBC Telemetry Data Output to UART.                              | . 60 |

| Figure 4.11: Hardware In the Loop Test Process.                              | . 62 |

| Figure 4.12: OBC and PC Estimated Body Rates for HIL Test.                   | . 63 |

| Figure 4.13: OBC and PC Actuator Control Values for HIL Test.                | . 64 |

| Figure 4.14: Test Setup for Power Consumption Measurements.                  | . 64 |

| Figure C.1: CubeSat Proposed Electrical Layout Standard (PC/104 Based). [23] | . 79 |

| Figure C.2: CubeSat Mechanical Layout Standard (PC/104 Based). [23]          | . 80 |

| Figure C.3: ADCS OBC Prototype.                                              | . 83 |

| Figure E 1: Top Level Implementation of EDAC on FPGA                         | 94   |

# LIST OF TABLES

| Table 2.1: MCU Comparison (current measurements @ 3.3 V)   | 12 |

|------------------------------------------------------------|----|

| Table 2.2: Comparison of MCU features.                     | 13 |

| Table 2.3: EFM32 Gecko Energy Mode Properties. [16]        | 18 |

| Table 3.1: ADC Driver Functions.                           | 37 |

| Table 3.2: RTC Driver Functions.                           | 39 |

| Table 3.3: Watchdog Driver Functions.                      | 40 |

| Table 3.4: MicroSD Driver Functions.                       | 41 |

| Table 3.5: Error Signal Code Descriptions and MCU Reaction | 46 |

| Table 4.1: Transmission Protocol from PC to OBC.           | 62 |

| Table 4.2: Transmission Protocol From OBC to PC            | 63 |

| Table 4.3: Power Consumption Test Results                  | 65 |

| Table 5.1: EFM32 Gecko and Giant Gecko Comparison          | 68 |

| Table 5.2: Flash and EEPROM Comparison.                    | 69 |

# **NOMENCLATURE**

#### **Abbreviations and Acronyms**

- ADCS Attitude Determination and Control Subsystem

- ADC Analog to Digital Converter

- CMSIS Cortex Microcontroller Software Interface Standard

- CPUT Cape Peninsula University of Technology

- COTS Commercially available Off-The-Shelf

- DAC Digital to Analog Converter

- DMA Direct Memory Access

- EPS Electronic Power System

- ESL Electronic Systems Laboratory

- HAL Hardware Abstraction Layer

- I2C Inter-Integrated Circuit

- IGRF International Geomagnetic Reference Field

- ISR Interrupt Service Routine

- LEO Low Earth Orbit

- MCU Microcontroller Unit

- OBC Onboard Computer

- OS Operating System

- RCO Resistor-Capacitor Oscillator

- RTC Real-Time Clock

- RTOS Real-Time Operating System

- SAA South Atlantic Anomaly

- SEE Single Event Effects

- SEL Single Event Latchup

- SEU Single Event Upset

- SGP4 Simplified General Perturbation no.4

- SPI Serial Peripheral Interface

- SRAM Static Random Access Memory

- SSTL Surrey Satellite Technology Limited

- TID Total Ionizing Dose

- TLE Two Line Elements

- TMR Triple Modular Redundancy

- UART Universal Asynchronous Receiver/Transmitter

- USART Universal Synchronous/Asynchronous Receiver/Transmitter

- XO Crystal Oscillator

# 1 BACKGROUND

#### 1.1 Mission

The Cape Peninsula University of Technology (CPUT) has recently started working on a series of nanosatellite (CubeSat) missions which are detailed in [1]. Due to the importance of a robust Attitude Determination and Control System (ADCS) in most satellite missions, CPUT decided to collaborate with the University of Stellenbosch because of their experience in the ADCS field as well as satellite research in general. The University of Stellenbosch has been involved in the development of two satellites, namely the SUNSAT in 1999 [2] and the SumbandilaSat [3] in 2009. The first CubeSat by CPUT is to be a small  $(10 \times 10 \times 10 \text{ cm})$  satellite with a long antenna as its main payload and a relatively basic ADCS. The mission will be to calibrate the radar antenna patterns for the Hermanus Magnetic Observatory's antenna array in Antarctica. A second, slightly larger satellite (3U CubeSat) will subsequently be developed. The payloads for this satellite still have to be determined.

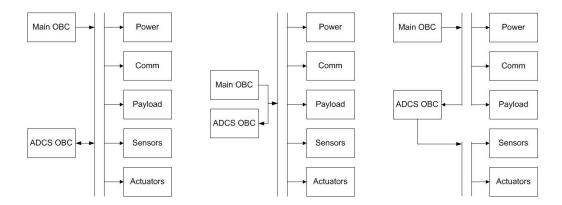

For the 3U CubeSat, the University of Stellenbosch will design a completely independent ADCS unit. This unit will control all the sensors and actuators, run all the algorithms and perform calculations in order to achieve the desired orientation which, through a high-level interface, can be set by the main *Onboard Computer* (OBC) and/or ground station. The two main reasons for implementing the ADCS in a separate unit are managing complexity and improving modularity.

#### 1. Complexity

The ADCS is a very complex subsystem responsible for updating sensor data and controlling actuators, while running multiple models (sun, orbit, etc.), estimators and control algorithms. Because of the large amounts of computations and data being handled, the ADCS tends to dominate an OBC's resources. In order to keep the main OBC free to react to mission-critical subsystems, such as power and communications, it is more desirable to implement the ADCS on a separate OBC.

#### 2. Modularity

Modularity refers to the ability to add, with minimal effort, a unit or module to a system that improves the overall ability of that system. The idea of a CubeSat as a standard satellite bus for which expansion boards of a different subsystem can be added to extend the functionality of the satellite fits very well into this definition of modularity. The

ADCS unit takes that same trend one step further by grouping all ADCS-related expansion boards (sensors and actuators) and having them controlled by a separate OBC. This unit can then be added easily to any CubeSat for which an ADCS is required.

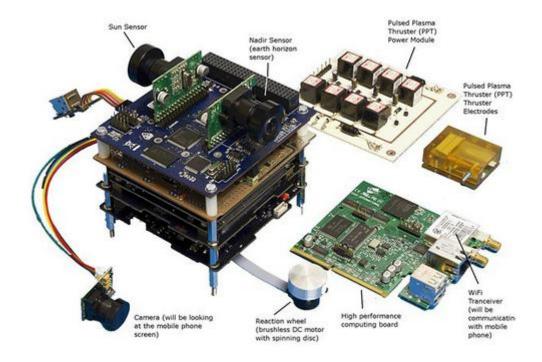

Stellenbosch University's *Electronic Systems Laboratory* (ESL) has already designed a horizon and sun sensor, called CubeSense, which is used in the STRaND CubeSat from *Surrey Satellite Technology Limited* (SSTL) [4] and can be seen in Figure 1.1. The actuators, OBC and ADCS algorithms are still in development.

Figure 1.1: SSTL STRaND CubeSat. [4]

This thesis will document the design and development of the OBC required for the ADCS unit on the 3U CubeSat. The ADCS OBC will act as the interface between the main OBC and the orientation control of the satellite. The desired attitude controller and determination estimator of the satellite can be sent to the ADCS OBC via a telecommand. This will then be interpreted and the control algorithms together with sensor data will then compute the necessary output/commands for the actuators to achieve the desired attitude. The lack of space and power on a CubeSat impose strict limits on its design, which will be discussed later in Section 2.1.

## 1.2 CUBESAT

Traditional satellites tend to be large, complex and expensive systems. To maximise the value of a satellite, multiple payloads are fitted onto one bus. This forced designers to use redundant subsystems and radiation-hardened components to ensure reliability of the satellite which in turn increased the size and cost of the satellite. As the payloads continued to increase in number and complexity, the satellite bus and subsystems had to be redesigned for almost every mission. This made it difficult for academic institutions (such as universities) to start a satellite programme, because of the high cost and technical expertise that even a small satellite used to require. This increasing complexity and cost spiral is the main reason for the development of the CubeSat standard, according to [5].

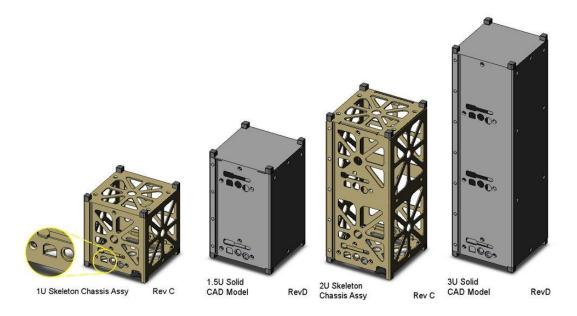

The CubeSat approach is trying to change this by adhering to a satellite bus standard. A 1U CubeSat bus is roughly  $10 \times 10 \times 10$  cm and weighs around 1 kg. Figure 1.1 shows an example of an 1U CubeSat with all its subsystems, excluding the body-mounted solar panels. These CubeSat units can be fit together to create a 2U ( $10 \times 10 \times 20$  cm), 3U ( $10 \times 10 \times 30$  cm), etc. Examples of the chassis to contain these CubeSats are shown in Figure 1.2. There are two main advantages when working with CubeSats. Firstly, the standard size of the satellite structure has allowed for the design of a standard launch adapter (P-POD) which made it easier for CubeSats to piggyback on big satellite launches for a fraction of the price of a dedicated launch [6]. Secondly, it is possible to buy all the components and subsystems to create a space-ready CubeSat [7][8]. Therefore none of the components have to be specially made or developed; it is only necessary to add a payload to the CubeSat to do meaningful research.

Figure 1.2: Examples of CubeSat Unit Sizes. [44]

The standard bus interface and protocol of a CubeSat makes it easier to design subsystems that can be used on multiple CubeSat missions. The use of *Commercially available Off-The-Shelf* (COTS) is encouraged to keep development costs to a minimum as well as to make use of the myriad of electronic components available on the market not necessarily aimed at the space industry. It is possible to manage the risk when not using space grade components on a satellite. This will be shown later in chapters 3 and 4.

The size of a CubeSat makes it a very affordable satellite bus to design and launch but it is this size that limits the weight and power usage when designing a subsystem for a CubeSat. Subsystems have to be very compact to fit into a CubeSat and the small solar panel surface area on the outside of the CubeSat chassis does not generate large amounts of electric power which results in very strict power budgets for each subsystem.

## **1.3 ADCS**

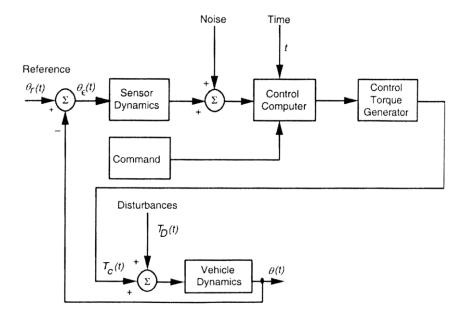

The ADCS is responsible for the orientation of the satellite within its orbit. This subsystem follows the same principle as most control loops and is shown in Figure 1.3. Sensors on the satellite provide the latest measurements regarding its orientation relative to sun (sun sensor), stars (star tracker), earth (horizon sensor and magnetometer) and/or spin rates (gyroscope). The measured data is then compared to reference values set by the main OBC. If an error exists due to sensor noise, external forces on the satellite (drag and solar pressure) and other perturbations (gravity from earth, moon and sun), the satellite can be realigned through the use of actuators such as magnetic torque rods, reaction/momentum wheels and even thrusters.

Figure 1.3: ADCS Control Loop for a Satellite. [7]

Being able to control the orientation of a satellite is very beneficial and might even be considered mandatory for some missions. The following are two common uses for an ADCS with examples:

1. Pointing a device or payload towards a target.

#### **Examples:**

- Pointing an imager at a target for longer exposure and therefore higher quality images.

- Pointing an antenna towards the ground station during an overpass to maximize transmission length and quality.

- 2. Spinning the satellite around an axis at a specified rate.

## **Examples**:

- Spinning the satellite around the axis normal to the orbit plane (Y-Thompson [9]) to stabilize it against external disturbance forces.

- Spinning the satellite around the nadir axis (barbeque spin) to ensure that equal amounts of sunlight reach all the body-mounted solar panels (which also improves thermal stability).

For a more in depth discussion of the advantages and implementations of ADCS for a satellite, refer to [10], pages 354-380.

#### 1.4 SPACE ENVIRONMENT

Space is a hazardous environment. The following section will highlight the major challenges when designing electronic equipment, such as the ADCS OBC, for space.

#### 1.4.1 RADIATION EFFECTS

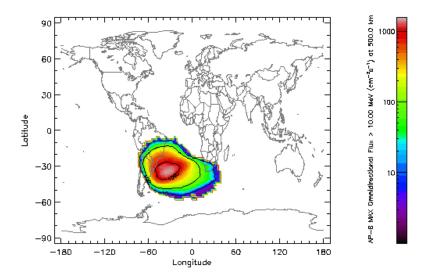

Stars emit various forms of charged particles, known as radiation, during its fusion process. On the earth's surface most of the radiation from space is diverted by the earth's magnetic field. Most of the time satellites in *Low Earth Orbit* (LEO) are within the safety of the magnetic field, except when passing over the *South Atlantic Anomaly* (SAA). The SAA (shown in Figure 1.4) is a region where radiation from the Van Allen belts as well as other charged particles enters the atmosphere. This radiation causes undesired effects in electronic equipment, especially semiconductor devices. A summary of these affects are explained below which can be found in more detail in [11] and [12], pages 214-221.

Figure 1.4: Proton Flux Simulation Showing the South Atlantic Anomaly. [40]

#### • Single Event Upset

A *Single Event Upset* (SEU) occurs when a charged particle causes a change in the contents and/or state of a device without causing permanent damage to that device. [11] A common example is when the content of a memory cell is changed by a charged particle. This is referred to as a bit-flip. These upsets usually do not damage a device, but it could cause undesired effects within the operation of a device or system.

#### • Single Event Latchup

A *Single Event Latchup* (SEL) occurs when radiation causes a parasitic transistor within the device to switch on and result in excessive current flow. [11] This excessive current flow may damage the device, due to the heat generated locally, if the latchup is not removed by means of power cycling (switching power on and off to device).

#### • Total Ionizing Dose

The *Total Ionizing Dose* (TID) is the amount of radiation build-up a device can withstand before its operation is deemed unreliable. [11] The TID tolerance can be seen as a measure for determining the life expectancy of an electronic device. Some electronic devices have a radiation-hardened version which has a greater TID tolerance, but they are considerably more expensive. Some COTS do have a TID tolerance large enough to justify its use on a satellite with a short mission in LEO.

#### 1.4.2 REMOTENESS

One of the major challenges when designing a satellite is to compensate for the fact that if a component or subsystem malfunctions in space, it cannot be brought in for repairs. Some satellites have the ability to reconfigure their software during operation, but when a serious hardware error occurs it usually results in the loss of the satellite. Implementing redundancy and radiation-hardened components are ways in which reliability can be designed into a satellite according to [11] and [12].

#### Redundancy

One form of redundancy is when a satellite has one or more dormant subsystems that can take over in case of a failure. A special case of redundancy called *Triple Modular Redundancy* (TMR) is when three subsystems/devices operate simultaneously and a controller chooses the result based on a majority vote.

#### • Radiation- Hardened Components

One of the major reasons for a failure on satellites is components failing because of radiation (as explained in 1.4.1). Therefore the simplest way to incorporate reliability into a system is to use radiation-hardened components. Some electronic devices have radiation-hardened versions available from their manufactures, but they are much more expensive.

Other challenges for satellite design include thermal issues due to the lack of atmosphere which could cause massive temperature gradients (depending on which side is illuminated by the sun), micro meteorites, spacecraft charging, outgassing and many more which are described in [11], pages 22-27. These challenges will not be discussed in this thesis, because they do not directly influence the design of electronic subsystems, such as, in this case, an ADCS OBC.

#### 1.5 DOCUMENT OUTLINE

The following section gives a short description of each chapter in this document.

- 1. **Background** An introduction to the mission and topics related to the project.

- 2. **Hardware Design** Details the requirement definition of the ADCS OBC and the system, subsystem and component level design.

- 3. **Software Development** Discusses the software development of the ADCS OBC which includes low level and user level interfaces.

- 4. **Tests and Measurements** Lists the results from the tests developed and measurements taken from ADCS OBC prototype.

- Conclusions and Recommendations Discusses the results of the tests and measurements with regards to the requirements and any recommended changes to the ADCS OBC.

- 6. **Summary** A summary of the project.

# 2 HARDWARE DESIGN

This chapter will discuss the techniques followed during the hardware design of the ADCS OBC. Firstly the requirements definition is presented, which served as the standard by which the entire system was designed. The next section covers the process of selecting the microcontroller. This is important for the design, because selecting the appropriate microcontroller directly and indirectly affects the rest of the OBC. Following that, an overview of the OBC will be provided, looking at the different subsystems: why they are there and what they will do. A lower-level overview will then follow which will briefly describe how all the subsystems were implemented and which components were used.

## 2.1 REQUIREMENT DEFINITION

It is important to clearly define the requirements before starting any design. Requirements need to take into account not only the main objective of the design, but the challenges it presents as well. For this project the objective is to design an ADCS OBC for a CubeSat. The following requirements were defined while taking into account the aspects discussed in the previous chapter, such as the complexity of an ADCS, the limitations of a CubeSat and the harsh space environment:

#### 2.1.1 PERFORMANCE

ADCS is a very complex subsystem. Therefore the OBC has to be powerful enough to handle all the complex computations (control algorithms, Kalman filters), precise control (floating-point and double data types) and large amounts of data (telemetry, models and sensor data).

#### 2.1.2 EFFICIENCY

A CubeSat is very limited in power and space. This means that the OBC has to be very efficient and designed as cost effective as possible in terms of power usage and size. Low-power components should be used where possible and if a component or subsystem is not used it should be powered down to conserve energy. The OBC is also required to use less than 1 Watt power during peak operation.

#### 2.1.3 RELIABILITY

On a satellite mission, reliability is always a major requirement because if a failure occurs in space it cannot be repaired and usually results in the end of the mission. The two most common implementations for reliability are to either use radiation-hardened components and/or include redundant components or subsystems. However, neither of these are an option

for the CubeSat. Radiation-hardened components are too expensive and redundancy takes up too much space.

The only way to ensure reliability is to design the OBC to be robust. Robustness is the ability to adapt and survive in case of an emergency. From a design point of view this means including error-detection measures that will respond by either trying to rectify or isolate these errors. The OBC should be robust on both the hardware as well as the software level in order to cope with the hazardous space environment.

#### 2.2 MICROCONTROLLER SELECTION

The *Microcontroller* (MCU) is the most important component on an OBC. The features of the MCU usually dictate how the rest of the OBC is designed, because it acts as the interface between the majority of the components. Due to the ever-growing electronic market, especially in terms of efficiency, many different MCUs are available to choose from.

#### 2.2.1 8-BIT VS. 16-BIT VS. 32-BIT MCUS

An 8-Bit MCU is used in designs where power usage is considered vital. Its small architecture allows it to control a system with minimal power usage, but also limits its mathematical capabilities, especially with large data types such as floats and doubles.

A 32-Bit MCU is mostly used for application purposes where large amounts of data are being processed and power is a secondary (or not even a) factor. It is very capable at math handling due to its larger registers and bus widths.

A 16-Bit MCU fills the slot between these two extremes. It is much better at math and floating-point handling, compared to 8-bit MCUs, while still maintaining efficiency and power consumption.

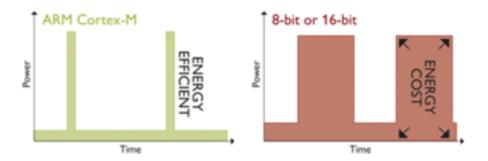

Taking the above into account, a 16-bit MCU would seem the logical choice for the ADCS OBC. However, a recent shift in the market has occurred. Manufactures, such as ARM [13] and Atmel [14], are providing 32-bit processors aimed at the low-power (8-bit / 16-bit) market. These MCUs do not only perform better, but their power usage is comparable (and even superior in some cases) to the 16-bit MCUs. This is possible because a 32-bit MCU will generally complete the same tasks and computations faster than a 16-bit MCU and therefore spend more time in an optimized "sleep mode" which results in less energy being used, as illustrated in Figure 2.1.

Figure 2.1: Cortex-M Energy Efficiency Solution. [10]

The new generation low-power 32-bit MCU was identified as an ideal candidate for the ADCS OBC. It is more than capable at handling the computational requirements of the ADCS algorithms but also includes enough energy-saving features which will be required on the limited power budget of a CubeSat.

#### 2.2.2 MICROCONTROLLER COMPARISONS

Table 2.1 compares most of the current low-power 32-bit MCUs from various manufacturers, except for two: the MSP430 is a 16-bit MCU and AT91SAM7 is based on an older 32-bit MCU architecture.

The MSP430 is used in the CubeSat main OBC from Pumpkin (FM430 [15]) and is very competitive with regards to energy consumption. This, in fact, highlights how efficient some of these low-power 32-bit MCUs actually are as they have better active and sleep efficiency than the MSP430. Even though the 16-bit and 32-bit MCUs have comparable power usage, the 32-bit MCUs have a clear advantage regarding performance.

It is interesting to note the similar performance of the EFM32 Gecko, LCP13x and STM32L MCUs. They are all based on ARM's next generation low-power 32-bit architecture called the Cortex-M3 range. The Atmel AT91SAM7A3 is based on the older generation ARM7TDMI architecture and is also included to showcase the differences between the current (Cortex-M3) and previous (ARM7) generation of low-power 32-bit MCUs. The ARM7TDMI architecture has flight heritage in space, onboard the UTIAS SFL's CanX range of satellites [16], which will hopefully translate into the new generation of ARM MCUs.

| <b>Table 2.1:</b> MCU Comparison | (current measurements | (a) | 3.3 V | V). |

|----------------------------------|-----------------------|-----|-------|-----|

|                                  |                       |     |       |     |

| Manufacturer | MCU          | Speed | Performance | Active | Sleep |

|--------------|--------------|-------|-------------|--------|-------|

|              |              | MHz   | DMIPS/MHZ   | uA/MHz | uA    |

| Energy Micro | EFM32 Gecko* | 32    | 1.25        | 180    | 0.6   |

| STM          | STM32L*      | 32    | 1.04        | 230    | 10.4  |

| NXP          | LPC13x*      | 72    | -           | 236    | 30    |

| Atmel        | AT32UC3Lx    | 50    | 1.28        | 300    | 3.5   |

| TI           | MSP430F16x   | 8     | 1.5         | 330    | 1.1   |

| Microchip    | PIC32MX3/4   | 80    | 1.56        | 688    | 25    |

| Freescale    | MCF521       | 80    | 0.95        | 801    | 5.38  |

| Atmel        | AT91SAM7A3   | 60    | 0.9         | 1167   | 175   |

<sup>\*</sup> Cortex-M3-Based Architectures Microcontrollers

Table 2.1 shows that the Cortex-M3-based MCUs are superior in terms of efficiency, closely followed by the AT32UC3L, which is based on the Atmel AVR architecture. These four MCUs have been evaluated further, as summarized in Table 2.2, based on the features of each MCU, which might be useful on an ADCS OBC. These include:

#### • On-chip memory

This includes the amount of available SRAM and flash memory on the chip. This will be required for code and program/user data. The ADCS program works with large data types (float and double) and contains large models, arrays and variables. Therefore, more on-chip memory will allow for larger and more feature rich ADCS programs to be executed.

#### • External Bus Interface

The *External Bus Interface* (EBI) is an interface that allows the MCU to extend its memory capabilities by accessing external memory. This external memory can usually be accessed by the user the same way in which the internal memory is accessed. This is useful when more memory might temporarily be required (telemetry data) or for storing multiple programs the MCU can execute.

#### • Inter-Integrated Circuit

The *Inter-Integrated Circuit* (I2C) is a popular bus-based communication channel also referred to as "two wire interface", because it only uses two IO lines for communication (clock and data). The I2C is the main communication channel on the CubeSat and links the different subsystems. It would therefore be beneficial for the MCU to include an

internal I2C controller, which would reduce the amount of chips on the PCB since an external I2C module will not be needed.

#### • Serial Peripheral Interface

The *Serial Peripheral Interface* (SPI) is a point-to-point-based communication channel which can transfer data at high speeds. This is useful on a satellite when large amounts of data need to be transferred between two subsystems without clogging up the main communication bus.

#### • Analog to Digital Converter

The *Analog to Digital Converter* (ADC) is a unit that samples analog signals (usually voltage) and converts it to a digital value. An ADC unit has a resolution which determines the accuracy of the digital value. ADCs are useful on a satellite because they can be used to measure currents and voltages for telemetry purposes.

Table 2.2: Comparison of MCU features.

| Features         | AT32UC3L | EFM32  | STM32L | LPC13xx |

|------------------|----------|--------|--------|---------|

| Flash (kB)       | 64       | 128    | 128    | 32      |

| SRAM (kB)        | 16       | 16     | 16     | 8       |

| EBI              | N        | Y      | Y      | N       |

| I2C              | 2        | 1      | 2      | 1       |

| SPI              | 1        | 2      | 2      | 1       |

| ADC (Resolution) | 12-bit   | 12-bit | 12-bit | 10-bit  |

Taking the data in Table 2.2 into account, the EFM Gecko MCU was chosen because of its energy efficiency as well as offering all the features that could prove useful on an ADCS OBC for a CubeSat.

#### 2.2.3 EFM GECKO MCU

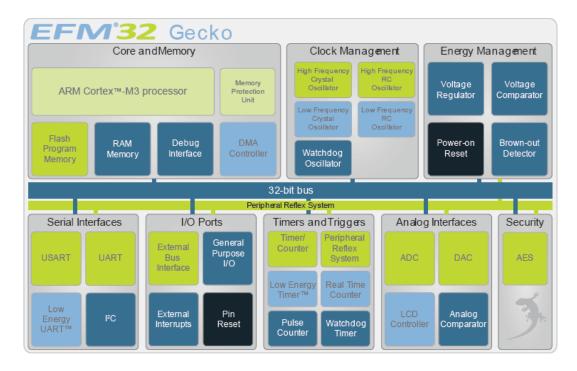

This section will discuss the *EFM32 Gecko MCU* (EFM32G) in further detail, especially looking at its core architecture, energy management schemes, memory and bus system and, finally, peripherals. Figure 2.2 presents a block diagram of the EFM32 MCU on system level. The different colours indicate the different energy modes, which will be further explained later in this section.

Figure 2.2: Diagram of EFM32 Gecko MCU. [12]

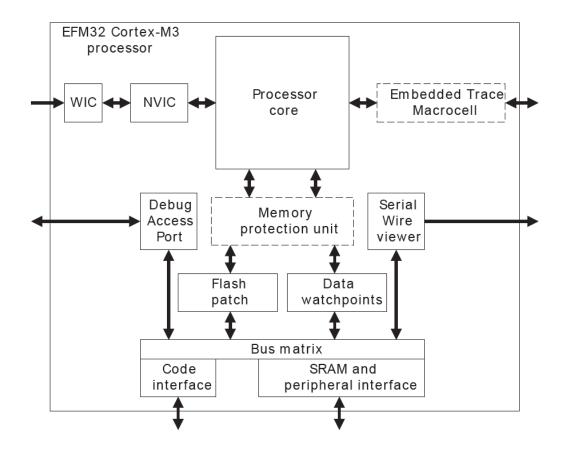

#### 2.2.3.1 ARM CORTEX-M3 CORE

The ARM Cortex-M3 core, shown in Figure 2.3, is based on a high-performance processor core and designed to optimize efficiency. The following are some of the features included with the Cortex-M3 processor.

#### • 3-Stage Pipeline

Most processor instructions consist of three stages, namely the *instruction fetch* (IF), decode and execute stages. The use of a 3-stage pipeline enables the processing of different stages in different pipelines simultaneously. This generally ensures that the processor is completing an instruction per cycle instead of waiting three cycles, for all three stages, to complete a single instruction.

#### • Harvard Architecture

The Harvard architecture uses different memory busses for code and data. On MCUs where there is no cache memory, the Harvard architecture effectively doubles the memory throughput, because the instruction and data (usually stored in separate memory locations such as flash and SRAM) can be fetched simultaneously.

**Figure 2.3:** Cortex-M3 Processor Core. [17]

#### • Hardware Division and Single-Cycle Multiplication

The Cortex-M3 processor core implements hardware division that is able to execute signed and unsigned division operations between two and 12 cycles. Together with a single cycle 32-bit multiplication, this allows for very efficient arithmetic computations, which are usually the most demanding responsibility of an MCU.

#### • Interrupt Handling

The Cortex-M3 processor includes a *nested vector interrupt controller* (NVIC) and *wakeup interrupt controller* (WIC). These controllers allow the MCU to handle interrupts during deep sleep modes, which lowers its energy consumption.

#### • Thumb-2 Instruction Set

The Thumb-2 instruction set is used by the Cortex-M3 processor and offers excellent code density. Even though the Cortex-M3 is a 32-bit MCU, the majority of its instructions are 16-bit [13]. The 32-bit registers and bus width decrease the program size

further because fewer instructions are required when working with larger data types (such as floating-point and double data types).

The Cortex-M3 includes many other features, such as a memory protection unit and extensive debugging capabilities, which can be studied further in the following references: [17] [18].

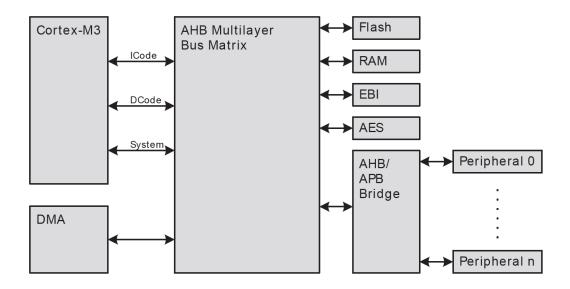

#### 2.2.3.2 MEMORY AND BUS SYSTEM

The EFM32G uses an *AMBA High-performance Bus* (AHB) bus which allows its four bus masters to interact with the system through a memory-mapped address space. The four masters are:

- **I-Code** for instruction fetches to code memory

- **D-Code** for data and debug access to code memory

- System for instruction fetches, data and debug access to system space

- **DMA** for memory transfers to and from the entire memory space

Figure 2.4 is a block diagram of the Cortex-M3 memory and bus system. The four bus masters are shown on the left, with the system components on the right. The peripherals are connected to the AHB through the AHB-to-APB bridge. The system is memory mapped and the address space is shown in Figure 2.5.

Figure 2.4: Cortex-M3 Memory and Bus System. [16]

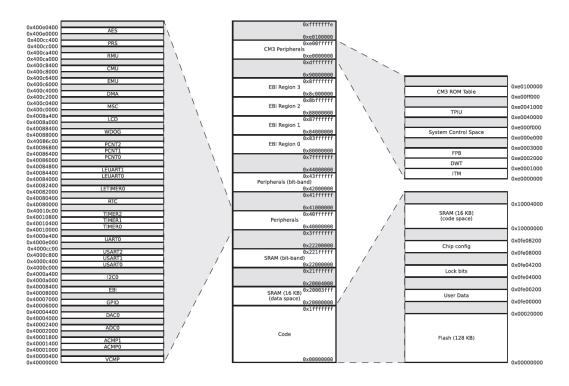

Figure 2.5: Cortex-M3 System Address Space. [16]

#### 2.2.3.3 PERIPHERALS

The EFM32G includes a wide variety of peripherals as well as a few specially developed lowenergy peripherals. These peripherals are the following:

#### 1. General Purpose Input/Output

The EFM32G includes up to 90 *General Purpose Input/Output* (GPIO) pins, depending on the package size. The EFM32G pins allow for multiple configurations of the peripherals to maximize the use of pins and peripherals. They also allow for up to sixteen asynchronous interrupt channels.

#### 2. Timers and Counters

The EFM32G includes three general purpose 16-bit timers. These timers can either be configured as counters, or used for input capture, output compare or *Pulse Width Modulation* (PWM). A watchdog timer and a separate low-energy 16-bit timer are also included, both of which can be used during sleep modes when most other peripherals are disabled.

#### 3. Analog

The EFM32G includes a 12-bit ADC with a sample rate of one million samples per second. The ADC can choose as input one of eight external pins or six internal signals. A 12-bit DAC is included which can either be used in two single-ended modes or in differential mode. A voltage comparator can be used to monitor or compare eight external pins with three internal references. A supply voltage monitor and temperature sensor is included as well for monitoring purposes.

#### 4. Communication

The EFM32G includes the UART communications protocol, which is usually used for debugging purposes. Two low-energy UARTs are also available that are able to operate independently from the main processor during sleep mode by means of the DMA controller. Two further USARTs are included as well and can each be configured either as a UART or an SPI port. The EFM32G further has an I2C module that includes address recognition, even during deep sleep modes.

This list is only a summary of the peripherals available on the EFM32G. For an in-depth look at the peripherals and features available on the EFM32G, please refer to [17].

#### 2.2.3.4 ENERGY MANAGEMENT

The EFM32G has five well-defined energy modes, EM0 – EM4. A variety of wake-up triggers and low latency switching between these modes, allow for the maximum amount of time in the lowest possible energy mode which is key to saving energy. Table 2.3 provides a summary of the properties of the different energy modes available in the EFM32G.

Table 2.3: EFM32 Gecko Energy Mode Properties. [17]

| Energy Mode              | EM0        | EM1       | EM2        | EM3    | EM4     |

|--------------------------|------------|-----------|------------|--------|---------|

|                          | Run        | Sleep     | Deep Sleep | Stop   | Shutoff |

| Current consumption      | 180 uA/Mhz | 45 uA/MHz | 0.9 uA     | 0.6 uA | 20 nA   |

| Wake-up time             | 0          | 0         | 2 us       | 2 us   | 163 us  |

| Core                     | On         |           |            |        |         |

| HF peripherals           | On         | On        |            |        |         |

| LF peripherals           | On         | On        | On         |        |         |

| Register & RAM retention | On         | On        | On         | On     |         |

| Reset detectors          | On         | On        | On         | On     | On      |

For a better understanding of which peripherals are available during a specific energy mode, compare Figure 2.6 with Figure 2.2. The peripherals are colour coded, where each colour represents the lowest energy mode in which the peripheral will respond to activity.

Figure 2.6: Energy Mode Indicator. [16]

#### 2.3 SYSTEM OVERVIEW AND DESIGN

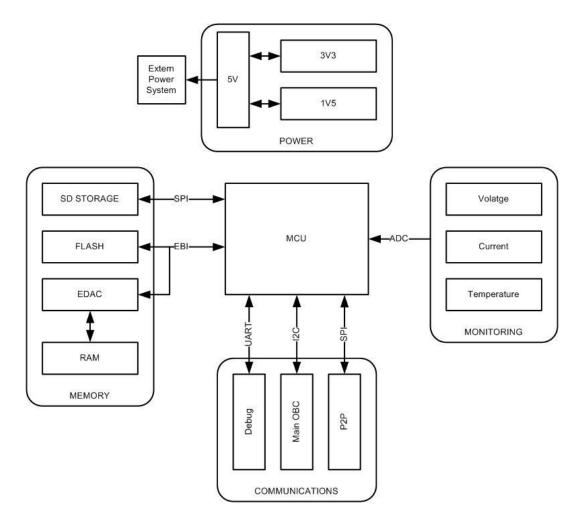

Figure 2.7 shows the ADCS OBC system in block diagram form. The MCU is the core of the OBC with four subsystems (power, monitoring, memory and communication) built around it. In the following sections each of these subsystems will be discussed in further detail with regards to their functions as well as their implementation.

#### 2.3.1 MCU

As mentioned in the previous section, the MCU directly and indirectly affects the other subsystems in the following ways:

- **Power** The MCU requires a stable power supply from the power subsystem.

- Monitoring The MCU actively samples and processes the monitored channels with its ADC peripheral unit.

- **Memory** The MCU is the only component responsible for storing and retrieving data from the external memory.

- **Communication** The MCU connects to external subsystems (main OBC, sensors and actuators) where it either receives data from, or transmits data to.

The significance of the MCU in the OBC necessitates the implementation of extra reliability and accuracy in its design. An external watchdog will add reliability against undesired lock-ups and external real-time and high-frequency crystal oscillators will generate more precise clock signals.

Figure 2.7: ADCS OBC Block Diagram.

#### **2.3.1.1** WATCHDOG

An external watchdog is implemented on the OBC for the MCU. According to [19], the watchdog is a component with an internal countdown timer and is connected to the reset line of the MCU. Unless the watchdog is periodically toggled by the MCU (to reset the internal timer) it will cause the MCU to reset.

The MCU already includes an internal watchdog that should allow the MCU to reset in case the MCU becomes unresponsive due to a software error (runtime exception). Adding an external watchdog would add another level of reliability to the OBC with very little overhead  $(2.90 \times 2.80 \times 1.20 \text{ mm})$  and 500 uA for the STWD100 [20]).

The watchdog used in this design is the STWD100 from ST Microelectronics [20]. The internal timer of the watchdog has to be reset within 1.6 s after the previous reset, which can easily be done when the real time clock generates an interrupt every second. If the internal

timeout is reached, the watchdog will reset the MCU for 210 ms which should allow the MCU to recover from its erroneous state.

#### 2.3.1.2 CRYSTAL OSCILLATOR

Oscillators generate the signals that drive the MCU core and peripherals. The MCU includes internal Resistor-Capacitor Oscillators (RCOs). The high-frequency RCO has a configurable frequency range of 1-28 MHz and the real-time RCO has a frequency of 32.768 kHz. On a satellite many of the subsystems depend on the accuracy, precision and stability of the oscillator signals, also known as frequency stability. The following two examples illustrate the importance of frequency stability.

#### 1. Real-Time Clock Synchronization

For multiple OBCs it is important that the respective *Real-Time Clocks* (RTCs) are synchronized and increment at the same rate. If not, one OBC could schedule a task for another OBC at a time stamp that might have already elapsed according to its real-time clock. On an ADCS OBC, the need for an accurate RTC is even more important since some algorithms require the absolute time (SGP4) and a large time error will result in inaccurate ADCS control.

#### 2. Communication Synchronization

For communication peripherals a stable clock source on both the receiver and the transmitter is important. If the oscillator signals start to drift, the receiver might latch a data bit when the transmitter data is still changing its state. If the error is detected the data has to be retransmitted, or worse, the error is not detected and undefined data could cause a larger error somewhere else in the system.

These are two examples showing the importance for the use of stable oscillators. Unfortunately, the frequency stability of RCOs is sensitive to temperature, supply voltage and load variations, which are very difficult to control in the harsh space environment. The solution is to use *Crystal Oscillators* (XOs) which deliver better frequency stability even under varying conditions.

The OBC design includes the following two external crystal oscillators:

#### 1. High-Frequency Crystal Oscillator

A high-frequency, 32 MHz, oscillator is responsible for driving the core and all the high-frequency peripherals (ADC, EBI, I2C, etc). By using a *High-Frequency Crystal*

Oscillator (HFXO), the MCU core is also able to operate at its maximum frequency range of 32 MHz, which the internal RCO (maximum of 28 MHz) will not be capable of.

#### 2. Low-Frequency Crystal Oscillator

A low-frequency, 32.768 kHz, oscillator is responsible for all the low-frequency peripherals including the real-time clock. A *Low-Frequency Crystal Oscillator* (LFXO) will make it easier to keep the RTCs synchronized between the main OBC and ADCS OBC.

For a detailed view of MCU and how it interfaces with the rest of the ADCS OBC refer to Appendix B.1.

#### 2.3.2 EXTERNAL MEMORY SUBSYSTEM

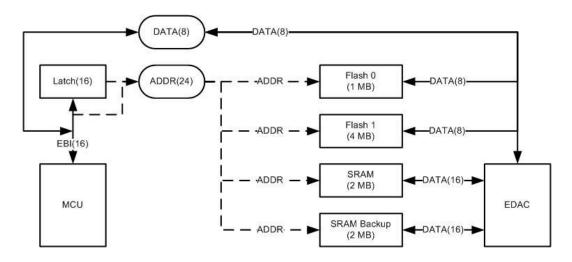

The ADCS OBC includes an external memory subsystem. The MCU internally includes 256 kB of flash and 16 kB of SRAM memory. For an ADCS OBC, this might not be enough memory to implement all the required features. The OBC might need to have multiple programs for the bootloader to choose from, depending on the situation (safe mode, full operation, etc.). Large program stacks (multiple kilobytes as confirmed by testing) are required due to the complex ADCS algorithms, models, large data types and various telemetry related data. To ensure all of these features can be implemented, an external memory subsystem is added on the OBC, which is shown diagrammatically in Figure 2.8.

Figure 2.8: External Memory System of ADCS OBC.

#### 2.3.2.1 MEMORY TYPES

Before the memory subsystem will be discussed in further detail, the differences between the SRAM and flash memory (the two main memory types used for most OBC designs) in terms

of performance and reliability will be looked at to understand the role they can fulfil and the challenges they will pose.

#### Flash

Flash memory is a non-volatile memory unit, in other words it retains its value even when not powered. It has very fast access speeds, but writing to flash memory is considerably slower than reading from it. Flash memory is also very resistant to radiation effects when being accessed, but it is susceptible to *Single Event Effects* (SEEs), such as SEU and SEL, when being programmed according to study done in [21]. Taking the above into consideration, flash memory is a very good storage candidate for program code. An MCU is programmed very seldom, therefore negating its weakness of slow programming time and SEEs. When continuously accessed during program execution it is very resistant to SEEs.

#### SRAM

Static Random Access Memory (SRAM) is a volatile memory unit. Unlike flash memory it retains its data only when powered. However, it has very fast read and write times which makes it an ideal candidate for storing program data which either rapidly changes their values or are merely temporarily allocated. Examples of these data types are variables used in the ADCS calculations, telemetry data temporarily stored before being transmitted to ground and sensor data which are periodically updated. Unfortunately SRAM is susceptible to radiation effects (SEEs) during both read and write operations [11]. To counteract the SEEs for this design an Error Detection and Correction (EDAC) module will be implemented for the SEUs and a robust power system will be implemented for the SELs.

#### 2.3.2.2 EXTERNAL MEMORY REGIONS

The MCU includes an *External Bus Interface* (EBI) with four chip select lines which are used to access four external memory modules, each with a specific function.

### 1. Flash 0 – Safe Mode

A flash memory module will be dedicated to storing a default safe mode operation program. This should be a simple program that will allow the satellite to make contact with the ground station, from where it will receive further commands. This should be the default program the ADCS OBC falls back on after a reset from an unresponsive state.

Because Flash 0 will only be storing one operating program, its capacity did not have to be as large as Flash 1 and was therefore chosen as one megabyte.

# **2.** Flash 1 – Multiple Operating Programs

An additional flash memory module will be used to store different programs which will execute after the safe mode program and the ground station have checked all the systems of the ADCS OBC. The reason for having multiple programs is that different programs are needed to handle different situations. Multiple programs can be used for reliability as well by storing the same program in three different memory locations as a form of triple mode redundancy. Extra programs can be uploaded from the ground station and stored in flash, either as corrections to existing programs or programs with different objectives. Because multiple programs will be stored on Flash 1, its capacity was chosen as four megabytes.

### 3. SRAM – Program Data

An SRAM memory module is used for program data by the MCU. It is much safer to let the MCU store important data in the external memory, because of the safety measures implemented (EDAC and separate controllable power lines). If an SEU would occur while using the internal SRAM it can go unnoticed and could cause a serious error. If a SEL should occur while using the internal SRAM it would force the entire system (ADCS OBC) to reset. Therefore the internal SRAM will be powered down and only the external SRAM will be used. An SEU in the external SRAM will be detected by the EDAC and a SEL will prompt the MCU to try and recover the SRAM (by power cycling) before resetting the system. Besides the added safety of using the external SRAM, the internal SRAM is limited to 16 kB of memory while external SRAM can store much more data (2 MB is used for this design).

# 4. SRAM – Backup

An extra SRAM memory module will be implemented as a backup due to the susceptibility of SRAM to radiation effects in space. This allows the MCU to reboot and use the extra SRAM module for the important data if a latchup should render the primary SRAM module unresponsive. This prolongs the time before it becomes necessary to use the internal SRAM of the MCU. This is important since the internal SRAM of the MCU has no form of EDAC and is therefore very susceptible to radiation effects. A SEL in the SRAM of the MCU could render the ADCS OBC useless.

#### 2.3.2.3 EXTERNAL MEMORY INTERFACE

The EFM32G MCU used for the ADCS OBC includes an EBI which uses 16 GPIO lines for address and data transmissions to external asynchronous devices. This allows for a maximum 8-bit address and 8-bit data single-cycle throughput. To increase the range of the EBI, a multiplexed read/write operation can be implemented utilizing a latch. This allows for two additional EBI configurations: 16-bit address/data and 24-bit address/8-bit data. This design uses the 24-bit address/8-bit data configuration to maximize the memory map for each chip select line and therefore the maximum size of each memory module. The control of the latch and access to these external memories are fully automated and discussed during the driver implementations of the EBI.

#### 2.3.2.4 ERROR DETECTION AND CORRECTION

An *Error Detection and Correction* (EDAC) subsystem is implemented to compensate for the susceptibility of SRAM to *Single Event Upsets* (SEUs) caused by the increased radiation level in space. The EDAC is very important since most of the data (not code) for the ADCS OBC is stored in SRAM and an undetected SEU (corrupt data) can cause undesired effects in the operation of the ADCS OBC.

Various forms of EDAC exist that can be implemented on an embedded system.

#### Software Based

A software-based EDAC system implements all the EDAC code within the MCU in the form of a driver between the program and memory. This removes the autonomous usage of the data stack by the MCU, which presents an extra overhead every time the SRAM is accessed for data. This is, however, very difficult to implement.

#### • Hardware Based

Some manufacturers offer hardware implementations for flow-through EDAC systems, like the Atmel EDAC (29C516E [22]). These units are located between the MCU and SRAM on the data bus and work fast enough to enable them to encode and decode the data during a read or write cycle. However, they are usually expensive and inflexible which forces the memory design around these units.

#### • FPGA

The FPGA-based EDAC system follows a hardware-based approach, but can be tailored to suit the requirements of a specific embedded design. A flow-through EDAC implementation can be designed that does not interfere with memory access. The FPGA

can also be used to implement other custom controllers needed on the OBC, such as an extra I2C controller, or port expander.

From the above descriptions, the FPGA-based EDAC system is the method best suited for this ADCS OBC design, due to its speed, flexibility and customization options. The ESL has experience in using FPGA-based EDAC systems in on-board satellite OBCs [23][24], which provided the necessary background and expertise to develop one for this project.

The EDAC system is implemented on an Igloo Nano (AGL030) FPGA from Actel [25]. This FPGA is designed for very low-power applications (efficiency) and the AGL030 version has no embedded SRAM which makes it less susceptible to radiation effects, ensuring reliability. The FPGA is also used on the CubeSense board design by the ESL [26].

#### 2.3.2.5 SRAM BUS ISOLATION

Figure 2.9 shows the design for isolating the SRAM modules from the data and address bus. When an SRAM has been damaged due to a latchup and its power supply is turned off, the module can still draw current via the address/data bus lines and even affect the data on the bus. This happens because no supply current is available to drive the input/output pins of the SRAM module into high impedance. It is therefore important that the system is able to isolate the SRAM module completely from the address/data bus if it is powered down. This is achieved in this design by using bus switches which can be toggled by the MCU to either connect the SRAM module to the bus, or isolate it, by driving the ports to high impedance.

Figure 2.9: SRAM Isolation Design Diagram.

### 2.3.2.6 SD CARD STORAGE

The memory subsystem further includes a 2 GB microSD storage card. The SD storage is a non-volatile memory based on NAND flash technology and has exceptional capacity. The MCU uses the SPI interface to communicate with the microSD card. The SD storage offers

another form of long-term storage that could be used to log various telemetry data to be requested by the ground station at a later time. At the time of conducting this research, microSD cards do not have any flight heritage in space and is added as an experiment.

For a detailed view of Memory Subsystem and how it interfaces with the rest of the ADCS OBC refer to Appendix B.2.

### 2.3.3 POWER SUBSYSTEM

The power subsystem is responsible for providing all the components on the OBC with their required supply voltage and regulating the current during operation. The main *Electronic Power System* (EPS) supplies to all the subsystems a 5 V and 3.3 V power line which can be used to power most of the components on the ADCS OBC. However, a separate power system was specifically designed on the ADCS OBC to power the components. This improves reliability in two key areas, namely stability and control.

# 1. Stability

When a power line is under heavy load (i.e. drawing heavy current) the supply voltage can drop due to undesired series resistance in the power line. This voltage drop can cause unwanted behaviour and even damage sensitive components. This can be prevented by regulating the required supply lines (3.3 V and 1.5 V) down from the 5 V power line supplied by the EPS. The output voltage will be very resistant to input voltage fluctuations as long as the input voltage drop remains above the specified dropout voltage of the regulator. The end result is a more stable supply voltage.

#### 2. Control

The advantage of designing a separate power system is that it supplies a means of control. The OBC can monitor the power system and detect if a too large current is being drawn or if a supply voltage is dropping too low. The OBC can then respond by power cycling the problematic power line to attempt to fix the latchup, or even switch it off completely. The OBC will then lose those components, but not the entire system.

Figure 2.10 shows the design of the power system in diagrammatic form, which will be broken down and discussed further below.

Figure 2.10: OBC Power System Block Diagram.

# 2.3.3.1 POWER SUPPLY LINES

A 5 V power line from the EPS is split into five power lines which are used in the ADCS OBC. These power lines are then used to power the various components.

# • General 5 V

This power line is the regulated 5 V power line supplied by the EPS. It is used to power the 5 V components on the OBC.

### • FPGA 1.5 V

This power line is regulated down from the 5 V power line supplied by the EPS. It is used to power the FPGA, which is the only component in the OBC that operates on a 1.5 V supply voltage.

# • General 3.3 V

This power line is regulated down from the 5 V power line supplied by the EPS. It is used to power the MCU and all other 3.3 V components, except the SRAM modules, which have their own power lines.

#### • SRAM 3.3 V

Each SRAM module has its own power line. These power lines are regulated down from the 5 V power line supplied by the EPS. They power only their respective SRAM modules. The reason for this is that the power lines can individually be power cycled or disabled if a latchup should occur.

### 2.3.3.2 REGULATORS

The 3.3 V and 1.5 V lines are regulated using low-dropout linear regulators. The *Texas Instruments* (TI) TPS76733 [27] and TPS73215 [28] were used in this design for the 3.3 V and 1.5 V lines respectively. Both regulators offer exceptional voltage regulation at 0.01% change in output voltage over change in input voltage.

The 3.3 V and 1.5 V regulators have a current limit of 1 A and 250 mA respectively. Both of these limits are far higher than the required current according to preliminary power calculations. In the final version of the OBC, a regulator with a current limit closer to the nominal operating current can be selected. Therefore, if one of the components draws excessive amounts of current the supply voltage will drop and the brown-out-reset of the MCU will respond by resetting the OBC.

#### 2.3.3.3 LOAD SWITCHES

Since SRAMs are the components on the OBC most susceptible to latchups, being able to switch the power to them on and off adds another layer of reliability. Power switches can be implemented with a simple PMOS circuit. However, a load switch from Fairchild Semiconductors (FPF2124 [29]) was chosen due to its current-limiting ability. For this design the current limit was configured to 200 mA, which is the rated latchup current for the Cypress Semiconductor SRAM (CY62167DV30 [30]) modules used in this design. When this current limit is reached and maintained for 10 ms the FPF2124 switches off the power line until it is toggled from an external controller (the MCU in the case of this design).

For a detailed view of Power Subsystem and how it interfaces with the rest of the ADCS OBC refer to Appendix B.5.

# 2.3.4 MONITORING SUBSYSTEM

Due to the harsh space environment, mentioned in section 1.4, the ability to continuously monitor the state of a system is very important. This allows the OBC to detect any abnormalities in the system which might be caused by faulty components or operations. These errors can either be fixed or even isolated before any serious damage is caused to the system.

The monitoring process should be sensitive and responsive: sensitive, in order for it to pick up the slightest change that could be a symptom of a larger problem and responsive, to be able to react quickly when a problem is detected.

As mentioned previously, the most common problem on an OBC is the susceptibility of SRAM to latchups due to radiation. This causes the SRAM to stop functioning as well as draw an excessive amount of current. This current, if not quickly dealt with, can damage the SRAM as well as other components on the OBC. A separate power line, with a current sensor and a load switch, was therefore implemented to try and isolate the SRAM modules in case of a latchup.

Figure 2.10, which illustrates the power system design, also shows how the monitoring system is implemented. The supply current and voltages are monitored which, from a hardware point of view, is the easiest way to detect any failures or malfunctions. The monitoring channels are as follows:

### • Voltage Sensors

The 3.3 V line and 1.5 V line is fed through a simple voltage divider circuit to the ADC unit of the MCU. The voltage measurements will be used for telemetry purposes. The MCU can also be configured to reset if the supply voltage drops below a certain threshold.

#### • Current Sensors

The current from the general 3.3 V power line, 1.5 V FPGA power line and both SRAM power lines are monitored by current shunt sensors. These currents are sampled as voltages over output resistors and fed through an op-amp buffer to the ADC unit. This implementation of a current sensor is shown in Figure 2.11 and discussed in more detail in Appendix A.2.

# Temperature

The MCU has an internal temperature sensor which will be used by the monitoring subsystem. The temperature measurements will be used mainly for telemetry purposes to assess the thermal situation in the ADCS unit and CubeSat.

Figure 2.11: Current Sensor Implementation. [28]

All the above mentioned monitoring channels are sampled by the ADC unit of the MCU. The data gathered is stored for telemetry purposes, but could also be processed and allow the MCU to react autonomously to expected problems. Two examples used in this design are power cycling SRAM modules after a latchup and brown-out reset for the MCU.

# 2.3.5 COMMUNICATION SUBSYSTEM

The communication subsystem is responsible for allowing the ADCS to communicate with other subsystems on the CubeSat. These typically include the main OBC, sensors and actuators. The communication subsystem for this design is very simple from a hardware point of view because all the required communication peripherals are included with the EFM32G MCU. The following communication interfaces were implemented.

### 2.3.5.1 UART

The *Universal Asynchronous Receiver/Transmitter* (UART) is a simple point-to-point communication interface. Data is serially transmitted on one channel and received on another. Transmission is asynchronous in the sense that it can start at any time, but both transmitter and receiver should be set up with the same speed for operation.

In this design, the UART interface will be used mainly for debugging purposes. It can also be configured to program the MCU or merely used as a simple communication method for outputting data during the development of drivers and control modes.

# 2.3.5.2 I2C

The *Inter-Integrated Circuit* (I2C) is a high-speed bus-based communication interface. A master can access one of many slaves by using an address identifier to notify the correct slave of an incoming transmission. Through the use of arbitration, clock synchronization and

stretching, it is possible to allow for multiple bus masters if required. The I2C uses two IO lines for communication: a communal clock signal and a data bus line. The features of the MCU I2C controller is explained in more detail in [17].

In this design, the I2C bus is used as the communal bus where telecommands and telemetry data are transmitted to and from the main OBC to the rest of the CubeSat subsystems. In order for the ADCS OBC to communicate with its own subsystems (sensors and actuators) the I2C can either be shared, via time slots or arbitration, or a separate I2C bus can be used between the ADCS subsystems, which include the ADCS OBC, sensors and actuators.

#### 2.3.5.3 SPI

The *Serial Peripheral Interface* (SPI) is a high-speed point-to-point communication interface. By synchronizing the communication between the transmitter and the receiver with a dedicated clock signal, transfer speed is only limited by the clock signal generated by the MCU. The SPI uses four IO lines for communication: a clock signal, a chip select signal, a transmit line and a receive line.

In this design, one SPI channel is used to communicate with the microSD card. Another could also be used for point-to-point access to a subsystem where large amounts of data transfer needs to take place. An example would be the ADCS OBC receiving an image file taken by a camera onboard the sun sensor or horizon sensor for telemetry or debugging purposes. Transmitting this large file over the communal shared bus (I2C in the case of most CubeSats) would unnecessarily occupy it for a long period of time and possibly prevent important communication to take place between the other satellite subsystems.

# 3 SOFTWARE DEVELOPMENT

The development of competent software is just as, if not more, important than the hardware design of an OBC. Software is responsible for instructing the different hardware components how and when to execute. The way in which these instructions are ordered (by means of a program) has to allow the system to achieve its intended purpose, which in the case of this project is the attitude and determination control of a CubeSat. Software programs are very complex and there are usually multiple implementations that achieve the same objective. It was therefore important that the software implementations for this project take into account the design requirements (performance, efficiency and reliability), because they apply to software as well as hardware.

This chapter starts from a low-level perspective by looking at the hardware abstraction layer supplied by ARM for its Cortex-M range architecture. A quick summary will then be given of all the drivers that were developed in order to utilize the hardware that was designed in the previous chapter. After that a section will be dedicated to the development of the error detection and correction algorithm and code that was implemented on the FPGA for the SRAM. Lastly, higher-level software will be discussed by looking at the operation of the bootloader and operating system with its control loop and background tasks.

### 3.1 HARDWARE ABSTRACTION LAYER

ARM uses a *Hardware Abstraction Layer* (HAL) called the *Cortex Microcontroller Software Interface Standard* (CMSIS) [13]. A HAL is low-level software that supplies a simple interface to access hardware features from various vendors or manufacturers. In the case of ARM, this standard is called the CMSIS and the interface allows access to the processor and peripherals on all microcontrollers based on the ARM Cortex-M architecture. Figure 3.1 shows the structure of the CMSIS and how it fits between user-developed code and Cortex-M processor-based MCUs.

The advantage of using a HAL is that it is backed by a large software community. Previously there were separate communities for each ARM-based microcontroller vendor. However, the Cortex-M community is now vendor independent, because all the software is based on the CMSIS. This greatly improves the ease with which code can be developed for a Cortex-M-based microcontroller due to the amount of code available and the ease at which it can be re-used. The EFM32G, the MCU used for this design, is a Cortex-M3-based MCU and its software is also based on the ARM CMSIS. Even though the EFM32G was released in

2009, a large pool of application code is already available due to the ease of developing code for the Cortex-M based MCUs, which can be found on their website [31].

Figure 3.1: ARM CMSIS Structure. [9]

# 3.2 Drivers

A device driver is a piece of code that allows the operating system or user application to set up, access and utilize a specific hardware device and/or peripheral. Drivers are very useful since they allow an application to access the features of the OBC without any low-level knowledge such as registers, protocols and timings. The use of the CMSIS has greatly increased the ease with which drivers for the Cortex-M-based MCUs are developed, because of the simple and standard interface to low-level structures such as registers and interrupts.