# UCC Library and UCC researchers have made this item openly available. Please let us know how this has helped you. Thanks!

| Title                | Monolayer doping of bulk and thin body group IV semiconductors                                                            |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| Author(s)            | Kennedy, Noel                                                                                                             |

| Publication date     | 2020-07                                                                                                                   |

| Original citation    | Kennedy, M. N. 2020. Monolayer doping of bulk and thin body group IV semiconductors. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                           |

| Rights               | © 2020, Michael Noel Kennedy. https://creativecommons.org/licenses/by-nc-nd/4.0/                                          |

| Item downloaded from | http://hdl.handle.net/10468/10941                                                                                         |

Downloaded on 2021-11-27T11:16:27Z

Michael Noel Kennedy, B.Sc (Hons)

**School of Chemistry**

University College Cork, Ireland.

# Monolayer doping of bulk and thin body Group IV semiconductors

Supervisors:

Dr. Brenda Long

Dr. Ray Duffy

Prof. Justin D. Holmes

Head of School: Dr. Humphrey Moynihan

**July 2020**

Presented for the degree of Doctor of Philosophy to the National University of Ireland

#### TABLE OF CONTENTS

| Declarationv                                                         |       |  |  |

|----------------------------------------------------------------------|-------|--|--|

| ABSTRACT                                                             |       |  |  |

| List of commonly used Abbreviations                                  | xiii  |  |  |

| Acknowledgments                                                      | xvi   |  |  |

| Dedication                                                           | xviii |  |  |

| CHAPTER 1                                                            |       |  |  |

| Introduction                                                         |       |  |  |

| 1.1 Abstract                                                         | 19    |  |  |

| 1.2 General concepts                                                 | 20    |  |  |

| 1.2.1 What is doping?                                                | 20    |  |  |

| 1.2.2 Transistor development                                         | 21    |  |  |

| 1.3 State of the art in semiconductor doping                         | 24    |  |  |

| 1.3.1 Beam-line ion implantation                                     | 24    |  |  |

| 1.3.2 Plasma doping                                                  | 27    |  |  |

| 1.3.3 <i>In-situ</i> chemical vapour deposition doping               | 29    |  |  |

| 1.3.4 Spin-on doping                                                 | 30    |  |  |

| 1.3.5 ALD and Gas phase MOVPE                                        | 32    |  |  |

| 1.4. Monolayer doping                                                | 34    |  |  |

| 1.4.1 Background                                                     | 34    |  |  |

| 1.4.2 MLD development                                                | 37    |  |  |

| 1.4.2.1 Phosphorus and Boron MLD                                     | 37    |  |  |

| 1.4.2.2 Application of MLD to alternative dopant and substrate types | 46    |  |  |

| 1.4.3 Limitations of MLD                                             | 52    |  |  |

| 1.5. References                                                      | 54    |  |  |

| CHAPTER 2                                                            |       |  |  |

| Characterization and experimental method                             |       |  |  |

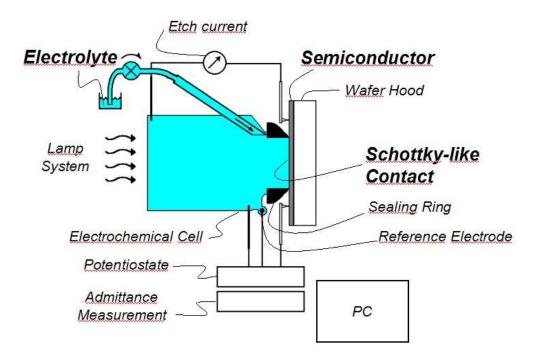

| 2.1 Electrochemical capacitance-voltage profiling                    | 67    |  |  |

| 2.2 Atomic force microscopy                                          | 71    |  |  |

| 2.3 X-ray photoelectron spectroscopy                                 | 72    |  |  |

| 2.4 Secondary ion mass spectrometry                                  |       |  |  |

| 2.5 Electron microscopy                                              | 74    |  |  |

| 2.6 Hall-effect measurements                                         |       |  |  |

| .7 Sheet resistance measurement                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------|-----|

| 2.8 Water contact angle (WCA) measurements                                                                             | 76  |

| 2.8 General MLD procedure                                                                                              | 76  |

| 2.9 References                                                                                                         | 77  |

|                                                                                                                        |     |

| CHAPTER 3                                                                                                              |     |

| Monolayer doping of silicon: development of phosphorus doping on plans<br>silicon-on-insulator and nanowire substrates | ar, |

| 3.1 Abstract                                                                                                           | 81  |

| 3.2 Introduction                                                                                                       | 82  |

| 3.3 Experimental methods                                                                                               | 85  |

| 3.3.1 General procedure for Si functionalization with ADP                                                              | 85  |

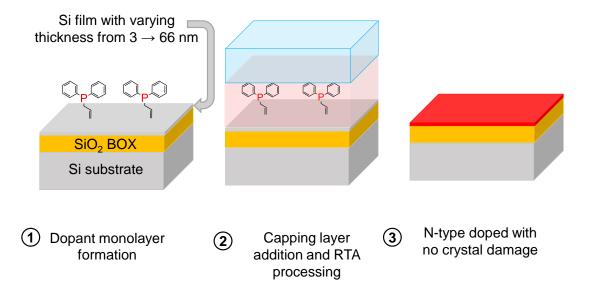

| 3.3.2 SOI fabrication process                                                                                          | 86  |

| 3.3.3 Nanowire fabrication process                                                                                     | 86  |

| 3.3.4 Characterization methods                                                                                         |     |

| 3.4 Results and Discussion                                                                                             |     |

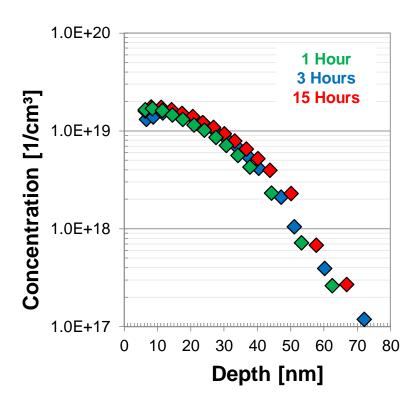

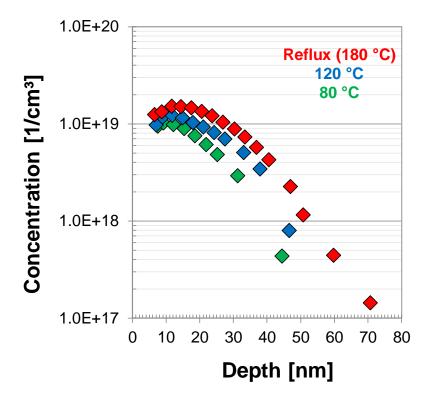

| 3.4.1 Optimization of process conditions on blanket silicon                                                            |     |

| 3.4.1.1 Optimization of hydrosilylation reaction conditions                                                            |     |

| 3.4.1.2 Optimization of annealing conditions                                                                           |     |

| 3.4.1.3 Necessity of capping layer?                                                                                    |     |

| 3.4.2 Application to SOI                                                                                               |     |

| 3.4.2.1 Material Characterization                                                                                      |     |

| 3.4.2.1.1 AFM analysis                                                                                                 |     |

|                                                                                                                        |     |

| 3.4.2.1.3 Electrical characterisation of P-MLD doped SOI                                                               |     |

| 3.4.2.1.4 XPS characterisation.                                                                                        | 81  |

| 3.4.2.1.5 Angle resolved XPS characterisation                                                                          | 83  |

| 3.4.2.1.6 Interface trapping of dopants analysed with SIMS                                                             | 84  |

| 3.4.2.1.7 Further work on SOI.                                                                                         | 85  |

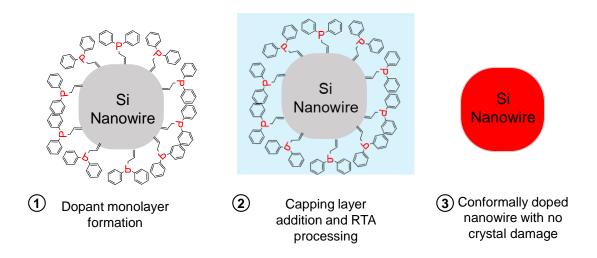

| 3.4.3 Application to Nanowires                                                                                         | 111 |

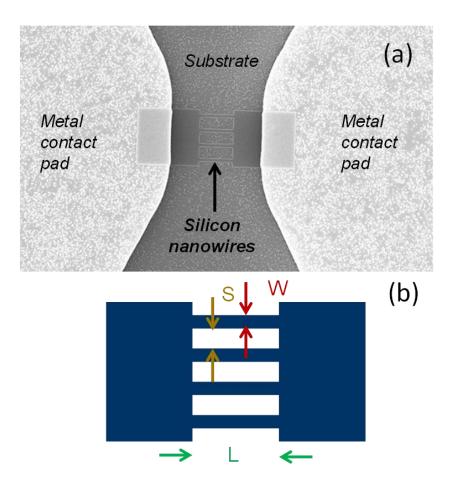

| 3.4.3.1 Material characterisation of test structures                                                                   | 111 |

| 3.4.3.1.1 SEM                                                                                                          | 89  |

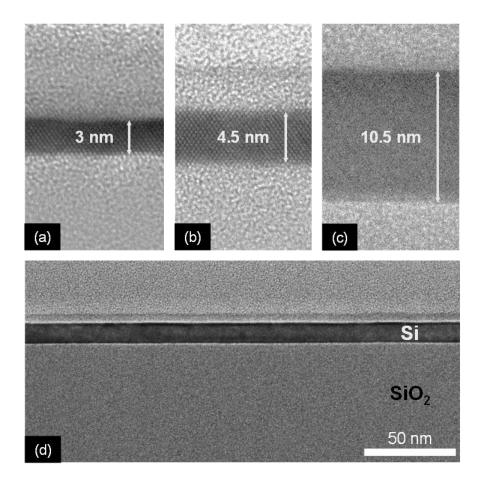

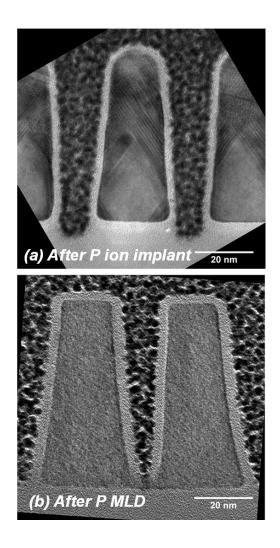

| 3.4.3.1.2 XTEM                                                                                                         | 90  |

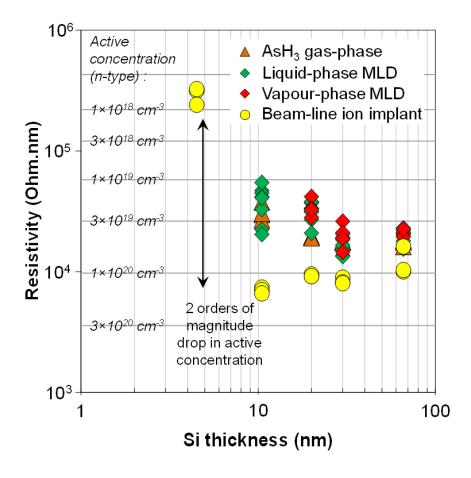

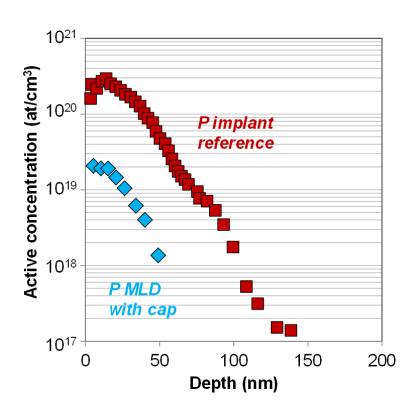

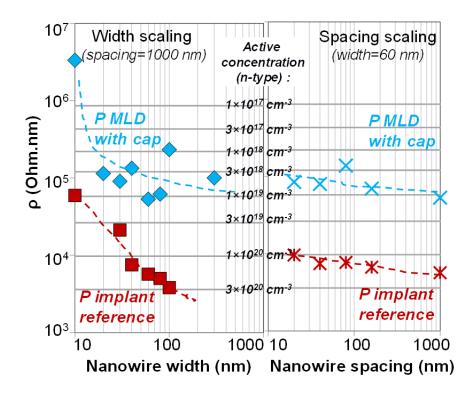

| 3.4.3.1.3 Carrier profiling                                                                                            | 91  |

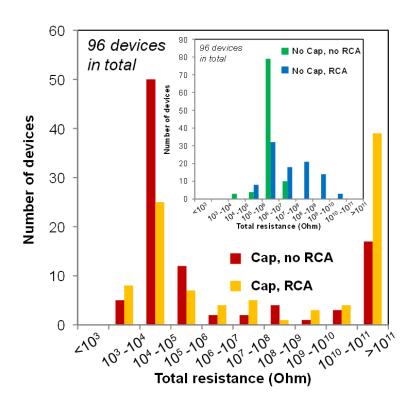

| 3.4.3.1.4 Electrical characterisation of nanowire test structures                                                      | 92  |

| 3.5 Conclusions and Outlook                                                                                   |         |

|---------------------------------------------------------------------------------------------------------------|---------|

| 3.6 References                                                                                                | 119     |

| CHAPTER 4                                                                                                     |         |

| MLD on silicon: Pushing the active carrier concentration limit                                                |         |

| 4.1 Abstract                                                                                                  | 124     |

| 4.2 Introduction                                                                                              | 126     |

| 4.3 Experimental methods                                                                                      | 129     |

| 4.3.1 ADP functionalization with nitride capping method                                                       |         |

| 4.3.2 General procedure for click chemistry strategy                                                          |         |

| 4.4 Results and discussion                                                                                    |         |

| 4.4.1 Phosphorus doped silicon by MLD with silicon nitride                                                    |         |

| 4.4.1.1 Outline                                                                                               | 131     |

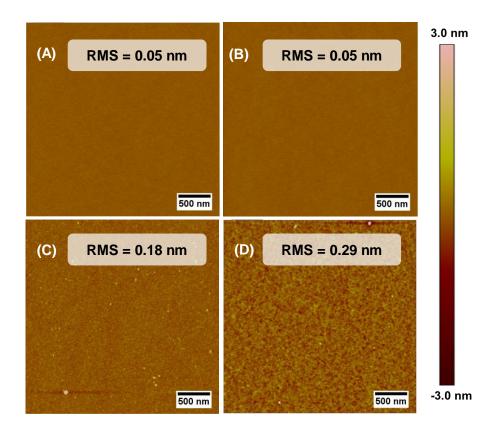

| 4.4.1.2 AFM analysis of samples processed with sputtered Si <sub>3</sub> N <sub>4</sub>                       | 132     |

| 4.4.1.3 Carrier profiling of samples capped with sputtered Si <sub>3</sub> N <sub>4</sub> vs SiO <sub>2</sub> | 134     |

| 4.4.1.4 Spike annealing using RTA                                                                             | 136     |

| 4.4.2 Development of As-MLD with arsanilic acid                                                               | 139     |

| 4.4.2.1 Reaction of arsanilic acid with Si through click chemistry                                            | 139     |

| 4.5 Conclusions and outlook                                                                                   | 152     |

| 4.6 References                                                                                                | 153     |

| CHAPTER 5                                                                                                     |         |

| Monolayer doping of germanium with arsenic: A new chemical route to optimal dopant activation                 | achieve |

| 5.1 Abstract                                                                                                  | 161     |

| 5.2 Introduction                                                                                              | 162     |

| 5.3 Experimental                                                                                              |         |

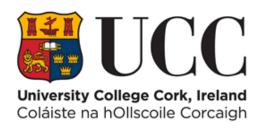

| 5.3.1 Functionalisation process for As-MLD on Ge                                                              | 166     |

| 5.3.2 Characterisation methods                                                                                | 167     |

| 5.3.3 Density functional theory modelling of As-acid binding                                                  | 167     |

| 5.4 Results and Discussion                                                                                    | 169     |

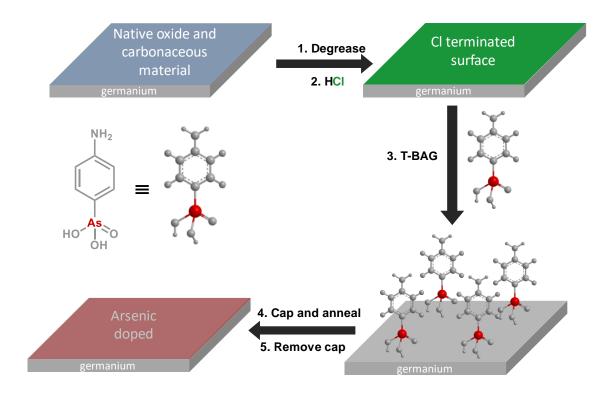

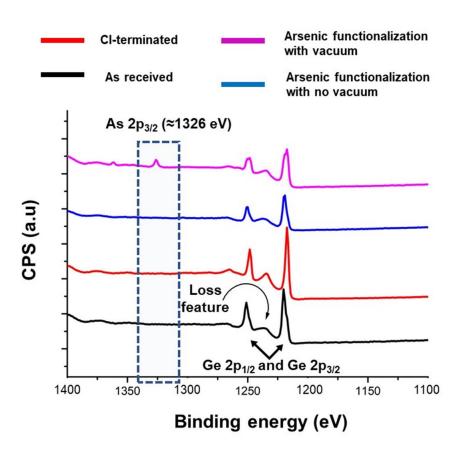

| 5.4.1 Surface characterisation of monolayer formation                                                         | 169     |

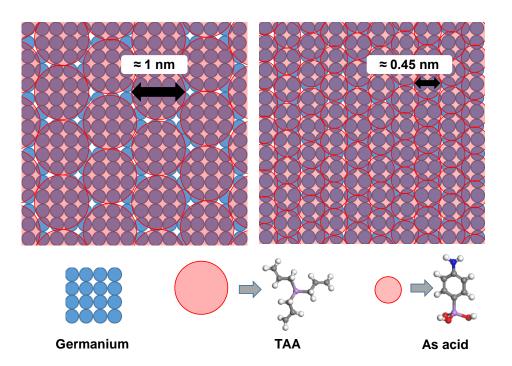

| 5.4.2 Theoretical calculations of molecule binding                                                            | 175     |

| 5.4.3 Material characterisation after MLD                                                                     | 178     |

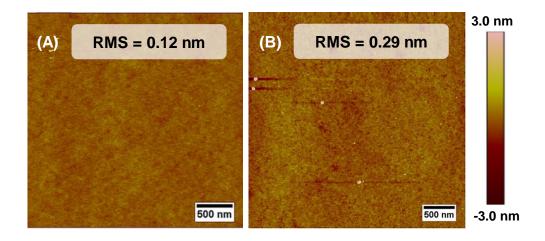

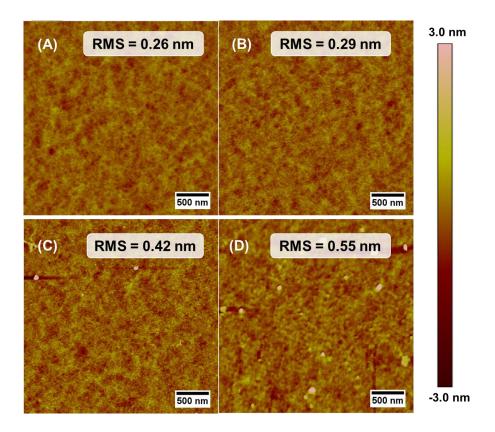

| 5.4.3.1 AFM analysis of surface topology                                                                      | 178     |

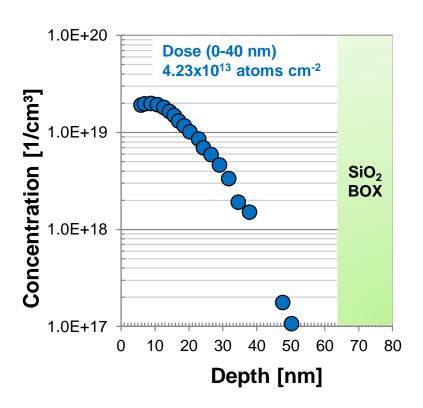

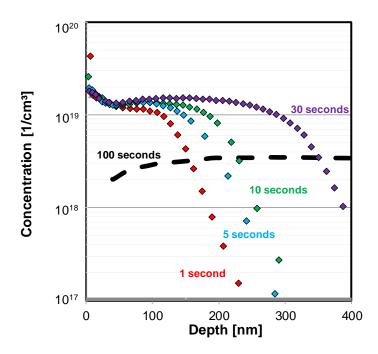

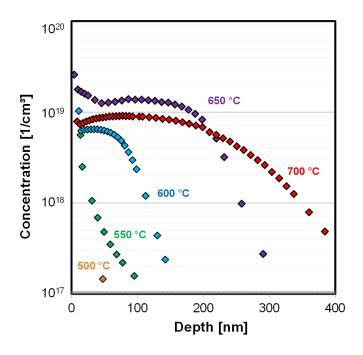

| 5.4.3.2 Dopant profiling and sheet resistance measurements                                                    | 179     |

| 5.4.3.3 Theoretical dose estimation and comparison                                                      |     |                             |

|---------------------------------------------------------------------------------------------------------|-----|-----------------------------|

|                                                                                                         |     | 5.5 Conclusions and outlook |

| 5.6 References                                                                                          |     |                             |

| CHAPTER 6                                                                                               |     |                             |

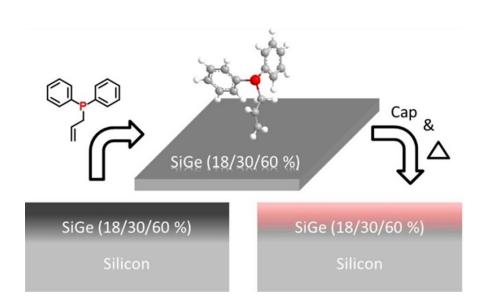

| MLD on silicon-germanium alloys: A balancing act between phosphorus incorporation and strain relaxation |     |                             |

| 6.1 Abstract                                                                                            | 199 |                             |

| 6.2 Introduction                                                                                        | 200 |                             |

| 6.3 Experimental methods                                                                                | 203 |                             |

| 6.3.1 SiGe wafer growth and surface functionalisation method                                            | 203 |                             |

| 6.3.2 Characterisation methods                                                                          | 204 |                             |

| 6.4 Results and Discussion                                                                              | 204 |                             |

| 6.4.1 Material characterisation of SiGe for MLD processing                                              | 204 |                             |

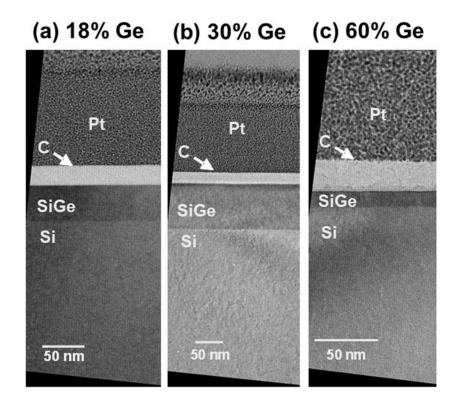

| 6.4.1.1 TEM analysis of starting SiGe substrates                                                        | 204 |                             |

| 6.4.1.2 Determination of SiGe content with XPS analysis                                                 | 205 |                             |

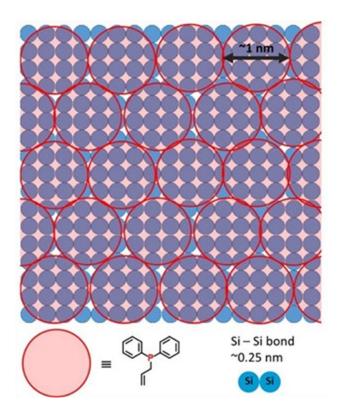

| 6.4.1.3 Packing density calculation of ADP on SiGe                                                      | 207 |                             |

| 6.4.1.4 Characterisation of SiGe after high temperature RTA                                             | 208 |                             |

| 6.4.2 Application of MLD to SiGe                                                                        | 210 |                             |

| 6.4.2.1 AFM analysis of surface topology                                                                | 210 |                             |

| 6.4.2.2 TEM analysis of crystal quality                                                                 | 212 |                             |

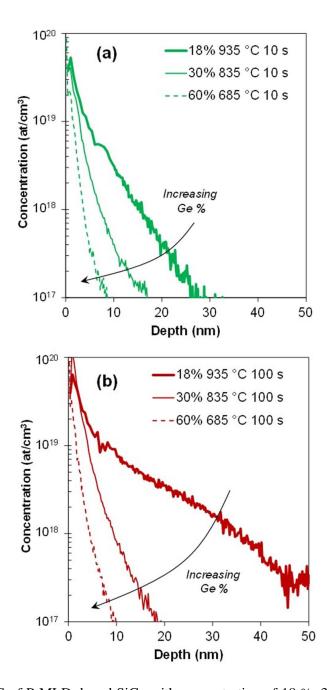

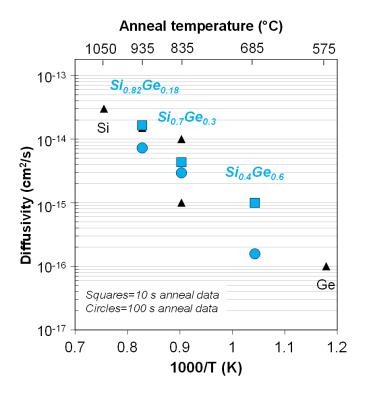

| 6.4.2.3 Dopant profiling with SIMS                                                                      | 214 |                             |

| 6.4.2.4 Analysis of diffusion co-efficient and discussion                                               | 215 |                             |

| 6.5 Conclusions and Outlook                                                                             | 219 |                             |

| 6.5 References                                                                                          | 220 |                             |

| CHAPTER 7                                                                                               |     |                             |

| Conclusions and Future Perspectives                                                                     |     |                             |

| 7.1 Conclusions                                                                                         | 229 |                             |

| 7.2 Future Perspectives                                                                                 | 233 |                             |

| CHAPTER 8                                                                                               |     |                             |

| Appendix                                                                                                |     |                             |

| 8.1 List of Publications                                                                                | 236 |                             |

| 8.1.1 Work related to this thesis                                                                       | 236 |                             |

|                                                                                                         |     |                             |

| 8.1.2 Other co-authored publications and conference papers | 238 |

|------------------------------------------------------------|-----|

| 8.1.3 Conference presentations                             | 239 |

| 8.1.4 Internship undertaken                                | 240 |

# **Declaration**

This is to certify that this is my own work and has not been submitted for another degree at University College Cork or elsewhere. All references are acknowledged in the contents of the text. I have read and understood the terms and conditions outlined by University College Cork with regards to plagiarism.

Michael Noel Kennedy

## **ABSTRACT**

The turn of the new year from 2019-2020 has brought us into a new decade with an unforeseen worldwide halt to what was previously considered "normal" life, due to a virus (coronavirus-19) with dimensions measured by scanning electron microscopy (SEM) to be in the nanometre range. This has emphasized the importance for the general public of acknowledging particles and materials in this nanometre range which cannot be seen without electron microscopy. Some of the technology being used to fight these viruses, such as ventilators, operate using electronics which contain semiconductor materials. Since the mid 1900 s the size of these electronics has decreased while doubling their quantity of transistors in line with Moore's law. This has allowed for increased performance with lower power consumption. Scaling of metal-oxide-semiconductor field effect transistors (MOSFETs) has progressed from the original micrometre range to current sub-10 nm dimensions, while also moving from planar to 3-dimensional (3-D) architectures. However, increasing difficulty has been found with these new and reduced material dimensions. All fabrication processes are stressed, but doping has particularly found limitations in this region. High concentrations of dopant atoms are required at increasingly shallow depths, while maintaining the crystalline integrity of the planar or 3-D doped substrate. Traditional methods of introducing these dopant atoms, such as ion implantation, have found difficulty with damage production and conformality on state-of-the-art applications. Monolayer doping, which is a method of semiconductor doping through chemical functionalisation of the target substrate with the required dopant-containing molecules, has shown promise as an alternative method for this state-of-the-art doping.

The aim of this thesis is to study the potential of monolayer doping for application to materials used in current and future transistor devices.

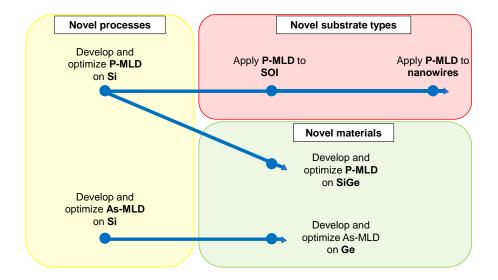

Chapter 1 acts as an introduction to the work which is discussed in this thesis. A brief history of transistor development is outlined to give context to the main application where MLD has been proposed as a solution. The use of transistors in every day electronic devices and their continued development towards smaller sizes and improved power and performance has led to the requirement for alternative doping methodologies. The traditional technique for doping, beam-line implantation is discussed with its issues on current device sizes and architectures outlined. Alternative doping methods such as plasma doping, and in-situ doping are also discussed with both the positives and negatives associated with each technique outlined. MLD has been proposed as a novel alternative with potential to conformally dope these nanostructures with no crystalline damage. The advantages of MLD are outlined with a detailed discussion on how the technique has developed since its inception in 2008. A number of limitations do remain when considering MLD as a viable industry alternative to more traditional doping techniques. These limitations are discussed and are addressed by the work later described in chapters 3-6. A number of fundamental properties associated with diffusion doping are also described which are necessary for a complete understanding of the work described in this text.

Chapter 2 describes the experimental methods involved with each work described in the following work chapters. Various functionalization methods used with each substrate type and dopant type are outlined in detail. A brief and general description of the MLD surface functionalisation process is also provided.

Chapter 3 outlines extensive testing of phosphorus MLD processing which was first optimized on blanket silicon wafers and then transferred to SOI and nanowire test structures. Characterization of P-MLD doped blanket wafers with SiO<sub>2</sub> capping with ECV and SIMS demonstrated that P diffusion into the silicon lattice was being inhibited and not following the expected limited source diffusion model. It was theorized that surface oxidation which results from the functionalization process is leading to this inhibited diffusion. Application of P-MLD to SOI both represented the first of this kind in literature and acted as a confirmation of previous blanket results. Electrical results on scaled SOI down to 4 nm film thickness, and nanowires demonstrated that MLD is capable of doping these advanced applications but requires increased carrier concentrations to compete with beam-line implantation.

Chapter 4 both provides solutions to some of the issues seen in the previous chapter and demonstrates a novel approach to doping Si with As. P-MLD processing which has been developed and extensively examined in the previous chapter to show an activation limit at 2 ×10<sup>19</sup> cm<sup>-3</sup> has been tested with silicon nitride capping and demonstrates increased activation levels approaching the target 1×10<sup>20</sup> cm<sup>-3</sup>. Results have been demonstrated with ECV and validation of total chemical concentrations via SIMS. Previous work on the use of nitride capping in the field of ion implantation has demonstrated that it has better "blocking" properties to prevent dopant out-diffusion, than oxide caps. It is theorized that this effect also leads to improved dopant incorporation from P-MLD. Application of this processing to nanostructures did not prove successful due to issues with cap addition and removal processes. These results are also outlined. Further work was carried out on planar Si to develop an As-MLD

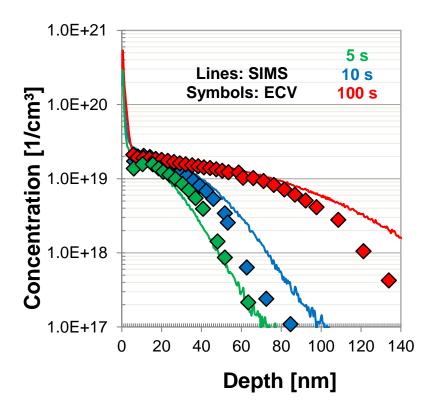

process using a relatively safe As precursor of Arsanillic acid with tethering by aggregation methodology. A successful approach was determined to be through click chemistry with activation levels of  $\approx 3 \times 10^{19}$  cm<sup>-3</sup> demonstrated with a  $5\times 10^{18}$  cm<sup>-3</sup> junction depth of 19 nm. This also represents an order of magnitude increase on previous arsenic doping of Si with MLD through click chemistry (previous high =  $2 \times 10^{18}$  cm<sup>-3</sup>). Control of active dose, max carrier concentration and junction depth has been shown through varied annealing parameters.

Chapter 5 discusses the application of a new functionalization method with As-acid to Ge substrates. Ge substrates are notoriously difficult to work with due to their unstable oxide layer. In this study a Cl-terminated Ge surface was utilized as a building block for functionalization with As-acid through a nucleophilic substitution reaction. XPS analysis showed that annealing in a vacuum environment was necessary for attachment of the As-acid molecule with monolayer formation assessed through reoxidation of the Ge 3d signal. DFT calculations determined that binding of the Asacid molecule to Ge via a di-dentate configuration was preferential compared to the mono-dentate and tri-dentate forms. Surface analysis with AFM during the MLD process demonstrated good surface quality with a minimal impact on roughness values. Active carrier concentrations from this As-MLD of  $\approx 2 \times 10^{19}$  cm<sup>-3</sup> represent the highest seen for As-MLD on Ge (2x previous record values), and are what has been recorded in literature as the electrically active limit through conventional RTA. Active carrier concentration values were validated through sheet resistance measurements. This study also demonstrated that incorporated dopant dose can be controlled in MLD via molecule size with comparison made between As-acid and the previously used triallylarsine showing that the smaller As-acid molecule is capable of packing more dose on the Ge surface.

Chapter 6 outlines the application of P-MLD to SiGe, which is another potential channel material for use in future advance logic technology nodes. Thin films of strained SiGe on Si were epitaxially grown with varied concentrations of Ge (18, 30 and 60 %). Applying high temperature thermal treatments to SiGe has the potential to develop defects as a result of strain relaxation. A detailed material characterization SiGe film properties using AFM and XTEM was carried out to determine what anneal temperatures each SiGe content could sustain during MLD. XPS and angle resolved XPS were used to identify the actual bulk and surface Ge compositions present in each SiGe sample in order to tailor reaction conditions for chemical functionalization. Dopant profiling of the resulting MLD doped SiGe was carried out with SIMS and determined that phosphorus incorporation decreases for increasing mole fraction of Ge, when the RTA temperature is a fixed amount below the melting temperature of each alloy.

Chapter 7 presents the conclusions gained from the work in this thesis and also expands on what future possibilities there are for MLD on an academic research and industrial application setting.

# List of commonly used Abbreviations

2-D - two dimensional

3-D - three dimensional

3,4-DCB -3,4 Dichlorobut-1-ene

ABAPE – Allylboronic acid pinacol ester

ABF – Ammonium hydrogen difluoride

ADP - Allyldiphenylphosphine

AFM – Atomic force microscopy

ALD – Atomic layer deposition

APT – Atomic probe tomography

As -Arsenic

As-azide – Arsenic Azide

B - Boron

C - Carbon

CMOS – Complementary metal oxide semiconductor

C-TLM – Circular transmission line method

CVD – Chemical vapour deposition

DCM - Dichloromethane

DFT – Density functional theory

DHEM – Differential hall effect measurement

DLTS – Deep level transient spectroscopy

DPP – Diethyl-1-propylphosphonate

ECV – Electrochemical capacitance voltage

FET – Field effect transistor

FIBDD – Focused ion beam directed deposition

GAA - Gate all around

Ge - Germanium

GP-MLD – Gas phase monolayer doping

IC – Integrated circuit

MLCD - Monolayer contact doping

MLD – Monolayer doping

MOVPE - Metal organic vapour phase epitaxy

ODPA – Octadecyl phosphonic acid

P - Phosphorus

PBE - Perdew-Burke-Ernzerhof

PEALD – Plasma enhance atomic layer deposition

PLAD – Plasma doping

PMMA – Poly methyl methacrylate

RBS – Rutherford backscattering spectroscopy

RCA – Radio corporation America

RF – Radio frequency

RMS – Root mean square

RSF – Relative sensitivity factor

RTA – Rapid thermal anneal

Sb – Antimony

SEM – Scanning electron microscopy

Si - Silicon

SiGe – Silicon-Germanium

SIMS – Secondary ion mass spectrometry

SNR – Signal to noise ratio

SOI – Silicon-on-insulator

SRP – Spreading resistance profiling

STM – Scanning tunneling microscopy

TAA - Triallylarsine

T-BAG – Tethering by aggregation

TDD – Threading dislocation density

TEM – Transmission electron microscopy

TOF-SIMS – Time of flight secondary ion mass spectrometry

VLS – Vapour liquid solid

WCA – Water contact angle

Xj – Junction depth

XPS – X-ray photoelectron spectroscopy

XTEM - Cross sectional transmission electron microscopy

# Acknowledgments

Some studies have shown that the average attention span of a human has dropped from 12 seconds in the year 2000, to 8 seconds in 2018, which coincides with the development of technology such as smartphones. Given that the aim of this thesis is to further advance research in this area it would be ironic if I were to write a long winded acknowledgment section which would run well beyond the measured attention span of which we are all now capable.

I never thought when I was beginning my undergraduate studies in UCC that I would spend most of the next decade at the university and enjoy such successful studies in collaboration with many fantastic individuals of which I will name a few. An incalculable amount is owed to my supervisor Dr. Brenda Long for introducing me to the world of postgraduate research in 2016 and guiding me through the doctoral process while helping all of her students to grow in every aspect of their lives. Without a doubt, I will be forever grateful for everything you have done for me. Whether it was discussing championship soccer or dopant diffusion there is no doubt that every conversation with Dr. Ray Duffy was enjoyable and a fantastic learning experience. The original CONDUCT research project which Brenda, Ray and I worked on from 2016 merged into CONDUCT 2 with the addition of Nikolay, Margarita, Fintan, John and Luke. Each and every one of you were a pleasure to work with and I appreciate how great of a contribution you have made to the work in this text. I am especially grateful for the work which Luke and I collaborated on in the Kane. I have no doubt in my mind that you will be a fantastic scientist in the years to come. A special mention

must also be made to Dan O' Connell, for all of the fantastic processing which he carried out in Tyndall over the course of both projects. The work of both CONDUCT projects would not have been possible without the funding of Enterprise Ireland and Applied Materials.

The School of Chemistry in UCC has provided a great platform for postgraduate studies. I appreciate the help from all staff members that I encountered over my time in the school. Prof. Justin Holmes guided the school over my postgraduate term while also guiding each of us students, whether it was in a conference room or just over coffee, thank you Justin. I promised that I would keep this short, so one final group remains that directly helped in completing my postgraduate studies and must be given a mention. To Shane, Will, Alex G, Eadaoin, Alex L, Giuseppe and all of the other postgraduate students, that are too many to mention, thank you for being such a great bunch to work with.

# **Dedication**

My Family

## **CHAPTER 1**

## Introduction

#### 1.1 Abstract

The year 2020 signals the start of a new decade and in the advanced logic industry it represents the progression from the 7 nm technology node to the 5 nm technology node. Moore's Law scaling of transistors has become increasingly challenged over the past decade by ever decreasing dimensions and performance requirements. The current roadmap for transistor development states that we are in the "more Moore" era where extreme scaling will further test Moore's law. New requirements for power, performance, chip area and cost will be the key metrics involved in gauging the success of semiconductor research and development for this field. Device architectures have successfully moved to finFETS from planar, but now require further advancement to gate-all-around (GAA) structures to maintain scaling and transistor properties advancement. These technology changes are demanding improved processing in all aspects of integrated circuit (IC) fabrication. Semiconductor doping remains a vital component of device processing for these advanced logic applications. Conventional doping methods such as ion implantation struggle to provide conformal and damage free doping of current 3-dimensional (3-D) nanostructures. Alternative doping methods such as plasma doping (PLAD), in-situ doping, atomic layer deposition (ALD) and metal organic vapour phase epitaxy (MOVPE) are being tested with varying degrees of success. Monolayer doping (MLD) is another method which is suitable for doping of nanostructures. MLD, by its nature is conformal and allows precise control over dopant diffusion and concentration, with no crystalline damage.

Work on MLD to date by a number of research groups worldwide, such as the Javey group in Berkeley, Dan group in Michigan/Shanghai, and Napolitani group in Padova, is outlined in this chapter. This technique has been applied to a variety of different materials, from silicon (Si) and germanium (Ge) to III-Vs with demonstrations of different dopant types and surface functionalization strategies. Specific consideration is given to achieving high active carrier concentrations with ultra-shallow diffusion, as these requirements are necessary for advanced logic applications. Particular deficiencies in the literature are noted and are addressed in the work Chapters 3-6 in this thesis. These areas include the achievement of active carrier concentrations greater than 2×10<sup>19</sup> atoms cm<sup>-3</sup> using phosphorus MLD (P-MLD) on Si, development of alternative methods of carrying out arsenic MLD (As-MLD) on Si, and the application of P-MLD and As-MLD to Ge and silicon-germanium (SiGe) alloys.

.

# 1.2 General concepts

## 1.2.1 What is doping?

Doping is the process of adding impurities to intrinsic semiconductors to alter their conductivity. Semiconductor materials have a small band gap in comparison with insulators and therefore the addition of small amounts of impurities leads to a dramatic increase in their conductivity. Both trivalent (*e.g.* boron) and pentavalent (*e.g.* phosphorus) elements are used to dope Group IV semiconductors such as Si and Ge. When an intrinsic Group IV semiconductor is doped with a trivalent or Group III impurity it becomes a p-type semiconductor. As an example, individual Si atoms in a crystalline Si substrate are bonded to four neighbouring Si atoms through their four

valence electrons. When a boron (B) atom is added, it replaces a Si atom in the lattice and since it contains one less valence electron it is considered as adding a hole to the lattice. The "p" in p-type doping denotes "positive", which means the semiconductor is rich in holes or positively charged ions. Alternatively, when an intrinsic Group IV material is doped with a pentavalent or Group V impurity, such as phosphorus (P), we get an n-type semiconductor, where "n" stands for "negative" as P contains an extra valence electron.

#### 1.2.2 Transistor development

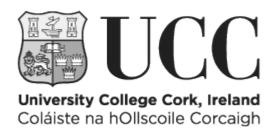

Transistors are semiconductor devices that are used for both amplifying and switching electronic signals and electronic power. Their ability to act as "on" and "off" switches is most commonly related to use in IC technology involved in most modern-day electronics. **Figure 1.1** shows a schematic of an n-type metal oxide semiconductor field-effect transistor (MOSFET) resulting from impurity doping. In this example the substrate is p-doped and contains two heavily n-type doped regions known as the source and drain. The flow of charge between the source and drain, through the channel, is determined by the gate properties in combination with the dielectric layer. Depending on whether a sufficient voltage is applied to the gate, the system will either be in the "on" or "off" state, as shown in the schematic.

**Figure 1.1**: Schematic of planar n-type MOSFET (NMOS). NMOS – "ON" on the left depicts a channel where flow of the electrons has been allowed. NMOS – "OFF" on the right depicts a channel where the flow of electrons has not been allowed. This switching between ON and OFF states is controlled by the gate.

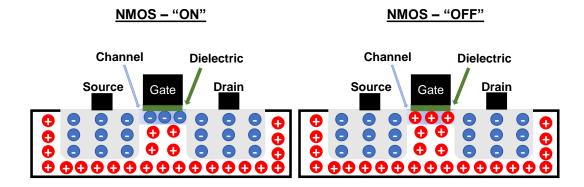

The dimensions of transistors have scaled over the past 50 years in accordance with Moore's law with the number (of transistors) on a chip roughly doubling every 2 years. The original planar device structure has progressed, with scaling, to the currently used Fin and silicon-on-insulator (SOI) structures. Although SOI preceded Fin's, the most commonly used structure today is the Fin structure. Both demonstrate quality electrostatics, but it is possible that economic factors have driven the success of Fins over SOI, as they are considered cheaper to produce. To give an example of the quantity of transistors in a single device, an iPhone 11 which was released in 2019 contains approximately 8.9 billion. This equates to roughly 1.2 transistors for every person in the world (world population 2017 ≈ 7.53 billion), all contained in one phone.

Over the past decade there have been many claims that this continued transistor scaling was not sustainable. Moore's law scaling is being pushed to the limit but current roadmaps show that the "more Moore" era will continue through to 2025.<sup>1, 2</sup> Cloud

computing and the requirement for "instant data" have pushed computing to the edge with a need for ultra-low-power devices that remain "always-on" while also being of high performance to enable the generation of data instantly. The International Roadmap for Devices and Systems 2018 (IRDS-2018) outlined the key aspects for continued device scaling over the near- and long-term future. Targets are set for key parameters of power, area and cost that will all decrease significantly, while performance will increase every 2-3 years in order to maintain a "more Moore" scaling. In terms of device architecture there is a predicted transition from current technology to a GAA structure in the near-term, which is depicted in **Figure 1.2** (up to 2025).

**Figure 1.2**: Transistor architectures have transitioned from planar to finFET to maintain Moore's law. Gate-all-around structures (GAA) are scheduled for implementation before 2025 in what is known as the "More Moore era". <sup>3</sup> STI in this figure refers to shallow trench isolation.

It is likely that Si will remain the backbone of the semiconductor industry into this "more Moore" era, as we move towards the development of GAA devices. However,

it is probable that alternative materials will be introduced, alongside Si, to create high-mobility channels. SiGe, Ge and III-V's, for example, are possible alternatives as they provide increased drive current due to their increased electron and hole mobility when compared with standard Si.<sup>4</sup> It is predicted by the IRDS-2018 that channel material for logic applications will move to SiGe in 2020 and then to Ge from 2025.

#### 1.3 State of the art in semiconductor doping

#### 1.3.1 Beam-line ion implantation

Semiconductor doping has traditionally been carried using a technique known as beam-line (BL) ion implantation. Given that this approach has been the most common method of implantation it will simply be referred to as ion implantation from here on. This is an approach where the semiconductor surface is bombarded with ions of the desired atom, whether it be an n-type dopant for Si such as P or arsenic (As), or a p-type dopant such as B or indium (In).

The concept of ion implantation was developed through the 1940s and 50s finally resulting in it being brought to market in the 1960s. A pivotal moment was the filing of a patent in 1954 by William Shockley of Bell laboratories. He described ion implantation as a process that could alter the conductivity of a Group IV semiconductor material by bombarding it with atoms from a Group III or V element with sufficient energy to enable it to enter the crystal lattice. This process causes amorphization of the implanted region which, Shockley realised, could be recrystallized through thermal treatments during which the impurity atoms are

incorporated into the crystal lattice causing a change in electrical properties.<sup>5</sup> Ion implantation has been extensively studied and optimised over the course of the last 50 years. Companies such as Texas Nuclear and IPC, which were the forerunners of the implantation industry, have through mergers and terminations transformed into the modern-day industry leaders of Applied Materials, Axcelis Technologies and Nissin Ion Equipment.<sup>6</sup>

Although ion implantation has been a fundamental process in transistor development to its current state, its limitations are evident when the process is applied to sub 10 nm 3-D nanostructures. These include irreparable crystal damage, poor conformality and difficulty achieving ultra-shallow junctions. Control of the depth at which dopant atoms are located after implantation is impacted both by the initial ion bombardment step and the subsequent thermal treatment for recrystallization/activation purposes. Production of ultra-shallow junctions is vitally important to modern devices given that device dimensions are in the sub 10 nm regime. Source and drain regions of complementary metal oxide semiconductor (CMOS) devices require high, ultrashallow doping levels to minimize junction leakage as the gate length decreases. A junction in this case is defined as the depth from the semiconductor surface where the concentration of intentionally introduced electrons (n-type doping) is equal to the concentration of holes which are intrinsic to the substrate. When attempting to implant dopant atoms at ultra-shallow depths, an extremely low implant energy is required. This causes a major problem as ion-ion repulsion (spreading of the ion beam) at low energies limits the tool's ability to transport and manipulate ions. Several solutions have been proposed, such as deceleration 8 or molecular ion implantation, 11 which may satisfy the current requirements for device fabrication but will likely struggle to meet

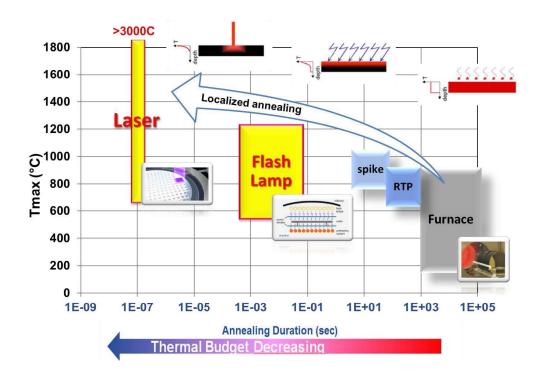

future demands, due to decreasing dimensions and 3-D architectures. <sup>9, 10</sup> As mentioned above, during the implantation process the crystal structure of the semiconductor is damaged, resulting in an amorphous implant region which is supersaturated with point defects, and has to be repaired through a thermal treatment. However, this thermal treatment, post implantation, has been found to result in enhanced dopant diffusion through a process known as transient enhanced diffusion which makes it difficult to attain ultra-shallow diffusion depths through standard ion implantation and thermal annealing. <sup>11</sup> Co-implantation with species such as fluorine, for B doping of Si, has shown some success in reducing dopant diffusion during the thermal anneal step. <sup>12</sup> Advanced annealing techniques such as laser annealing and flash lamp annealing (FLA) have also demonstrated shallower diffusion depth and increased activation levels when used in combination with ion implantation.

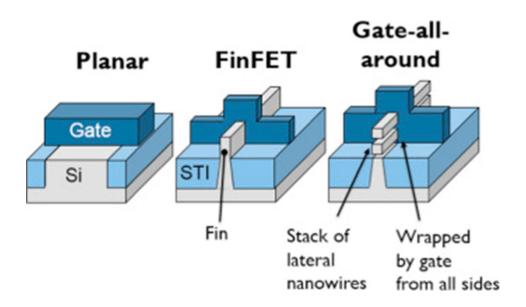

The ion implantation process also struggles to adapt to non-planar surfaces such as finFETs, which are currently in the sub 10 nm regime. When applying ion implantation to these smaller 3-D devices the crystal damage caused is much more difficult to reverse if it is possible at all. If the Fin is completely amorphized it has been found that defective recrystallisation occurs, as shown in **Figure 1.3**. Even when the Fin is not completely amorphized the regrowth process may take place at different velocities, between the bulk and the sidewall, resulting in a large number of twin defects leading to limited drive current while also impacting resistivity. This results in higher junction leakage and parasitic resistance problems. He use of "hot" implantations has been studied in an attempt to prevent the amorphization of the substrate. It was found, however, that this approach led to increased channelling, due to the lack of amorphization, and therefore deeper dopant profiles, which is counterproductive

considering the requirement for ultra-shallow.<sup>15</sup> When considering finFET devices with a narrow Fin pitch, the directional nature of ion implantation will lead to a shadowing effect which limits both control of dose and dopant positioning this results in non-conformal doping.<sup>16</sup>

**Figure 1.3**: Cross-section transmission electron microscopy images of an ion implanted Fin structure before (a) and after (c) thermal annealing. Visible twin defects remain after thermal treatment. Adapted with permission from reference 13, Applied Physics Letters, AIP Publishing (2007).

#### 1.3.2 Plasma doping

As was previously stated, some of the main downsides associated with ion implantation are crystal damage (amorphization), non-conformality and difficulty producing ultra-shallow junction depths (Xj). Through years of research and development plasma doping (PLAD) has been found as a viable alternative which is capable of addressing some of these issues.

PLAD is an adaptation of ion implantation, where a dopant-containing gaseous precursor is energized into a plasma by a radio frequency (RF) source. The required dopant ions are then extracted from the plasma by applying a voltage to the substrate and targeting them into a semiconductor wafer. The voltage applied determines the implantation depth which enables ultra-shallow junction formation. This is considered to be one of the main advantages of PLAD as it produces ultra-shallow junctions much more quickly than ion implantation. Although PLAD is based on a relatively simple concept it is challenging as it relies on a number of secondary processes (deposition, resputtering, in diffusion, etc.). These secondary processes are a result of neutral atoms from the plasma depositing on the target substrate followed by their interaction with incident ions that may cause them to re-sputter to other locations on the substrate. During subsequent activation anneals the deposited neutral atoms are also capable of in-diffusion into the substrates crystal lattice.

Lee *et al.*, carried out a study on the amorphization caused by ion implantation and compared it with plasma doping.<sup>18</sup> They claim that plasma doping produces considerably less damage than ion implantation due to the lower energies required for the incorporation of dopant ions. However, although there is less damage from this technique, it will still lead to the presence of defects after recrystallization with similar consequences to those described with ion implantation.

The ability of PLAD to uniformly dope non-planar structures is critical to its success in device fabrication in the future. Some of the earliest work examining this topic was carried out by Mizuno *et al.*, <sup>19</sup> they successfully doped the vertical sidewall of a trench

capacitor using PLAD. Even at this extremely early stage in the development of the technique, this group managed to achieve a thinly doped region (30-50 nm deep) at the relatively low processing temperature of 120 °C. However, when looking at more recent 3-D device architectures with more densely packed structures such as finFets, PLAD has encountered difficulties producing conformal doping.<sup>20</sup>

PLAD has also been found to result in high levels of dopant trapping at the SiO<sub>2</sub>:Si interface,<sup>21</sup> This effect is worsened when using heavier dopant atoms, Kim *et al.* compared plasma doping using P and As on a set of finFET structures. Through use of atomic probe tomography (APT), they found that the majority of dopant atoms were segregated along the boundary of the Si substrate. They discovered that using heavier As ions resulted in more surface damage and led to increased surface oxidation.

#### 1.3.3 In-situ chemical vapour deposition doping

Chemical vapour deposition (CVD) is a commonly used method for producing thin semiconductor films on bulk substrates. It involves the growth of a film of the required substance in either monocrystalline, polycrystalline or amorphous forms, <sup>22-25</sup> when the bulk substrate is exposed to a vapour containing the required mixture of precursors which react with or decompose onto the substrate surface. <sup>24</sup>

*In-situ* doping of these CVD films is a very complex process. Introducing another component in the vapour phase to the growth mixture inevitably leads to the possibility of more chemical interactions taking place.<sup>26</sup> This issue can sometimes be resolved through examination of the mechanisms and fine-tuning of process parameters *e.g.* gas

flow, chamber pressure. The main issue when considering CVD as a rival to ion implantation is the lack of uniformity and control over the location of the dopant atoms in the grown films.<sup>27</sup>

CVD has also been demonstrated as a method with potential for growing nanostructures such as nanowires.<sup>23, 27</sup> Doping of Group IV nanowires during the growth process is usually carried out by introducing phosphine (PH<sub>3</sub>) or diborane (B<sub>2</sub>H<sub>6</sub>) gas precursors which decompose and dissolve into the liquid growth seed used in vapour-liquid solid growth (VLS).<sup>28</sup> This mechanism of *in-situ* doping has been found to severely impact the growth rate of nanowires and some reports claim that it completely inhibits nanowire growth when using high ratios of phosphine to silane, or arsine to silane.<sup>29, 30</sup> It has also been found that dopant incorporation during the growth process does not result in uniform doping throughout the 3-D nanowire structure with increased levels found in the sidewalls.<sup>27</sup> Negative impacts on nanowire morphology, such as nano-faceting, have also been observed when introducing B as the dopant molecule with diborane precursor.<sup>31, 32</sup>

## 1.3.4 Spin-on doping

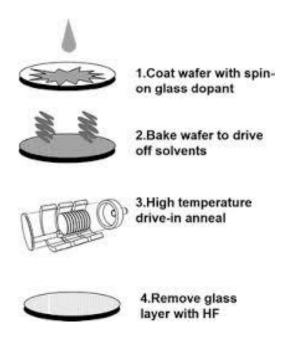

Spin-on doping is a technique most commonly used for doping of Si solar cells.<sup>33, 34</sup> It may also have applications for doping of CMOS and other electronic devices.<sup>35</sup> This doping technique is regarded as a low-cost and simple method for non-destructive semiconductor doping.<sup>36</sup> In its simplest form, spin-on doping utilizes sol-gel processing techniques to coat the semiconductor wafer with a dopant source. **Figure 1.4** provides a general outline of the spin-on-doping process for semiconductor wafers. This initially involves the coating of the target substrate with a solution, usually

containing the dopant atom incorporated in monomer molecules which are Si based, such as phosphosilicates. This solution is then cured, at a relatively low temperature in comparison to later dopant diffusion/activation anneals, to "solidify" into a gel through solvent evaporation and polymerization. Finally, samples are annealed to diffuse the dopant atoms into the Si substrate.<sup>35, 37</sup> Numerous publications have investigated the application of spin-on doping to Si and Ge substrates with dopant species varying from P, Sb and Ga.<sup>38-44</sup>

**Figure 1.4**: A general spin-on-doping process outline. Reprinted with permission from reference 45 MEMS Reference Shelf, vol 1. Springer (2011). <sup>45</sup>

Some of the downsides of spin-on doping include its lack of uniformity, and poor dose control over large areas.<sup>36</sup> Another major disadvantage when comparing spin-on doping to other rival techniques is that the removal of the spun-on layer is relatively difficult, often leaving an undesirable residue. Hoarfrost *et al.*,<sup>35</sup> proposed an approach which they believed would resolve some of these issues. They spun-on a solution of dopant-containing organic polymers and carried out the same processing steps used in

spin-on doping. As expected, the organic polymer film burned off during rapid thermal annealing (RTA) and they believe that the resulting deposit can be easily removed through wet chemical treatments providing a solution to conventional spin-on doping's major issue. This approach appears to be promising but still lacks the uniformity of MLD. Traditional spin-on doping does not have the required characteristics to be of use for doping of modern electronic devices, as it will be difficult to conformally cover arrays of tightly pitched 3-D nanostructures. Further work will have to be done on variations of this process for it to have an impact on the industry.

#### 1.3.5 ALD and Gas phase MOVPE

Atomic layer deposition (ALD) is another technique that is widely recognised as a possible alternative to implantation for future doping applications. <sup>46,47</sup> It is a gas phase deposition method which consists of sequential, self-saturating surface reactions. The required chemicals are introduced into the reaction chamber in what is known as a "pulse" to react with the surface followed by a "purge" to remove the excess gas and prevent gas phase reaction with the chemical involved in the next pulse-purge steps. The main advantage associated with ALD is its ability to conformally coat surfaces of complex geometry, whether they are planar or 3-D, with controlled layer formation. However, this often requires high cost processing with long times which lead to a low throughput. Further development of ALD using plasma sources, referred to as plasma enhanced atomic layer deposition (PEALD), will enable lower operating temperatures than those used in standard atomic layer deposition. Work by Baik *et al.*, has shown that PEALD in combination with flash lamp annealing can lead to high (> 10<sup>20</sup> cm<sup>-3</sup>) incorporation levels of n-type dopants in Ge.<sup>48</sup>

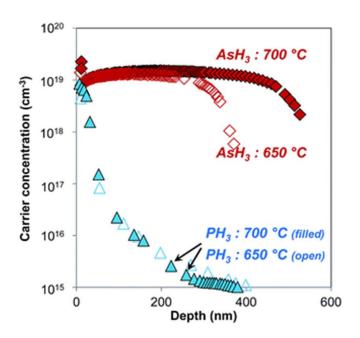

Metal organic vapour phase epitaxy (MOVPE) has also been used as a method of gas phase doping with the potential for conformal doping of 3-dimensional nanostructures. In general, MOVPE is used as a gas phase technique for growth of semiconductor layers. It is capable of operating at temperatures in excess of 1000 °C. The adaptation of this tool for group IV semiconductor doping has been pioneered by the Tyndall National Institute. This system is capable of utilizing highly toxic gases such as arsine and phosphine at elevated temperatures allowing for effective doping (**Figure 1.5**).<sup>49,</sup> However, maintaining control of the dose using MOVPE is difficult due to simultaneous deposition and diffusion of dopants into the substrate at the elevated processing temperatures used.

**Figure 1.5**: Example of work by Duffy *et al.*, doping Ge with As and P through MOVPE. Activation results shown are measured with electrochemical capacitance voltage profiling. Reprinted with permission from reference 50, Journal of Materials Chemistry C, Royal Society of Chemistry (2014).<sup>50</sup>

#### 1.4. Monolayer doping

## 1.4.1 Background

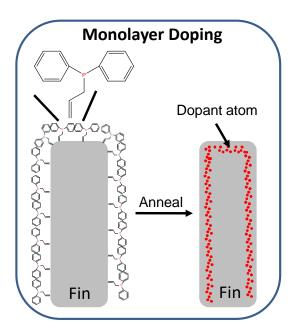

Monolayer doping is a doping technique which was pioneered by Javey *et al.* that provides a solution to problems encountered with ion implantation.<sup>51</sup> It has the potential to produce ultra-shallow junctions with minimal crystal damage to the substrate. As was previously stated, one of the major problems facing the semiconductor doping industry in the coming years is the ability to conformally dope tightly pitched arrays of 3-D structures, such as finFET's, and non-line-of-sight doping, e.g. for GAA devices. MLD has shown great promise in this area.<sup>52</sup>

**Figure 1.6**: Schematic depicting the application of monolayer doping to a Fin structure., © 2014 IEEE

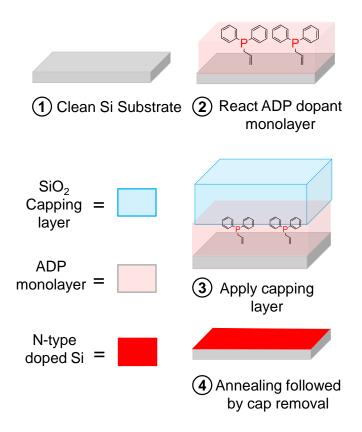

The process in its simplest form involves the chemical reaction of a molecule containing the target dopant atom to what is usually a hydrogen terminated Si surface (formed through a short dip in hydrofluoric acid). A suitable MLD molecule will contain the required dopant atom while also containing a reactive functionality intended for interaction with the semiconductor surface. It is also important that the remaining functional groups of the molecule are "un-reactive" and will not polymerise or lead to multilayer formation. These properties promote a self-limiting monolayer formation which is of course for MLD. In most studies surface functionalisation step is followed by the application of a capping layer to promote in-diffusion of the target atom into the substrate through thermal annealing, and subsequent capping layer removal.<sup>53</sup>

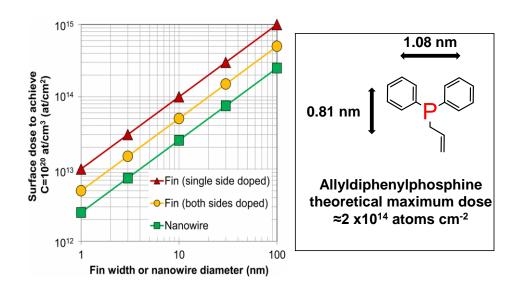

Due to the self-limiting nature of the reaction between the dopant molecule and the Si surface it is possible to apply a consistent and repeatable dopant dose. Long et al,

demonstrated the relationship between surface dose and resultant carrier concentrations after doping, if dopants were confined within the dimensions of Fins or nanowires. The work in **figure 1.7** shows that it is possible to achieve carrier concentrations in excess of  $1x10^{20}$  atoms cm<sup>-3</sup> for sub-10 nm fin width or nanowire diameter, with surface dose values  $\leq 1x10^{14}$  atoms cm<sup>-2</sup>. A dose of  $2x10^{14}$  atoms cm<sup>-2</sup> would in this case be satisfactory to achieve carrier concentrations greater than  $1x10^{20}$  atoms cm<sup>-3</sup> for dimensions up to 20 nm. For example, allyldiphenylphosphine (ADP) which is a P-MLD precursor has dimensions (shown in **figure 1.7**) that would equate to a maximum achievable dose value of  $2x10^{14}$  atoms cm<sup>-2</sup>. Decreasing the size of the dopant molecule provides a possible route towards achieving the same levels of incorporation as seen with ion implantation.

**Figure 1.7:** The graph represents work by Long et al where they estimated the relationship between Fin/nanowire dimensions and the required surface dose to achieve carrier concentrations in excess of  $1x10^{20}$  atoms cm<sup>-3</sup>. Adapted with permission from reference 52, © 2011 IEEE

#### 1.4.2 MLD development

#### 1.4.2.1 Phosphorus and Boron MLD

The majority of MLD publications to date have dealt with variations of P and B doping of Si. In this section we will discuss some of the state-of-the-art MLD processing and characterization developed by groups worldwide for P and B MLD on Si. O'Connell *et al.* previously summarized MLD literature up to 2016 in a comprehensive review article.<sup>36</sup> In the following sections the work up to 2016 will be noted and progress since this date will be examined in detail.

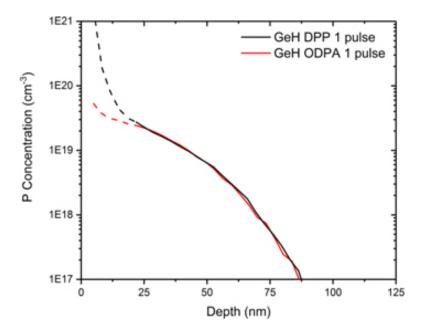

When reviewing MLD it is important to note and describe the pioneering work that was carried out by Javey *et al.* to introduce the topic to the world of academic research in 2008.  $^{51, 53}$  They developed methods of P-MLD and B-MLD through the use of diethyl-1-propylphosphonate (DPP) and allylboronic acid pinacol ester (ABAPE), respectively, as dopant precursors. Chemical concentrations which may not all be electrically active, measured by secondary ion mass spectrometry (SIMS), of the resulting doped Si exceeded  $1 \times 10^{20}$  atoms cm<sup>-3</sup> for both dopant types and demonstrated sub 50 nm Xj at  $5 \times 10^{18}$  atoms cm<sup>-3</sup>. These publications provided the basis for further work on the topic which would be carried out by multiple groups worldwide to refine and optimize MLD processing.

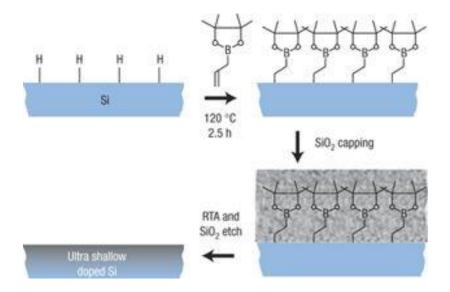

**Figure 1.8**: B- and P-MLD was pioneered by Ho *et al.*, with an example of the B-containing monolayer functionalisation procedure depicted. Reprinted by permission from reference 51, Nature Materials, Springer Nature (2008).

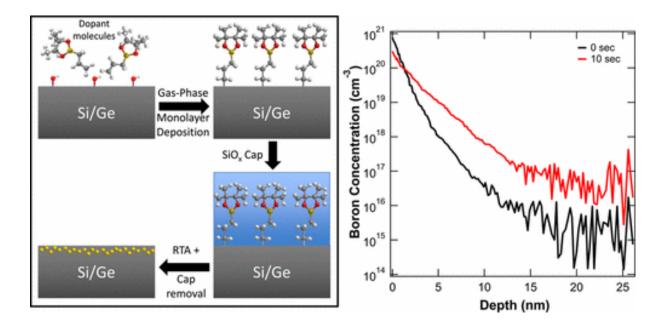

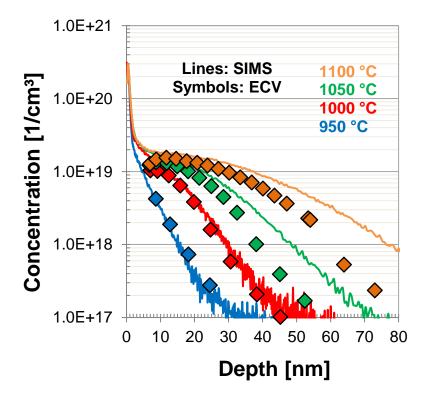

Standard MLD is a liquid phase process that is used to form the surface monolayer. Taheri *et al.*,  $^{54}$  have developed a method known as gas phase monolayer doping (GP-MLD). A modified ALD apparatus was utilised to carry out these gas phase functionalisation reactions. This alternative to standard MLD also allows doping of 3-dimensional nanoscale architectures without having to consider wetting factors which can hinder nanowire doping. This gas-phase method was combined with a 1000 °C anneal for time periods of spike (no hold time at the maximum anneal temperature) and 10 second, respectively. They achieved carrier concentrations above 1 x  $10^{20}$  atoms cm<sup>-3</sup> total incorporated dopant atoms as measured by SIMS which are shown in **Figure 1.9**. The surface concentration of B using a spike anneal in Si was  $7.5 \times 10^{20}$  atoms cm<sup>-3</sup> with an Xj of 3.5 nm (at  $5 \times 10^{18}$  atoms cm<sup>-3</sup>). These values are at the limit of SIMS characterization but do represent some of the potential that MLD processing has for ultra-shallow doping.

Localized doping is a key feature of ion implantation with which MLD is striving to compete with. Through the use of nano-lithography, it has been shown by Taheri *et al. that* MLD is capable of selectively doping specific regions on the Si surface, *et al.* using a pattern of 2 µm poly methyl methacrylate (PMMA) resist squares. After application of this resist they carried out GP-MLD and removed the resist. Demonstration of localized doping was confirmed through conductive atomic force microscopy (AFM). Voorthuijzen *et al.*,<sup>55, 56</sup> had previously ventured into the area of localized doping via MLD. These publications also demonstrate that MLD is capable of integration into a variety of process schemes, as dopant monolayer functionalization was demonstrated both before and after nanolithography steps.

**Figure 1.9**: Taheri *et al.* developed a method for gas phase MLD which they applied to Si and Ge substrates with SIMS data showing high chemical incorporation of dopants at ultra-shallow depths. Reprinted with permission from reference 54 by Taheri *et al.* Copyright (2017) American Chemical Society.

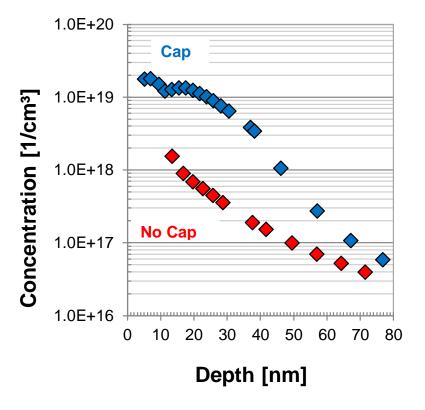

Significant effort has been put into understanding whether capping layers are necessary for optimal dopant incorporation with MLD. Addition and removal of a SiO<sub>2</sub> capping layer involves several process steps which are beneficial to circumvent if possible. Caccamo *et al.*, carried out a detailed study into the impact of capping layer variation on the resultant dopant incorporation from MLD on Si.<sup>57</sup> They utilized a P containing dopant molecule (diethyl-1-propyl phosphonate) with a variety of SiO<sub>2</sub> deposition methods for capping layer addition and made a comparison with a sample where no cap was applied. Using spreading resistance profiling (SRP) for analysis of active carrier concentration profiles they determined that CVD capping with SiO<sub>2</sub> resulted in the highest maximum active carrier concentration values of 2×10<sup>19</sup> atoms cm<sup>-3</sup> and greatest total dose incorporation.

Monolayer contact doping (MLCD) is a variation of MLD where the target Si substrate is contacted with a second Si substrate, which has previously been functionalized with the dopant molecule, and thermally annealed. This thermal treatment induces diffusion of the dopant atom into both target and donor substrates, while also providing energy for activation. <sup>58, 59</sup> The main advantage of this method is the ability to carry out the MLD process without the use of capping layers. Hazut *et al.*, demonstrated that MLCD using a variety of P precursors (diphenylphosphine oxide, triphenylphosphine oxide, and tetraethylmethylenediphosphonate) resulted in total chemical concentration values (by SIMS) approaching the solid solubility levels of P incorporation at  $\approx 5 \times 10^{20}$  atoms cm<sup>-3</sup>. When applied to Si nanowires, the measured electrical resistance led to the conclusion that a maximum active carrier concentration of  $\approx 1 \times 10^{19}$  atoms cm<sup>-3</sup> was achieved. A further novel contribution made by Hazut *et al.*, was to develop a method of doping nanowires with both n and p-type dopants in a single step to produce parallel

p-n junctions.<sup>60</sup> This study once again demonstrated maximum active carrier concentrations of  $\approx 1 \times 10^{19}$  atoms cm<sup>-3</sup> for P doped nanowires which were measured through scanning tunnelling microscopy (STM).

Veerbeek. et al 61 examined the use of MLCD and an MLCD/MLD combination for the doping of highly porous nanowires, which would have had a large surface area due to the increased porosity. They reported MLCD dose values an order of magnitude higher than those they achieved using MLD and the same reaction conditions. In this study a relatively large carborane molecule (1-triethoxysily1-2-methyl-carborane), which contains 10 B atoms, was synthesized with the aim of increasing the possible dose available for doping. This area of dose control is an important topic for MLD. Tailoring the size of the molecular precursor should, in theory, enable a wide range of doses to be introduced. Possibly the most significant demonstration of this precursor tailoring to date has been by Wu et al., where macromolecules containing P were chemically bound to Si with the aim of controlling single dopant atom placement in the target crystalline lattice. 62, 63 This control of single dopant atoms is extremely challenging for other doping techniques and, with its potential application to quantum computing, could prove to be a breakthrough application for MLD processing. 64, 65

Hazut *et al.*<sup>66</sup> also pioneered a variation of MLD known as remote monolayer doping which has the ability to selectively dope regions of a substrate. Photolithography processing was used to pattern a photoresist mask which is applied to the target substrate. This enabled determination of areas which are selectively doped. A donor substrate is functionalized with the dopant atom source. These substrates are then

brought into contact, in a similar manner to MLCD, and through thermal processing it is capable of selectively doping areas of the target substrate. Characterisation of the MLD doped substrates was carried out with false colour scanning electron microscopy (SEM), sheet resistance measurements, and SIMS.

As was previously discussed, incorporation of dopant atoms during nanowire growth has proven difficult as it has been shown to result in defective growth. Puglisi *et al.*, demonstrated that nanowires which had been grown via CVD could be doped following growth by MLD.<sup>67</sup> Electron microscopy analysis showed that, after MLD, the nanowire structures were not damaged and had no visible defects. SRP analysis of active carrier concentrations on a planar sample which had also been doped via the same MLD processing demonstrated max active carrier concentration levels  $\approx 1 \times 10^{19}$  atoms cm<sup>-3</sup>.

Carbon (C) contamination of electronic devices would cause an issue as it would negatively impact electrical properties due to C-dopant defect formation resulting in deactivation of the dopant atoms. When selecting a dopant molecule, it is possible to minimize this issue but not completely remove it. All dopant molecules used in MLD contain an organic shell composed of C and possibly other elements. During thermal treatments, these elements are also capable of diffusing into the Si substrate. Several studies have been carried out to investigate the impact of C (and other elements) contained in these molecules on the activation of dopants introduced via MLD, with varied conclusions as discussed below. For example, it was reported by Shimizu *et al.*, <sup>68</sup> using APT, that C and O contamination are restricted to the first few nanometres

of Si ( $\approx$  2-3 nm) and they proposed that the removal of these layers would solve the issue.

**Figure 1.10**: APT analysis of P-MLD doped Si was conducted by Shimizu *et al*. Through elemental mapping they determined that the majority of C and O contaminants, introduced by MLD, were confined within  $\approx 2$  nm of the surface. Reprinted with permission from reference 68, Nanoscale (2014).

Gao *et al.*,<sup>69</sup> have investigated the impact of introducing C into Si during P-MLD processing with deep level transient spectroscopy analysis (DLTS) of the resulting defects. They determined that up to 20% of P atoms were electrically deactivated by C or oxygen (O) related defects. In a further publication Gao *et al.*,<sup>70</sup> proposed a method of removing these C related defects via post MLD annealing processes. They proposed the use of "longer" anneals at relatively low temperatures (up to 400 °C) to remove the C-related defects. Although relatively low temperatures are used for these thermal treatments, they are for time periods greater than two minutes which would

both slow throughput and lead to an additional step in MLD processing which could be seen as a negative industrially. A recent report by Zhi *et al.*, also proposes a thermal pyrolysis method for reducing the impact of C contamination on P-MLD samples.<sup>71</sup> This fundamental issue of C incorporation during MLD processing will continue as a point of contention when considering the process as a viable alternative to implantation industrially.

Further to this work on P-MLD, Gao *et al.*, studied the impact of C and related defects on B-MLD.<sup>72, 73</sup> Utilizing the same characterization methods as previously used on P-MLD doped samples they determined that B-MLD, with ABAPE, does not suffer from the same degree of dopant deactivation. Up to 99 % of B was found to be active with 1 % deactivated through binding with O impurities which form majority hole traps. The C defects which caused issues with P-MLD samples were found to have no negative impact on B-MLD samples as they only captured electrons and did not interact with the hole population introduced from B doping.

The impact of surface states on MLD was studied by Park *et al.*<sup>74,75</sup> In this study they examined different crystal orientations, crystallinities and surface defects using B-MLD with ABAPE as a dopant precursor. They found that (100) Si functions as a more efficient surface state for MLD compared to (110) Si which they deduced was a result of the lesser reaction sites available on the (110) surface for termination with the ABAPE molecule. SIMS profiles demonstrated high surface carrier concentrations greater than  $\approx 1 \times 10^{20}$  atoms cm<sup>-3</sup> for both states. The accuracy of SIMS in this surface region is heavily dependent on calibration and is always in question.

Developing novel applications for MLD should enable greater industrial application of this methodology. He *et al.* has recently proposed P-MLD as a means of doping Si for phototransistors. This form of transistor relies on exposure to light for operation and is commonly used in state-of-the-art photonic applications. Through the use of P-MLD, they produced Si nanowires with a core P-N junction, which they characterized with SEM, TEM, SIMS and electrical measurements. It was determined in this study that P-MLD enables the formation of highly repeatable phototransistors which is promising for commercialisation purposes.

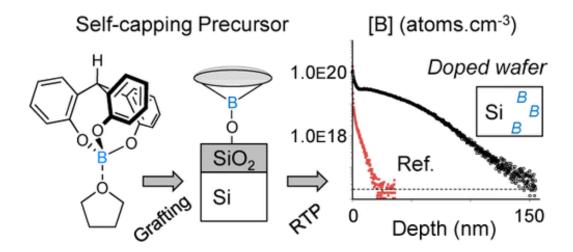

Although, planar and nanowire Si functionalization have been the main test methods of MLD, it has also been applied to nanoparticles. Mathey *et al.*, <sup>78</sup> demonstrated that B-MLD could be applied to nanoparticles while also introducing the concept of a self-capping molecule (**Figure 1.11**). In this study a set of molecules (Tris(2-hydroxyphenyl)methane-borate tetrahydrofuran adduct and Phenanthro[9,10-d][1,3,2]dioxaborole) were used that contained relatively large terminal functional groups which acted as a capping layer to promote diffusion into the target substrates. Removal of the capping step from MLD would be beneficial from the commercial and throughput perspectives. The underlying issue with capping is the requirement for deposition methods that will also conformally coat tightly pitched nanostructures. This could potentially lead to a situation in future device dimensions where it would be possible to produce conformal dopant monolayer coverage while not being able to conformally cap the sample. Therefore, it is imperative that alternative methods for promoting diffusion into the substrate or capping are explored. Tzaguy *et al.*, have also recently used SiO<sub>2</sub> nanoparticles as a target for B-MLD dopant attachment. <sup>79</sup>

**Figure 1.11**: Mathey *et al.*, both demonstrated that MLD is applicable to nanoparticles and developed a self-capping precursor approach for B-MLD. Reprinted with permission from reference 78 © American Chemical Society (2015)

# 1.4.2.2 Application of MLD to alternative dopant and substrate types.

When surveying the landscape of MLD literature it is quite obvious that publications on the use of alternative n-type dopants for Si are sparse. To date there have only been three publications related to As and three related to antimony (Sb) doping of Si and Ge. There are a number of reasons as to why there is such a disparity between the work involving P/B and As/Sb/others. The toxicity of As and Sb precursors is well recorded, with most academic research set-ups unsuitable for their use due to safety concerns. There are also issues with reactivity of As- or Sb precursors. To the best of the authors knowledge there are no commercially available As- or Sb- molecules which contain the allyl (R-C=CH<sub>2</sub>) functional group capable of reacting with Si and Ge through the most commonly used reaction types of hydrosilylation/hydrogermylation. Therefore, alternative reaction types are required for the attachment of these precursors in MLD.

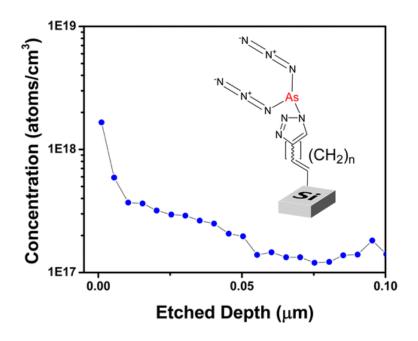

O'Connell et al. 80 synthesized a triallylarsine (TAA) molecule which they used to dope Si nanostructures down to 20 nm in width, finding a maximum decrease in resistivity of 7 orders of magnitude after doping. O'Connell et al. further developed a click chemistry approach for attaching an arsenic azide (As-azide) molecule to a Hterminated Si surface. Given that the As-azide would not directly attach to the Si-H surface they initially formed a dialkyne monolayer on the Si through thermal hydrosilylation. The follow up reaction between the As-azide and the dialkyne monolayer is referred to as the "click" step. Click reactions are defined as a means of generating substances by joining smaller modular units. This both demonstrated a novel functionalization method and provided a new method for As-MLD.<sup>81</sup> This study demonstrated low activation levels of As after MLD processing with maximum carrier concentrations of  $\approx 2 \times 10^{18}$  atoms cm<sup>-3</sup> measured with electrochemical capacitance voltage profiling (ECV). The authors proposed that these low dopant levels would have application in "devices where low defect densities are required to minimise dark currents such as high operating temperature detectors and low-capacitance photodiodes for electron detection".

**Figure 1.12**: O'Connell introduced the concept of click chemistry to MLD surface functionalisation. The graph shows ECV active carrier concentration values from this method of As-MLD with As-azide precursors. Reprinted with permission from reference 81 © American Chemical Society (2015).

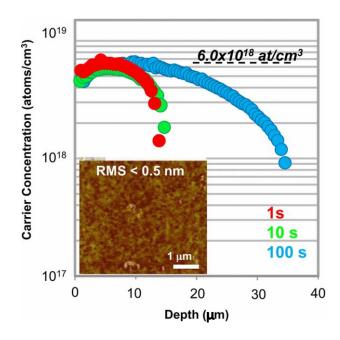

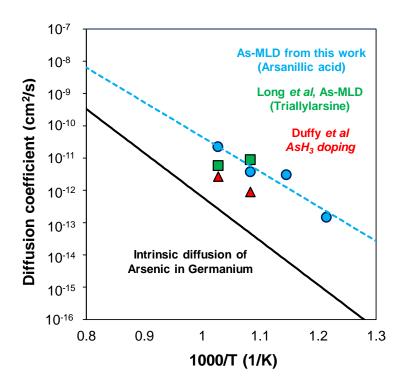

The application of MLD to other substrate types, such as planar Ge and nanowires, has proven to be a high interest topic of research in recent years. Long *et al.* also used TAA as an As-MLD precursor and developed As-MLD on blanket Ge wafers showing a maximum active dopant concentration level of  $6 \times 10^{18}$  atoms cm<sup>-3</sup>.<sup>52, 82</sup> Due to the material properties of Ge (melting point = 938 °C) it is not suited to RTA temperatures above 700 °C. It was theorized that this  $6 \times 10^{18}$  atoms cm<sup>-3</sup> mark represented a solubility limit of As for Ge via MLD.

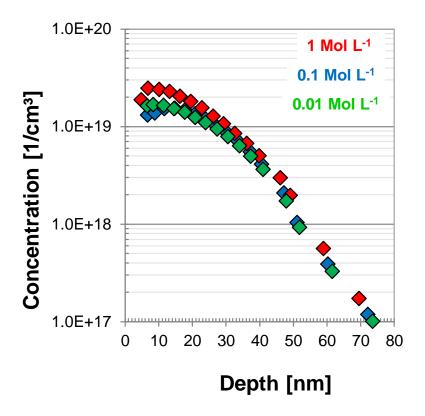

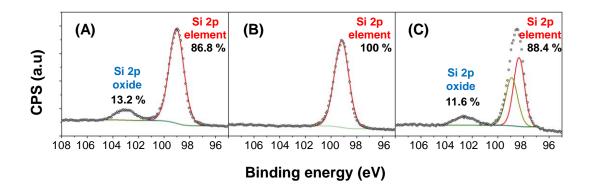

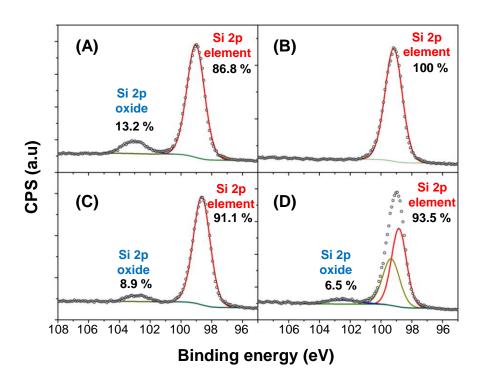

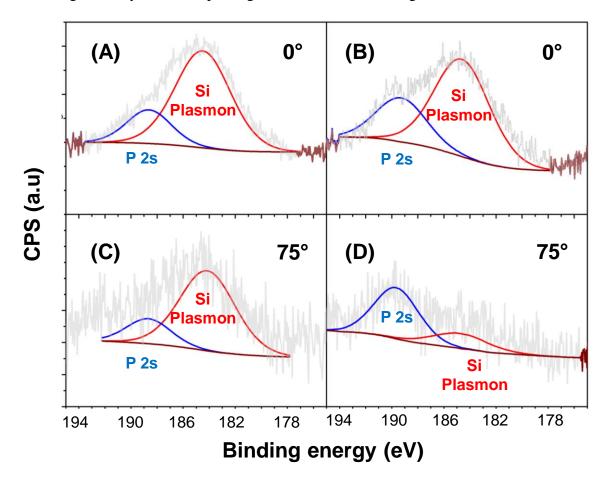

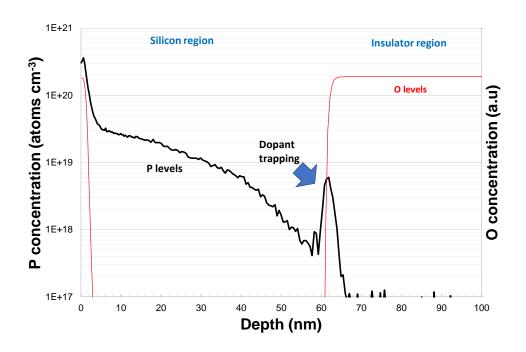

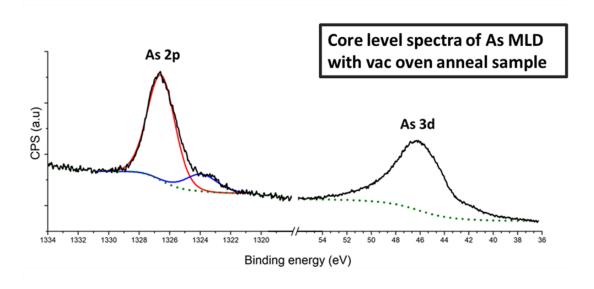

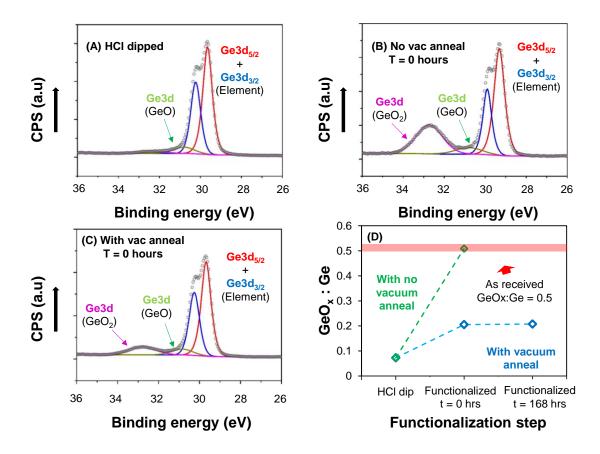

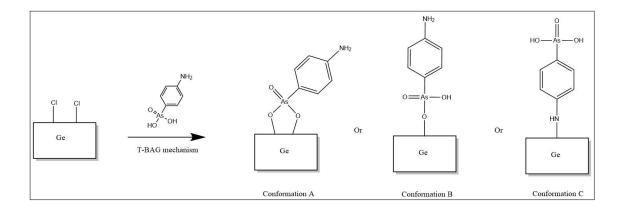

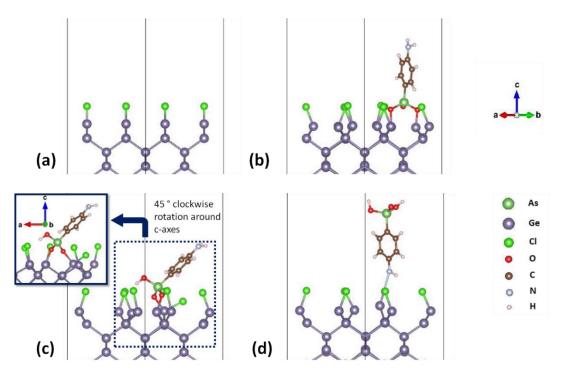

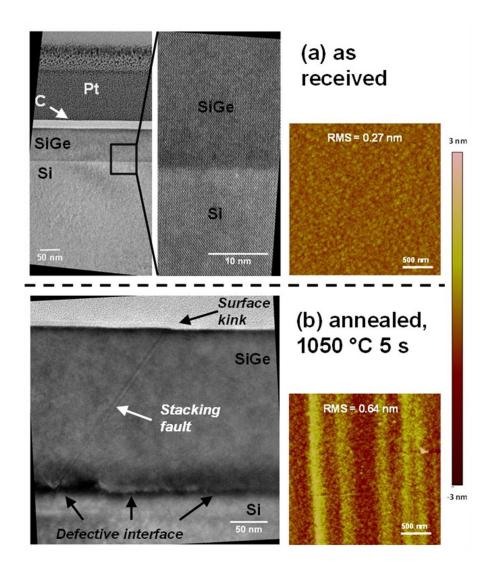

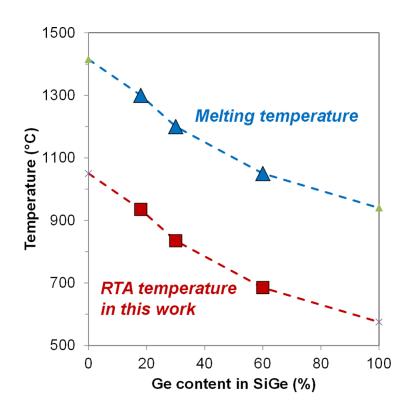

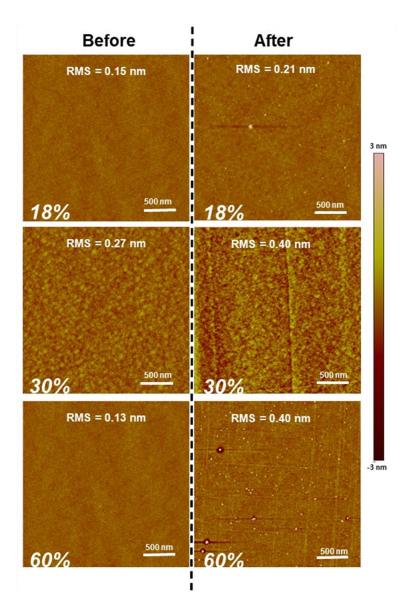

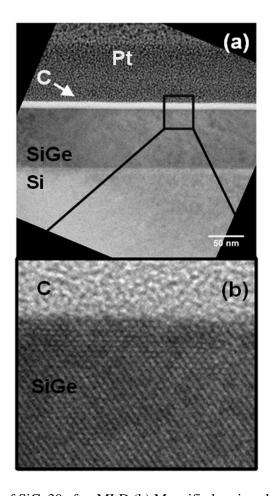

**Figure 1.13**: ECV analysis of active carrier concentrations achieved through As-MLD with TAA on Ge substrates by Long *et al.* © 2014 IEEE