# Steep-slope Devices for Power Efficient Adiabatic Logic Circuits

Juan Núñez and María J. Avedillo

Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC/Universidad de Sevilla)

Abstract— Reducing supply voltage is an effective way to reduce power consumption, however, it greatly reduces CMOS circuits speed. This translates in limitations on how low the supply voltage can be reduced in many applications due to frequency constraints. In particular, in the context of low voltage adiabatic circuits, another well-known technique to save power, it is not possible to obtain satisfactory power-speed trade-offs. Tunnel field-effect transistors (TFETs) have been shown to outperforms CMOS at low supply voltage in static logic implementations, operation due to their steep subthreshold slope (SS), and have potential for combining low voltage and adiabatic. To the best of our knowledge, the adiabatic circuit topologies reported with TFETs do not take into account the problems associated with their inverse current due to their intrinsic p-i-n diode. In this paper, we propose a solution to this problem, demonstrating that the proposed modification allows to significantly improving the performance in terms of power/energy savings compared to the original ones, especially at medium and low frequencies. In addition, we have evaluated the relative advantages of the proposed TFET adiabatic circuits, both at gate and architecture levels, with respect to their static implementations, demonstrating that these are greater than for FinFET transistor designs.

*Index Terms*—Adiabatic logic, Tunnel field-effect transistors, Steep subthreshold slope, Low power.

## I. INTRODUCTION

Very intensive research targeting the reduction of power and energy consumption of complementary metal-oxidesemiconductor (CMOS) electronics circuits and systems has been being conducted during the last decade. The need for ultralow-power and energy-efficient circuits is due to different reasons. The impossibility of further increasing the system complexity because of power density problem of CMOS and the boom of portable devices working from batteries are the main ones [1]. More recently, the arising of IoT or implantable medical devices which eventually use energy harvesting has boosted the activity in the area [2],[3].

The reduction of power and energy has been addressed from different domains, including both software and hardware approximations. Concerning the latter, methodologies and techniques at distinct abstraction levels are possible. At the circuit level, it is well known that reducing the supply voltage is a very powerful way of reducing power. In fact, supply voltage reduction enabled by the scaling of CMOS technologies has significantly reduced power consumption in the past. However, the further scaling of supply voltages to reduce dynamic power while maintaining adequate speed is counterbalanced by the exponential growth of leakage currents. Keeping speed with lower voltage supply requires lowering the threshold voltage of the transistors, which, because of the 60 mV/decade minimum subthreshold slope (*SS*) of CMOS

devices, produces unacceptable off-state leakage currents. This has motivated intensive research into devices with *SS* below the physical limit of CMOS, known as steep slope devices, to achieve better transistor performance at reduced supply voltages [4].

Among them, Tunnel field-effect transistors (TFETs) have been extensively explored [5]-[11]. Several works have shown power benefits for iso-performance or higher performance at iso-power up to moderate operating frequencies [12]-[17]. This is because current TFETs do not reach the high on current values exhibited by CMOS transistors at their nominal supply voltage. Difficulties encountered to simultaneously achieve high I<sub>ON</sub> current and reduced I<sub>OFF</sub> current in TFETs are being investigated to be solved using different approaches [16]-[22]. A completely different approach for low power circuits is quasiadiabatic logic. Adiabatic circuits are operated such that power dissipation in transistor's resistance is almost eliminated and energy stored in circuit capacitances is recovered. The former requires very slow charging and discharging of capacitances and so the speed of adiabatic gates is significantly smaller than in conventional complementary logic gates. However, in order to take advantage of adiabatic operation, power must be dominated by its dynamic component. In other words, power savings are not obtained for very low frequencies. Because of this, the amount by which the supply voltage can be reduced in adiabatic logic is more limited than in their conventional counterparts. In fact, there are very few works on low voltage adiabatic CMOS circuits. In [23] it is shown that they cannot achieve a satisfactory trade-off between energy and operating frequency.

The better performance of TFETs for low voltage suggests it is interesting exploring TFET adiabatic circuits. We believe that combining the adiabatic operating principle and TFETs can lead to ultra-low-power and energy-efficient circuits. Up to our knowledge, just a few papers have addressed this issue. In this paper, we present a comprehensive study that not only investigates suitable circuit topologies for TFETs quasiadiabatic logic gates and provides design guidelines for them but also evaluates power and energy savings achieved. It will also be shown that the use of adiabatic gates in complex circuits provides significant advantages in terms of power consumption compared to conventional static implementations as they do not need to increase the supply voltage to operate at high frequencies.

The rest of the paper is structured as follows. Section II introduces background for this work on both the adiabatic logic style and the TFET devices characteristics. Section III describes the implementation of a widely used adiabatic gate topology with TFETs and proposes novel circuit topologies that solve drawbacks of other previously reported. In Section IV simulation results are discussed at gate level. The design and

evaluation of a complex circuit are presented as a case study in Section V. Finally, some conclusions are given in Section VI.

#### II. BACKGROUND

## A. Adiabatic logic

Adiabatic logic has been used as a technique to design circuits with low power consumption by reducing the exchange of energy between the circuit and the environment. In real circuits, due to the presence of power dissipating elements, such as resistors, this exchange cannot be reduced to zero, although it can be minimized by using ramped power supplies through which energy is stored and recovered from the output node of the circuits. That is, unlike CMOS design styles, in adiabatic logic transitions between 0 and  $V_{DD}$  do not occur abruptly.

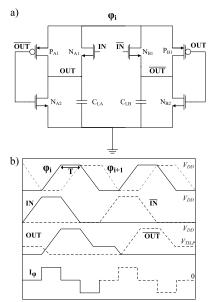

To illustrate the operation of an adiabatic gate, we consider the Positive Feedback Adiabatic Logic (PFAL) [24] buffer in Fig 1a. This topology has been selected since it exhibits the best performance in terms of energy compared to other families of adiabatic circuits [24]. It consists of an adiabatic amplifier, that is, a latch composed of the pair of transistors  $P_A$ - $N_{A2}$  and  $P_B$ - $N_{B2}$ . Logic functionality is implemented by transistors  $N_{A1}$  and  $N_{B1}$ . Other logic functionalities can be obtained by replacing these transistors by the corresponding network and its complement. Note that both the positive and negative outputs are obtained. A ramped power supply ( $\varphi_i$ ) is applied, with the same rising, falling, hold and reset times (see Fig 1b). The cascade connection of this type of gates requires a successive offset of 90° in  $\varphi_i$  for each of the interconnected levels ( $\varphi_{i+1}$  in dashed line in Fig 1b).

When  $\varphi_i$  switches from 0 to  $V_{DD}$ , the output is evaluated according to the inputs (IN and its complement  $\overline{IN}$ ), which are stabilized previously, as shown in Fig 1b. Note that in the first pulse of  $\phi_i$  IN is at a high logic level, driving current through transistor  $N_{A1}$  to charge the output capacitance  $C_{LA}$  (I<sub> $\varphi$ </sub>>0 in Fig 1b). The node  $\overline{OUT}$  remains at a low level because, on the one hand,  $\overline{IN}$  is low, cutting the N<sub>B1</sub> transistor and, on the other hand, OUT is rising together with the power supply, making the  $V_{GS}$  seen by transistor P<sub>B2</sub> transistor practically 0 and, hence, cutting the transistor. For the second cycle of  $\varphi$ , where the inputs have different values (IN='0',  $\overline{IN}$ ='1'), the scenario is the opposite. When  $\varphi_i$  is high the outputs keep their value in order to be evaluated by the next stage with  $\varphi_{i+1}$ . Note that in this scenario  $I_{\omega}=0$ . Transistors  $P_{A1}(P_{B1})$  and  $N_{B2}(N_{A2})$  take care of when  $OUT='1'/\overline{OUT}='0'$ storing the information (OUT='0'/ $\overline{OUT}$ ='1'). Finally,  $\varphi_i$  descends from  $V_{DD}$  to 0. As long as its value remains above the threshold voltage of the P transistor ( $V_{TH,P}$ ), the output will discharge overlapped with  $\varphi_i$ , restoring the energy stored in the output capacitance ( $I_{0} < 0$  in Fig 1). When that value is reached, the P transistor is cut off and with it, the remaining energy in the capacitor is dissipated or reused in the next cycle depending on the value of the inputs.

The total energy dissipated is the sum of three terms: active losses ( $E_{ADL}$ ), those associated with the remaining voltage at the output ( $E_{VT}$ ) and those of leakage ( $E_{LEAK}$ ). In static designs, there is an energy component that decreases with frequency, that of leakage, while the dynamic part (see (1)) is independent of frequency. However, this dynamic energy increases when the switching activity does. In adiabatic circuits, the leakage energy also decreases with frequency and there is remnant energy that

Fig 1. (a) Schematic of a PFAL buffer (b) Waveforms illustrating its operation.

does not vary with frequency, but adiabatic energy losses (dynamic component) do increase with frequency. On one hand, for low frequencies, where the leakage is dominant, there is no reason to expect advantages of adiabatic circuits. On the other hand, for very high frequencies, where the dynamic component dominates, static circuits would be more efficient than adiabatic ones. Thus, it is in an intermediate frequency range that the adiabatic design style can present advantages in terms of efficiency, given that, in those scenarios, its dynamic energy component is below that of the static designs

#### B. Tunnel field-effect transistors

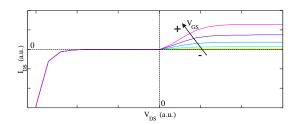

TFETs are one of the most attractive steep SS devices [1]- [7]. Subthreshold swing under 60mV/dec has been experimentally obtained in different material systems [25], [26]. TFETs exhibit distinguishing characteristics with respect to several MOSFETs, including super-linear onset, ambipolarity, enhanced Miller capacitance effect due to the dominance of gate to drain capacitance or asymmetric conduction which are being addressed [27]-[30]. Let us focus on the asymmetric conduction which is relevant for this work. Fig 2 depicts output I-V curves for an N-type TFET device. Differences are evident compared with a MOSFET transistor. TFET behavior is very much unlike for positive and negatives drain to source voltages. It is usual to define the TFET as a unidirectional device, although this is not completely true as it can be observed in the figure. The asymmetric conduction can be more precisely defined as:

Fig 2. I-V characteristic of an N-type TFET.

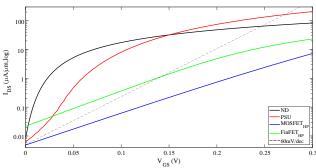

Fig 3.  $I_{DS}$ - $V_{GS}$  characteristics of simulated transistors for  $V_{DS}$ =0.3V.

• Low conduction of the *n*-type (*p*-type) TFET transistors with a moderate negative (positive) drain to source voltage.

• Large current of the *n*-type (*p*-type) TFET transistors for high enough negative (positive) *V*<sub>DS</sub>, due to the forward biasing of the intrinsic *p*-*i*-*n* diode.

Additionally, this behavior is almost independent of  $V_{GS}$ . It occurs both for positive and negative values and for  $V_{GS} = 0$ . The design of circuits using TFETs requires considering, among other non-ideal effects, the impact of p-i-n leakage current. [31]-[33]. As in conventional CMOS technologies, a given TFET device is not competitive for all possible applications. For example, in terms of power, depending on the required operating frequency, different TFETs are more suitable. In this work two predictive TFET models have been used. The first are 20nm AlGaSbInAs heterojunction transistors, which have been developed by Notre Dame University (ND) [33], exhibits ultra-low off current but limitations in terms of speed. The second are 20nm GaSb-InAs heterojunction transistors, which have derived by Pennsylvania State University (PSU) [35], and are advantageous when the operating frequency is the primary concern.

Fig 3 shows drain-source current ( $I_{DS}$ ) versus gate-source voltage,  $V_{GS}$ , (with  $V_{DS}$ =0.3V) for both TFETs and the HP MOSFET and FinFET transistors. Currents have been normalized with respect to the transistor width and have been calculated using minimum length transistors. Clearly, TFETs exhibit larger currents at reduced supply voltage.

## III. IMPLEMENTATION OF ADIABATIC CIRCUITS USING TFETS

This section deals with the design of PFAL adiabatic circuits with TFETs, highlighting the problems that arise when using these devices and proposing a modification of this topology that solves them.

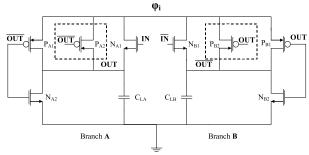

The main difference between the implementation of PFAL circuits in CMOS and tunnel technologies lies in the fact that, given the asymmetrical conduction of TFETs, it is necessary to enable a return path for charge recovery, different from that of injection [38]. Fig 4 shows the modified PFAL TFET-based topology, in which flipped P transistors  $P_{A2}$  and  $P_{B2}$  have been added in each branch for that purpose [38].

#### A. Reverse conduction currents in TFET-based PFAL circuits

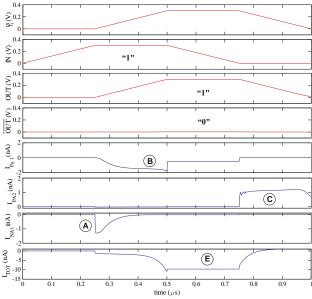

Fig 5 illustrates the operation of branch A of the PFAL buffer in Fig 4 designed with ND transistors, operating at a frequency of 1MHz and with a high voltage level of 0.3V. The figure

Fig 4. Schematic of a TFET-based PFAL buffer [38].

Fig 5. Descriptive waveforms of the PFAL buffer operation for IN='1'.

shows the power supply, the input, the outputs, as well as the currents flowing through transistors  $P_{A1}$ ,  $P_{A2}$ ,  $N_{A1}$  and the total current ( $I_{TOT}$ ) supplied by  $\phi_i$ . To ease the interpretation of the figures, voltages are depicted in red and currents in blue. Note that for these simulations negative currents are drained from the power source whereas positive are recovered.

In Fig 5, the input is at a high level at the rising edge of  $\varphi_i$ , so transistors  $P_{A1}$  and  $N_{A1}$  drive current to the load capacitance  $C_{LA}$  Note that  $N_{A1}$  transistor starts to drive before  $P_{A1}$  because, at the beginning of the rising edge of  $\varphi_i$ , OUT=0 and its  $V_{GS}$  voltage is maximum (mark "A" in Fig 5). As OUT rises, the  $V_{GS}$  voltage of  $N_{A1}$  begins to decrease, while that of  $P_{A1}$  ( $V_{GS} = \overline{OUT} - \varphi_i$ ) becomes larger and, thus, this transistor is the one that provides most of the current to charge  $C_{LA}$  in the final part of the rising edge of  $\varphi_i$  (mark "B" in Fig 5).

As expected, once the output is stabilized at a high level, the current circulating through branch A ( $I_{PA1}+I_{PA2}+I_{NA1}$ ) becomes practically zero. When  $\varphi_i$  starts to fall and triggers the discharge of OUT, the current is recovered mainly through  $P_{A2}$  transistor (mark "C" in Fig 5).

However, reverse conduction currents from a certain negative  $V_{DS}$  value (shown in Fig 2), cause the appearance of a conduction path between  $\phi_i$  and ground through  $P_{A2}$  and  $N_{A2}$  transistors which spoils the adiabatic operation of the circuit.

Fig 6.(a) Schematic of the proposed PFAL buffer topology to avoid reverse currents. (b) Waveforms showing the correct operation of the modified topology.

#### B. Proposed PFAL topology

The origin of the reverse currents appearing on  $P_{A2}$  (and  $P_{B2}$ ) transistor is an excessive negative  $V_{DS}$  voltage when the output OUT ( $\overline{OUT}$ ) is at zero and the power supply is high. To avoid these currents, we propose a modification of the PFAL topology in which this transistor is replaced by two identical ones connected in series. Fig 6a shows this modification, in which  $P_{A2}$  transistor (and  $P_{B2}$  in the other branch) has been replaced by the series connection of transistors  $P_{A21}$  and  $P_{A22}$ . In this way, the total  $V_{DS}$  voltage is distributed among each of the new transistors, so that the reverse current remains within the zone of practically zero currents, avoiding the incorrect operation described above. The proposed solution implies increasing the number of transistors from 8 to 10 (25% of area penalty).

Fig 6b shows waveforms of the operation of the proposed topology. In this case, the evaluation of consecutive logical zero and one in the input is shown. Note that now the current through the two new transistors in series ( $I_{PA21}$  in Fig 6b) exhibits the expected behavior, recovering charge from  $C_{LA}$  on the falling edge of the supply voltage when the output is high (mark "A"). It is now evident that the total current of the power supply ( $I_{TOT}$ ) exhibits an expected behavior, with one part being consumed during charging the output capacitance ( $I_{TOT}$ <0, marks "B") and another part being recovered during the discharge ( $I_{TOT}$ >0, marks "C").

## IV. EVALUATION OF THE PERFORMANCE OF TFET-BASED ADIABATIC GATES

This section compares power consumption and frequency tradeoffs for simple logic gates implemented with adiabatic logic and conventional static logic. Specifically, for adiabatic design, the buffer/inverter described above will be used (Fig 6a), while for static logic an inverter is selected. In these experiments, we consider voltage levels between 0V and 0.3V and a load capacitance at the output of 1fF. This study includes different models of TFETs (ND and PSU described in section II.B), as well as FinFET HP transistors. FinFET HP has been selected at the conventional reference transistor since it achieves the best results among the conventional studied ones, as expected from the data in Table I. Minimum-size transistors for each technology have been considered.

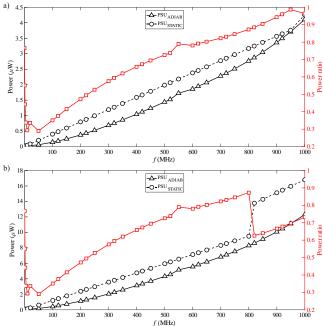

Fig 7a depicts the results obtained for power consumption versus frequency assuming a train of pulses at the input of the adiabatic buffer. The figure shows that the designs based on the proposed topology (ND<sub>PROP</sub> and PSU<sub>PROP</sub>) exhibit power performance around 40 times lower for the lower frequencies (up to 100KHz) than the conventional ones (ND and PSU), due to the elimination of the current flowing through the flipped recovery P transistor. Note that, at low frequencies, the modified design with PSU transistors consumes less power than the original with ND TFETs. This evidences that the proposed topology is necessary to exploit the advantages of ND transistors at low frequencies. However, increasing the frequency will reduce the differences between the results of the original and proposed designs, since current levels of the flipped transistors will be negligible compared to those associated to the charging and discharging of the output capacitance. In addition, the frequency from which PSU transistor design becomes more efficient than ND transistors is reduced from 50MHz to 5MHz.

On the other hand, as shown in Fig 7b, the proposed solutions also offer better performance in terms of energy per operation compared to FinFET HP. Specifically, the proposed design with ND transistors is more efficient up to 30MHz, while the one using PSU transistors exhibits less energy across the entire explored frequency range.

Finally, a comparison has been carried out between the power consumption of adiabatic and conventional static design styles. The results are shown in Fig 7c, which represents the ratio between adiabatic and static circuit consumption (i.e. a ratio less than 1 implies advantages of adiabatic versus static). On the one hand, the advantages of the ND tunnel design are given for low/medium frequencies (between 0.3MHz and 15MHz), exhibiting maximum savings of around 70% at 2MHz. On the other hand, advantages for the PSU tunnel designs are obtained from 0.2MHz, achieving power savings of more than 50% from 5MHz to 100MHz, with a maximum of around 75% at 40MHz. Finally, it should be noted that quite smaller savings are obtained with adiabatic FinFETs (from 10MHz to 100MHz with a maximum around 20% at 50MHz). These results suggest the potential of TFETs for the design of efficient low-voltage adiabatic circuits.

Fig 7. Evaluation of the performance of the original and proposed implementations of the TFET-based adiabatic buffer. Results for a FinFET HP have been also included. (a) Power versus frequency. (b) Energy per operation versus frequency. (c) Power ratio (with respect to static inverters implemented in the same technologies) versus frequency.

## V. CASE STUDY: KOGGE-STONE ADDERS

The power consumption results shown in the previous section considering a pulse train at the gate input, although they provide a starting point for our study, do not correspond to a realistic scenario in which the circuit nodes switch at different frequencies depending on the combination of inputs applied. Thus, as a case study we have evaluated and compared a more complex circuit, an 8-bit Kogge-Stone (KS) adder [40] for both the static and the proposed adiabatic implementations using PSU transistors. Fig 8a shows power consumption of the evaluated adders with  $V_{DD}=0.3V$  considering random sequences at the inputs of the adder (in black). Additionally, to assess if the adiabatic design is more efficient than the static one, power ratio is depicted (red). A ratio less than one means that the adiabatic design consumes less power than the static one. Note that adiabatic implementation is more efficient than static for the entire explored frequency range. The power ratio shows some correspondence with the one obtained at gate level (Fig 7c) in that it presents a minimum around 20MHz, although it is observed that for higher frequency values the adiabatic buffer consumption is higher than that of the static inverter.

One of the main advantages of adiabatic designs over static designs is that there is no need to increase the supply voltage when the logic depth of the circuit increases, which allows significant power savings. This is due to the natural operation of adiabatic logic in a gate-level pipelined fashion. In this sense we have evaluated the connection of three KS adders in series. Fig 8b shows power consumption and power ratio for this architecture. For lower frequencies the behavior is similar to that of isolated adders since the adder network operates with  $V_{DD}$ =0.3V. However, around 800MHz it is observed that the static designs need to increase their supply voltage to 0.4V, so the advantages of adiabatic designs against static ones become even more evident.

#### VI. CONCLUSIONS

The potential of TFETs for low-voltage adiabatic circuits has been explored. A modification of a previously reported TFET adiabatic topology has been proposed. It eliminates a phenomenon associated with the current of the intrinsic p-i-n diode of this type of transistors which limits its performance. Our results show that the proposed topology improves power savings, especially for low operating frequencies. Experiments with two TFETs predictive technologies show significantly larger power savings of TFETs adiabatic gates with respect to conventional MOS technologies ones. The steep slope characteristics of these transistors can be exploited to reduce leakage power without degrading too much current at low voltage and so enabling power savings of adiabatic operation, as it is the case of the ND transistor. Also, it can be exploited to increase the on current at low voltages so that adiabatic losses

Fig 8. Power versus frequency (black) and power ratio (red) for (a) single 8bits Kogge-Stone adder and (b) interconnection of three Kogge-Stone adders.

are reduced which translates in larger power savings even at larger frequencies, as it is the case of the PSU transistor. We have also shown, through the design of a KS adder and a network of KS adders, that the implementation of complex circuits using adiabatic gates can take advantage of the fact that operating frequency at a given supply voltage is independent of logic depth, contrary to static designs.

#### ACKNOWLEDGMENT

This work has been funded by Ministerio de Economía y Competitividad del Gobierno de España with support from FEDER (Project TEC2017-87052-P).

#### REFERENCES

- X. Li, K. Ma, S. George, J. Sampson and V. Narayanan, "Enabling Internet-of-Things: Opportunities brought by emerging devices, circuits, and architectures," 2016 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Tallinn, 2016, pp. 1-6.

- [2] A. S. Adila, A. Husam and G. Husi, "Towards the self-powered Internet of Things (IoT) by energy harvesting: Trends and technologies for green IoT," 2018 2nd International Symposium on Small-scale Intelligent Manufacturing Systems (SIMS), Cavan, 2018, pp. 1-5.

- [3] H. Chapade and R. Zele, "On-chip RF to DC Power Converter for Bio-Medical Applications," 2019 32nd International Conference on VLSI Design and 2019 18th International Conference on Embedded Systems (VLSID), Delhi, NCR, India, 2019, pp. 522-524.

- [4] X. Li, M. S. Kim, S. George, A. Aziz, M. Jerry, N. Shukla, J. Sampson, S. Gupta, S. Datta, V. Narayanan, "Emerging Steep-Slope Devices and Circuits: Opportunities and Challenges," *Springer*. Aug. 2018.

- [5] A. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," Proceedings of the IEEE, vol. 98, no. 12, Dec. 2010.

- [6] A. Seabaugh, "The Tunneling Transistor", *IEEE Spectrum*, vol.2, no.4, pp.55-62, Oct. 2013.

- [7] H. Lu and A. Seabaugh, "Tunnel Field-Effect Transistors: State-of-the-Art", J. of the Electron Device Society, vol.2, no.4, pp.44-49, Jul. 2014.

- [8] Nikonov, Dmitri E., and Ian A. Young. "Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits." *IEEE Journal on Exploratory Solid-State Computational Devices and Circuits*, vol. 1 pp. 3-11, Dec. 2015.

- [9] D. Esseni, M. Guglielmini, B. Kapidani, T. Rollo and M. Alioto, "Tunnel FETs for Ultralow Voltage Digital VLSI Circuits: Part I—Device–Circuit Interaction and Evaluation at Device Level," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 22, no. 12, pp. 2488-2498, Dec. 2014.

- [10] M. Alioto and D. Esseni, "Tunnel FETs for Ultra-Low Voltage Digital VLSI Circuits: Part II–Evaluation at Circuit Level and Design Perspectives," in *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, vol. 22, no. 12, pp. 2499-2512, Dec. 2014.

- [11] U. E. Avci, D.H. Morris and I.A. Young, "Tunnel Field-Effect Transistors: Prospect and Challenges", *IEEE Journal of the Electron Device Society*, vol. 3, no. 3, pp. 88-95, Jan. 2015.

- [12] A.M. Ionescu, H. Riel: "Tunnel field-effect transistors as energy-efficient electronic switches", *Nature*, no. 479, pp. 329–337, 2011.

- [13] H. Chenming; P. Patel; A. Bowonder; J. Kanghoon et al., "Prospect of tunneling green transistor for 0.1V CMOS," *Electron Devices Meeting*, *IEEE International*, pp.16.1.1/4, 2010.

- [14] H. Liu, S. Datta, V. Narayanan, "Steep switching tunnel FET: a promise to extend energy-efficient roadmap for post-CMOS digital and analog/RF applications", *Symp. on Low Power and Design*, 2013.

- [15] S. Datta, R. Bijesh, H. Liu, D. Mohata and V. Narayanan, "Tunnel Transistors for Low Power Logic", *IEEE Compound Semiconductor Integrated Circuit Symposium*, pp. 1-4, Oct. 2013.

- [16] J. Núñez, M.J. Avedillo, "J. Núñez and M. J. Avedillo, "Comparison of TFETs and CMOS Using Optimal Design Points for Power–Speed Tradeoffs," *IEEE Trans. on Nanotech.*, vol.16, no.1, pp. 83-89, Jan. 2017.

- [17] J. Núñez, M.J. Avedillo, "Comparative Analysis of Projected Tunnel and CMOS Transistors for Distinct Logic Applications Areas", *IEEE Transactions on Electron Devices*. vol. 63, no. 12, pp. 5012-5020, 2016.

- [18] E.A. Casu, W.A. Vitale, N. Oliva1, T. Rosca, A. Biswas, C. Alper, A. Krammer, G.V. Luong, Q.T. Zhao, S. Mantl, A. Schuler, A. Seabaugh and

A.M. Ionescu, "Hybrid Phase-Change – Tunnel FET (PC-TFET) Switch with Subthreshold Swing < 10mV/decade and sub-0.1 body factor: digital and analog benchmarking", IEEE Electron Devices Meeting, pp. 508-511, 2016

- [19] W.A. Vitale, E. A. Casu, A. Biswas, T. Rosca, C. Alper, A. Krammer, G. V. Luong, Q.T. Zhao, S. Mantl, A. Schüler A. M. Ionescu "A Steep-Slope Transistor Combining Phase-Change and Band-to-Band-Tunneling to Achieve a sub-Unity Body Factor" *Scientific Reports*, vol. 7, n. 355. 2017.

- [20] Chowdhury, Nadim, M. Farhaduzzaman Azad, S, Khosru, Q.D.M., "Negative Capacitance Tunnel Field Effect Transistor: A Novel Device with Low Subthreshold Swing and High ON Current". *ECS Transactions*. 58. 2014.

- [21] M. Kobayashi, K. Jang, N. Ueyama and T. Hiramoto, "Negative Capacitance for Boosting Tunnel FET performance," *IEEE Transactions* on Nanotechnology, vol. 16, no. 2, pp. 253-258, March 2017.

- [22] A. Saeidi; F. Jazaeri; I. Stolichnov; G. V. Luong; Q.-T. Zhao et al. : Effect of hysteretic and non-hysteretic negative capacitance on tunnel FETs DC performance; Nanotechnology. 2018-01-26.

- [23] S. Houri, G. Billiot, M. Belleville, A. Valentian and H. Fanet, "Limits of CMOS Technology and Interest of NEMS Relays for Adiabatic Logic Applications," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 62, no. 6, pp. 1546-1554, June 2015.

- [24] Teichmann, Philip "Adiabatic Logic, Future Trend and System Level Perspective", XVII, Springer; 2012.

- [25] S. O. Koswatta, S. J. Koester, and W. Haensch, "On the possibility of obtaining MOSFET-like performance and sub-60-mV/dec swing in 1broken-gap tunnel transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 12, pp. 3222–3230, Dec. 2010.

- [26] D. Sarkar, X. Xie, W. Liu, W. Cao, et al., "A subthermionic tunnel fieldeffect transistor with an atomically thin channel", *Nature*, vol. 526, pp. 91-95, October 2015.

- [27] S. Mookerjea, R. Krishnan, S. Datta, and V. Narayanan, "On enhanced Miller capacitance effect in interband tunnel transistors," *IEEE Electron Device Lett.*, vol. 30, no. 10, pp. 1102–1104, Oct. 2009.

- [28] Mukundrajan, R., Cotter, M., Bae, S., et al., 'Design of energy-efficient circuits and systems using tunnel field effect transistors', *IET Circuits Devices Syst.*, 2013, 7, (5), pp. 294–303.

- [29] D.H. Morris, U.E Avci, R. Rios and I.A Young, "Design of low voltage Tunneling-FET logic circuits considering asymmetric conduction characteristics", *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, Vol. 4, No. 4, pp380388, Dec 2014.

- [30] N. Dagtekin and A. Mihai Ionescu, "Impact of Super-Linear Onset, Off-Region Due to Uni-Directional Conductance and Dominant CGD on Performance of TFET-Based Circuits," *IEEE Journal of the Electron Devices Society*, vol. 3, no. 3, pp. 233-239, May 2015.

- [31] G. V. Luong et al., "Strained Silicon Complementary TFET SRAM: Experimental Demonstration and Simulations," in *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 1033-1040, 2018.

- [32] Y. Lee *et al.*, "Low-Power Circuit Analysis and Design Based on Heterojunction Tunneling Transistors (HETTs)," in *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 9, pp. 1632-1643, Sept. 2013.

- [33] J. Núñez and M. J. Avedillo, "Reducing the Impact of Reverse Currents in Tunnel FET Rectifiers for Energy Harvesting Applications," in *IEEE Journal of Electron Devices Soc.*, vol. 5, no. 6, pp. 530-534, Nov. 2017.

- [34] H. Lu T. Ytterdal, A. Seabaugh, "Universal TFET model". nanoHUB.

- [35] H. Liu; V. Saripalli; V. Narayanan; S. Datta (2014), "III-V Tunnel FET Model 1.0.0," https://nanohub.org/resources/21012.

- [36] W. Zhao and Y. Cao, "New generation of predictive technology model for sub-45nm design exploration", Proc. 7th Int. Symp. Quality Electronic Design, 2006.

- [37] Vandenberghe, William G. et al., "Figure of merit for and identification of sub-60 mV/decade devices", *Applied Physics Letters*, vol. 102, id. 013510. 2013.

- [38] J. Núñez and M. J. Avedillo, "Comparison of TFETs and CMOS Using Optimal Design Points for Power–Speed Tradeoffs," in *IEEE Transactions on Nanotechnology*, vol. 16, no. 1, pp. 83-89, Jan. 2017.

- [39] J. Liu, M. B. Clavel and M. K. Hudait, "TBAL: Tunnel FET-Based Adiabatic Logic for Energy-Efficient, Ultra-Low Voltage IoT Applications," *IEEE Journal of the Electron Devices Society*, vol. 7, pp. 210-218, 2019.

- [40] P. M. Kogge and H. S. Stone. A parallel algorithm for the efficient solution of a general class of recurrence equations. *IEEE Transactions on Computers*, C-22(8):786–793, Aug 1973.