# TESE DE DOUTORAMENTO

# DEVELOPMENT OF ELECTRONICS FOR THE VELO UPGRADE DETECTOR

Antonio Fernández Prieto

ESCOLA DE DOUTORAMENTO INTERNACIONAL

PROGRAMA DE DOUTORAMENTO EN INVESTIGACIÓN EN TECNOLOXÍAS DA INFORMACIÓN

SANTIAGO DE COMPOSTELA 2020

**Pablo Vázquez Regueiro**, Profesor contratado Doutor da Universidade de Santiago de Compostela na Área de Física de Partículas.

#### **FAI CONSTAR**:

Que a memoria titulada "Development of electronics for the VELO upgrade detector." foi realizada por Antonio Fernández Prieto baixo a miña supervisión no departamento de física de partículas da Universidade de Santiago de Compostela. Así mesmo, expreso a miña conformidade co mesmo e autorizo a súa presentación ante a comisión examinadora do Programa de Doutoramento en Investigación en Tecnoloxías da Información, constituíndo así a Tese de Doutoramento para optar ao Grao de Doutor en Enxeñaría.

July 30, 2020

Asdo. Pablo Vázquez Regueiro

Asdo. Antonio Fernández Prieto

# Dedicated to the memory of my father Antonio Fernández Gómez

"Aut viam inveniam aut faciam."

Hannibal Barca

"No es sabio el que sabe donde está el tesoro, sino el que trabaja y lo saca."

Francisco de Quevedo

# **Acknowledgments**

There are many people and institutions that I would like to thank for helping me. I hope not to leave anybody out, to all my sincere gratefulness.

I would like to start manifesting my gratitude to my supervisor Pablo Vázquez for his advice and patience, this thesis won't be possible without him.

I am pleased to be part of an extraordinary team as it is the VELO and LHCb group. It is extraordinary not only from the technical point of view but also on the personal level, as it was proven in the coronavirus crisis by creating the HEV [1]. I would also like to thank all VELO group. Special thanks to Karol Hennessy, who always helped me since the first moment I arrive at CERN. But, how can I forget the rest of the VELO people with whom we share a lot of work: Jan Buytaert, Paula Collins, Martin Van Beuzekom, Kristof De Bruyn, Dónal Murray and many others. I also want to thank the LHCb online CNRS and CPPM teams: Guillaume Vouters, Federico Alessio, Frederic Hachon, Paolo Durante, Luis Granado Cardoso and many others for their support and their prompt answers.

Last but not least, a special mention for the USC LHCb hardware team from whom I learned a lot, this is a well-balanced group where all the personal skills are complemented with the rest of the team: Abraham Gallas (he can get you anything), Pablo Vázquez (he will always think a new smart idea), Edgar Lemos (the tester and now the ambassador at CERN), Eliseo Pérez (Our "bonding man" and also a bit McGyver he only needs duct tape and carboard to build a cooling system), Antonio Pazos (for whom there is no small footprint), Efrén Rodriguez (the rookie of the team) and Marcos Seco (even though he is not a hardware guy, he is always helping around and giving me more IPs).

I have to thank the Spanish Ministry of Economy and Competitiveness for funding my research.

#### ANTONIO FERNÁNDEZ PRIETO

Non quero esquecerme tampouco de todos os compañeiros cos que compartín o piso de Saint Genis Eliseo, Edgar, Julián, María, Antonio Romero, Miguel, Miriam, Carlos Vázquez, Óscar Boente, Bea, Pablo Baladrón e Asier. Mencionar tamén a todos os habituais das pausas para o café non citados antes: Juán, Cibrán, Nestor.

Sei que me queda moita xente no tinteiro coa que non tiven o pracer de traballar pero grazas a todos os membros do IGFAE por axudarme sempre que o precisei.

No terreo persoal quero agradecer principalmente a miña nai, Fina, que sempre me apoiou e a quen lle debo todo. Quero acordarme tamén dos meus amigos de Narón Alex, Iván e Adrián.

Antonio.

# **Contents**

| 1 | Intr | roduction 1                                                           |     |  |

|---|------|-----------------------------------------------------------------------|-----|--|

|   | 1.1  | Thesis content                                                        | 2   |  |

|   |      |                                                                       |     |  |

| 2 | The  | Large Hadron Collider and Large Hadron Collider beauty (LHCb)         |     |  |

|   | Exp  | eriment                                                               | 3   |  |

|   | 2.1  | The Large Hadron Collider (LHC)                                       | 3   |  |

|   |      | 2.1.1 LHC filling schemes                                             | 5   |  |

|   | 2.2  | The LHCb Experiment                                                   | 7   |  |

|   | 2.3  | The LHCb upgrade                                                      | 12  |  |

|   |      | 2.3.1 LHCb trigger and readout upgrade                                | 13  |  |

|   |      | 2.3.2 LHCb on detector hardware upgrade                               | 15  |  |

|   |      |                                                                       |     |  |

| 3 | VEr  | rtex LOcator (VELO) upgrade                                           | 21  |  |

|   | 3.1  | Planar silicon sensors                                                | 22  |  |

|   | 3.2  | VeloPix Front-End (FE) Application Specific Integrated Circuit (ASIC) | 23  |  |

|   |      | 3.2.1 VELO FE data framing                                            | 26  |  |

|   |      | 3.2.1.1 Pixel data                                                    | 26  |  |

|   |      | 3.2.1.2 Special frames                                                | 27  |  |

|   |      | IDLE frame                                                            | 28  |  |

|   |      | Sync frame                                                            | 29  |  |

|   |      | Bunch ID frame                                                        | 29  |  |

|   |      | 3.2.2 Timing and Fast Control (TFC) command response                  | 29  |  |

|   | 3.3  | On-detector electronics                                               | 30  |  |

|   |      |                                                                       | 2.1 |  |

#### Antonio Fernández Prieto

|   |     | 3.3.2   | High-speed data tapes                                          | 32 |

|---|-----|---------|----------------------------------------------------------------|----|

|   |     | 3.3.3   | Vacuum feedthrough board and Opto-Power Board                  | 33 |

|   | 3.4 | Coolin  | g                                                              | 34 |

|   | 3.5 | Mecha   | nics and RF foil                                               | 35 |

| 4 | VEI | .O upgr | rade Off-Detector Electronics                                  | 37 |

|   |     |         | 4.0.0.1 LHCb VELO data taking operation                        | 39 |

|   | 4.1 | PCIe40  | )                                                              | 41 |

|   | 4.2 | LHCb    | VELO TELL40 firmware                                           | 43 |

|   |     | 4.2.1   | Low Level Interface (LLI)                                      | 44 |

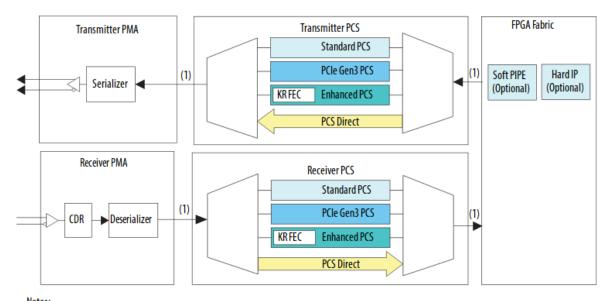

|   |     |         | 4.2.1.1 Intel Arria 10 Transceiver Native PHYsical layer (PHY) |    |

|   |     |         | overview                                                       | 44 |

|   |     |         | 4.2.1.2 VELO specific Physical Medium Attachment (PMA)         | 47 |

|   |     |         | 4.2.1.3 VELO specific Physical Coding Sublayer (PCS)           | 47 |

|   |     | 4.2.2   | TFC                                                            | 48 |

|   |     | 4.2.3   | Pre-Router                                                     | 51 |

|   |     | 4.2.4   | Router                                                         | 53 |

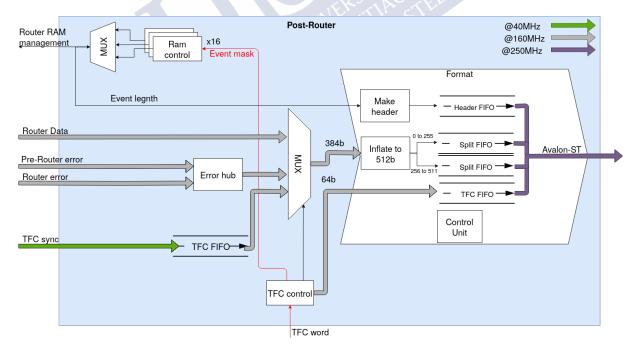

|   |     | 4.2.5   | Post-Router                                                    | 56 |

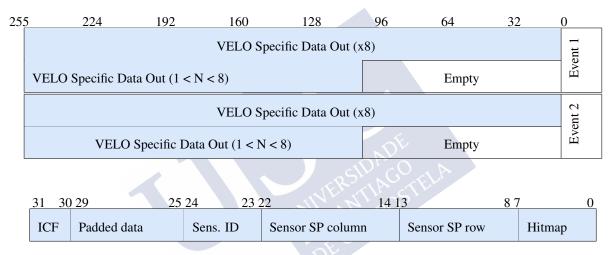

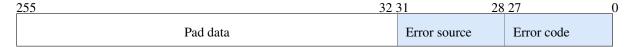

|   |     |         | 4.2.5.1 Data processing output format                          | 59 |

|   |     | 4.2.6   | Isolated Cluster Flagging (ICF)                                | 61 |

|   |     | 4.2.7   | Clustering                                                     | 61 |

|   |     | 4.2.8   | Event ID                                                       | 62 |

|   |     | 4.2.9   | MiniDAQ output (Multi Event Package (MEP))                     | 63 |

|   |     |         | 4.2.9.1 Event packaging and multiple fragment packages         | 64 |

|   |     | 4.2.10  | TELL40 error handling                                          | 65 |

|   |     |         | 4.2.10.1 LHCb framework error handling                         | 65 |

|   |     |         | 4.2.10.2 VELO error handling                                   | 67 |

|   |     | 4.2.11  | ASIC Identification                                            | 68 |

|   |     | 4.2.12  | Monitoring                                                     | 70 |

|   |     |         | 4.2.12.1 LLI Base Address Register (BAR) (BAR2)                | 70 |

|   |     |         | 4.2.12.2 General purpose BAR (BAR0)                            | 72 |

|   |     | 4.2.13  | Resources                                                      | 73 |

| Con | tents |

|-----|-------|

|     | 73    |

|   |      | 4.2.14 Cl  | ocking                                                       | 73  |

|---|------|------------|--------------------------------------------------------------|-----|

|   |      | 4.2.15 LF  | ICb VELO bypass                                              | 75  |

|   |      | 4.2.16 Fu  | ture developments                                            | 77  |

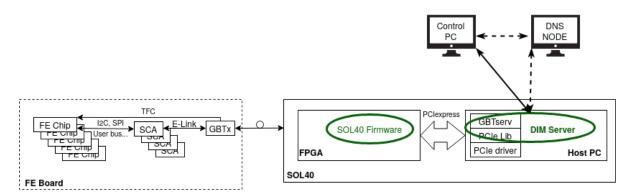

|   | 4.3  | LHCb VE    | LO control and timing distribution firmware (SOL40)          | 80  |

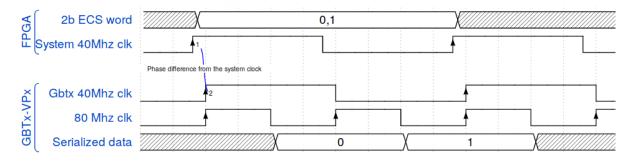

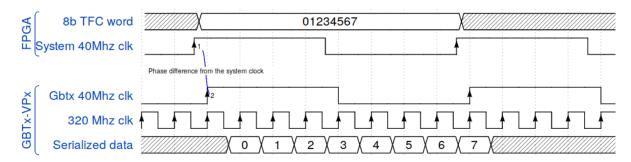

|   |      | 4.3.1 Ve   | loPix Experiment Control System (ECS) link                   | 82  |

|   |      | 4.3        | 3.1.1 VELO interface board BAR0                              | 84  |

|   |      | 4.3        | 3.1.2 VELO FE transmission and reception operation           | 85  |

|   |      | 4.3.2 Ve   | loPix TFC link                                               | 86  |

|   | 4.4  | LHCb con   | trol software                                                | 87  |

| 5 | Firn | nware deve | lopment and hardware validation.                             | 91  |

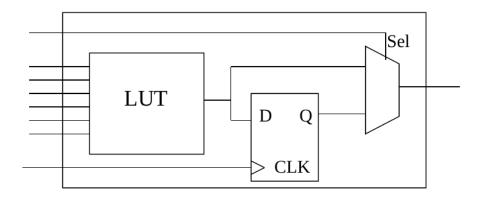

|   | 5.1  | What is a  | Field Programmable Gate Array (FPGA)?                        | 91  |

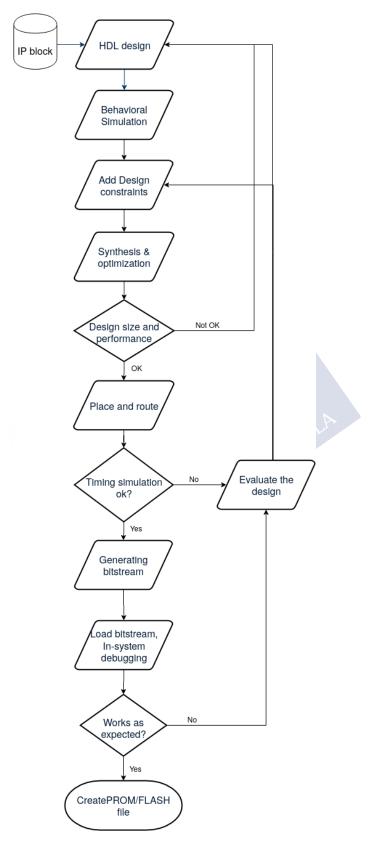

|   | 5.2  | Firmware   | design flow                                                  | 93  |

|   |      | 5.2.1 Mo   | odelSim/QuestaSim simulation                                 | 96  |

|   |      | 5.2.2 Int  | rel/Altera Quartus design environment                        | 96  |

|   |      | 5.2        | 2.2.1 Qsys                                                   | 96  |

|   |      | 5.2        | 2.2.2 Chip Planner                                           | 97  |

|   |      | 5.2        | 2.2.3 Timequest                                              | 97  |

|   |      | 5.2        | 2.2.4 Hardware validation tools                              | 97  |

|   |      | 5.2.3 Xi   | linx "ISE" and "Vivado" design environments                  | 98  |

|   |      | 5.2        | 2.3.1 Intellectual Property core (IP) catalog and integrator | 99  |

|   |      | 5.2        | 2.3.2 Timing tools                                           | 99  |

|   |      | 5.2        | 2.3.3 Hardware manager                                       | 99  |

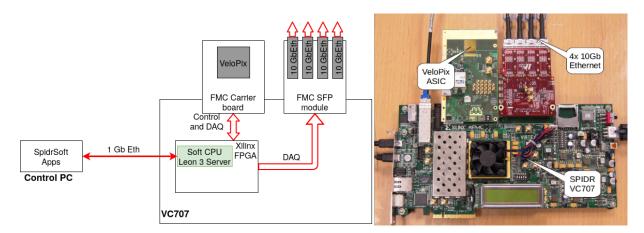

|   | 5.3  | Speedy PI  | xel Detector Readout (SPIDR) readout system                  | 99  |

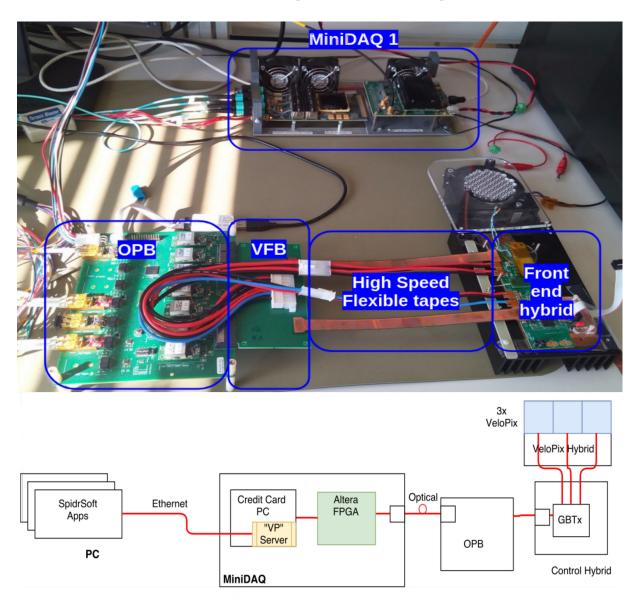

|   | 5.4  | MiniDAQ    | 1 readout system                                             | 100 |

|   |      | 5.4.1 Mi   | iniDAQ server                                                | 102 |

|   |      | 5.4.2 Mi   | iniDAQ1 Data AcQquisition (DAQ)                              | 103 |

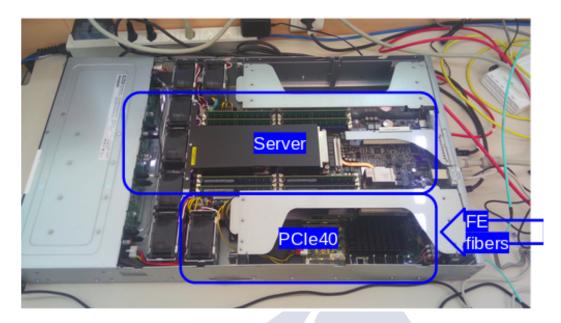

|   | 5.5  | MiniDAQ    | 2 readout system                                             | 103 |

|   | 5.6  | MiniDAQ    | 3 readout system                                             | 104 |

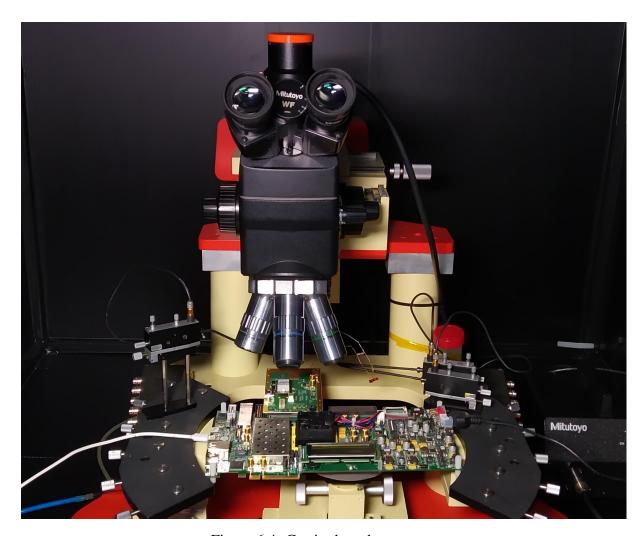

|   | 5.7  | Hardware   | validation                                                   | 105 |

|   | 5.8  | VELO Tes   | ets with beam particles                                      | 115 |

| 6 | Test | benches fo | r production quality assurance                               | 119 |

#### Antonio Fernández Prieto

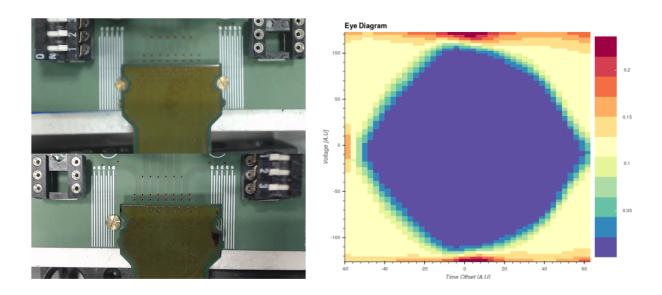

|    | 6.1         | High speed tapes test bench     |                                                                        |     |

|----|-------------|---------------------------------|------------------------------------------------------------------------|-----|

|    | 6.2         | High v                          | oltage tapes test bench                                                | 122 |

|    | 6.3         | VeloPi                          | x Carrier board Quality Assurance (QA)                                 | 122 |

| 7  | Con         | clusions                        | s and future work                                                      | 125 |

| 8  | Sum         | mary o                          | f the thesis                                                           | 127 |

|    | 8.1         | Contex                          | t                                                                      | 127 |

|    | 8.2         | LHCb                            | upgrade                                                                | 130 |

|    | 8.3         | The LI                          | HCb VELO upgrade                                                       | 133 |

|    |             | 8.3.1                           | Underground electronics                                                |     |

|    |             | 8.3.2                           | Electronics at the ground level                                        | 135 |

|    |             |                                 | 8.3.2.1 VELO control firmware                                          | 137 |

|    |             |                                 | 8.3.2.2 VELO readout firmware                                          | 137 |

|    |             | 8.3.3                           | QA firmware                                                            | 138 |

|    |             |                                 | 8.3.3.1 Bypass firmware                                                | 138 |

|    |             |                                 | 8.3.3.2 Test-bench for High Speed and High Voltage tapes               | 139 |

| 9  | Resu        | ımo da                          | tese en galego                                                         | 141 |

|    | 9.1         | Contex                          | to                                                                     | 141 |

|    | 9.2         | 0.2 Mellora do experimento LHCb |                                                                        |     |

|    | 9.3         | Mellor                          | a do detector de vértices do LHCb                                      | 147 |

|    |             | 9.3.1                           | Electrónica na caverna                                                 | 148 |

|    |             | 9.3.2                           | Electrónica na superficie do experimento                               | 150 |

|    |             |                                 | 9.3.2.1 Firmware de control do VELO                                    | 152 |

|    |             |                                 | 9.3.2.2 Firmware de adquisición de datos do VELO                       | 152 |

|    |             | 9.3.3                           | Firmware para controis de calidade e desenvolvemento do hardware       | 153 |

|    |             |                                 | 9.3.3.1 Firmware de bypass                                             | 154 |

|    |             |                                 | 9.3.3.2 Banco de probas dos cables de alta velocidade e alta tensión . | 154 |

| A  | Old         | TELL4                           | 0 output data format                                                   | 155 |

|    | <b>A.</b> 1 | Old da                          | ta formats                                                             | 155 |

| Bi | bliogi      | raphy                           |                                                                        | 157 |

|                 | Contents |

|-----------------|----------|

| Acronyms        | 162      |

| List of Figures | 169      |

| List of Tables  | 175      |

# **CHAPTER 1**

# INTRODUCTION

The Standard Model (SM) of particle physics is a theory that describes the electromagnetic, weak and strong interactions, explaining most of the phenomena observed in nature. The SM declares that the material in the universe is built of two types of particles: fermions and bosons. Fermions, which comprise all quarks and leptons, are the building blocks of matter and they follow the Pauli exclusion principle. On the other hand, bosons are the force carriers that act as the "glue" that holds matter together, they carry the electromagnetic, strong, and weak forces among fermions.

Unfortunately, the SM can not formulate some phenomena, such as: the gravitational interactions, why do the 3 flavour families (explained in the previous paragraph) exist?, why this structure? or how to explain the asymmetry between matter and antimatter in the universe, etc. This drives many New Physics models along the last years and also high energy physics experiments to explore these models.

In the area nearby Geneva (Switzerland) is the seat of the European Organization for Nuclear Research (CERN) that holds several high energy physics experiments. One of CERN facilities is the LHC, a 27 km circular accelerator designed to collide protons at a nominal centre of mass energy of  $\sqrt{s} = 14 TeV$ . The LHC has 4 interaction points, located where the four experiments are built ATLAS, CMS, LHCb and ALICE.

This thesis is intended to be a guide that allows the understanding of the LHCb VELO upgrade electronics from both hardware and firmware point of view. It will also explain the integration of this system with the rest of the LHCb sub-detectors. The work presented in this thesis is the fruit of a large collaboration that goes beyond VELO collaboration and also

involves common developments for the whole LHCb experiment. However, this thesis does not cover other minor tasks carried out within the framework of VELO upgrade, but which were not the central tasks of the thesis: shifts on the LHCb experiment, total ionizing dose and single event effects tests.

Instituto Galego de Física de Altas Enerxías (IGFAE) group, to which I belong since the beginning of this thesis, is involved in the design of the back-end readout and control firmware, testing of the front-end ASIC, validation and integration of the different electronic components of the VELO system. IGFAE is also involved in the production and QA for the VeloPix carrier board used for the testing of the front-end ASIC, high speed and high voltage flexible tapes.

#### 1.1 Thesis content

This thesis is organized as follows:

- **chapter 2** This chapter describes the LHC operation and the different filling schemes, which is important to understand and design the readout electronics of the LHCb VELO upgrade that will operate at the LHC rate. This chapter also describes the reason and the LHCb experiment, the weakness and needs of the original experiment that motivated a major upgrade during the LHC Long Shutdown 2 (LS2) that is taking place during 2019-2020.

- **chapter 3** This chapter shows a complete overview of the LHCb VELO upgrade that is going to be installed in the pit during LS2 of the LHC with a special emphasis on the electronics design.

- **chapter 4** This chapter describes the design of the electronics placed at the surface LHC intersection point 8, LHCb surface.

- **chapter 5** This chapter explains, chronologically, the different setups used for the design of the VELO upgrade electronics, culminating with a VELO test beam campaign in October 2018. This chapter also covers the methodology followed for the design of the firmware.

- **chapter 6** This chapter gathers all the setups designed at IGFAE to warranty the quality of the assembly components in which Santiago's group was involved.

# CHAPTER 2

# THE LARGE HADRON COLLIDER AND LHCB EXPERIMENT

#### 2.1 The LHC

The world largest particle collider, LHC [2] is hosted by the CERN. It is placed in the surrounding area of Geneva (Switzerland). The LHC is a circular collider of 27km built in the tunnels of the old LEP collider, placed between 45 m and 170 m under the ground level.

The particle acceleration mechanism is performed in several stages and it is supported by smaller accelerators. The LHC can accelerate different kinds of Ions, such as nuclei of lead, argon or xenon atoms. However, the most commonly used particles are the protons. In the case of protons, the acceleration mechanism starts by extracting them from a simple bottle of hydrogen gas. The extraction is performed by a duoplasmatron which consists of a metal cylinder with an electrical field applied, allowing the removal of the electrons present in the hydrogen. At this point, the protons leave the Duoplasmatron with 1.4% the speed of light (~ 4000 km/s) and enter in a series of accelerator stages: A 50 MeV LINear particle ACcelerator (LINAC), 1.4 GeV Proton Synchrotron Booster (PSB), 25 GeV Proton Synchrotron (PS), 450 GeV Super Proton Synchrotron (SPS).

Once the protons are accelerated at the SPS, they are finally transferred to the two beam pipes of the LHC, where they reach their maximum energy of 6.5 TeV per beam pipe and then they collide inside the four detectors present at the LHC ring (ALICE, ATLAS, CMS and LHCb) with an energy of 14 TeV at the centre of mass and a 30 MHz inelastic collision rate. The acceleration

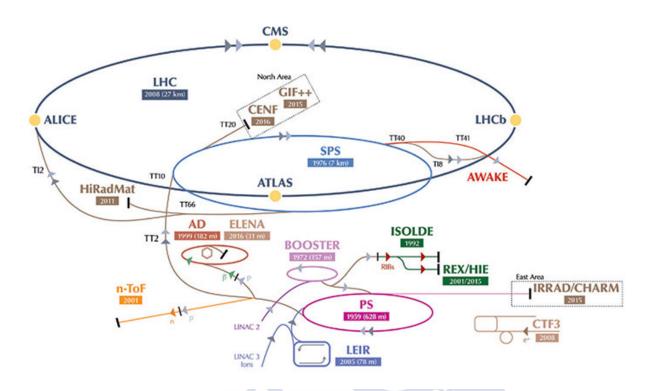

Figure 2.1: LHC complex detector.

of the particles is achieved by using sixteen radio-frequency cavities distributed along the ring. However, the radio-frequency cavities accelerate the protons in a straight line. Thus, to maintain the protons, it is needed to bend the trajectory of the protons by using Niobium-Titanium (Nb-Ti) superconducting dipole magnets that have a nominal bending field of 8.65 T and operate below 1.9 K in static baths of pressurized super-fluid helium.

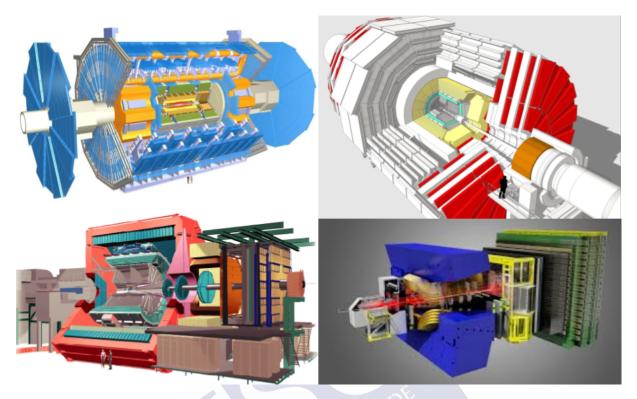

Each detector has its own physics target. While ATLAS [3] and CMS [4] are general purpose detectors, with a large physics programme, designed for the study of collisions that produce a high transverse momentum particles, the ALICE experiment [5] is devoted to heavy ion studies resulting from nucleus-nucleus collisions taken in the LHC lead special runs. Finally, the LHCb experiment [6], which is the frame of the content of this thesis (see section 2.2), was originally devoted to the CP violation and rare decays study. But, thanks to the excellent performance of the detector, the LHCb collaboration is able to deploy a larger physics program.

CERN experiments are not only the four shown above. There are multitude of small detectors placed along the LHC and the other pre-acelerators. The LHC also hosts TOTEM and LHCf experiments that focus on the forward particles and they are placed close to CMS and ATLAS re-

Figure 2.2: (Top left) ATLAS Experiment, (Top right) CMS experiment, (Bottom left) ALICE experiment, (bottom right) LHCb experiment.

spectively. MoEDAL, which is also placed in the LHC (around LHCb VELO), is used to search for a hipothetical particle called magnetic monopole. As shown in Figure 2.1, other experiments like a Radioactive Ion Beam facility (ISOLDE), neutron Time Of Flight (nTOF), fixed-target experiments (COMPASS, NA61, NA62, etc.) are placed along the rest of the accelerator complex. An Antiproton Decelerator (AD) is shown in Figure 2.1. It is used in combination with a new decelerator called ELENA to serve the experiments that study antimatter (AlPHA, ASACUSA, ATRAP and BASE).

# 2.1.1 LHC filling schemes

As it has been mentioned above, the LHC particle acceleration complex has multiple steps previous to the interaction of the two opposite beams. Due to the construction of the different accelerators, the beams are not a constant flow of accelerated particles, nor evenly distributed along time. The distribution of these particles with time is the so-called filling scheme of the LHC. The particles travelling the LHC are gathered in bunches, where the minimum separation

#### Antonio Fernández Prieto

between the two colliding bunches is 25 ns.

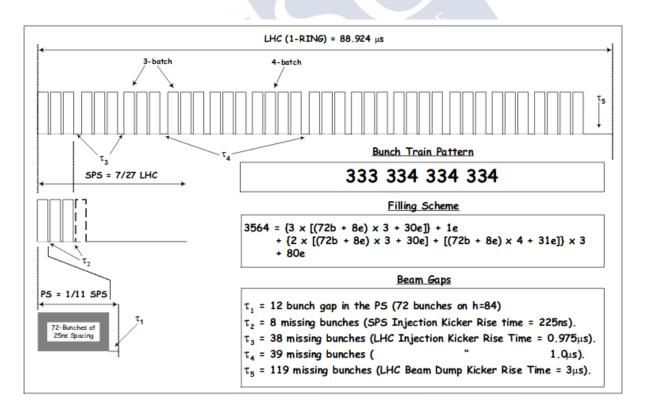

These schemes have several constraints by the construction of the LHC:

- LHC clock that runs at  $\sim 40 \, \mathrm{MHz}^1$ .

- LHC ring length of 27.6km, which combined with the previous point, gives a theoretical maximum number of bunches present at the ring of 3564.

- $\bullet$  The LHC injection also applies several constraints: a beam dump gap of at least 3  $\mu s$

$<sup>^{1}</sup>$ The actual LHC clock frequency can vary between 40.0784 and 40.0789 MHz, but as a simplification, in this thesis, these clocks are referred as 40 MHz or a multiple of it, for example, 160 MHz clocks should be  $\sim$ 160.3125 MHz.

Figure 2.3: 25 ns LHC Filling scheme.

to allow for the rise time of the dump "kicker" magnet<sup>2</sup>, space between adjacent batches injected into the LHC must be greater than the rise time of the LHC injection "kicker" magnets  $(0.95\mu s)$  and the LHC injection "kicker" flat top cannot exceed  $7.86 \mu s$ .

A filling scheme can vary with the particles present in the LHC [7] (75 ns, 43 bunch, Ions scheme, etc.), however, the most commonly used and also the most demanding in terms of frequency is the 25 ns filling scheme that uses 2808 of the 3564 slots, as can be seeing in Figure 2.3.

The coincidence of the beams in the four experiments could have four scenarios: beambeam, beam-empty, empty-beam, empty-empty. Table 2.1 shows the number of beam-beam collisions on each interaction point per orbit<sup>3</sup> for the 25 ns filling scheme. The different number of collisions is caused by the different gaps in the filling scheme. The number of collisions of ATLAS and CMS interaction points is coincident because they are built on opposite sides of the LHC ring, while ALICE and LHCb are not symmetric and thus they have a different number of collisions. The number of collisions delivered is maximized for ATLAS and CMS, giving an average rate of collisions ~30 MHz.

| <b>Interaction Point (experiment)</b> | Number of collisions |

|---------------------------------------|----------------------|

| IP1 (ATLAS)                           | 2808                 |

| IP2 (ALICE)                           | 2736                 |

| IP5 (CMS)                             | 2808                 |

| IP8 (LHCb)                            | 2622                 |

Table 2.1: Number of collisions for the 25 ns filling scheme in the four interaction points.

# 2.2 The LHCb Experiment

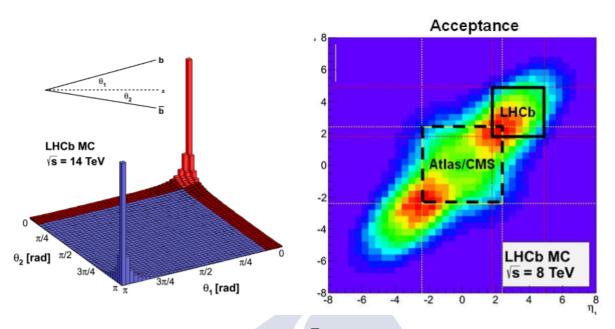

In the proton-proton collision mode, the LHC produces a huge amount of  $b \bar{b}$  pairs per second in the forward and backward direction of the beams. The LHCb detector [6] was designed as

<sup>&</sup>lt;sup>2</sup>This type of magnets are used in the injection and extraction stage because they minimize the beam loss and they are very precise in terms of trajectory, phase and space. These magnets are a type of dipoles that can quickly switch a particle beam between paths. At injection, they merge the circulating beam with the incoming one by appending the comming in particles after the circulating bunches. At dumping, it does the opposite by ejecting the entire bunch of protons.

<sup>&</sup>lt;sup>3</sup>LHC orbit is a full loop; in other words, the entire filling scheme time.

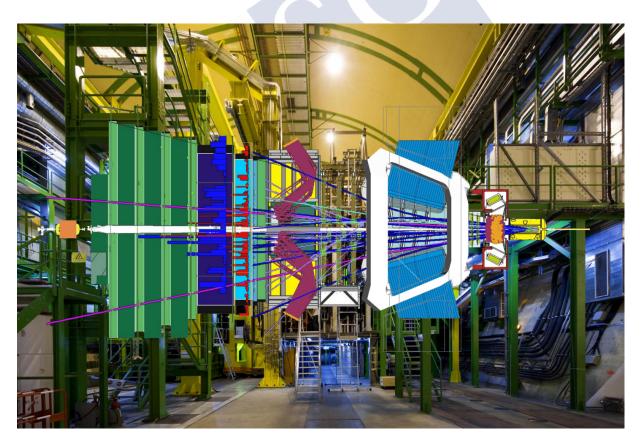

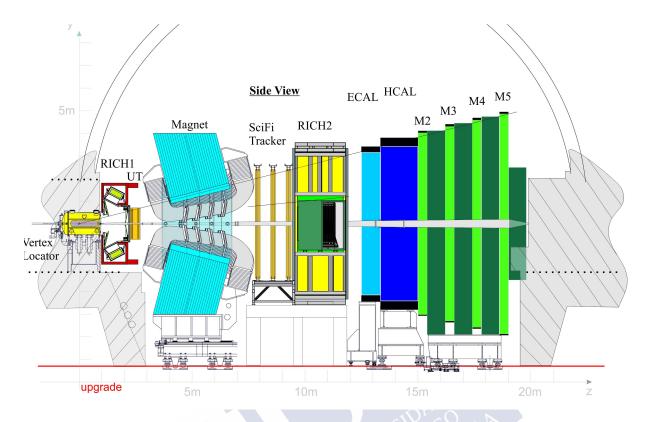

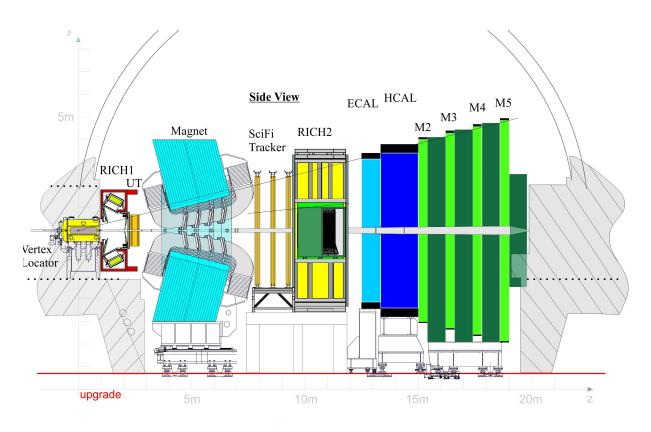

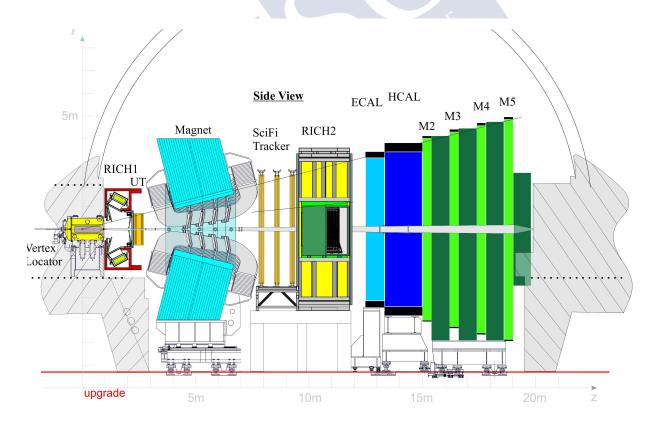

a forward arm spectrometer (Figure 2.4), covering an angle between 10 and 300 mrad. LHCb complements the other LHC detectors, as it covers a pseudo-rapidity range<sup>4</sup> between 2 and 5 (Figure 2.5).

The LHCb experiment has an excellent tracking resolution, particle identification and a flexible trigger. The tracking is performed by the VELO and four tracking stations distributed upstream and downstream the magnet. Particle identification is carried out with two Ring-Imaging Cherenkov Detectors (RICH) detectors, electric and hadronic calorimeters and a muon detector.

A dipole magnet that covers the forward acceptance of the detector was installed to measure the momentum of the charged particles. The magnet consists of two trapezoidal aluminium coils bent by 45° at the two transverse sides, arranged inside an iron window-frame yoke. The magnet gap is wedge-shaped in both, the vertical and horizontal planes, following the detector acceptance.

<sup>&</sup>lt;sup>4</sup>Pseudo-rapidity describes the range of particle angles relative to the beam axis that a detector can measure. It has a value 0 for the plane perpendicular to the beam and infinite for the beam axis.

Figure 2.4: LHCb detector.

Figure 2.5: (Left) Angular distribution of b and  $\overline{b}$ . (Right) Illustration of the acceptance complementarity as a function of pseudo-rapidity between experiments at the LHC.

The flexible trigger system consists of two stages [8]. At first, a hardware level trigger uses information provided by the calorimeter and muon systems to filter 1 MHz of the 30 MHz of the colliding proton bunches. All the data that pass through the first trigger, are sent to a CPU farm where the events are reconstructed and selected. Thus, the LHCb output rate is  $5 \, \text{kHz}$ . LHCb experiment data taking has been successfully performed during LHC Run 1 and 2, collecting nearly  $9.2 \, \text{fb}^{-1}$ .

Although this thesis is made under the frame of the LHCb upgrade, it is necessary to describe the hardware of the original detector to justify the reasons behind the upgrade. The main systems are:

**VErtex LOcator (VELO) [9]** is the sub-detector closest to the interaction point in the whole LHC, 8.2 mm during data taking<sup>5</sup>. VELO is used to measure the trajectory of the particles close to the interaction point in order to distinguish between primary and secondary vertices. VELO sub-detector consists of 42 semi-circular modules with two 300  $\mu$ s thick silicon strip sensors arranged in radial shape (measuring r) and azimuthal (measuring  $\phi$ ).

<sup>&</sup>lt;sup>5</sup>During beam injection or unstable beam, the sensors are moved away from the beam axis to prevent any damage.

**Tracking stations** consist of two sub-detectors with different technologies. The first one [10][11] is based on a large-surface silicon microstrip detector, which may itself be divided into two: four layers before and twelve after the magnet. In order to give an idea of the surface covered by this sub-detector, the station upstream the magnet covers a 1.7 m<sup>2</sup>, whereas the downstream station covers 4.2 m<sup>2</sup>. The second sub-detector is a gas tracking detector [12] that allows the measurement of the momentum of the particles covering a large area. It is built by grouping straw-tubes filled with a mixture of Argon and CO<sub>2</sub>. These straw tubes are arranged in three stations of four layers each, similar to the silicon trackers.

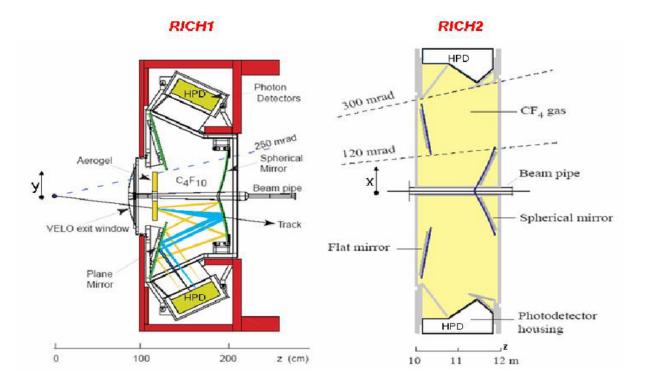

RICH [13] is the sub-detector capable of distinguishing the pions and kaons in a range between 2 and 100 GeV/c by measuring the Cherenkov light. This sub-detector is divided into two stations, one before the dipole magnet between VELO and the first tracking station and other after the magnet between last tracking station and the calorimeter. When the particles travel through a very dense gas (C<sub>4</sub>F<sub>10</sub> or CF<sub>4</sub>), faster than the speed of light traveling through this gas, they emit a cone of light that is reflected on mirrors, driving the light outside of the detector acceptance for digitalization on hybrid photon detectors.

Calorimeter [14] system is designed to identify and measure the energies of the electrons, photons and hadrons. It consists of several layers: the Scintillating Pad Detector (SPD), the pre-shower detector, the Electromagnetic Calorimeter (ECAL), and the scintillating tile iron plate Hadron Calorimeter (HCAL). The SPD determines whether particles hitting the calorimeter system are charged or neutral, while the pre-shower indicates the electromagnetic character of the particle (i.e. whether it is an electron or a photon). They are used at the trigger level in association with the ECAL to indicate the presence of electrons, photons, and neutral pions which are inductors of an event of interest for LHCb.

The working principle of the different layers is similar. It alternates layers of metal, to initiate a particle shower, with a scintillating material and a photo-detector to convert the shower into an electrical signal. Each calorimeter subsystem is configured with the appropriate metal layer, scintillating material, photo-detector and the dimensions for optimal detection of every type of particle. Thus, SPD and pre-shower use a 15 mm thick scintillating pads interspaced with a 2.5 times the radiation length lead converter. Then, the light is collected using wavelength shifting fibres and driven to a multi-anode photomultiplier tube in the periphery of the sub-detector. ECAL uses lead plates to create the

particle shower and scintillating plates with a different cell size, depending on the position. The cell granularity is the same as for the SPD and pre-shower. The light detection is performed on photo-multiplier tubes with an individually regulated high voltage base. Finally, the HCAL uses iron plates interspaced with scintillating tiles arranged in parallel to the beam pipe. Like the ECAL, the inner and outer regions use different cell dimensions.

**Muon detector** [15] is located at the far-end of the LHCb. It comprises five stations (one in front of the calorimeter SPD and pre-shower and the remaining four downstream), the four latest stations are interleaved with iron filters.

Each one of the five stations is divided into four regions with respect to the radial distance to the beam axis, all with the same acceptance. Inner regions have better granularity due to their higher particle density. The granularity is likewise better in the horizontal plane, to give an accurate measurement of the track momentum and transverse-momentum.

The different granularity choice drives the use of two different technologies for the muon detection: the first one is used in the inner region of the first station and it is called triple Gas Electron Multiplier (triple-GEM) and the second one, used for the rest of the detector, is called Multi-Wire Proportional Chambers (MWPC).

Online system ensures the transfer of data from the FE electronics to permanent storage under known and controlled conditions. This includes not only the movement of the data themselves, but also the configuration of all operational parameters and the monitoring of these, as well as environmental parameters, such as temperatures or pressures. The online system must also ensure that all detector channels are properly synchronized with the LHC clock. It can be decomposed into three sub-systems: Data AcQquisition (DAQ) that transfers the data belonging to an event of a LHC bunch crossing from the detector FE to permanent storage, Timing and Fast Control (TFC) that drives all stages of the data readout between the FE and the final storage by distributing the synchronous clock, resets and fast control commands, and Experiment Control System (ECS) that controls and monitors the operation of the detector.

Figure 2.6: LHCb upgrade detector.

# 2.3 The LHCb upgrade

Results from LHCb analyses so far, have mostly been consistent with the SM. However, the experiment needs to collect more data to reduce the current statistical uncertainties, and therefore continue with the quest for physics Beyond the SM (BSM). In 2019-2020, during the LHC Long Shutdown 2 (LS2), LHCb is suffering an important upgrade (LHCb Upgrade Phase I) [16]. The detector operated in Run I and II was not able to handle all the luminosity<sup>6</sup> that the collider could provide, thus the LHC was working with offset collisions in LHCb interaction point to reduce the delivered luminosity. This offset will be kept for the upgrade I but the upgraded detector will be designed to operate at 5 times the actual luminosity, up to  $2 \times 10^{33} \text{cm}^{-2} \text{s}^{-1}$ , expecting an integrated luminosity of  $50 \text{ fb}^{-1}$  by the end of Run IV (2030). Moreover, the events will be fully-reconstructed at the LHC inelastic event rate using a fully software-based trigger. All LHCb sub-detectors will be upgraded as well as their readout system in order to sustain the new

<sup>&</sup>lt;sup>6</sup>The luminosity measures the number of collisions produced per cm<sup>2</sup> and per second.

experimental conditions.

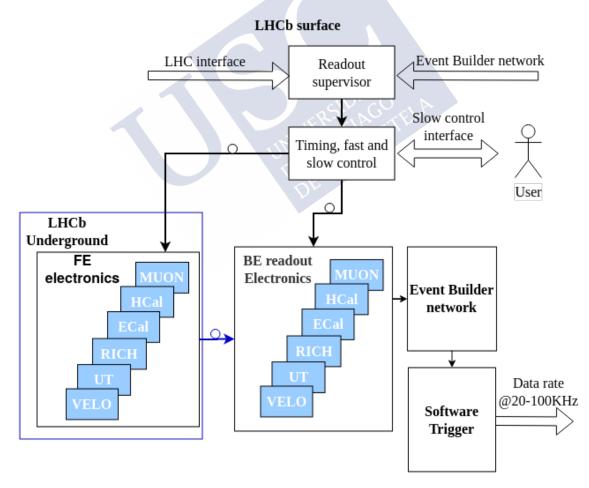

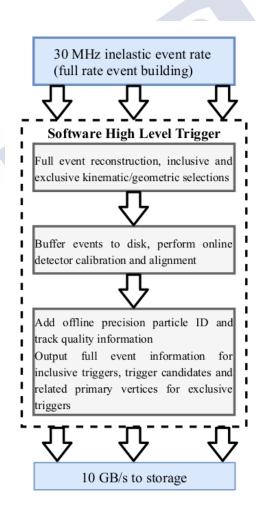

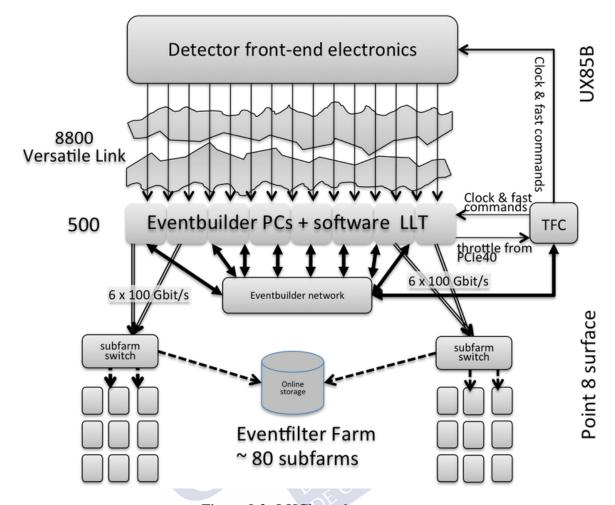

#### 2.3.1 LHCb trigger and readout upgrade

The main limitations of the original LHCb experiment was that the collision rate had to be reduced to a fixed latency 1 MHz rate. The cause of this reduction was the hardware trigger of the experiment. The low acquisition rate causes inefficiencies in the trigger chain, especially for purely hadronic decays. Thus, from the readout point of view, the primary objective is to implement a trigger-less hardware detector. To reduce the storage costs, all sub-detectors must perform zero-suppression before propagating the data to the DAQ system.

The whole detector will be operated through the optical fibre radiation hard Versatile Link [17], differentiating two kind of links: full duplex for control and timing information and sim-

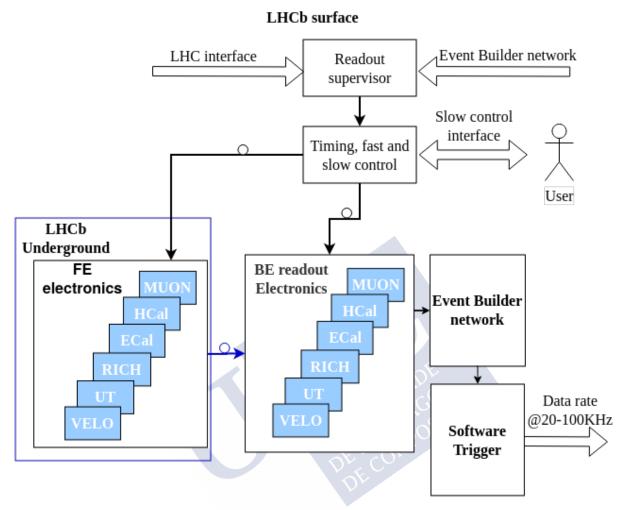

Figure 2.7: LHCb upgrade Readout architecture.

plex for data acquisition. Timing and control information (TFC/ECS) is driven on the same link using the GigaBit Transceiver (GBT) protocol [18]. On the other hand, data links will be read out using GBT for all sub-detectors but VELO that will use an specific protocol Gigabit Wireline Transmitter (GWT) [19] (more details on chapter 3).

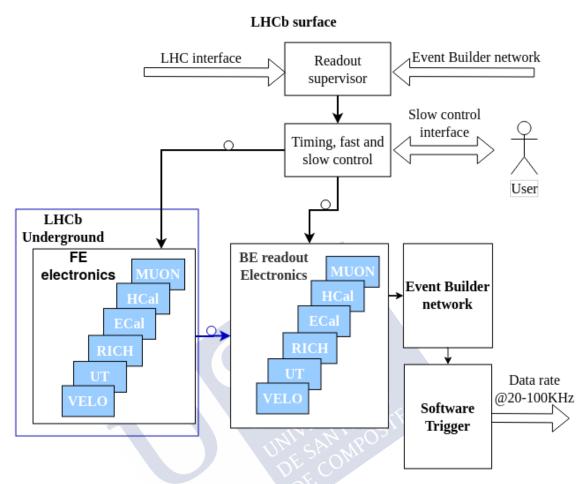

All Back-End (BE) electronics are designed to control, synchronize and read out the experiment. They are placed in the surface area of LHCb and they share the same hardware, a board called PCIe40 connected to a server. The functionality of this board is determined by its firmware.

Figure 2.7 shows the architecture for the upgraded LHCb where all FE electronics record and transmit data synchronously at 40 MHz to the readout boards through the versatile links.

Figure 2.8: LHCb upgrade trigger diagram.

Muon and Calorimeter detectors transmit in parallel event information to the high level trigger software, which will take the physics accept or reject decision per LHC bunch crossing and propagate it through the TFC system. This system is based on two different types of boards: a readout supervisor board (S-ODIN) and an interface board (SOL40). The first one acts as an interface with the LHC, generating the TFC commands of the detector. The second one handles the distribution to all FEs of two kinds of signals: the previously mentioned TFC and the control/monitoring commands, ECS, from the multiple computers used as Supervisory Control And Data Acquisition (SCADA).

The flow of the data and its various transformations are summarized in Figure 2.8. In this architecture all FE electronics record and transmit data continuously to the readout boards, where each sub-detector pre-process the data in real time in a so-called "data processing" block. After the sub-detector processing, the combined data from all links of the readout board (TELL40) are passed as a new fragment to the data-processing block which can contain sub-detector specific processing. This fragment is passed on to the MEP building, which combines several fragments from consecutive bunch-crossings into an event-block and transfers them to a ring-buffer on the TELL40 server host. The Event Building software consists essentially of two processes: a readout-unit which is sending the blocks and a builder-unit which is collecting the blocks and creating multi-events (MEPs).

The data are driven from the sub-detectors FE via a multi-Tb/s readout network into a computing centre where events will be fully reconstructed prior to the lowest level trigger decision. The estimated data stored after the software trigger will be around 10Gb/s.

# 2.3.2 LHCb on detector hardware upgrade

From the detector point of view, all FE electronics will be replaced to cope with the new readout scheme, a new tracking system will be installed as well as an improvement in the radiation tolerance for the particle identification detectors.

The modifications to each sub-detectors are:

**Vertex Locator:** In the case of this sub-detector, it will suffer major changes [20]. The sensor technology will migrate from silicon strip to pixel that gives a better spatial resolution and can also be operated closer to the interaction point. This, combined with the increase in the delivered luminosity by a factor 5, dictates that the FE electronic and sensor design

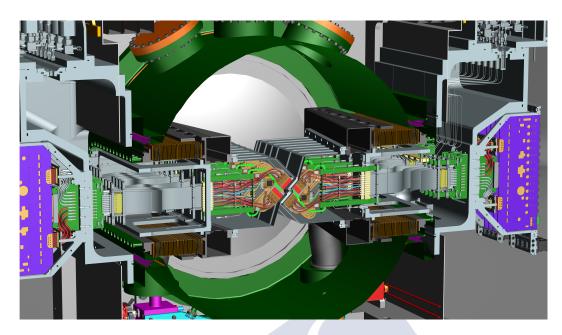

Figure 2.9: CAD model of the LHCb VELO upgrade.

must be radiation tolerant and the sensor bias voltage will be increased from 500V to 1000V. The entire sub-detector will increase its power consumption around a factor 2, hence a novel cooling design was developed in order to cool the FE electronics and keep a low material budget. As the sensor technology is changed, the shape of the VELO stations will be different as well, therefore, a new radio frequency foil to separate VELO and LHC vacuum was designed. A detailed description of the system is given in chapter 3 and chapter 4.

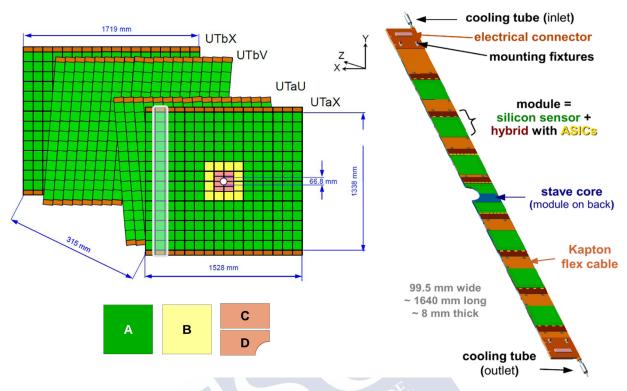

**Tracking stations:** As the VELO case, the LHCb will have a brand new set of tracking stations [21]. The replacement of the tracking stations is needed because the original LHCb, operated during Run I and II, was not designed to be enough radiation hard for the integrated radiation dose of Runs I to IV. Moreover, the strips geometry present in the previous tracking stations leads to a significantly high occupancy under the new running conditions. The upgraded tracking system will consist of 2 different sub-detectors: The Upstream Tracker (UT) that will replace the old first tracking station between the RICH1 and the LHCb spectrometer magnet. After the LHCb spectrometer magnet, the tracking will be done by the Scintillating Fibre Tracker (SciFi) that will replace the silicon and gas tracking stations.

Figure 2.10: (Left) Layout of the detection layers of the UT. Each rectangle represents a silicon sensor and diverse shadings indicate different sensor geometries. (Right) Sketch of a UT stave.

The UT sub-detector has four planes of silicon strip sensors as shown in Figure 2.10. The sensors have a finer granularity than the old ones to cope with the greater density of particles. The sensors strips are arranged vertically to increase the precision in the horizontal direction, which is the bending direction of the dipole magnet. The middle planes are angled by  $\pm 5^{\circ}$  for stereo measurements. Each plane is built from units called "staves". Staves placed far from the beam have fourteen sensor units (each alternatively mounted front and back) of a sandwich of foam and carbon fibre structure with embedded tubes acting as support and coolant. Central staves include four extra half-length sensor units in the region closest to the beam pipe. Each sensor unit contains one sensor, four or eight FE ASICs, a hybrid circuit and a stiffener. Each FE ASIC has 128 input channels with a 6 bit Analog to Digital Converter (ADC).

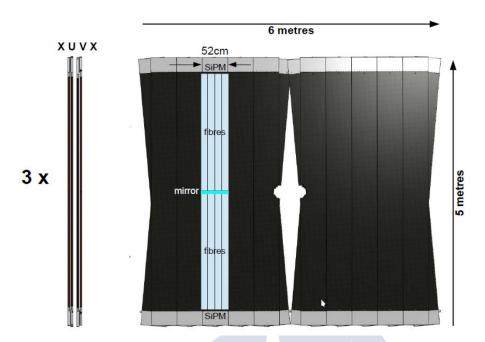

The SciFi sub-detector consists of three stations with four detector planes each, as shown in Figure 2.11. Each station is built from individual modules  $(0.5 \,\mathrm{m} \times 4.8 \,\mathrm{m})$  comprising 8 2.4 m long fibre mats. The mats consist of 6 layers of densely packed scintillating

Figure 2.11: Schematic yz- and xy-view of one SciFi tracking station. It is composed out of 4 layers, two vertical (x) and two with a stereo angle of  $\pm 5^{\circ}$  (u, v). Each layer is made of 10 or 12 individual fibre modules.

fibres with a diameter of  $250\,\mu m$ . The scintillation light is recorded with arrays silicon photo-multipliers, digitalized in a custom ASIC. To reduce the thermal noise of the silicon photo-multipliers are cooled down to -40°C.

**RICH detectors:** In order to allow operation of the RICH detector system at the upgrade luminosity, the first station of the RICH optical system is being redesigned: in particular, the focal length of the spherical mirrors will be increased from 2.7 m to 3.7 m to reduce the hit occupancy on the photo-detectors. The cooling system and the support mechanics will also be modified to allow stable operation and easier access to the detector during maintenance.

New photo-detectors (Multi-anode Photo Multiplier Tubes, MaPMTs) have been chosen and they will be read out using a 8-channels ASIC, named CLARO [22], designed to sustain a photon counting rate up to 40MHz while minimizing the power consumption and the cross-talk. A 128 bit digital register allows selection of thresholds and attenuation values and provides features useful for testing and debugging. More detailed information in [23].

Figure 2.12: RICH1 has a vertical optical layout (y-axis), while RICH2 has a horizontal optical symmetry (x-axis). The two drawings are not to scale.

calorimeters: Calorimeters will only suffer minor changes. The main change is to rebuild the whole front end and back end electronics, along with the rest of the sub-detectors, to read out at the LHC frequency. Working at higher luminosity also forces the reduction of the Photo Multiplier Tubes (PMT) gain to ensure the lifetime during LHC Run 3. Finally, the PreShower and SPD will be removed since they are not used for the upgraded trigger.

**Muon chambers:** Muon system, as well as the rest of the particle identification system (RICH and calorimeters), will suffer only minor changes to read out the electronics at the LHC clock, will remove the first muon plane, and also additional shielding will be added around the beam pipe and in front of the second plane, M2, to reduce the occupancy generated in these regions by the escalation in fluence.

# **CHAPTER 3**

# **VELO UPGRADE**

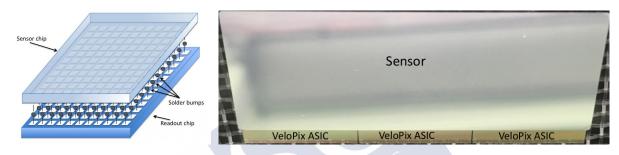

The upgraded VELO sub-detector [20] will be a hybrid pixel detector consisting of 208 silicon sensors, each of those ball-bonded to 3 FE ASICs. The migration from the old strips technology into pixels is due to the better granularity and, therefore, tracking precision.

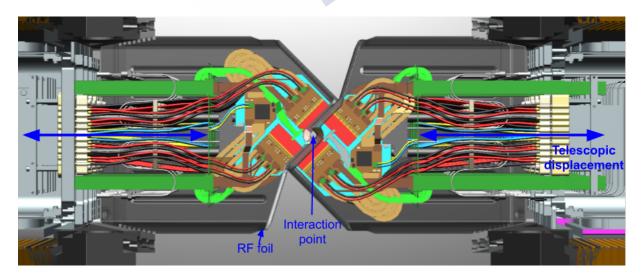

The closest sensor will be placed at 5.1 mm from the interaction point (3 mm closer to the beam than in the old sub-detector) within a secondary vacuum isolated from the LHC primary vacuum. Sensors are distributed in 26 stations along the beam in two opposite retractable (by 6 cm) halves as it is shown in Figure 3.1. Each station is divided up in 2 slices. Each of those includes the so-called module, containing the sensors and the FE electronics, and the auxiliary power and interconnection electronics. The absortion of the modules telescopic displacement is

Figure 3.1: Close-up view of the VELO sub-detector.

taken by the flexible data tapes and the powering cables.

The retraction of the modules keeps them far from the beam during the LHC injection, avoiding any damage in the sensors and FE. Once the beam is stable, the two VELO halves will close to the nominal beam distance to take data.

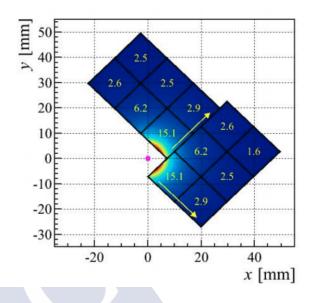

Based on Monte Carlo simulations, the highest occupancy ASICs will have pixel hit rates about 900 Mhits/s, which is equivalent to 520 Mhits/s in terms of cluster rates. This translates into a bit rate of  $\sim 16\,\text{Gb/s}$  adding up to  $\sim 3\,\text{Tb/s}$  data for the  $\sim 41\,\text{Mpixels}$  of the whole VELO. One of the major challenge of the sensors and the readout chips is caused by their orthogonal arrangement to the beam

Figure 3.2: VeloPix data rate [Gb/s].

pipe. The irradiation profile along the sensors is inversely proportional to the squared distance to the interaction point, with the greatest concentration of hits at the innermost sensor regions. Figure 3.2 shows an estimation of the VeloPix data rates in the hottest module<sup>1</sup>, where the highest rate (red and yellow) is received in the region closest to the iteration point (pink dot).

## 3.1 Planar silicon sensors

The VELO upgrade will be made of hybrid pixels, consisting of a planar silicon sensor [24] connected to a three readout ASICs (section 3.2) by using flip-chip technology [25]. This technology allows the union between the sensor and the FE ASIC by using an array of small soldering bumps (12  $\mu$ m diameter) known as "bump bonds" shown in Figure 3.3.

The chosen planar silicon sensors are  $200 \,\mu\text{m}$  thick Hamamatsu "n-on-p" optimized for electron collection in order to mitigate the timewalk effect<sup>2</sup>. Sensor efficiency is higher than 99%,

<sup>&</sup>lt;sup>1</sup>The hottest module has the highest estimation of hits. This corresponds with the station number eight.

<sup>&</sup>lt;sup>2</sup>This effect is caused by the different spectrum of the sensor collected charge, which generates a non-negligible spread in the time response at the input of the electronics pre-amplifier. Hence, hits with small collected charge generate signals with a slower rising edge, generating a late detection of the pixel hits.

reducing the risk of missing the first measurement points. The pitch of the sensor is compatible with the readout chip and with elongated pixels of  $55 \times 137 \,\mu\text{m}^2$  in the region between ASICs. The sensor is built with a  $450 \,\mu\text{m}$  guard ring and the deep reactive-ion etching needed for the foil clearance.

By the end of LHC Run IV (2030), the hottest sensor will be exposed to a fluence of  $8\times10^{15}~n_{eq}/cm^2$ . Hence, they will operate at -20°C to protect the silicon from thermal runaway effects after irradiation. They also need to withstand bias voltage of 1000 V to provide enough signal at the end of their lifetime.

Figure 3.3: (Left) Hybrid pixel detector. (Right) VELO "Tile": Sensor flip-chip to 3 VeloPix ASICs.

# 3.2 VeloPix FE ASIC

To read out the charge collected in the sensors, a new FE ASIC called VeloPix [26], based on the MediPix/TimePix family, has been designed to meet the very demanding readout rate, radiation

| Technology         | 130 nm CMOS                                                                     |

|--------------------|---------------------------------------------------------------------------------|

| Pixel matrix       | $256\times256$ pixels with a pixel size of $55 \mu\text{m}\times55 \mu\text{m}$ |

| Radiation hardness | 4 MGy achieved using triplicated voting registers                               |

| Power consumption  | < 1.5 W/ASIC                                                                    |

| Readout            | Unsorted binary data driven at 40 MHz                                           |

| Data throughput    | 20.52 Gb/s                                                                      |

Table 3.1: VeloPix ASIC specifications.

hardness and low power consumption requirements of the experiment (Table 3.1). A single sensor is bump-bonded to 3 VeloPix ASICs comprising a "Tile". The VeloPix has to timestamp the collected data according to the 3564 bunch crossings of one LHC orbit, for that 12 bits are needed, but to optimize the data bandwidth, only 9 bits of tagging are transmitted. The full 12 bits are later reconstructed in the BE readout board (chapter 4).

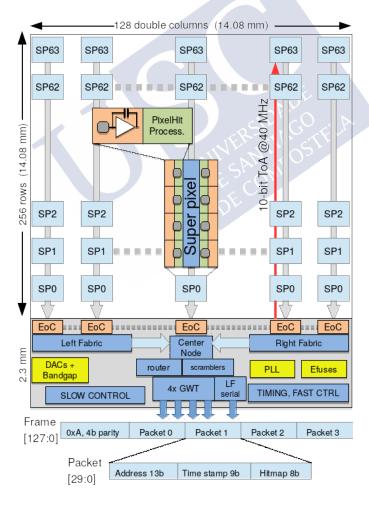

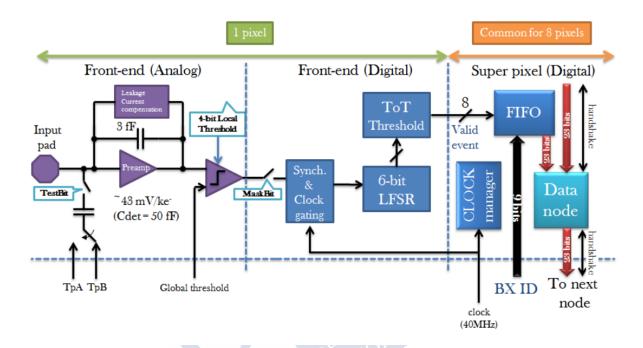

The architecture of the ASIC is shown in Figure 3.4. The VeloPix transmits only zero suppressed binary data generated from time over threshold measurements in the pixel. On this architecture (from left to right on Figure 3.5) the signal enters in the pad from the bump bond connection to the sensor, it is amplified in the analog FE, digitized in the pixel level and grouped in clusters of 2 by 4 pixels (Super Pixel Packet (SPP)). The SPP data are vertically transmitted, with a clock rate of 160MHz, over the matrix until they reach the End of Column block (EoC).

Figure 3.4: General architecture of VeloPix.

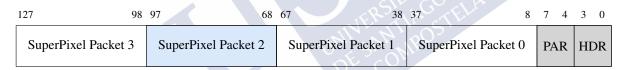

Then the data go to a central node where they are packed in groups of four SPPs, a bit of parity per SPP and a header of the full packet are added. The 128 bit frames are now sent into the ASIC transceiver where the data are scrambled following the polynomial  $X^{30} + X + 1$  to maximize the transitions allowing a good data transmission<sup>3</sup>.

Figure 3.5: Schematic of the pixel and super pixel architecture.

With the aim of reducing the power consumption of the CERN standard serializer (GBT) and keeping in mind the radiation hardness of the ASIC, a readout link serializer block, named GWT [27] was designed. A single GBT serialiser and its corresponding high-speed Phase Locked Loop (PLL) requires ~300 mW whereas the GWT serializer uses a multi-phase delay locked-loop which consumes less than 100 mW for the equivalent functionality. The VeloPix ASICs are operated in vacuum and if we reduce the power footprint, the demands of the cooling system also decrease. Furthermore, the GWT serializer has a higher usable bandwidth of 5.13 Gb/s vs. 4.8 Gb/s for the GBT. This serializer works by feeding a 16 bit input round-robin multiplexer with a byte of data on both edges of a 320 MHz clock (8 times faster than LHC clock). The reading of this multiplexer is triggered by the signal generated on a multi-phase delay-locked

<sup>&</sup>lt;sup>3</sup>The clock is transmitted embedded with the data and therefore a good clock recovery relies on these transitions.

loop, which generates 16 phases evenly spaced from the given 320 MHz clock. The timestamp could also be encoded in gray code to reduce the digital activity in the ASIC and, therefore, reduce the power consumption.

The VeloPix has a slow control interface connected to the Experiment Control System (ECS) from which are accessible the configuration and monitoring registers. Full details about this interface can be found in section 4.3.

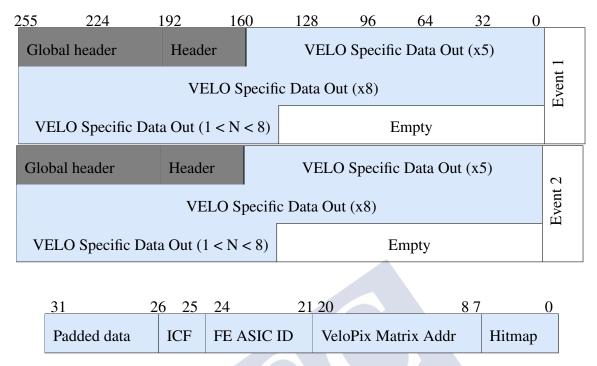

## 3.2.1 VELO FE data framing

The data generated by FE ASIC go to the BE board through optical fibre following the VELO-specific protocol GWT. The GWT output frame operates at the LHC clock frequency of 40 MHz. Each frame consists of 128 bits, shown in Figure 3.6. This frame has a 4 bit header, always sending the binary value "1010", that allows the word alignment of the data on the back end side (subsection 4.2.1). Moreover, four 30 bit SPPs are sent along with their corresponding parity bits. Depending on the content of each SPP, the data transfered could be: Pixel data or special frames.

Figure 3.6: GWT data frame.

#### 3.2.1.1 Pixel data

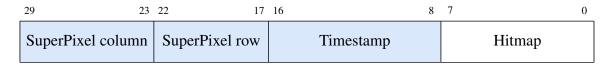

When pixel data are transmitted, each SPP field follows the format shown on Figure 3.7. Pixel data can be distinguished from special frames because they have a hitmap field different from 0. From left, Most Significant Bit (MSB), to right, Less Significant Bit (LSB) the information transmitted is:

- 13 bits define the hitted Super Pixel (SP) address (upper 7 bit for the column and lower 6 bit the row). Pixel row = SP row x 4; Pixel column = SP column x 2.

- 9 bits of timestamp (Bunch Cross Identifier (BXID)) optionally encrypted in gray code.

Figure 3.7: SuperPixel Data format.

• 8 bits define the hit pixel in a super pixel. Pixels are geometrically ordered, as shown in Figure 3.8.

Figure 3.8: Hitmap pixel ordering.

The 9 bits of timestamp correspond to the lower nine bits of the full 12 bit LHC BXID. Special frames with the full 12 bit BXID can be sent from VeloPix, described in the following subsection.

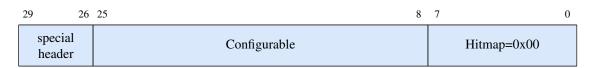

#### 3.2.1.2 Special frames

Valid SPPs are always indicated by a non-zero hitmap. All special frames, which do not contain actual event data, are indicated by zero hitmap. Also, valid SPPs don't have a fixed header at position [29:26], but all special control packets do in order to distinguish them more easily. Since special frames do not have to traverse the pixel columns, they do not suffer from the large latency variances of the SuperPixel hit data. Some small variances may remain, however, as the output to the BE is never guaranteed to be fixed latency. Table 3.2 shows the full list of special frames.

| Header [29:26] | Configurable packet data[25:8] | Hitmap [7:0] | Packet type    |

|----------------|--------------------------------|--------------|----------------|

| 0x0            | 6'h0, BX ID[11:0]              | 8'h00        | BX ID          |

| 0x1            | Configurable[17:0]             | 8'h00        | TFC Sync       |

| 0x2            | 3'h0, chip ID[14:0]            | 8'h00        | Chip ID        |

| 0x3            | 12'h0, TFC bits[5:0]           | 8'h00        | TFC Align Mode |

| 0x4            | Configurable[17:0]             | 8'h00        | Invalid (Idle) |

Table 3.2: configurable FE SuperPixel Packet frame.

The special sub-frames are defined per SPP, so one can construct a complete GWT frame with four different special SPP sub-frames. The most useful would be with a BXID packet (0x0), a TFC Sync (0x1), a Chip ID packet (0x2), and a TFC Align Mode packet (0x3). The Sync mechanism is described below. The Chip ID is a unique VeloPix identifier (used to confirm fibre/cable mapping). The TFC Align Mode is used to identify which TFC bits which have been set in the TFC word.

#### **IDLE** frame

By default, when no valid hit data are arriving at the GWT serialiser, "Invalid packets" are sent with the SuperPixel header 0x4. See Figure 3.9. Note that unlike the GBT protocol, which has a different header for valid and invalid data, the GWT header remains fixed (binary "1010") at all times, irrespective of idle or valid data. A mixture of idle and valid SPP sub-frames is allowed in a GWT frame. For example, if only one SPP arrives at the GWT serialiser in a 25 ns window, then the GWT frame will consist of three idle sub-frames and one valid data SPP sub-frame. The position of the valid sub-frame is not fixed and it is a function of the state of the end-of-column routing logic of the VeloPix (in short, the GWT frame is *not* filled SPP0 first, then SPP1 . . . ).

Figure 3.9: Idle frame.

#### Sync frame

When the VeloPix receives a TFC Sync message, it sends a corresponding TFC Sync frame. This is configured as at least one of the 4 available SPP slots. The TFC Sync frame would correspond to a header = 0x1 and configurable pattern 18h'2BABE by default. The remaining 8 bits are set to 0 to indicate that the packet is special as previously mentioned. The other SPPs can be configured to send VeloPix Chip ID, full 12 bit SPP as seen in Table 3.2.

The TFC Sync mechanism is required to time-align the FE and BE. The BE requires a sync frame to initiate valid data taking. Before the Sync frame, the BE cannot determine the correct allocation of a single SPP within an orbit, as only 9 of the 12 bits are transmitted. Subsequent Sync frames can be used as a cross-check of the FE to the BE. The 9 bit SPP imposes a maximum latency constraint on the output of the VeloPix. Any data delayed by more than 512 clock cycles, 9 bits, will be incorrectly timestamped at the BE. However, Monte-Carlo studies have shown that the fraction of VeloPix data exceeding this requirement is negligibly small.

#### **Bunch ID frame**

Bunch ID counter provides a global timing reference across the VeloPix. The counter runs at 40 MHz offering a maximum dynamic range of 9 bits for time stamping data packets. The full 12 bits of the counter can be queried with a TFC command Snapshot, or embedded into TFC Sync frames as described in the previous section.

## 3.2.2 TFC command response

All LHCb FE electronics receive TFC commands described in subsection 4.2.2. The transmission of these commands from the BE board is shown in subsection 4.3.1. VeloPix ASIC only reacts to the following commands:

**BXID reset.** This command is sent every turn of the LHC, it resets the 12 bit bunch counter.

**FE reset.** This command performs a reset of the VeloPix without touching the bunch counter. It is asserted at the same time as the "Header only" and "BX Veto" commands. Moreover, a FE reset is always followed by a "Sync" command.

**Sync.** The VeloPix response is described above in subsection 3.2.2.

**Calibration.** Upon receiving a TFC calibration command, the VeloPix injects test-pulse data into the matrix. The exact configuration of which pixels are activated by the testpulses can be configured through the slow control interface (ECS).

**Snapshot.** This command is only be dealt over the ECS data path and GWT/DAQ data are unaffected. All counters are transferred to a set of snapshot registers on the current SPP and can be read via ECS and compared to the expected value. This command does not affect the data taking.

**Shutter.** This is not a LHCb TFC command, but this signal is transmitted to the VeloPix enabling the GWT data adquisition. A known feature of the VeloPix is that during the transitions of this signal, noise will be transmitted through the GWT links, and thus it is mandatory to reduce these transitions.

## 3.3 On-detector electronics

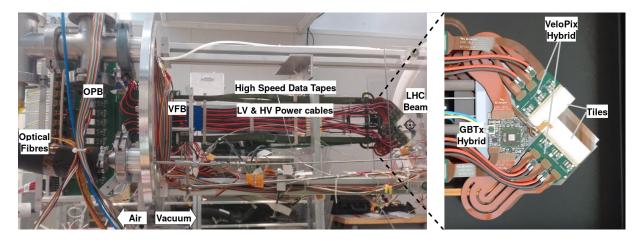

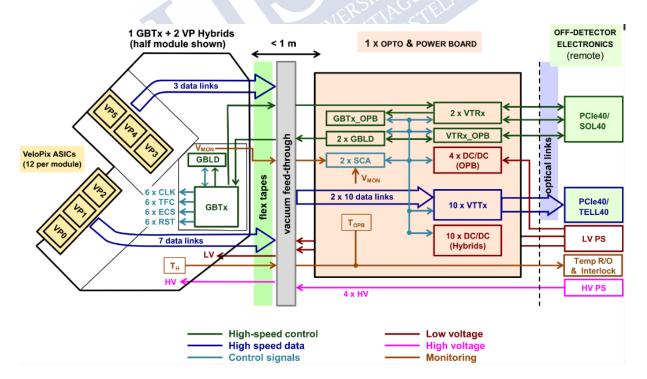

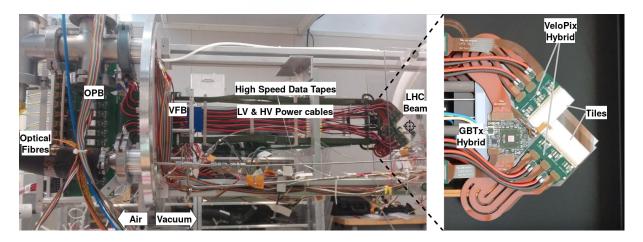

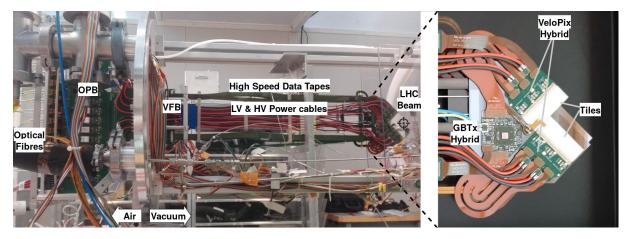

Figure 3.10 shows a VELO slice, while Figure 3.11 is its schematic. From right to left (in Figure 3.10), what can be seen is: a VELO module, the high-speed tapes and low and high voltage cables, the Vacuum Feedthrough Board (VFB) and the Opto-Power Board (OPB). The high-speed tapes [28] have low mass to reduce the radiation length in the detector acceptance and they are flexible enough to allow the detector opening during LHC beams filling without

Figure 3.10: VELO slice.

compromising signal integrity. High-speed transmission lines travel almost 1 m before reaching the optical converters. A feedthrough board is needed to make the electrical connection between vacuum and air-side electronics. All the electrical readout and control signals are converted into optical in the OPB and driven 300 m to the FPGA based BE board on the surface.

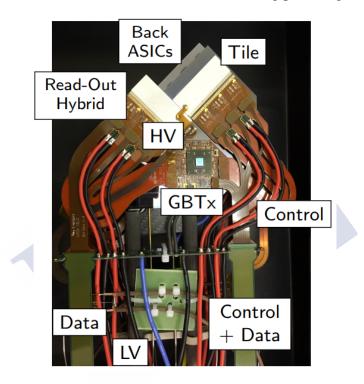

## 3.3.1 VELO module

A single module (Figure 3.12) is equipped with 4 sensor tiles on a silicon substrate, 2 per side, with microchannel evaporative CO<sub>2</sub> cooling (section 3.4). Every tile contains 3 VeloPix ASICs, with a peak module occupancy of 61 Gb/s. The variability in the hit distribution causes that the VeloPixes placed close to the interaction point receive more hits, thus the number of 5 Gb/s readout links on these ASICs is larger than the periphery ones. Monte Carlo simulations show the ASIC data rate of Figure 3.2. Hence, the nearest ASICs to the interaction point that has a data rate of 15 Gb/s uses 4 readout links, ASICs in the middle region of the module that expect an occupancy of 6 Gb/s use 2 links, and the periphery ASICs with less than 3 Gb/s of occupancy use only 1 link. Ten is the aggregated number of links of a single module. All of them share the

Figure 3.11: LHCb VELO electronics overview.

same off-detector readout board, TELL40 (section 4.2).

Each side of the substrate has a Giga Bit Transceiver ASIC (GBTx) ASIC [29] that controls and distributes the timing signals to the 6 VeloPix through a full-duplex link. The electronic design of the module was made to reduce the effect of the mismatch in the coefficient of thermal expansion and using the minimum mass in the acceptance of the sub-detector. Consequently, two kinds of Printed Circuit Board (PCB) interconnected by Kapton tapes were designed, one for hosting the GBTx ASIC and one for the VeloPix wire-bonding pads (Figure 3.12).

Figure 3.12: VELO module.

## 3.3.2 High-speed data tapes

All module readout and control signals are routed inside the vacuum using low mass high-speed flex tapes with Kapton microstrip technology in the acceptance region where low mass materials are critical for the detector performance (~5 cm). Four flexible PCB tapes built in stripline technology drive up to 7 links. The dielectric used for these flexible tapes has to be radiation tolerant and provide low dissipation loss for high frequency signals. Besides, high reliability and yield would be required for the impedance control. The best candidate material

found, Pyralux®AP Plus [30], was retained. It is also widely used in medical, aerospace and military applications.

## 3.3.3 Vacuum feedthrough board and Opto-Power Board

The VFB is placed at the end of the high speed tapes. This board has to deal with a pressure of  $\sim 10^{-7}$  mbar on its inner side and the atmospheric pressure of the ambient air on the outer side. To help handling the difference of pressure the PCB was designed with edge metallization.

On the air-side of the vacuum feedthrough is connected to the OPB through a PCI express connector. The main functions of the OPB are: to provide low voltage to the FE electronics, to monitor the FE temperatures and to convert the signals from electrical into optical and viceversa.

All the active components used on the OPB board are radiation tolerant: the FEASTMP DC/DC converters [31], the Versatile Twin Transmitter (VTTx) and Versatile Transceiver (VTRx) [17] electro-optical converters, the GBTx gigabit transceiver and the GBT Slow Control Adapter (GBT-SCA) ASIC [32] which is used for control and monitoring.

Figure 3.13: (Left) Cross section scheme for the microchannel cooling with a superposition of the VeloPix ASICs. (Right) Schematic of the microchannel attachment of the fluidic connector.

Figure 3.14: (Left) Draw of the edge region and clearance to the module. (Right) Picture of the LHCb VELO RF foil.

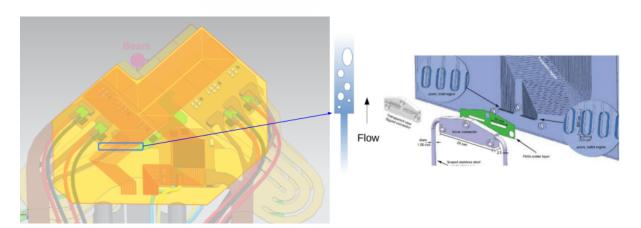

## 3.4 Cooling

As it was described above, a VELO module contains 12 VeloPix ASICs and 2 GBTx ASICs dissipating a total power of 36 W. The prevention of the thermal runaway and the annealing control of the sensors, caused by the irradiation suffered in the LHC environment, is achieved maintaining the module within an operating temperature of -20°C. A novel microchannel evaporative  $CO_2$  cooling system was designed to fulfil the cooling needs, keeping a low material budget in the acceptance of the sub-detector [33]. Figure 3.13 shows the microchannel cooling of a module. The working principle consists of making circulate liquid  $CO_2$  (close to the boiling point) through capillaries made on the silicon substrate. These capillaries have two regions: The first one has a section of  $60\,\mu\text{m} \times 60\,\mu\text{m}$  and the main region have a section of  $120\,\mu\text{m} \times 200\,\mu\text{m}$ . This widening allows the boiling of the  $CO_2$ , keeping a constant temperature along with the module. This solution has been selected due to the excellent thermal efficiency, the absence of thermal expansion mismatch with silicon ASICs and sensors, the radiation hardness of  $CO_2$ , and very low contribution to the material budget.

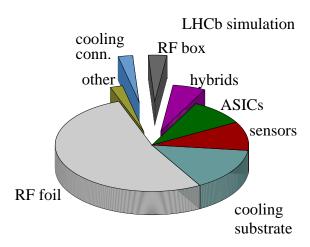

total material:  $21.3\%X_0$

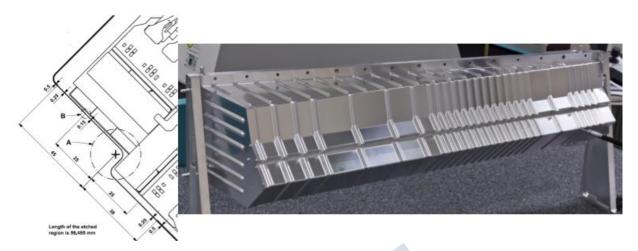

Figure 3.15: Pie chart showing the contributions from different components to the total material budget in the upgraded VELO within the pseudorapidity angles 0.8° and 15.4°.

## 3.5 Mechanics and RF foil

The VELO sub-detector is a 1.1 m long piece surrounding the LHC point 8 collision point, divided into two movable halves facing each other. Figure 3.14 shows the aluminium foil of one of the halves. The subdetector must be placed in an isolated vacuum from the LHC primary vacuum to avoid compromise the accelerator operation. Thus, an isolation aluminium foil must withstand a differential pressure of 10 mbar between primary and secondary vacuum. The foil also shields the detector from radiofrequency pick-ups from LHC beams.

From the mechanical point of view, the aluminium foil for the upgrade I must accomplish several constraints:

- As it can be seen in Figure 3.15, the foil thickness has a significant effect on the impact parameter resolution. Hence, to reduce the multiple scattering effects, the thickness is reduced from 300  $\mu$ m in the old VELO to an uniform thickness of 250  $\mu$ m, chemically etched downto 150  $\mu$ m in the region closest to the sensors.

- As the upgraded detector will operate closer to the beam (from 8.1 mm to 5.1 mm), the clearance of inner aperture of the foil must also be smaller, going from 5.5 mm to 3.5 mm.

$\bullet\,$  Inner clearance between the foil and the sensors must be 900  $\mu m.$

## CHAPTER 4

# VELO UPGRADE OFF-DETECTOR ELECTRONICS

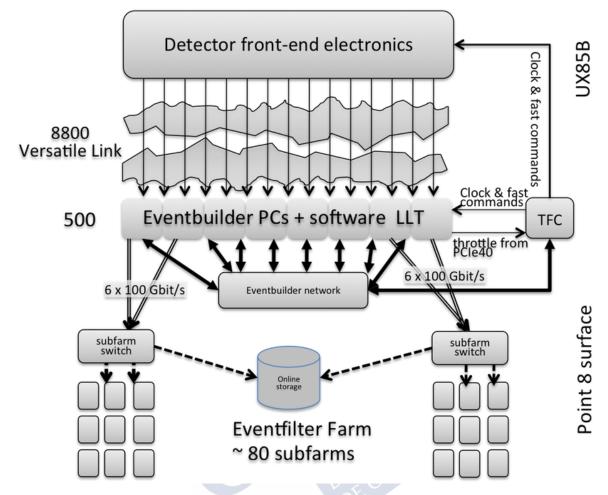

LHCb Off-Detector Electronics (ODE) comprises all the systems placed in the surface of LHC interaction point 8 that are responsible for control, timing and readout of the underground experiment. A new data centre [34] is being built to house all ODE within a cable distance around 300 m from the detector. All data transfer between the data centre and the detector is performed over optical links. Figure 4.1 shows the facilities of the new data centre.

The LHCb upgrade control and readout scheme was introduced already in section 2.3. The aim of this chapter is to go in-depth into the LHCb electronics on the surface, with an especial emphasis on VELO control, timing and DAQ readout boards.

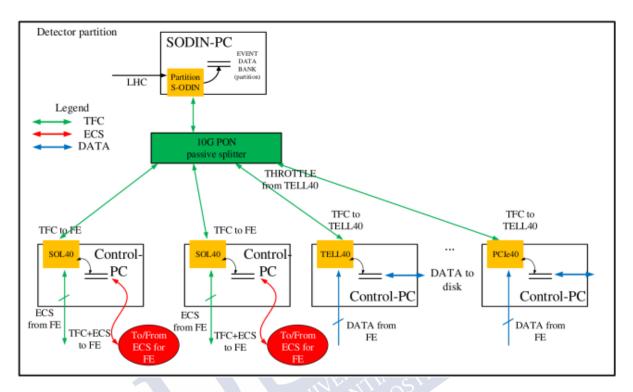

Already explained in the detector overview, the event readout acquisition of the experiment is managed centrally from the readout supervisor board (also known as S-ODIN). Interface boards (SOL40) and Readout Boards (TELL40) work as slaves of S-ODIN.

Due to the centralized nature of the TFC system, the distribution of the signals presents some challenges in terms of timing distribution, clock recovery, jitter, synchronization and robustness of the system. TFC synchronization between a LHCb experiment and the accelerator is done centrally in the S-ODIN boards (Figure 4.2). To ease the detector operation, each sub-detector has one or several detector partitions controlled by a single S-ODIN board. Each S-ODIN is connected to the LHC independently, allowing better robustness. An extra board supervises all the experiment partitions. Each partition S-ODIN recovered the clock, cleaned and fanned it out. In addition to that, it has to monitor and control the system allowing to each partition to be

Figure 4.1: New LHCb data centre and the optical fibre cabling to the cavern.

aligned by itself. The TFC also has to be aligned with the LHC beam structure, as explained in subsection 2.1.1, with a tolerance below 100 ps.

As all communications are done via optical links, the transceivers in the cards that propagate the TFC information need to work in a way that it maintain the LHC clock quality transmission, phase and latency. All these signals have to reach  $\sim 2500$  FE and 500 BE destinations.

The synchronicity between all the units that make up a partition is guaranteed over Passive Optical Network (PON) technology [35], where a passive optical splitter allows to reach many destinations from a single point of start without re-driving the stream. As the clock, timing and readout control signals are centrally generated and they are the same for all destinations, they can be distributed passively.

Figure 4.2 shows the architecture of a TFC partition, where the TFC information is centrally generated and synchronous with the LHC clock in S-ODIN. Data are sent over a timing-trigger and control PON splitter and connected to the different BE boards located in the surface of the experimental area (SOL40 and TELL40 boards). From the SOL40s, the ECS and TFC signals are distributed to the FE and the TELL40s collect FE data and make a real time pre-processing

of the sub-detector events before combining this data in the event building computers.

Figure 4.2: Architecture of the TFC system for a sub-detector partition

To implement the control and readout architecture of the LHCb experiment a common PCIe mezzanine board, called PCIe40 (Figure 4.4), was designed. Depending on the firmware flavour, it could be configured as S-ODIN, SOL40 or TELL40. This chapter describes the BE board hardware and firmware designs needed for operating the VELO sub-detector.

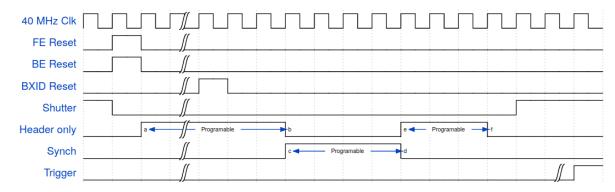

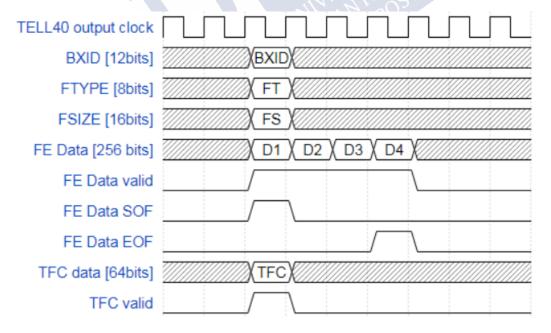

#### 4.0.0.1 LHCb VELO data taking operation

The synchronization of all detector electronics is a fundamental task of the readout electronics. This is carried out by the TFC system from the readout supervisor board. Later in this chapter, there will be an in-depth description of the different synchronization commands that concerns the VELO FE control and the readout board, but in this item, we are going to describe the big picture for the synchronization and the starting of the data taking from VELO BE electronics point of view.

Figure 4.3: LHCb TFC starting sequence.

The LHCb data must be tagged with an unique identifier, BXID, that is restarted every 3564 40MHz clock cycles with the "BXID Reset" signal.

Starting the data taking requires a sequence with multiple steps as it is shown in Figure 4.3. At the beginning, the "shutter" for the data acquisition is unset to prevent useless FE data to be sent to the BE readout boards, for VELO case the shutter signal is asserted from a register on the interface boards. At this point, all the FE and BE Finite State Machines (FSMs) are driven to the initial state by sending their corresponding "Reset" commands, after that a configurable time-window with the FEs sending header only data to configure the links to the BE and waiting for the BXID reset to guarantee that all FE counters are synchronous. Now, the synchronization between the VELO FEs and BE readout boards takes place. On one side, each FE receives the synchronization command generated in the S-ODIN board and responds with a specific TFC frame through the readout links (see subsection 3.2.2). On the other side, the readout board, which by default is on idle mode (not taking data) waiting for the FE specific frame to lock to its BXID. Afterwards, a programmable number of header only data, the shutter is open again to start physics data taking, triggering on the proton-proton events based on the filling scheme of the LHC.

<sup>&</sup>lt;sup>1</sup>Header only data mode allows the FE links to stay active without driving valid data to the BE readout board.

Figure 4.4: PCIe40 board fully populated.

## 4.1 PCle40

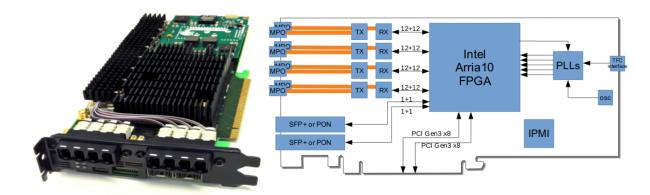

The PCIe40 is a 14 layer PCB hosting an Intel Arria 10 FPGA (device model 10AX115S4F45E3SG) [36]. This PCB is meant to be used in the ODE of LHCb and ALICE experiments, but in this thesis, I will focus on the LHCb case. The board is populated with eight Multi-fibre Push On (MPO) optical connections with 12 links each, four transmitters and four receivers that handle up to 48 links running at 10Gb/s on each direction. The Opto electrical conversion is performed in the MiniPODs, 1 per MPO, and each link is connected to a single FPGA high speed input/output. The PCIe40 board is controlled and read out via two independent PCIexpress version 3 of 8 links each, with a maximum combined throughput of 128Gb/s and a sustained 108Gb/s [37]. Moreover, two 3.2Gb/s bidirectional timing-trigger and control PON links are mounted, allowing the interface of the timing signals of the experiment.

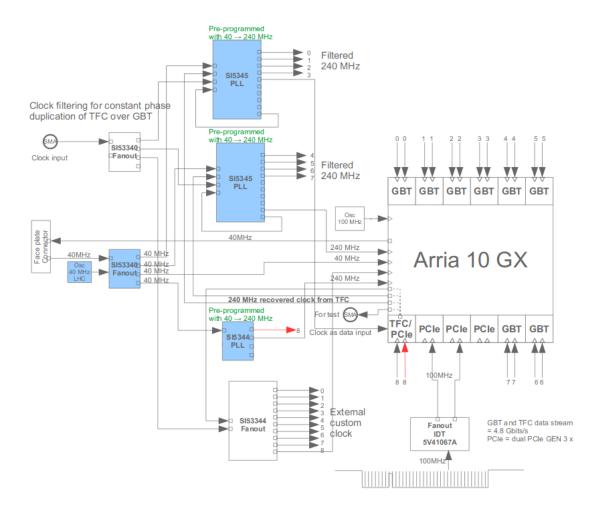

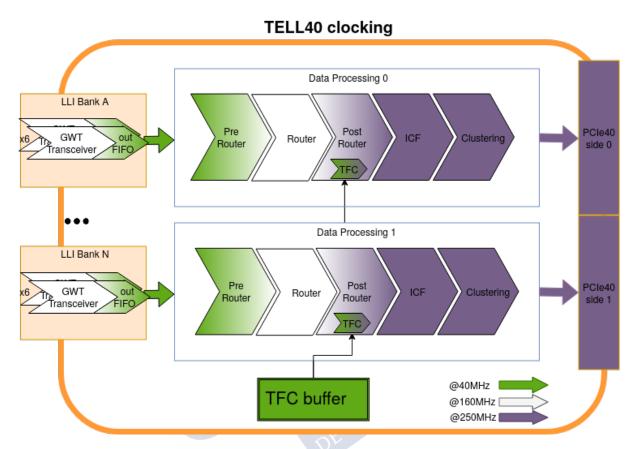

To improve the performance of the high speed data transmission on the FPGA, a very stable clock is needed, requiring the implementation of several external PLLs and Jitter cleaners (Si5345 [38]) that provide a clock with a jitter of 90 fs RMS, see Figure 4.5.

The functionality of the board is defined by its firmware. TELL40 and SOL40 firmwares are developed in an LHCb wide common framework with provision made for sub-detector specialization. The framework is focussed on the shared tasks for all sub-detectors like: input/output management, TFC interface, protocols handling, SCADA common developments, etc.

The FE data collected and processed in a single TELL40 board is propagated to the host computer through the PCIexpress connector. As it has two eight link interfaces, to reduce firmware complexity, two independent data-streams are instantiated, as it is shown for the VELO case in

Figure 4.5: PCIe40 clock distribution.

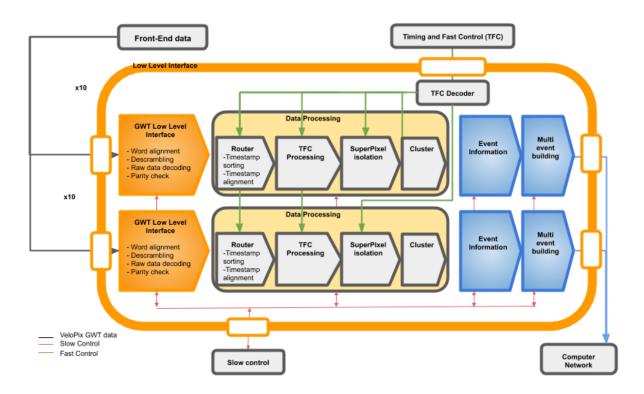

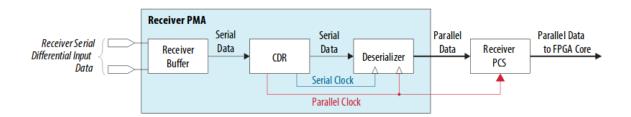

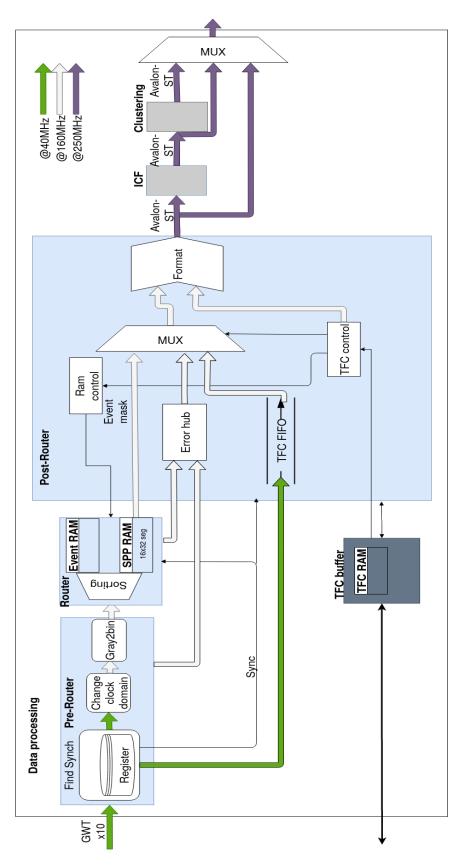

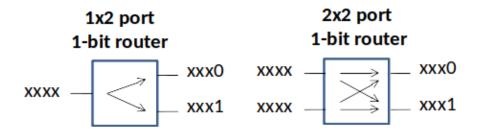

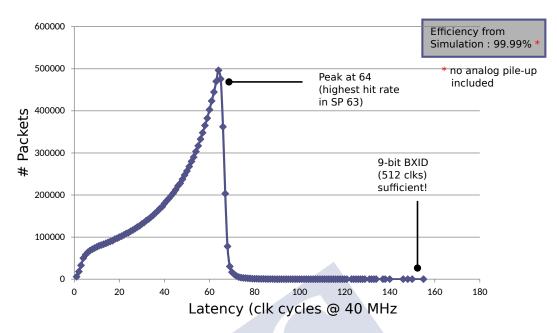

the Figure 4.6. Each of those framework data-streams has the following functionality blocks: GBT LLI that recovers the data from the optical fibre, error recovering block, a GBT decoding block, alignment of the different fibres according to their BXID information, TFC accept/reject of the data (and its associate communication with the system), sub-detector specific processing, identification of the events, event packaging and finally PCIexpress interface.

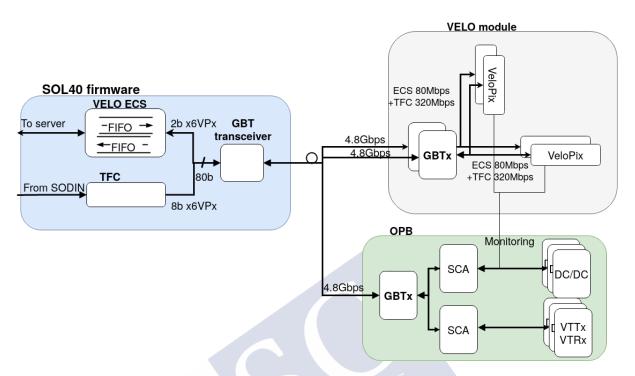

The SOL40 board has a common development that handles TFC communication with S-ODIN, slow control communication with the host computer and FE (see section 4.3 and section 4.4).

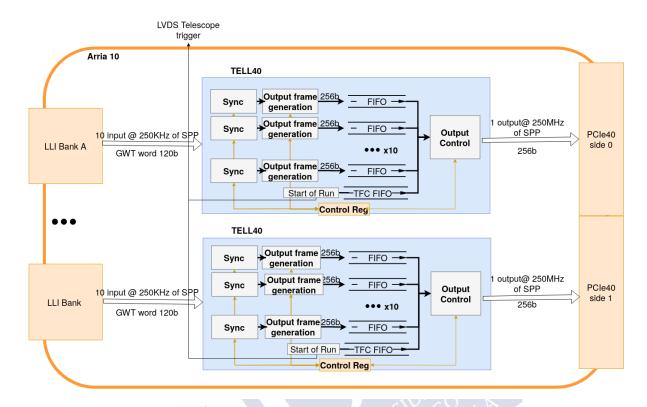

Figure 4.6: VELO DAQ firmware architecture. Two parallel data streams are instantiated (each one associated with a PCIexpress interface).

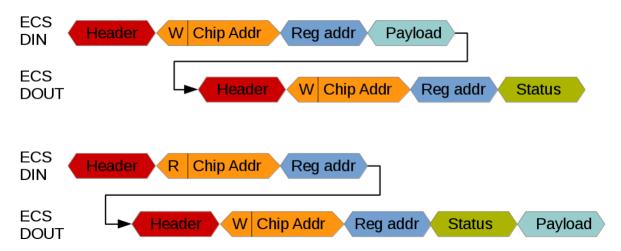

## 4.2 LHCb VELO TELL40 firmware

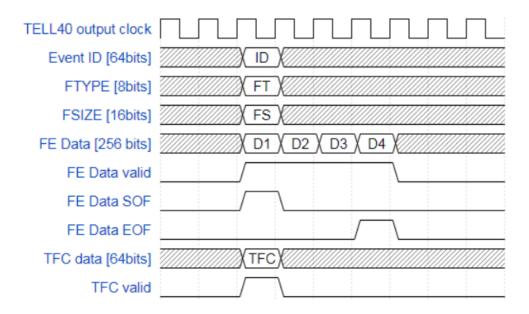

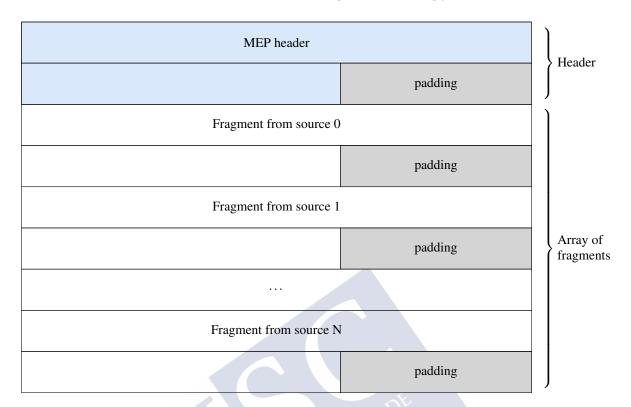

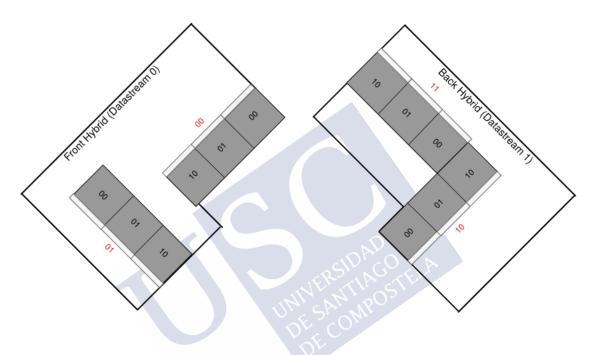

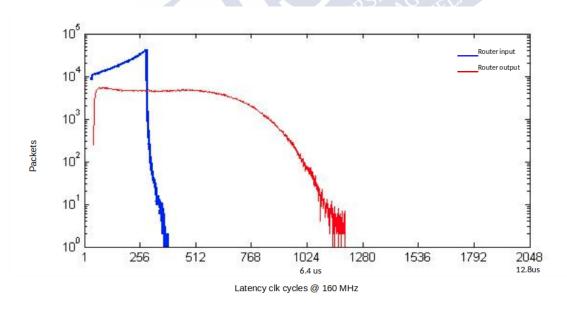

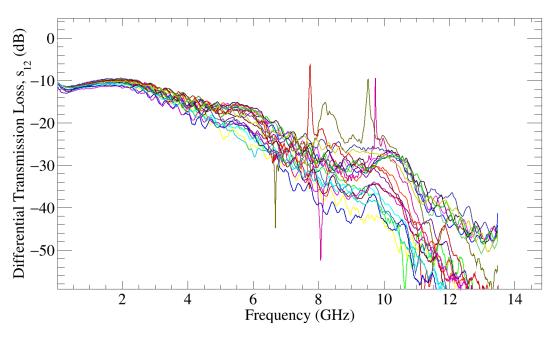

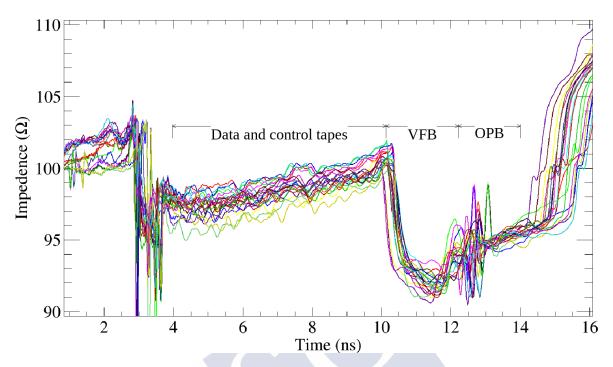

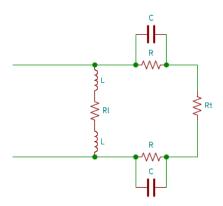

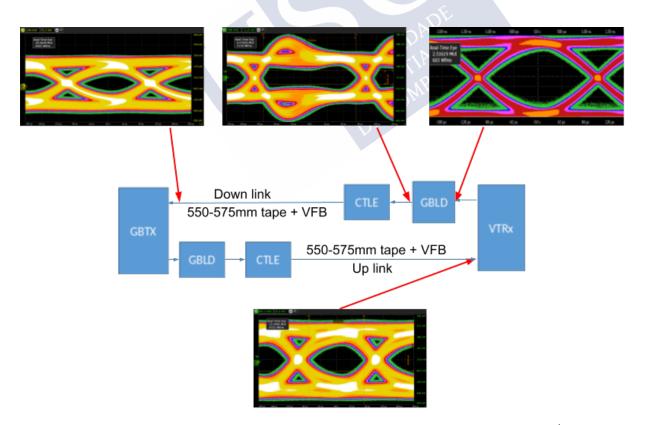

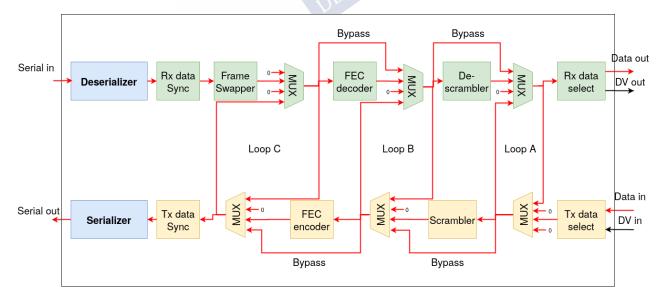

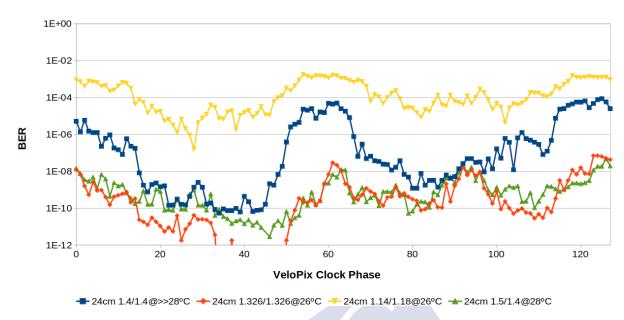

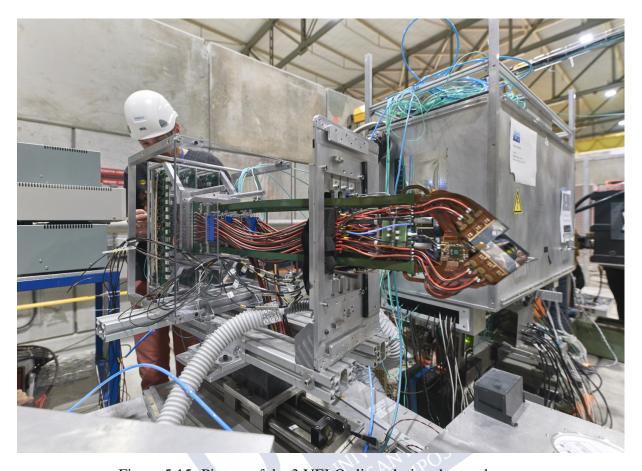

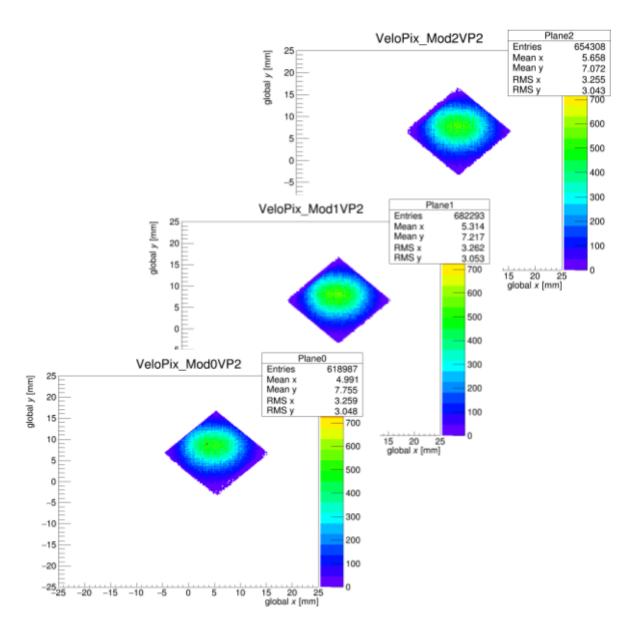

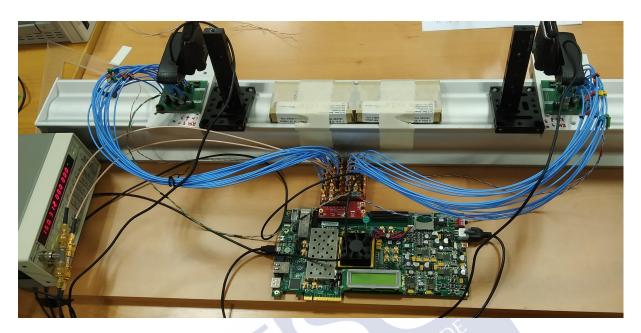

The VELO readout board firmware scheme (Figure 4.6), flushed into the PCIe40 card (TELL40), is almost a full modification of the LHCb firmware framework. The rationale for adopting such a strategy is that the VeloPix ASIC is the only LHCb FE reading out unsorted data over a specific protocol, (section 3.2). Hence, a new firmware transceiver had to be designed to handle the VELO protocol. This protocol does not support forward error correction and, thus, it does not exist an equivalent to the framework GBT error correction block. Nevertheless, error detection is performed with a parity checker discarding corrupt data that do not match with their parity (more information in subsubsection 4.2.1.3). The main task of the readout firmware is sorting the BXID timestamp information, but also some auxiliary processing is performed by flagging isolated hits and clustering the data. Unfortunately, some of the common developments