# Thermal and electrical stability assessment of AlGaN/GaN Metal-Oxide-Semiconductor High Electron Mobility Transistors (MOS-HEMT) with HfO<sub>2</sub> gate dielectric

Z. Gao\*, M. F. Romero, F. Calle, Member, IEEE

*Abstract*—AlGaN/GaN HEMTs and MOS-HEMTs using HfO<sub>2</sub> as gate dielectric have been analyzed at room temperature, after STA and TC test, during off-state electrical step stress, HTRB and PBTI tests. Results showed that the leakage current in as-fabricated MOS-HEMTs decreased by 10<sup>6</sup> and the on/off ratio increased by over 10<sup>4</sup> than the HEMTs. Moreover, it was even higher after a STA test, up to 10<sup>8</sup>, in the MOS-HEMTs, and the surface trapping effects were mitigated, especially if a KOH cleaning was used before HfO<sub>2</sub> deposition. The MOS-HEMTs also showed higher electrical stability after off-state step electrical stress, HTRB and PBTI tests.

*Index Terms*—AlGaN/GaN, HEMTs, HfO<sub>2</sub>, MOS-HEMTs, surface cleaning, electrical stress.

#### I.MOTIVATION AND OBJECTIVES

GaN based high electron mobility transistors (HEMTs) have drawn great attention due to their potential in high temperature (HT), high power and high frequency applications [1]. However, high gate leakage current and current collapse are still some of the most critical problems limiting the performance and reliability of the devices [2, 3]. MOS-HEMTs using gate insulators such as, SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, Gd<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> have been studied to solve this problem [3, 4]. In particular, HfO<sub>2</sub>, with electron affinity of 1.75-2.0 eV [5], band gap of 5.3 eV [6], was proven to be effective in reducing leakage current in Si, GaAs and GaN based MOS devices [7]. Although some authors do not use any particular treatment before dielectric deposition [8, 9], the use of a surface treatment, such as KOH, was shown to be effective in reducing the gate leakage in different GaN-based devices [10, 11]. However, further investigation on electrical stability and interface properties of high-k/GaN structures is still needed to achieve reliable and competitive AlGaN/GaN-based devices for RF and power applications.

In this work, AlGaN/GaN MOS-HEMTs and MOS diodes (MOSD) with  $HfO_2$  as gate dielectric and an

optimized KOH-based surface treatment was assessed at room temperature (RT) and after various thermal and electrical stress tests, in order to compare their degradation mechanisms with the HEMTs and those MOS-HEMTs with only organics cleaning prior to HfO<sub>2</sub> deposition.

### **II.EXPERIMENTAL DETAILS**

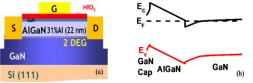

The devices were fabricated on AlGaN/GaN heterostructures with a GaN cap (2 nm) grown on Si(111) by metal-organic chemical vapor deposition. The Al content and the thickness of the AlGaN layer is 31% and 22 nm, respectively. The GaN layer (0.6  $\mu$ m) is unintentionally doped. A schematic cross section of the devices is shown in Fig. 1. Both HEMTs and diodes were processed simultaneously on the wafer as follows.

Fig. 1. (a) Schematic cross-section and (b) the corresponding energy band diagram of the heterostructure.

First, ohmic contacts were defined using a Ti/Al/Ni/Au (20/120/40/50 nm) metal stack, evaporated by e-beam and rapid-annealed at 850°C for 30 s in N<sub>2</sub> ambient. Afterwards, mesa etching device isolation (100 nm depth) was carried out by inductively coupled plasma etching using Cl<sub>2</sub>/Ar based process. The contact resistance (R<sub>c</sub>) of the ohmic contacts was 0.75  $\Omega$ ·mm and the sheet resistance (R<sub>sheet</sub>) of the 2-dimensional electron gas was 420  $\Omega/\Box$ , as calculated by means of the transmission line method. The sheet carrier density (n<sub>s</sub>) and the electron mobility ( $\mu$ ) of the devices calculated from Hall measurements were 0.7×10<sup>13</sup> cm<sup>-2</sup> and 1016 cm<sup>2</sup>/V·s, respectively.

The wafer was divided into three pieces, one of them (named "Control") was used as a reference for HEMTs processing. The other two pieces were used to process

This work was supported by RUE (CSD2009-00046) and CAVE (TEC2012-38247) projects, from Ministerio de Ciencia e Innovación of Spain. MFR acknowledges funding from Programa Juan de la Cierva-Incorporación (Spain) under Contract No. IJCI-2014-19473. Z. Gao and F. Calle are with the ISOM and Dep. Ingeniería Electrónica, ETSI de Telecomunicación, Universidad Politécnica de Madrid, Madrid, Spain. (e-mail: gaozhan.veronica@isom.upm.es). M. F.

Romero is with the Facultad de Ciencias Jurídicas y Empresariales, Universidad Francisco de Vitoria, 28223 Pozuelo de Alarcón, Spain, and also with the Departamento de Ingeniería Electrónica, Escuela Téc-nica Superior de Ingenieros de Telecomunicación, Instituto de Sistemas Optoelectrónicos y Microtecnología, Universidad Politécnica de Madrid, 28040 Madrid, Spain.

MOS-HEMTs with HfO<sub>2</sub> films (5 nm thickness).

Prior to  $HfO_2$  deposition, one sample (named "Org") was cleaned only with organics solvents: acetone (5 min), methanol (5 min) and rinsed with deionized water, and the other (named "KOH") was cleaned with an optimized cleaning with KOH (0.5 M) for 20 s after organics.  $HfO_2$  was deposited in an ALD reactor at 200°C using Hf based precursors and H<sub>2</sub>O, by Ctechnano Coating Technologies [12].

Subsequently, all the samples were gate patterned using standard photolithography. Metallization of the gate contact Ni/Au (20/200 nm) and lift-off were performed. The gates (G) of the HEMTs are 1.2  $\mu$ m in length and 50  $\mu$ m in width, and the distance between source (S) and drain (D) is 5  $\mu$ m, with the same S-G and G-D distances. The diodes have square shapes with a side length of 100  $\mu$ m.

Finally, the Ti/Au feed metallization was defined with the dielectric layer on top of ohmic metal previously etched using diluted HF:H<sub>2</sub>O (1:10) for 5 minutes.

Some of the HEMTs and MOS-HEMTs were used to analyze the thermal stability after a short thermal annealing (STA) at 400°C for 10 min and a thermal cycle (TC) test from 25°C to 325°C with a step of 100°C. Current-voltage (I-V) measurements at RT before and after STA, and at each step during TC test were taken.

Another set of devices was used to test the device robustness after electrical stresses including: an off-state electrical stress, a HT reverse bias (HTRB) test and a positive bias temperature instability (PBTI) test. The off-state electrical stress consisted of a long-term drainbias step stress at RT, keeping the gate source voltage  $(V_{GS})$  at -7 V (off-state), and sweeping the drain source voltage (V<sub>DS</sub>) from 13 V to 39 V, with a 2 V step for 1800 s at each step. The HTRB test was taken with  $V_{DS}$ = 23 V and  $V_{GS} = -7$  V during 120 hours with a base plate T of 125°C. The PBTI test was series of stress sections with increasing stress time from 200 s to 1000 s. During stress, the devices were subject to a positive gate stress from 0.6 V to 1.4 V while the S and D grounded. The same electrical measurements were systematically monitored before and right after each stress step, in order to assess the devices stabilities.

#### **III.RESULTS AND DISCUSSION**

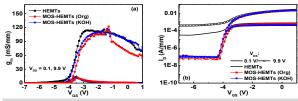

## A. As fabricated devices

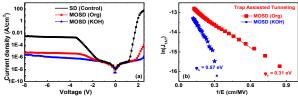

I-V characteristics of the AlGaN/GaN Schottky diodes (SD) and HfO<sub>2</sub> MOSD are shown in Fig. 2(a). Results show that the reverse gate current ( $I_{rev}$ ) of MOSD is about 10<sup>4</sup> lower than the SD, regardless of cleaning procedure. However, the lowest forward current ( $I_{for}$ ) is observed in the MOSD (KOH), about 10<sup>6</sup> lower than SD, and 10 times lower than MOSD (Org). Schottky barrier height was close to 1.0 eV for the SD,

and the ideality factor was about  $2.0\pm0.6$ , extracted from the forward I-V curve, close to the results shown in the literatures [13], [14].

Fig. 2. (a) Gate leakage current and (b) TAT fitting plots of  $HfO_2$  based MOSD and SD.

In addition, the electron transport mechanisms were analyzed in both devices using the techniques discussed in [15], [16]. For the SD, Schottky emission (SE) fit well with the experimental I-V curves, which means the dominant electron transport mechanism was SE, and for the MOSDs (Org and KOH), trap assisted tunneling (TAT) fit well with the experimental results, indicating TAT in the oxide layer is the dominate electron transport mechanism, and the activation energy was calculated to be 0.31 eV (at  $V_G = 1$  V to 2.8 V) and 0.57 eV (at  $V_G = 1.2$  V to 2.5 V), respectively, as shown in Fig. 2(b).

The energy level at 0.31 eV is likely due to carbon substituting N(C<sub>N</sub>) [17]. The deep traps with activation energy level of 0.57 eV are often observed at GaN side of the AlGaN/GaN interface [18–20]. Interestingly, the carbon related traps were not observed in the MOSD (KOH), proving that the KOH cleaning could remove the C on the GaN surface effectively [21].

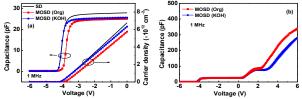

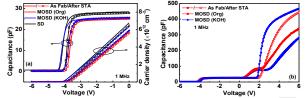

The capacitance-voltage (C-V) curves and the carrier density ( $n_s$ ) of the diodes are shown in Fig. 3(a). From the MOSD, the dielectric constant of the HfO<sub>2</sub> is about 15, in agreement with the literature [22]. Neither hysteresis nor frequency dispersion were observed in SD or MOSDs. No threshold voltage shift ( $\Delta V_{th}$ ) was observed in MOSD (KOH) with respect to the SD, however,  $\Delta V_{th}$  about +0.4 V was observed in MOSD (Org), possibly due to negative fixed oxide charges at the oxide/heterostructure interface [23, 24].

Fig. 3. (a) C-V and carrier density characteristics of SD and MOSDs and (b) C-V curves the MOSDs at the -6 V to 6 V range.

In order to further study the HfO<sub>2</sub> dielectric and HfO<sub>2</sub>/GaN interface, MOSDs were swept from -6 to 6 V (Fig. 3(b)). When positive gate bias was applied, electrons accumulated at the AlGaN layer, leading to dielectric capacitance ( $C_{HfO2}$ ). An extra step (at ~1 V) is observed in this region, which could be related to trapping centers at the HfO<sub>2</sub>/GaN interface, possibly due to lack of post-deposition annealing [25]. The interface state density ( $D_{it}$ ) as a function of energy level can be

calculated using conductance method [26]. The equivalent parallel conductance  $\left(\frac{G_p}{\omega}\right)$  can be calculated from the experimental measurements:

$$\frac{G_p}{\omega} = \frac{\omega G_m C_b^2}{G_m^2 + \omega^2 (C_b - C_m)^2},\tag{1}$$

where  $\omega = 2\pi f$ , f,  $G_m$  and  $C_m$  are measurement frequency, measured conductance and capacitance and  $C_b$  is the static state capacitance.

On the other hand,

$$\frac{G_p}{\omega}$$

is given as:

$$\frac{G_p}{\omega} = \frac{q\omega\tau_{it}D_{it}}{1+(\omega\tau_{it})^2}$$

(2)

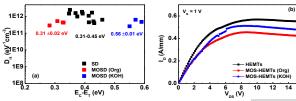

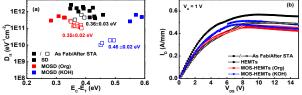

where  $\tau_{it}$  is the trap time constant. By fitting the experimental  $\frac{G_p}{\omega}$  curves with Eq. 2,  $D_{it}$  can be achieved. The results are shown in Fig. 4 (a). The traps located at energy level of 0.56±0.01 eV in MOSD (KOH), 0.31±0.02 eV in MOSD (Org), in the range of 0.31-0.45 eV in SD.

Fig. 4. (a)  $D_{it}$  as a function of energy level for the diodes and (b)  $I_D$ - $V_{DS}$  curves of HEMTs and MOS-HEMTs.

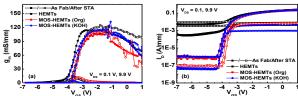

I-V characteristics of the (MOS-)HEMTs are shown in Fig. 4(b). The MOS-HEMTs showed decreased maximum drain current ( $I_{D,max}$ ): by -10% (Org) and -16% (KOH), and increased ON resistance ( $R_{ON}$ ): by 11% (Org) and 9% (KOH), compared with the HEMTs. Also, the maximum transconductance ( $g_{m,max}$ ) decreased by -3% in the MOS-HEMTs (Org and KOH) (Fig. 5(a)). Similar to MOSDs, no V<sub>th</sub> shift ( $\Delta V_{th}$ ) was observed in MOS-HEMTs (KOH), and +0.1 V shift in MOS-HEMTs (Org).

Fig. 5. (a)  $g_m\text{-}V_{\rm GS}$  and (b)  $I_D\text{-}V_{\rm GS}$  curves of the MOS-HEMTs and HEMTs at  $V_{\rm DS}$  = 0.1 V, 9.9 V.

In addition, regardless of cleaning technique, the MOS-HEMTs showed  $I_{D, OFF}$  (V<sub>G</sub>=-7 V) smaller than 0.1  $\mu$ A/mm and on/off ratio 10<sup>7</sup>, 10<sup>4</sup> times higher than the HEMTs (Fig. 5(b)). These results show that MOS-HEMTs using HfO<sub>2</sub> can reduce both drain and gate leakage currents.

## **B.**Thermal Stability

## 1) Short Thermal Annealing Test (STA)

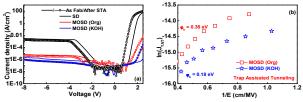

I-V characteristics of the SDs and MOSDs before and after the STA are shown in Fig. 6(a). After the STA, MOSD (KOH) showed the lowest  $I_{rev}$  and  $I_{for}$ , about 1

$\mu$ A/cm<sup>2</sup> (V<sub>G</sub> = -8 V) and <u>1 m</u>A/cm<sup>2</sup> (V<sub>G</sub> = 3 V). *I<sub>rev</sub>* decreased after STA, by 10<sup>2</sup> in SD, and by 10 times in MOSDs, regardless of cleaning procedure. *I<sub>for</sub>* increased slightly in the diodes.

The main electron transport mechanism in the MOSD (KOH) is still TAT after the STA, but with shallow vacancies with activation energy of 0.18 eV (at  $V_G = 0.8$  V to 2 V) (Fig. 6(b)). According to literature, this trap center at energy level in the range 0.17-0.24 eV could be related to linear line defects due to the dangling bonds along dislocation cores [27]. In the case of the MOSD (Org), the activation energy is about 0.38 eV (at  $V_G = 1$  V to 2.5 V) and it is likely due to HfO<sub>2</sub>/GaN interface traps on the oxide side [28].

Fig. 6. (a) Gate leakage current of SD and MOSDs and (b) TAT fitting plots of MOSDs after STA.

The C-V characteristics and the  $n_s$  of the diodes before and after the STA are shown in Fig. 7(a). SD and MOSD (KOH) showed a more positive V<sub>th</sub> shift (+0.2 V) than the MOSD (Org) (+0.02 V). This could be explained by the traps at AlGaN/GaN interface with activation energy of 0.57 eV, which were de-trapped after the STA, causing the positive V<sub>th</sub> shift.

Fig. 7. (a) C-V and  $n_s$  characteristics of SD and MOSDs and (b) positive sweep of the MOSDs before and after STA.

The C-V curves of the MOSDs (KOH) during positive sweep in Fig. 7(b) showed that the extra step, assigning to trapping centers at the HfO<sub>2</sub>/GaN interface, is vanished after the STA, as expected. Interface density as a function of energy level calculated using the conductance method are shown in Fig. 8(a). After STA, the traps in the SD and in the MOSD (Org) are located in the same energy level (around 0.35 eV), but in the case of MOSD (KOH) are located at an energy level of 0.45 eV, similar traps were observed in Al<sub>2</sub>O<sub>3</sub>/AlGaN interface [29]. The energy level of the trapping centers was further summarized in Table 1.

Table 1 Energy level of the trapping centers calculated from I-V and C-f characteristics in the SD and MOSDs before and after STA.

| $\mathbf{E}_{\mathbf{C}}\mathbf{-}\mathbf{E}_{\mathbf{T}}\left(\mathbf{eV}\right)$ |        | SD         | MOSD<br>(Org) | MOSD<br>(KOH) |

|------------------------------------------------------------------------------------|--------|------------|---------------|---------------|

| I-V                                                                                | Before |            | 0.31          | 0.57          |

|                                                                                    | After  |            | 0.38          | 0.18          |

| G <sub>p</sub> /w-f                                                                | Before | 0.31~ 0.45 | 0.31          | 0.56          |

|                                                                                    | After  | 0.35       | 0.35          | 0.45          |

I-V characteristics of the HEMTs and MOS-HEMTs before and after the STA are shown in Fig. 8(b). After STA,  $I_{D,max}$  decreased and  $R_{ON}$  increased in all the devices, which is consistent with the n<sub>s</sub> decrease shown in Fig. 7(a). The magnitude of  $I_{D,max}$  and  $g_{m,max}$  were close among all three kinds of devices, 0.47±0.1 A/mm and 115 mS/mm, respectively.  $R_{ON}$  of the MOS-HEMTs was 8.2  $\Omega$ ·mm, 15% smaller than the HEMTs.

Transfer characterization showed that  $\Delta V_{th}$  was about +0.2 V for HEMTs and MOS-HEMTs (KOH), +0.1 V for MOS-HEMTs (Org). This is similar to the results of SD and MOSD, which can be caused by the detrapped interface traps at the AlGaN/GaN interface after STA.

Fig. 8. (a)  $D_{it}$  as a function of energy level for the diodes and (b)  $I_D$ - $V_{DS}$  curves of HEMTs and HfO<sub>2</sub> MOS-HEMTs before and after STA.

$I_{OFF}$  decreased by 10 to  $10^2$  times in the MOS-HEMTs (Org and KOH) (Fig. 9(b)), in good agreement with the MOSDs. The highest on/off ratio after the STA (~  $10^7$ ) corresponded to MOS-HEMTs (KOH), which is about  $10^4$  higher than the HEMTs, similar to that before STA. Therefore, MOS-HEMTs using HfO<sub>2</sub> with a KOH cleaning are suitable for high speed switch applications working at HT.

Fig. 9. (a)  $g_m\text{-}V_{GS}$  and (b)  $I_D\text{-}V_{GS}$  curves of  $HfO_2$  MOS-HEMTs and HEMTs before and after STA.

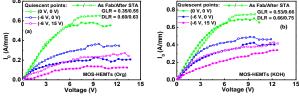

Besides, pulsed measurements were taken in the MOS-HEMTs (KOH and Org) before and after STA (Fig. 10). The results showed that GLR increased by 25% in the MOS-HEMTs (KOH), indicating less surface trapping effects after STA. This is caused by Ga vacancies or oxygen complex reduction after annealing. Therefore, the STA is helpful to reduce the trapping effects in the MOS devices. Moreover, KOH cleaning can help reduce the C-related defects on the surface of the devices, further improve the devices characteristics.

Fig. 10. Pulsed  $I_D$ - $V_{DS}$  curves of HfO<sub>2</sub> based (a) MOS-HEMTs (Org) and (b) MOS-HEMTs (KOH) before and after STA.

# 2) Thermal Cycle Test (TC)

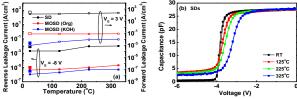

Schottky and MOS-devices were subjected to a TC test from RT to 325°C with increment of 100°C. The  $I_{rev}$  (at  $V_G = -8$  V) and  $I_{for}$  (at  $V_G = 3$  V) evolution of the diodes with T are shown in Fig. 11. Results showed that  $I_{rev}$  increased gradually with T in all devices.  $I_{rev}$  and  $I_{for}$  of MOSDs (Org and KOH) at 325°C were about 10<sup>3</sup> lower than that of the SDs, demonstrating the effectiveness of the HfO<sub>2</sub> gate dielectric in the suppression of gate leakage current at HT. In addition,  $I_{rev}$  and  $I_{for}$  exhibited smaller than 10 times increase after TC test, showing that the increase of  $I_{rev}$  caused by HT is not permanent.

Fig. 11. (a)  $I_{\rm rev}$  and  $I_{\rm for}$  evolution of SDs and MOSDs and (b) C-V curves of SD during TC test.

No hysteresis was observed in the CV curves of SDs or MOSDs (Org and KOH) during the TC test, indicating that very few traps in the oxide near the semiconductor interface are activated by T. However, midgap-to-flatband stretchout was observed in the SDs and MOSDs (Org and KOH) with rising T, as shown in Fig. 11(b). The interface trap density was estimation with a rough calculation using the Eq. 2. The D<sub>it</sub> density was calculated to be  $5.5 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> for HEMTs,  $2.8 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> for MOSDs (Org) and  $1.9 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> for MOSDs (KOH). The stretch out observed here are most possibly due to the thermal inducted hot electrons at the AlGaN/GaN interface.

Fig. 12. (a) Evolution of  $I_{D,max}$ ,  $R_{ON}$  and (b)  $g_{m,max}$ ,  $V_{th}$  during TC test.

The electrical parameters  $(I_{D,max}, g_{m,max}, R_{ON}, V_{th})$ evolutions of the devices (Fig. 12) show that I<sub>D,max</sub> and g<sub>m,max</sub> decrease with increasing T, and the decrease rate of MOS-HEMTs are smaller than HEMTs, and they are similar between the two devices. ID,max decrease of MOS-HEMTs (KOH) at 325°C was ~50%, smaller than MOS-HEMTs (Org) and HEMTs. Also it is smaller compared with the results in previous studies, where ~70% I<sub>D.max</sub> showed decrease at 425°C in Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN MOS-HFETs [30], I<sub>D,max</sub> decreased by ~40% at 200°C in SiO<sub>2</sub>/AlGaN/GaN grown on sapphire [31], and I<sub>D.max</sub> decreased by ~60% at 425°C in Gd<sub>2</sub>O<sub>3</sub>/AlGaN/GaN MOS-HEMTs [32]. In addition, g<sub>m,max</sub> decreased 45% in MOS-HEMTs (KOH) at 325°C,

which is slightly lower than the  $Al_2O_3/AlGaN/GaN$  MOS-HFETs, where  $g_{m,max}$  dropped by ~55% at 200°C [30]. These results showed that the MOS-HEMTs using HfO<sub>2</sub> with KOH cleaning have better thermal stability compared with previous studies [29-31].

$V_{th}$  shift was due to the thermal activated hot electrons, in agreement with the C-V measurements. After TC test, MOS-HEMTs (KOH) showed recovery over 95%, MOS-HEMTs (Org) over 90% and HEMTs 85%, proving that the electrical properties decrease during TC test is not permanent. Results showed that HfO<sub>2</sub> MOS-HEMTs would be a good choice for HT operation, particularly those with a KOH cleaning.

### C.Electrical stress

## 1) Step Stress

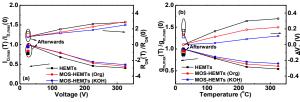

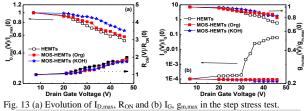

The devices were subjected to a step stress test, as described in section II. The evolutions of the electrical parameters as a function of the stress step in the three kinds of devices are shown in Fig. 13. All devices showed I<sub>D, max</sub> decrease, but the MOS-HEMTs (KOH) showed the smallest change (~ 17%). I<sub>G, off</sub> increase of the MOS-HEMTs are negligible regardless of cleaning procedures. However, HEMTs showed dramatical I<sub>G,OFF</sub> increase after  $V_{DG} = 30$  V, leading to devices degradation [33]. This critical voltage phenomena can be explained by the inverse piezo effects together with the hot electrons in the devices [33–35].

Crystallographic defects could be induced by the inverse piezoelectric effect caused by high vertical electric field, and acting as trapping centers at the G-D edge of the HEMTs [24, 25, 27, 28]. Also, the electron diffusion could be accelerated due to the presence of hot electrons during stress, which may accelerate the piezoelectric strain effects, enhancing the device degradation [29, 30]. This behavior was not observed in the MOS-HEMTs up to 47 V, proving that the HfO<sub>2</sub> dielectric can inhibit early degradation of the devices.

# 2) High Temperature Reverse Bias (HTRB)

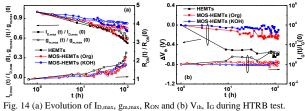

Also, the devices were subjected to HTRB test, as described in section II. The devices electrical parameters variations over stress time in Fig. 14 (a) showed that after 120 h of HTRB test, the HEMTs showed 48%  $I_{D.max}$  decrease, 40%  $g_{m,max}$  decrease and 1.5 times  $R_{ON}$  increase. However, the MOS-HEMTs showed much smaller change, especially the MOS-HEMTs(KOH),  $I_{D.max}$  and  $g_{m,max}$  decreased by 28% and 18%, respectively, and  $R_{ON}$  increased by 70%.  $I_{G,OFF}$  increased by over 10 times in the HEMTs, but not in the MOS-

HEMTs (KOH and Org).  $V_{th}$  shifts were -0.6 V in HEMTs, -0.1 V ~ -0.3 V in MOS-HEMTs (Org), and - 0.02 V ~ -0.15 V in MOS-HEMTs (KOH).

The  $V_{th}$  shift as well as the electrical degradation during HTRB test are due to oxygen diffusion and field driven oxidation [41] or the structural defects caused by the electrical stress [42].

In the HEMTs, oxygen would diffuse to the GaN cap, leading to oxidation of the surface, forming grooves on the device surface [41], which might develop to pits and cracks and introduce trapping center, leading to leakage increase and electrical degradation in the devices. Another possibility is inter-diffusion between the Au in the gate metal and Ga [43], together with the existence of holes, unbounded Ga<sup>3+</sup> or/and Al<sup>3+</sup> ions may occur [44]. With the injected oxygen, Ga<sub>2</sub>O<sub>3</sub> or/and Al<sub>2</sub>O<sub>3</sub> could be created, bringing about pits and cracks, and causing device failure.

In the MOS-HEMTs,  $HfO_2$  layer can prevent the infusion of oxygen or oxidation of the GaN, thus mitigate the structural degradation, especially in the case of the MOS-HEMTs with KOH cleaning.

After the HTRB tests, all the MOS-HEMTs showed over 98% recovery ( $I_{D,max}$ ,  $R_{ON}$ ,  $g_{m,max}$ ,  $V_{th}$ ), the HEMTs showed 85% recovery, indicating that the HfO<sub>2</sub> layer helped protect the device from possible structure damage during electrical stress.

### 3) Positive bias temperature instability (PBTI)

PBTI tests were performed on the MOS-HEMTs, as described in section II.  $g_{m,max}$  decreases and  $V_{th}$  shifts were observed on both kinds of MOS-HEMTs.  $g_{m,max}$ decrease is due to the channel mobility decrease by ways of Coulomb scattering during PBTI stress. Dependent of  $V_{th}$  shift on stress time and stress voltage follows up a power law relationship [45]:

$$\Delta V_{th} \sim (V_{GS,srtess} - V_{th0})^{\gamma} t_{stress}^{n}$$

(3)

where  $V_{th0}$  is the initial  $V_{th}$  value, *n* and  $\gamma$  are stress time and stress voltage exponent, respectively.  $\gamma$  indicates the accessibility of defects in the gate dielectric, where the lower  $\gamma$ , the wider distribution of dielectric defects centered around the channel Fermi level. [45] By fitting the  $\Delta V_{th}$  with Eq. 3, n and  $\gamma$  can be extracted.  $\gamma$  is fitted to be 1.0 for MOS-HEMTs (Org) and 2.5 for MOS-HEMTs (KOH), indicating that the MOS-HEMTs (KOH) is much more promising for reliability improvement.

#### **IV.CONCLUSIONS**

In summary, this work has showed the improvement of electrical and thermal stability of GaN based MOS-HEMTs with HfO<sub>2</sub> compared with standard HEMTs, and the effects of KOH cleaning before dielectric deposition. Results proved that an optimized KOH treatment prior to HfO<sub>2</sub> deposition can enhance the beneficial effects of HfO<sub>2</sub>/AlGaN/GaN MOS-HEMTs with respect to standard HEMTs: lower leakage current and fixed interface traps, higher drain current than the standard design. Also, this work has proven that STA can improve the interface properties of all the devices, especially in the MOS devices using KOH cleaning. Three kinds of electrical stress were carried out on the devices: step stress, HTRB and PBTI tests. HfO2 MOS-HEMTs help improve the device reliability after step stress and HTRB test and MOS-HEMTs (KOH) are more reliable than MOS-HEMTs (Org) after PBTI test.

In general, this work showed that  $HfO_2$  MOS-HEMTs (KOH) can help mitigate the degradation effects caused by thermal or electrical stress, and it will be a good candidate for high temperature and extensive life-time operations in the future.

#### References

U. K. Mishra *et al.*, "AlGaN/GaN HEMTs-an overview of device operation and applications," *Proc. IEEE*, 90, 6, 1022–1031, 2002, DOI: 10.1109/JPROC.2002.1021567.

[2]S. Turuvekere *et al.*, "Evidence of Fowler–Nordheim Tunneling in Gate Leakage Current of AlGaN/GaN HEMTs at Room Temperature," *IEEE Trans. Electron Devices*, 61, 12, 4291–4294, Dec. 2014, doi: 10.1109/TED.2014.2361436.

[3] Z. Yatabe *et al.*, "Insulated gate and surface passivation structures for GaNbased power transistors," *J. Phys. D. Appl. Phys.*, 49, 39, 393001, Oct. 2016, DOI:10.1088/0022-3727/49/39/393001.

[4] M. A. A. Khan *et al.*, "AlGaN/GaN metal oxide semiconductor heterostructure field effect transistor," *Electron Device Lett. IEEE*, 21, 2, 63–65, Feb. 2000, DOI: 10.1109/55.821668.

[5] S. Monaghan *et al.*, "Determination of electron effective mass and electron affinity in HfO<sub>2</sub> using MOS and MOSFET structures," *Solid. State. Electron.*, 53, 4, 438–444, Apr.2009, DOI: 10.1016/j.sse.2008.09.018.

[6] M. C. Cheynet *et al.*, "Crystal structure and band gap determination of HfO<sub>2</sub> thin films," *J. Appl. Phys.*, 101, 5, 54101, Mar. 2007, DOI: 10.1063/1.2697551.

[7] A. Fontser*e et al.*, "Wafer scale and reliability investigation of thin HfO<sub>2</sub> AlGaN/GaN MIS-HEMTs," *Microelectron. Reliab.*, 52, 9–10, 2220–2223, Sep. 2012, DOI: 10.1016/j.microrel.2012.06.131.

[8] Y. C. Chang *et al.*, "Structural and electrical characteristics of atomic layer deposited high κ HfO<sub>2</sub> on GaN," *Appl. Phys. Lett.*, 90, 23, 232904, Jun. 2007, DOI: 10.1063/1.2746057.

[9] X. Sun *et al.*, "Study of gate oxide traps in HfO<sub>2</sub>/AlGaN/GaN metal-oxidesemiconductor high-electron-mobility transistors by use of ac transconductance method," *Appl. Phys. Lett.*, 102, 10, 103504, Mar. 2013, DOI: 10.1063/1.4795717.

[10] H. G. Kim *et al.*, "Effect of KOH treatment on the Schottky barrier height and reverse leakage current in Pt/n-GaN," *J. Electron. Mater.*, 35, 1, 107–112, Jan. 2006, DOI: 10.1007/s11664-006-0191-0.

[11] S. Ganguly *et al.*, "Performance enhancement of InAlN/GaN HEMTs by KOH surface treatment," *Appl. Phys. Express*, 7, 3, 34102, Mar. 2014, DOI: 10.7567/APEX.7.034102.

[12] Ctechnano, "http://ctechnano.com/coating-technologies/what-is-ald/."

[13] Y. Lv *et al.*, "Extraction of AlGaN/GaN heterostructure Schottky diode barrier heights from forward current-voltage characteristics," *J. Appl. Phys.*, 109, 7, 74512, Apr. 2011, DOI: 10.1063/1.3569594.

[14] H. Kim et al., "Passivation effects in Ni/AlGaN/GaN Schottky diodes by annealing," Appl. Phys. Lett., 89, 5, 1–4, 2006, DOI: 10.1063/1.2234569.

[15] D. Yan *et al.*, "On the reverse gate leakage current of AlGaN/GaN high electron mobility transistors," *Appl. Phys. Lett.*, 97, 15, 153503, 2010, DOI: 10.1063/1.3499364.

[16] F. Husna *et al.*, "High-Temperature Performance of AlGaN/GaN MOSHEMT With SiO<sub>2</sub> Gate Insulator Fabricated on Si (111) Substrate," *IEEE*

*Trans. Electron Devices*, 59, 9, 2424–2429, Sep. 2012, DOI: 10.1109/TED.2012.2204888.

[17] M. Matsubara and E. Bellotti, "A first-principles study of carbon-related energy levels in GaN. I. Complexes formed by substitutional/interstitial carbons and gallium/nitrogen vacancies," J. Appl. Phys., 121, 19, 195701, May 2017, DOI: 10.1063/1.4983452.

[18] A. R. Arehart *et al.*, "Direct observation of 0.57eV trap-related RF output power reduction in AlGaN/GaN high electron mobility transistors," *Solid. State. Electron.*, 80, 19–22, Feb. 2013, DOI: 10.1016/j.sse.2012.09.010.

[19] A. Y. Polyakov and I.-H. Lee, "Deep traps in GaN-based structures as affecting the performance of GaN devices," *Mater. Sci. Eng. R Reports*, 94, 1–56, Aug. 2015, DOI: 10.1016/j.mser.2015.05.001.

[20] A. Y. Polyakov *et al.*, "Deep Traps in AlGaN/GaN High Electron Mobility

[20] A. Y. Polyakov et al., "Deep Traps in AlGaN/GaN High Electron Mobility Transistors on SiC," ECS J. Solid State Sci. Technol., 5, 10, Q260–Q265, Sep. 2016, DOI: 10.1149/2.0191610jss.

[21] M. Diale et al., "Analysis of GaN cleaning procedures," Appl. Surf. Sci., 246, 1–3, 279–289, Jun. 2005, DOI: 10.1016/j.apsusc.2004.11.024.

[22] C. F. Shih et al., "Investigations of GaN metal-oxide-semiconductor

[22] C. F. Shih *et al.*, "Investigations of GaN metal-oxide-semiconductor capacitors with sputtered HfO<sub>2</sub> gate dielectrics," *J. Alloys Compd.*, 480, 2, 541– 546, Jul. 2009, DOI: 10.1016/j.jallcom.2009.01.141.

[23] G. Dutta *et al.*, "Positive Shift in Threshold Voltage for Reactive-Ion-Sputtered Al2O3/AlInN/GaN MIS-HEMT," *IEEE Electron Device Lett.*, 35, 11, 1085–1087, Nov. 2014, DOI: 10.1109/LED.2014.2357837.

[24] S. Ganguly *et al.*, "Presence and origin of interface charges at atomic-layer deposited Al<sub>2</sub>O<sub>3</sub>/III-nitride heterojunctions," *Appl. Phys. Lett.*, 99, 19, 1–4, 2011, DOI: 10.1063/1.3658450.

[25] T. Hashizume *et al.*, "State of the art on gate insulation and surface passivation for GaN-based power HEMTs," *Mater. Sci. Semicond. Process.*, vol. 78, no. September, pp. 85–95, May 2018, DOI: 10.1016/j.mssp.2017.09.028

[26] X. Lu et al., "Study of Interface Traps in AlGaN/GaN MISHEMTs Using LPCVD SiN<sub>x</sub> as Gate Dielectric," *IEEE Trans. Electron Devices*, 64, 3, 824– 831, Mar. 2017, DOI: 10.1109/TED.2017.2654358.

[27] H. K. Cho *et al.*, "Electron traps and growth rate of buffer layers in unintentionally doped GaN," *J. Cryst. Growth*, 223, 1–2, 38–42, Feb. 2001, DOI: 10.1016/S0022-0248(00)00982-9.

[28] S. Liu *et al.*, "Interface/border trap characterization of Al<sub>2</sub>O<sub>3</sub>/AlN/GaN metal-oxide-semiconductor structures with an AlN interfacial layer," *Appl. Phys. Lett.*, 106, 5, 51605, Feb. 2015, DOI: 10.1063/1.4907861.

[29] M. Meer et al., "Impact of wet-oxidized Al<sub>2</sub>O<sub>3</sub>/AlGaN interface on AlGaN/GaN 2-DEGs," Semicond. Sci. Technol., 32, 4, 04LT02, Apr. 2017, DOI: 10.1088/1361-6641/aa60a3.

[30] D. Donoval *et al.*, "High-temperature performance of AlGaN/GaN HFETs and MOSHFETs," *Microelectron. Reliab.*, 48, 10, 1669–1672, 2008, DOI: 10.1016/j.microrel.2008.04.017.

[31] W. S. Tan *et al.*, "Electrical characteristics of AlGaN/GaN metal-insulator semiconductor heterostructure field-effect transistors on sapphire substrates," *J. Electron. Mater.*, 32, 5, 350–354, 2003, DOI: 10.1007/s11664-003-0157-4.

Electron. Mater., 32, 5, 350–354, 2003, DOI: 10.1007/s11664-003-0157-4.

[32] Z. Gao et al., "Thermal Assessment of AlGaN/GaN MOS-HEMTs on Si Substrate Using Gd<sub>2</sub>O<sub>3</sub> as Gate Dielectric," *IEEE Trans. Electron Devices*, 63, 7, 2729–2734, Jul. 2016, DOI: 10.1109/TED.2016.2564301.

[33] S. Demirtas *et al.*, "High voltage degradation of GaN High Electron Mobility Transistors on silicon substrate," *Microelectron. Reliab.*, 50, 6, 758–762, Jun. 2010, DOI: 10.1109/MMWCST.2012.6238124.

[34] S. Demirtas and J. A. del Alamo, "Effect of trapping on the critical voltage for degradation in GaN high electron mobility transistors," in 2010 IEEE International Reliability Physics Symposium, 2010, 134–138. DOI: 10.1109/IRPS.2010.5488838.

[35] Jungwoo Joh and J. A. del Alamo, "Critical Voltage for Electrical Degradation of GaN High-Electron Mobility Transistors," *IEEE Electron Device Lett.*, 29, 4, 287–289, Apr. 2008, DOI: 10.1109/LED.2008.917815.

[36] J. A. del Alamo and J. Joh, "GaN HEMT reliability," *Microelectron. Reliab.*, 49, 9–11, 1200–1206, Sep. 2009, DOI: 10.1016/j.microrel.2009.07.003.

[37] J. Joh, F. Gao, T. Palacios, and J. A. del Alamo, "A model for the critical voltage for electrical degradation of GaN high electron mobility transistors," *Microelectron. Reliab.*, 50, 6, 767, 2010, DOI: 10.1016/j.microrel.2010.02.015.

[38] J. Joh *et al.*, "Role of stress voltage on structural degradation of GaN high electron-mobility transistors," *Microelectron. Reliab.*, 51, 2, 201–206, Feb. 2011, DOI: 10.1016/j.microrel.2010.08.021.

[39] H. Kim *et al.*, "Reliability Evaluation of High Power AlGaN/GaN HEMTs on SiC Substrate," *Phys. status solidi*, 188, 1, 203–206, Nov. 2001, DOI: 10.1002/1521-396X(200111)188:1<203::AID-PSSA203>3.0.CO;2-C.

[40] Y.-L. Yang *et al.*, "Examination of hot-carrier stress induced degradation on fin field-effect transistor," *Appl. Phys. Lett.*, 104, 8, 83505, Feb. 2014, DOI: 10.1063/1.4866437.

[41] F. Gao et al., "Role of oxygen in the OFF-state degradation of AlGaN/GaN high electron mobility transistors," *Appl. Phys. Lett.*, 99, 22, 223506, Nov. 2011, DOI: 10.1063/1.3665065.

[42] P. Makaram *et al.*, "Evolution of structural defects associated with electrical degradation in AlGaN/GaN high electron mobility transistors," *Appl. Phys. Lett.*, 96, 23, 1–4, 2010, DOI: 10.1063/1.3446869.

[43] S. Nakahara et al., "Room Temperature Interdiffusion Study of Au/Ga Thin Film Couples," *Thin Solid Films*, 13, 15–26, 1984, DOI: 10.1016/0040-6090(84)90384-5. [44] F. Gao et al., "Impact of water-assisted electrochemical reactions on the OFF-state degradation of AlGaN/gaN HEMTs," *IEEE Trans. Electron Devices*, 61, 2, 437–444, 2014, DOI: 10.1109/TED.2013.2293114.

[45] T.-L. Wu et al., "Toward Understanding Positive Bias Temperature Instability in Fully Recessed-Gate GaN MISFETs," *IEEE Trans. Electron Devices*, 63, 5, 1853–1860, May 2016, DOI: 10.1109/TED.2016.2539341.