Wayne State University Dissertations

January 2019

# Bundle: Taming The Cache And Improving Schedulability Of Multi-Threaded Hard Real-Time Systems

Corey Tessler Wayne State University

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations

Part of the Computer Sciences Commons

#### **Recommended Citation**

Tessler, Corey, "Bundle: Taming The Cache And Improving Schedulability Of Multi-Threaded Hard Real-Time Systems" (2019). Wayne State University Dissertations. 2339. https://digitalcommons.wayne.edu/oa\_dissertations/2339

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

# BUNDLE: TAMING THE CACHE AND IMPROVING SCHEDULABILITY OF MULTI-THREADED HARD REAL-TIME SYSTEMS

by

#### **COREY TESSLER**

#### DISSERTATION

Submitted to the Graduate School,

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

#### DOCTOR OF PHILOSOPHY

MAJOR: COMPUTER SCIENCE

Approved By:

Nathan Fisher, Ph.D. Advisor Date

Frank Mueller, Ph.D.

Daniel Grosu, Ph.D.

Abusayeed Saifullah, Ph.D.

#### **ACKNOWLEDGMENTS**

This research presented was supported, in part, by the National Science Foundation under Grant Numbers CNS-1618185, CNS-0953585, CNS-1205338, and IIS-1724227.

This research would not have been possible without the clear, dedicated, and gentle guidance provided by Professor Nathan Fisher of Wayne State University. He is a treasure to the University and to all who know him. Thank you.

To the committee members: Professor Daniel Grosu, Professor Frank Mueller, and Professor Abusayeed Saifullah. Please accept my gratitude for your willingness to sit on the committee along with your thoughtful feedback and suggestions. This work is made better by your contributions, thank you.

I am fortunate to have a wonderful role-model for a mother, Anastasia Tessler. Her lifelong dedication to her children extends beyond her biological children to those she adopted in the classroom. As a teacher in Detroit, her thoughtful creativity excited students to excel academically and her compassion forged life-long relationships with them and their families. She stands as an example of service to others through education to all of us. Thank you for your unwavering support and all of the lessons.

And lastly, thank you to two very important friends: Michael Noonan and Kathryn Horner. They are wonderful, unique people with generous spirits. May you rely upon me as I have relied upon you for companionship, distraction, and wholly inappropriate humor.

### TABLE OF CONTENTS

| List of Tables                                     | viii |

|----------------------------------------------------|------|

| List of Figures                                    | ix   |

| Chapter 1 Introduction                             | 1    |

| 1.1 Thesis                                         | 6    |

| 1.2 Contributions                                  | 6    |

| Chapter 2 Model and Notation                       | 10   |

| 2.1 Models and Perspectives                        | 10   |

| 2.2 Sporadic Task Model                            | 11   |

| 2.3 Architecture Model                             | 12   |

| 2.4 Objects, Tasks, Threads, Ribbons, Entry Points | 13   |

| 2.5 Control Flow Graphs                            | 14   |

| 2.6 Notation Summary                               | 16   |

| Chapter 3 Inter-Thread Cache Benefit               | 17   |

| 3.1 Defining the Inter-Thread Cache Benefit        | 18   |

| 3.2 Comparison of Perspectives                     | 19   |

| 3.2.1 WCET                                         | 21   |

| 3.2.2 CRPD                                         | 22   |

| Chapter 4 Related Work                             | 24   |

| 4.1    | Worst-Case Execution Time and Cache Memory                              | 24 |

|--------|-------------------------------------------------------------------------|----|

| 4.2    | Cache Related Preemption Delay                                          | 25 |

| 4.3    | Cache Analysis in Multi-Threaded Programs                               | 27 |

| 4.4    | Predictable Cache Behavior                                              | 28 |

| 4.5    | Positive Perspectives on Caches                                         | 29 |

| Chapte | r 5 Single-Task BUNDLE                                                  | 31 |

| 5.1    | BUNDLE Scheduling                                                       | 31 |

| 5.2    | Conflict Free Regions and Conflict Free Region Graphs                   | 33 |

|        | 5.2.1 Extracting Conflict Free Regions                                  | 35 |

|        | 5.2.2 Worst Case Execution Time with Cache Overhead (WCETO)             | 42 |

|        | 5.2.3 Structures                                                        | 47 |

|        | 5.2.4 Structure WCETO Calculation                                       | 48 |

| 5.3    | Evaluation of BUNDLE                                                    | 54 |

|        | 5.3.1 WCET vs WCETO Analysis                                            | 54 |

|        | 5.3.2 BUNDLE Run-Time Performance                                       | 58 |

| 5.4    | Summary                                                                 | 61 |

| Chapte | r 6 Single-Task BUNDLEP                                                 | 63 |

| 6.1    | BUNDLE Sub-Optimal Cache Sharing                                        | 64 |

| 6.2    | BUNDLEP Overview                                                        | 65 |

| 6.3    | Conflict Free Region Extraction and Conflict Free Region Graph Creation | 67 |

|        | 6.3.1 Expanded Control Flow Graphs                                      | 67 |

|        | 6.3.2 Conflict Free Region Graph Creation                               | 69 |

|        | 6.3.3 Assignment                                                        | 71 |

|        | 6.3.4 Linking                                      |  |

|--------|----------------------------------------------------|--|

| 6.4    | BUNDLEP                                            |  |

|        | 6.4.1 Hardware Support                             |  |

|        | 6.4.2 BUNDLEP's Scheduling Algorithm 80            |  |

|        | 6.4.3 Priority Assignment                          |  |

| 6.5    | BUNDLEP WCETO Calculation                          |  |

| 6.6    | BUNDLEP Evaluation                                 |  |

|        | 6.6.1 Context Switch Costs                         |  |

| 6.7    | Summary                                            |  |

| 6.8    | Ancillary Preamble                                 |  |

| 6.9    | Ancillary: ILP Transformation and Example 97       |  |

| 6.10   | Ancillary: WCETO Example                           |  |

| Chapte | r 7 Non-Preemptive Multitask BUNDLE 102            |  |

| 7.1    | NPM-BUNDLE Model and Notation                      |  |

|        | 7.1.1 Dividing and Task Parts                      |  |

|        | 7.1.2 Worst-Case Execution Time Function Growth    |  |

| 7.2    | Non-Preemptive EDF Schedulability                  |  |

|        | 7.2.1 Non-Preemptive Chunks                        |  |

|        | 7.2.2 Improving the Non-Preemptive Chunk Size      |  |

|        | 7.2.3 Threads per Job (TPJ) Scheduling Algorithm   |  |

|        | 7.2.4 Non-Preemptive Feasibility of TPJ and DIVIDE |  |

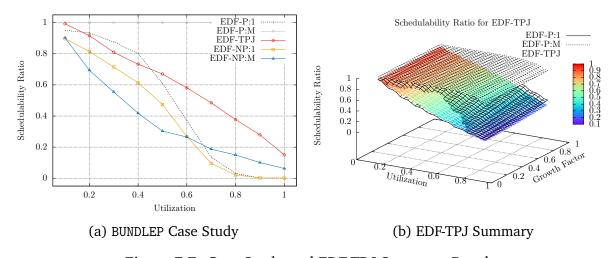

| 7.3    | Evaluation                                         |  |

|        | 7.3.1 Generating Task Sets                         |  |

|        | 7.3.2  | Case Study                                    |

|--------|--------|-----------------------------------------------|

|        | 7.3.3  | Evaluation Metrics                            |

|        | 7.3.4  | Results                                       |

| 7.4    | Summ   | nary                                          |

| Chapte | r 8 N  | Multi-Processor Multi-Task BUNDLE 138         |

| 8.1    | Backg  | round and Related Work                        |

|        | 8.1.1  | Federated Scheduling                          |

|        | 8.1.2  | Proposed Model Changes                        |

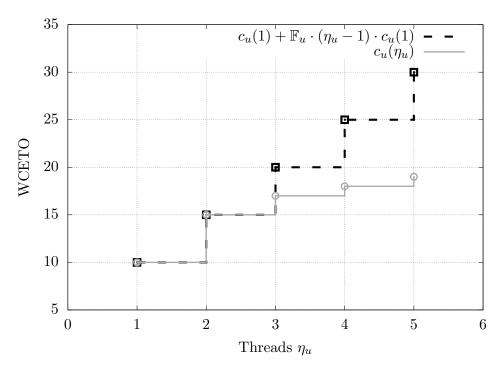

|        | 8.1.3  | Discrete Concave Functions and Growth Factors |

|        | 8.1.4  | Related Work                                  |

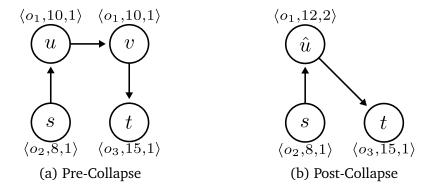

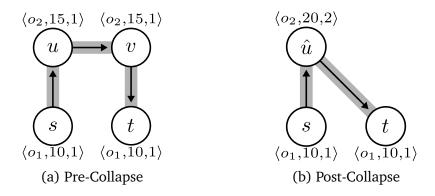

| 8.2    | Collap | osing Nodes                                   |

|        | 8.2.1  | Infeasibility and the Impact of Collapse      |

|        | 8.2.2  | Beneficial Collapse                           |

|        | 8.2.3  | Optimal Collapse                              |

| 8.3    | DAG-0  | OT Schedulability                             |

| 8.4    | Candi  | date Ordering                                 |

|        | 8.4.1  | Greatest Benefit                              |

|        | 8.4.2  | Least Penalty                                 |

| 8.5    | Low U  | Itilization Tasks                             |

| 8.6    | Evalua | ation                                         |

|        | 8.6.1  | Evaluation Metrics                            |

|        | 8.6.2  | Results                                       |

| 0.7    | Cumm   | 170                                           |

| Chapte  | r 9 F   | uture Work                       | 171 |

|---------|---------|----------------------------------|-----|

|         | 9.0.1   | Scheduling Support               | 171 |

|         | 9.0.2   | Preemptive Multi-Task BUNDLEP    | 172 |

|         | 9.0.3   | From Switched to Unswitched CFRs | 172 |

| Chapte  | r 10 C  | Conclusion                       | 174 |

| List of | Publica | ations                           | 177 |

| REFERI  | ENCES   |                                  | 179 |

| Abstrac | ct      |                                  | 190 |

| Autobio | ograph  | ical Statement                   | 193 |

# LIST OF TABLES

| Table 1.1 | Cache Perspectives in Hard-Real Time Analysis   |

|-----------|-------------------------------------------------|

| Table 2.1 | List of Symbols                                 |

| Table 3.1 | Example Model Parameters                        |

| Table 3.2 | Categories from [1, 2] and Cache Assignment     |

| Table 3.3 | Segment WCET                                    |

| Table 6.1 | MIPS 74K Architecture Parameters                |

| Table 7.1 | NPM-BUNDLE Notation                             |

| Table 8.1 | ITCB-DAG Notation                               |

| Table 8.2 | Collapse of $u$ and $v$ from Figure 8.8         |

| Table 8.3 | Collapse of $x$ and $y$ from Figure 8.9         |

| Table 8.4 | Federated Schedulability Test Comparisons       |

| Table 8.5 | Task Generation Graph Creation Parameters       |

| Table 8.6 | Task Generation Execution Assignment Parameters |

| Table 8.7 | Task Generation Timing Assignment Parameters    |

| Table 8.8 | Task Set Assembly Parameters                    |

# LIST OF FIGURES

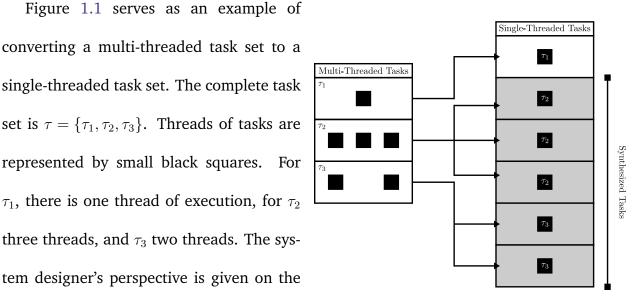

| Figure 1.1 | Synthesized Tasks                                                    | 4  |

|------------|----------------------------------------------------------------------|----|

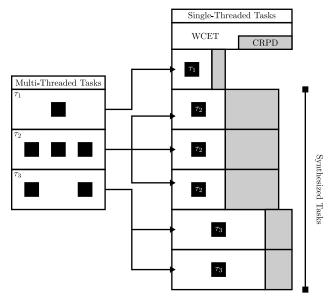

| Figure 1.2 | CRPD and Synthesized Tasks                                           | 5  |

| Figure 1.3 | Contributions of BUNDLE                                              | 6  |

| Figure 1.4 | Contributions of BUNDLEP                                             | 7  |

| Figure 1.5 | Contributions of NPM-BUNDLE                                          | 7  |

| Figure 1.6 | Contributions of ITCB-DAG                                            | 8  |

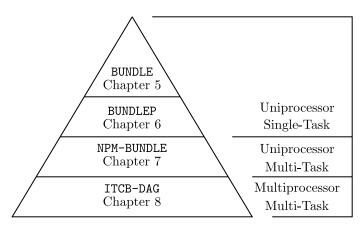

| Figure 1.7 | Scope of Contributions                                               | 9  |

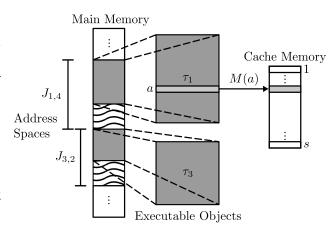

| Figure 3.1 | Address Space for Two Jobs                                           | 18 |

| Figure 3.2 | Control Flow Graph for: $\rho_1$                                     | 19 |

| Figure 3.3 | Worst Schedule of $\tau_1$ , 4550 Cycles                             | 22 |

| Figure 5.1 | CFG, CFRs, and CFRG of a ribbon                                      | 33 |

| Figure 5.2 | Requirements of Conflict Free Region                                 | 34 |

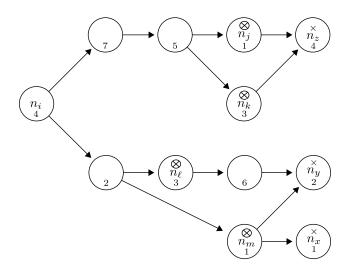

| Figure 5.3 | Next Intra-Thread Cache Conflicts from $n_i$ marked with a $	imes$   | 37 |

| Figure 5.4 | Next Inter-Thread Cache Conflicts from $n_i$ marked with a $\otimes$ | 40 |

| Figure 5.5 | Largest region of Figure 5.4 with no conflicts from $n_i$            | 40 |

| Figure 5.6 | Extraction of the initial CFR from the CFG                           | 42 |

| Figure 5.7 | CFG to CFRG with WCETO Values                                        | 43 |

| Figure 5.8 | WCETO from CFRG                                                      | 45 |

| Figure 5.9  | CFR Requirements for WCETO Calculation                                              | 46                |

|-------------|-------------------------------------------------------------------------------------|-------------------|

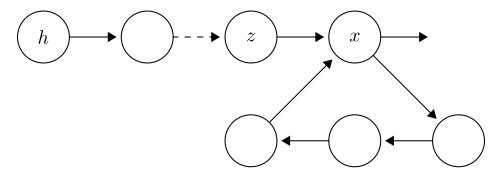

| Figure 5.10 | Linear Structure from $h$ to $z$ Preceding a Loop                                   | 47                |

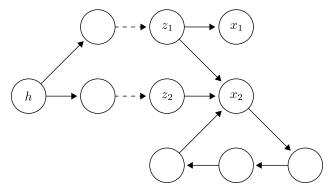

| Figure 5.11 | Branching Structure from $h$ to $Z=\{z_1,z_2\}$ with Boundary Nodes $X=\{x_1,x_2\}$ | $\{x_1, x_2\}$ 48 |

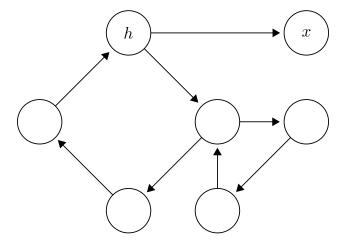

| Figure 5.12 | Looping Structure with Loop Head $h$ and Boundary Nodes $X=\{x\}$ .                 | 48                |

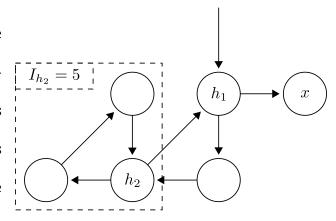

| Figure 5.13 | Embedded loop of $h_2$ within $h_1$                                                 | 50                |

| Figure 5.14 | BUNDLE Evaluation Parameters                                                        | 54                |

| Figure 5.15 | $c_1$ : Classical WCET for One Thread to Execute $\rho$                             | 56                |

| Figure 5.16 | $\gamma_1$ Classical CRPD for One Preemption of $\rho$                              | 56                |

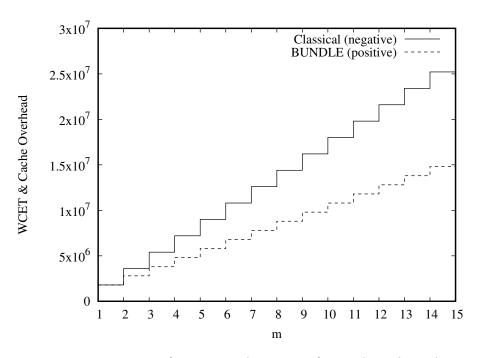

| Figure 5.17 | Comparison of WCET and WCETO for $m$ threads and $i=1{,}000$                        | 57                |

| Figure 5.18 | WCET + Preemption Cost When $i=10000$                                               | 58                |

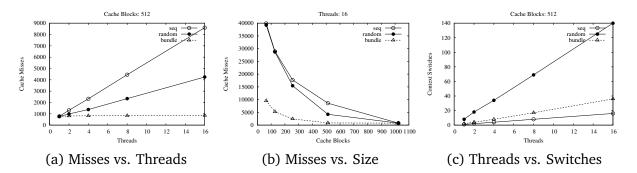

| Figure 5.19 | Run Time Overhead Results                                                           | 59                |

| Figure 5.20 | Minimum Context Switch Cost (in Cycles) for seq to Dominate BUNDLE                  | 60                |

| Figure 5.21 | Constraints of Single Task BUNDLE                                                   | 62                |

| Figure 6.1  | Summary of BUNDLEP improvements                                                     | 63                |

| Figure 6.2  | Sub-Optimal BUNDLE Execution                                                        | 64                |

| Figure 6.3  | Optimal BUNDLEP Execution                                                           | 65                |

| Figure 6.4  | Summary of BUNDLEP improvements                                                     | 68                |

| Figure 6.5  | Requirements of Conflict Free Regions and Conflict Free Region Graphs for BUNDLEP   | 69                |

| Figure 6.6  | Loop heads and Inner-Most Loop Heads                                                | 70                |

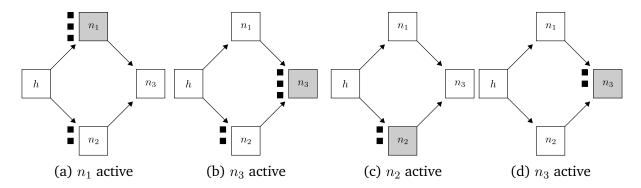

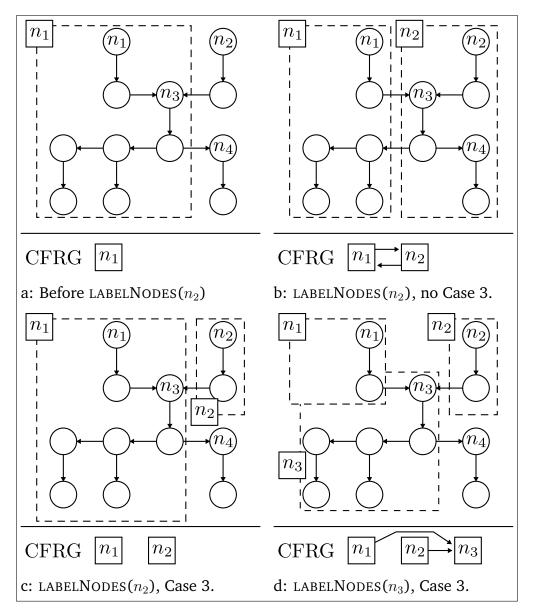

| Figure 6.7  | Call to LabelNodes $(n_3)$                                                          | 73                |

| Figure 6.8  | Case 3 Protection                                                                   | 76                |

| Figure 6.9  | XFLICT Interrupts and BUNDLEP                                                       | 79                |

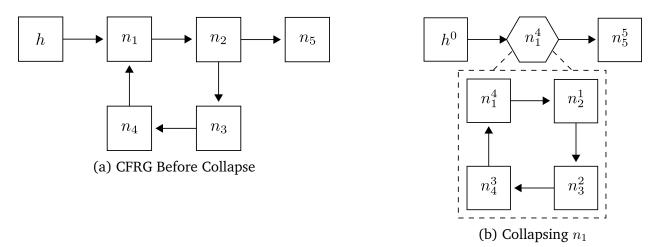

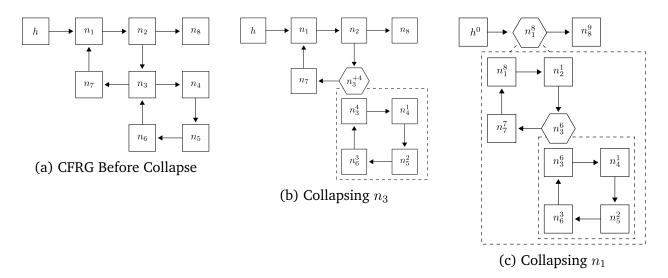

| Figure 6.10 | Collapsing One Loop of a CFRG                        | 3 |

|-------------|------------------------------------------------------|---|

| Figure 6.11 | Summary Node Priority Requirements                   | 5 |

| Figure 6.12 | Collapsing Embedded Loops                            | 5 |

| Figure 6.13 | CFRG Individual Nodes and ILP Objective              | 8 |

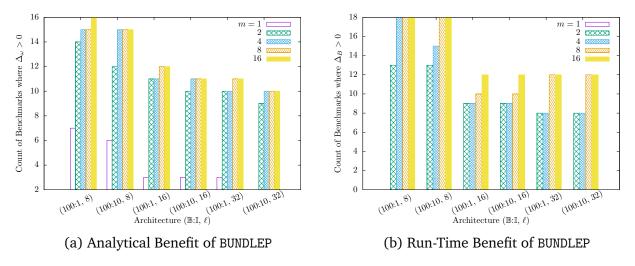

| Figure 6.14 | Benefits of BUNDLEP                                  | 4 |

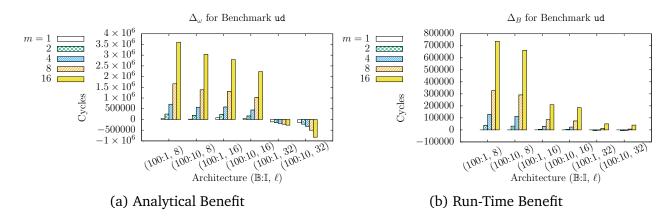

| Figure 6.15 | Results for the ud Benchmark                         | 5 |

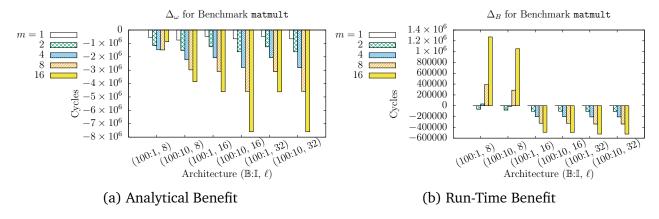

| Figure 6.16 | Results for the matmult Benchmark                    | 6 |

| Figure 6.17 | CFRG Individual Nodes and ILP Objective              | 0 |

| Figure 7.1  | Summary of NPM-BUNDLE contributions                  | 2 |

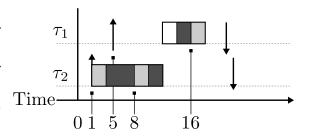

| Figure 7.2  | Scheduling Behavior                                  | 4 |

| Figure 7.3  | Schedulability and Transformable Task Sets           | 6 |

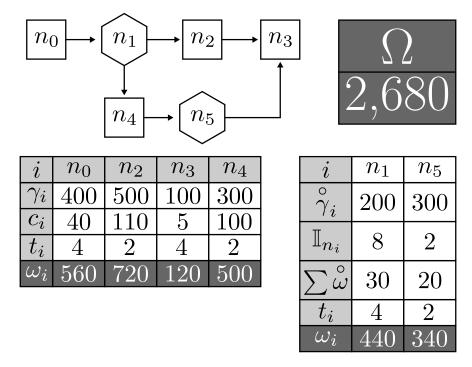

| Figure 7.4  | Example Task Set $\tau = \{\tau_0, \tau_1, \tau_2\}$ | 4 |

| Figure 7.5  | Task Set Generation Parameters                       | 9 |

| Figure 7.6  | Schedulability Test Combinations                     | 1 |

| Figure 7.7  | Case Study and EDF-TPJ Summary Results               | 2 |

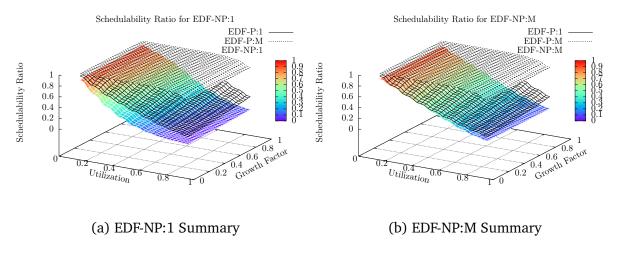

| Figure 7.8  | EDF-NP:1 and EDF-NP:M Summary                        | 3 |

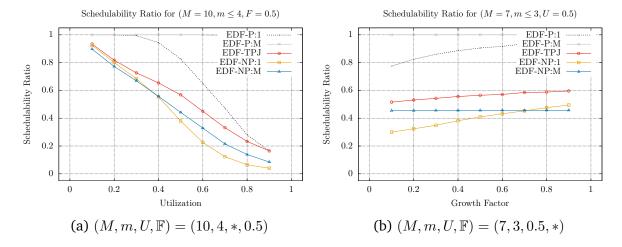

| Figure 7.9  | U>1 Feasibility                                      | 4 |

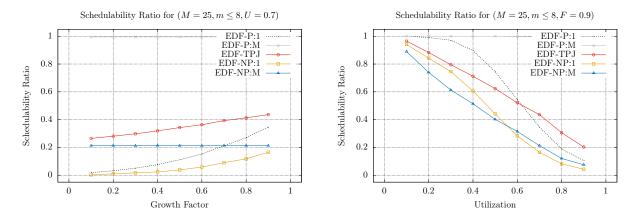

| Figure 7.10 | $M \leq 10$ Performance                              | 4 |

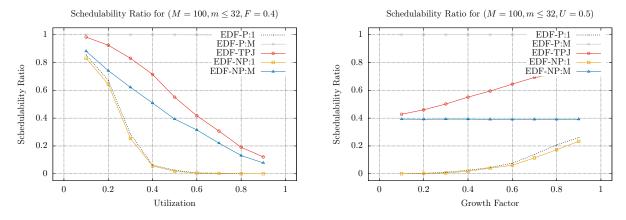

| Figure 7.11 | M>10 EDF-TPJ Performance Above EDF-P:1               | 5 |

| Figure 7.12 | M=100 EDF-TPJ Performance                            | 6 |

| Figure 8.1  | Summary of ITCB-DAG contributions                    | 8 |

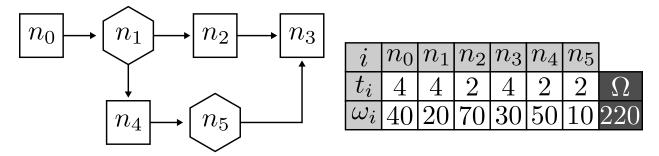

| Figure 8.2  | A DAG Task                                           | 1 |

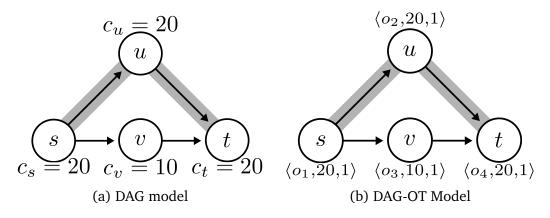

| Figure 8.3  | From DAG to DAG-OT                                   | Δ |

| Figure 8.4  | Example Growth Factor                     |

|-------------|-------------------------------------------|

| Figure 8.5  | Node Collapse                             |

| Figure 8.6  | Critical Path Reduction                   |

| Figure 8.7  | Critical Path Extension                   |

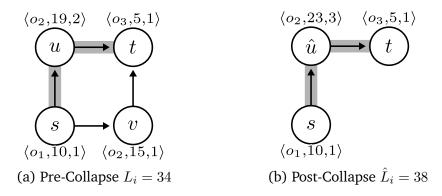

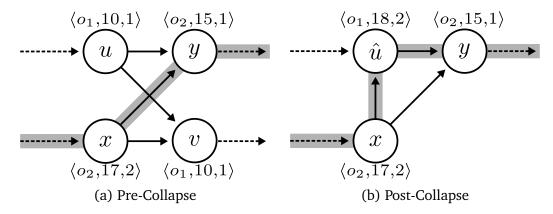

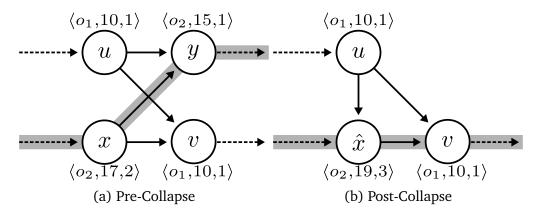

| Figure 8.8  | Collapse of $(u, v)$ before $(x, y)$      |

| Figure 8.9  | Collapse of $(x, y)$ before $(u, v)$      |

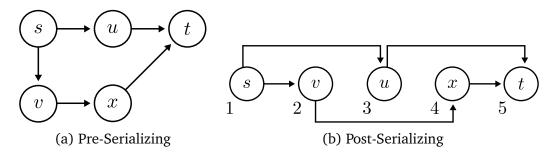

| Figure 8.10 | Serializing a Task $\tau_i$               |

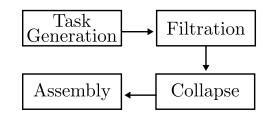

| Figure 8.11 | Task Set Generation Pipeline              |

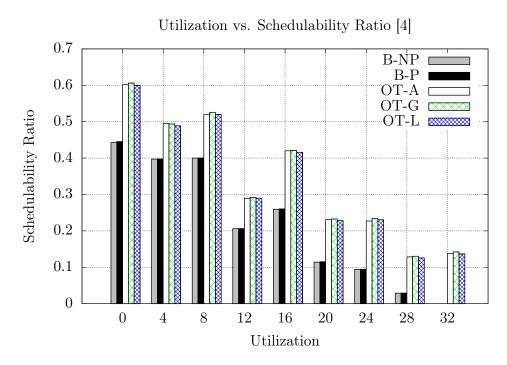

| Figure 8.12 | Mean Schedulability Ratio                 |

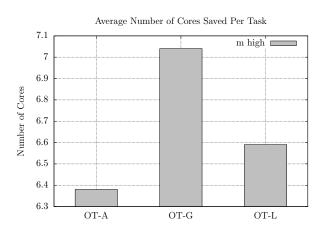

| Figure 8.13 | Mean Core Savings                         |

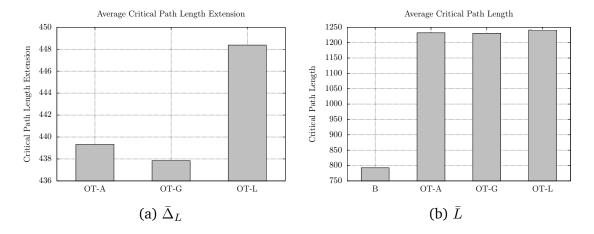

| Figure 8.14 | Mean Critical Path Lengths and Extensions |

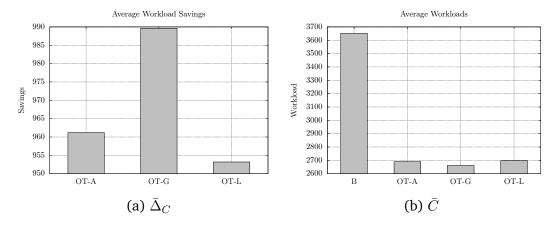

| Figure 8.15 | Mean Workloads and Savings                |

#### **CHAPTER 1 INTRODUCTION**

Computational systems and their applications have become ubiquitous. From racks of super-computers, to smart phones, to pin sized personal sensors, there are a scant few environments where a microprocessor is absent. As the use of computational systems increases, so too does our reliance and trust in them to operate in safety critical environments such as nuclear power plants, pace-makers, automotive and flight controls. When accuracy and safety depend on a computational system, we find hard real-time systems.

As a discipline, computer science provides the theoretical and practical tools necessary to guarantee the safety of hard real-time systems. However, the features of the underlying computational platforms (the architecture) and the programming models applied to them are constantly evolving – so too must the analysis of safety critical systems. Herein, the impact of cache memory and threaded execution is examined in the context of hard real-time systems. The *classical* perspective of threads and cache is advanced to an *integrated* one, resulting in safe and reliable systems that execute upon smaller and less powerful platforms. Additionally, the integrated perspective could be applied outside of the hard real-time setting they were developed for to improve the performance of threaded computational systems.

Currently, the evolution of computational platforms is focused upon increasing the number of concurrent threads of execution by providing processors with an increased number of cores and cache dedicated to those cores. As an example, the AMD Thread-ripper 2990WX [3] processor can execute sixty four threads simultaneously. It contains

over eighty megabytes of cache memory, with three megabytes of private cache dedicated to individual cores.

Simultaneously, the scope of safety critical applications is increasing to encompass applications that cannot be addressed by single-threaded processors. NVIDIA's Jetson TX2 plaftform [4] is designed for autonomous vehicles. It carries 256 cores to handle the demanding multi-threaded tasks associated with image processing, route planning, and motor control. Like autonomous vehicles, it is reasonable to expect the number of hard real-time systems which demand multi-threaded platforms to increase. Improving the performance of these platforms through the proposed integrated perspective increases the efficiency of these systems, thus reducing the number of processors needed, power consumed, weight, and overall cost.

In a hard real-time system, as with other systems, all computations must produce the correct answer; they must be logically correct. However, hard real-time systems have a second requirement: all computations must complete on time. A correct answer delivered too late, such as "apply emergency braking" is not only useless, it is a failure of the system with catastrophic results. Similarly, a correct answer delivered too early is also considered a failure. For a hard real-time system there are two types of correctness: logical, and temporal. Both must be met for any hard real-time system to be reliable, safe, and deployed.

Logical correctness is determined by context, depending on the inputs and parameters of the system deployed. Temporal correctness is the subject of study for *schedulability analysis*. It is uncommon for any computational system to have a single logical operation to complete, this is also true for hard real-time systems. For hard real-time systems logical

operations are divided into tasks (individual programs), which execute on the shared processor(s). Tasks compete for execution time on the processor(s) and if the competition is too great the temporal correctness of the system is at risk.

Schedulability analysis determines if a set of tasks will always be temporally correct for a given computational architecture. Each task has a frequency with which it will be requested, a window of time which it must be completed within called its deadline, and a worst-case execution time (WCET). The WCET of a task bounds the amount of time a task takes to complete on the shared processors. The limitations of the architecture are included in a *schedulability test* including the processor(s). When a schedulability test determines every request to execute a task will be temporally correct using a specific *scheduling algorithm*, the task set is said to be *schedulable*. A schedulable task set guarantees a system is safe to deploy for its stated operation (given that it is logically correct).

An important component to schedulability analysis is the calculation of worst-case execution times for tasks. For classical models of real-time systems, shared resources are often considered detractors to schedulability analysis and exclusively increase WCETs. Cache memory is one such shared resource viewed from this exclusively negative perspective. It is a natural perspective, derived from a preempting task invalidating cache lines, thus extending a preempted task's execution time.

Using the classical periodic task model [5] as an example, it is implied that a task has a single thread of execution. The model lacks a representation for tasks with multiple threads. To apply WCET and schedulablility techniques developed for the periodic and other classical models, a task that executes multiple threads is treated as several duplicate tasks with a single thread of execution. These single threaded tasks duplicated from multi-

threaded tasks are referred to as synthetic tasks. Any multi-threaded task that releases a job with m threads will be converted to m synthetic tasks each releasing one job.

single-threaded task set. The complete task set is  $\tau = {\tau_1, \tau_2, \tau_3}$ . Threads of tasks are represented by small black squares. For  $\tau_1$ , there is one thread of execution, for  $\tau_2$ three threads, and  $\tau_3$  two threads. The system designer's perspective is given on the left side of the figure, where the three tasks

Figure 1.1: Synthesized Tasks

encapsulate their threads. On the right side of the figure is the analytical perspective, where tasks must have exactly one thread of execution. Worst-case execution time and schedulability analysis is performed on the six (rather than three) tasks.

From the analytical perspective, the synthetic tasks are independent of one another competing for the shared resources of target architecture. One classical analytical model where threads are treated independently is the fork-join model [6]. Where each thread has a WCET calculated from its longest execution path. Each thread then contributes its execution demand independently of others to the schedulability test.

For classical models, tasks are assumed to be in competition for cache space. The inclusion of threads, which are converted to tasks, only amplifies the negative affect. Cacherelated preemption delay analysis (CRPD), as the name implies, is the delay of a tasks completion time due to preemptions by other tasks. These delays impact schedulability negatively by increasing worst-case execution times on a per task basis.

Figure 1.2 highlights the increase in execution demand the classical perspective necessitates. Since *all* tasks compete for cache space, all tasks must be considered in calculated CRPD values. This includes competition between synthetic tasks which were duplicated from the same multithreaded task; eg. two threads of  $\tau_3$  compete for cache space when converted to synthesized tasks.

Figure 1.2: CRPD and Synthesized Tasks

Threads are not always in competition with other threads for cache space. In fact threads may mutually benefit from reusing the same cached values by virtue of sharing the same memory space. A cache miss during the execution of one thread can place values into the cache that produce a cache hit for a second thread. These unexpected cache hits reduce the execution time of the second thread and the system overall. This speed up is called the *inter-thread cache benefit*. The efforts of this work focus on quantifying the inter-thread cache benefit to decrease individual task WCET bounds and increase system schedulability.

Herein an argument is made for a new task model, scheduling algorithm, and schedulability analysis techniques. Classical approaches to Worst Case Execution Time (WCET), Cache-Related Preemption Delay (CRPD), and schedulability analysis typically produce separate values. Accounting for the inter-thread cache benefit requires an approach that integrates the disciplines.

### 1.1 Thesis

Scheduling individual threads of a multi-threaded task in a cache cognizant manner improves system schedulability through predictable and quantifiable inter-thread cache benefits. When compared to classical scheduling algorithms and analysis, this positive perspective reduces WCET and CRPD values. Realizing the benefit is achievable with the addition of a familiar (yet novel) low cost hardware mechanism.

### 1.2 Contributions

In support of the thesis, the following contributions are made. As an initial theoretical work, BUNDLE [7] describes the negativity of the classical perspective. In BUNDLE a positive perspective of caches is introduced along with central mechanisms for scheduling and worst-case execution time calculation.

- 1. A positive perspective on caches in the form of the inter-thread cache benefit. (Section 3.1)

- 2. A novel model of multi-threaded tasks that allows the inter-thread cache benefit of instruction caches to be quantified. (Chapter 2)

- 3. The introduction of the concepts of worst case execution time and cache overhead (WCETO), conflict free regions, and conflict free region graphs. (Section 5.2)

- 4. The BUNDLE cache cognizant scheduling algorithm for a single task with multiple threads. (Section 5.1)

- 5. A WCETO method for a task scheduled by BUNDLE. (Section 5.2.2)

Figure 1.3: Contributions of BUNDLE

Improving upon BUNDLE is the purpose of BUNDLEP [8]. Prioritizing bundles based upon their longest path maximizes the inter-thread cache benefit between threads. Priorities also improve the worst-case execution time calculation method by reducing the complexity of their calculation.

- 1. The BUNDLEP cache cognizant scheduling algorithm for a single task with multiple threads. (Section 6.4.2)

- 2. A WCETO method for a task scheduled by BUNDLEP. (Section 6.5)

- 3. Proof of optimal cache sharing under BUNDLEP scheduling.

- 4. A novel hardware interrupt mechanism to anticipate execution named XFLICT which uses an XFLICT\_TABLE of addresses. (Section 6.4.1)

- 5. A toolset for BUNDLEP analysis and simulation for programs compiled for MIPS processors [9].

Figure 1.4: Contributions of BUNDLEP

Both BUNDLE and BUNDLEP are limited to the analysis and execution of a single multi-threaded task. Non-preemptive multi-task BUNDLE [10] (NPM-BUNDLE), expands the applicability of the scheduling and analysis techniques to multiple tasks.

- 1. A hierarchical scheduling mechanism using non-preemptive EDF for jobs scheduled by BUNDLEP with intra-task thread-level preemptions named Non-Preemptive Multi-Task BUNDLE (NPM-BUNDLE). (Chapter 7)

- 2. The introduction of task division for multi-threaded task sets. (Section 7.1.1)

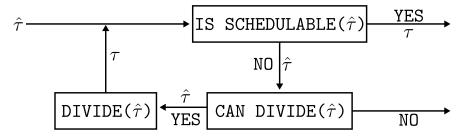

- 3. A scheduling algorithm and task dividing process named Threads per Job (TPJ) for NPM-BUNDLE. (Section 7.2.3)

- 4. Proof of TPJ's non-preemptive multi-threaded feasibility. (Theorem 7.2.3)

- 5. A toolset for NPM-BUNDLE analysis of synthetic tasks [11].

Figure 1.5: Contributions of NPM-BUNDLE

NPM-BUNDLE brings the BUNDLE techniques and analysis to multiple tasks. However, the application is limited to a single processor. As a first step toward expanding to a multiprocessor setting, the following contributions are made as part of ITCB-DAG:

- 1. Augmenting the parallel directed acyclic graph (DAG) model to include executable objects and threads per node. (Section 8.1.2)

- 2. The concepts of collapsing nodes and candidacy for collapse. (Section 8.2)

- 3. The Dedicated Core Reduction Algorithm which increases schedulability by (potentially) allocating fewer cores per high-utilization task. (Section 8.3)

- 4. Two heuristics for ordering nodes to be collapsed. (Section 8.4)

- 5. A synthetic evaluation demonstrating the positive impact of collapse and BUNDLE scheduling for DAG tasks. (Section 8.6)

Figure 1.6: Contributions of ITCB-DAG

In series, these contributions can be viewed as increasing the scope of the inter-thread cache benefit. Starting with BUNDLE, which introduces the inter-thread cache benefit, scoped to a single task running on a uniprocessor systems. BUNLDEP improves upon BUNDLE in the uniprocessor setting, but does not increase the scope. The subsequent work NPM-BUNDLE increases the scope, bringing the inter-thread cache benefit to multi-task systems. Finally, ITCB-DAG further increases the scope by the inclusion of multiprocessor systems.

Figure 1.7 summarizes the scope of contributions. However, these contributions should not be considered final in their respective scopes. While these contributions are substantial, they do not address every theoretical or practical opportunity to incorporate interthread cache benefits in all settings; they are necessary fundamental steps towards greater adoption. There are numerous opportunities to improve upon the BUNDLE analysis and scheduling techniques.

Figure 1.7: Scope of Contributions

These contributions are novel in the context of hard real-time systems, creating a positive perspective of caches for multi-threaded tasks. Previous works applicable to the worst-case execution time of single-threaded tasks [2, 12, 1] take a positive perspective on cache memory, reducing execution time bounds. In contrast, cache-related preemption delay [13, 14, 15, 16, 17] takes a negative perspective of cache memory, accounting for the execution time penalty preemptions induce in both single and multi-threaded tasks (through synthesis). These contributions are the *first* to bring a positive perspective of cache memory to multi-threaded tasks for hard real-time systems, with the goal of reducing the total system execution time. Table 1.1 places these contributions under the BUNDLE umbrella in comparison to the disciplines of WCET and CRPD analysis.

|          | Single<br>Threaded | Multi-Threaded |

|----------|--------------------|----------------|

| Positive | WCET               | BUNDLE         |

| Negative | CRPD               | CRPD           |

Table 1.1: Cache Perspectives in Hard-Real Time Analysis

#### CHAPTER 2 MODEL AND NOTATION

In this chapter, an introduction is given for the models and concepts used or augmented to obtain a positive perspective on caches. It defines the task model, schedulability conditions, program model, architecture model, and notation shared between the different BUNDLE scheduling algorithms and analysis. Additionally, the shared concepts of ribbons, threads, inter-thread cache benefit, and control flow graphs are defined.

### 2.1 Models and Perspectives

Throughout this work, there are references to *classical* models and the *negative* perspective. To clarify, an existing task model, scheduling algorithm, schedulability test, or WCET calculation method that cannot account for the inter-thread cache benefit is said to take the negative perspective, or is a classical model. The language is derived from the treatment of cache as a shared resource which can only extend execution times through conflicts.

In contrast, the *positive* perspective allows for caches to benefit execution. A task model, scheduling algorithm, schedulability test, or WCET method that includes the inter-thread cache benefit is termed *integrated*. The integrated methods proposed in this work which take the positive perspective are placed in the BUNDLE family (referring to common thread-level scheduling technique).

Typically, classical models assume a single thread of execution per task. Therefor, analysis of multi-threaded tasks for a classical model depends on each thread being converted to an independent task with one thread of execution. Such tasks are referred to as *synthetic*

tasks. For one multi-threaded task with m threads, m synthetic tasks (with one thread of execution) will be included in the model.

# 2.2 Sporadic Task Model

The sporadic task model [18] is used as a representative of the classical perspective and as the basis for modification to suit BUNDLE's task model. The set of tasks n is represented by the symbol  $\tau = \{\tau_0, \tau_1, ..., \tau_{n-1}\}$ . A task is a computation that performs a specific function by executing on a processor. A job released by a task is a request to perform the computation within a specific time frame. Each task i is an ordered triple of minimum inter-arrival time p, relative deadline d, and worst case execution time c,  $\tau_i = (p_i, d_i, c_i)$ . The minimum interarrival time of a task is the fewest number of processor cycles between job releases, which will take no more than the cycles given by the worst case execution time to complete. Jobs are indexed by their release k for a task i,  $J_{i,k}$  with an absolute release time of  $R_{i,k}$ . Each job also has an absolute deadline calculated from its release time and the task's relative deadline  $D_{i,k} = R_{i,k} + d_i$ . If the job does not complete its execution before the absolute deadline it is called a deadline miss.

A *scheduling algorithm* selects which job will execute on a processor at any moment. Scheduling algorithms make their decisions online, or offline. Online algorithms make scheduling decisions while the system is executing jobs, offline algorithms predetermine job and processor assignments. Jobs are given a static or dynamic priority depending on the algorithm which influences which job will be scheduled.

A schedulability test determines if all jobs that potentially released by  $\tau$  will always meet their deadlines when scheduled by an algorithm A. If all potential job releases will meet

their deadlines the task set is deemed *schedulable*. A test is said to be *sufficient* if a task set is schedulable by *A* satisfies the test. However, if the test is not satisfied the task set may still be schedulable. A test is said to be *necessary* if all schedulable task sets satisfy the test.

### 2.3 Architecture Model

This work is focused on a single processor with a single level direct-mapped cache, in Chapter 8 the scope is expanded to multiple processors. Instructions and data are loaded from main memory into the cache before they are used by the processor. The smallest unit of storage for main and cache memory is a *block*. A block holds one or more *words* with a size expressed in bytes.

When a block is moved from main memory to cache the number of cycles required to perform the operation is called the block reload time, abbreviated BRT and represented by the symbol  $\mathbb{B}$ . Regardless of the instruction type, all instructions take the same number of cycles per instruction (CPI) to complete, represented by the symbol  $\mathbb{I}$ . Execution of an instruction with values exclusively found in the cache is referred to as a *cache hit* consuming  $\mathbb{I}$  cycles. If a value is not found in the cache, it is called a *cache miss* incurring the cost of a BRT before execution, taking  $\mathbb{B} + \mathbb{I}$  cycles.

Generally, caches may have multiple levels and replacement policies. This work is limited to single level direct-mapped caches where each block of main memory maps to exactly one block in the cache. The size of the cache is given by the number of blocks s. Typically, cache memory is segregated by purpose: one cache for instructions and another cache for data. This work applies only to the more predictable instruction cache.

Cache memory is typically smaller (and faster) than main memory. To be able to cache

any value from main memory a mapping between the two is needed. For a direct-mapped cache [19], each block of main memory is mapped to exactly one block in the cache. For a given program address a in main memory, the block of main memory a belongs to is denoted  $\hat{M}(a)$ . The cache block that a belongs to and  $\hat{M}(a)$  maps to is given by M(a).

# 2.4 Objects, Tasks, Threads, Ribbons, Entry Points

Programs take many forms, from scripting languages, compiled programs, assembly, and machine instructions. An *executable object* or object, are the machine encoded instructions that execute upon the processor. Every instruction has an absolute address in main memory denoted *a*. An object of a task is loaded into main memory as part of releasing a job. Instructions of an object may access, by in memory address, any other instruction or data value of the job. The combined set of reachable addresses for a job is referred to as the *memory space* of the job or task. For simplicity, we assume all jobs of the same task are loaded into the same absolute location in main memory with the same memory space for each release.

Tasks in the sporadic model implicitly represent the object, and memory space of each execution request; a job. Jobs also have an implicit entry point, a single instruction from which execution may begin. In contrast, a multi-threaded program makes multiple requests to execute the same object within the same memory space. These requests are referred to as threads. Additionally, a multi-threaded program may have multiple entry points. As such, a multi-threaded program does not align well with the sporadic model.

To address these shortcomings, the sporadic model is modified for multi-threaded programs. The set of task  $\tau = \{\tau_0, \tau_1, ..., \tau_{n-1}\}$  is preserved. However, each task is represented

by a triple of period, relative deadline, and initial ribbon,  $\tau_i = (p_i, d_i, \rho_i)$ . A *ribbon* is the set of instructions reachable from a single entry point and is identified by the address of its entry point  $a_i$ . A *thread*  $t_i$  is a single request to execute the instructions of a ribbon  $\rho_i$ . When referring to an arbitrary thread of  $\rho_i$  the notation  $t_i$  will be used. However, when referring to a specific thread the notation includes an index, i.e. the third thread of  $\rho_i$  is  $t_{i,3}$ . When a job is released, execution begins with threads of the initial ribbon called *initial* threads.

A ribbon  $\rho_i$  that is within the object of a task  $\tau_j$  is said to *belong* to a task, denoted  $\rho_i \in \tau_j$ . Similarly, a thread belongs to a ribbon  $t_i \in \rho_i$ , the thread also belongs to the task the ribbon belongs to  $t_i \in \tau_j$ , and a thread belongs to the job it was released from  $t_i \in J_{i,k}$ . All threads that belong to the same job may access the entire memory space of the job. No thread belonging to one job may access the memory space of a different job. Although the model supports the release of additional threads by the initial and subsequent threads, such release patterns are not explored in this work.

### 2.5 Control Flow Graphs

A key concept in BUNDLE's approach to program analysis and scheduling is the control flow graph (CFG) [20]. A control flow graph, is a weakly connected directed graph G given by the triple of nodes, edges, and entry instruction G = (N, E, h). Typically, the nodes  $n \in N$  of a CFG are basic blocks. A basic block is a set of instructions that execute serially; if the first instruction is executed the remaining instructions of the basic block will always execute one after another (unless an error or interrupt occurs). Basic blocks are identified by their starting instruction. Directed edges between nodes  $(u, v) \in E \land u, v \in N$

represent the possible changes in the execution path through the CFG. Execution begins with the entry instruction h, which can reach any other node in the graph. All paths through the CFG begin with h and end in a single terminal node denoted z.

Treatment of control flow graphs within this work differs from their typical use in a simple but important way. Nodes of a CFG are single instructions rather than basic blocks. A compatible definition would be that all basic blocks are of length one. Several operations will be described that divide and reassemble the control flow graph of a ribbon. The control flow graph will be separated into conflict free regions (these are also control flow graphs). Conflict free regions will then be assembled into a conflict free region graph (also a control flow graph) where conflict free regions act as nodes not graphs. The relationship between these graphs is detailed Chapter 5.

# 2.6 Notation Summary

The following table summarizes the notation given in this section, it also lists symbols that will be used consistently throughout later sections.

| Symbol                         | Meaning                                                                       |  |

|--------------------------------|-------------------------------------------------------------------------------|--|

| au                             | Set of $n$ tasks $\{\tau_0, \tau_1,, \tau_{n-1}\}$                            |  |

| $\tau_i = (p_i, d_i, \rho_i)$  | A task with minimum inter-arrival time, relative deadline, and initial ribbon |  |

| $J_{i,k} = (R_{i,k}, D_{i,k})$ | Job release $k$ of task $i$ with absolute release time and absolute deadline  |  |

| $\mathbb{B}$                   | Block Reload Time (BRT)                                                       |  |

| I                              | Cycles Per Instruction (CPI)                                                  |  |

| $ ho_i$                        | A ribbon                                                                      |  |

| $a_i$                          | An address in main memory                                                     |  |

| G = (N, E, h)                  | Control Flow Graph (CFG) of nodes, edges, and entry instruction               |  |

| R = (N, E, h)                  | Conflict Free Region Graph (CFRG)                                             |  |

| M(a)                           | Block of cache memory utilized by absolute memory address <i>a</i>            |  |

| $\hat{M}(a)$                   | Block of main memory a resides in                                             |  |

| s                              | 0. 0.1 1 . 11 1                                                               |  |

| m                              | Number of initial threads released with each job                              |  |

| Н                              | A set of CFR entry points                                                     |  |

| T                              | Set of threads                                                                |  |

| $t_i$                          | A thread of ribbon $\rho_i$                                                   |  |

| $t_{i,k}$                      | The $k^{th}$ thread of ribbon $\rho_i$                                        |  |

| $\pi$                          |                                                                               |  |

| C                              | Simulated cache with methods: present, insert, clear, conflicts               |  |

| p(n)                           | Set of next intra-thread cache conflicts                                      |  |

| ×                              | Intra-thread cache conflict                                                   |  |

|                                | P(n) Set of next inter-thread cache conflicts                                 |  |

| $igotimes_L$                   | Inter-thread cache conflicts                                                  |  |

| L                              | Length of path                                                                |  |

| $\overline{\omega}_i$          | Priority of CFR (bundle) $n_i$                                                |  |

| $c_{n_i}(m)$                   | WCETO of CFR $n_i$ for $m$ threads                                            |  |

| $c_i(m)$                       | WCETO of task $\tau_i$ for $m$ threads                                        |  |

Table 2.1: List of Symbols

### CHAPTER 3 INTER-THREAD CACHE BENEFIT

Central to BUNDLE's positive perspective is the inter-thread cache benefit. This chapter provides a definition of the benefit. Additionally, the impact of the benefit is directly compared to the classical perspectives of WCET and CRPD analysis by means of an example. To ease the presentation for the reader, the following table summarizes the symbols required to follow the example.

| Symbol       | Meaning                                        |  |

|--------------|------------------------------------------------|--|

| $\tau$       | Set of tasks                                   |  |

| $	au_i$      | Task i                                         |  |

| $J_{i,k}$    | $k^{th}$ job of task $i$                       |  |

| $ ho_j$      | A ribbon $j$                                   |  |

| $t_{i,k}$    | $k^{th}$ thread of ribbon $\rho_i$             |  |

| m            | Number of threads released per job of $\tau_1$ |  |

| a            | Main Memory Address                            |  |

| M(a)         | Cache Block Containing $a$                     |  |

| $\mathbb{B}$ | Block Reload Time                              |  |

| I            | Cycles Per Instruction                         |  |

# 3.1 Defining the Inter-Thread Cache Benefit

As part of scheduling a job on the processor, the object of the job's task is copied into main memory. Additional memory may be reserved or requested by each job, increasing its address space. In Figure 3.1, the address spaces of the fourth job of task one and the second job of task three are shown in main memory. The shaded area is

Figure 3.1: Address Space for Two Jobs

the copy of the executable object, and the sinuous area is the additional reservation made by the job.

Threads share the address space of their job. A thread  $t_j$  that belongs to a job of task  $\tau_i$  ( $t_j \in \tau_i$ ), resides in the memory space of a job  $J_i$  of task  $\tau_i$ . Within an address space, instructions have an address a which maps to a cache block M(a) (illustrated in Figure 3.1).

When a thread  $t_k$  executes without interruption by preemption, an instruction access that results in a cache miss is called an *opportunity instruction*, or simply an *opportunity*. Similarly, during uninterrupted execution, any instruction access that hits the cache is called an *expected instruction* or an *expectation*.

When multiple threads are executed, the execution time of one or more threads may be influenced by cache interactions. When a thread  $t_j$  preempts a thread  $t_k$ ,  $t_j$  may evict cache blocks of  $t_k$  placed there. If those evicted cache blocks correspond to expected

instructions,  $t_j$  will increased  $t_k$ 's execution time since  $t_k$  must now pay  $\mathbb{B}$  for each evicted block. Conversely, a thread  $t_j$  may unexpectedly place opportunity instructions of  $t_k$  in the cache during a preemption of  $t_k$ , reducing  $t_k$ 's execution time.

Inter-Thread Cache Benefit: Thus, the inter-thread cache benefit for a thread of  $t_j$  is the speed-up of  $t_j \in \tau_i$  due to the conversion of opportunities into expectations by the placement of values in the cache from a thread of  $t_k \in \tau_i$  when  $t_k$  is scheduled before  $t_j$ .

# 3.2 Comparison of Perspectives

| Tasks               | Task                          | Ribbons             | Thread Releases   |

|---------------------|-------------------------------|---------------------|-------------------|

| $\tau = \{\tau_1\}$ | $\tau_1 = (p_1, d_1, \rho_1)$ | $\rho = \{\rho_1\}$ | m=2               |

| Cache Siz           | e (Number of Blocks)          | CPI                 | BRT               |

| s = 200             |                               | I = 1               | $\mathbb{B} = 10$ |

Table 3.1: Example Model Parameters

Using the model parameters in Table 3.1, an example ribbon  $\rho_1$  releasing two threads is presented as a CFG in Figure 3.2. The purpose of this example is to clarify the inter-thread cache benefit and expose the pessimism in the classical WCET, CRPD, and scheduling analysis techniques.

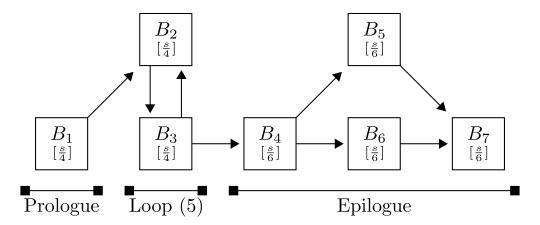

Figure 3.2: Control Flow Graph for:  $\rho_1$

| Block | Category   |  |

|-------|------------|--|

| $B_1$ | must-miss  |  |

| $B_2$ | first-miss |  |

| $B_3$ |            |  |

| $B_4$ |            |  |

| $B_5$ | must miss  |  |

| $B_6$ | must-miss  |  |

| $B_7$ |            |  |

| Cache Part n of 12 | Blocks            |       |       |

|--------------------|-------------------|-------|-------|

| 1                  |                   | $B_5$ | $B_6$ |

| 2                  | $B_1$             | $B_7$ |       |

| 3                  |                   | $D_7$ |       |

| 4                  | $B_2$             |       |       |

| :                  | $B_2$ $B_3$ $B_4$ |       |       |

| 11                 | $B_4$             |       |       |

| 12                 |                   | $B_5$ | $B_6$ |

Table 3.2: Categories from [1, 2] and Cache Assignment

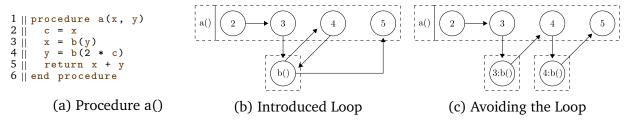

The CFG in Figure 3.2 utilizes basic blocks (serialized sets of instructions) with lengths expressed in terms of the cache size. Below each block labeled with a B, is the block's length expressed as fraction of the cache size s. The parenthesized value at the bottom of the figure indicates the maximum number of iterations the loop will execute. Figure 3.2 differs from the common use of CFG's in this work, other figures will typically use basic blocks of length one.

For the purpose of the example, the ribbon  $\rho_1$  is analyzed by the WCET calculation methods of Arnold [1] and Mueller [2]. CRPD costs are determined using Lee et al.'s [21] useful cache block (UCB) technique. Although simpler and less accurate than modern techniques, these methods were chosen for illustrative purposes and their continued use in subsequent works.

A necessary step in WCET calculation is the categorization of instructions, such as *must-miss* and *first-miss*. A must-miss never hits the cache. A first-miss always hits the cache after its initial miss. To find first-miss instructions the CFG is searched iteratively looking for return paths. Only instructions with return paths are candidates for first-misses. Table 3.2 presents the cache mapping and categorizations.

Lee et al.'s [21] useful cache block (UCB) approach to CRPD calculation borrows the iterative return path approach. From Figure 3.2, the only candidates for first-miss and UCB instructions are contained in basic blocks  $B_2$  and  $B_3$ . No other blocks have a return path and would be categorized as must-miss, and not useful.

#### 3.2.1 WCET

Using these categorizations and the loop bound, the worst case execution time of  $\rho_1$  is the sum of the execution times of the prologue, the entry executions of  $B_2$  and  $B_3$ , the repetitions of  $B_2$  and  $B_3$ , and the epilogue. Table 3.3 gives the intermediate values; the total execution time taking into consideration reloads is:  $\frac{s(\mathbb{B}+\mathbb{I})}{4} + \frac{2s(\mathbb{B}+\mathbb{I})}{4} + \frac{8s(\mathbb{I})}{4} + \frac{3s(\mathbb{B}+\mathbb{I})}{6} = \frac{s(5\mathbb{B}+13\mathbb{I})}{4} = 3150$

| Section         | Basic Blocks                        | WCET                                                               |

|-----------------|-------------------------------------|--------------------------------------------------------------------|

| Prologue        | $B_1$                               | $\left(\frac{s}{4}\cdot(\mathbb{B}+\mathbb{I})\right)$             |

| Loop Entry      | $B_2 + B_3$                         | $\left(\frac{s}{4} \cdot 2 \cdot (\mathbb{B} + \mathbb{I})\right)$ |

| Loop Repetition | $(B_2+B_3)\cdot 4$ (repeats)        | $\left(\frac{s}{4} \cdot 2 \cdot 4 \cdot (\mathbb{I})\right)$      |

| Epilogue        | $B_4 + (B_5 \text{ or } B_6) + B_7$ | $\left(\frac{s}{6} \cdot 3 \cdot (\mathbb{B} + \mathbb{I})\right)$ |

Table 3.3: Segment WCET

Under the classical model two synthetic tasks are created for the two threads of  $\rho_1$ . Assigning the WCET of 3150 to both synthetic tasks, the total execution requirement for one job is 6300 every  $p_1$  time units.

However, this is overly pessimistic. The worst possible execution scenario and schedule for the two threads is the sequential execution of  $t_{1,1}$  followed by  $t_{1,2}$ , where  $t_{1,1}$  takes the "high" road executing  $B_5$  and  $t_{1,2}$  takes the low "road" through  $B_6$ . This maximizes the number blocks  $t_{1,2}$  will miss from the cache. Even so, blocks  $B_2$ ,  $B_3$ ,  $B_4$  are present in the cache when  $t_{1,2}$  reaches them.

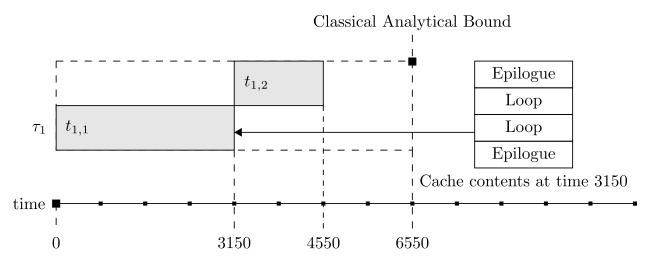

Using the worst case schedule, the WCET of  $t_{1,2}$  is:  $\frac{s(\mathbb{B}+\mathbb{I})}{4} + \frac{5s(\mathbb{I})}{4} + \frac{s(\mathbb{B}+\mathbb{I})}{4} + \frac{s(\mathbb{I})}{4} = \frac{2s(\mathbb{B}+4\mathbb{I})}{4}$  = 1400. The total job execution requirement is 3150 + 1400 = 4550 cycles, less than the 6300 cycles calculated from the synthetic task analysis and application of the Arnold and Mueller approaches. Figure 3.3 illustrates the worst possible schedule of  $t_{1,1}$  and  $t_{1,2}$  including a summary of cache contents at time 3150, which is compared to the WCET bound calculated from classical perspective.

Figure 3.3: Worst Schedule of  $\tau_1$ , 4550 Cycles

#### 3.2.2 CRPD

Cache Related Preemption Delay (CRPD) is an analytical technique that accounts for the execution time extension of one task due to the cache interference of another. A task executing in isolation may store and reuse values from the cache. When preempted, those stored cache values may be invalidated before they are reused. Upon resumption the preempted task must pay the BRT for each invalidated cache block.

A method for CRPD calculation is the Lee et. al [21] useful cache block (UCB) approach. A UCB is "a cache block that contains a memory block that may be referenced before being replaced by another memory block." CRPD for a task is limited by the num-

ber of UCBs within it.

From Figure 3.2 there are two basic blocks that contribute UCBs to the ribbon  $\rho_1$ :  $B_2$  and  $B_3$ . Applying Lee's method, the CRPD of a preemption of thread of  $\rho_1$  is  $\frac{2s(\mathbb{B}+\mathbb{I})}{4}=1100$ . However, this bound is overly pessimistic.

By construction (and shown in Table 3.2) once the "Loop" instructions are cached they cannot be invalidated. If  $t_{1,1}$  were preempted by  $t_{1,2}$  after the first iteration of the loop, the instructions of the loop body ( $B_2$  and  $B_3$ ) would be cached in parts 4-10. No other instructions of  $t_{1,2}$  map to those cache lines and cannot invalidate them. Furthermore, there is no schedule of  $t_{1,1}$  and  $t_{1,2}$  which incurs any CRPD.

Lee's approach to CRPD calculation is known to be an overestimate, there are refinements such as the UCB-ECB [22], UCB-Union, and UCB-Union Multiset [13] approaches. However, the UCB calculation is a component of each of them and the advanced techniques suffer from the same inability to address cache memory as a benefit rather than a detriment. Similarly, the Arnold [1] and Mueller [2] approaches play a role in subsequent WCET methods and none incorporate the inter-thread cache benefit.

#### CHAPTER 4 RELATED WORK

While no existing work focuses on the inter-thread cache benefit to improve schedulability, this chapter provides a survey of related publications from the classical and positive perspectives. Chapter 1 gave a brief introduction to hard real-time systems and cache memory, the reader may find Liu's [23] and Hennessey's [19] work helpful on the topics.

## 4.1 Worst-Case Execution Time and Cache Memory

Cache memory brings to additional complexity to worst-case execution time analysis through non-uniform execution times due to cache misses or hits and has received considerable attention [24, 25]. A central concept of accounting for non-uniform execution times is the categorization of memory references (including instructions). A reference will be categorized as *first-miss*, *must-miss*, or *must-hit*. A must-miss reference will never be found in the cache during execution, where a must-hit will always be present. A first-miss will absent for its initial execution reference and present for others.

The works of Arnold [1] and Mueller [2, 12] use static cache simulation for direct-mapped caches to classify references. Their techniques involve repeatedly searching the CFG of the task for return paths to references. These techniques have been refined and expanded: White et al. [26] incorporated data caches, Li et al. [27] included set-associative caches and pipelines, among others.

Arnold and Mueller's work are of particular value to this work due to their role in Heptane. An open-source WCET analysis tool, Heptane extends Mueller's work in part to demonstrate the incorporation of branch prediction into WCET analysis [28]. In this work,

the Heptane toolset is extended to support our proposed WCETO analysis for BUNDLEP in Chapter 6.

# 4.2 Cache Related Preemption Delay

As an area of study cache related preemption delay (CRPD) is the examination of the extension of execution time of one job due to the preemption of another. Taking the perspective of a task being preempted, before preemption there are blocks in the cache that will be reused later. When preempted, the preempting task will execute instructions evicting the reusable blocks. Upon resuming the preempted task, the time required to reload those blocks that would have been reused is the CRPD.

Typically denoted  $\gamma$  in the literature, the CRPD of a task is an upper bound on the amount of time required to reload cache blocks evicted during a preemption. Schedulability tests incorporate  $\gamma$  in one of two ways 1.) increasing a task's WCET value 2.) adding (a factor of)  $\gamma$  to the task's response time [29, 30, 13, 14, 22, 31, 15].

Calculating the CRPD for a task or task set is made from one of three perspectives. The *preempting perspective* where the bound on the number of cache blocks affected is determined by the preempting task. The *preempted perspective* where the bound on the number of cache blocks affected is determined by the preempted task. The *combined perspective* bounds the number of cache blocks affected by considering both the preempted and preempting tasks.

Tomiyama and Dutt [17] developed an approach based on the preempting perspective. They are credited with creating the concept of the *evicting cache block* (ECB). Defined as "a memory block of the preempting task is called an evicting cache block, if it may be

accessed during the execution of the preempting task." [13].

Lee [21] take the perspective of the preempted task, noting that a preemption may not be harmful. For a preempted task, only those cache blocks which are reused can extend execution times if evicted. Cache blocks which are not reused may be evicted without penalty. They call these cache blocks *useful cache blocks* or UCBs, and are defined as "a cache block that contains a memory block that may be referenced before being replaced by another memory block".

The combined perspective considers the possible harm a preempting task could inflict on a preempted task. The number of useful cache blocks limit the total number of affected blocks in the preempted task. Negi et al. [22] developed the UCB-ECB approach using the intersection of the preempted tasks UCBs and the preempting tasks ECBs to bound the CRPD. Tan and Mooney [15] improved upon the UCB approach, observing the CRPD cost included multiple evictions for the same UCB per preemption. Their approach, named the UCB-Union also considers the UCBs of the preempted task with the ECBs of preempting tasks.

Among the combined approaches, Altmeyer's [14] ECB-Union Multiset, and UCB-Union Multiset out-perform the others. Principally, the use of a multi-set prevents over counting of evictions due to multiple levels preemptions during a single preemption of a lower priority task. Altmeyer employs an alternative response time function developed by Staschulat [31] with a cumulative CRPD value, rather than a per preemption value. Lastly, Altmeyer proposes what he coins the "Combined" approach which takes the minimum of the ECB-Union Multiset and UCB-Union Multiset which out-performs all methods.

Tighter analysis (reducing) of CRPD values increases schedulability by limiting the im-

pact of each preemption. A complimentary method to reducing the impact of CRPD on schedulability is to limit or defer preemptions. In the limited or deferred preemption setting, a higher priority task may preempt a lower priority task only when some condition is satisfied [32, 33, 34, 35]. Heuristics for placing preemption points to reduce CRPD values were proposed in [36, 21]. Bril et al. [37] augment preemption threshold scheduling by incorporating CRPD values into schedulability analysis. Bertogna et al. [38] provide a more formal approach for optimally determining preemptions in programs that can be represented by linear control flowgraphs given the CRPD overhead of each preemption and a bound on the maximum non-preemption region [34]. Later work, extended this to more general control flowgraphs [39] or more precise CRPD characterizations of the preemption costs [40].

Each of the CRPD methods described are limited to a single threaded task. The proposed techniques of this work focus on multi-threaded tasks. While not directly applicable, the concepts developed for CRPD calculation of ECBs and UCBs are leveraged in the proposed work. These existing methods also serve as a basis for comparison of the classical perspective to the proposed methods.

## 4.3 Cache Analysis in Multi-Threaded Programs

Multi-threaded WCET analysis typically takes the classical perspective on cache memory. An example is feasibility analysis for the fork-join [6] model, where the WCET of a thread is the longest single threaded execution through the object of the thread. Each thread's WCET value contributes to the overall demand independently of other threads.

Concurrent program analysis [41] of has been extended to consider variable configura-

tions such as shared multi-level caches [42]. These methods take the negative perspective, where cache interactions exclusively increase execution times. For shared caches, the analysis includes the maximum extension due to cache sharing, by constructing the worst-case interleavings of threads.

# 4.4 Predictable Cache Behavior

Refinements of the classical perspective include techniques that attempt to mitigate or manage the cache impact between tasks. Their goal is to reduce or eliminate conflicts between jobs by creating predictable cache behavior. On multi-core systems, Memory-Centric Scheduling [43] limits execution of tasks by considering its access to main and cache memory. Memory-Centric Scheduling depends on tasks that fit the PRedictable Execution Model (PREM) [44].

PREM-compliant tasks are divided (by the programmer) into intervals in one of two categories. Compatible fall into the first category, accessing main memory at any point during execution. Predictable intervals are the second category, and are further divided into loading and execution phases. During the loading phase all main memory accesses are placed in the lowest level cache. When the loading phase is complete, the execution phase may begin where no memory accesses will result in a cache miss.

Under PREM, great care is taken to avoid concurrent memory access between tasks. No two loading phases may take place simultaneously. Furthermore, compatible intervals are treated as loading phases. Isolation of tasks is by design due to the negative perspective of caches, as such PREM is unable to account for the potential inter-cache benefit between threads.

PREM tasks require the programmer to define compatible and predictable intervals. When active participation in memory management is infeasible or undesirable, passive predictable cache behavior may involve several techniques. An example of combined management efforts is made in Ward's allocation framework for mixed-criticality on multi-core MC<sup>2</sup> [45].

Ward applies three techniques simultaneously. Page coloring (also referred to as partitioning) [46] is used, where pages of memory are assigned colors in such a manner that no two pages can conflict in the cache. Tasks are assigned colored pages as their working set of memory during execution. Cache locking is introduced [45], which requires a task to hold a color lock for each of the colored pages it needs before execution. Cache scheduling considers the colors of each task when scheduling them, (possibly preemptively scheduling them) to avoid conflicts with other tasks. Similar to PREM, the focus is on isolation to reduce the negative impact of cache interference between tasks without considering the positive impact of caches.

# 4.5 Positive Perspectives on Caches

We are aware of two techniques that take a positive perspective on caches. Calandrino [47] limits the cache spread of threads (called subtasks) for multi-threaded tasks. The empirical results show higher cache hit rates. However, no analytical method to bound the cache spread is given.

Persistent Cache Blocks [48, 49] (PCBs) take a positive perspective on caches for subsequent job releases. A PCB is a cache block that remains in the cache after a job has completed which is then reused by a subsequent job. As such, PCBs are limited to tasks.

Additionally, the PCB approach requires modification to existing worst case response time (WCRT), WCET and CRPD analytical methods. Over-simplistically, PCBs are removed from WCET calculations and included once in response time analysis. The result is a benefit to system schedulability.

#### CHAPTER 5 SINGLE-TASK BUNDLE

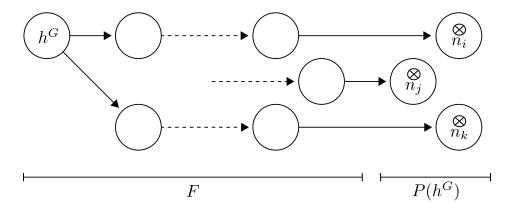

The BUNDLE scheduling algorithm and WCETO analysis serve as the basis of our positive perspective on instruction caches. It is limited to a single processor, and single task releasing m initial threads per job release. Scheduling and analysis operate upon derivatives of the control flow graph of the initial ribbon called conflict free regions and the conflict free region graph. The description of BUNDLE's techniques begins with a definition of scheduling algorithm, followed by formal definitions of conflict free regions and conflict free region graphs before detailing the WCETO method.

# **5.1** BUNDLE **Scheduling**

BUNDLE takes its name from the manner in which it schedules threads of a job. Threads are placed in a container called a *bundle*, only one bundle is active, and only threads of the active bundle are scheduled on the processor at any time. A bundle is associated with a conflict free region (CFR): a subset of instructions of the ribbon where no two instructions conflict in the cache. When a bundle is *active* or *inactive*, it is also said that the associated conflict free region is active or inactive. A thread leaves the active bundle by attempting to execute an instruction of a different region. When leaving the active bundle and entering a new bundle a thread is blocked until the bundle it enters becomes active. The active bundle is *depleted* when all threads leave it. Scheduling threads by their bundle allows the sharing of cache values (hits) to be quantified and the penalty of cache misses reduced.

To provide context, BUNDLE's scheduling algorithm is presented as pseudocode in Figure 1. Since the algorithm is limited to one task, the task and job indices are omitted.

Introduced in the pseudocode are several new symbols. T is the set of m threads per job release. H is the set of entry instructions of CFRs. Though previously unstated, every CFR (which is a CFG) has an entry instruction that distinguishes it from the others. Line 8 utilizes a unique mechanism for halting threads, before a thread can execute the entry instruction of an inactive CFR the thread is blocked and the scheduler is invoked; we call this *anticipating execution*. We are unaware of any hardware platform that supports anticipating execution, nor is an implementation suggested in this section. For BUNDLE we assume the mechanism exists, a hardware mechanism is proposed in Section 6.4.1 suitable for both BUNDLE and BUNDLEP.

#### **Algorithm 1** BUNDLE Scheduling Algorithm

```

\triangleright Set of m threads

1: T

2: H

3: procedure BUNDLE

4:

A \leftarrow T

Active bundle

> Array of inactive bundles (blocked threads)

B \leftarrow \varnothing

5:

while true do

6:

Select t \in A

7:

RUN(t) until t's next instruction is h \in H

8:

B[h] \leftarrow B[h] \cup a

▷ Place t in a new bundle

9:

A \leftarrow A \setminus t

\triangleright Remove t from the active bundle

10:

▷ The active bundle has been depleted

if |A| = 0 then

11:

Select z \in H, |B[z]| \neq 0

12:

A \leftarrow B[z]

13:

B[z] \leftarrow \emptyset

14:

end if

15:

end while

16:

17: end procedure

```

At the beginning of the BUNDLE procedure, the active bundle A contains all threads of the job waiting to execute the initial instruction of the ribbon. For each iteration of the loop a thread is selected from the active bundle on Line 7. The thread t executes until it encounters an entry instruction of a different bundle on line 8, it is then removed from the

active bundle placed in its new inactive bundle and blocked. If removing t depleted the active bundle A, an *arbitrary* non-empty bundle is selected as active in the body of the **if** block on Line 11. The loop repeats until all threads complete.

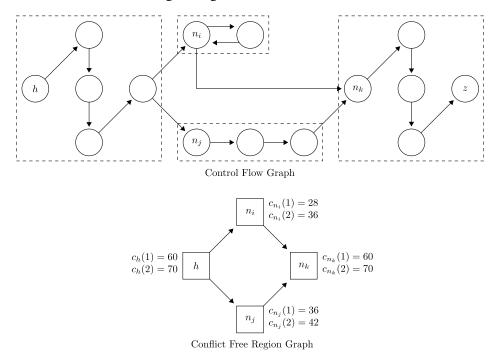

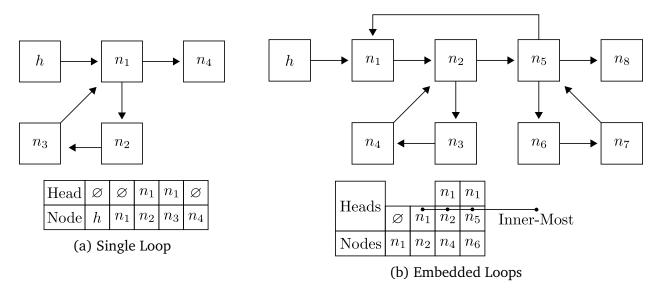

## 5.2 Conflict Free Regions and Conflict Free Region Graphs

The scheduling algorithm relies upon bundles and their associated conflict free regions (CFRs) to make scheduling decisions. Calculations for WCETO values also depend on conflict free regions over the structure of the conflict free region graph (CFRG). CFRs and the CFRG are derived from the CFG of the ribbon. This section provides formal definitions and methods of creation for CFRs and CFRGs suitable for BUNDLE.

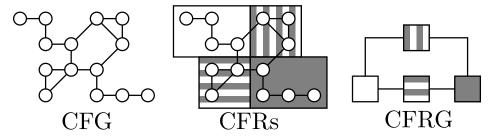

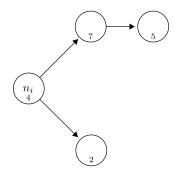

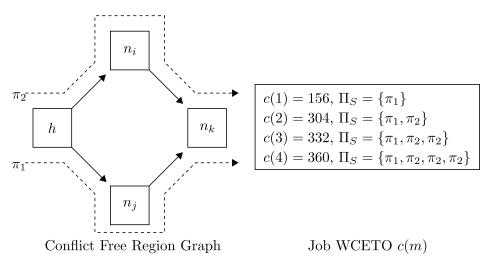

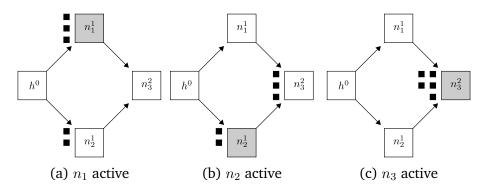

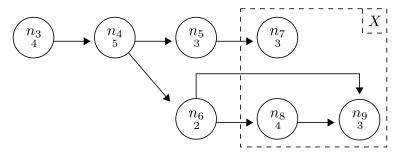

Figure 5.1: CFG, CFRs, and CFRG of a ribbon

The following definitions refer to the CFG of a ribbon as G=(N,E,h) and the CFRG R=(N,E,h). When necessary to remove ambiguity the sets are given a superscript of their origin, e.g.  $N^G$  identifies the nodes of the CFG and  $N^R$  the nodes of the CFRG. Recall the nodes of a CFG are individual instructions, edges represent potential paths of execution between them. Nodes of the CFRG are CFRs, when referring to a specific CFR  $n_i$  is used, nonspecific CFRs are given by F. CFRs are extracted from the CFG and placed in the CFRG with their connectivity preserved. For an edge  $(n_1, n_2)$  in the CFG, if  $n_1$  and  $n_2$  reside in distinct CFRs, then the CFRG must contain an edge between those CFRs. The relationship

between the CFG, CFRs, and CFRG of a ribbon is illustrated in Figure 5.1.

**Regions of a Control Flow Graph**: a region is a selection of the vertexes and edges of a CFG G. When extracting a region from G, the graph's connectivity is preserved. I.e, two vertexes connected in G must also be connected in any region containing both.

Formally, for a region r=(N,E,h) of a control flow graph  $G=(N^G,E^G,h^G)$ , where  $N\subset N^G$  and  $E\subset E^G$ . For all pairs of vertexes  $(u,v)\in N$ ,  $(u,v)\in E\iff (u,v)\in E^G$ . Regions contain an entry instruction  $h\in N$  that is weakly connected to all other vertexes in N.

Conflict Free Region: a region F = (N, E, h) of G is conflict free if no two instructions of F in distinct memory blocks utilize the same cache block.

$$\forall n_i, n_j \in N, \hat{M}(n_i) \neq \hat{M}(n_j) \iff M(n_i) \neq M(n_j)$$

To restate, the requirements of a CFR F are:

- No two instructions (outside of the same main memory block) map to the same cache block

- 2. All instructions of F are weakly connected to the entry instruction h

- 3. For any two instructions  $(n_i, n_j) \in F$ , if there was an edge between them in G then  $(n_i, n_j) \in E$  (of F)

Figure 5.2: Requirements of Conflict Free Region

Conflict Free Region Graph: a conflict free region graph  ${\cal R}=(N^R,E^R,h^R)$  is a CFG of

CFRs of  $G=(N^G,E^G,h^G)$  where connectivity between CFRs is preserved and all instructions of G are included in some CFR  $n \in N^R$ . In the definitions below, a CFR i is denoted  $n_i \in N^R$ . For a CFR  $n_i$  the triple is given by  $n_i = (N_i, E_i, h_i)$ .

$$\forall n \in N^G, n \in \bigcup_{n_j \in N_i \land n_i \in N^R} n_j \tag{5.2.1}$$

$$\forall (u, v) \in E^G, u \in N_i \land n_i \in N^R \land v \notin N_i \implies \exists (n_i, n_j) \in E^R, v \in N_j$$

(5.2.2)

Equation 5.2.1 ensures that each node of the CFG is included in some CFR, the set of instructions  $n_j \in N_i \wedge n_i \in N^R$  are those  $n_j$  found in the set of instructions  $N_i$  from the CFR i which is contained in the CFRG as  $n_i \in N^R$ . Equation 5.2.2 preserves connectivity from the CFG in the CFRG, when an edge from the CFG is not contained within a CFR there must exist an edge in the CFRG.

# **5.2.1** Extracting Conflict Free Regions

The process of analyzing the control flow graph and assigning instructions to conflict free regions is called *extraction*. Support for the process is given by the definition of intra and inter-thread cache conflicts. These definitions ensure extraction meets the first requirement for CFRs, that no conflicts exist. The conventional use of symbols will continue for the following definitions, in context of the ribbon being analyzed: CFG  $G = (N^G, E^G, h^G)$ , an arbitrary CFR F = (N, E, h), CFRG  $R = (N^R, E^R, h^R)$ , CFRs  $n_i = (N_i, E_i, h_i)$  where  $n_i \in N^R$ .

When referring to any type of control flow graph of a ribbon, CFR, CFRG, or CFG the notation remains the same, since all of the structures are CFGs. For a CFG G=(N,E,h) a node  $n\in N$  is an instruction. For a CFR F=(N,E,h) a node  $n\in N$  is also an instruction. For a CFRG R=(N,E,h) a node  $n\in N$  is a CFR. The context determines which type of node or edge is being referred to.

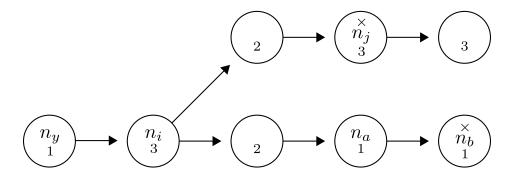

**Valid Path:** a path  $\pi = \langle n_0, n_1, ... \rangle$  of ordered nodes is valid if and only if, for every adjacent pair of nodes  $n_i, n_{i+1}$  in the path there exist a directed edge in the CFG.

$$\forall (n_i, n_{i+1}) \in \pi, (n_i, n_{i+1}) \in E^G$$