# UCC Library and UCC researchers have made this item openly available. Please let us know how this has helped you. Thanks!

| Title                   | High frequency point-of-load (POL) DC-DC converters employing CMOS or GaN HEMT switches                                                              |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)               | Walsh, Eoin                                                                                                                                          |

| Publication date        | 2019-11-23                                                                                                                                           |

| Original citation       | Walsh, E. 2019. High frequency point-of-load (POL) DC-DC converters<br>employing CMOS or GaN HEMT switches. MRes Thesis, University<br>College Cork. |

| Type of publication     | Masters thesis (Research)                                                                                                                            |

| Rights                  | © 2019, Eoin Walsh.<br>https://creativecommons.org/licenses/by-nc-nd/4.0/                                                                            |

| Item downloaded<br>from | http://hdl.handle.net/10468/10881                                                                                                                    |

Downloaded on 2021-11-27T12:39:01Z

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# High Frequency Point-of-Load (POL) DC-DC Converters Employing CMOS or GaN HEMT Switches

By Eoin Walsh.

Submission for MEngSc. University College Cork.

Supervisors Mr. Séamus O'Driscoll Dr. Terence O'Donnell

23/11/2019

# Contents

| Abstract  |                                                      | 10 - |

|-----------|------------------------------------------------------|------|

| 1. Introd | uction                                               | 11 - |

| 1.1 I     | ntroduction to Buck Converters                       | 11 - |

| 1.2 \$    | tep Down Converter Topologies                        | 11 - |

| 1.2.1     | Buck Converter                                       | 12 - |

| 1.2.2     | 3-Level Buck Converter                               | 13 - |

| 1.3 I     | nductor Considerations                               | 14 - |

| 1.4 \$    | witch Losses                                         | 15 - |

| 2. Litera | ture Review and Background Theory                    | 17 - |

| 2.1 0     | Converter Topologies                                 | 17 - |

| 2.1.1     | Buck Converter                                       | 17 - |

| 2.1.2     | Multi-Level Buck Converter                           | 18 - |

| 2.2 H     | High Frequency Magnetics                             | 19 - |

| 2.3 H     | High Frequency Switch Layout                         | 20 - |

| 2.3.1     | Multi-Finger MOSFET                                  | 20 - |

| 2.3.2     | Bulk 180 nm NMOS and PMOS                            | 22 - |

| 2.3.3     | Gallium Nitride High-Electron-Mobility Transistors   | 22 - |

| 2.4 H     | High Frequency Switch Losses                         | 23 - |

| 2.4.1     | Turn-On and Turn-Off Switching Losses                | 23 - |

| 2.4.2     | Diode Reverse Recovery Loss                          | 26 - |

| 2.4.3     | MOSFET Conduction Losses                             | 28 - |

| 2.4.4     | Dead-time Losses                                     | 29 - |

| 2.4.5     | Gate Driving Losses                                  | 29 - |

| 3. Simul  | ations for 2 and 3-Level Buck Converters             | 30 - |

| 3.1 I     | TSpice and MATLAB                                    | 30 - |

| 3.2 I     | Drivers and Bootstrap Capacitors Models              | 30 - |

| 3.3 (     | Dutput Capacitor Model                               | 32 - |

| 3.4 I     | nductor Models                                       | 33 - |

| 3.4.1     | Introduction                                         | 33 - |

| 3.4.2     | Commercial Surface-Mounted Chip Inductors Considered | 33 - |

| 3.4.3     | Candidate Inductors                                  | 35 - |

| 3.4.4     | Coilcraft Inductor Model                             | 35 - |

| 3.4.5     | Bourns Inductor Model                                | 37 - |

| 3.4.6      | 6 Murata Inductor Model                                                         | 37 -      |

|------------|---------------------------------------------------------------------------------|-----------|

| 3.4.7      | 7 TDK Inductor Model                                                            | 37 -      |

| 3.4.8      | 8 Tindall's Inductor and Reference Low Loss <i>Air-core</i> Inductor Models     | 38 -      |

| 3.5        | Switching Behaviour                                                             | 40 -      |

| 3.5.1      | 1 Diode Reverse Recovery and 3 <sup>rd</sup> Quadrant Reverse Conduction        | 40 -      |

| 3.5.2      | 2 Switch Output Capacitance                                                     | 50 -      |

| 3.6        | Full Converter Simulations and Operating Waveforms                              | 55 -      |

| 3.6.1      | 1 2-Level <i>Air-core</i> Buck Converter                                        | 55 -      |

| 3.6.2      | 2 3-Level <i>Air-core</i> Buck Converter                                        | 57 -      |

| 3.6.3      | Buck Converter with Tyndall's TF MoS "MagPwr" MS2 inductor                      | 59 -      |

| 3.6.4      | 4 Buck Converter with Coilcraft PFL1005 Inductor                                | 63 -      |

| 3.6.5      | 5 Buck Converter with Murata LQW18CN55NJ00 Inductor                             | 66 -      |

| 3.6.6      | 6 Analysis                                                                      | 69 -      |

| 3.7        | Breakdown of Switch Losses – Simulated in LTSpice                               | 71 -      |

| 3.7.1      | LS Turn-Off, HS Turn-On, Dead Time $(td(L - H))$                                | 72 -      |

| 3.7.2      | HS Turn-Off, LS Turn-On, Dead Time $(td(H - L))$                                | 73 -      |

| 3.7.3      | 3 Simulated Switch Waveforms Incorporated in MATLAB Code                        | 74 -      |

| 3.7.4      | 4 Circuit Board Parasitic Ringing                                               | 74 -      |

| 4. Oper-76 | n Switch-Node Measurements and Validating Simulations on 2-Level Buck Converter | Prototype |

| 4.1        | Introduction to Open Switch-Node Measurements                                   | 76 -      |

| 4.1.1      | 1 Measurement Equipment                                                         | 76 -      |

| 4.1.2      | 2 Buck Converter Circuit Boards                                                 | 76 -      |

| 4.1.3      | 3 Importance of Measurement Points and Scope Probe Ground Lead Set-Up           | 77 -      |

| 4.2        | Open Switch-Node Measurements (No Inductor Fitted)                              | 78 -      |

| 4.2.1      | 1 Switch-Node Voltage Waveforms and Dead-times                                  | 78 -      |

| 4.2.2      | 2 Measurement Data – Open Switch-node Power Losses                              | 80 -      |

| 4.3        | Open Switch-Node Simulation Set-Up                                              | 81 -      |

| 4.3.1      | Power Path Parasitic Voltage Ringing                                            | 81 -      |

| 4.3.2      | 2 Open Switch-Node Waveforms: Measurements and Simulations                      | 83 -      |

| 4.3.3      | 3 Differences between Measurements and Simulations                              | 84 -      |

| 4.4        | Open Switch–Node Operation                                                      | 85 -      |

| 4.4.1      | 1 Open Switch-Node: SwLSTurn Off                                                | 86 -      |

| 4.4.2      | 2 Open Switch–Node: <i>SwHS</i> Turn On                                         | 87 -      |

| 4.4.3      | 3 Open Switch–Node: <i>SwHS</i> Turn Off                                        | 88 -      |

| 4.4.           | .4 Open Switch–Node: SwLS Turn On                                                                | 89 -        |

|----------------|--------------------------------------------------------------------------------------------------|-------------|

| 4.4.           | .5 Simulated Loss Analyses for Open Switch–Node                                                  | 90 -        |

| 4.4.           | .6 Open Switch–Node Analysis: Power Stage Losses                                                 | 91 -        |

| 4.4.           | .7 Open Switch–Node Analysis: Driver Losses                                                      | 92 -        |

| 4.5            | Simulated Open-Circuit Switch-node Results and Analysis                                          | 93 -        |

| 5. Cor<br>- 96 | nverter Measurements with Tyndall Thin-Film Inductor, <i>Air-core</i> Inductor and SMT Ch<br>5 - | ip Inductor |

| 5.1            | Comparison of Simulated and Measured Results                                                     | 96 -        |

| 5.1.           | .1 PFL1005 Inductor, 2-Level EPC2040 Buck Converter                                              | 96 -        |

| 5.1.           | .2 Air-core Inductor, 2-Level EPC2040 Buck Converter                                             | 97 -        |

| 5.1.           | .3 Tyndall Thin-Film MS2 <i>MagPwr</i> Inductor, 2-Level EPC2040 Buck Converter                  | 99 -        |

| 5.2            | Conclusions Comparisons between Inductors                                                        | 100 -       |

| 6. Sim         | nulated Performance of 2-Level and 3-Level Converters                                            | 101 -       |

| 6.1            | Open-Circuit Switch-Node Converters                                                              | 101 -       |

| 6.2            | 2-Level and 3-Level Converter Power Paths with various Inductors                                 | 102 -       |

| 6.3            | Efficiency over Switching Frequency and Load for 2-Level and 3-Level Converters                  | 103 -       |

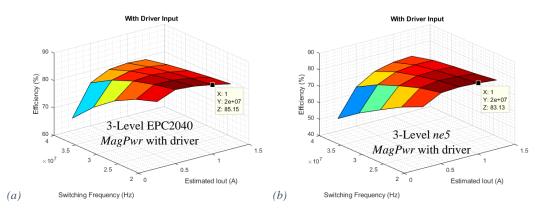

| 6.3.           | .1 Comparison of 2-Level and 3-Level Converter with EPC2040 Switch and <i>MagPu</i><br>- 103 -   | wr Inductor |

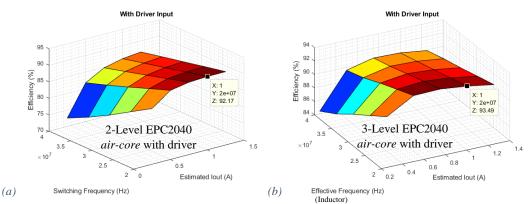

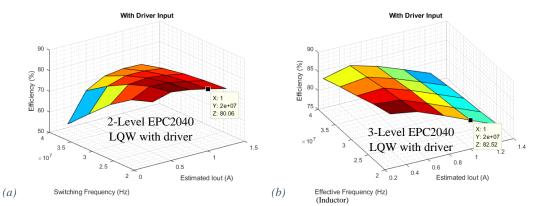

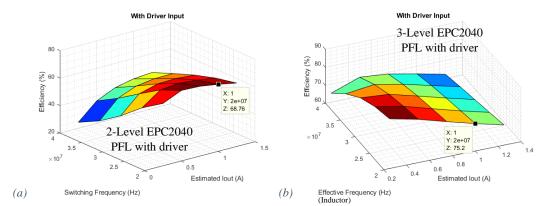

| 6.3.           | .2 Comparison of Inductor Models, in a 2-Level Converter with EPC2040 Switcher                   | s 104 -     |

| 6.3.           | .3 Comparison of Inductor Models, in a 3-Level Converter with EPC2040 Switcher                   | s 105 -     |

| 6.3.           | .4 Comparison of EPC2040 and <i>ne5</i> Switch Converters with <i>MagPwr</i> Inductors           | 106 -       |

| 6.3.           | .5 Comparison of 2-level and 3-Level Converters for the Same Inductor Frequency                  | 107 -       |

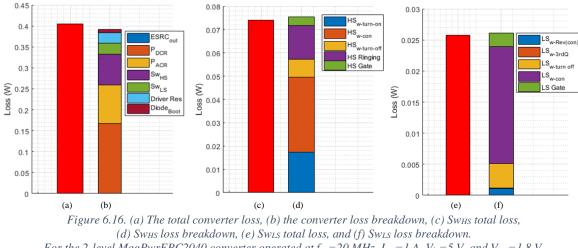

| 6.4            | Simulated Loss Breakdown of 2-Level Converter with EPC2040 and MagPwr                            | 109 -       |

| 6.5            | Discussion on Simulated Converter Losses                                                         | 110 -       |

| 6.5.           | .1 Inductor Losses                                                                               | 111 -       |

| 6.5.           | .2 SwHS Loss Breakdown                                                                           | 112 -       |

| 6.5.           | .3 SwLS Loss Breakdown                                                                           | 113 -       |

| 7. Cor         | nclusions                                                                                        | 114 -       |

| 8. App         | pendix                                                                                           | 116 -       |

| 8.1            | Air-core Inductor Converter Measured Results for 25 MHz.                                         | 116 -       |

| 8.2            | Tyndall Thin-Film MS2 MagPwr Inductor Converter Results for 20 MHz                               | 116 -       |

| 8.3            | Tyndall Thin-Film MS2 MagPwr Inductor Converter Results for 25 MHz.                              | 117 -       |

| 8.4            | Tyndall Thin-Film MS2 MagPwr Inductor Converter Results for 35 MHz                               | 117 -       |

| Variable       | List                                                                                             | 118 -       |

| Reference      | ces                                                                                              | 123 -       |

# Table of Figures

| Figure 1.1. Ideal buck converter: (a) circuit diagram, (b) input voltage, switch-node voltage, and inducto    |

|---------------------------------------------------------------------------------------------------------------|

| current waveforms                                                                                             |

| Figure 1.2. The ideal 3-level buck converter: (a) circuit diagram, (b) switches' gate-source voltag waveforms |

| Figure 1.3. The equivalent circuit model for an inductor. Image from Coilcraft (website) 14                   |

| Figure 1.4. (a) Cross-section of an NMOS, (b) with effective capacitances 15                                  |

| Figure 2.1. Simplified circuit diagram for Intel's FIVR (16-phase buck regulator). Image from [8] 17          |

| Figure 2.2. Topologies for: (a) the 2-level buck, (b) the 4-level buck, and (c) the modified 4-level buc      |

| converter                                                                                                     |

| Figure 2.3. Area vs. efficiency for inductors at various frequencies. From [11]                               |

| Figure 2.4. Top view of MOSFET configurations: (a) single-finger MOSFET, (b) three single-finger              |

| MOSFETs connected in parallel, and (c) three-finger MOSFET.                                                   |

| Figure 2.5. Cross-section of a four-finger n-type MOSFET. Based on [12] 21                                    |

| Figure 2.6. Cross-section of a 5 V ne5 and pe5 180 nm CMOS 22                                                 |

| Figure 2.7. Cross-section of a GaN HEMT, E-mode p-GaN gate. Image from [17]                                   |

| Figure 2.8. Example of the high-side switch waveforms during turn-on with Miller plateau                      |

| Figure 2.9. Switches with common source inductance (shown for high-side switch only) 25                       |

| Figure 2.10. Example of the high-side switch waveforms during turn-off with Miller plateau                    |

| Figure 2.11. Asynchronous buck converter's diode current and voltage waveforms for (a) a full period,         |

| 27 -                                                                                                          |

| Figure 2.12. Synchronous buck converter current waveforms for the inductor, the high-side switch, and th      |

| low-side switch [24] 28                                                                                       |

| Figure 2.13. Synchronous buck converter waveforms, inductor current, high-side gate-source voltage, low       |

| side gate-source voltage, and diode current [24].                                                             |

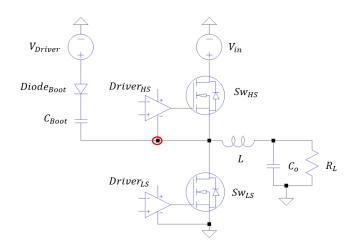

| Figure 3.1. Simplified 2-level buck converter, with drivers and bootstrap diode and capacitor                 |

| Figure 3.2. Simplified 3-level buck converter, with drivers and cascaded bootstrap diodes and capacitors.     |

| 31 -                                                                                                          |

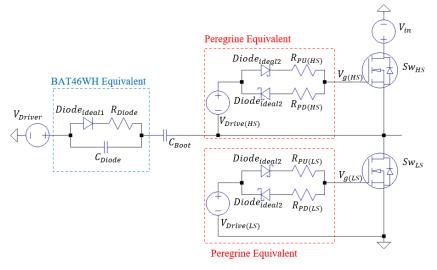

| Figure 3.3. Lumped circuit models for bootstrap capacitor, its BAT46WH diode, and Peregrine drivers           |

| 32 -<br>Fi 2.4 J F F F F F F F F F F F F F F F F F F                                                          |

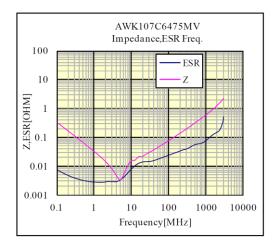

| Figure 3.4. Impedance vs. Frequency for AWK107C6475MV capacitor                                               |

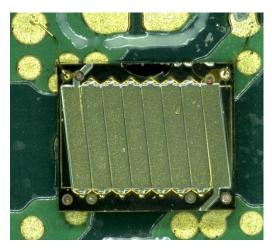

| Figure 3.5. Tyndall's "MagPwr" thin-film inductor.                                                            |

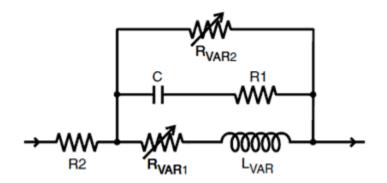

| Figure 3.6. The LTSpice inductor model for the PFL1005. From Coilcraft                                        |

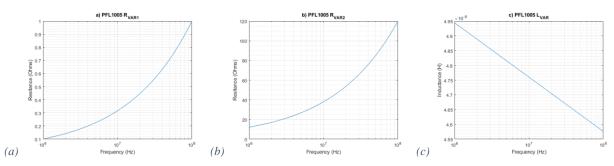

| Figure 3.7. The variable component values for the PFL1005-36N and logarithmic frequency (a) $R_{VAR1}$ , (b)  |

| $R_{VAR2}$ , and (c) $L_{VAR}$                                                                                |

| Figure 3.8. LTSpice model for SRP2510A-R22M inductor. From Bourns                                             |

| Figure 3.9. LQW18CN55NJ00# equivalent circuit diagram. From Murata                                            |

| Figure 3.10. MLF2012 inductor series equivalent circuit diagram. From TDK                                     |

| Figure 3.11.Lumped circuit model for MagPwr and air-core inductors                                            |

| Figure 3.12. 50 nH air-core inductor                                                                          |

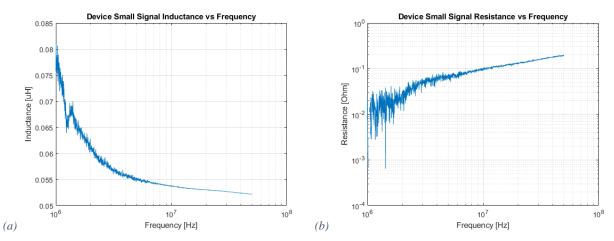

| Figure 3.13. The air-core inductor's (a) inductance and (b) resistance response to frequency (logarithmi      |

| scale) 39                                                                                                     |

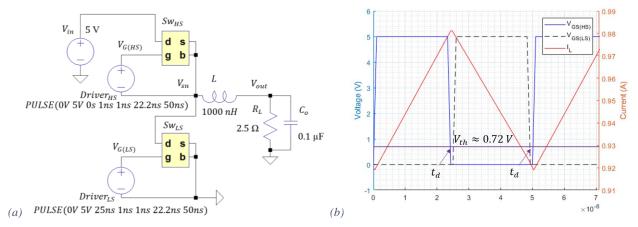

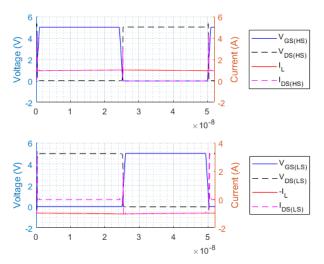

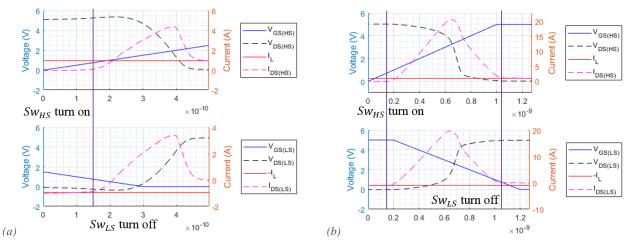

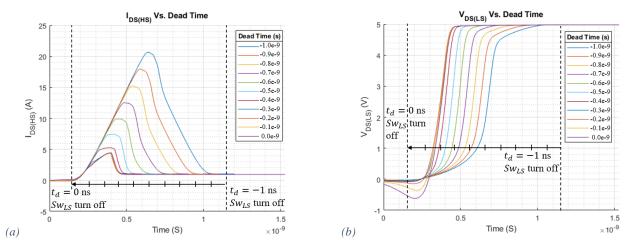

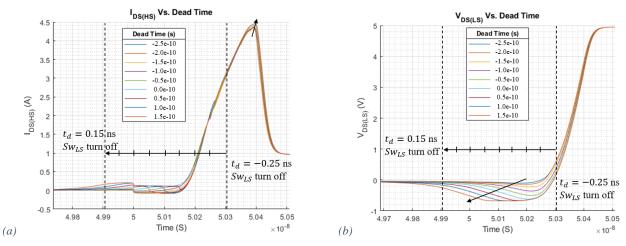

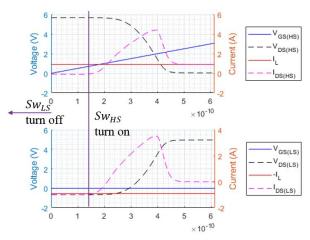

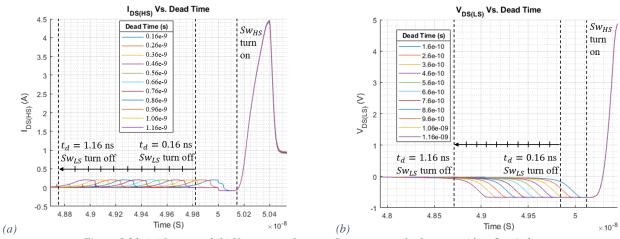

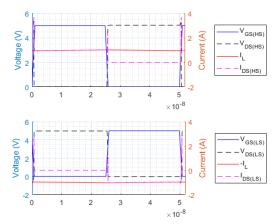

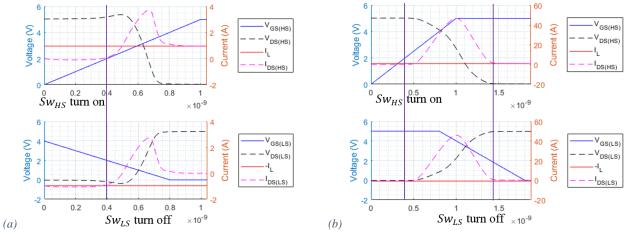

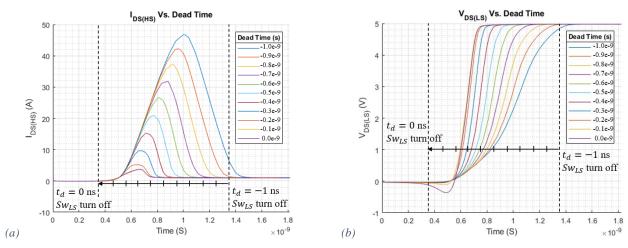

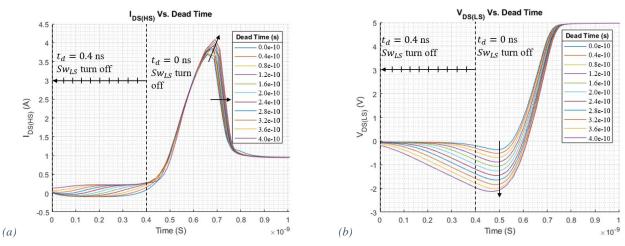

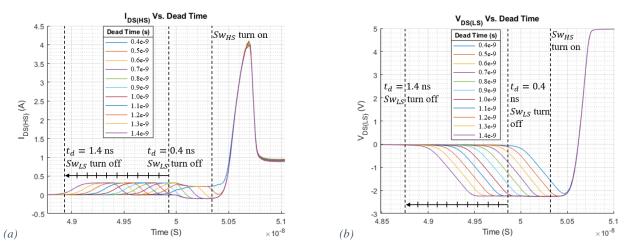

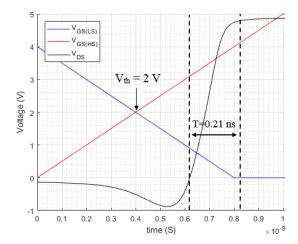

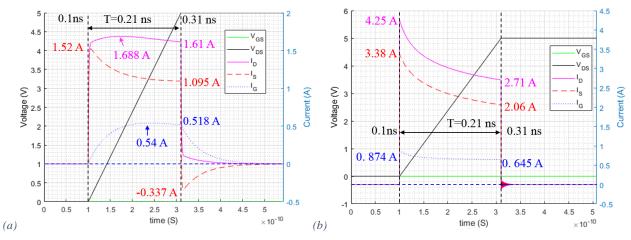

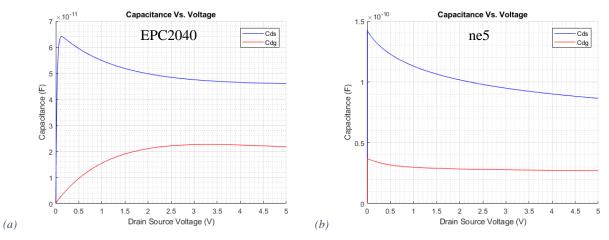

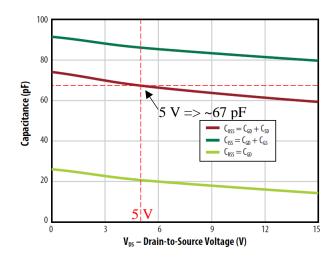

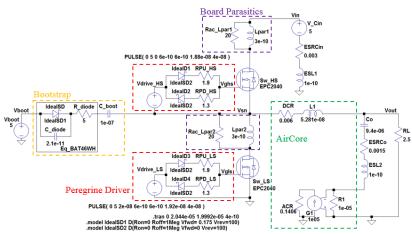

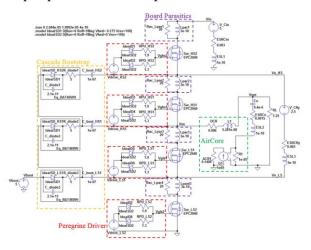

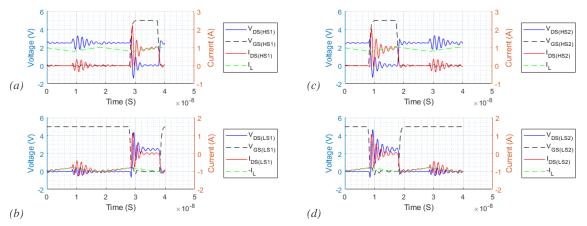

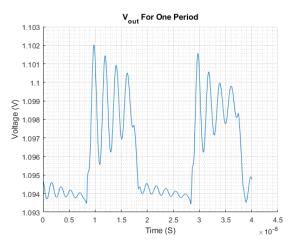

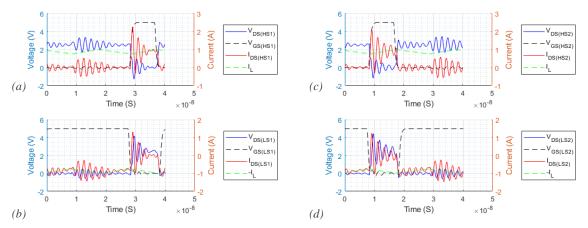

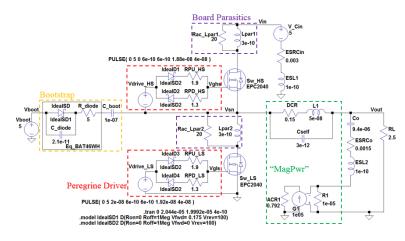

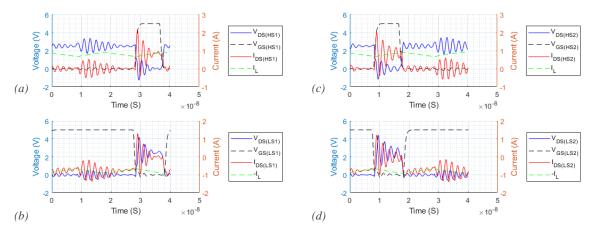

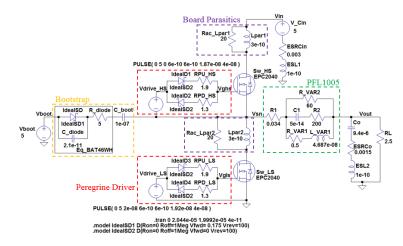

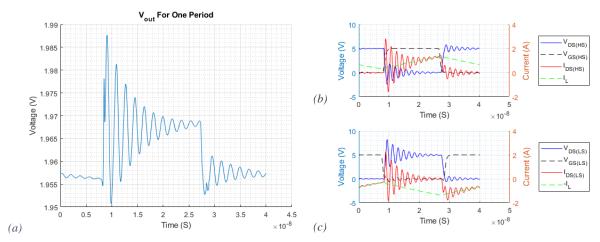

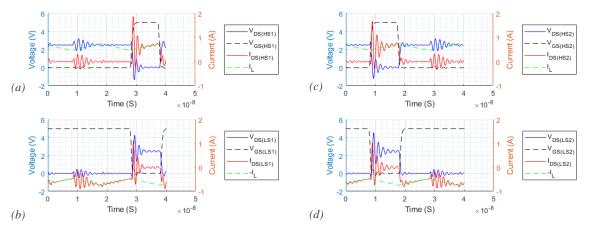

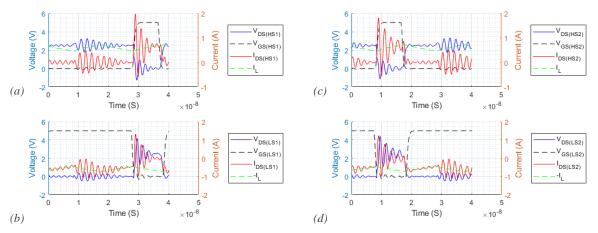

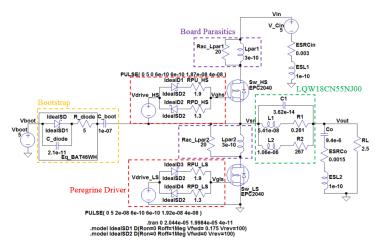

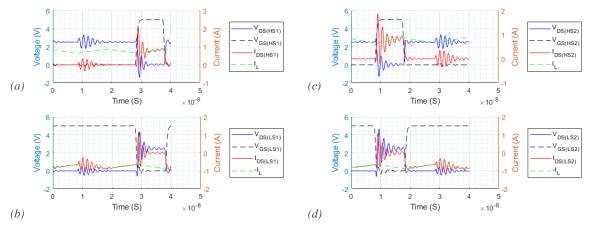

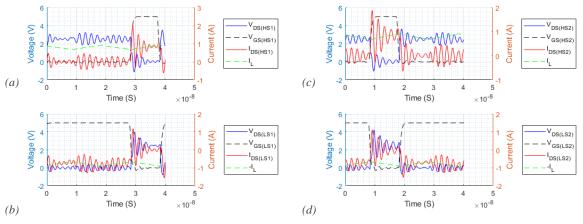

Figure 3.14. (a) Circuit diagram, and (b) inductor current and gate voltages, when  $t_d = 1$  ns with ne5 switches..... - 40 -Figure 3.16. The ne5 switch waveforms when (a)  $t_d = 0$  ns, and (b)  $t_d = -1$  ns, at Sw<sub>HS</sub> turn-on........... - 41 -Figure 3.17. (a)  $I_{DS(HS)}$  and (b)  $V_{DS(LS)}$  waveforms, at Sw<sub>HS</sub> turn-on, for negative t<sub>d</sub> with ne5 switches. - 42 -Figure 3.18. The ne5 switch waveforms when (a)  $t_d = -0.25$  ns, and (b)  $t_d = 0.15$  ns, at Sw<sub>HS</sub> turn-on. - 42 -Figure 3.19. (a)  $I_{DS(HS)}$  and (b)  $V_{DS(LS)}$  waveforms, at SW<sub>HS</sub> turn-on, for small t<sub>d</sub> with ne5 switches. ... - 43 -Figure 3.21. (a)  $I_{DS(HS)}$  and (b)  $V_{DS(LS)}$  waveforms at Sw<sub>HS</sub> turn-on, for large t<sub>d</sub> with ne5 switches...... - 44 -Figure 3.22. The (a) circuit Diagram, and (b) inductor current and gate voltages, when  $t_d = 1$  ns, with Figure 3.24. The EPC2040 switch waveforms when (a)  $t_d = 0$  ns, and (b)  $t_d = -1$  ns, at Sw<sub>HS</sub> turn-on. - 45 -Figure 3.25. (a)  $I_{DS(HS)}$  and (b)  $V_{DS(LS)}$  waveforms, at SW<sub>HS</sub> turn-on, for negative t<sub>d</sub> with EPC2040 switches. - 46 -Figure 3.26. The EPC 2040 switch waveforms when  $t_d = 0.4$  ns, at Sw<sub>HS</sub> turn-on...... - 46 -Figure 3.27. (a)  $I_{DS(HS)}$  and (b)  $V_{DS(LS)}$  waveforms, at SW<sub>HS</sub> turn-on, for small t<sub>d</sub> with EPC2040 switches...-47 -Figure 3.29. (a) I<sub>DS(HS)</sub> and (b) V<sub>DS(LS)</sub> waveforms, at Sw<sub>HS</sub> turn-on, for large t<sub>d</sub> with EPC2040 switches. ...-48 -Figure 3.30. Sw<sub>HS</sub> and Sw<sub>LS</sub> waveforms, td = 0.6 ns and with EPC2040 switches at Sw<sub>HS</sub> turn on..... - 49 -Figure 3.32. Circuit diagram for testing the equivalent energy capacitances for, (a) EPC2040 and (b) ne5 switches..... - 51 -Figure 3.34. Current and Voltage Waveforms for (a) EPC2040 and (b) ne5, for equivalent energy capacitance determination..... - 52 -Figure 3.35. Cdg (blue) and Cds (red) vs. VDS, for (a) the EPC2040 switch and (b) the ne5 switch. ..... - 52 -Figure 3.36. EPC2040 small signal capacitances vs. V<sub>DS</sub>, from datasheet ...... - 54 -Figure 3.37. Full circuit diagram for the 2-Level buck converter, with the air-core inductor, and EPC2040 or ne5 switches..... - 55 -Figure 3.38. (a)  $V_{out}$ , (b)  $Sw_{HS}$  and (c)  $Sw_{LS}$  waveforms, for the 2-level buck converter, at  $f_{sw} = 25$  MHz,  $I_{out}$ Figure 3.39. (a)  $V_{out}$ , (b)  $Sw_{HS}$ , and, (c)  $Sw_{LS}$  waveforms, for the 2-level buck converter, at  $f_{sw} = 25$  MHz, I<sub>out</sub> = 1 A..... - 56 -Figure 3.40. Full circuit diagram for the 3-Level buck converter, with the air-core inductor, and EPC2040 or ne5 switches..... - 57 -Figure 3.42. (a) Sw<sub>HS1</sub>, (b) Sw<sub>LS1</sub>, (c) Sw<sub>HS2</sub>, and (d) Sw<sub>LS2</sub> waveforms, for the 3-level buck converter, - 58 Figure 3.44. (a) Sw<sub>HS1</sub>, (b) Sw<sub>LS1</sub>, (c) Sw<sub>HS2</sub>, and (d) Sw<sub>LS2</sub> waveforms, for the 3-level buck converter, 59 Figure 3.45. Full circuit diagram for the 2-Level buck converter, with the MagPwr inductor, and EPC2040 or ne5 switches..... - 59 -

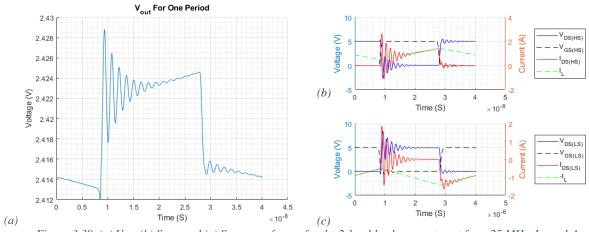

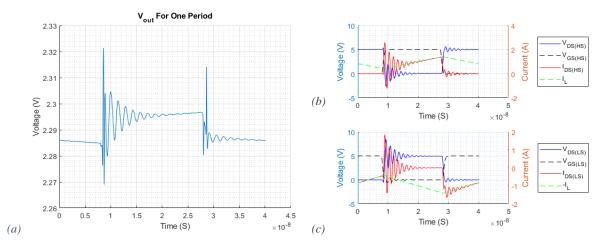

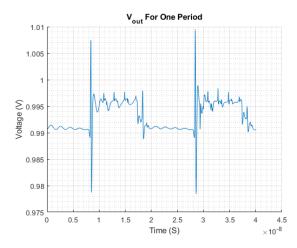

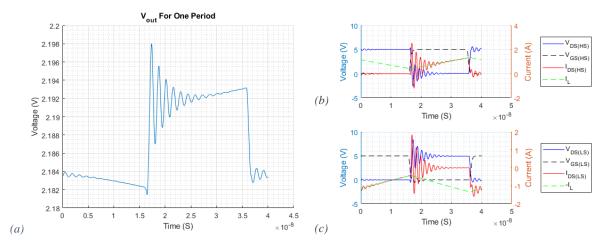

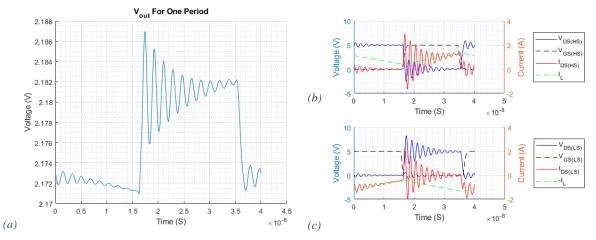

| Figure 3.46. (a) $V_{out}$ , (b) $Sw_{HS}$ and (c) $Sw_{LS}$ waveforms, for the 2-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A.                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.47. (a) $V_{out}$ , (b) $Sw_{HS}$ and (c) $Sw_{LS}$ waveforms, for the 2-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                   |

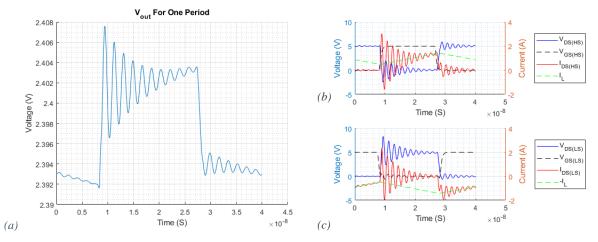

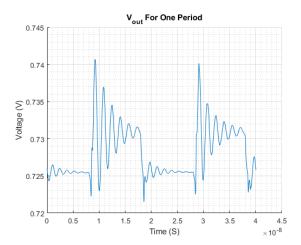

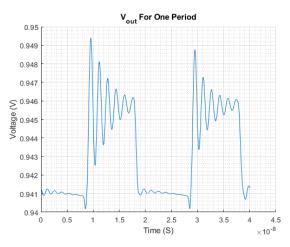

| Figure 3.48. $V_{out}$ waveform, for the 3-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                                                          |

| Figure 3.50. $V_{out}$ waveform, for the 3-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                                                          |

| Figure 3.52. Full circuit diagram for the 2-Level buck converter, with the PFL1005 inductor, and EPC2040 or ne5 switches                                                                                                                        |

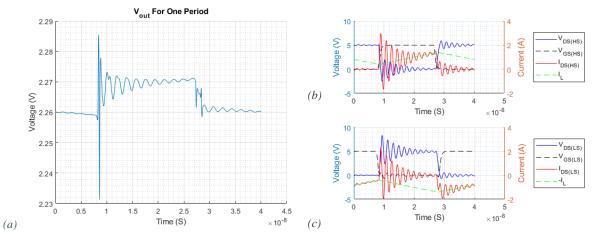

| Figure 3.53. (a) $V_{out}$ , (b) $Sw_{HS}$ , and (c) $Sw_{LS}$ waveforms, for the 2-level buck converter, at $f_{sw} = 25$ MHz,<br>$I_{out} = 1$ A                                                                                              |

| Figure 3.54. (a) $V_{out}$ , (b) $Sw_{HS}$ and, (c) $Sw_{LS}$ waveforms, for the 2-level buck converter, at $f_{sw} = 25$ MHz,<br>$I_{out} = 1$ A                                                                                               |

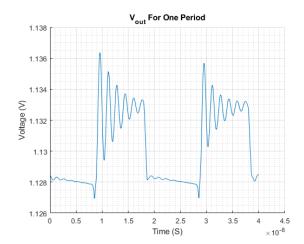

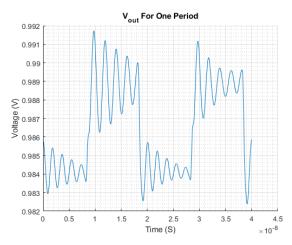

| Figure 3.55. $V_{out}$ waveform, for the 3-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                                                          |

| Figure 3.57. The V <sub>out</sub> waveform, for 3-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                                                   |

| Figure 3.59. Full circuit diagram for the 2-Level buck converter, with the LQW18CN55NJ00 inductor, and EPC2040 or ne 5 switches                                                                                                                 |

| Figure 3.60. (a) $V_{out}$ , (b) $Sw_{HS}$ and, (c) $Sw_{LS}$ waveforms, for the 2-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                  |

| Figure 3.61. (a) $V_{out}$ , (b) $Sw_{HS}$ and, (c) $Sw_{LS}$ waveforms, for 2-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                      |

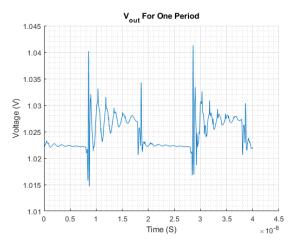

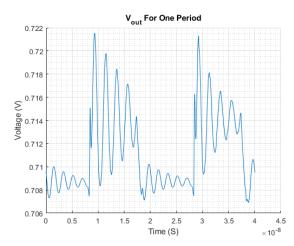

| Figure 3.62. $V_{out}$ waveform, for 3-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                                                              |

| Figure 3.64. $V_{out}$ waveform, for 3-level buck converter, at $f_{sw} = 25$ MHz, $I_{out} = 1$ A                                                                                                                                              |

| Figure 3.65. (a) Sw <sub>HS1</sub> , (b) Sw <sub>LS1</sub> , (c) SwHS2, and (d) SwLS2 waveforms, for 3-level buck converter, -69 -<br>Figure 3.66. The switch waveforms for the 2-level buck converter with a PFL inductor and EPC2040 switches |

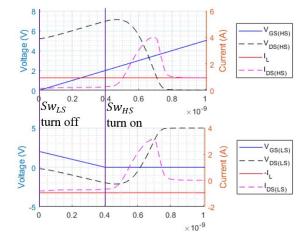

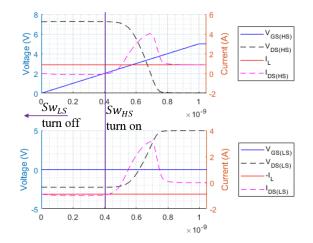

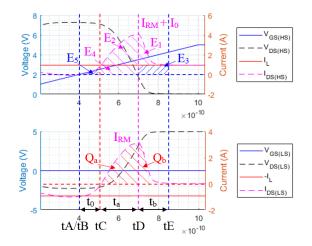

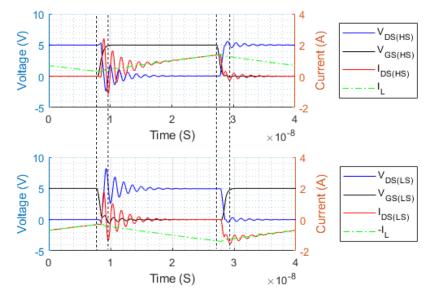

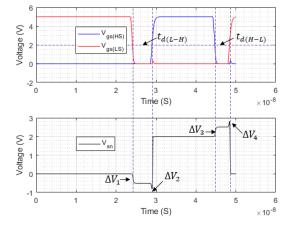

| Figure 3.67. SwLS turn-off and SwHS turn-on waveforms.                                                                                                                                                                                          |

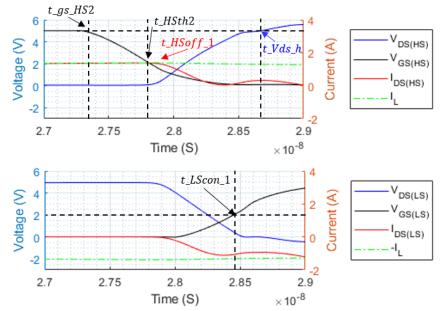

| Figure 3.68. <i>SwHS</i> turn-off and <i>SwLS</i> turn-on waveforms                                                                                                                                                                             |

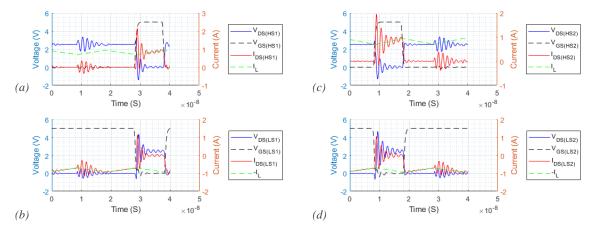

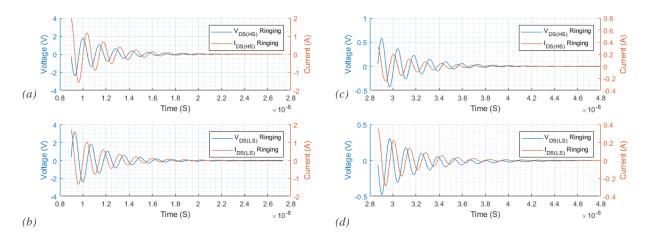

| Figure 3.69. The current and voltage ringing waveforms (a) for $Sw_{HS}$ after $Sw_{HS}$ turns on (b) for $Sw_{LS}$ after $Sw_{HS}$ turns on, (c) for $Sw_{HS}$ after $Sw_{HS}$ turns off, and (d) for $Sw_{LS}$ after $Sw_{HS}$ turns off      |

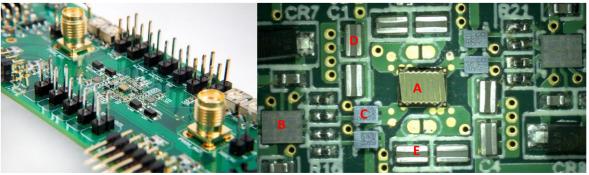

| Figure 4.1. Tyndall's "MagPwr", EPC1 MS2 buck converter circuit board                                                                                                                                                                           |

| Figure 4.2. Circuit board set-up for later "full-converter" measurements                                                                                                                                                                        |

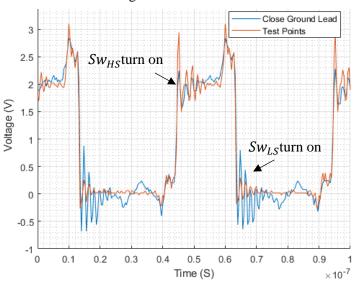

| Figure 4.3. V <sub>sn</sub> , measured with FET Input Probe at Test Point and Passive Probe with Close Ground Lead.                                                                                                                             |

| EPC1 MS2 buck converter board, open switch-node 77 -                                                                                                                                                                                            |

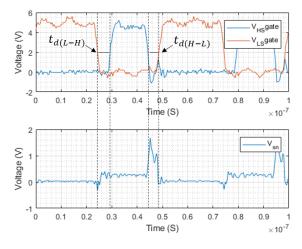

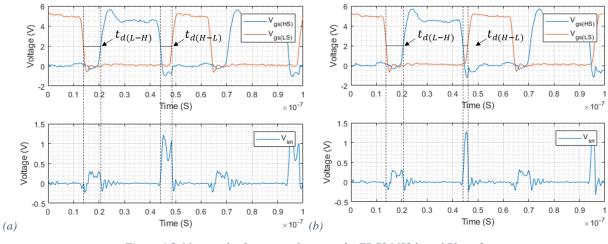

| Figure 4.4. Measured voltage waveforms on the EPC1 MS2 board Phase 1, with $td(L - H) \approx 4.9$ ns and                                                                                                                                       |

| $td(H - L) \approx 3.6$ ns                                                                                                                                                                                                                      |

| Figure 4.5. Measured voltage waveforms on the EPC5 MS2 board Phase 2                                                                                                                                                                            |

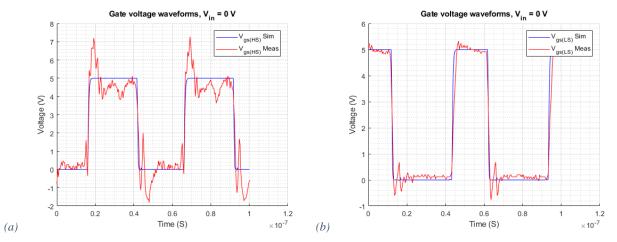

| Figure 4.7. (a) $V_{g_{S(HS)}}$ simulated and measured waveforms. (b) $V_{g_{S(LS)}}$ simulated and measured waveforms 81 -                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

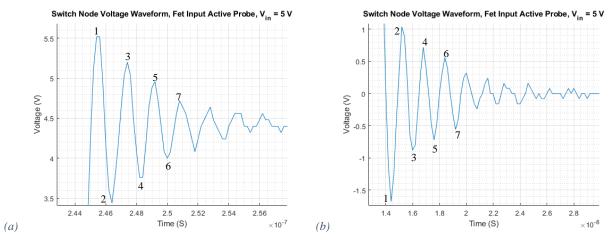

| Figure 4.8. Close up look at $V_{sn}$ ripple, for $V_{in} = 5$ V, open switch-node, EPC1 board                                                                                                                                      |

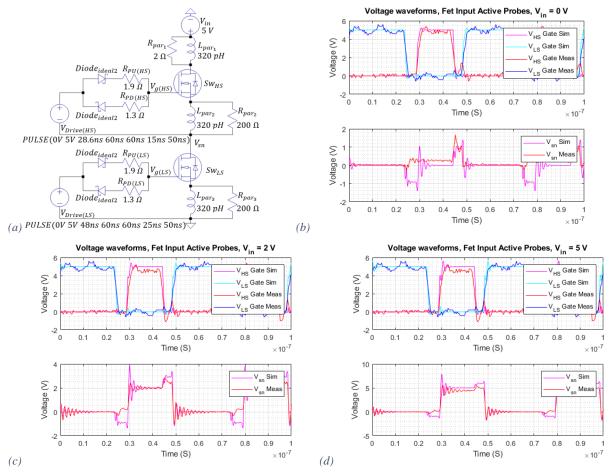

| Figure 4.9. (a) Simulations circuit diagram for comparison with measured results                                                                                                                                                    |

| Figure 4.10. $V_{gs(HS)}$ , $V_{gs(LS)}$ and $V_{sn}$ waveforms over one period, operated at $fsw = 20$ MHz and $Vin = 2$                                                                                                           |

| $V_{\text{subs}} = 85 - 85$                                                                                                                                                                                                         |

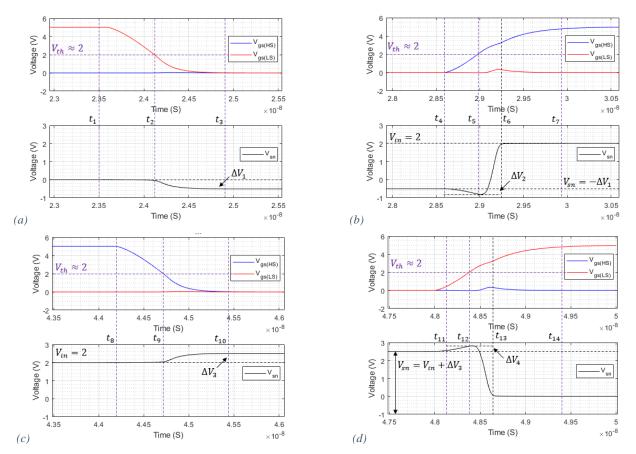

| Figure 4.11. Close up views of the simulated open-circuit switch-node voltage waveforms operated at $f_s =$                                                                                                                         |

| $20 \text{ MHz}$ and $V_{in} = 2 V$ ,                                                                                                                                                                                               |

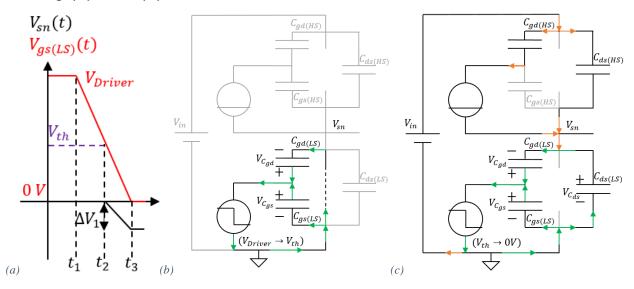

| Figure 4.12. (a) The voltage waveforms. The switch capacitances and currents between (b) $t1 - t2$ , and (c)                                                                                                                        |

| t2 - t3                                                                                                                                                                                                                             |

| Figure 4.13. (a) The voltage waveforms. The switch capacitances and currents between (b) $t4 - t5$ , and (c)                                                                                                                        |

| <i>t</i> 5 – <i>t</i> 6 87 -                                                                                                                                                                                                        |

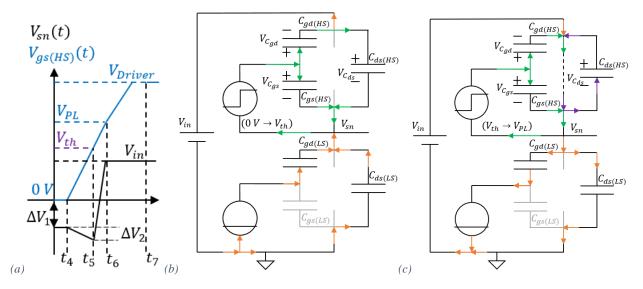

| Figure 4.14(a) The voltage waveforms. The switch capacitances and currents between (b) $t8 - t9$ , and (c)                                                                                                                          |

| <i>t</i> 9 – <i>t</i> 10 88 –                                                                                                                                                                                                       |

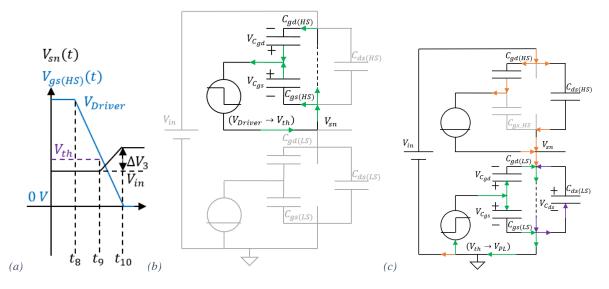

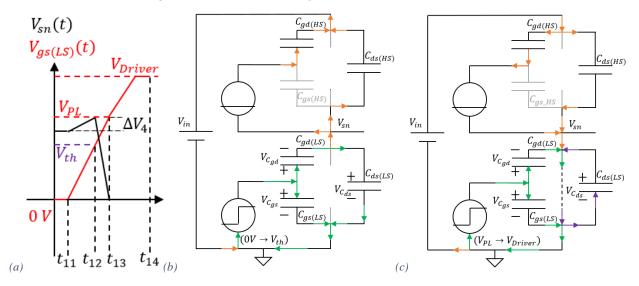

| Figure 4.15(a) The voltage waveforms. The switch capacitances and currents between (b) $t11 - t12$ , and                                                                                                                            |

| (c)t12 - t13                                                                                                                                                                                                                        |

| Figure 4.16. The circuit diagram for $C_{iss(ER)}$ test. The test conditions are $V_{DS} = 6 \text{ V}$ , $I_D = 1.5 \text{ A}$ and $V_{GS} = 0$                                                                                    |

| to 5 V                                                                                                                                                                                                                              |

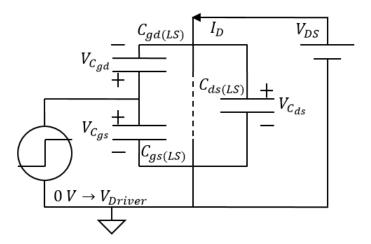

| Figure 4.17. LTSpice circuit diagram for open-circuit switch-node, $V_{in} = 0$ V, $V_{Driver} = 5$ V, and $f_{sw} = 20$                                                                                                            |

| MHz                                                                                                                                                                                                                                 |

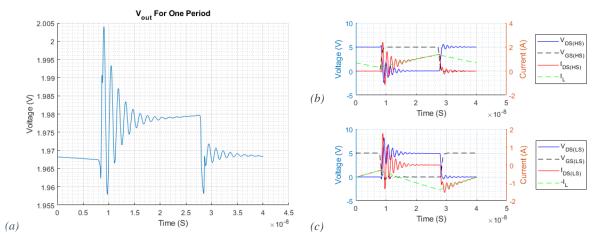

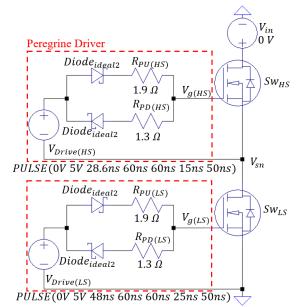

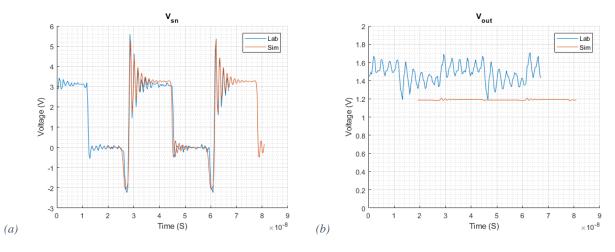

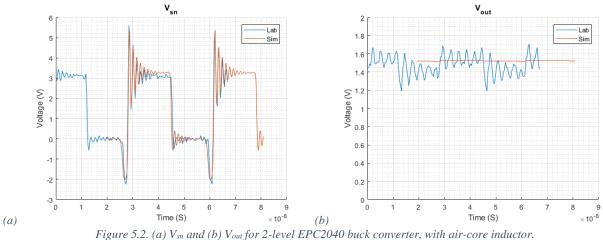

| Figure 5.1. (a) Vsn and (b) Vout for 2-level EPC2040 buck converter, with PFL1005 Coilcraft inductor                                                                                                                                |

| chip                                                                                                                                                                                                                                |

| Figure 5.2. (a) $V_{sn}$ and (b) $V_{out}$ for 2-level EPC2040 buck converter, with air-core inductor                                                                                                                               |

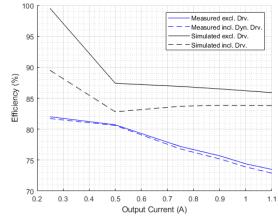

| Figure 5.2. (a) $v_{sh}$ and (b) $v_{oh}$ for 2 hover E1 C2040 bleck converter, with an core inductor matter $y_{f}$<br>Figure 5.3. Comparison of measured and simulated efficiencies for air-core inductor, $f_{sw} = 30$ MHz 98 - |

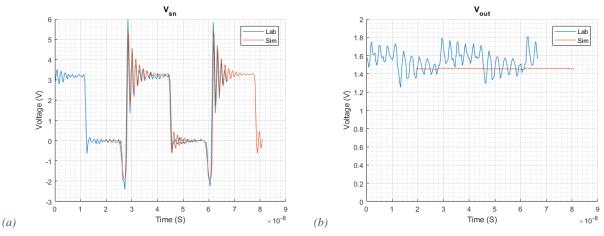

| Figure 5.4. (a) $V_{sn}$ and (b) $V_{out}$ for 2-level EPC2040 buck converter, with "MagPwr" inductor                                                                                                                               |

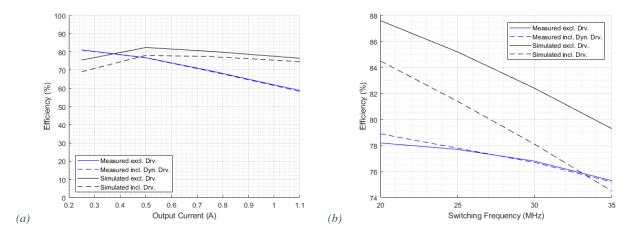

| Figure 5.5. Comparison of measured and simulated efficiencies for MagPwr inductor, $V_{in} = 3.3 V_{} - 100 -$                                                                                                                      |

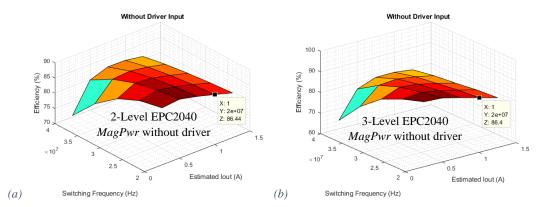

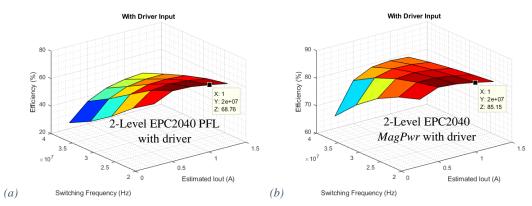

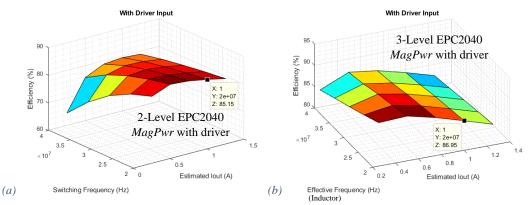

| Figure 5.5. Comparison of measured and simulated efficiencies for Wag1 withductor, $v_{in} = 5.5 v_{} = 100 e^{-1}$<br>Figure 6.1.The efficiencies of (a) the2-Level converter (D = 0.41) and (b) the3-Level converter (D = 0.42),  |

| -103 -                                                                                                                                                                                                                              |

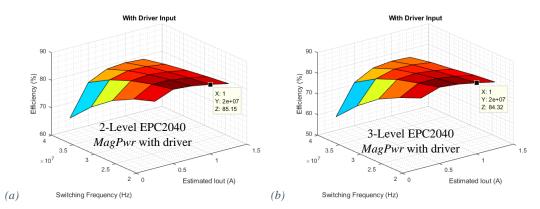

| Figure 6.2. The efficiencies of (a) the 2-Level converter ( $D = 0.415$ ) and (b) the 3-Level converter ( $D = 0.415$ )                                                                                                             |

| 0.425),                                                                                                                                                                                                                             |

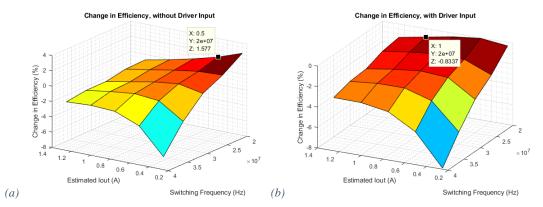

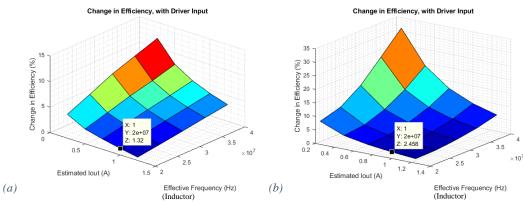

| Figure 6.3. Change in efficiency for the MagPwr inductor with the EPC2040 switches, from 2-level to 3-                                                                                                                              |

| level converter,                                                                                                                                                                                                                    |

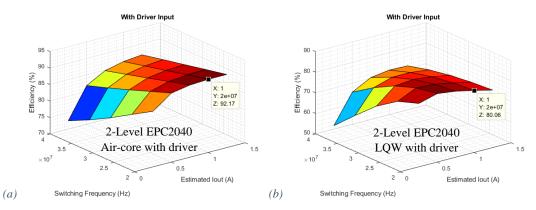

| Figure 6.4. The efficiencies of the 2-Level converter with the EPC2040 switches for various I <sub>out</sub> and f <sub>sw</sub> ,                                                                                                  |

| 104 -                                                                                                                                                                                                                               |

| Figure 6.5. The efficiencies of the 2-Level converter with the EPC2040 switches for various I <sub>out</sub> and f <sub>sw</sub> ,                                                                                                  |

| 105 -                                                                                                                                                                                                                               |

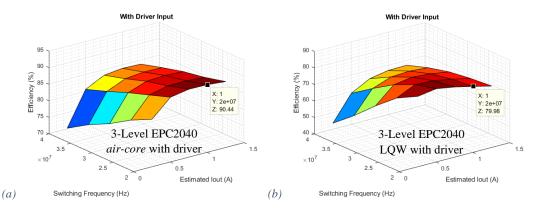

| Figure 6.6. The efficiencies of the 3-Level converter with the EPC2040 switches for various $I_{out}$ and $f_{sw}$ ,                                                                                                                |

| 105 -                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                     |

| Figure 6.7. The efficiencies of the 3-Level converter with the EPC2040 switches for various $I_{out}$ and $f_{sw}$ ,                                                                                                                |

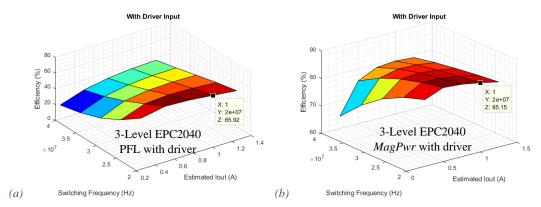

| 106 -<br>Figure 6.8. The officiancies of the 2.1 evel convertor with the MacDum inductor for verious 1 and f                                                                                                                        |

| Figure 6.8. The efficiencies of the 2-Level converter with the MagPwr inductor for various $I_{out}$ and $f_{sw}$ ,<br>106 -                                                                                                        |

|                                                                                                                                                                                                                                     |

| Figure 6.9. The efficiencies of the 3-Level converter with the MagPwr inductor for various $I_{out}$ and $f_{sw}$ ,<br>107 -                                                                                                        |

|                                                                                                                                                                                                                                     |

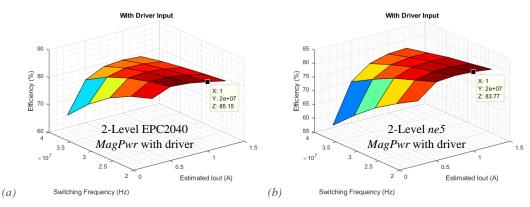

| Figure 6.10. The efficiencies of (a) the 2-Level converter ( $D = 0.38$ ) and (b) the 3-Level Converter ( $D = 0.30$ )                                                                                                              |

| 0.39), 107 -                                                                                                                                                                                                                        |

| Figure 6.11. The efficiencies of (a) the 2-Level converter ( $D = 0.38$ ) and (b) the 3-Level Converter ( $D = 0.39$ ),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.12. The efficiencies of (a) the 2-Level converter ( $D = 0.435$ ) and (b) the 3-Level Converter ( $D = 0.50$ ),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 6.13. The efficiencies of (a) the 2-Level converter ( $D = 0.41$ ) and (b) the 3-Level Converter ( $D = 0.42$ ),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

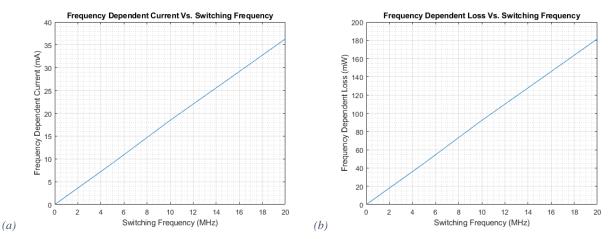

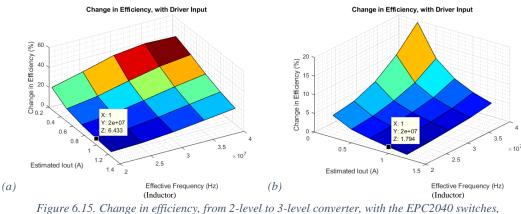

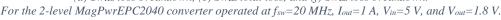

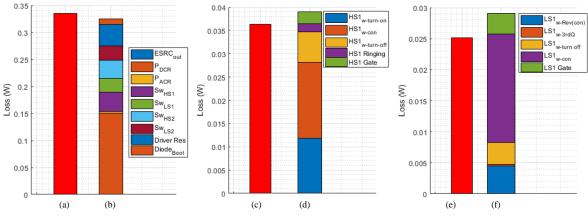

| Figure 6.14. Change in efficiency, from 2-level to 3-level converter, with the EPC2040 switches, 109 - Figure 6.15. Change in efficiency, from 2-level to 3-level converter, with the EPC2040 switches, 109 - Figure 6.16. (a) The total converter loss, (b) the converter loss breakdown, (c) $Sw_{HS}$ total loss, 110 - Figure 6.17. (a) The total converter loss, (b) the converter loss breakdown, (c) $Sw_{HS1}$ total loss, 110 - Figure 6.17. (a) The total converter loss, (b) the converter loss breakdown, (c) $Sw_{HS1}$ total loss, 110 - Figure 6.17. (a) The total converter loss, (b) the converter loss breakdown, (c) $Sw_{HS1}$ total loss, 110 - Figure 6.17. (a) The total converter loss, (b) the converter loss breakdown, (c) $Sw_{HS1}$ total loss, 110 - Figure 6.17. (a) The total converter loss, (b) the converter loss breakdown, (c) $Sw_{HS1}$ total loss, |

## Abstract

This thesis compares 2-level and 3-level buck converters, for use in very high frequency Point-of-Load (POL) DC-DC conversion. The nominal conversion is from 5 V to 1.8 V, at a 1 A output current, as is appropriate for use in a battery powered device. Today's typical commercial POL solution for this challenge employs a monolithic CMOS power switcher operating at 2-3 MHz and uses a discrete surface mountable (SMT) ferrite chip inductor. This work investigates the performance achievable over the 20-40 MHz range with the use of a new specially designed and fabricated Tyndall thin-film magnetics-on-silicon (tf-MoS) inductor component.

Two different power switching bridge types, CMOS and GaN, are investigated by both analytic loss modelling and by SPICE simulation. The CMOS bridge assumes a PMOS and NMOS combination using device models from a 180 nm CMOS process and the GaN bridge is based on commercially available discrete enhancement mode GaN HEMT switches. A behavioural model for a state-of-the-art commercial driver is developed. Measurements are initially made on a prototype 2-level GaN bridge circuit with open-circuit switch-node to allow for determination of load independent silicon losses. These measurements are used to validate both the switch with driver models and the circuit loss analyses.

Inductor loss is one of the key practical limitations towards achieving very high frequency switching. Both modelling and measurement techniques are used to investigate the performance of the custom thin-film inductor. An ultimate reference case, low-loss air-core inductor was wound and used to measure the lowest achievable complete converter loss over the 20-40 MHz range. Two SMT ferrite chip inductor options were selected based on datasheets review and fitted in the prototype to achieve the best performance with currently available commercial components. These three inductors and a new custom Tyndall thin film inductor are all simulated and tested in combination with the 2-level GaN switching bridge.

The measured overall efficiencies with loss breakdowns are presented for the various combinations of switch components and inductor technologies in 2-level converter. These measurements validate the models and simulations so that simulations for an extension to the 3-level converter and its performance comparison versus the 2-level converter may be made.

# 1. Introduction

## 1.1 Introduction to Buck Converters

In this thesis, Point-of-Load (POL) voltage regulation, using the DC-DC buck (step-down) converter is investigated. The focus is on the low power, mobile application. The battery voltage will vary, depending on factors such as state-of-charge, temperature, and load current, whereas the components being powered (for instance the CPU or transceivers), will be designed for a specific well-regulated input voltage. The POL converter provides the tightly regulated voltage with the high bandwidth necessary to support a rapidly changing load. For such a converter, in mobile applications, it is highly desirable to reduce the size, height and weight of the components involved. This thesis investigates the possibility of increasing the switching frequency (or effective switching frequency) to reduce size of the passive components (inductor and capacitors). The implication of the increased switching frequency and smaller passive component sizes and values on converter efficiency is considered.

The multi-level topology [10] multiplies the effective switching frequency of the inductor (for given switch frequency), reduces the voltages across the transistors and reduces the applied inductor volt-seconds. The multi-level technique can be utilised to reduce the inductor value or to increase efficiency. The drawback of the multi-level topology is that it adds additional switches, drivers, control complexity and capacitors to the circuit. This thesis compares the 2-level buck converter with a 3-level version of a multi-level buck converter.

The inductor filters the switch-node voltage and delivers smooth current into the output. Typically, the inductor is the largest component in the converter and hence this thesis focuses on all factors which influence its size. A larger inductance provides lower current ripple but at the expense of larger sizes because inductor volume is proportional to inductance value. The inductance value influences the operating mode of the converter and for instance; its value may be chosen to allow its current to go slightly negative (boundary conduction mode, BCM) before the high-side switch turn-on to create zero voltage switching (ZVS) on the high side switch. This thesis will also examine the inductor losses and size for a variety of inductor device formats and materials.

By increasing the switching frequency, a smaller inductor can be used to achieve the same amount of output ripple. This increases the losses in the switches, and switches that are capable of very high switching frequencies will generally handle lower voltages. The choice of switches is very important to achieve high efficiency at high frequency. High frequency allows lower switching ripple and small component sizes, for inductors and capacitors.

The switch, inductor, and topology trade-offs are explored by simulation and experiment for 2-level and 3-level buck converters in the 20-40 MHz range.

This chapter provides an overview of how the 2-level and 3-level buck converters operate. The challenges of operating inductors and switches at high switching frequencies and the loss mechanisms with each are also explored.

## 1.2 Step Down Converter Topologies

For step-down DC-DC voltage conversion there are several popular topologies, with their own benefits and drawbacks. Voltage dividers or linear regulators are simple but by their very nature their efficiencies are dictated by conversion ratio. Converters such as the forward or flyback which use transformers may be unnecessarily bulky for low power applications, they are better suited for higher voltages or when isolation is required. Switched-Capacitor (SC) converters can have very small footprints while delivering very high

efficiency at a fixed conversion ratio. The SC and buck converters may be merged to create a hybrid converter which boast smaller footprint and high efficiency with dynamic voltage regulation. SC converters and their hybrids work best at lower powers and with larger step-down ratios.

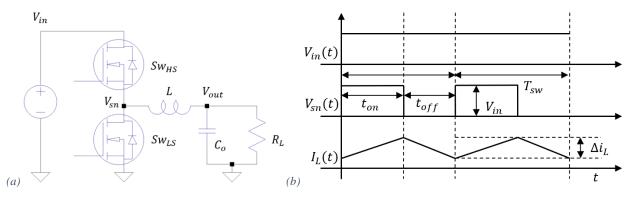

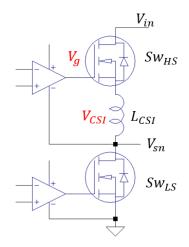

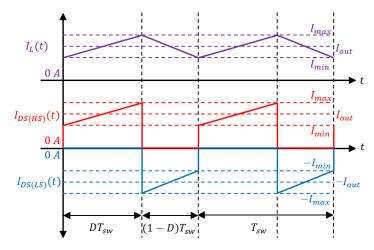

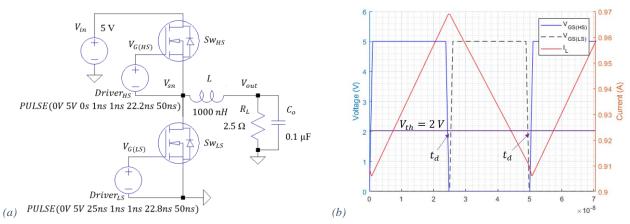

#### 1.2.1 Buck Converter

The ideal topology diagram for the basic (2-level) synchronous buck converter is shown in Figure 1.1(a). The core concept behind the buck converter, is that two switches are used to chop a DC voltage into a pulsed waveform with smaller average voltage than the input DC voltage. The high-side switch is referred to as  $Sw_{HS}$  and the low-side switch as  $Sw_{LS}$ . When one switch is on the other is always off, to avoid short-circuiting or "shoot-through". When  $Sw_{HS}$  is on  $V_{sn} = V_{in}$ , and when  $Sw_{LS}$  is on  $V_{sn} = 0$  V. Thus, the pulse width is  $Sw_{HS}$  on-time  $(t_{on})$  and the pulse goes from ground to  $V_{in}$ . The ratio of  $t_{on}$  and the switching period  $(T_{sw})$ , is referred to as the duty cycle  $(D = t_{on}/T_{sw})$ . This pulse is then applied to an LC filter to create a smooth DC output voltage, with low ripple. In a lossless converter, the output voltage  $(V_{out})$  is:

$$V_{out} = DV_{in}.$$

(1.1)

When  $Sw_{HS}$  is on the inductor (L) sees a positive voltage ( $V_L = V_{in} - V_{out}$ ), hence it has a positive current ramp. When  $Sw_{HS}$  is off, the inductor sees a negative voltage ( $V_L = -V_{out}$ ), and discharges through  $Sw_{LS}$  and the output. The converters in this thesis are operated with mostly positive inductor current. For the synchronous buck converter, the inductor current may be positive or negative during continuous conduction mode (CCM). The output capacitor ( $C_o$ ) absorbs AC inductor current ripple and provides steady output voltage.

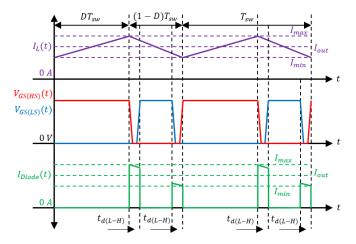

Figure 1.1. Ideal buck converter: (a) circuit diagram, (b) input voltage, switch-node voltage, and inductor current waveforms.

For (CCM) the equations used to determine the minimum output capacitance  $(C_{min})$  and the minimum inductance  $(L_{min})$  required are:

$$C_{min} > \frac{\Delta i_L}{8*f_{sw}*\Delta v_{out}} \tag{1.2}$$

and

$$L_{min} > \frac{V_{out}(1 - D_{min})}{f_{sw} * \Delta i_{L(max)}}$$

(1.3)

where  $\Delta i_L$  is the inductor current ripple;  $\Delta v_{out}$  is the output voltage ripple;  $D_{min}$  is the minimum duty cycle (maximum possible input voltage); and  $\Delta i_{L(max)}$  is the maximum ripple current (maximum possible input voltage). The capacitance and inductance are both inversely proportional to the switching frequency. Typically, the larger the capacitance and the larger the inductance the larger the physical sizes of the

capacitor and inductor required. Increasing switching frequency, can be used to decrease inductors and capacitors size, but their losses may increase. Reducing the sizes of the switches will reduce their parasitic capacitances but will cause greater on-resistances and hence large conduction losses.

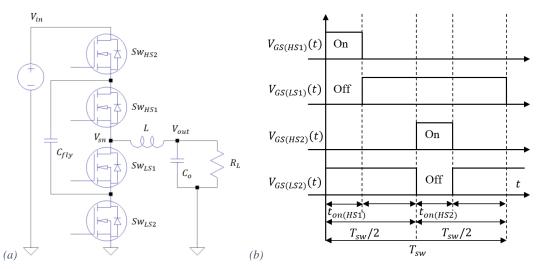

#### 1.2.2 3-Level Buck Converter

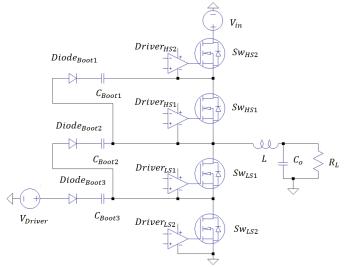

The circuit diagram for the 3-level buck converter is shown in Figure 1.2(a). The 3-level has a similar structure to the 2-level buck converter, with the addition of two more switches and a flying capacitor ( $C_{fly}$ ). The flying capacitor voltage ( $V_{C_{fly}}$ ) is charged to nominally  $V_{in}/2$ .

The switching waveforms for the 3-level topology are shown in Figure 1.2(b). This topology has three possible switch-node voltage levels:  $V_{in}$ ,  $V_{in}/2$ , and ground. By managing these at the switch-node, this allows for an output voltage range from ground to  $V_{in}$ . The operation mode in this thesis is for  $0 < V_{out} < V_{in}/2$ . Each period can be broken into four stages.

Stage 1:  $Sw_{HS1}$  and  $Sw_{LS2}$  are on. The inductor voltage is positive ( $V_L = V_{C_{fly}} - V_{out}$ ). Note  $C_{fly}$  is applied at the switch-node to charge the inductor. This stage's duration is determined by  $Sw_{HS1}$  on-time ( $t_{on(HS1)}$ ). For this thesis, both high-side switches have the same on-time ( $t_{on(HS)}$ ).

Stage 2 and Stage 4:  $Sw_{LS1}$  and  $Sw_{LS2}$  are on. The inductor voltage is negative ( $V_L = -V_{out}$ ), it discharges through the low-side switches and the output.

Stage 3:  $Sw_{HS2}$  and  $Sw_{LS1}$  are on.  $V_{in}$  is connected in series with  $C_{fly}$  and the inductor, both of which are charged. The inductor voltage is positive ( $V_L = V_{in} - V_{C_{fly}} - V_{out}$ ); it is being charged.

For linear charging of the inductor,  $C_{fly}$  is chosen so that there is negligible voltage ripple on the flying capacitor ( $\Delta v_{C_{fly}} \ll \text{Vin}$ ). The duty cycle is defined as  $t_{on(HS)}/T_{sw}$ .

Figure 1.2. The ideal 3-level buck converter: (a) circuit diagram, (b) switches' gate-source voltage waveforms.

There are three benefits to this topology, firstly in the 2-level buck converter the switches must block the entirety of  $V_{in}$ ; in the 3-level they only have to be able to block  $V_{in}/2$ . The smaller switch voltage rating allows for reduction in losses and smaller switch size and enables operation at higher  $f_{sw}$ . Secondly, (assuming that  $\Delta v_{C_{fly}}$  is negligible) the voltage that the inductor has to step-down halves from  $V_{in}$  to  $V_{in}/2$ ,

and thus D is doubled so that  $L_{min}$  can be reduced per Equation (1.3). The nominal D for the 2-level converter in this thesis is 0.36, thus  $L_{min}$  is approximately halved. Thirdly, the inductor is charged and discharged twice per period, doubling its effective frequency ( $f_{eff}$ ). As per Equation (1.3) this means that  $L_{min}$  is halved of the equivalent 2-level. Combining the second and third benefits,  $L_{min}$  can be reduced to approximately a quarter (for D=0.36) for same switch switching frequency. The drawbacks to the 3-level are the additions of extra capacitors, switches and drivers with their associated footprints and losses. The circumstances where the 3-level buck converter is a viable alternative is an overall focus for this thesis.

#### **1.3 Inductor Considerations**

In the typical POL converter, the inductor takes the largest amount of space. It is shown from the inductance equation, that inductance is proportional to area:

$$L = N_{turns}^{2} * A_{cross} * \mu / l_{core}$$

(1.4)

where  $N_{turns}$  is the number of turns,  $A_{cross}$  is the cross-sectional area of the inner core material,  $\mu$  is the magnetic permeability of the core, and  $l_{core}$  is the mean core length. Thus, for a larger inductance a larger core is needed or more turns, hence larger inductor size.

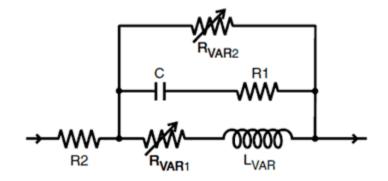

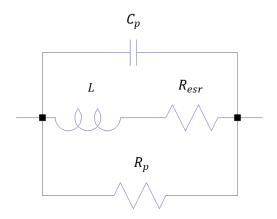

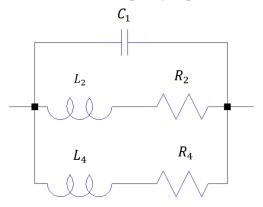

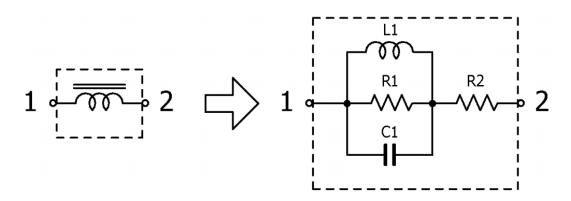

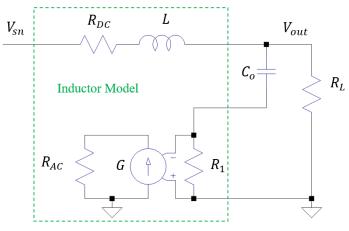

A lumped inductor model is shown in Figure 1.3. It has an inductance value  $L_{var}$  which is frequency dependent, due to the amplitude permeability ( $\mu_A(f)$ ) characteristic. *C* models the inductor's self-capacitance, and  $R_1$  is determined at the devices' resonant impedance.  $R_2$  represents the DC resistance loss. The frequency dependent variable resistors,  $R_{var1}$  models the skin and proximity effects.  $R_{var2}$  models the core loss.

Figure 1.3. The equivalent circuit model for an inductor. Image from Coilcraft (website).

The basic layout of an inductor is a wire coiled around a highly magnetic core. As current is passed through the turns, energy is stored in an electromagnetic field. A changing current creates an induced EMF which will be in a direction to try oppose the change in current. The direct current resistance (DCR) or winding resistance, is the resistance through the length of the wire that is coiled around the core [1]. The self-capacitance passes the high frequency displacement current flowing across the winding as each winding turn creates a small capacitor with its neighbouring turn.

The skin effect in a conductor causes higher resistance at higher frequency because of the tendency for high frequency current to flow at the surface due to the decrease in the magnetic field penetrating the conductor [2]. The proximity effect causes a higher resistance at higher frequency due to circular or eddy currents caused by the ac magnetic fields created by the currents in nearby conductors. Both skin and proximity effects are frequency dependent [3].

Some of the core loss is due to eddy currents in the core magnetic material [1], as eddy currents produce their own magnetic fields to oppose the field that caused them [3]. Hysteresis loss is the other component of core loss.

When the converter switching frequency is increased, skin, proximity and core losses will be increased. If the increase of frequency results in lower inductance needed, this can mean that a smaller inductor could be used. A smaller inductor would have fewer winding turns, hence lower DCR, increased self-capacitance, proximity, and skin effects. There is a balance to be found.

This thesis will compare the Tyndall National Institute thin-film Magnetics-on-Silicon (TF MoS "*MagPwr*" MS2) inductor [4], with commercially available discrete surface-mounted (SMT) inductors, and a baseline low loss air-core inductor.

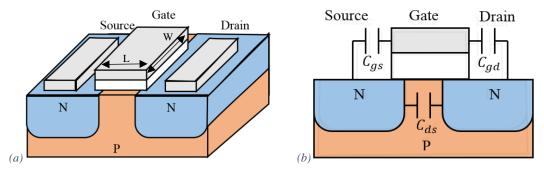

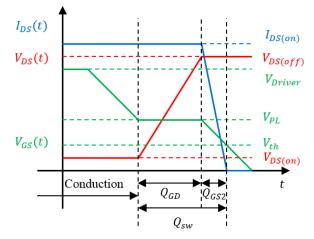

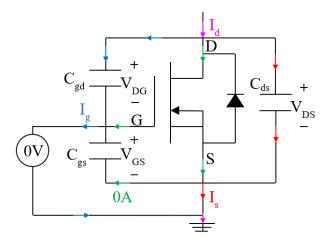

#### 1.4 Switch Losses

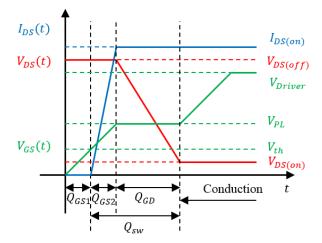

The simplified structure of an n-type metal-oxide-semiconductor field-effect transistor (NMOS) is shown in Figure 1.4(a). For an ideal enhancement mode device, no current will flow between drain and source terminals until the gate voltage,  $(V_{GS})$ , exceeds a threshold voltage,  $V_{th}$ , when an inversion (n-type) layer is formed under the insulator beneath the gate contact. This layer forms a connection between the drain and source and allows current to flow from drain to source  $(I_{DS})$  with low resistance. The device is a field controlled device and the gate insulator prevents DC current flow through the gate but due to its capacitance, there will be a displacement gate current flows which cause energy losses during device turn on and off.

Figure 1.4. (a) Cross-section of an NMOS, (b) with effective capacitances.

A smaller sized switch results in an  $R_{DS}$  increase and smaller gate capacitance. Smaller switches (lower width, W) can turn-on and turn-off quicker, hence have lower switching losses, making them more suitable for higher switching frequencies. Ideally when a MOSFET is off, there is unlimited blocking between the drain and source. With sufficient  $V_{DS}$  or a small enough gate length, eventually a connection would be made, this is referred to as breakdown. Reducing L reduces the breakdown voltage, so smaller switches typically have lower breakdown voltage.

Another relationship is between the width to length (W/L) ratio of the channel and the on-resistance of the switch ( $r_{on}$ ). In general, the larger the W/L ratio the smaller the on-resistance (larger drift currents). With a larger W/L ratio there is a larger cross-sectional area or smaller distance to travel. This is shown in the equation for resistance:

$$R = \rho l_{path} / A_{cross} \tag{1.5}$$

where R is the resistance,  $\rho$  is the resistivity,  $l_{path}$  is the length to travel,  $A_{cross}$  is the cross-sectional area. L is generally fixed according to the voltage rating required for the device. In Figure 1.4(b), the cross-section of an NMOS with its effective capacitances is shown. There are effective lumped capacitances between: the drain-source ( $C_{ds}$ ), the gate-source ( $C_{gs}$ ), and the gate-drain ( $C_{gd}$ ). At high frequency, these capacitances are significant, due to the capacitance current being proportional to frequency. The small signal input capacitance ( $C_{iss}$ ), the small signal output capacitance ( $C_{oss}$ ), and the small signal reverse transfer capacitance ( $C_{rss}$ ), are defined as:

$$C_{iss} = C_{gd} + C_{gs}, \tag{1.6}$$

$$C_{oss} = C_{gd} + C_{ds}, \tag{1.7}$$

and

$$C_{rss} = C_{gd}. \tag{1.8}$$

These capacitances vary with DC operating point.

There have been some several methods used to adapt and redesign the CMOS such as multi-finger MOSFETs, VDMOS, LDMOS [5-7]. These methods can be reduce the switch size or to reduce switching losses. For example, the multi-finger devices have drain and source regions shared between parallel devices and hence have lower gate-drain and gate-source capacitances.

Dead-times  $(t_d)$  are inserted between a  $Sw_{HS}$  turning off, and its  $Sw_{LS}$  compliment turning on and vice versa. Real switches cannot turn-on or turn-off instantaneously. If there is an overlap where both are on, there is a shorting of the input voltage to ground, with only the switches in the path. This is referred to as shoot-through, which leads to massive losses and possible switch destruction. There are two dead-times the fall dead-time  $(t_{d(H-L)})$  and the rise dead-time  $(t_{d(L-H)})$ .  $t_{d(H-L)}$  is defined as the time between the  $Sw_{HS}$  turning off and  $Sw_{LS}$  turning on.  $t_{d(L-H)}$  is defined as the time between  $Sw_{LS}$  turning off and  $Sw_{HS}$  turning on.

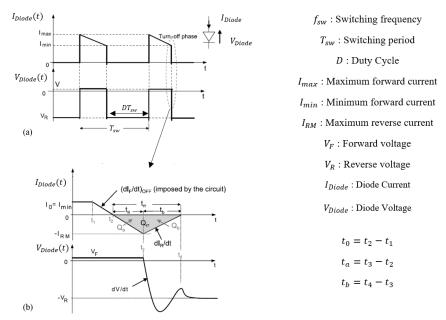

As the inductor cannot have a sudden interruption in current, during the dead-time the inductor current as shown in Figure 1.1(b) flows though the body diode of  $Sw_{LS}$ . It can be optimal for a freewheeling diode to be connected in parallel with the switch to improve performance. The diode loss can be broken down into diode conduction (during dead-time) and diode reverse recovery loss (QRR) (3<sup>rd</sup> quadrant conduction and recovery for GaN switches). These are explored in greater detail in Chapter 2.4.2 on page - 26 -.

There are also gate losses associated with turning on/off the switch and keeping the switch on or off for GaN HEMT which has gate leakage current.

All of the significant switch loss components are examined in this thesis:  $Sw_{HS}$  turn-on power loss  $(P_{on(HS)})$ ,  $Sw_{HS}$  turn-off power loss  $(P_{off(HS)})$ ,  $Sw_{HS}$  QRR power loss  $(P_{QRR(HS)})$ ,  $Sw_{HS}$  conduction power loss  $(P_{con(HS)})$ ,  $Sw_{HS}$  gate power loss  $(P_{gate(HS)})$ ,  $Sw_{LS}$  fall dead-time power loss  $(P_{t_{d(H-L)}})$ ,  $Sw_{LS}$  rise dead-time power loss  $(P_{t_{d(L-H)}})$ ,  $Sw_{LS}$  conduction power loss  $(P_{con(LS)})$ , and  $Sw_{LS}$  gate power loss  $(P_{gate(LS)})$ .

# 2. Literature Review and Background Theory

## 2.1 Converter Topologies

This section of the literature review investigates traditional switched-inductor based voltage regulators (such as the buck), step-down switched-capacitor (SC) converters, SC-buck hybrid converters, and multi-level flying-capacitor converters. The efficiencies, sizes, and optimal operating conditions of the topologies are discussed.

## 2.1.1 Buck Converter

Two effective ways of miniaturizing the buck converter are to increase the switching frequency or to use multi-phasing. The benefits and drawbacks of increasing the frequency is discussed in the introduction, this section convers the multi-phasing approach.

In a multi-phase converter, the inductor current is split into N smaller parallel buck converters. The switchnode voltage of each parallel converter is out of phase with the others by  $360^{\circ}$ /N, hence each inductor current is out of phase with the others. This reduces the current ripple and allows for a smaller input and output capacitances. The total inductance is typically the same and there may be a separate one for each phase or there may be a coupled arrangement. As the current is split into parallel paths, the heat losses are spread over a larger area, reducing power loss density. One disadvantage is that there are more switches, increasing the total switch size. Another disadvantage is that current balancing requires more advanced control.

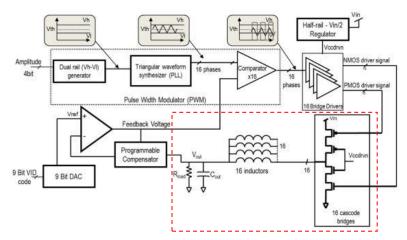

One example of the use of both multi-phasing and high frequency in buck design is [8]. The circuit diagram is shown in Figure 2.1. In this example, 16 phases are connected in parallel. In Figure 2.1, the error detector and pulse-width modulator (PWM) are shown in simplified form and the red dashed box is added to highlight the DC-DC converter power path.

Figure 2.1. Simplified circuit diagram for Intel's FIVR (16-phase buck regulator). Image from [8].

A noteworthy technique to allow advanced CMOS geometry node integration may be seen in Figure 2.1; the switches are arranged in cascode bridges. In an NMOS-PMOS cascode bridge, there are four switches per phase instead of two (one high-side and one low-side). The bridge drivers are controlled through high-voltage level shifters and support soft-switching operations, zero-voltage switching (ZVS) and zero-current switching (ZCS); soft switching can greatly reduce switching losses and hence allow for high efficiency in high switching frequency converters [9]. The gates of the cascode devices are connected to the "half-rail"

$(V_{ccdrvn})$ , which is regulated to  $V_{in}/2$ . This is the negative supply of the PMOS bridge driver, as well as the positive supply of the NMOS bridge driver. Due to this arrangement, 22 nm logic devices can be used while still handling voltages up to 1.8 V DC (0.9 V per switch). As CMOS technology nodes are scaled successively, while high frequency handling capabilities increase, this also leads to lower voltage handling capabilities.

This converter steps input voltages in the range of 12 V to 20 V down to an output voltage of 1.8 V. The high switching frequency of 140 MHz allows the components to be reduced in size enough to fit into existing unused space on the die. The high switching frequency allows each phase inductor to have a very small inductance value so that it can be realised with air-core alone. There is no magnetic material, which would be too lossy at 140 MHz. The effective current density of the FIVR is 31 A/mm, and an efficiency of up to 90% is achieved. The total  $I_{out}$  is in the range of 1 A to 15 A. The measured output voltage ripple is less than 4 mV, comfortably under 1% of the output voltage. This is achieved by using air-core inductors well under 2 mm<sup>2</sup> in area. The measured speed of response of the control is under 30 ns for the majority of the spike, with a total time of 100 ns to return to DC. This allows a peak spike of approximately 50 mV. The turn-on and turn-off time of the FIVR is approximately 0.6  $\mu$ s.

This design demonstrates the very high level of integration that can occur in a DC-DC converter operating at a very high switching frequency and with multiple phases, it also utilizes cascode bridges and soft switching, these techniques allow for reduction in power losses and component size

#### 2.1.2 Multi-Level Buck Converter

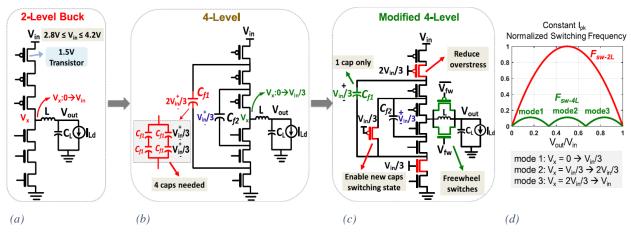

A highly integrated multi-level converter is described in [10]. This paper compares a 2-level buck, a 4-level buck, and a novel modified 4-level buck. The converter is designed using 28 nm fully depleted silicon-on-insulator (FDSOI) 1.5 V CMOS transistors and pulse frequency modulation (PFM) and operates in discontinuous conduction mode (DCM). The converter has a  $V_{in}$  range of 2.8 V to 4.2 V, a  $V_{out}$  range of 0.6 V to 1.2 V, a  $P_{out}$  range of 10  $\mu$ W to 40 mW, a peak efficiency of 78%, and a maximum  $f_{sw}$  of 200 MHz. Its total footprint is 1.5 mm<sup>2</sup>, excluding a pair of 5 nF flying capacitors and a 3 nH inductor.

The switches are stacked to distribute the voltage stress. The high-density capacitors in the scaled CMOS process have low voltage ratings (1.4 V for 28 nm) and must be stacked; stacking increases area and decreases power density. SC converters can achieve high efficiency and power densities, but only for fixed voltage ratios.

Multi-level converters enable a wide range of input and output voltages. They achieve higher overall efficiency by merging the benefits of inductive and capacitive converters. The flying capacitors reduce the switch-node voltage swing, thus reducing the voltage across the inductor. This means that the switching frequency may be reduced for the same ripple, to improve overall efficiency. The inductor may be used in a resonant mode to allow soft charge/discharge the capacitors, as another way to improve efficiency and power density.

For a 2-level (standard) buck, at least three stacked 28 nm transistors (1.5 V) would be required to block 4.2 V, shown in Figure 2.2(a) [10]. The 2-level offers no "voltage-breaking" advantage. The large effective series resistance (ESR) results in high conduction losses. A small on-chip inductor requires an increase in switching frequency to 100 MHz, resulting in high switching losses. There is no the frequency multiplication advantage. The switching frequency of a 2-level converter operating in discontinuous conduction mode (DCM) or in boundary conduction mode BCM) is given by:

$$f_{SW-2L} = \frac{2I_{out}V_{in}D(1-D)}{LI_{pk}^2}$$

(2.1)

where  $I_{pk}$  is the peak inductor current.

For a 4-level buck, the internal nodes between the stacked transistors are exploited by adding flying capacitors. As the switch-node voltage is reduced by a factor of three, the DCM switching frequency is given by:

$$f_{SW-4L} = \begin{cases} \frac{2I_{out}V_{in}D(1/3-D)}{LI_{pk}^2} & 0 < D < \frac{1}{3} \ (mode \ 1); \\ \frac{2I_{out}V_{in}(D-1/3)(2/3-D)}{LI_{pk}^2} & \frac{1}{3} < D < \frac{2}{3} \ (mode \ 2); \\ \frac{2I_{out}V_{in}(D-2/3)(1-D)}{LI_{pk}^2} & \frac{2}{3} < D < 1 \ (mode \ 3). \end{cases}$$

(2.2), (2.3), and (2.4)

Figure 2.2(d) shows that the equivalent switching frequency (for any of the three modes) of the 4-level converter is less than 20% of that of the 2-level converter. The figure shows that for the same inductance value, the normalised switching frequency can be reduced by a factor up to 23, and citing a 33% improvement in efficiency. The drain-source voltages of the 4-level converter's switches never exceed  $V_{in}/3$ . Alternatively the extra levels may be used to reduce the volt-seconds burden on the inductor so that smaller inductance values can be used. Modes 1-3 refer to PWM modes and the order in which the input source and ground is alternatively switched through the various multi-level capacitors.

The diagrams in Figure 2.2(a-c) show the circuit topologies.

*Figure 2.2. Topologies for: (a) the 2-level buck, (b) the 4-level buck, and (c) the modified 4-level buck converter. (d) Normalized switching frequency versus conversion ratio for the 2-level buck and the 4-level buck converter, operating in DCM with constant peak current I<sub>pk</sub>. From [10].*

## 2.2 High Frequency Magnetics

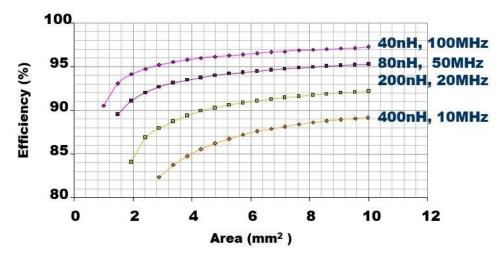

Paper [11] reviews the impact of inductors in high frequency DC-DC converters. Inductor size in portable applications is examined, specifically the Tyndall micro-fabricated magnetics-on-silicon inductor, which has a relatively large inductance per area, given its high frequency capability. There is also some analysis of the performance of SC-buck hybrid topologies.

Figure 2.3, extracted from [11], clearly shows that smaller inductor values, for a given area, are more efficient. The efficiency of an inductor can be calculated using the losses associated with its operation or from direct measurement. The equation for loss can be approximated by:

$$P_L = r_L * i_{L(rms)}^2 \tag{2.5}$$

where  $r_L$  is the ESR of the inductor (representing all AC losses (copper and core) for the inductor) and  $i_{L(rms)}$  is the root mean square current through the inductor.

Inductor efficiency is calculated using:

$$Efficiency = \frac{ConverterOutputPower}{ConverterOutputPower + InductorLoss}.$$

(2.6)

In the model used, eddy currents, hysteresis, DC, and AC (six harmonics) losses were all included. The result is shown in Figure 2.3. The buck converter is operated at 10 MHz, 20 MHz, 50 MHz, and 100 MHz. Using Equation (1.3) it is clear that inductance is inversely proportional to switching frequency. For each frequency, inductor efficiency is compared to the physical area taken up by the inductor. This work demonstrates how increasing the switching frequency of a buck converter can be utilized to reduce inductor size and loss.

Figure 2.3. Area vs. efficiency for inductors at various frequencies. From [11].

#### 2.3 High Frequency Switch Layout

#### 2.3.1 Multi-Finger MOSFET

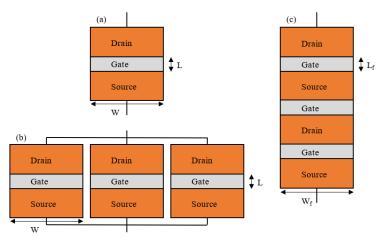

The multi-finger MOSFET (MFM) is discussed in this section, including its layout, operation, advantages, and disadvantages. The typical layout of a MOSFET is shown in Figure 2.4(a). By combining the MOSFET in parallel with two identical MOSFETs, as shown in Figure 2.4(b), the width is essentially tripled. This reduces the on-resistance, resulting in lower conduction losses, but increasing equivalent capacitances ( $C_{gs}$ ,  $C_{gd}$  and  $C_{ds}$ ), which can increase drive and switching losses. The three-finger MOSFET shown in Figure 2.4(c) has the same on-resistance as the device in Figure 2.4(b), as it also has triple the width of the single-finger device. The advantage of the three-finger MOSFET is that the MFM has lower overall  $C_{gs}$  and  $C_{gd}$  capacitances than the multiple MOSFETs connected in parallel.

Figure 2.4. Top view of MOSFET configurations: (a) single-finger MOSFET, (b) three single-finger MOSFETs connected in parallel, and (c) three-finger MOSFET.

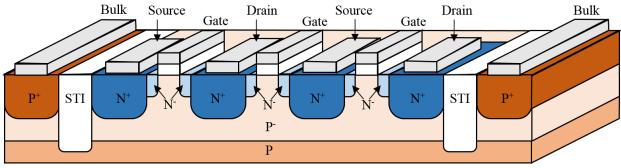

Figure 2.5 shows the cross-section of a four-finger MOSFET [12]. The four-finger MOSFET shown includes the bulk and shallow trench isolation (STI), and also has lightly doped drains (LDDs). LDDs improve MOSFET reliability at the expense of current drive [13].

Figure 2.5. Cross-section of a four-finger n-type MOSFET. Based on [12].

As the number of gate fingers  $(N_f)$  increases, there is lower drain and source resistance, thus total resistance is reduced, leading to an increase in drain current. As more gates are connected in parallel, gate resistance is also reduced [14]. This reduction is limited, so that eventually, increasing the number of fingers does not significantly change the series parasitic resistance. The equation below gives the relationship between the total width ( $W_{total}$ ) and  $N_f$  and  $W_f$ :

$$W_{total} = N_f * W_f. \tag{2.7}$$

In general, the drain-body and source-body capacitances ( $C_{db}$  and  $C_{sb}$ ) decrease with the number of fingers (up to a point). The exception is  $C_{db}$  with an even number of fingers, in which case  $C_{db}$  gradually increases as the number of fingers increases.

The gate resistance,  $R_{gate}$ , is given by:

$$R_{gate} = R_{sch} \frac{W}{_{3*M*L*N_f^2}} \tag{2.8}$$

where  $R_{sch}$  is the resistance of poly layer (gate layer) and M is a unitless coefficient. M depends on how the gate is accessed [15]. As  $R_{gate}$  is inversely proportional to  $N_f^2$ , the resistance is reduced by using the

multi-finger technique. Multi-fingering was used with the CMOS designed in this thesis switches to reduce on-resistance.

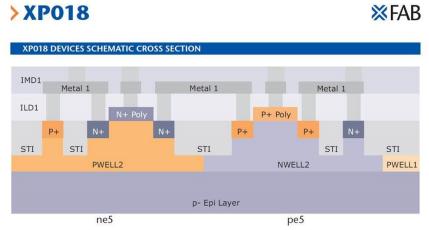

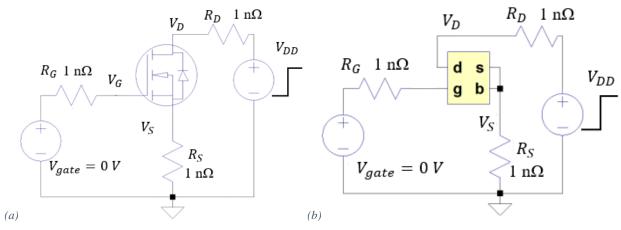

## 2.3.2 Bulk 180 nm NMOS and PMOS

This thesis deals with simulating converters that use multi-finger bulk CMOS switches. Models for the 5 V ne5 (NMOS) and pe5 (PMOS) bulk 180 nm CMOS devices of the XP018 series from X-FAB [16] are used. Figure 2.6 shows their cross-section. For the NMOS, there is p+ contact to the body. The body is connected to the n+ source and will form a body diode between source/body and the drain. The polysilicon gate regions are shown over the channels n+ poly for the NMOS and p+ poly for the PMOS.

Figure 2.6. Cross-section of a 5 V ne5 and pe5 180 nm CMOS.

#### 2.3.3 Gallium Nitride High-Electron-Mobility Transistors

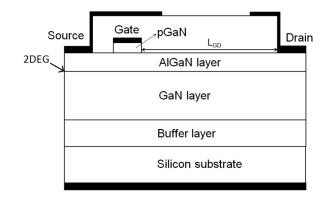

The converter tested in this thesis uses 15 V EPC2040 [16] enhancement mode GaN switches manufactured by EPC. These 15V devices give somewhat similar performance to the *ne5* and *pe5* 5V CMOS devices designed. This section reviews that switch technology. The operation, advantages and disadvantages of gallium-nitride (GaN) high-electron-mobility transistors (HEMTs) is reviewed, with reference to [17-23].

In terms of material properties, GaN naturally has a wider band gap (3.4 eV) than Si (1.1 eV). This means that it has a higher critical electric field and shorter drift region for the same breakdown voltage (VB). Thus, a GaN transistor can have a much shorter length for the same blocking voltage, resulting in a smaller area. It has extremely low intrinsic carrier concentration,  $1.9 \times 10^{-10} \text{ cm}^{-3}$  (Si is  $1.5 \times 10^{10} \text{ cm}^{-3}$ ), hence a lower leakage current. It has a piezo-polarization nature, meaning that it can have a high channel concentration without intentional doping, hence high electron mobility. Ga is a group three element and N is group five. When the two elements are combined, the structure has spontaneous polarization. This means that the bonds are polar, and because the structure is non-centrosymmetric, this polarization is intrinsic. GaN can also be grown on Si, making it cheaper than, for example, SiC or diamond.

GaN can form a heterojunction with AlGaN. A heterojunction is when an interface is formed between two different semiconductors with dissimilar bandgaps. In the formation of heterojunctions, it is beneficial to have large differences in bandgaps (AlGaN is 6.2 eV) and to have a small lattice mismatch so that there is no dislocation. The lattice mismatch between GaN and AlGaN causes a strain between the two layers, which produces the piezoelectric polarization. If there is a gradient in polarization, there is an induced positive charge. This charge attracts electrons, which form the two-dimensional electron gas (2DEG) [18]. The electrons are confined in a quantum well. The cross-section of a GaN switch is shown in Figure 2.7.