# Timing Architecture for ESS

Autor: Javier Cereijo García

2020

**Directores: Daniel Piso Fernández** Roberto Rodríguez Osorio

Roberto Rodríguez Osorio Tutor:

Programa de doctorado en Investigación en Tecnologías de la Información

UNIVERSIDADE DA CORUÑA

ii

Dr. Daniel Piso Fernández Director Engineering Architecture Technology Group Arm Ltd. Dr. Roberto Rodríguez Osorio Profesor Titular de Universidad Dpt. de Ingeniería de Computadores Universidade da Coruña

#### CERTIFICAN

Que la memoria titulada "Timing Architecture for ESS" ha sido realizada por D. Javier Cereijo García bajo nuestra dirección en el Programa de Doctorado Interuniversitario en Investigación en Tecnologías de la Información, y concluye la Tesis Doctoral que presenta para optar al grado de Doctor.

En A Coruña, a 10 de Julio de 2020

Fdo.: Daniel Piso Fernández Director de la Tesis Doctoral Fdo.: Roberto Rodríguez Osorio Director de la Tesis Doctoral

Fdo.: Javier Cereijo García Autor de la Tesis Doctoral iv

## Acknowledgements

I would like to acknowledge and thank a lot of people without whom I would not have been able to do this thesis.

In the first place I would like to thank my supervisors for all the support and help while doing this thesis. Without them I would not have achieved it. Daniel Piso Fernández who was my key and door to the European Spallation Source, and Roberto Rodríguez Osorio who helped me at the university and with the research for this thesis.

I would also like to thank Javier Díaz Bruguera, who introduced and gave me the opportunity to do this thesis at the European Spallation Source.

I would like thank all my colleagues at the European Spallation Source, in the Integrated Control System division and specially those of them in the Hardware and Integration group, including my line manager Karl Vestin and work package manager Faye Chicken. In no particular order, I am grateful to Joao Paulo Martins, Saeed Haghtalab, John Sparger and Nicklas Holmberg for challenging me with new usecases for the timing system. This gratefulness also includes the people that are not part of the European Spallation Source any more, like Nick Levchenko and David Brodrick for sharing their integration experience, Ursa Rojec for introducing me to EPICS and Simone Farina for his help with everything and specially hardware. Of course I would like to thank Jerzy Jamroz and Felipe Torres González for their discussions of different implementations of timing systems and Michael Davidsaver for his help with *mrfioc2*, EPICS and everything related to timing in general. I would also like to thank the stake holders of the timing system for their feedback and suggestions. Also Jukka Pietarinen from Micro-Research Finland.

I would specially like to thank the chief engineer Timo Korhonen for being my supervisor at the European Spallation Source and for the help, guidance and discussions about all the technologies that I have used when working with the timing system. And finally I would like to thank the person at the European Spallation Source who helped me the most when I was not sure how to advance and who pushed me to continue and finish the job. Thank you Jeong Han Lee.

There is more people that have helped me with this project, although I have not mentioned. I would like to thank all of them.

Finally I would like to thank my friends, family and my girlfriend M-C for their support and listening to me.

# Resumo

O sistema de temporización é unha compoñente fundamental para o control e sincronización de instalacións industriais e científicas, coma aceleradores de partículas. Nesta tese traballamos na especificación e desenvolvemento do sistema de temporización para a European Spallation Source (ESS), a maior fonte de neutróns actualmente en construción. Abordamos este traballo a dous niveis: a especificación do sistema de temporización, e a implementación física de sistemas de control empregando circuítos reconfigurables.

Con respecto á especificación do sistema de temporización, deseñamos e implementamos a configuración do protocolo de temporización para cumprir cos requirimentos do ESS e ideamos un modo de operación e unha aplicación para a configuración e control do sistema de temporización.

Tamén presentamos unha ferramenta e unha metodoloxía para implementar sistemas de control empregando FPGAs, coma os nodos do sistema de temporización. ámbalas dúas están baseadas en statecharts, unha representación gráfica de sistemas que expande o concepto de máquinas de estados finitos, orientada a sistemas que necesitan ser reconfigurados rápidamente en múltiples localizacións minimizando a posibilidade de erros. A ferramenta crea automaticamente código VHDL sintetizable a partir do statechart do sistema. A metodoloxía explica o procedemento para implementar o statechart como unha arquitectura microprogramada en FPGAs.

RESUMO

viii

# Resumen

El sistema de temporización es un componente fundamental para el control y sincronización de instalaciones industriales y científicas, como aceleradores de partículas. En esta tesis trabajamos en la especificación y desarrollo del sistema de temporización para la European Spallation Source (ESS), la mayor fuente de neutrones actualmente en construcción. Abordamos este trabajo en dos niveles: la especificación del sistema de temporización, y la implementación física de sistemas de control empleando circuitos reconfigurables.

Con respecto a la especificación del sistema de temporización, diseñamos e implementamos la configuración del protocolo de temporización para cumplir con los requisitos de ESS e ideamos un modo de operación y una aplicación para la configuración y control del sistema de temporización.

También presentamos una herramienta y una metodología para implementar sistemas de control empleando FPGAs, como los nodos del sistema de temporización. Ambas están basadas en statecharts, una representación gráfica de sistemas que expande el concepto de máquinas de estados finitos, orientada a sistemas que necesitan ser reconfigurados rápidamente en múltiples localizaciones minimizando la posibilidad de errores. La herramienta crea automáticamente código VHDL sintetizable a partir del statechart del sistema. La metodología explica el procedimiento para implementar el statechart como una arquitectura microprogramada en FPGAs.

RESUMEN

х

## Abstract

The timing system is a key component for the control and synchronization of industrial and scientific facilities, such as particle accelerators. In this thesis we tackle the specification and development of the timing system for the European Spallation Source (ESS), the largest neutron source currently in construction. We approach this work at two levels: the specification of the timing system and the physical implementation of control systems using reconfigurable hardware.

Regarding the specification of the timing system, we designed and implemented the configuration of the timing protocol to fulfil the requirements of ESS and devised an operation mode and an application for the configuration and control of the timing system.

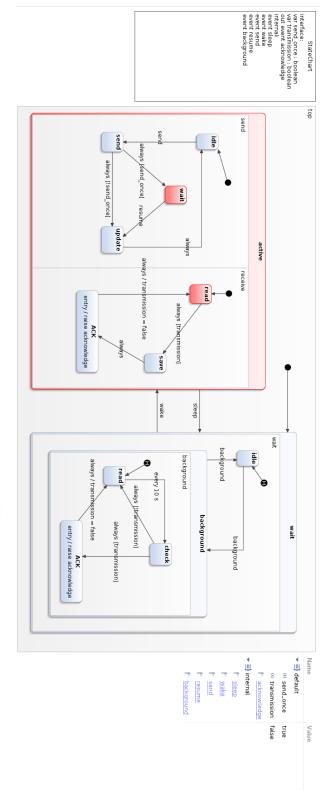

We also present one tool and one methodology to implement control systems using FPGAs, such as the nodes of the timing system. Both are based on statecharts, a graphical representation of systems that expand the concepts of Finite State Machines, targeted at systems that need to be reconfigured quickly in multiple locations minimizing the chance of errors. The tool automatically creates synthesizable VHDL code from a statechart of the system. The methodology explains the procedure to implement the statechart as a microprogrammed architecture in FPGAs.

ABSTRACT

xii

## Preface

Industrial and scientific facilities are getting more and more complex to deal with new challenges and become more efficient. This affects the equipment that makes up these centres but also, and maybe even more importantly, the systems that integrate all of these devices so that they can work together to fulfil the goal of the facility. One of these is the control system, which is responsible for managing the rest of the systems so that they operate in the correct way and in unison. Control systems are intricate networks that comprise hardware, software and their respective configurations, and that are integrated together to successfully run the machine or facility.

One of the integral parts of control systems is the timing system. The timing system is in charge of synchronizing all of the devices together and to the rest of the world outside the facility or centre. This last part is usually done by connecting to an external source, such as the Global Positioning System, from which the timing system derives its reference of time and that it uses to orchestrate the facility. Timing systems usually have a master node that defines the time for the centre disciplined by the external source and dispatches it to the rest of the timing system, formed by slave nodes. The master node is also the central point where the operation and configuration are managed from, and it codes this configuration so that it can be sent and used by the slave nodes. The slave nodes receive the time and information sent by the master node and react accordingly. The typical reactions are sending precise triggers and timestamping different signals and occurrences.

There are a number of challenges that the timing system needs to solve for performing its duties correctly. The most important one is the synchronization of the facility. For achieving synchronization it is mandatory to define one common master clock and send it to the rest of the timing system nodes. If this is not done, and it is decided for each of the nodes to run its own clock, all of them with the same frequency, one issue quickly shows up: even if the clocks are off by just a fraction of a part per million, given the frequency at which the timing system operates, usually around 100 MHz, in a matter of a few seconds the nodes will drift from each other by more than one cycle of the clock. The only solution is then to define and distribute a common master clock that is shared by all of the nodes. On top of defining the common clock, it is needed to define a moment in time that acts as the reference of time and distribute this moment to all nodes without delay. Since this is not possible, specially because the nodes that need to be synchronized are far away from each other, in some cases hundreds of meters or kilometres away, an alternative solution is needed, which entails calculating the delay of the transmission between the nodes, so that the original moment in time can be calculated.

In this thesis we study, integrate and make some contributions to the timing system of one scientific facility currently under design and construction, the European Spallation Source. The European Spallation Source is a scientific facility for research with neutrons that will be the largest in the world when it starts operating. It is formed by a linear accelerator that shoots a beam of protons at a target wheel that produces neutrons by the spallation process. The neutrons are then guided to a set of experiments, where they are used to perform science in different fields. The European Spallation Source is a collaboration among several European countries, that design and build the different parts and systems all over Europe as an in-kind project, and deliver the parts to Lund, in southern Sweden, where they are assembled together. While the actual facility is located in Lund, the data produced by the experiments will travel to Copenhagen in the neighbour country of Denmark where it will be processed and stored.

The timing system at the European Spallation source is implemented with a master node, called a event generator, that sends events and other timing information to event receivers, which react to the events as they are configured to, mainly to trigger the different devices in a synchronized way. In the context of the timing system, an event is an enumerated pulsed signal. Most of the nodes of the timing system at the European Spallation Source are provided by Micro-Research Finland. This timing system is in charge of creating and distributing the events that are used to trigger the different devices, distributing synchronous clocks, defining and sharing a common time reference used for timestamping signals and other occurrences and distributing some beam-related parameters throughout the facility. In this thesis we deal with the design, implementation and integration of the timing system for the European Spallation Source. This includes studying the European Spallation Source facility, the systems and devices that form it and their requirements. Then we come up with a way of implementing all of these in the protocol that is used by the timing system, and we develop a strategy for implementing the control and configuration of the event generator and the event receivers. This includes developing the lists of events and data distributed by the timing system and the configuration of the nodes according to these lists.

On top of this we present some contributions that we developed for the timing system of the European Spallation Source. Among them is a new mode of operation of the event receivers, so that they can work independently from an event generator. This has been very useful at the European Spallation Source due to the in-kind nature of the project. Another contribution relates to a high-level application that will be used for commissioning and ramp-up of the European Spallation Source after shutdown periods that allows to pre-define a series of sequences of events and data that are sent automatically and in a synchronized way. We also present a new board devised and designed by the European Spallation Source and an in-kind collaborator, and that will be used to deliver timing in locations of the facility where, for a number of reasons such as constrained space or just saving costs, it is impossible or at least impractical to deploy one of the normal event receivers. Finally we present a tool and a methodology to implement control systems in reconfigurable hardware minimizing the chance of errors. Both the tool and the methodology are based on statecharts, an expansion of Finite State machines. The tool translates the system represented by an statechart into VHDL ready to be synthesized and implemented in hardware, while the methodology explains how to create a microprogrammed architecture targeted at FPGAs that implements statecharts. Having tools and processes that are error-free is very important in big facilities such as the European Spallation Source, since the complexity of the machine induces the appearance of issues that may prevent the facility from working properly or even be destroyed or harm people.

PREFACE

xvi

# Contents

| A        | Acknowledgements v |                     |                                                                                                                |  |    | $\mathbf{v}$ |  |

|----------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------|--|----|--------------|--|

| R        | Resumo vii         |                     |                                                                                                                |  |    |              |  |

| R        | esum               | en                  |                                                                                                                |  |    | ix           |  |

| A        | bstra              | $\operatorname{ct}$ |                                                                                                                |  |    | xi           |  |

| Pı       | reface             | 9                   |                                                                                                                |  | 2  | xiii         |  |

| Li       | st of              | abbre               | viations                                                                                                       |  | xx | vii          |  |

| 1        | Intr               | oducti              | lon                                                                                                            |  |    | 1            |  |

|          | 1.1                | Neutro              | ons for science                                                                                                |  |    | 2            |  |

|          |                    | 1.1.1               | The European Spallation Source ERIC                                                                            |  |    | 3            |  |

|          | 1.2                | Contro              | ols and timing at ESS                                                                                          |  |    | 4            |  |

|          | 1.3                |                     | this thesis $\ldots$                                                                                           |  |    | 6            |  |

| <b>2</b> | The                | ESS t               | timing system                                                                                                  |  |    | 9            |  |

|          | 2.1                | Synch               | $ronization \ldots \ldots$ |  |    | 9            |  |

|          |                    | 2.1.1               | Phase locked loops                                                                                             |  |    | 10           |  |

|          |                    | 2.1.2               | Transmission delays                                                                                            |  |    | 12           |  |

|          | 2.2                | Synch               | ronization technologies                                                                                        |  |    | 13           |  |

|          |                    | 2.2.1               | NTP                                                                                                            |  |    | 13           |  |

|          |                    | 2.2.2               | PTP                                                                                                            |  |    | 14           |  |

|          |                    | 2.2.3               | Other current technologies                                                                                     |  |    | 14           |  |

|          | 2.3                | Definit             | tions                                                                                                          |  |    | 15           |  |

|          |                    | 2.3.1               | Beam cycle                                                                                                     |  |    | 15           |  |

|          |                    | 2.3.2               | Beam pulse                                                                                                     |  |    | 15           |  |

|          |                    | 2.3.3               | Event                                                                                                          |  |    | 16           |  |

### CONTENTS

|   |                          | 2.3.4                                                                                                                        | Trigger                                                                                                                                                                                                                                                                                                                                     |  |

|---|--------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   |                          | 2.3.5                                                                                                                        | Data items 16                                                                                                                                                                                                                                                                                                                               |  |

|   |                          | 2.3.6                                                                                                                        | Event frequency                                                                                                                                                                                                                                                                                                                             |  |

|   |                          | 2.3.7                                                                                                                        | Sequence                                                                                                                                                                                                                                                                                                                                    |  |

|   |                          | 2.3.8                                                                                                                        | Supercycle                                                                                                                                                                                                                                                                                                                                  |  |

|   |                          | 2.3.9                                                                                                                        | Timestamp                                                                                                                                                                                                                                                                                                                                   |  |

|   |                          | 2.3.10                                                                                                                       | Clock                                                                                                                                                                                                                                                                                                                                       |  |

|   |                          | 2.3.11                                                                                                                       | Real world time                                                                                                                                                                                                                                                                                                                             |  |

|   | 2.4                      | The E                                                                                                                        | SS timing system $\ldots \ldots 18$                                                                                                                                                                                                                                   |  |

|   |                          | 2.4.1                                                                                                                        | Topology                                                                                                                                                                                                                                                                                                                                    |  |

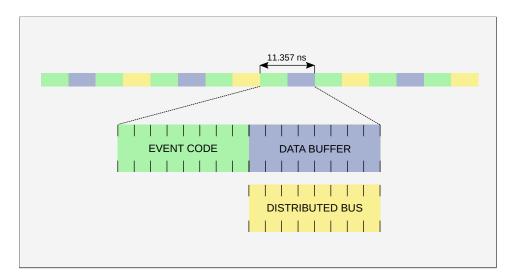

|   |                          | 2.4.2                                                                                                                        | The data stream $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 21$                                                                                                                                                                                                                                                         |  |

|   |                          | 2.4.3                                                                                                                        | Timestamping $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 26$                                                                                                                                                                                                                                                     |  |

|   |                          | 2.4.4                                                                                                                        | Hardware                                                                                                                                                                                                                                                                                                                                    |  |

|   |                          | 2.4.5                                                                                                                        | The integration of timing in the ESS control system $.34$                                                                                                                                                                                                                                                                                   |  |

|   |                          | 2.4.6                                                                                                                        | Timing system requirements                                                                                                                                                                                                                                                                                                                  |  |

|   |                          | 2.4.7                                                                                                                        | Timing system consuming systems                                                                                                                                                                                                                                                                                                             |  |

|   |                          | 2.4.8                                                                                                                        | The ESS timing structure                                                                                                                                                                                                                                                                                                                    |  |

| • |                          |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                             |  |

| 3 |                          |                                                                                                                              | Software codesign of the ESS timing system in-                                                                                                                                                                                                                                                                                              |  |

|   | -                        | ation                                                                                                                        | 43                                                                                                                                                                                                                                                                                                                                          |  |

|   | 3.1                      |                                                                                                                              | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                        |  |

|   | 3.2                      |                                                                                                                              | iniIOC                                                                                                                                                                                                                                                                                                                                      |  |

|   | <u></u>                  | 3.2.1                                                                                                                        | Embedded EVRs         50           opercycle         51                                                                                                                                                                                                                                                                                     |  |

|   | 3.3                      |                                                                                                                              | Dercycle 51                                                                                                                                                                                                                                                                                                                                 |  |

|   |                          |                                                                                                                              | 1 0                                                                                                                                                                                                                                                                                                                                         |  |

|   | 3.4                      | The E                                                                                                                        | $\overline{SS}$ data model specification                                                                                                                                                                                                                                                                                                    |  |

|   | 3.4                      | The E<br>3.4.1                                                                                                               | SS data model specification                                                                                                                                                                                                                                                                                                                 |  |

|   | 3.4                      | The E3<br>3.4.1<br>3.4.2                                                                                                     | SS data model specification53Differences between Event and Data53Operation event list54                                                                                                                                                                                                                                                     |  |

|   | 3.4                      | The E<br>3.4.1                                                                                                               | SS data model specification                                                                                                                                                                                                                                                                                                                 |  |

| 4 |                          | The E3<br>3.4.1<br>3.4.2<br>3.4.3                                                                                            | SS data model specification       53         Differences between Event and Data       53         Operation event list       54         Data definition       59                                                                                                                                                                             |  |

| 4 |                          | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br>omate                                                                                   | SS data model specification       53         Differences between Event and Data       53         Operation event list       54         Data definition       59         d synthesis of Statecharts       63                                                                                                                                 |  |

| 4 | <b>Aut</b><br>4.1        | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br>omate<br>Statech                                                                        | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64                                                                                                                                                                                                 |  |

| 4 | Aut                      | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br>omate<br>Statech<br>Hardw                                                               | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69                                                                                                                                                                   |  |

| 4 | <b>Aut</b><br>4.1        | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br><b>omate</b><br>Statecl<br>Hardw<br>4.2.1                                               | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69Graphical representations of statecharts71                                                                                                                         |  |

| 4 | <b>Aut</b><br>4.1        | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br><b>omate</b><br>Statecl<br>Hardw<br>4.2.1<br>4.2.2                                      | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69Graphical representations of statecharts71Parsing and analysis of statecharts72                                                                                    |  |

| 4 | <b>Aut</b><br>4.1<br>4.2 | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br>omate<br>Statech<br>Hardw<br>4.2.1<br>4.2.2<br>4.2.3                                    | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69Graphical representations of statecharts71Parsing and analysis of statecharts72Restrictions on the original statechart74                                           |  |

| 4 | <b>Aut</b><br>4.1        | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br><b>omate</b><br>Statecl<br>Hardw<br>4.2.1<br>4.2.2<br>4.2.3<br>Implem                   | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69Graphical representations of statecharts71Parsing and analysis of statecharts72Restrictions on the original statechart74nentation strategy76                       |  |

| 4 | <b>Aut</b><br>4.1<br>4.2 | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br><b>omate</b><br>Statecl<br>Hardw<br>4.2.1<br>4.2.2<br>4.2.3<br>Implen<br>4.3.1          | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69Graphical representations of statecharts71Parsing and analysis of statecharts72Restrictions on the original statechart74nentation strategy76Orthogonality78        |  |

| 4 | <b>Aut</b><br>4.1<br>4.2 | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br><b>omate</b><br>Statecl<br>Hardw<br>4.2.1<br>4.2.2<br>4.2.3<br>Implen<br>4.3.1<br>4.3.2 | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69Graphical representations of statecharts71Parsing and analysis of statecharts72Restrictions on the original statechart74nentation strategy76Orthogonality78Depth79 |  |

| 4 | <b>Aut</b><br>4.1<br>4.2 | The E3<br>3.4.1<br>3.4.2<br>3.4.3<br><b>omate</b><br>Statecl<br>Hardw<br>4.2.1<br>4.2.2<br>4.2.3<br>Implen<br>4.3.1          | SS data model specification53Differences between Event and Data53Operation event list54Data definition59d synthesis of Statecharts63harts64are synthesis of statecharts69Graphical representations of statecharts71Parsing and analysis of statecharts72Restrictions on the original statechart74nentation strategy76Orthogonality78        |  |

### xviii

### CONTENTS

|              |                                         | 4.3.5  | Actions and conditions                          |     | 84  |

|--------------|-----------------------------------------|--------|-------------------------------------------------|-----|-----|

|              |                                         | 4.3.6  | Implementations steps                           |     | 85  |

|              |                                         | 4.3.7  | Example                                         |     | 91  |

|              |                                         | 4.3.8  | Evaluation                                      |     | 92  |

|              |                                         | 4.3.9  | Extension of the application to other languages |     | 93  |

|              | 4.4                                     | Microp | programmed implementation                       |     | 94  |

|              |                                         | 4.4.1  | Microprogramming                                |     | 95  |

|              |                                         | 4.4.2  | Mapping a statechart into a microprogram        |     | 96  |

|              |                                         | 4.4.3  | Architecture                                    |     | 103 |

|              |                                         | 4.4.4  | Case example                                    |     | 112 |

|              |                                         | 4.4.5  | Evaluation                                      | •   | 115 |

| <b>5</b>     | Con                                     | clusio | ns                                              |     | 119 |

|              | 5.1                                     | Future | e work                                          |     | 120 |

|              | 5.2                                     |        | ations derived from this thesis                 |     |     |

| A            | Bea                                     | m moo  | les                                             |     | 123 |

| в            | Beam destinations 125                   |        |                                                 | 125 |     |

| $\mathbf{C}$ | Resumen en castellano de esta tesis 127 |        |                                                 | 127 |     |

### xix

CONTENTS

xx

# List of Figures

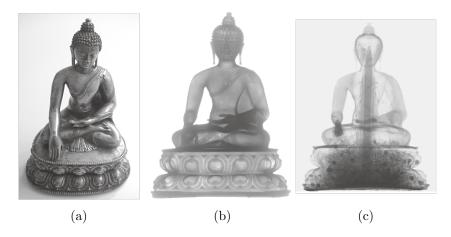

| 1.1 | (a) Buddha sculpture, (b) X-ray image, (c) neutron image.<br>Source [1] | 2  |

|-----|-------------------------------------------------------------------------|----|

| 1.2 | ESS linac layout. Source: ESS                                           | 4  |

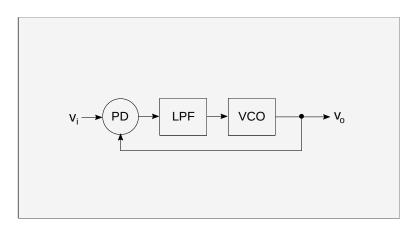

| 2.1 | Phase locked loop.                                                      | 11 |

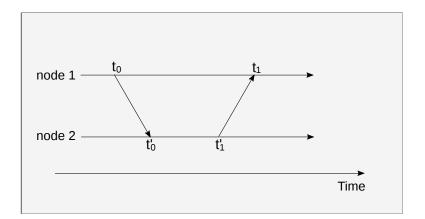

| 2.2 | Calculating the delay of the transmission between two nodes.            | 13 |

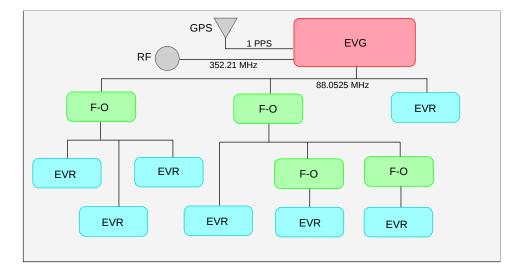

| 2.3 | Topology example of the ESS timing system.                              | 20 |

| 2.4 | Frame structure of the data stream.                                     | 23 |

| 2.5 | The mTCA-EVM-300 card                                                   | 30 |

| 2.6 | The mTCA-EVR-300U card.                                                 | 34 |

| 2.7 | The PCIe-EVR-300DC card.                                                | 34 |

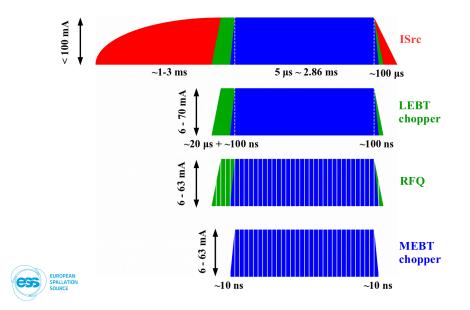

| 2.8 | The beam pulse structure of ESS after several devices of the            |    |

|     | accelerator. Source: ESS                                                | 42 |

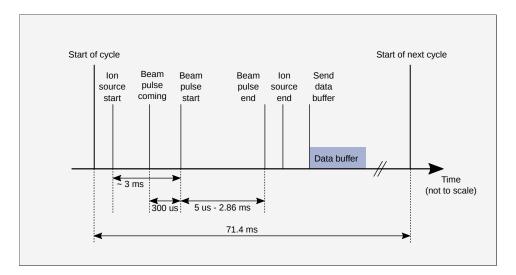

| 3.1 | Example of the timeline of the events in the sequencer during           |    |

|     | normal operation.                                                       | 57 |

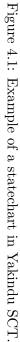

| 4.1 | Example of a statechart in Yakindu SCT.                                 | 66 |

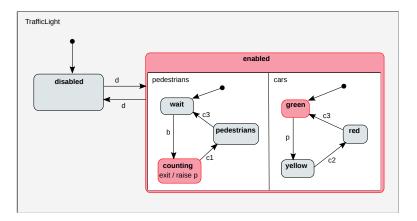

| 4.2 | Statechart showing orthogonality.                                       | 69 |

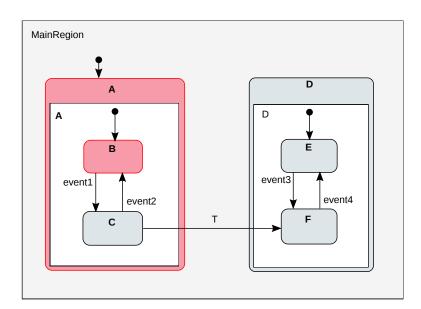

| 4.3 | Statechart showing a forbidden transition.                              | 76 |

| 4.4 | Statechart equivalent to the statechart shown in Figure 4.3             |    |

|     | but without the forbidden transition                                    | 77 |

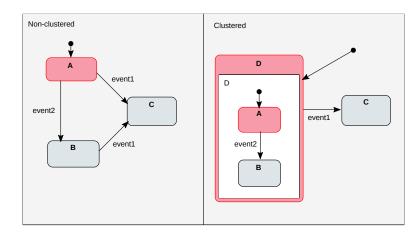

| 4.5 | Statechart showing <i>clustering</i>                                    | 80 |

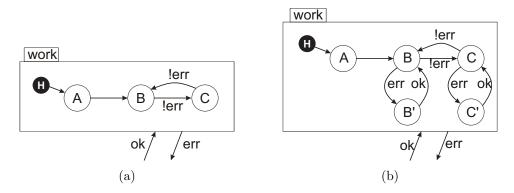

| 4.6 | (a). super-state with history. (b). Proposed implementation             |    |

|     | using wait states                                                       | 83 |

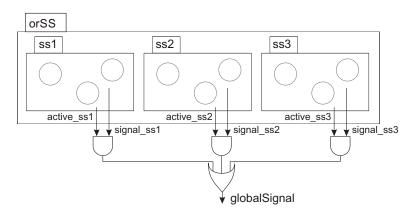

| 4.7 | Distributed generation of a global signal                               | 85 |

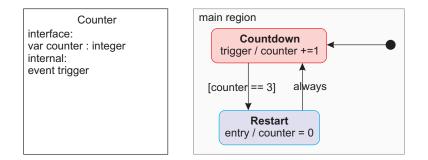

| 4.8 | Simple statechart with actions and conditions                           | 85 |

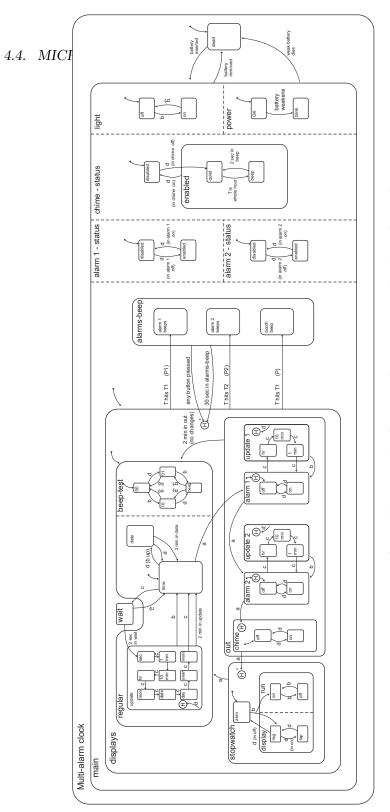

| 4.9 | Recreation of Harel's example of a statechart to control a              |    |

|     | digital watch.                                                          | 97 |

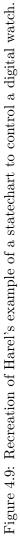

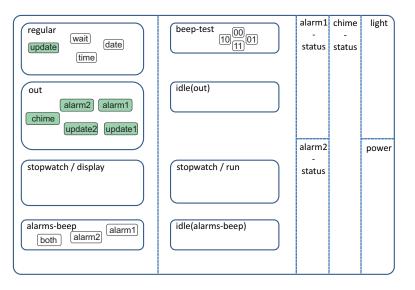

| 4.10 | Main and ghost - main microprograms that implement the<br>displays super-state. The microinstructions in the ghost<br>microprogram replicate all the transitions taken by the main<br>one, but they only perform actions when ghost - main runs<br>the microinstructions that implement two specific AND-states:<br>beep-taste and run. All other microinstructions are idle mi-<br>croinstructions and are struck-through |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

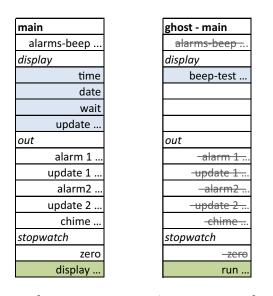

| 4.11 | Proposed microinstruction format showing $n + 1$ conditions<br>and $m + 1$ actions. The length of most fields depends on<br>the number of allowed counters, inputs and outputs; or the<br>maximum number of microinstructions in an <i>AND</i> -super-state.101                                                                                                                                                            |

| 4.12 | Example of a six-condition evaluation implemented as four-<br>condition microinstructions in two steps. Auxiliary states<br>eval_a and eval_notc are included to implement a larger<br>number of transitions than those directly supported by the                                                                                                                                                                          |

|      | format                                                                                                                                                                                                                                                                                                                                                                                                                     |

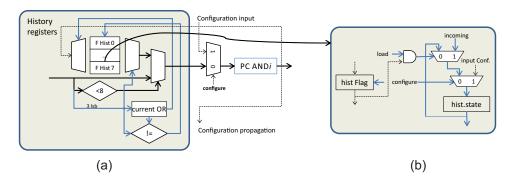

| 4.13 | History register and its connection to the PC, which is up-<br>dated when leaving the current OR-state. History is initial-<br>ized at configuration time as shown in part (b) of the figure. 105                                                                                                                                                                                                                          |

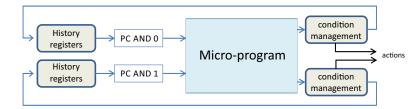

| 4.14 | Circuit that runs up to two AND-super-states. Dual port<br>memory is concurrently addressed by two PCs. Conditions<br>are evaluated and actions are taken independently for both<br>super-states. Transitions are refined using the history and<br>new values for the PC are produced every cycle 105                                                                                                                      |

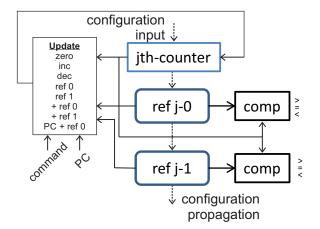

| 4.15 | Scheme of a counter. At configuration time an initial and ref-<br>erence values are loaded. The counter behaviour is controlled                                                                                                                                                                                                                                                                                            |

|      | by the active states                                                                                                                                                                                                                                                                                                                                                                                                       |

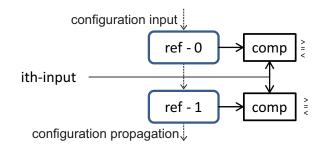

| 4.16 | Input comparison. At configuration time two reference values<br>are loaded. These values are used to calculate the current                                                                                                                                                                                                                                                                                                 |

| 4.17 | value with the reference ones during normal operation 107<br>Example of chaining eight conditions. Eventually, all the con-<br>ditions will activate only one output bit, which sets the tran-                                                                                                                                                                                                                             |

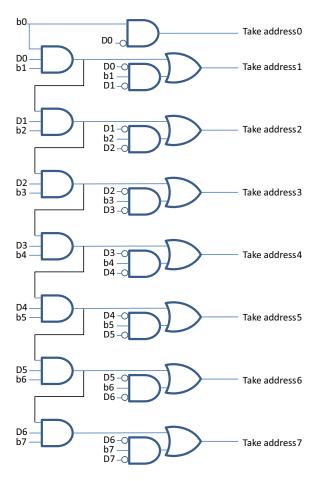

|      | sition that will take place                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 18 | Circuit for output selection. The selection value is retrieved                                                                                                                                                                                                                                                                                                                                                             |

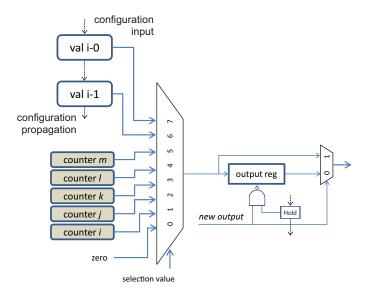

| 4.10 | from the active microinstructions                                                                                                                                                                                                                                                                                                                                                                                          |

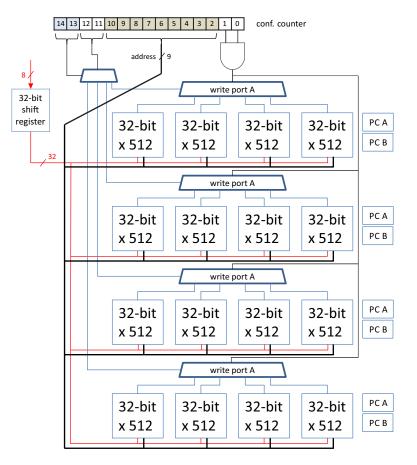

| 4.19 | Load of a microprogram with four rows of four blocks per row.                                                                                                                                                                                                                                                                                                                                                              |

| 1.10 | A simple configuration counter is used to load each word in                                                                                                                                                                                                                                                                                                                                                                |

|      | the right position, row and memory block                                                                                                                                                                                                                                                                                                                                                                                   |

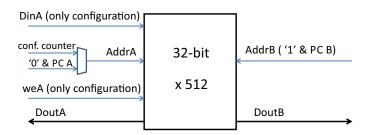

| 4.20 | Dual port memory block. Two AND-states may be addressed                                                                                                                                                                                                                                                                                                                                                                    |

|      | simultaneously using both ports                                                                                                                                                                                                                                                                                                                                                                                            |

xxii

| 4.21 | Example of microprogrammed organisation of states of the      |

|------|---------------------------------------------------------------|

|      | statechart in Figure 4.9. The dashed lines separate the AND-  |

|      | super-states. The leftmost one carries out most of the load,  |

|      | while its neighbour is mainly formed by ghost super-states    |

|      | with the exception of beep-test and stopwatch/run. The        |

|      | other five AND-super-states are very simple but, hierarchi-   |

|      | cally, are at the same level as the main ones                 |

| 4.22 | Micro-code example for two selected super-states. The for-    |

|      | mat supports up to six transitions and four actions. Some     |

|      | transitions are highlighted with arrows for the sake of clar- |

|      | ity. Condition-chaining bits are not shown. Both super-states |

|      | support history                                               |

|      |                                                               |

LIST OF FIGURES

xxiv

# List of Tables

| 1   | List of abbreviation used in this thesis                                   |

|-----|----------------------------------------------------------------------------|

| 3.1 | ESS data buffer item list                                                  |

| 4.1 | Comparison of the resource utilisation for the statechart in<br>Figure 4.1 |

| 4.2 | Comparison of the resource utilisation for the statechart in<br>Figure 4.9 |

| 4.3 | FPGA resources utilisation by our implementation of the dig-               |

| 4.4 | ital watch in Figure 4.9                                                   |

|     | Figure 4.1                                                                 |

| A.1 | ESS beam modes. Source: $[2]$                                              |

| B.1 | ESS beam destinations                                                      |

LIST OF TABLES

xxvi

# List of abbreviations

| Abbreviation         | Definition                                                               |

|----------------------|--------------------------------------------------------------------------|

| AC                   | Alternating Current                                                      |

| AMC                  | Advanced Mezzanine Card                                                  |

| API                  | Application Programming Interface                                        |

| ASIC                 | Application Specific Integrated Circuit                                  |

| ASIP                 | Application Specific Instruction Processor                               |

| BCM                  | Beam Current Monitor                                                     |

| CA                   | Channel Access                                                           |

| CERN                 | European Organization for Nuclear Research                               |

| CPU                  | Central Processing Unit                                                  |

| dBm                  | Decibel-milliwatt                                                        |

| DIN                  | Deutsches Institut für Normung (German organization for standardization) |

| DMSC                 | Data Management and Software Centre                                      |

| DOM                  | Document Object Model                                                    |

| DTL                  | Drift Tube Linac                                                         |

| EPICS                | Experimental Physics and Industrial Control System                       |

| ERIC                 | European Research Infrastructure Consortium                              |

| $\mathbf{ESS}$       | European Spallation Source                                               |

| EVG                  | EVent Generator                                                          |

| EVM                  | EVent Master                                                             |

| $\mathrm{EVR}$       | EVent Receiver                                                           |

| $\mathbf{FC}$        | Faraday Cup                                                              |

| $\operatorname{FEL}$ | Free Electron Laser                                                      |

| FIFO                 | First-In-First-Out                                                       |

| FMC                  | FPGA Mezzanine Card                                                      |

| F-O                  | Fan-Out                                                                  |

| FPGA                 | Field-Programmable Gate Array                                            |

| FRIB                 | Facility for Rare Isotope Beams                                          |

| $\mathbf{FSM}$       | Finite State Machine                                                     |

|                      |                                                                          |

| Abbreviation          | Definition                                      |

|-----------------------|-------------------------------------------------|

| FW                    | FirmWare                                        |

| $\operatorname{Gbps}$ | Giga bit per second                             |

| ${ m GeV}$            | Giga electron-volt                              |

| GPS                   | Global Positioning System                       |

| GSI                   | GSI Helmholtz Centre for Heavy Ion Research     |

| HDL                   | Hardware Description Language                   |

| HEBT                  | High Energy Beam Transport                      |

| Hz                    | Hertz                                           |

| IBM                   | International Business Machines corporation     |

| ICS                   | Integrated Control System                       |

| ID                    | IDentifier                                      |

| IFB                   | InterFace Board                                 |

| ILL                   | Institut Laue-Langevin                          |

| I/O                   | Input/Output                                    |

| ÍOC                   | Input/Output Controller                         |

| IT                    | Information Technology                          |

| J-PACR                | Japan Proton Accelerator Research Complex       |

| JTAG                  | Joint Test Action Group                         |

| KiB                   | Kibi Byte                                       |

| LCLS                  | Linac Coherent Light Source                     |

| $\operatorname{LEBT}$ | Low Energy Beam Transport                       |

| LED                   | Light-Emitting Diode                            |

| LLRF                  | low Level Radio Frequency                       |

| LPC FMC               | Low Pin Count FPGA Mezzanine Card               |

| LPF                   | Low Pass Filter                                 |

| LPS                   | Local Protection System                         |

| LUT                   | Look-Up table                                   |

| LVPECL                | Low-Voltage Positive Emitter-Coupled Logic      |

| mA                    | milli Ampere                                    |

| MByte                 | Mega Byte                                       |

| MCH                   | MicroTCA Carrier Hub                            |

| MEBT                  | Medium Energy Beam Transport                    |

| MeV                   | Mega electron-volt                              |

| MHz                   | Mega Hertz                                      |

| MPS                   | Machine Protection System                       |

| MRF                   | Micro-Research Finland                          |

| ms                    | milli second                                    |

|                       |                                                 |

| mTCA                  | Micro Telecommunications Computing Architecture |

xxviii

| Abbreviation         | Definition                                                               |

|----------------------|--------------------------------------------------------------------------|

| MW                   | Mega Watt                                                                |

| ns                   | nano second                                                              |

| NTP                  | Network Time Protocol                                                    |

| PBI                  | Proton Beam Instrumentation                                              |

| $\mathbf{PC}$        | Personal Computer or Program Counter                                     |

| PCI                  | Peripheral Component Interconnect                                        |

| PCIe                 | Peripheral Component Interconnect express                                |

| PD                   | Phase Detector                                                           |

| PL                   | Programmable Logic                                                       |

| PLA                  | Programmable Logic Array                                                 |

| PLC                  | Programmable Logic Controller                                            |

| $\operatorname{PLL}$ | Phase Locked Loop                                                        |

| PPS                  | Pulse Per Second                                                         |

| $\mathbf{PS}$        | Processing System                                                        |

| PTP                  | Precision Time Protocol                                                  |

| PV                   | Process Variable                                                         |

| RAM                  | Random Access Memory                                                     |

| $\operatorname{RF}$  | Radio Frequency                                                          |

| m RFQ                | Radio Frequency Quadrupole                                               |

| RMS                  | Root Mean Square                                                         |

| RTM                  | Rear Transition Module                                                   |

| SCSI                 | Small Computer System Interface                                          |

| $\operatorname{SFP}$ | Small Form-factor Pluggable                                              |

| $\operatorname{SLS}$ | Swiss Light Source                                                       |

| SNS                  | Spallation Neutron Source                                                |

| $\operatorname{SoC}$ | System-on-Chip                                                           |

| $\mathrm{TTL}$       | Transistor-Transistor Logic                                              |

| UK                   | United Kingdom                                                           |

| UML                  | Unified Modeling Language                                                |

| USA                  | United States of America                                                 |

| UTC                  | Coordinated Universal Time                                               |

| $\mu TCA$            | Check mTCA                                                               |

| VCO                  | Voltage-Controlled Oscillator                                            |

| VHDL                 | VHSIC (Very High Speed Integrated Circuit) Hardware Description Language |

| VME                  | Versa Module Eurocard                                                    |

| XML                  | Extensible Markup Language                                               |

|                      |                                                                          |

Table 1: List of abbreviation used in this thesis.

xxix

LIST OF ABBREVIATIONS

xxx

## Chapter 1

## Introduction

Making new science and developing better engineering practises is becoming more and more complex each day, with better, bigger, more powerful and more efficient experiments and machines being needed to reach new grounds, as current ones are reaching their limits. One example is the biggest machine in the world, the Large Hadron Collider at CERN, the European Organization for Nuclear Research located in Geneva, which intends to go beyond our current understanding of Physics and for that it needs more energetic collisions, and thus a larger diameter to minimize synchrotron radiation [3]. Other example is the fusion nuclear reactor ITER in France, which intends to be the first fusion device to produce a ten-fold return on energy (Q=10) [4] and thus be efficient enough for commercial use.

These industrial and scientific facilities require for their operation reliable, state-of-the-art control systems, which get more sophisticated as the complexity of the systems or devices they manage increases. These control systems are intricate networks that comprise hardware, software and their respective configurations, and that are integrated together to successfully run the machine or facility. It is of uttermost importance that all configurations are implemented in a flexible and error-free manner, since the increasing sophistication of the control systems brings out any issue or defect with harmful consequences. For this reason it is becoming more and more prevalent the use of tools that automatize and simplify the process of designing, implementing and integrating control systems, providing safer, more reliable and more flexible systems for better industrial and scientific facilities.

Figure 1.1: (a) Buddha sculpture, (b) X-ray image, (c) neutron image. Source [1].

## **1.1** Neutrons for science

Neutrons are a very powerful and extensively used tool for researching and understanding the internal structure of matter and the properties and composition of materials. Neutrons have some special characteristics, such as the possibility of matching their energy and wavelength scale to atomic and molecular processes, or using them as weakly coupled probes, as they can penetrate deeply and harmlessly in the sample being studied. They are also very sensitive to hydrogen, allowing the study of the structure and dynamics of organic matter, such as polymers and biological matter [5]. Usually a beam of neutrons is used to probe a small sample under study. The sample scatters the neutron beam in a specific way that allows scientist to obtain information, for example the scattering pattern can produce an image of the atomic structure. Among the applications of neutron scattering are clean energy and the environment, pharmaceuticals, healthcare, nanotechnology, materials engineering, fundamental physics, IT, biochemical engineering, food science, drug synthesis and biophysics [6]. Figure 1.1 shows a Buddha sculpture studied under two different techniques: X-ray and neutrons, where it is possible to notice the difference in the output between the two methods.

There are two main kinds of neutron sources: continuous and pulsed sources. The most common type of continuous sources are nuclear reactors that produce a continuous flux of neutrons, such as the Institut LaueLangevin (ILL) [7] in Grenoble, France. Pulsed sources, on the other hand, trigger the emission of neutrons from a target at a certain repetition rate. Spallation sources, which are pulsed sourced, use a high power proton beam, exceeding 1 MW, to hit a metal target and destabilise its atoms, which then emit neutrons. Examples of spallation sources are Spallation Neutron Source (SNS) [8] in Oak Ridge National Laboratory (USA), Japan Proton Accelerator Research Complex (J-PARC) [9], or the European Spallation Source (ESS) in Sweden.

#### 1.1.1 The European Spallation Source ERIC

ESS is an European Research Infrastructure Consortium (ERIC) with 13 European members, including the host nations of Sweden (where the ESS facility is being built) and Denmark (where the Data Management and Software Centre (DMSC) will be located) [10]. The construction of ESS started in 2014 in Lund, southern Sweden, and should be operational at full performance in 2025 [11]. The production of neutrons happens thanks to two big different parts:

- A proton linear accelerator, which will be the most powerful linear proton accelerator ever built [10]. It will produce a 5 MW, 2.86 ms long beam of protons at 2 GeV, which will hit the target with a repetition rate of 14 Hz. The average pulse current is 62.5 mA [11]. It will have a normal conducting section consisting of a Radio Frequency Quadrupole (RFQ) and a Drift Tube Linac (DTL) that accelerates the beam produced by the proton source, with a Low Energy Beam Transport (LEBT) and Medium Energy Beam Transport (MEBT) in between the different systems. The normal conducting section will accelerate the beam up to 90 MeV, most of the acceleration will be achieved in superconducting cavities: spoke cavities up to 200 MeV, medium- $\beta$  cavities up to 570 MeV and high- $\beta$  up to the final 2 GeV. The normal conducting linac and spoke cavities will be fed by a 352.21 MHz radio-frequency (RF), and the rest of the cavities by 704.42 MHz. Finally a High Energy Beam Transport (HEBT) will drive the beam to the target. Figure 1.2 shows a diagram of the accelerator.

- A five-tonne helium-cooled target wheel, where the spallation process takes place, converts the proton beam into slow neutron beams. Due to the low efficiency of the process, a great flux is needed for the experiments, which drives the requirements for the accelerated proton

Figure 1.2: ESS linac layout. Source: ESS.

beam and its high power. Most of the 5 MW beam power will be dissipated as heat in the target, which will be located inside a 6000 tons shielding monolith [11].

The neutrons produced by the spallation process need to be moderated to extract the useful slow neutrons, which will be guided to 22 neutron instruments, each of them with a specific purpose and characteristics. The data generated by the instruments will be sent across the Öresund strait to the DMSC at the University of Copenhagen, in the Nørre campus.

ESS is a collaboration facility where the member states support the ESS project mainly through in-kind projects by providing systems which are engineered, designed and built in the members' homeland, and that are later shipped and installed locally at ESS. Meanwhile the host members of Sweden and Denmark provide most of the cash needed.

## 1.2 Controls and timing at ESS

The ESS Integrated Control System (ICS) is used in all parts of ESS: accelerator, target, instruments and conventional facilities. The software toolbox that was decided to be used is the *Experimental Physics and Industrial Control System* (EPICS) [12]. EPICS is an open-source environment developed by a collaborative community for developing and implementing real-time distributed control systems for big research centres and industry. It is widely used in particle accelerators, large telescopes and other experiments. It was developed to implement systems with a big number of computers linked by network, and it provides monitoring, interactivity, data archiving and control among other scientific applications. Communication is done following a distributed client-server model, where all nodes can act as client or server depending on the requirements. EPICS uses a special protocol called *Channel Access* (CA), that all nodes in the system use; the nodes are called *Input/Output Controllers* (IOCs). The new version 4 of EPICS extends its

### 1.2. CONTROLS AND TIMING AT ESS

functionality and adds better features and support.

ESS will use hardware based on its applications split in three layers [11]: slow industrial automation based on Programmable Logic Controllers (PLCs) for slow, reliable input/output (I/O); distributed I/O based on the EtherCAT standard [13] with real-time capabilities for applications with moderate data rates; and fast applications. The fast applications need real-time processing in the megahertz level, with data rates of hundreds of MBytes per second and early processing. For this applications the  $\mu$ TCA or MicroTCA (MTCA.4) [14] standard was chosen. One of the systems that are critical for the fast applications at ESS, and every accelerator or research centre in general, is the timing system. Its main purpose is to provide synchronization of several systems accross the facility the facility, which includes triggering devices at the specific time needed for the correct operation of the machine (usually with a configurable delay from a common source), providing synchronized clocks for data sampling and distributing other information reliably [15]. All of this must be achievable with tight requirements on drift and jitters, usually in the range of few ns, or even subns for the clocks. Due to these requirements on stability and reliability the timing signals are usually implemented in hardware, while being controlled, managed and read from the control system.

The timing system is not only needed to synchronize the operation of all the different systems but also to set a common time-reference for the entire facility and guarantee that all acquired data and control signals can be correlated with coherent timestamps. The most common way to achieve this is by having a master that sends its local time and other related information across the facility through a dedicated timing network to a series of timing slaves or receivers that synchronize their internal time to the received one. There are two main timing system paradigms [16]:

- Time-based timing systems: in a time-based timing system the master, once the slaves have locked their internal time to that of the master, broadcasts messages with instructions expected to be performed at specific times. Then the slaves use their local time, derived from the master's, to know when to generate the requested triggers and signals.

- Event-based timing systems: in an event-based timing system the master is the one that waits until the requested time to broadcast events to the slaves, which react immediately as they are configured to. In this paradigm, an *event* is just an enumerated pulse signal that triggers

actions in the slaves. ESS uses an event-based timing system whose implementation will be discussed in this work.

Usually timing systems combine both paradigms, where each of them has obvious advantages: an event-based system can very easily drive actuators, especially when the timing system needs to react immediately or with low latency to external conditions. On the other hand knowing or being able to know the expected actions and times well in advance can help lowering the network traffic when a lot of actions are expected in a short time. Having a common time-reference for all the nodes in the system is needed in both paradigms for timestamping acquired data. It is worth noting that timebased systems with short deadlines between the broadcast of messages and the requested time of reaction is for most effects indistinguishable from a event-based system [16].

## **1.3** About this thesis

In this work we describe the technical implementation of the ESS timing system, in order to guarantee a common time reference for the facility, use coherent timestamps and synchronise the operation of all parts of the facility. This includes the explanation of the timing system from its fundamental working pieces, the design of a structure which allows the timing system to interface all the ESS subsystems that require synchronisation and the integration of the timing system in the ESS control system. It also includes a discussion about the synchronisation of the ESS facility.

This thesis is divided as follows: the present Chapter 1 gives an introduction about the ESS facility, the control system, a general presentation of timing systems and the scope of the work. Chapter 2 is concerned about the challenge of synchronising large facilities such as ESS, the ESS timing system is introduced in detail and explains the strategy to deal with the synchronisation challenge. Chapter 3 presents new developments in the technical implementation of the timing system at ESS and its integration in the ESS control system, both at low level and at EPICS level, and provides a description of the synchronisation strategy at ESS. Chapter 4 presents a new tool to quickly deploy FPGA systems automatically built from a high level graphical user interface description, and an alternative way to implement the same high level graphical user interface description as microprograms in FPGA-based systems. Finally, Chapter 5 presents the conclusions of this

# 1.3. ABOUT THIS THESIS

work and summarises the next steps in the project.

# Chapter 2

# The ESS timing system

# 2.1 Synchronization