University of Nebraska at Omaha DigitalCommons@UNO

Student Work

12-1-1999

## A Genetic-Based Approach to Multi-layer Channel Routing In VLSI Design.

Mark P. Cloyed

Follow this and additional works at: https://digitalcommons.unomaha.edu/studentwork

#### **Recommended Citation**

Cloyed, Mark P., "A Genetic-Based Approach to Multi-layer Channel Routing In VLSI Design." (1999). Student Work. 3586.

https://digitalcommons.unomaha.edu/studentwork/3586

This Thesis is brought to you for free and open access by DigitalCommons@UNO. It has been accepted for inclusion in Student Work by an authorized administrator of DigitalCommons@UNO. For more information, please contact unodigitalcommons@unomaha.edu.

# A Genetic-Based Approach to Multi-layer Channel Routing In VLSI Design

A Thesis

Presented to the

Department of Computer Science

And the

Faculty of the Graduate College

University of Nebraska at Omaha

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

University of Nebraska at Omaha

By

Mark P. Cloyed

December 1999

UMI Number: EP74785

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI EP74785

Published by ProQuest LLC (2015). Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

#### **Thesis Acceptance**

Acceptance for the faculty of the Graduate College, University of Nebraska, in partial fulfillment of the requirements for the degree of Master of Science, University of Nebraska at Omaha.

٠.

Committee

Name

Department

Computer Science Hes zacmanesh Az duran Electron

TT

Chairman

. 11/29/99

Date

#### A Genetic-Based Approach

#### To Multi-layer Channel Routing in VLSI Design

Mark P. Cloyed

University of Nebraska at Omaha, 1999

Advisor: Dr. Hesham H. Ali

As our reliance on electric and electronic devices increases, the need to improve the design and manufacture of integrated circuits (ICs) grows. A microchip can be bettered if it can be made more powerful, smaller, cheaper, and/or more easily manufactured. The physical design phase of chip manufacture offers significant room for improvement.

This thesis intends to investigate the detailed channel routing phase of VLSI physical design. Channel routing has been seen to be intractable, in that an optimal solution may require too much time for calculation. Constraints severely limit many algorithms to an approximate solution. The heuristics developed thus far have fallen short of an optimal solution for similar reasons.

This thesis presents an evolutionary approach to channel routing. A genetic algorithm makes use of a parent solution to derive next generation solutions in an attempt to overcome local minimums. A three-layer approach is used to evaluate the use of various layering schemes, and also to reduce the number of constraints involved. When multiterminal nets or multi-nets are involved, a division parameter is used to determine if the best results are generated by treating the multi-net as a whole, or broken down into as small as two-terminal nets. A greedy approach is used to generate the original parents, and a compaction algorithm is used to further improve the output. The results are then represented three-dimensionally by a computer-aided design program, where it can be analyzed for accuracy.

| Thesis Acceptance I                                        |

|------------------------------------------------------------|

| AbstractII                                                 |

| Chapter 1 Introduction1                                    |

| 1.1 The History of VLSI Development1                       |

| 1.2 Previous Approaches to Channel Routing4                |

| 1.3 What Has Been Lacking                                  |

| 1.4 Project Identification                                 |

| 1.5 Expected Results10                                     |

| 1.6 Thesis Organization                                    |

| Chapter 2 Defining the Problem and Its Terminology         |

| 2.1 An Overview of Channel Routing12                       |

| 2.2 Definition of Terminology13                            |

| 2.3 Problem Formulation                                    |

| 2.4 Input Analysis                                         |

| 2.5 Summary                                                |

| Chapter 3 An Overview of Prior Research in Channel Routing |

| 3.1 Two Layer Approaches                                   |

| 3.1.1 The LEA Family of Algorithms                         |

| 3.1.2 The Dogleg Router                                    |

| 3.1.3 The Net Merge Router                                 |

| 3.1.4 Yet Another Channel Router                           |

## Table of Contents

| 3.1.5 The Greedy Channel Router27                                        |

|--------------------------------------------------------------------------|

| 3.1.6 The Hierarchical Method28                                          |

| 3.1.7 The Genetic Algorithm                                              |

| 3.2 Three-Layer Approaches                                               |

| 3.2.1 The Extended Net Merge and CWL Channel Routers                     |

| 3.2.2 The Hybrid HVH-VHV Router                                          |

| 3.3 Summary                                                              |

| Chapter 4 The Genetic Algorithm                                          |

| 4.1 An Overview                                                          |

| 4.2 How the Genetic Algorithm Works                                      |

| 4.3 The Mutation Process                                                 |

| 4.4 The Selection Process                                                |

| 4.5 Global Control Parameters                                            |

| Chapter 5 The Multi-layer Channel Router41                               |

| 5.1 The Basis for the Router Process41                                   |

| 5.2 Data Structures Used44                                               |

| 5.3 Process Elaboration46                                                |

| 5.3.1 Creating Nets47                                                    |

| 5.3.2 Finding the Maximum Clique48                                       |

| 5.3.3 Evaluating the Vertical Constraints, Cycles and the Longest Path49 |

| 5.3.4 Creating Parent Solutions                                          |

| 5.3.5 Improving the Solution by Compaction                               |

| 5.3.6 Expressing the Value of the Solution      | 56 |

|-------------------------------------------------|----|

| 5.3.7 The Mutation Phase                        | 58 |

| 5.3.8 Choosing New Parents                      | 60 |

| 5.3.9 The Reporting Mechanism                   | 61 |

| 5.4 The Main Process                            | 63 |

| 5.5 Generating a Graphic Output                 | 64 |

| Chapter 6 Experimental Results                  | 67 |

| 6.1 The Problem Sets Used                       | 67 |

| 6.2 Separation Value                            | 70 |

| 6.3 The Control Parameter p0                    | 73 |

| 6.4 The Generation Size                         | 75 |

| 6.5 The Control Parameter R                     | 76 |

| 6.6 Using Elite Mode                            | 77 |

| 6.7 Two-Layer Versus Three-Layer Analysis       | 79 |

| 6.8 Time Complexity                             | 81 |

| 6.8.1 Time Complexity of the Analysis Phase     | 81 |

| 6.8.2 Time Complexity of the Parent Creation    | 82 |

| 6.8.3 Time Complexity of the Genetic Algorithm  | 83 |

| 6.9 Comparing the Parents to the Final Solution | 84 |

| 6.10 General Observations                       | 85 |

| Chapter 7 Conclusions                           | 87 |

| 7.1 A Recap of the Benefits                     | 87 |

| Appendix A: Source Code            | 92 |

|------------------------------------|----|

| Bibliography                       | 90 |

| 7.3 Directions for Future Research | 89 |

| 7.2 Positive and Negative Effects  | 88 |

## List of Figures

| Figure 1.1 The I | Design Cycle of VLSI                    | 2  |

|------------------|-----------------------------------------|----|

| Figure 1.2 The I | Physical Design Process                 | 3  |

| Figure 2.1 Typic | cal Channel Layout                      | 13 |

| Figure 2.2 Track | k and Vertical Layout                   | 15 |

| Figure 2.3 Deter | rmining the Maximum Clique from the HCG | 16 |

| Figure 2.4 Deter | rmining the Longest Path from the VCG   | 18 |

| Figure 2.5 Ident | tifying Cycles in the VCG               | 19 |

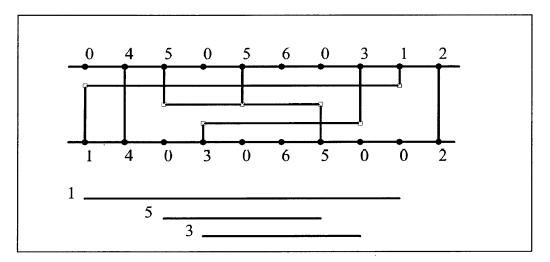

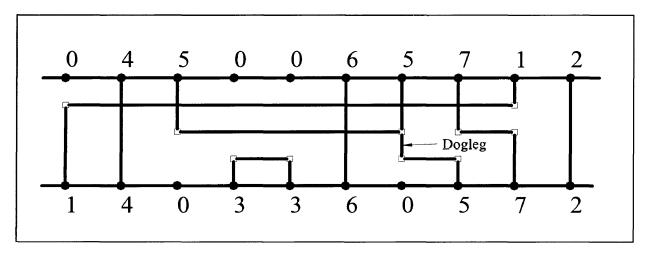

| Figure 3.1 An E  | Example of the Left-Edge Algorithm      | 23 |

| Figure 3.2 The I | Dogleg Routing Algorithm                | 24 |

| Figure 4.1 The G | Genetic Algorithm                       |    |

| Figure 4.2 Muta  | ation by Switching                      |    |

| Figure 4.3 Muta  | ntion by Crossover                      | 36 |

| Figure 4.4 Muta  | tion by Inversion                       | 37 |

| Figure 5.1 Struc | cture for the Basic Net Storage         | 42 |

| Figure 5.2 HVH   | I Layering Model                        | 42 |

| Figure 5.3 VHV   | ' Layering Model                        | 43 |

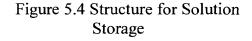

| Figure 5.4 Struc | ture for the Solution Storage           | 45 |

| Figure 5.5 Net C | Creation                                | 47 |

| Figure 5.6 Maxi  | mum Clique                              | 49 |

| Figure 5.7 Creat | ting the Vertical Constraint Graph      | 50 |

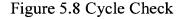

| Figure 5.8 Cycle | e Check                                 | 51 |

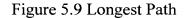

| Figure 5.9 Longest Path                                                             |

|-------------------------------------------------------------------------------------|

| Figure 5.10 Making the Parent Solutions53                                           |

| Figure 5.11 Checking for Free Space53                                               |

| Figure 5.12 The Compaction Algorithm55                                              |

| Figure 5.13 The Expansion Algorithm55                                               |

| Figure 5.14 The Costing Algorithm57                                                 |

| Figure 5.15 Counting Vias58                                                         |

| Figure 5.16 Performing Mutation59                                                   |

| Figure 5.17 The Sorting Algorithm61                                                 |

| Figure 5.18 The Output Algorithm62                                                  |

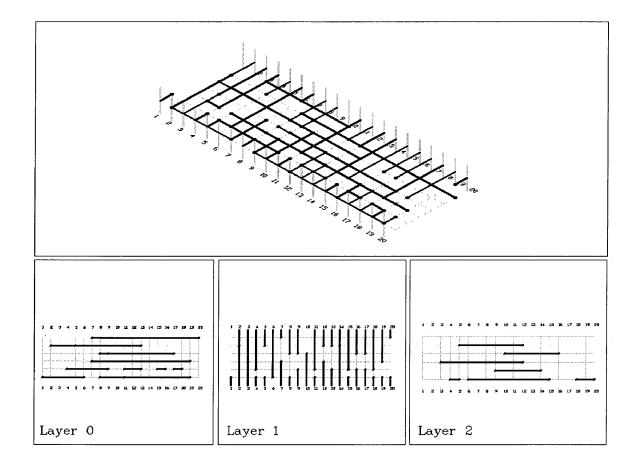

| Figure 5.19 AutoCAD <sup>®</sup> Output Screen Showing Track and Layer Assignment65 |

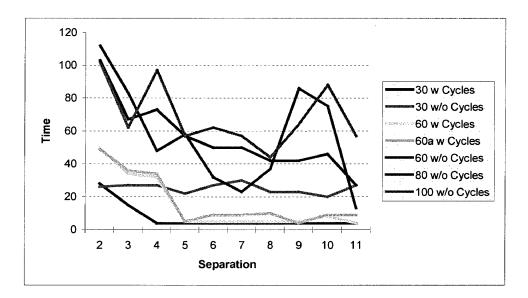

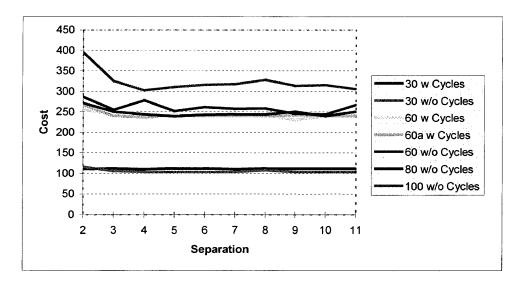

| Figure 6.1 The Effect of Separation on Time69                                       |

| Figure 6.2 The Effect of Separation on Cost70                                       |

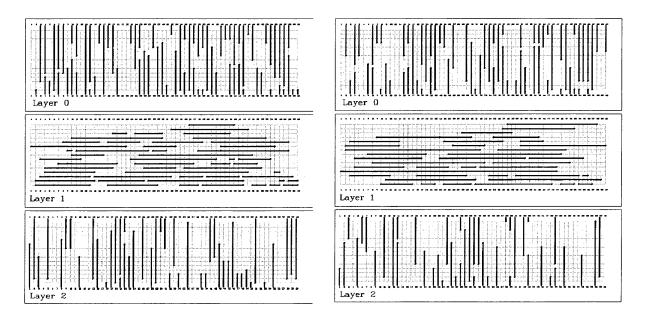

| Figure 6.3 Outputs Based on Separation71                                            |

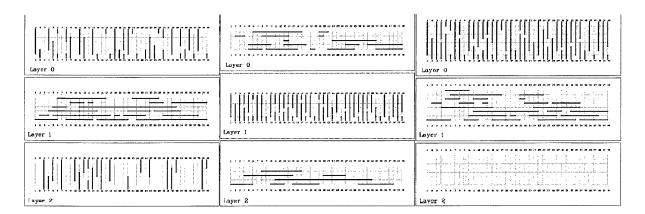

| Figure 6.4 Layering Modes for 40 Terminal Problem Set                               |

## List of Tables

| Table 6.1 Definition of Problem Sets    68                        |  |

|-------------------------------------------------------------------|--|

| Table 6.2 Characteristics of 40 Terminal Problem Sets    69       |  |

| Table 6.3 Comparison of Separations of 2 and 4                    |  |

| Table 6.4 Time and Cost on 40 Terminal Sets with Separation       |  |

| Table 6.5 Best p0 Values                                          |  |

| Table 6.6 Effect of p0 on the 40 Terminal Problem Sets            |  |

| Table 6.7 The Effect of Generation Size on Cost and Time       75 |  |

| Table 6.8 The Effect of R on the Cost    77                       |  |

| Table 6.9 Effect of Elite Mode on Cost and Time    78             |  |

| Table 6.10 Analysis of Layer Mode on the 40 Terminal Problem Sets |  |

| Table 6.11 Comparison of Greedy and Genetic Algorithms            |  |

### Chapter 1

## Introduction

#### **1.1 The History of VLSI Development**

The development of the integrated circuit has changed dramatically over the last thirtyfive years. Integrated circuits (ICs) have affected electronic and electrical device production in almost all facets of life. Circuit designs have changed from as small as 1000 circuits in a chip during 1965, to as many as five and one half million transistors during 1995. The potential exists to create a chip with over a billion transistors in the next 10 to 15 years. There can be seen several levels of integration from Small Scale Integration, using typically as many as 20 gates per chip, to Medium Scale Integration, incorporating as many as 200 gates per chip. Large Scale Integration normally involves as many as 5000 gates, while Very Large Scale Integration (VLSI) incorporates over 5000 gates per chip. VLSI design is now the largest part of production and research.

The physical design process for VLSI design involves multiple layers of metal oxide and silicon insulator, arranged on a silicon wafer in such a way to form gates, transistors, and circuits. An on-going limitation is the precision available in manufacturing, which limits the size of the smallest feature within the chip. An additional issue to be researched, is the increasing complexity of circuitry. As the feature size is reduced, either the chip size can be reduced, or there is the availability of more circuitry per chip. The latter requires

more time and effort to design and test. Changes in technology and types of materials used in the chip design can facilitate small changes in the precision size, which increases the complexity of the circuit design process. This design process deserves further investigation, because improvements to it can reduce the time from conception to market delivery.

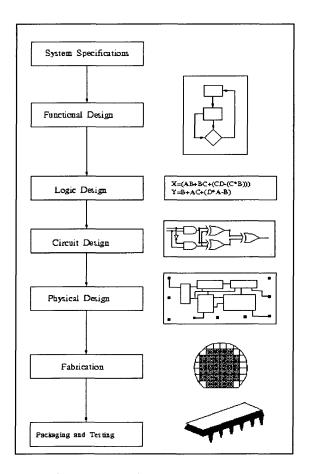

The design process is shown in Figure 1.1. It begins with the system specification. In this phase, the function of the circuit is determined in general terms. From the system specification, a functional design of the circuitry is created. This is done in terms of a flow chart of the steps needed to perform the function. The functional design then leads to the logic design. In this phase, the flow chart is converted into an algebraic expression that represents the output from the process. The circuit design phase follows, in which the algebraic

Figure 1.1 The Design Process

equation is analyzed and processed into a logic gate representation of the circuit. After the circuit has been laid out, the physical design phase takes the circuit design, and processes it into the physical layout of predefined circuit blocks and the connection leads between those blocks. Finally, the fabrication cycle or phase implements this physical design into a set of chips that are then packaged and tested for accuracy before finally shipping to their ultimate destination.

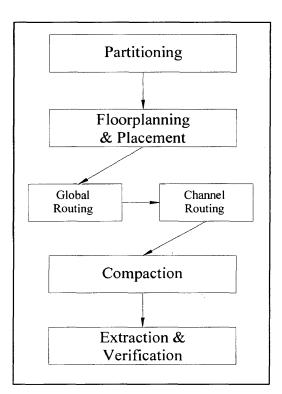

The physical design process, as figure 1.2 shows, can be broken down into the following stages: First, the circuits are partitioned into blocks. Because of the nature of VLSI design and the large number of gates involved, it is impossible to work with all of them at one time. The gates are partitioned into small enough blocks to make them manageable. After the partitioning has been determined, the floorplanning and placement stage is performed. In this stage, the gates are arranged in such a way so that they are closest to the

Figure 1.2 Physical Design

gates to which they will be interconnected. After the floorplanning and placement stage is accomplished, the routing stage begins. The routing stage occurs on two levels. The circuit is first globally routed to define the major circuits that will connect the different blocks and gates together. This is performed in general terms, following which the channel routing is performed. In the channel routing phase, the circuits, or nets, are given specific locations between chips or between blocks to connect the different blocks together. Each connection requires a specific amount of space to make those connections, without interfering with other circuits in the area. After the channel routing, the compaction phase looks for unused areas of the layout, in an attempt to reduce the overall chip size. Finally, the chip enters an extraction and verification stage, where the chip is checked for design rule accuracy of the circuits. The circuit is checked to make sure it falls within fabrication limitations.

Each phase of the physical design process is computationally intense, and so improvements can yield significant benefits. The focus of this thesis is in the channel routing phase. Channel routing has been proven to be an NP-complete problem, meaning that no single algorithm has been found that handles all situations to provide an optimal solution. With these points in mind, we offer a multi-layer channel routing algorithm. It is intended to accept, as input, a wide range of problem sets, and return as output a near-optimal solution for the routed nets. We must first look at the previous approaches that have been taken in trying to solve this problem.

#### **1.2 Previous Approaches to Channel Routing**

Various approaches have been taken to resolve the channel routing problem. The problem is of an intractable nature, as an optimal solution is not always practical. In some instances, an optimal solution requires too much time and can be very computationally complex. Constraints can also cause optimal solutions to fail. Heuristics have been developed to try to find a reasonable solution, but tend to have problems falling into local minimums. In 1971, Hashimoto and Stevens proposed the Left-Edge algorithm [HS71], which organized the nets in order of ascending left node, then used a type of greedy algorithm to assign nets to specific locations. Deutsch offered a dogleg router algorithm [DD76]. A dogleg is a vertical segment connecting two horizontal net segments. In this algorithm, analysis begins at either end of the channel, with doglegs allowed between multi-terminal nets, to reduce track width. A multiterminal net, or multi-net as it will be referred to, is a set of three or more pins requiring a connection between all of them.

More recently, Yoshimura and Kuh offered a net merge channel router, called the YK algorithm, which partitioned the connection region, or channel, into zones, and then routed each zone [YK82]. The nets of adjacent zones are combined to create a composite net that could be placed in a track. Reed, Sangiovanni-Vincentalli, and Santamauro proposed the YACR2 (Yet Another Channel Router) algorithm that made use of vacant columns, and tracks to resolve vertical constraint violations [RS85]. The greedy channel router was developed by Rivest and Fiduccia to assign tracks to the nets column by column, from left to right [RF82]. Its intent was to reduce track width, allow doglegs in any column, and combine split horizontal nets where convenient. Burstein and Pelavin offered an algorithm based on a hierarchical method [BP83]. The nets are routed globally in the channel, and then the channel is repeatedly divided into smaller sections to be rerouted as necessary to better define the track assignments.

Last year, Jingsen Zheng offered an evolution-based, or genetic, algorithm for two layer channel routing [ZJ98]. In his graduate thesis, he presented a process that made use of interim solutions to evolve new solutions. The intent was to overcome local minimums by accepting less than optimal solutions as interim steps working toward an optimal solution.

#### **1.3 What Has Been Lacking**

Prior solutions to the channel routing problem have been inconclusive. Optimal algorithms can not handle constrained situations, or can take too much time to process when evaluating large data sets. An evaluation of the heuristic algorithms reveals their shortcomings. Several do not support doglegs or cyclic vertical constraints. This leads to a channel width that is wider than necessary. Some algorithms give solutions with excessive doglegs and vias, while others can be rather complicated to implement.

The genetic algorithm is of special interest, as it is the basis for this thesis. We are extending the work of Zheng in his thesis, on an evolution-based two-channel router. Zheng indicated the problems he encountered with the genetic algorithm [ZJ98]. Horizontal and vertical constraints posed the greatest challenge to overcome. The longest path, as defined in the vertical constraint graph (VCG) can also affect the time required to find a solution. Breaking down multi-nets into two-terminal nets was beneficial in some cases, but detrimental in others. He also indicated that the technique used to create the

initial populations also played a part in the time required to derive a solution, and in the quality of that solution.

All of these shortcomings help to point out that the channel routing issue is not a simple one. The heuristics can have difficulty escaping from local optimums. This sets the stage for less than optimal results. If we can reduce the constraints surrounding a routing situation, we can more easily and more accurately route the channel with a minimum track width. If we can escape from local optimums, we may be able to derive a more optimal solution.

#### **1.4 Project Description**

It is the intent of this thesis to evaluate alternative methods of channel routing. This phase of VLSI design is known to be NP-complete, in that there is not a general solution available that is optimal and can be performed in a reasonable amount of time for all situations. There have been many heuristics proposed, but they have been seen to be too narrow in scope or take too much time to process the input. Heuristics also tend to involve too many constraints, which can affect the output dramatically.

We intend to extend upon the work that Jingsen Zheng presented in his thesis on an evolution-based approach to channel routing. In this thesis, we will investigate the effect of several factors on the channel routing question to allow for a more optimal solution.

- A three-layer approach

- A separation parameter, used to break multi-nets into smaller sub-nets

- The value of the parameter used in selecting valid solutions,  $p_{\theta}$

- The value of the variable used to define the termination point, **R**

- Using an 'elitist mode' in selecting interim solutions

- The effect of the generation size, or number of children generated by a parent solution

An evolutionary approach is still employed. We will use a three-layer approach, as the latest developments in VLSI have allowed a third layer for circuitry. With this additional layer, we have the ability to evaluate an HVH (horizontal-vertical-horizontal) layering scheme and compare it to a VHV (vertical-horizontal-vertical) layering scheme. These three-layer approaches can also be compared to the two-layer approach previously used. We intend to use an array to maintain our list of net segments' parameters, and another array to store the track and layer onto which each net segment is assigned. This would allow the use of doglegs in the channel routing.

A separation parameter will be employed to divide multi-nets into smaller network sections. Using this parameter, we can evaluate a multi-net in its complete form, and in smaller sections, with the two-terminal net as a lower bound. This separation parameter can be adjusted to break the multi-nets into smaller multi-nets to fine-tune the output. We would like to see how this parameter affects the overall solution. The values of two control parameters,  $p_0$  and R, determine which solutions are kept to be parents for succeeding generations, and what the point of termination should be, respectively. In evaluating which solutions to keep, two final selection methods can be incorporated. In an elitist mode, only the top solutions are retained to create future generations. In a non-elitist mode, a random sample of the solutions is kept to become parents. The number of children derived from each parent can also affect the quality of the solution, as well as the time required to process the problem set.

A greedy routine will be used to create the initial populations. In this approach, the nets are placed in the channel in a 'first come, first served' basis. The first net is randomly chosen, and then the nets are processed in order to place them in the layers and tracks, based on their terminal placement. Nets that have both terminals located on the top of the channel will naturally be placed toward the top of the channel and those with both terminals on bottom will be placed toward the bottom of the channel. This should give better initial populations, so that the evaluation will be more robust, and hopefully allow more time to overcome local optimums.

We also intend to incorporate a compaction phase in the circuit design. As the tracks undergo mutation, the compaction phase will help further reduce the track width. In evaluating the feasibility of the generation, a costing formula will be employed with weights for horizontal and vertical violations as well as the track width. Finally, the results of the channel routing algorithm will be used as input to AutoCAD<sup>®</sup>, a computer-aided design program. A three-dimensional representation of the channel routing will be generated, which can be viewed and rotated to check for accuracy and to analyze it to determine whether it approaches an optimal solution.

#### **1.5 Expected Results**

By employing an evolutionary or genetic approach to channel routing, we allow some less than optimal solutions as interim generations. The advantage to including these solutions is that it allows the algorithm to mutate that solution into a possibly better overall solution than is currently thought to be 'best'. Using this approach, we can attack the problem from different angles, so as to avoid falling into a local minimum that in itself tends to only offer a poorer solution when trying to improve upon it.

By including a third metal layer in the evaluation, we take advantage of several things. First of all, we have the ability to reduce the track width to as much as half of the twochannel version. This can lead to a smaller chip design and possibly less wire length. Secondly, we also have the ability to remove vertical constraints from the picture. By using a VHV layering model, we can route all net nodes efficiently where before a vertical constraint would force more track width to allow room to overcome the constraint. By using a separation parameter, to adjust how we handle multi-nets, we should be able to better minimize track width by the inclusion of doglegs. We can also evaluate the option of handling a multi-net as one large net versus several smaller nets. We expect to find a middle ground that better optimizes the solution, but doesn't run into the extended time constraints required for a large number of two-node nets to be processed. Lastly, incorporating a compaction phase helps to keep the intermediate solutions from having excessively wide tracks with significant amounts of unused track space.

#### **1.6 Thesis Organization**

In this thesis, we will define the problem at hand, including definitions as they apply to channel routing. In chapter two, the basic terminology will be identified, as well as the use of graph models to evaluate the conditions for the routing necessary. The objectives of minimizing channel width and connections, and eliminating constraints, will be detailed, as well. Chapter three provides an overview of the previous work done in the study of channel routing from a two-layer and a three-layer aspect. An overview of the genetic algorithm will be presented in chapter four, followed by an explanation of the genetic algorithm for the multi-layer channel router in chapter five. Chapter six discusses an analysis of the experimental results, as well as the performance of this algorithm. Finally, in chapter seven, conclusions are offered, as well as possible options for future research. We must next define the problem and the terminology used in the discussion of channel routing.

### Chapter 2

## Defining the Problem and Its Terminology

#### 2.1 An Overview of Channel Routing

As mentioned in the previous chapter, the problem of channel routing is difficult at best. To further analyze the problem, we must first look at the task at hand. The blocks of circuits have been physically arranged, relative to each other, and the interconnections between the various blocks have been identified. The floorplanning and placement stage has allotted areas between these blocks that are to be used to route the interconnections between circuits. These areas are divided into rectangular regions, and those regions are evaluated. The regions that have a circuit block on opposing sides are known as the 'channels'. Two-dimensionally speaking, channels can exist both horizontally and vertically, but they are analyzed in the same fashion, without a loss of generality. A region having circuit blocks on all sides is called a switchboxes, which have circuitry on all six sides. Switchbox routing requires special analysis, and is beyond the scope of this thesis, so we will limit our discussion to channel routing.

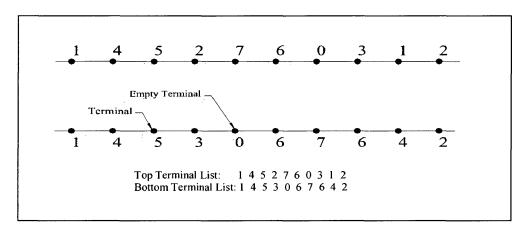

The channel is defined by the terminals along its opposing sides. Our evaluations will be made on channels arranged in a horizontal orientation, with the terminals located along the top and bottom of the channel. The various parts of the channel can be identified in figure 2.1. The channel has its top and bottom row of terminals, with the terminals numbered to identify their interconnections. These interconnections, or nets, are the elements we must arrange in an orderly fashion. All pins marked with the number one are to be connected, as are the pins marked with the number two, and so forth. The pin location is defined by its count from the left most pin, counting to the right. The channel length is defined by the number of pins included in the problem set. Those pins with the number zero are empty terminals and are not to be connected. The terminal list contains the order of the net connections for the pins, organized from left to right.

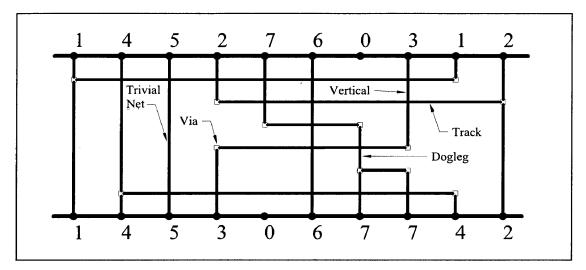

Figure 2.1 Typical Channel Layout

#### 2.2 Definition of Terminology

Several terms will be used throughout this analysis of the channel routing problem. It is appropriate that we define them at this time.

Figure 2.2 Track and Vertical Layout

- **net** the connection between similarly numbered pins

- **multi-net** a net that contains more than two connections to pins

- **sub-net** a portion of a multi-net having two or more terminals

- **terminal** the pin or connection point of a net to the circuit block

- trivial net a net that connects a terminal from the top terminal list with a terminal directly below it in the bottom terminal list

- **track** the horizontal path that a net may travel along the channel

- vertical the vertical path that a net travels from its horizontal track to the terminal of the circuit block

- via the connection between layers of circuitry that connects the track to the vertical of a net

- layer refers to the physical layer within the circuit design on which the circuit lies

- **HVH** a three-layer model with two horizontal layers, one on the top and bottom, with a vertical layer between

• VHV – a three-layer model with two vertical layers, one on the top and bottom, with a horizontal layer between

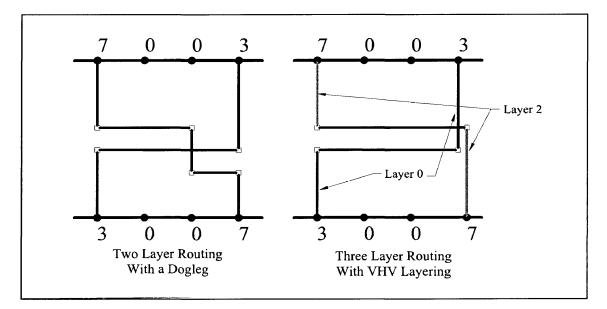

We are using a reserved layer model. This means that one layer is designated strictly for tracks, while another layer is strictly for verticals. In our treatment of the problem, we will be using a two-layer and a three-layer model, with the third layer designated for either tracks or verticals, as the problem set deems necessary. We complete the connection between layers by implementing vias. Vias are used at the ends of tracks to connect to the verticals, and may be used within multi-nets to connect two segments where a dogleg exists. A dogleg is created when a multi-net is assigned to more than one track. The dogleg is the vertical part of the multi-net between tracks, as shown in Figure 2.2.

#### 2.3 Problem Formulation

Our objective is to create an arrangement of nets by assigning them to particular layers and tracks within the channel so that they accurately complete the electrical connections between blocks of circuits. The number of tracks required should be minimized, to offer a more compact layout. Obviously, the exclusion of conflicts between the assigned placement of nets is essential. Other goals can be to minimize the overall length of the routing connections, or the total wire length, and the minimizing of the number of vias required. To better understand what kind of solution is expected, an analysis of the problem set is in order. Several parameters exist that can give us an idea of what to expect for an optimal solution. The use of graph models can be employed to aid us in this analysis.

#### 2.4 Input Analysis

Analyzing the problem set offers us several important parameters that help us identify what an optimal solution should look like. We can first look at the number of tracks necessary to complete the connections. We can determine the minimum number of tracks required by comparing the nets' beginning and ending points, with respect to how they overlap. Two nets that require a common distance of the channel can not be assigned to the same track. By looking at all the nets' spatial relationship to each other, we can determine the minimum number of tracks required. Figure 2.3 shows the terminal layout

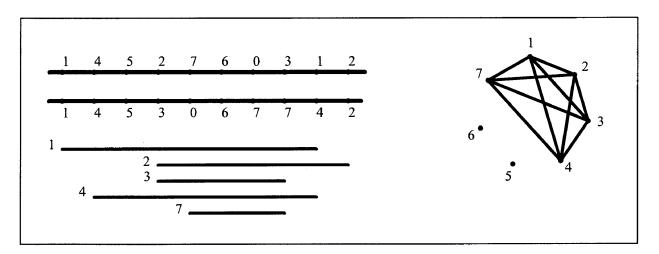

Figure 2.3 Determining the Maximum Clique from the HCG

of a channel. Below it, the nets are arranged beside each other based on their starting and ending points in the channel. Note that nets 5 and 6 are trivial nets and, as such, do not require a track for routing.

If we draw a vertical line through the arrangement of nets, it may cross one or more of them. If we find the placement that crosses the maximum number of nets, we can count the number of nets crossed. This represents the point where the channel would need to be the widest. We can incorporate graph theory to help us in determining this value. The graph for the problem set is created with the nets as nodes, and the overlaps as undirected edges between the nodes. This graph is known as the horizontal constraint graph, or HCG. We can extract the maximum number of nets overlapping each other by calculating the largest group of nodes in which each node contains an edge to every other node in the group. This is more commonly referred to as the maximum clique of the graph. In the HCG, the maximum clique gives us the maximum overlap of the nets, or the minimum track width for the channel. If we use a three-layer model that incorporates two horizontal layers, HVH layering, we have the ability to move half of the nets' tracks to that extra horizontal layer. This allows us to reevaluate the problem set so that now the minimum tracks required is one-half of the maximum clique.

We can also evaluate any possible conflicts between the top and bottom terminal lists. These conflicts are called vertical constraints, and can be easily evaluated using a graph model. Again the nets are used as nodes of the graph, but in this case, we compare the

Figure 2.4 Determining the Longest Path from the VCG

top and bottom terminal lists, column by column, looking for a difference between the top and bottom terminals. This difference is considered a constraint in that the nets can not have their vertical components overlap. Figure 2.4 shows the terminal list with its associated vertical constraint graph, or VCG.

In the VCG, the edge represents the constraint between the upper and lower terminal, and therefore, is a directed graph. If we examine the VCG in figure 2.4, we see a directed edge between nets 2 and 3, 3 and 7, and 1 and 4. Each of these edges indicates the need for at least two tracks to allow room for the verticals of the nets to connect with their respective tracks. To evaluate this graph, we look for the longest directed path between nodes. The length of this path represents a lower bound on the number of tracks required

to connect the nodes of the problem set. In the example above, the longest path would be two for the path from 2 to 3 and 3 to 7.

Another important parameter, which can be extracted from the VCG, gives us a different perspective on constraints. We must also check the vertical constraint graph for the existence of cycles within the directed edges. If a cycle can be detected, we will be unable to define the longest path, as the cycle would provide an infinite path length. Secondly, a cycle indicates that the routing problem being evaluated has a more serious problem. Figure 2.5 shows the terminal layout containing a cyclic vertical constraint. Unless doglegs are used, there is no way to successfully route the example in a two-layer model. A three-layer model, however, will solve the problem by allowing one net's

Figure 2.5 Identifying Cyclcs in the VCG

verticals on the first layer of a VHV layering mode, while the other net's verticals can overlap by placing them on the second vertical layer.

#### 2.5 Summary

We now have an understanding of the channel routing problem, and how to evaluate the problem set so that the parameters of an optimal solution are known. We have defined the terminology used in the study of channel routing, and how we evaluate a problem set. If we can find the maximum clique of the HCG, the longest path of the VCG, and whether the problem set has cyclic vertical constraints, we know what we should expect our algorithm to produce for an optimal solution.

Many others have developed algorithms in an attempt to solve the channel routing problem. We will now provide an overview of several of those processes.

### Chapter 3

## An Overview of Prior Research on Channel Routing

The channel routing problem has existed for close to 35 years. There have been many approaches to the problem, from the single layer approaches, such as those reviewed by M. Marek-Sadowska and T. T. Trang [MT83]. While they appear to be a simpler procedure, there is still intensive computation involved. Single-layer routing problems are known to be NP-complete [RD84].

Two-layer approaches have been discussed in chapter one, but will be presented in greater depth in section 3.1. Three-layer approaches have been more recently proposed. They will be presented following the two-layer algorithms in section 3.2.

We would like to offer a new method of evaluating the channel routing problem. The problem has been approached from many angles, but none have been able to completely encompass all aspects of any given problem set. All seem to have their special circumstances in which they excel. If we look at what has been proposed before, we can then consider what other ways we can break down the problem to provide a more optimal answer for a wider range of input conditions.

#### 3.1 Two-Layer Approaches

As mentioned in chapter 1, several algorithms have been developed to tackle channel routing from a two-layer point of view. As J. Zheng mentions in his thesis, most of the research in this category has been on heuristic methods, due to the NP-hard nature of the problem [ZJ98]. We will examine the LEA family of algorithms, the dogleg routing algorithm, the net merger router, the YACR2 router, greedy channel router, hierarchical method, and finally, the genetic algorithm.

#### 3.1.1 The LEA family of Algorithms

The Left-Edge Algorithm, LEA, was first proposed by Hashimoto and Stevens [HS71]. This algorithm produces an optimal solution for the problem sets it can process, so it is not one of the heuristic algorithms. The algorithm has a limitation in that it will not work on problem sets with vertical constraints.

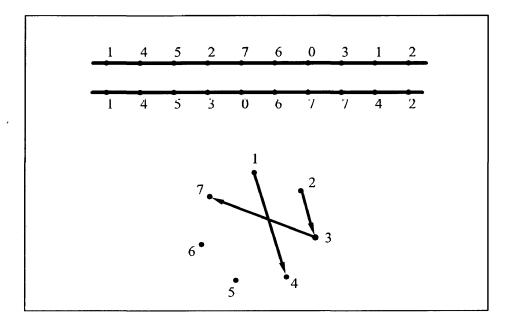

The Left-Edge algorithm begins by sorting the nets in ascending order of their left-most terminal positions. It then places the nets, processing them in their sorted order, into the first available track of the channel. It always begins with the top track and works toward the bottom. A reserved layer policy is used here, so that there is a layer for the verticals and a separate layer for the tracks. An example is shown in figure 3.1.

Figure 3.1 An Example of the Left-Edge Algorithm

This algorithm, while easy to prove its optimal nature, is not very practical. The restriction of not allowing vertical constraints is too limiting, as most channel routing problems contain some vertical constraints. Sherwani points out that it has been found to be a good initial router, which would lay out the basis for the routing scheme, after which, a clean-up procedure could be employed to handle constraints [SN95].

#### 3.1.2 The Dogleg Router

The LEA algorithms were seen to have another shortcoming. Since they assigned the entire net to a single track, in some cases it led to the use of more tracks than was actually necessary. D. N. Deutch (1976) proposed an algorithm he called the Dogleg Router. It was based on the Left-Edge theory, but it would break multi-nets down into simple two-

Figure 3.2 The Dogleg Routing Algorithm

terminal sub-nets before placing them. The vertical between two sub-nets was used to connect them together.

While the algorithm offered benefits over the basic Left-Edge Algorithm, it did add a wrinkle of its own. It could handle vertical constraints between the top and bottom terminal list, but still did not handle cycles in the vertical constraint graph. The process of finding the least number of doglegs to use has been shown to be NP-complete [SG85]. Badly placed doglegs can even increase the number tracks the solution requires. Another problem caused by the excessive use of doglegs is in the length of the path. As this algorithm is also a reserved layer algorithm, extra doglegs would require extra vias. This lengthens the path and can reduce the reliability of the circuit.

## 3.1.3 The Net Merge Router

Another approach to improving upon the LEA, by handling vertical constraints, was presented by Yoshimura and Kuh with their net merging algorithm, called the YK algorithm [YK82]. While previous research made use of the horizontal constraint graph, HCG, to determine the minimum number of tracks required, YK algorithm also makes use of the vertical constraint graph, VCG, to analyze relationships between the nets. The intention is to combine nets that do not have vertical constraints between them so that the number of nets and tracks required can be minimized.

Two conditions must be met to allow the nets to be combined:

- 1. There cannot be an edge between the nodes in the HCG.

- 2. There must not be a directed path from one node to the other in the VCG.

By evaluating two nets without common constraints as one net, the overall amount of calculation can be reduced. The process looks at the channel in zones, rather than looking at it on a column by column basis, so its efficiency is improved. If net i from one zone meets the conditions from net j in another zone, they can be merged together to simplify the analysis for track assignment. This process is repeated until nets can not be combined further, after which the merged nets are placed in tracks.

The process produced good results, although it was restricted by two conditions, it did not allow doglegs, and could not handle cycles in the VCG. Finding optimal pairs of nets for the merging process was difficult to perform. When merging nets, the future effects were difficult to predict.

#### 3.1.4 Yet Another Channel Router

Others evaluating the left-edge approach were finding other ways to handle vertical constraints. Reed, Sangiovanni-Vincentalli, and Santamauro proposed the YACR2 (Yet Another Channel Router) algorithm based on the following observations [RS85]. A vertical constraint is a localized problem. Further, there is usually unused space in the surrounding verticals and tracks that can be used to resolve this constraint, by employing a localized maze routing approach. If constraints cannot be resolved, extra tracks can be added to offer additional space.

A basic LEA is employed to initially assign track placement. Several maze routing techniques are employed to reroute constraints to one side or the other. The entire process is performed in a four-phase process. It begins by finding the column with the highest density in the channel. Phase 1 routes the high-density column, and then phase 2 routes the columns to the right. Phase 3 uses a modified LEA approach to route the left side columns by using a right-edge evaluation, following which phase 4 uses various maze re-routing techniques to resolve constraints.

While YACR2 was efficient, it was a much more elaborate implementation. It did handle vertical constraints well, while minimizing the number of tracks required.

## 3.1.5 The Greedy Channel Router

In 1982, Rivest and Fiduccia developed another twist on the LEA, which they called the greedy channel router [RF82]. They observed that assigning an entire net to just one track was very restrictive. They proposed a process that evaluated the channel from left to right, column by column. In the evaluation, each net within that column was placed in a track, and then the process moves to the next column. In this way, nets may change tracks part way through its path, i.e. a dogleg can occur. There are no restrictions to where a dogleg can occur or how often.

If two ends of a net cannot be connected immediately, the nets are placed on tracks to be pathed to the right. If space develops, the router will use a dogleg to reduce the number of tracks separating them, until an unused vertical is available to connect them. The nets when apart are referred to as split nets, and when the net is finally connected with a vertical, it is referred to as a collapsed net.

The greedy algorithm's biggest advantage is in handling cycles in the VCG. It deals favorably with vertical constraints, and minimizing the number of tracks needed, but has as its weakness the tendency to use too many doglegs and vias.

## 3.1.6 The Hierarchical Method

Others took very different approaches to the topic of channel routing. In 1983, M. Burstein, and R. Pelavin presented their hierarchical router for two-layer channel routing [BP83]. This method used a 'divide and conquer' point of view to net placement. In this method, the channel is reduced in height to a 2 x n channel and this channel is used to route all of the nets. Special Steiner trees are created to route the connections globally. A cost is calculated for each step in the connection path, moving either horizontally or vertically. The net is initially pathed by the lowest cost and then the channel is recursively expanded out as the nets are divided out into individual rows.

The biggest drawback to the hierarchical method is that it cannot handle cycles in the VCG. Otherwise, it also uses a reserved layer model and does allow doglegs. It is reasonably efficient and produces a very good solution.

## 3.1.7 The Genetic Algorithm

As this thesis is an extension of Jingsen Zheng's graduate thesis in 1998, it is important to distinguish his work, for it lays the groundwork for our current research. The genetic algorithm was first proposed by A. T. Rahmani and N. Ono [RO93]. Their approach was to look at the channel routing problem as an optimization problem. A solution to the problem was represented as a vector of positive numbers, with a cost associated that measured how close the solution came to an optimal solution. The cost was calculated based on the number of tracks required and number of violations that occurred. The process created many solutions with the goal of finding the solution with the lowest cost.

Zheng used this as the basis for his genetic algorithm in the following manner. The problem set was initially analyzed to determine its relevant characteristics. The maximum clique was calculated, the VCG was evaluated for cycles, and if none, the longest path was determined. He also calculated the number of nets, terminal density, and average number of terminals per net. These parameters were used to select one of two routing techniques. The first, router-1, did not allow doglegs, and therefore would not handle a cyclic VCG. Router-2 broke down multi-nets into two-terminal sub-nets and would handle most cyclic VCG cases.

The nets are routed, and then a mutation phase modifies the assignments looking for vertical constraint violations. The mutation continues until no progress is made, at which time the output is created and the entire process terminates. The algorithm was most affected by constraints in the HCG and VCG, causing its solutions to vary from problem to problem. Another limitation was that the size of the problem set greatly affected the performance of the algorithm and the amount of memory needed for the computations.

This concludes our overview of the two-layer channel routing approaches. We will now look at the three-layer methods that have been presented so far.

#### 3.2 Three-Layer Approaches

Three-layer channel routing algorithms have begun to surface, due to the increasing availability of three metal layers in chip design. Sherwani points out that the Motorola 2900ETL macrocell array, the Dec Alpha chip, and Intel's 486 and original Pentium chips were all designed using a three-layer design [SN95].

Most all of the three-layer approaches are extensions of two-layer methods. We will look at an extension of the net merge algorithm by Chen and Liu [CL84], another extension of the same by Cong, Wong, and Liu [CW87], and finally a hybrid HVH-VHV router by Ptchumani and Zhang [PZ87].

#### 3.2.1 The Extended Net Merge and CWL Channel Routers

The first of the three-layer approaches to be based on the net merge algorithm was presented by Y. Chen and M. Liu [CL84]. Theirs was an extension of the YK algorithm of Yoshimura and Kuh [YK82]. Their process was to perform two types of merging. The first was serial merging, where two nets have neither horizontal nor vertical constraints, and so can be assigned to the same track and layer. The second was parallel merging, in which there exists a horizontal constraint between two nets, but not a vertical constraint, so the nets can be put on the same track in different layers. The process of creating zones is still incorporated. Cong, Wong, and Liu [CW87] offered another extension of the YK algorithm, which can referred to as the CWL algorithm. Their process was very similar to Yoshimura and Kuh [YK82] in that it merges nets into composite nets based on not having horizontal constraints between the nets based on their zones. They further merged composite nets into super-composite nets where their only constraint was horizontal. This allowed the super-composite nets to be assigned to the same track on different layers.

Evaluating the algorithms, they both suffered from less than optimal results if the net pairings were less than optimal. CWL gave solutions with extra tracks due to adjacent vias in nets being merged.

## 3.2.2 The Hybrid HVH-VHV Router

As a final three-layer example, we look at the channel router developed by V. Pitchumani and Q. Zhang [PZ87]. This process partitions the set of nets into two groups. One group is made up of the nets that lend themselves to an HVH layering scheme, and the other group is made up of those better suited in a VHV layering scheme. A transition track is used to complete the connections between partitions.

The hybrid algorithm does not allow doglegs, and Sherwani indicates that this algorithm is not for all situations [SN95]. He does say that it performs best when the problem set is entirely an HVH or VHV layering group.

# 3.3 Summary

With this analysis of many channel routing algorithms, we see that the problem has been addressed from many different points of view. There have been many two-layer solutions offered, each providing a solution to a particular facet of the problem. Several three-layer algorithms have been developed from two-layer versions to improve upon their results. It is clear that no single algorithm is best for all situations.

We will now present the basis for our multi-layer channel router. First an understanding of the genetic algorithm and how it is applies to solving computationally intensive problems is in order. Afterward, we will present the algorithm for the multi-layer channel router.

# Chapter 4

# The Genetic Algorithm

## 4.1 An Overview

The Genetic Algorithm is patterned after the evolutionary process of 'survival of the fittest'. It mimics the way nature will foster succeeding generations based on their ability to change to better fit in with and make the most of their environment. In nature, a bird with a more sharply pointed bill can better extract insects from a fallen log, and so flourishes. In a similar way, the genetic algorithm creates temporary solutions to a problem, and then uses those solutions to create new solutions, keeping the better solutions and throwing away those that fall further from the optimal.

We first heard of Genetic Algorithms when J. Holland introduced them in 1975 [HJ75]. They were developed to help evaluate the adaptive processes of natural systems. Today, we find them to be a valuable tool in evaluating processes that either have a large search space, or are large in terms of calculations required for an optimal answer. To better define the genetic algorithm's properties, we will use a partitioning problem as an example.

The partitioning problem comes from an earlier phase in the VLSI microchip design. When initially laying out the locations for the circuits, each circuit is defined by a minimum area it must occupy. These circuits are placed together, but must be partitioned into groups for layout purposes. In our example, we will look at how the genetic algorithm can be applied to evaluate the partitioning problem, so that two partitions are created that require nearly the same surface area. This problem can be evaluated optimally for rather small quantities of circuits, but quickly becomes difficult, if not impossible, to analyze by optimal methods as the problem set increases in size, therefore the genetic algorithm is well suited to provide a near optimal solution. Let us first understand the Genetic Algorithm process.

#### 4.2 How the Genetic Algorithm Works

There are several steps involved in the Genetic Algorithm process. The problem must first be properly defined, as well as identifying the requirements the solution must meet. Once defined, a representation of the solution can be determined. The representation should take the form of a string, so that it can be easily manipulated, and is sometimes referred to as the chromosome. A cost must also be defined so that the correctness of a solution can be measured.

After the problem is well defined, initial solutions are derived. These first solutions, called the parent solutions, are then used as the basis to derive additional solutions. These are referred to as the child solutions or offspring. The child solutions are then evaluated by the costing criteria for their ability to solve the problem. The best child

input the problem set analyze input to formulate solution content create parent solutions, cost them, and store best while not done do { for each parent { mutate to create a child solution if fit enough, keep it (cost) } for all children and parents { store the best so far choose new parents } }until done report results

Figure 4.1 The Genetic Algorithm

solutions are kept and then used as the bases to derive more child solutions. The process continues in this fashion, until it fails to show progress. A limiting variable controls the process by increasing with failures until it reaches a maximum value, after which the results are reported. Figure 4.1 shows the pseudocode for the genetic algorithm. We will now look at the key portions of algorithm to analyze its inner processes.

## 4.3 The Mutation Process

The derivation of a child solution is accomplished by a type of mutation. Mutation can be accomplished by several means. In one case, a parent solution can be modified by switching either one or two parts of the solution to create a new solution. As an example, figure 4.2 shows a parent string and the resulting child string after a mutation.

| Example 1<br>Parent:<br>Child: | 1 0 0 <b>1</b> 1 1 0 0 1 0 1 1 1 0 1 1 0 0 1<br>1 0 0 <b>0</b> 1 1 0 0 1 0 1 1 1 0 1 1 0 0 1               |

|--------------------------------|------------------------------------------------------------------------------------------------------------|

| Example 2<br>Parent:<br>Child: | 4 5 3 <b>6</b> 1 2 5 7 9 <b>8 9</b> 0 4 5 3 2 1 2 7<br>4 5 3 <b>9</b> 1 2 5 7 9 <b>8 6</b> 0 4 5 3 2 1 2 7 |

Figure 4.2 Mutation by Switching

The first example would be a possible mutation of the partitioning problem. In that example, the fourth entry has been switched, so that the fourth circuit was changed from one partition to the other. Generally this is performed one unit at a time and then the new solution is evaluated and another switch may be performed. In the second example, the fourth and eleventh positions have been switched. This could apply to a multi-partition problem, or our channel routing problem, in which two nets' placements are switched.

| Example 1 |                                                     |

|-----------|-----------------------------------------------------|

| Parent1:  | 1000110010111011001                                 |

| Parent2:  | 0100101101010100100                                 |

| Child1:   | 1000110 <b>101010100100</b>                         |

| Child2:   | 1 0 0 0 1 1 0 <b>0 1 0 1 1 1 0 1 1 0 0 1</b>        |

|           |                                                     |

| Example 2 |                                                     |

| Parent1:  | 4 5 3 6 1 2 5 7 9 8 9 0 4 5 3 2 1 2 7               |

| Parent2:  | 2487134956132727359                                 |

| Child1:   | 4 5 3 6 1 2 5 7 9 <b>8</b> 9 0 <b>2 7 2 7 3 5 9</b> |

| Child2:   | 248713495613 <b>4532127</b>                         |

|           |                                                     |

Figure 4.3 Mutation by Crossover

Another process, the crossover, involves using two parent solutions to create new child solutions, by taking a portion of one parent and appending to it the complimentary part from the other parent. In figure 4.3, we see two examples of this. For the partitioning problem in example 1, the parents are crossed over starting with the eighth circuit. In the second example, the crossover occurs with the twelfth position.

Still another form of mutation involves reversing the string or chromosome, end for end. This type is referred to as inversion, and can be performed on a part or on the full length of the string. In figure 4.4, example 1, for the partitioning problem, demonstrates the sixth through the thirteenth positions of the string being inverted, while in example 2, the entire string is inverted. Nearly any change can be useful as a means of deriving a new and different solution.

| Example 1 |                              |

|-----------|------------------------------|

| Parent:   | 10011 <b>10010111</b> 011001 |

| Child:    | 10011 <b>11101001</b> 011001 |

| Example 2 |                              |

| Parent:   | 4536125798904532127          |

| Child:    | 7212354098975216354          |

|           |                              |

|           |                              |

Figure 4.4 Mutation by Inversion

Mutation offers several benefits. It should be a randomly applied change so that its result is not necessarily predetermined. This gives us the opportunity to escape local minimums, and try to reach an optimal solution for the problem. Using more than one type of mutation offers increased opportunity for solutions to approach an optimal solution. The value of that solution, to the common goal, is the next issue of investigation.

## 4.4 The Selection Process

After the child solutions are derived, they are evaluated for their fitness, or their ability to solve the problem. This evaluation is very specific to each problem, but usually involves a cost for the solution's suitability in solving that problem. As an example, in the partitioning problem, the total area of each partition can be calculated, and their difference can be used as a cost. As there would be connections between the partitions, another possible costing factor could be the number of connections that travel between the partition may be required. All of these options can be used together, with a weighting factor for each, to promote the more important criteria. Having been defined, we can now use this costing procedure to evaluate both the parents and children for their ability to solve the problem.

The costs for all children and parents are compared, and the lowest cost solution is stored. Several of the solutions are then chosen as the parents for succeeding generations. Multiple policies for retaining a solution as a parent can be used. The best can be saved, or a random sampling can be kept. The important element here is to keep a varied sampling, so that the succeeding generations have some diversity. This offers the possibility to find better solutions and avoid falling into local minimums.

## 4.5 Global Control Parameters

There is also a global component to the evaluation process. As each new solution is created, the evaluation criteria are also changing. There are several control variables involved in the process that should be identified at this time. The first is the variable p, which controls the selection of child solutions. When a new solution is generated, it's cost is calculated and is compared with its parent. The positive or negative gain is compared with this control variable p to see if it is worthy of being retained. The value of p can change depending on the success or failure of child solutions created. If the child solution shows a positive gain, p is kept at it's origination value  $p_0$ . If the succeeding solutions do not show a positive gain, the value of p can decrease to allow solutions to be retained that do not show a positive gain. This again allows for diversity so that local minimums can be overcome.

The other variable used to control the global process is defined as r. The value of r begins at zero, and increases as the newly created generations fail to improve in their suitability to solve the problem. If the new solution is an improvement, the value of r is reduced by a user defined upper bound value, R, for the next child creation. Thus, the

variable, r, increases in value if the process stagnates in its search for a better solution. When the value of r reaches the upper bound, R, the process stops generating new solutions. After the evolution process has terminated, the stored best solution is output.

Another factor that influences the process concerns the manner in which the parent and child solutions are created. The number of parents created and saved, as well as the number of children generated can also affect the quality of the overall outcome. This can also depend on the size of each generation, as a larger generation size will require more memory and tend to reduce the number of parent and child solutions that can be stored. Generally speaking, the greater the number of parents and children that are created, the greater the possibility of reaching an optimal solution quickly and efficiently.

We will now look at the multi-layer channel router problem and how the Genetic Algorithm can be applied to provide an efficient and effective solution. The basis for our using the algorithm is first identified, as well as the way the algorithm is applied. An analysis of the specific data structures used is followed by the details of the processes involved in the algorithm, as they apply to the channel router.

# Chapter 5

# The Multi-layer Channel Router

Because of the complexity of the channel routing problem, a genetic algorithm seems to be an excellent heuristic to find a near optimal solution. By its diversity, it can more easily overcome local minimums. With technology rapidly changing, improvements in the manufacturing process have allowed for an additional layer of circuitry within the chip, to reduce channel width, and help resolve constraints. We can make use of these two ideas as the basis for a new multi-layer channel routing process.

## 5.1 The Basis for the Router Process

The channel routing process begins by looking at the problem itself, to find the most efficient method of connecting similarly numbered pins through a channel, where the pins or terminals are on the top and bottom of the channel. The solution should offer a design with as narrow a channel as feasible, and without conflicts in the circuitry layout. The input for this process is a text file, with the number of terminals per side of the channel as its first entry, followed by a list of the top terminal connection numbers and then the bottom terminal connection numbers. This identifies the terminals that need to be connected and their order along the channel. We want the ability to run the process in a two-layer mode or a three-layer mode.

The process takes, as part of its command line, the input file name. The input file is

evaluated to determine the number of nets required, along with their beginning and

ending points in the channel. A user defined separation variable determines how the nets are assigned. An array of structures, as shown in figure 5.1, stores this information, as well as the net number, as defined by the terminal numbering sequence from the input file. The control parameters are defined by the user, following which the overall characteristics of

struct net { int net num; int strt pin; int end pin; }; struct net netlist[ ];

Figure 5.1 Structure for Basic Net Storage

the problem set are analyzed to determine the best way of approaching the problem. The analysis also involves setting the expectations of a reasonable solution. The greater of the maximum clique of the horizontal constraint graph and the longest path length of the vertical constraint graph can be used as the lower bound for the number of tracks in an optimal solution. The decision as to whether to use two or three layers is made, and if

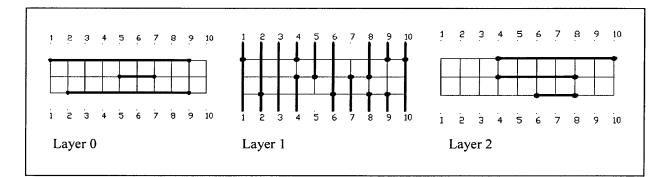

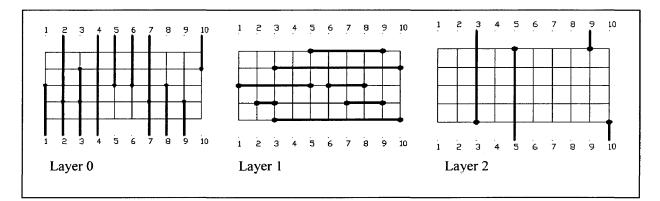

Figure 5.2 HVH Layering Model

Figure 5.3 VHV Layering Model

three layers are chosen, it is determined whether to use the HVH or VHV layering scheme. Figures 5.2 and 5.3 give examples of channel routing using the HVH and VHV layering schemes, respectively.

Following this analysis phase, the initial parent solutions are derived. The parent solutions are sent through a compaction process that tries to minimize the number of tracks necessary, as well as expanding when conflicts arise between two nets vying for the same space. The parents are then evaluated using a costing routine to determine the best solution so far, and that solution is stored for future evaluation. Each parent is then used as the basis for generating several children via a mutation process. As each child is produced, it is run through the compaction process, and then evaluated for its fitness. Based on the evaluations of both the children and parents, a portion of the group is chosen to be the parents for the next generation. This process continues until an exit control variable reaches a user defined maximum value. All through the process, the

child solutions are compared against the best solution, and if an improvement is found, the new solution is saved.

After the genetic portion of the algorithm has concluded, the reporting phase outputs the best solution to a file that can be input into AutoCAD<sup>®</sup>, a computer-aided design package, to visually display the channel layout. The display can then be analyzed for its accuracy and desirability in a three-dimensional manner on screen.

Now that we have the basic flow of the process, we will look more closely at the actual components of each process to get a better understanding of what takes place. An understanding of the data structures involved is presented first.

## 5.2 Data Structures Used

There are a number of arrays used in the process, several to store the net information and layout, while others are used during the analysis phase. Two arrays, *t\_in* and *b\_in* store the top and bottom terminal lists, respectively. Another two arrays, *left\_pt\_list* and *right\_pt\_list*, store the nets by net number based on their left and right points in the terminal list. *Netlist* is an array of structures, see Figure 5.1 earlier, that stores the nets' base information of net number, starting point and ending point. *Sol* is another array of structures, this one storing the various solutions created by the process. This array, as shown in Figure 5.4, is two-dimensional, the first index identifying the solution number,

and the second specifying which net in *netlist* it addresses. The structure within this array defines what layer and track number are to be used for a particular net. The small storage space required for these two arrays, allows us to handle larger problem sets without memory overflows. Finally, the array, *Solcost*, stores the costs involved with each solution generated.

struct layout {

int track;

int layer;

};

struct layout sol[];

To handle the analysis of the problem set, vcg is a two-dimensional array used to calculate the vertical constraint graph. *Color* is an array used to perform depth first search analysis, while *saved* stores the solution numbers that will be used as parents for the next generation. Within several of the subroutines, the array *lyr\_ck* is used to track net placement so that conflicts in assigned location can be identified.

There are also a number of variables to be identified, that handle special storage needs. The control variables, *sep*, *p*, *p*<sub>0</sub>, *r*, and *bigr* are used to adjust the performance of the algorithm. *Sep* controls the number of terminals a net can have. A value of two creates two terminal nets, while a value of four would create nets with up to four terminals. The variable, *p*, controls the selection of child generations, with *p*<sub>0</sub> storing the base value. The variable, *r*, controls the termination of the genetic process. The value of *r* increases as the process doesn't progress, or is reduced by *bigr*, when it does generate beneficial solutions. As r increases, *bigr* also serves as a termination value for the value of r.

Additionally, there are several variables used to track some of the settings used within the algorithm. The value of the highest numbered net is stored in *top\_net*, *total\_nets* stores the total number of nets created, *total\_seg* stores the number of non-trivial nets, and *total\_term* stores the number of terminals contained in the problem set. The maximum clique of the horizontal constraint graph is calculated and stored in *max\_clique*, *longestpath* stores the length of the longest path in the vertical constraint graph, *layers* stores the number of layers in use, and *vhv* is set to true if the vertical constraint graph signals that a cycle exists. This would require two vertical layers to resolve the conflict. Several other less significant variables handle loop counting, true / false values, and string values used for file access.

# 5.3 Process Elaboration

We will now look more closely at several of the modules involved in the genetic algorithm for multi-layer channel routing to get a better understanding of their functions. An examination of the sub-routines that handle creating nets, finding the maximum clique, vertical constraints, and longest path will be performed. We will also look at the routines that handle creating the parent solutions, costing and compacting them, mutating parent solutions into child solutions, the update routine that modifies p, which determines

whether to keep possible solutions, and finally the output function that creates an output file to create a graphic representation using AutoCAD<sup>®</sup> Release 2000.

## 5.3.1 Creating Nets

The process of creating nets, from the top and bottom terminal lists, makes use of the variable *sep*. The terminal lists are evaluated from left to right. The process searches for the terminal numbers corresponding to the first net, and then determines where net-1 begins and ends. Figure 5.5 shows an overview of the algorithm.

for i = 1 to the number of terminals do {

set the count for this net to zero

for each terminal do {

if the net # for top or bottom matches i then {

if count = 0 then store this as a starting point

else { store the point as an end point

add 1 to count

if count = the separation value then

use current point as start of new net

}

}

}

Figure 5.5 Net Creation

The variable *sep* is used to specify how many terminals can be included in each net. As an example, if net X contains five terminals throughout the length of the channel, and if

*sep* has a value of two, then four nets would be created, between the first and second of its terminals, between the second and third, etcetera. Under the same conditions, if *sep* had a value of three, there would be two nets created between its terminals one and three, and between three and five. If, as a final example, *sep* had a value of four, then there would still be two nets created, but this instance would have a net from its first to fourth terminal and a second net from the fourth to fifth.

The process continues by looking for the terminals marked as having net number two attached, to create nets as defined by the value of *sep*, until the maximum number of terminals has been evaluated.

## 5.3.2 Finding the Maximum Clique

The process of finding the maximum clique is taken from the work of Jingsen Zheng [ZJ98]. On pages 39 and 40, he describes a process that calculates the maximum clique of the problem set. We first want to identify the intervals that each net will require. Each net is evaluated to retrieve its starting and ending points, and the net number is recorded in the *left\_pt\_list* and *right\_pt\_list* arrays in the locations of these points, respectively. We can then traverse the arrays from left to right, incrementing the value of the variable *clique* for each net that is encountered in the left point list and decrementing each time a net number is encountered in the right point list. The maximum value of *clique* is stored

for each net segment do {

place its net # in the left point list at its starting point

place its net # in the right point list at its ending point

}

for each entry in the list do {

if the left point list has a net starting then

add 1 to clique

if the right point list has a net ending then

subtract 1 from clique

}

return the maximum clique value

Figure 5.6 Maximum Clique

and is returned as the value of the maximum clique upon termination of the routine. Figure 5.6 shows the algorithm for finding the maximum clique.

## 5.3.3 Evaluating the Vertical Constraints, Cycles, and the Longest Path

An evaluation of vertical constraints in the problem set offers several valuable pieces of information. A graph of the vertical constraints, or VCG, can be created, which can then be used to search for cycles in the net design, and can also be used to determine the longest path of the VCG. This is particularly helpful in defining a lower bound on the number of tracks when a single layer is used for the horizontal tracks.

The vertical constraint graph is stored in an n x n array called vcg, where n is the number of terminals in the problem set. In figure 5.7, we see the algorithm used to create the

for each terminal do {

if the top net # is zero or the bottom net # is zero or

the top and bottom net #s are the same then

continue

else vcg[top net #][bottom net #] =1

}

Figure 5.7 Creating the Vertical Constraint Graph

VCG. The initial creation of the VCG is performed by evaluating the top and bottom terminal lists together. The terminal lists are compared, starting with their first pins respectively and moving toward the other end. The evaluation consists of checking to see if at least one of the pins is labeled with a net number of zero, indicating that there is no net on that pin, or that the pins have the same net number. If neither of these conditions is true, then *vcg* is marked with the number one (1) to indicate a vertical constraint in the position using the net numbers from the top list as the first index, and the net number from the bottom list as the second index.